Faculty of Information Technology

Czech Technical University in Prague

Department of Digital Design

Master's thesis

Design of a digital I2C slave IP block

Jan Vošalík

Supervisor: Ing. Jan Schmidt, Ph.D.

| Acknowledgement                                                                                                                           |                        |

|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| I would like to express thanks to Ing. Stanislav Trojan and Ing. Jan Schmid guidance and leadership during my work on my Master's thesis. | t PhD. for their help, |

|                                                                                                                                           |                        |

|                                                                                                                                           |                        |

| Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I hereby declare that the presented thesis is my own work and that I have cited all sources of information in accordance with the Guideline for adhering to ethical principles when elaborating an academic final thesis.                                                                                                                                                                                                                                                                                                                                                                                 |

| I acknowledge that my thesis is subject to the rights and obligations stipulated by the Act No. 121/2000 Coll., the Copyright Act, as amended. I further declare that I have concluded an agreement with the Czech Technical University in Prague, on the basis of which the Czech Technical University in Prague has waived its right to conclude a license agreement on the utilization of this thesis as a school work under the provisions of Article 60(1) of the Act. This fact shall not affect the provisions of Article 47b of the Act No. 111/1998 Coll., the Higher Education Act, as amended. |

| In Prague on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## **Abstrakt**

Nízká spotřeba se stala velice důležitou součástí návrhu dnešních čipů. Cílem této diplomové práce je návrh zařízení pro přenos dat mezi I2C a APB sběrnicemi za použití technik pro nízkou spotřebu. Verifikace je též součástí práce.

Práce nejprve srovnává různé techniky návrhu zařízení s nízkou spotřebou. Jako výsledek tohoto porovnání bylo v návrhu užito techniky hradlování hodin. Byla provedena analýza s patřičným odůvodněním popisující, na které registry bylo hradlování hodin použito.

Jednotlivé kroky postupu začínají od specifikace a pokračují až po fyzický design. Verifikace byla provedena samokontrolními testy. Pokrytí kódu je v práci rovněž užito společně s grafickou ukázkou pokrytí stavových strojů.

Pro možnost srovnání více výsledků bylo užito více metod hradlování hodin, kterými jsou: hradlování nepoužito, automatické hradlování (provedeno během syntézy), manuální hradlování (manuálně vloženy hradlovací buňky) a kombinovaná metoda manuálního a automatického hradlování.

Odhad spotřeby (nástroji k tomu určenými) byl proveden jak po syntéze, tak po fyzickém návrhu. Odhady, které byly provedeny po fyzickém návrhu, byly provedeny pro mód nečinnosti a komunikační mód zařízení. Výsledky odhadu spotřeby jsou porovnány a ukázány jsou i případy užití a spotřeba u těchto případů.

Klíčová slova: RTL, I2C, APB, low power design, clock gating, odhad spotřeby.

#### **Abstract**

Low power has become a very important part of designing today's chips. The goal of this thesis is to design a device for transmitting data between I2C and APB buses while considering low power techniques in the design. Verification is also a part of this thesis.

This thesis first compares the different techniques used for low power design. As a result of the comparison, clock gating technique is used in the design. An analysis was done to describe the registers that the clock gating is used for, and the reasons to use clock gating at these registers.

The work flow goes from specification to physical design. Verification was done using self-checking tests and code coverage is also used in the thesis, along with graphical examples of FSM coverage.

Four different methods of clock gating were used to compare different results. These methods are: no clock gating use, automatic clock gating (placed during synthesis), manual clock gating (manually placed cells), and manual clock gating, combined with automatic clock gating.

Power estimations were done and compared after the synthesis, as well as after the physical design. The power estimations done after the physical design, were done for idle and communication mode of the device. The results of the power consumption estimation are compared and use cases are shown, as well with their power consumption.

Keywords: RTL, I2C, APB, low power design, clock gating, power estimation.

# Content

| Co | ontent       | X                                        |

|----|--------------|------------------------------------------|

| Fi | gure index   | xv                                       |

| Τa | able index   | xvii                                     |

| U  | sed abbrevia | ationsxviii                              |

| 1  | Introduc     | tion                                     |

|    | 1.1 The      | purpose and goals of this document       |

|    | 1.2 Brie     | f overview of each chapter               |

|    | 1.2.1        | Chapter 1 - Introduction                 |

|    | 1.2.2        | Chapter 2 - Protocols descriptions2      |

|    | 1.2.3        | Chapter 3 - Low-Power techniques         |

|    | 1.2.4        | Chapter 4 - Design and Verification flow |

|    | 1.2.5        | Chapter 5 - Power consumption results    |

|    | 1.2.6        | Chapter 6 - Summary                      |

| 2  | Protocol     | s descriptions                           |

|    | 2.1 I2C      | Protocol description4                    |

|    | 2.1.1        | Speed modes                              |

|    | 2.1.2        | SDA and SCL Signals                      |

|    | 2.1.3        | Reserved addresses5                      |

|    | 2.1.4        | Data transfer example5                   |

|    | 2.1.5        | Start and Stop condition                 |

|    | 2.1.6        | Data validity 6                          |

|    | 2.1.7        | Clock stretching                         |

|    | 2.1.8        | Write operation example                  |

|    | 2.1.9        | Read operation example                   |

|    | 2.1.10       | Combined operation example               |

|    | 2.2 APB      | Protocol description                     |

|    | 2.2.1        | Operating states                         |

|    | 2.2.2        | APB Signals detailed description         |

|    | 2.2.3        | Write transfer without waiting states    |

|    | 2.2.4        | Write transfer with waiting states       |

|    | 2.2.5        | Read transfer without waiting states     |

|   | 2.2        | .6      | Read transfer with waiting states                             | 12 |

|---|------------|---------|---------------------------------------------------------------|----|

| 3 | Lov        | v-Pow   | ver techniques                                                | 13 |

|   | 3.1        | Low     | power design motivation                                       | 13 |

|   | 3.2        | Тур     | es of power consumption                                       | 13 |

|   | 3.2        | .1      | Dynamic power                                                 | 13 |

|   | 3.2        | .2      | Static (leakage) power                                        | 15 |

|   | 3.3        | Low     | power techniques overview and comparing                       | 16 |

|   | 3.4        | Cloc    | k-gating                                                      | 18 |

|   | 3.4        | .1      | Automatic clock gating done by Synthesis tools / Clock gating | 20 |

|   | 3.4        | .2      | Manual clock gating / Clock tree gating                       | 20 |

|   | 3.5        | Milt    | iple-Vt                                                       | 20 |

|   | 3.6        | Mul     | ti Vdd                                                        | 20 |

|   | 3.6        | .1      | Level Shifters                                                | 21 |

|   | 3.7        | Mul     | ti-level voltage scaling (MVS), Dynamic voltage scaling (DVS) | 22 |

|   | 3.8        | Dyn     | amic voltage and frequency scaling (DVFS)                     | 22 |

|   | 3.9        | Ada     | ptive voltage scaling (AVS)                                   | 23 |

|   | 3.10       | Pow     | ver gating (Power Switching)                                  | 24 |

|   | 3.1        | 0.1     | How Power gating works                                        | 24 |

|   | 3.1        | 0.2     | Ways how to shut down blocks                                  | 24 |

|   | 3.1        | 0.3     | Power switches                                                | 25 |

|   | 3.1        | 0.4     | Isolation cells                                               | 25 |

|   | 3.1        | 0.5     | Enable level shifter                                          | 26 |

|   | 3.1        | 0.6     | Retention registers                                           | 27 |

|   | 3.1        | 0.7     | Always on logic                                               | 28 |

|   | 3.11       | Con     | clusion of the listed low-power techniques                    | 29 |

|   | 3.1        | 1.1     | Clock gating and clock tree gating                            | 29 |

|   | 3.1        | 1.2     | Multi Vdd, SVS                                                | 29 |

|   | 3.1        | 1.3     | DVS, MVS, DVFS, AVS                                           | 29 |

|   | 3.1        | 1.4     | Power gating, Power Shut-Off                                  | 29 |

|   | 3.1        | 1.5     | Pipelining                                                    | 29 |

|   | 3.1        | 1.6     | Asynchronous design                                           | 29 |

|   | 3.1        | 1.7     | Conclusion                                                    | 29 |

| 4 | Des        | sign ar | nd Verification flow                                          | 31 |

|   | <i>1</i> 1 | Intro   | oduction                                                      | 21 |

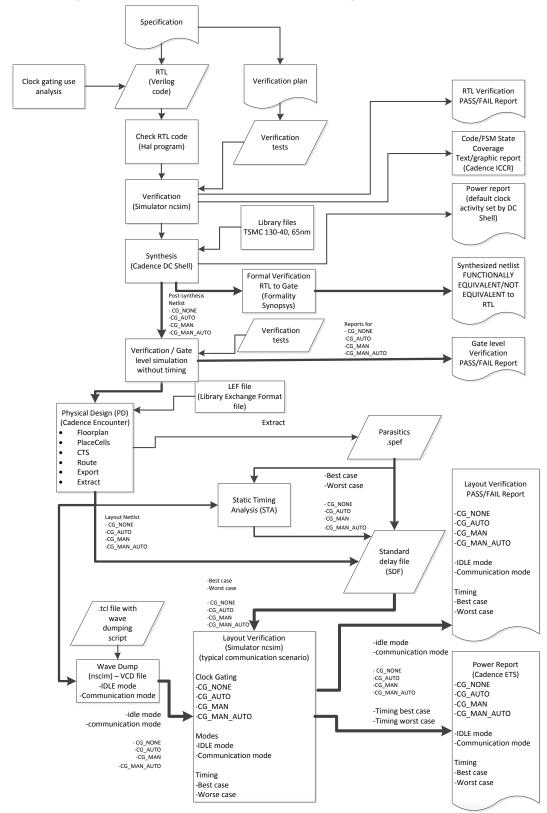

| 4.2 | Desi | gn and verification flow diagram                                                   | 32 |

|-----|------|------------------------------------------------------------------------------------|----|

| 4.3 | Spec | cification                                                                         | 33 |

| 4.3 | .1   | General description                                                                | 33 |

| 4.3 | .2   | Typical usage / Typical communication scenario                                     | 34 |

| 4.3 | .3   | Other functions of the DP device except the typical communication scenario $\dots$ | 34 |

| 4.3 | .4   | Register map                                                                       | 34 |

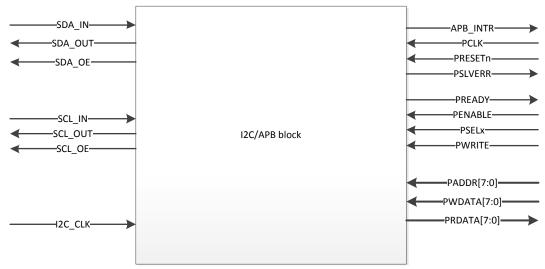

| 4.3 | .5   | Top level description                                                              | 36 |

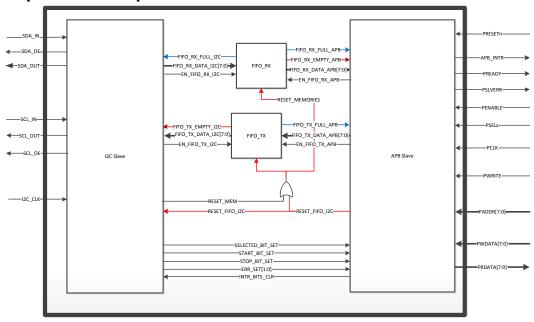

| 4.3 | .6   | Functional descriptions                                                            | 36 |

| 4.3 | .7   | I2C                                                                                | 38 |

| 4.3 | .8   | APB                                                                                | 44 |

| 4.3 | .9   | FIFOs                                                                              | 49 |

| 4.3 | .10  | Clock requirements                                                                 | 49 |

| 4.4 | Anal | ysis of clock gating use in the design                                             | 50 |

| 4.4 | .1   | Clock gating types                                                                 | 50 |

| 4.4 | .2   | Clock-gating analysis in I2C block                                                 | 50 |

| 4.4 | .3   | Clock-gating analysis in APB block                                                 | 52 |

| 4.4 | .4   | Clock-gating code example                                                          | 52 |

| 4.5 | RTL. |                                                                                    | 53 |

| 4.5 | .1   | Coding                                                                             | 53 |

| 4.5 | .2   | Resynchronization between the clock domains                                        | 53 |

| 4.5 | .3   | Signals for DFT                                                                    | 54 |

| 4.5 | .4   | I2C Slave Default address                                                          | 54 |

| 4.5 | .5   | Changing APB addresses for operations                                              | 54 |

| 4.5 | .6   | Fifos                                                                              | 54 |

| 4.6 | RTL  | code check (Hal)                                                                   | 54 |

| 4.7 | Veri | fication                                                                           | 55 |

| 4.7 | .1   | Introduction to verification                                                       | 55 |

| 4.7 | .2   | Verification strategy                                                              | 56 |

| 4.7 | .3   | Frequencies used during verification                                               | 57 |

| 4.7 | .4   | Verification Plan                                                                  | 58 |

| 4.7 | .5   | Code coverage                                                                      | 60 |

| 4.8 | Synt | hesis                                                                              | 64 |

| 4.8 | .1   | What happens during synthesis                                                      | 64 |

| 4.8 | .2   | Synthesis nower consumption                                                        | 64 |

|   | •   | 4.8.3 | 3     | Synthesis power consumption summary                        | 66 |

|---|-----|-------|-------|------------------------------------------------------------|----|

|   | 4.9 | )     | Forn  | nal verification RTL to Gate                               | 66 |

|   | 4.1 | LO    | Veri  | fication – Gate level simulation without timing            | 66 |

|   | 4.1 | l1    | Phys  | ical design                                                | 66 |

|   |     | 4.11  | .1    | Introduction                                               | 66 |

|   |     | 4.11  | .2    | Floorplan                                                  | 67 |

|   |     | 4.11  | .3    | Place cells                                                | 67 |

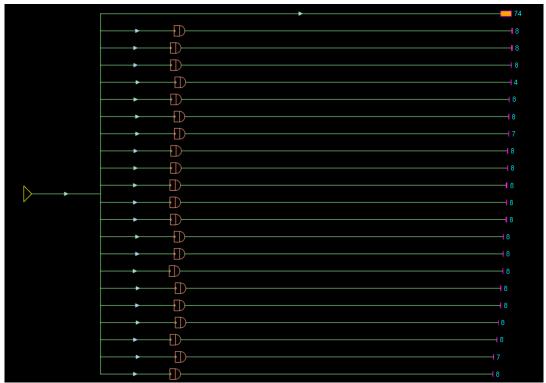

|   |     | 4.11  | .4    | Clock tree synthesis                                       | 67 |

|   |     | 4.11  | .5    | Root                                                       | 72 |

|   |     | 4.11  | .6    | Export                                                     | 72 |

|   |     | 4.11  | .7    | Extract                                                    | 72 |

|   |     | 4.11  | .8    | Final Floorplan                                            | 72 |

|   | 4.1 | L2    | Layo  | ut Verification with timing                                | 75 |

|   |     | 4.12  | .1    | Description                                                | 75 |

|   |     | 4.12  | .2    | Layout Verification Power reports for timing worst case    | 75 |

| 5 | ı   | Pow   | er co | nsumption results                                          | 78 |

|   | 5.1 | L     | Pow   | er consumption results                                     | 78 |

|   | 5.2 | 2     | Pow   | er consumptions results evaluation                         | 79 |

|   |     | 5.2.1 | L     | Automatic clock gating                                     | 79 |

|   |     | 5.2.2 | 2     | Manual clock gating                                        | 79 |

|   | į   | 5.2.3 | 3     | Manual + automatic clock gating combination                | 80 |

|   | 5.3 | 3     | Prac  | tical examples of use                                      | 80 |

|   |     | 5.3.1 | L     | DP IP block as a device assessing a memory                 | 80 |

|   | į   | 5.3.2 | 2     | DP IP block as a device accessing temperature measure unit | 81 |

|   |     | 5.3.3 | 3     | Summary                                                    | 82 |

| 6 | ;   | Sum   | mary  | ·                                                          | 83 |

|   | 6.1 | L     | Goal  | S                                                          | 83 |

|   | 6.2 | 2     | Low-  | -power techniques                                          | 83 |

|   | 6.3 | 3     | Wor   | kflow and power estimations                                | 83 |

|   | 6.4 | ļ     | Veri  | fication                                                   | 83 |

|   | 6.5 | 5     | IP cc | ore                                                        | 84 |

|   | 6.6 | 5     | Resu  | ılts                                                       | 84 |

|   | (   | 6.6.1 | L     | Automatic placing of the clock gating cells                | 84 |

|   | (   | 6.6.2 | 2     | Manual placing of clock gating cells                       | 84 |

|    | 6.6. | The combination of manual and automatic clock gating | 84 |

|----|------|------------------------------------------------------|----|

| (  | 6.7  | Conclusion                                           | 84 |

| 7  | Refe | erences                                              | 86 |

|    | 7.1  | References cited                                     | 86 |

|    | 7.2  | Other used literature                                | 87 |

| A. | Арр  | endix – Regression report                            | 88 |

| В. | Арр  | endix – Schematics from Novas Verdi                  | 89 |

| C. | Stru | icture of the enclosed CD                            | 97 |

# Figure index

| Figure 1: Connection of the DP device among other devices in a system             | 1              |

|-----------------------------------------------------------------------------------|----------------|

| Figure 2: Complete data transfer                                                  | 5              |

| Figure 3: START and STOP conditions                                               | 6              |

| Figure 4: Bit transfer on I2C bus – data validity                                 | 6              |

| Figure 5: I2C Write operation example                                             | 7              |

| Figure 6: I2C Read operation example                                              | 7              |

| Figure 7: I2C Combined operation example                                          | 7              |

| Figure 8: APB Operating states                                                    | 8              |

| Figure 9: Write transfer without waiting states                                   | 10             |

| Figure 10:APB Write transfer with waiting states                                  | 11             |

| Figure 11: Read transfer without waiting states                                   | 11             |

| Figure 12: APB Read transfer with waiting states                                  | 12             |

| Figure 13: Switching power                                                        | 13             |

| Figure 14: Internal power                                                         | 14             |

| Figure 15: Static leakage currents                                                | 15             |

| Figure 16: Low Power Techniques comparison                                        | 17             |

| Figure 17: Principle of clock-gating connection (not completely correct)          | 18             |

| Figure 18: Glitches in latch free clock gating                                    | 19             |

| Figure 19: Correct clock-gating cell connection – connection in a dont_touch cell | 19             |

| Figure 20: Multi Vdd blocks connection                                            | 21             |

| Figure 21: Blocks with different Level shifter                                    | 21             |

| Figure 22: DVFS blocks                                                            | 22             |

| Figure 23: AVS blocks                                                             | 24             |

| Figure 24: Power-switching Network Transistors                                    | 25             |

| Figure 25: Use of isolation cell                                                  | 26             |

| Figure 26: Level shifter                                                          | 26             |

| Figure 27: Retention register                                                     | 27             |

| Figure 28: Connection of retention register signals                               | 28             |

| Figure 29: Always on logic                                                        | 28             |

| Figure 30: Design and Verification flow diagram                                   | 32             |

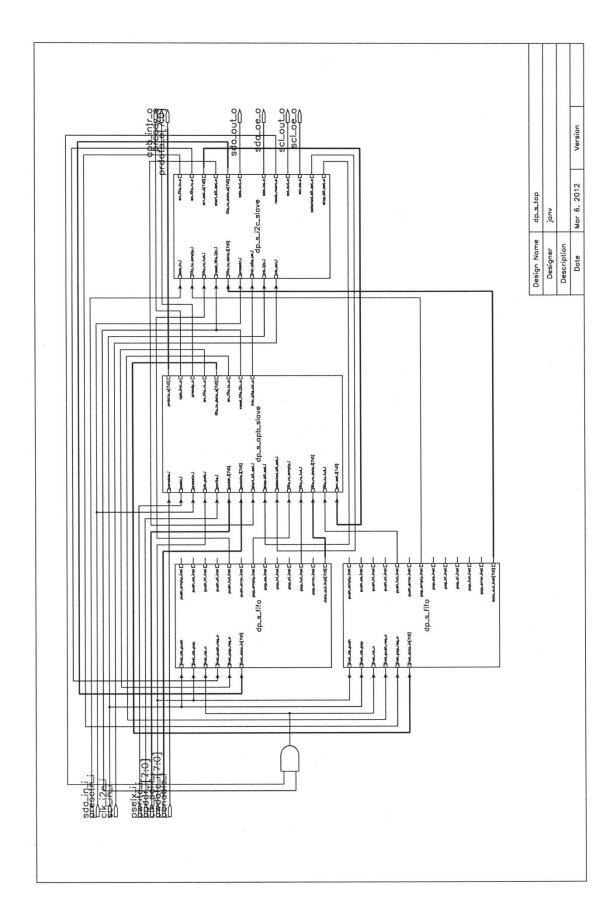

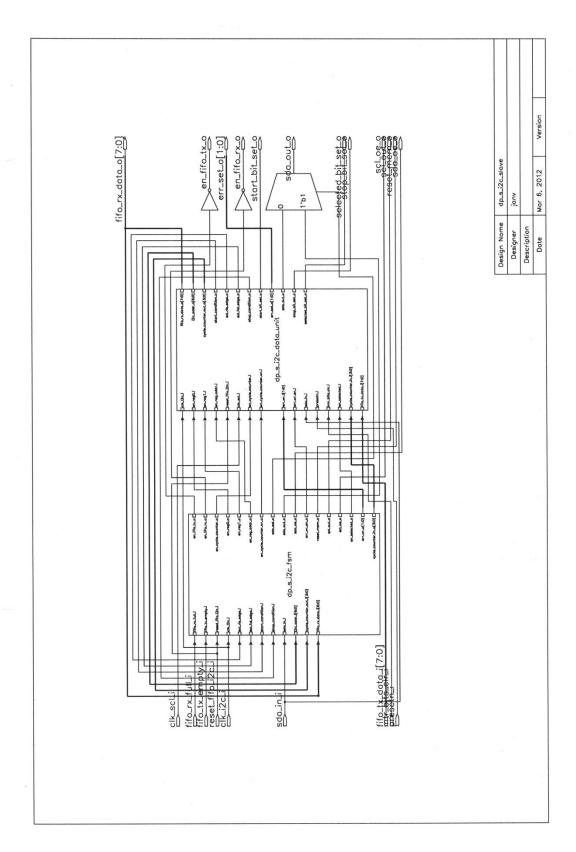

| Figure 31: Top-level schema of the I2C/APB Block                                  | 33             |

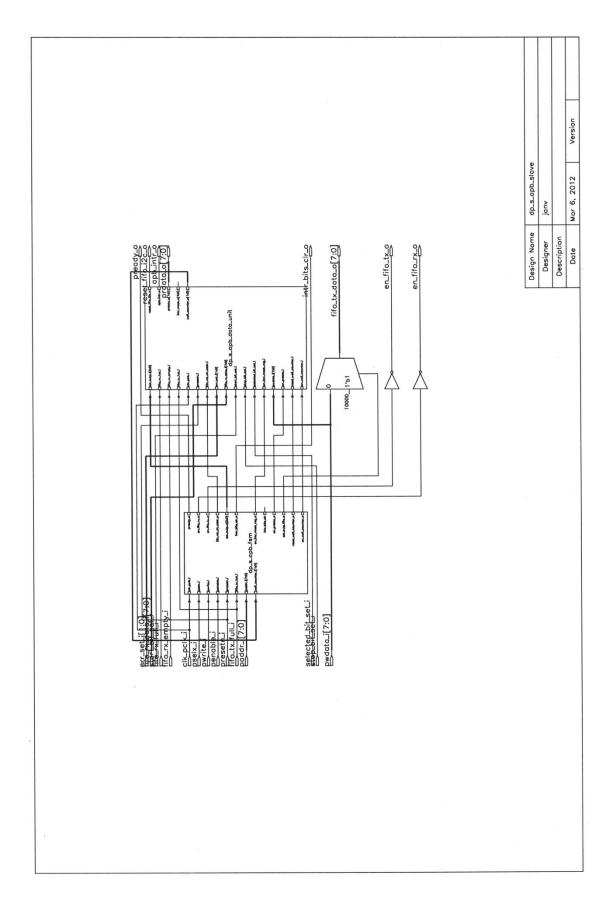

| Figure 32: Top-level schema of I2C/APB Blocks                                     | 36             |

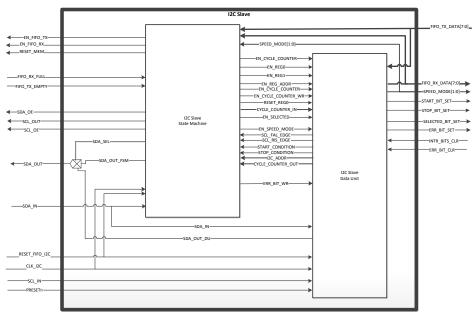

| Figure 33: I2C Slave block diagram                                                | 38             |

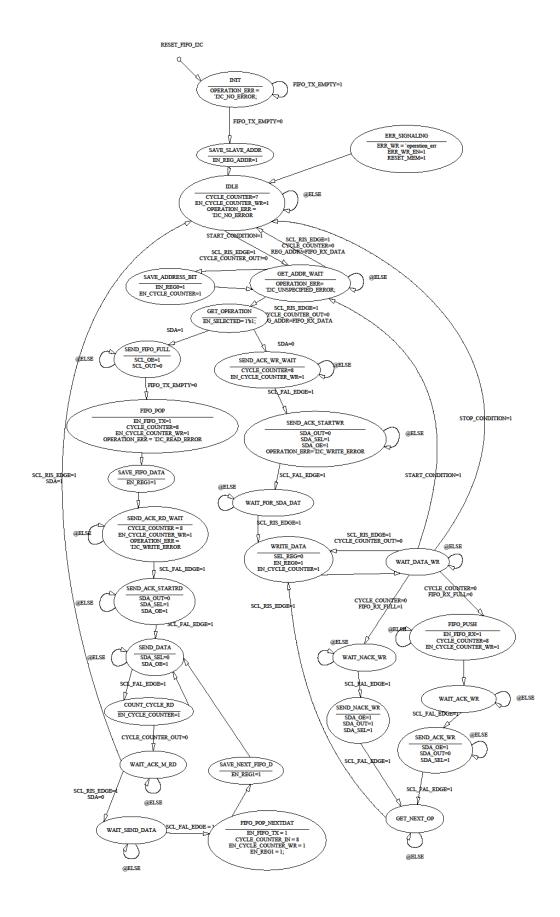

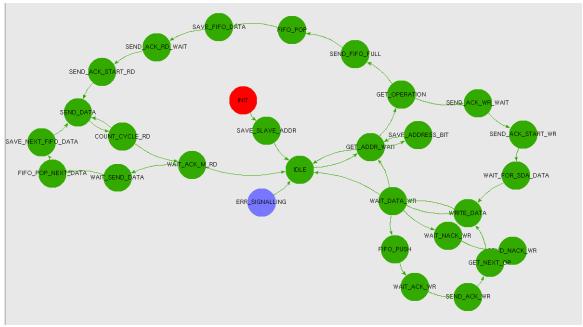

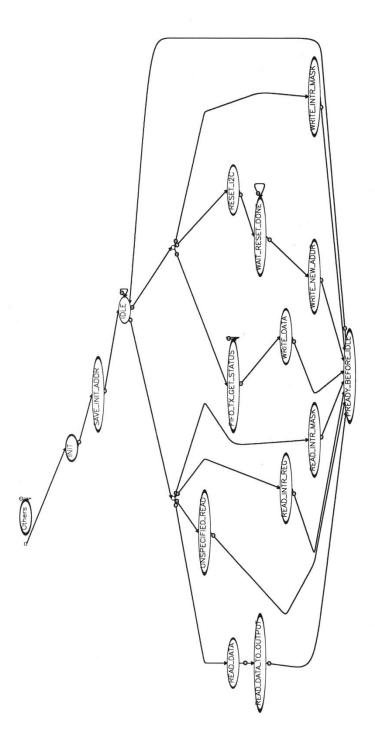

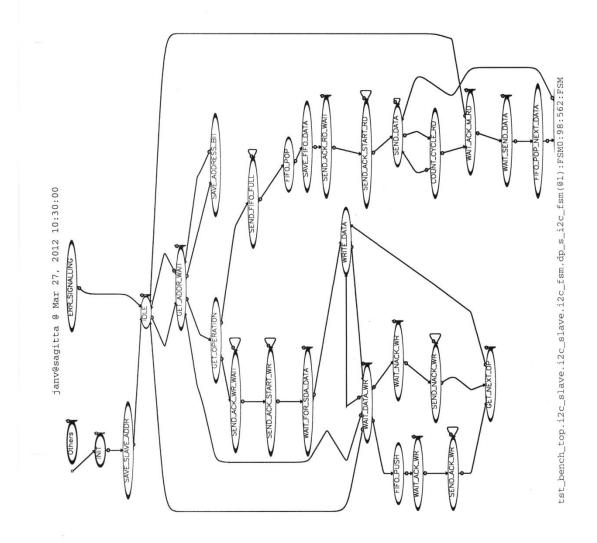

| Figure 34: I2C FSM Diagram                                                        | 40             |

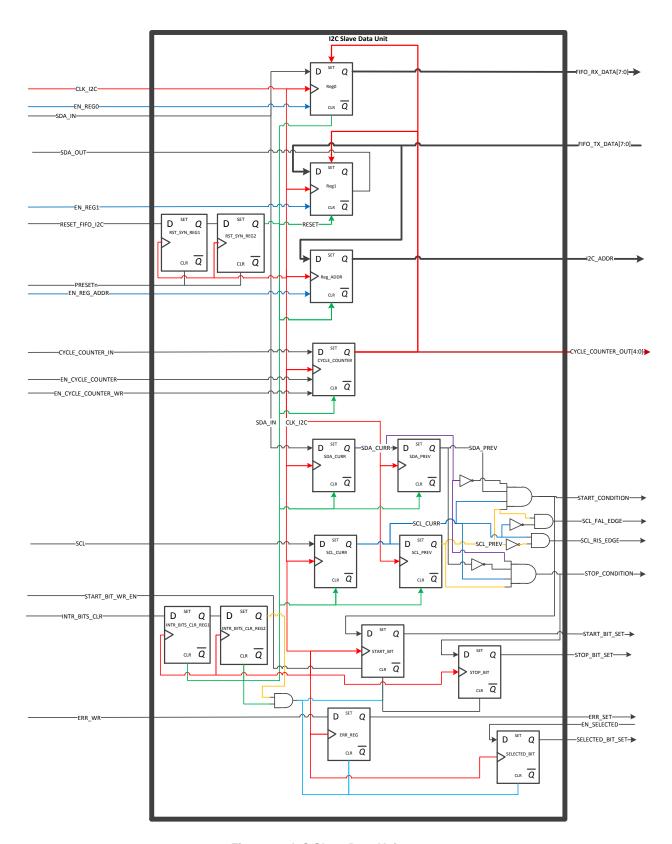

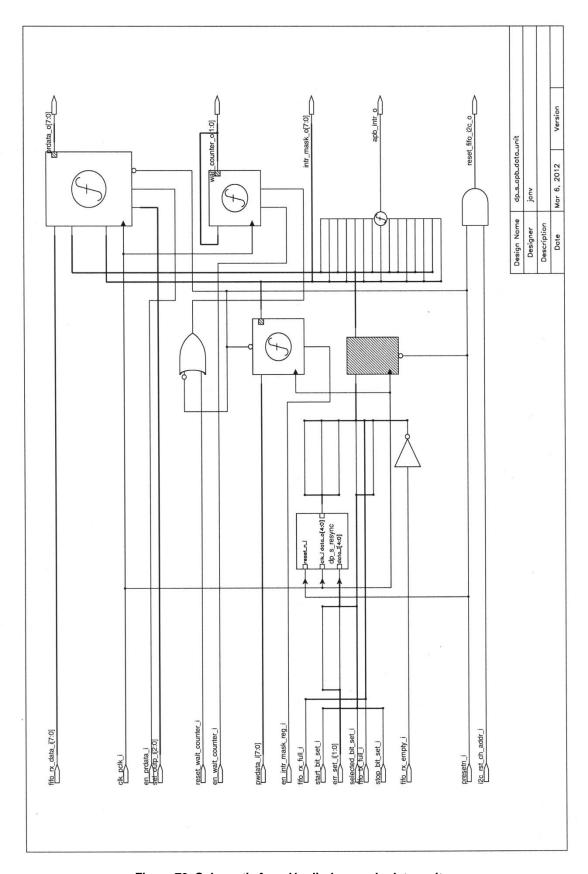

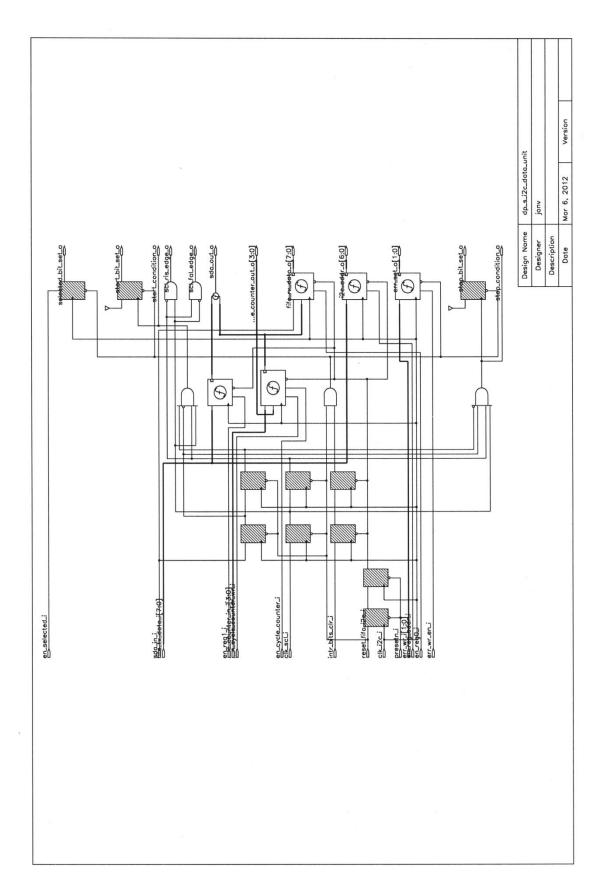

| Figure 35: I2C Slave Data Unit                                                    | 43             |

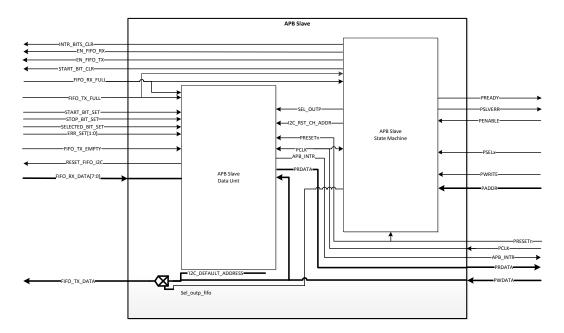

| Figure 36: APB Block diagram                                                      | 45             |

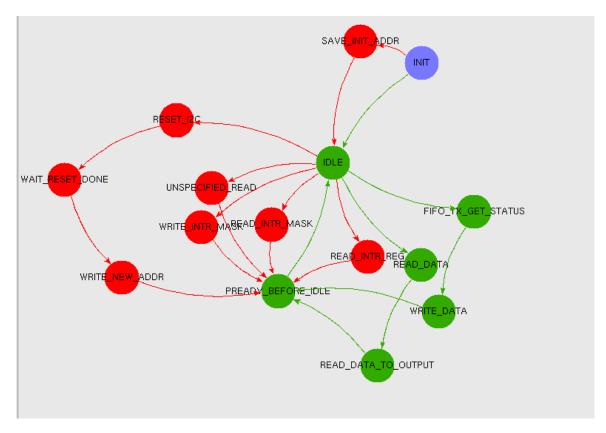

| Figure 37: APB FSM Diagram                                                        | 16             |

|                                                                                   | 40             |

| Figure 38: APB Block Data Unit                                                    |                |

| Figure 38: APB Block Data Unit<br>Figure 39: Clock gating code example            | 48             |

| -                                                                                 | 48<br>53       |

| Figure 39: Clock gating code example                                              | 48<br>53<br>55 |

| Figure 43: Code coverage code/data overview                             | . 61 |

|-------------------------------------------------------------------------|------|

| Figure 44: Implicit else example                                        | . 61 |

| Figure 45: APB FSM state coverage (not using default I2C Slave address) | . 62 |

| Figure 46: I2C FSM state coverage                                       | . 63 |

| Figure 47: APB FSM state coverage (using default I2C Slave address)     | . 63 |

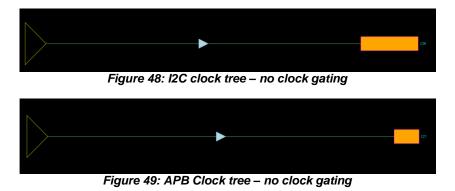

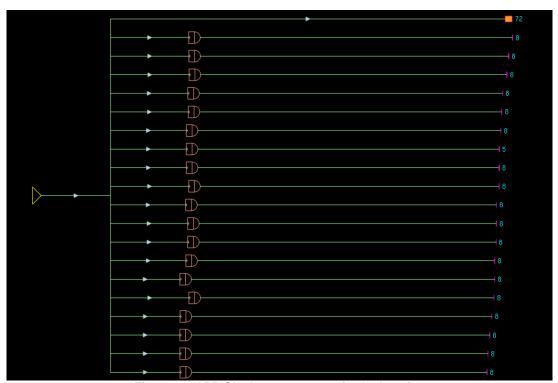

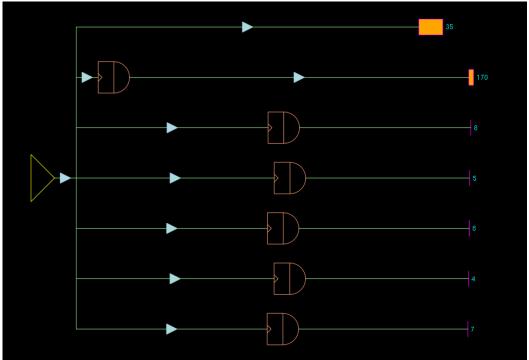

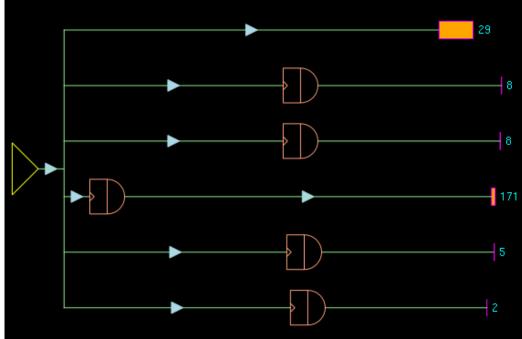

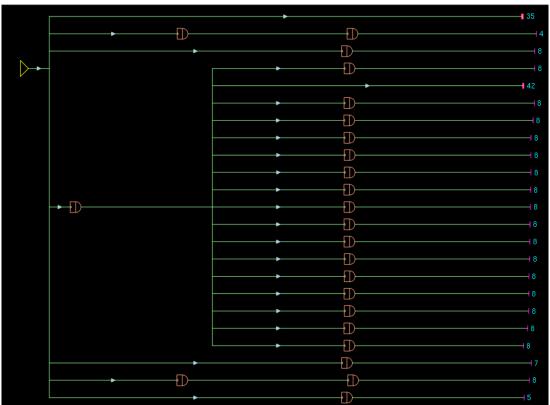

| Figure 48: I2C clock tree – no clock gating                             | . 67 |

| Figure 49: APB Clock tree – no clock gating                             | . 67 |

| Figure 50: I2C Clock tree – automatic clock gating                      | . 68 |

| Figure 51: APB Clock tree – automatic clock gating                      | . 68 |

| Figure 52: I2C Clock tree – manual clock gating                         | . 69 |

| Figure 53 APB Clock tree – manual clock gating                          | . 69 |

| Figure 54: I2C Clock tree – Manual + automatic clock gating             | . 70 |

| Figure 55: APB Clock tree – Manual + automatic clock gating             | . 70 |

| Figure 56: Clock tree – no clock gating                                 | . 71 |

| Figure 57: Clock tree – automatic clock gating                          | . 71 |

| Figure 58Clock Tree – manual clock gating                               | . 71 |

| Figure 59: Clock Tree – manual + automatic clock gating                 | . 71 |

| Figure 60: Floorplan – no clock gating                                  | . 73 |

| Figure 61: Floorplan no clock gating with nets                          | . 73 |

| Figure 62: Floorplan – automatic clock gating                           | . 73 |

| Figure 63: Floorplan – automatic clock gating with nets                 | . 73 |

| Figure 64: Floorplan – manual clock gating                              | . 74 |

| Figure 65: Floorplan – manual clock gating with nets                    | . 74 |

| Figure 66: Floorplan – manual + automatic clock gating                  | . 74 |

| Figure 67: Floorplan – manual + automatic clock gating with nets        | . 74 |

| Figure 68: Schematic from Verdi: dp_s_top                               | . 90 |

| Figure 69: Schematic from Verdi: dp_s_slave                             | . 91 |

| Figure 70: Schematic from Verdi: dp_s_apb_data_unit                     | . 92 |

| Figure 71: Schematic from Verdi: dp_s_apb_fsm                           | . 93 |

| Figure 72: Schematic from Verdi: dp_s_i2c_slave                         | . 94 |

| Figure 73: Schematic from Verdi: dp_s_i2c_data_unit                     | . 95 |

| Figure 74: Schematic from Verdi: dp_s_i2c_fsm                           | . 96 |

|                                                                         |      |

# **Table index**

| Table 1: Reserved addresses                                        | 5  |

|--------------------------------------------------------------------|----|

| Table 2: APB Signals desription                                    | 9  |

| Table 3: Most common low-power techniques overview                 | 16 |

| Table 4: Low power design techniques – compared according to usage | 17 |

| Table 5: Top-level I / O Port list                                 | 33 |

| Table 6: Register map table                                        | 35 |

| Table 7: I2C FSM States                                            | 41 |

| Table 8: I2C Registers list                                        | 44 |

| Table 9: APB FSM States                                            | 47 |

| Table 10: APB Registers list                                       | 48 |

| Table 11: I2C Slave minimum frequency                              | 49 |

| Table 12: I2C Always-on registers                                  | 50 |

| Table 13: I2C Registers that can be clock gated                    | 51 |

| Table 14: APB Always-on registers                                  | 52 |

| Table 15: APB Registers with applied clock gating                  | 52 |

| Table 16: Names of constants and their APB functions               | 54 |

| Table 17: Frequencies used during verification                     | 57 |

| Table 18: Verification Plan                                        | 58 |

| Table 19: Power consumption results – after synthesis              | 66 |

| Table 20: Power consumption results                                | 78 |

| Table 21: Power consumption energy savings                         | 78 |

| Table 22: Number of instances in the design                        | 79 |

| Table 23: Consumption for use to access a memory                   | 80 |

| Table 24: Consumption for use to access a temperature measure unit | 81 |

# **Used abbreviations**

| Abbreviation   | Explanation                                              |

|----------------|----------------------------------------------------------|

| AVS            | Adaptive voltage scaling                                 |

| CG_AUTO        | Automatic clock gating (used during Synthesis)           |

| CG_MAN         | Manual clock gating                                      |

| CG_MAN_AUTO    | Manual clock gating combined with automatic clock gating |

|                | during synthesis                                         |

| CG_NONE        | No clock gating                                          |

| COR            | clear on read                                            |

| CTS            | Clock Tree Synthesis                                     |

| DP             | Diploma project                                          |

| DP device      | Diploma project device                                   |

| DVFS           | Dynamic voltage and frequency scaling                    |

| DVS            | Dynamic voltage scaling                                  |

| Fm             | Fast-mode                                                |

| Fm+            | Fast-mode Plus                                           |

| Hs             | High-Speed mode                                          |

| Multi Vdd, MSV | Multiple supply voltages                                 |

| Multi Vt       | Multi-Threshold                                          |

| RO             | Read only                                                |

| RW             | Read/Write                                               |

| S&RPG          | Save and restore power gating                            |

| Sm             | Standard-mode                                            |

| SOC            | System on chip                                           |

| SRPG           | State retention power gating                             |

| WO             | write only                                               |

## 1 Introduction

## 1.1 The purpose and goals of this document

This document is the documentation to my Master's theses. The goal of this thesis was to design an IP core that will be able to communicate with I2C and APB bus as a Slave device with use the of low-power techniques. It was intended to design a device for physical layer only – the protocols for a particular use (e.g. if the I2C Master wants an answer from CPU or if data are only being sent to CPU and to answer is expected) would have to be designed according to the use.

Let's assume that from now on the, the abbreviation DP device will be used for this device, standing for Diploma project device.

I2C is a bit serial bus. It is often used in pad-limited design, where the speed can be limited. It has the advantage in using only two signals for communication (SDA, SCL signals).

APB bus is a parallel bus; in this case, it is used as an 8-bit bus. APB bus is used to connect peripheral devices with a CPU. One of the first activities of the project was to study how the protocols work. Therefore there is also a brief description of these protocols.

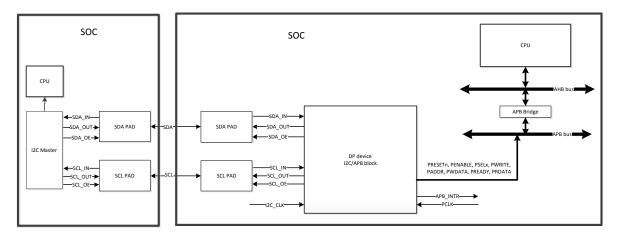

The overall connection of the device is shown in Figure 1. The DP device is connected to I2C using pads (on the left side of the picture) and connected to a CPU using APB bus (right side of Figure 1).

Figure 1: Connection of the DP device among other devices in a system

Low-power techniques were supposed to be described and used in the design. I researched of these techniques and described them in the document. After taking in count their characteristics and use, I decided to use clock gating, as it would be the most suitable technique for this design. The use of clock gating is also part of the assignment.

Development of the IP on RTL level was the next step in the project. This was first designed as schemas, which are also shown and described in this document. I then wrote the RTL in Verilog 2001. Clock gating is included in the Verilog coded as an option through defines, which gives the option of using or not using the clock gating cells I manually placed in the design.

There were four different alternatives of clock gating that were used in order to compare the power consumption – no clock gating, automatic clock gating (done during synthesis), manual clock gating (placing manually clock gating cells) and manual clock gating combined with automatic clock gating. These four different alternatives were measured and compared.

The overall goal was to use low power aware design and compare the consumption results with and without the use of these techniques. The assignment says to compare the consumption estimation after synthesis, however because these estimations are not very accurate and usually differ by 30-50%, I went further and continued with physical design and measured the consumption after the physical design was done. That gave very accurate power consumption estimations which gave adequate results.

## 1.2 Brief overview of each chapter

#### 1.2.1 Chapter 1 - Introduction

This chapter contains an introduction to the topic with description of the overall project as well as its goals.

## 1.2.2 Chapter 2 - Protocols descriptions

This chapter briefly describes I2C and APB protocols that were used in the design.

#### 1.2.3 Chapter 3 - Low-Power techniques

This chapter describes all the different kinds of techniques for low-power design as well as the reasoning why clock gating was used in the design.

#### 1.2.4 Chapter 4 - Design and Verification flow

This chapter describes the whole design and verification flow that was used for the development of the IP. It contains the RTL description of the device, description of verification and the verification tests that were used, descriptions of FSMs, the description and reasoning for what registers clock gating was used for. It describes also the different phases of physical design such as Floorplan, Cell place, Clock tree synthesis and Routing.

## 1.2.5 Chapter 5 - Power consumption results

This chapter contains final consumption results and explanations why in different modes are different power consumptions. This chapter also describes use cases of the design and the power consumption in those cases.

## 1.2.6 Chapter 6 - Summary

This chapter contains the summary of this whole document and describes the results that were reached in this thesis.

## 2 Protocols descriptions

## 2.1 I2C Protocol description

This device communicates with the I2C standard rev. 03. The device is an I2C Slave device operating in Sm, Fm and Fm+ modes with 7-bits addressing. The explanations of these terms follow. The description of the I2C protocol is not complete in this document, but is focused on these characteristics. The complete documentation of the I2C Standard can be found in (B.V., 2007).

I2C is a bidirectional 2-wire bus for efficient inter-IC control. This bus is called the Inter-IC or I2C-bus. Only two bus lines are required: a serial data line (SDA) and a serial clock line (SCL). Serial, 8-bit oriented, bidirectional data transfers can be made at up to 100 kbit/s in the Standard-mode, up to 400 kbit/s in the Fast-mode, up to 1 Mbit/s in the Fast-mode Plus (Fm+), or up to 3.4 Mbit/s in the High-speed mode. (B.V., 2007)

Two wires, serial data (SDA) and serial clock (SCL), carry information between the devices connected to the bus. Each device is recognized by a unique address and can operate as either a transmitter or receiver, depending on the function of the device. In addition to transmitters and receivers, devices can also be considered as masters or slaves when performing data transfer. A master is the device which initiates a data transfer on the bus and generates the clock signals to permit that transfer. At that time, any device addressed is considered a slave.

#### 2.1.1 Speed modes

All devices are downward compatible – any device may be operated at a lower bus speed. Sm, Fm and Fm+ modes have the same bus protocol and data format. The data format of Hs mode, however is different.

- **Standard-mode** (Sm) up to 100 kbit/s

- **Fast-mode** (Fm) up to 400 kbit/s

- **Fast-mode Plus (Fm+)** up to 1 Mbit/s

- **High-speed mode (Hs)** up to 3.4 Mbit/s

#### 2.1.2 SDA and SCL Signals

- SDA (serial data line) serves for transferring data

- SCL (serial clock line) used as a logical clock for I2C

#### 2.1.3 Reserved addresses

Table 1: Reserved addresses

| Slave address | R/W bit | Description                          |  |

|---------------|---------|--------------------------------------|--|

| 0000 000      | 0       | general call address[1]              |  |

| 0000 000      | 1       | START byte[2]                        |  |

| 0000 001      | X       | CBUS address[3]                      |  |

| 0000 010      | X       | reserved for different bus format[4] |  |

| 0000 011      | X       | reserved for future purposes         |  |

| 0000 1XX      | X       | Hs-mode master code                  |  |

| 1111 1XX      | X       | reserved for future purposes         |  |

| 1111 0XX      | X       | 10-bit slave addressing              |  |

## 2.1.4 Data transfer example

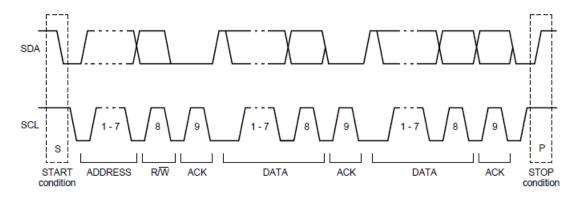

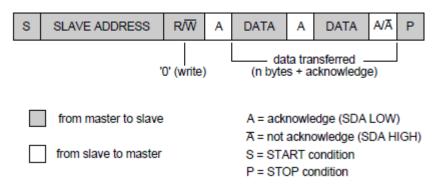

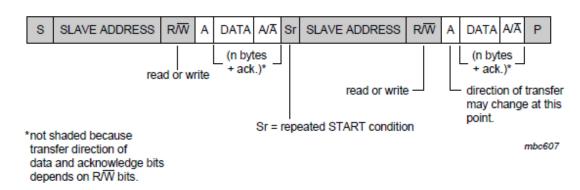

Figure 2 shows a complete data transfer in a block level. After the START condition (S), a slave address is sent. This address is seven bits long followed by an eighth bit which is a data direction bit  $(R/\overline{W})$  — a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master. However, if a master still wishes to communicate on the bus, it can generate a repeated START condition (Sr) and address another slave without first generating a STOP condition. Various combinations of read/write formats are then possible within such a transfer.

Figure 2: Complete data transfer

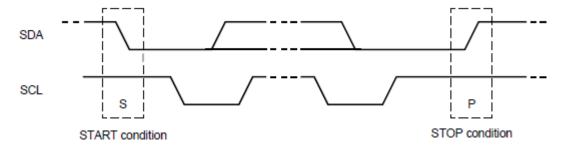

#### 2.1.5 Start and Stop condition

All transactions begin with a START (S) and are terminated by a STOP (P) condition. The bus is considered to be busy after the START condition. The bus is considered to be free again a certain time after the STOP condition. The bus stays busy if a repeated START (Sr) is generated instead of a STOP condition. In this respect, the START (S) and repeated START (Sr) conditions are functionally identical.

Figure 3: START and STOP conditions

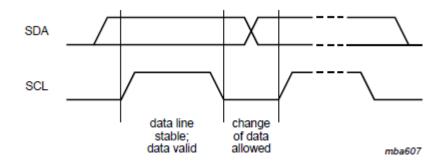

#### 2.1.6 Data validity

The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW (see Figure 4). One clock pulse is generated for each data bit transferred.

Figure 4: Bit transfer on I2C bus - data validity

## 2.1.7 Clock stretching

Clock stretching pauses a transaction by holding the SCL line LOW. The transaction cannot continue until the line is released HIGH again. Clock stretching is optional.

On the byte level, a device may be able to receive bytes of data at a fast rate, but needs more time to store a received byte or prepare another byte to be transmitted. Slaves can then hold the SCL line LOW after reception and acknowledgment of a byte to force the master into a wait state until the slave is ready for the next byte transfer in a type of handshake procedure

## 2.1.8 Write operation example

Figure 5 shows the I2C write operation example. It is very similar to Figure 2, where the transfer was described in general. On Figure 5 the  $R/\overline{W}$  is set to 0, which means that the operation is write. The whole operation ends either with Slave sending a

NACK (for example when the Slave's memory is full) or by Master sending a STOP condition.

Figure 5: I2C Write operation example

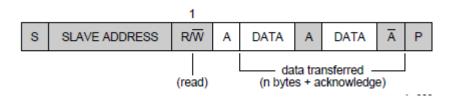

### 2.1.9 Read operation example

Figure 6 shows the I2C Read operation example. The  $R/\overline{W}$  signal is set to 1, which sets the I2C operation to read. The operation ends when the I2C Master sends NACK and Stop condition afterwards.

Figure 6: I2C Read operation example

#### 2.1.10 Combined operation example

An example of two different operations is shown on Figure 7. After the first operation a Repeated Start condition is sent by the I2C Master and a new operation follows starting with the new Slave address. After all of the operations are finished, a STOP condition is sent by the I2C Master.

Figure 7: I2C Combined operation example

## 2.2 APB Protocol description

This device communicates with AMBA 3 APB Protocol. The complete documentation for this protocol can be found under (ARM, 2004).

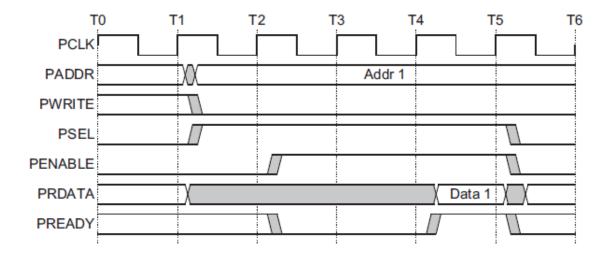

APB is a parallel unpipelined synchronous protocol where every transfer takes at least two cycles. This APB version also includes signal PREADY which is used for extending the APB transfer by the slave device. This can be useful if the device needs more than two cycles for the transfer. Any number of extra additional cycles can be added. This means from 0 higher.

APB uses the following signals:

- Input signals: PSELx, PENABLE, PRESETn, PCLK, PWRITE, PADDR, PWDATA

- Output signals: PREADY, PSLVERR, PRDATA

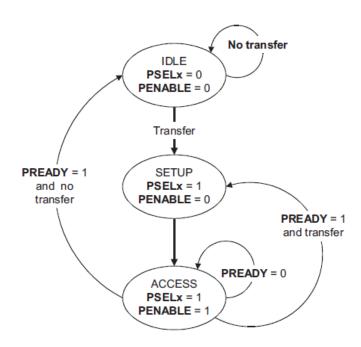

### 2.2.1 Operating states

The APB bus can be in three different operating states as shown on Figure 8. Those states are further described under Figure 8.

Figure 8: APB Operating states

- **IDLE** This is the default state of the APB.

- **SETUP** When a transfer is required the bus moves into the SETUP state, where the appropriate select signal, PSELx, is asserted. The bus only remains in the SETUP state for one clock cycle and always moves to the ACCESS state on the next rising edge of the clock.

- ACCESS The enable signal, PENABLE, is asserted in the ACCESS state. The address, write, select, and write data signals must remain stable during

the transition from the SETUP to ACCESS state. Exit from the ACCESS state is controlled by the PREADY signal from the slave:

- o If PREADY is held LOW by the slave then the peripheral bus remains in the ACCESS state.

- If PREADY is driven HIGH by the slave, then the ACCESS state is exited and the bus returns to the IDLE state if no more transfers are required. Alternatively, the bus moves directly to the SETUP state if another transfer follows.

## 2.2.2 APB Signals detailed description

Table 2: APB Signals desription

| Signal    | Source                | Description                                                  |  |

|-----------|-----------------------|--------------------------------------------------------------|--|

| PCLK.     | Clock source Clock    | The rising edge of PCLK times all transfers on               |  |

|           |                       | the APB.                                                     |  |

| PRESETn   | System bus equivalent | Reset. The APB reset signal is active LOW.                   |  |

|           |                       | This signal is normally connected                            |  |

|           |                       | directly to the system bus reset signal.                     |  |

| PADDR     | APB bridge            | Address. This is the APB address bus. It can be              |  |

|           |                       | up to 32 bits wide and is driven                             |  |

|           |                       | by the peripheral bus bridge unit.                           |  |

| PSELx     | APB bridge            | Select. The APB bridge unit generates this                   |  |

|           |                       | signal to each peripheral bus slave. It indicates            |  |

|           |                       | that the slave device is selected and that a data            |  |

|           |                       | transfer is required. There is a PSELx signal for            |  |

|           |                       | each slave.                                                  |  |

| PENABLE   | APB bridge            | Enable. This signal indicates the second and                 |  |

|           |                       | subsequent cycles of an APB transfer.                        |  |

| PWRITE    | APB bridge            | Direction. This signal indicates an APB write                |  |

|           |                       | access when HIGH and an APB read access                      |  |

|           |                       | when LOW.                                                    |  |

| PWDATA    | APB bridge            | Write data. This bus is driven by the peripheral             |  |

|           |                       | bus bridge unit during write cycles when                     |  |

|           |                       | PWRITE is HIGH. This bus can be up to 32 bits                |  |

| DDE A DEZ | G1                    | wide.                                                        |  |

| PREADY    | Slave interface       | Ready. The slave uses this signal to extend an APB transfer. |  |

| PRDATA    | Slave interface       | Read Data. The selected slave drives this bus                |  |

| IKDATA    | Slave illerrace       | during read cycles when PWRITE is LOW.                       |  |

|           |                       | This bus can be up to 32-bits wide.                          |  |

| PSLVERR   | Slave interface       | This signal indicates a transfer failure. APB                |  |

|           | Dia ve interface      | peripherals are not required to support the                  |  |

|           |                       | PSLVERR pin. This is true for both existing                  |  |

|           |                       | and new APB peripheral designs. Where a                      |  |

|           |                       | peripheral does not include this pin then the                |  |

|           |                       | appropriate input to the APB bridge is tied                  |  |

|           |                       | LOW.                                                         |  |

|           |                       |                                                              |  |

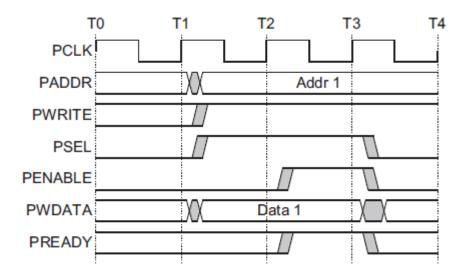

### 2.2.3 Write transfer without waiting states

Figure 9: Write transfer without waiting states

The write transfer starts with the address, write data, write signal and select signal, which are all changing after the rising edge of the clock. After the following clock edge the enable signal is asserted, PENABLE, and this indicates that the Access phase is taking place. The address, data and control signals all remain valid throughout the Access phase. The transfer completes at the end of this cycle.

The enable signal, PENABLE, is deasserted at the end of the transfer. The select signal, PSELx, also goes LOW unless the transfer is to be followed immediately by another transfer to the same peripheral. (B.V., 2007)

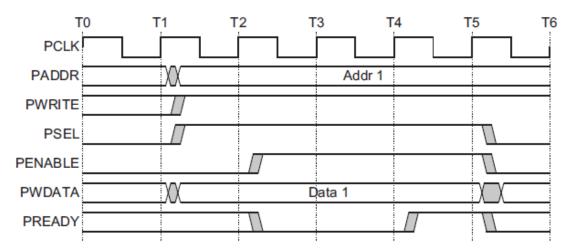

### 2.2.4 Write transfer with waiting states

Waiting states can be used to extend the transfer. As shown on Figure 10, waiting states are used when PREADY signal is low during the transfer.

During an Access phase, when PENABLE is HIGH, the transfer can be extended by driving PREADY LOW. The following signals remain unchanged for the additional cycles:

- address, PADDR

- write signal, PWRITE

- select signal, PSEL

- enable signal, PENABLE

- write data, PWDATA.

PREADY can take any value when PENABLE is LOW. This ensures that peripherals that have a fixed two cycle access can tie PREADY HIGH.

Figure 10:APB Write transfer with waiting states

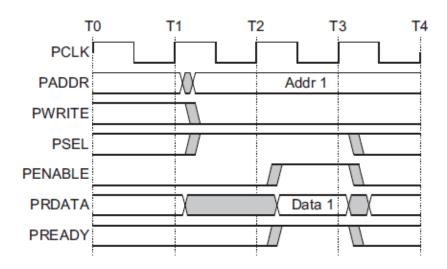

## 2.2.5 Read transfer without waiting states

Figure 11 shows the read transfer without using wait states. The timing of the signals was already described in the write transfer paragraph above.

Figure 11: Read transfer without waiting states

## 2.2.6 Read transfer with waiting states

The transfer is extended if **PREADY** is driven LOW during an Access phase. The protocol ensures that the following remain unchanged for the additional cycles:

- address, PADDR

- write signal, PWRITE

- select signal, PSEL

- enable signal, PENABLE.

Figure 12: APB Read transfer with waiting states

## 3 Low-Power techniques

## 3.1 Low power design motivation

Challenges that cause us to deal with low power design are mainly the following:

- Increasing device density

- Increasing clock frequencies

- Lowering supply voltage

- Lowering transistor threshold voltage

High power consumption leads to higher temperatures. The goal is to keep the temperature low to avoid parasite effects. The principle of achieving this is to provide performance only when it is required.

## 3.2 Types of power consumption

## 3.2.1 Dynamic power

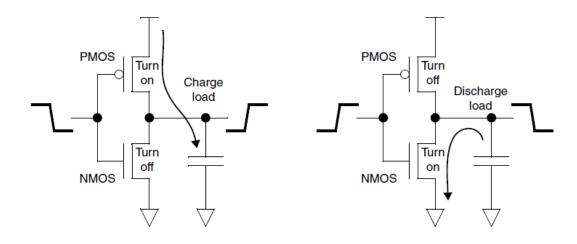

Dynamic power consists of internal power and switching power.

Internal power is consumed by the cells when one of the inputs changes, but the output doesn't change. Internal power results from the short-circuit (crowbar) current that flows through the PMOS-NMOS stack during a transition.

#### 3.2.1.1 Switching power

Because the current flows only during logic transitions on the net, the long-term dynamic power consumption depends on the clock frequency (possible transitions per second) and the switching activity (presence or absence of transitions actually occurring on the net in successive clock cycles).

Figure 13: Switching power

The higher the clock frequency is, the more often there is activity on the transistors (change of value), because with synchronous devices activity is done with the change of clock. In other words, switching power results from the charging and discharging of the external capacitive load on the output of a cell.

These parameters can be summed in the following formula:

$$P_{dyn}=C_{eff}*V_{dd}^2*f_{clk}$$

Here we can see that the dynamic power depends on capacitance, voltage (which obviously has the greatest impact on dynamic power consumption because of the square power) and the clock frequency. The techniques described in the following text will mostly focus on how to use the voltage and frequency for lowering the power consumption.

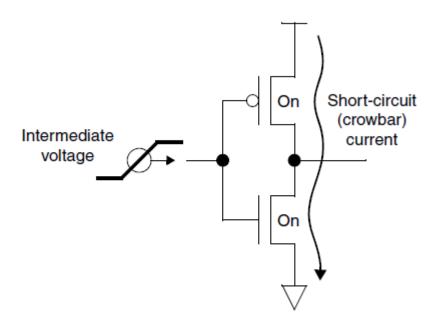

#### 3.2.1.2 Internal power

Internal power is consumed during the short period of time when the input signal is at an intermediate voltage level. During which, both the PMOS and NMOS transistors can be conducting. This condition results in a nearly short-circuit conductive path from VSS to ground, as illustrated in Figure 1-2. A relatively large current, called the crowbar current, flows through the transistors for a brief period of time. Lower threshold voltages and slower transitions result in more internal power consumption.

Figure 14: Internal power

(Synopsys, 2010)

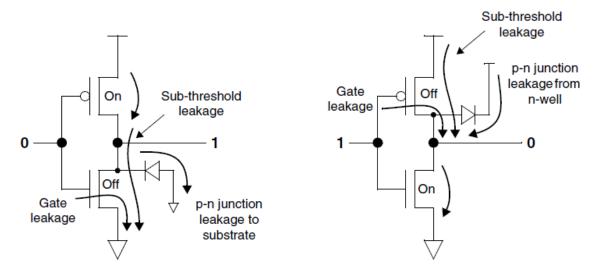

### 3.2.2 Static (leakage) power

Static power is leakage at transistors at all times. This consumption remains at all times constant.

The main causes of leakage power are reverse-bias p-n junction diode leakage, subthreshold leakage, and gate leakage. These leakage paths in a CMOS inverter are shown in

Figure 15: Static leakage currents

#### 3.2.2.1 p-n junctions leakage

Leakage at reverse-biased p-n junctions (diode leakage) has always existed in CMOS circuits. This is the leakage from the n-type drain of the NMOS transistor to the grounded p-type substrate, and from the n-well (held at VDD) to the p-type drain of the PMOS transistor. This leakage is relatively small.

#### 3.2.2.2 Sub-threshold leakage

Sub-threshold leakage is the small source-to-drain current that flows even when the transistor is held in the "off" state. In older technologies, this current was negligible. However, with lower power supply voltages and lower threshold voltages, "off" gate voltages are getting close to "on" threshold voltages. Sub-threshold leakage current increases exponentially as the gate voltage approaches the threshold voltage.

#### 3.2.2.3 Gate leakage

Gate leakage is the result of using an extremely thin insulating layer between the gate conductor and the MOS transistor channel. Gate oxides are becoming so thin that only a dozen or fewer layers of insulating atoms separate the gate from the source and drain. Under these conditions, quantum-effect tunneling of electrons through the gate oxide can occur, resulting in significant leakage from the gate to the source or drain.

(Synopsys, 2010)

## 3.3 Low power techniques overview and comparing

There are different techniques used for low-power. The next several paragraphs are an introduction to low power techniques. The focus therefore is on comparing different techniques and their use and purpose.

Table 3: Most common low-power techniques overview

| Technique                                                                     | Description                                                                                                                                                                                                                                                                                    |  |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Clock gating and clock tree gating                                            | Disables blocks or clock tree parts not in use.                                                                                                                                                                                                                                                |  |

| Multiple supply voltages (MSV,<br>Multi Vdd), Static Voltage scaling<br>(SVS) | Operates different blocks at different, fixed supply voltages. Also known as voltage islands. Signals that cross voltage domain boundaries are level-shifted.                                                                                                                                  |  |

| Dynamic voltage scaling (DVS), Multi-level voltage scaling (MVS)              | Operates different blocks at variable supply voltages. Uses look-up tables to adjust voltage on-the-fly to satisfy varying performance requirements. Signals that cross voltage domain boundaries are level-shifted.                                                                           |  |

| Dynamic voltage and frequency scaling (DVFS)                                  | Operates different blocks at variable supply voltages and frequencies. Uses look-up tables to adjust voltage and frequency on-the-fly to satisfy varying performance requirements. Signals that cross voltage domain boundaries are level-shifted.                                             |  |

| Adaptive voltage scaling (AVS)                                                | Operates different blocks at variable supply voltages. Uses in-block monitors to determine frequency requirements, and adjusts voltage on-the-fly to satisfy them.                                                                                                                             |  |

| Power gating or<br>Power Shut-Off (PSO)                                       | Turns off supply voltage to blocks not in use. Significantly reduces – but does not eliminate – leakage. Block outputs float.                                                                                                                                                                  |  |

| Power gating with retention                                                   | Stores system state prior to power-down. Avoids complete reset at power-up, which reduces powerup/ reset delay and power consumption.                                                                                                                                                          |  |

| State retention power gating (SRPG)                                           | Stores the system state in local registers. When on standby or idling, gates the clock, and the register saves the data. State retention registers use both a continuous power supply and a switchable supply.  Other logic is powered only by the switchable supply, and can be powered down. |  |

| Save and restore power gating (S&RPG)                                         | As SRPG, but uses a memory array.                                                                                                                                                                                                                                                              |  |

(Goering, 2008)

Table 4: Low power design techniques – compared according to usage

| Dynamic Power         | Leakage Power                  | Design       | Architectural |

|-----------------------|--------------------------------|--------------|---------------|

| Clock gating          | Multi Vt                       | Multi Vt     | Pipelining    |

| Variable frequency    | Power gating                   | Clock gating | Asynchronous  |

| Variable power supply | Back (substrate) bias          | Power gating |               |

| Multi Vdd             | Use new devices-FinFet,<br>SOI | Multi Vdd    |               |

| Voltage islands       |                                | DVFS         |               |

| DVFS                  |                                |              |               |

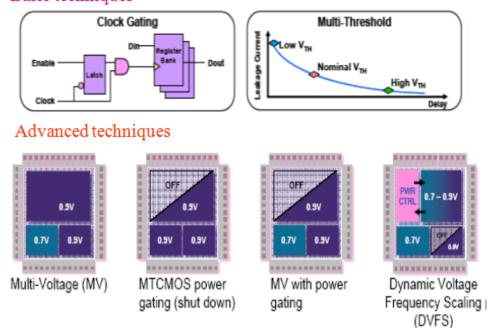

## Basic techniques

Figure 16: Low Power Techniques comparison

(Murali, 2009)

## 3.4 Clock-gating

RTL clock gating works by identifying groups of flip-flops which share a common enable signal. Traditional methodologies use this enable term to control the select on a multiplexer connected to the D port of the flip-flop or to control the clock enable pin on a flip-flop with clock enable capabilities. RTL clock gating uses this enable term to control a clock gating circuit which is connected to the clock ports of all of the flip-flops with the common enable term. Therefore, if a bank of flip flops which share a common enable term have RTL clock gating implemented, the flip-flops will consume zero dynamic power as long as this enable term is false.

(Frank Emnett, 2000)

Clock gating is particularly useful for registers that need to maintain the same logic values over many clock cycles. Shutting off the clocks eliminates unnecessary switching activity that would otherwise occur to reload the registers on each clock cycle. The main challenges of clock gating are finding the best places to use it and creating the logic to shut off and turn on the clock at the proper times.

Clock gating is relatively simple to implement because it only requires a change in the netlist. No additional power supplies or power infrastructure changes are required.

(Synopsys, 2010)

Clock-gating lowers average power consumption; however it always increases the maximum immediate consumption. Therefore it is convenient to use clock-gating only for registers that have their enable signal mostly disabled. It is important to do an analysis of use of different registers and apply clock-gating only on those where it's suitable. Usually it is recommended to have at least 3-4 flip-flops with the same common enable signal for making clock-gating effective. In case of using clock-gating for less than 3 flop-flops with the same enable signal it can have an effect of increased consumption.

(Bečvář, 2011)

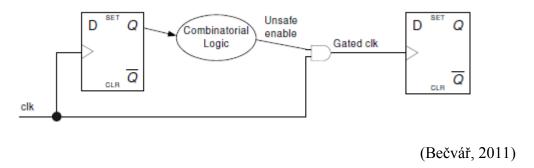

Figure 17: Principle of clock-gating connection (not completely correct)

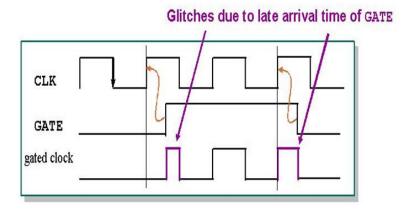

Figure 17 shows the principle of clock-gating. The AND gate is enabling the clock. This is not a correct connection though, because with having the AND gate it will cause a glitch impulse on the gated clock instead of the right clock impulse as shown on Figure 18.

(Murali, 2009)

Figure 18: Glitches in latch free clock gating

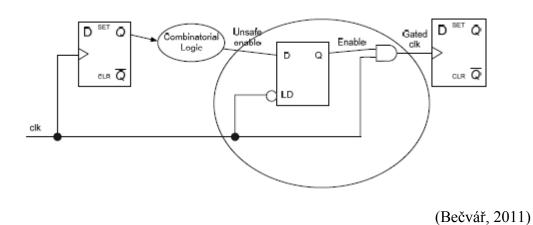

Therefore a level-sensitive latch is used with the AND gate inside the clock gating cell from a library which needs to be used. The use of the cell is shown on Figure 19. The latch holds the enable signal from the active edge of the clock until the inactive edge of the clock.

Figure 19: Correct clock-gating cell connection – connection in a dont\_touch cell

Clock gating effects only dynamic power consumption as it is dependent on preventing clock activity.

### 3.4.1 Automatic clock gating done by Synthesis tools / Clock gating

Synthesis tools can detect low-throughput data paths where clock gating can be used with the greatest benefit, and can automatically insert clock-gating cells in the clock paths at the appropriate locations.

(Synopsys, 2010)

Automatic clock gating uses so called functional gating – input and output values of the flip flop are compared and if they are different, the clock enable signal is enabled. A big advantage of automatic clock gating during synthesis is that it only needs a change of one command to enable clock gating use.

## 3.4.2 Manual clock gating / Clock tree gating

Manual clock gating is done by the IP designer by manually setting the enable signal for a set of flip flops in the FSM. This enable signal is propagated through a clock gating cell. Usually different state modes are used.

## 3.5 Miltiple-Vt

Some CMOS technologies support the fabrication of transistors with different threshold voltages (Vt values). In that case, the cell library can offer two or more different cells to implement each logic function, each using a different transistor threshold voltage. For example, the library can offer two inverter cells: one using low-Vt transistors and other using high-Vt transistors.

A low-Vt cell has higher speed, but higher sub-threshold leakage current. A high-Vt cell has low leakage current, but less speed. The synthesis tool can choose the appropriate type of the cell to use based on the tradeoff between speed and power. For example, it can use low-Vt cells in the timing-critical paths for speed and high-Vt cells everywhere else for lower leakage power.

(Synopsys, 2010)

#### 3.6 Multi Vdd

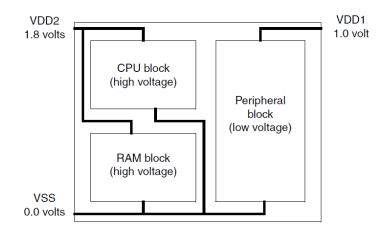

Different parts of a chip might have different speed requirements. For example, the CPU and RAM blocks might need to be faster than a peripheral block. A lower supply voltage reduces power consumption but also reduces speed. To get maximum speed and lower power at the same time, the CPU and RAM can operate with a higher supply voltage while the peripheral block operates with a lower voltage, as shown in Figure 20.

Figure 20: Multi Vdd blocks connection

(Synopsys, 2010)

#### 3.6.1 Level Shifters

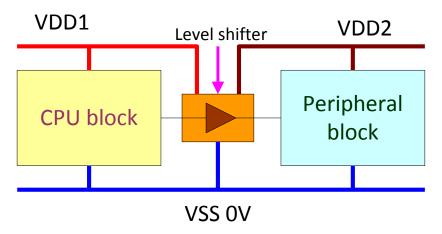

Level shifters are used for transferring data between two blocks with different power voltage as shows Figure 21.

Figure 21: Blocks with different Level shifter

In any multi-voltage design, level shifters are required at the interfaces of blocks operating at different voltages. It is much easier to design one direction level shifters.

(Murali, 2009)

In theory, the bus interface of CPU can be a higher or lower voltage, for practical reason the bus is always operate at a voltage higher than or equal to the CPU. Otherwise system errors occur.

(Yang, 2008)

# 3.7 Multi-level voltage scaling (MVS), Dynamic voltage scaling (DVS)

This is an extension of Multi Vdd case where a block or subsystem is switched between two or more voltage levels. Only a few, fixed, discrete levels are supported for different operating modes.

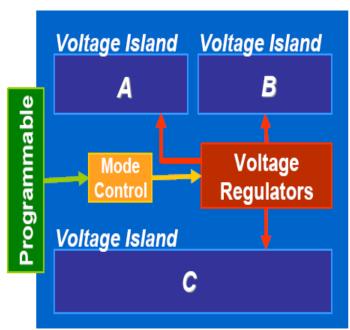

# 3.8 Dynamic voltage and frequency scaling (DVFS)

DVFS is an extension of MVS where a larger number of voltage levels are dynamically switched between to follow changing workloads.

**Timing/Voltage Values:** DVFS uses a set of discrete voltage / frequency pairs. Determining which values to support is a key design decision, application dependent. Too few operating points results in systems that spend too much time ramping between levels. Too many levels results in the power supply spending too much time "hunting" between different target voltages.

**Switching Times and Algorithms:** Switching performance levels takes time for both voltage regulators and clock generators. Switching voltage levels is particular slow and switching frequencies is orders of magnitude faster than voltage level switching. Increase the voltage first and decrease the voltage after the frequency is lowered.

(Yang, 2008)

Figure 22: DVFS blocks

**Mode control block** - Voltage as well as frequency is dynamically varied as per the different working modes of the design.

**Voltage regulators block** - When high speed of operation is required, voltage is increased to attain higher speed of operation with the penalty of increased power consumption.

(Murali, 2009)

The principle of multivoltage operation can be extended to allow the voltage to be changed during operation of the chip to match the current workload. For example, a math processor chip in a laptop computer might operate at a lower voltage and lower clock frequency during simple spreadsheet computations, thereby saving power; and then at a higher voltage and higher clock frequency during 3-D image rendering when the highest performance is needed. The changing of supply voltage and operating frequency during operation to meet workload requirements is called dynamic voltage and frequency scaling.

The chip and voltage supply can be designed to use a number of established levels, or even a continuous range. Dynamic voltage scaling requires a multilevel power supply and a logic block to determine the best voltage level to use for a given task. Design, implementation, verification, and testing of the device can be especially challenging because of the ranges and combinations of voltage levels and operating frequencies that must be analyzed and accommodated.

Dynamic voltage scaling can be combined with power switching technology so that each block in the design can operate at multiple voltage levels for different performance requirements, or shut off completely when not needed at all.

(Synopsys, 2010)

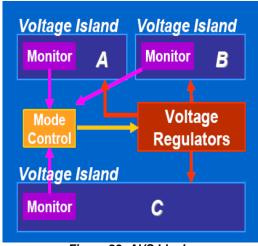

# 3.9 Adaptive voltage scaling (AVS)

AVS is an extension of DVFS where a control loop is used to adjust the voltage. Performance Monitor is integrated with IP is monitoring to get the best thermal tracking. The performance monitor communicates with a power controller which in return sets the voltage of the power supply.

(Yang, 2008)

AVS contains voltage areas with variable software controlled VDD. Monitors in each block communicate with the mode controller that controls Voltage regulators as shows in Figure 23.

Figure 23: AVS blocks

(Murali, 2009)

# 3.10 Power gating (Power Switching)

# 3.10.1 How Power gating works

Power gating circuit blocks that are not in use are temporarily turned off. On the other hand, this increases time delays as power gated modes have to be safely entered and exited. The shutting down of these blocks is done by either hardware timers or software drivers.

(Murali, 2009)

Power switching has the potential to reduce overall power consumption substantially because it lowers leakage power as well as switching power. It also introduces some additional challenges, including the need for a power controller, a power-switching network, isolation cells, and retention registers.

(Synopsys, 2010)

# 3.10.2 Ways how to shut down blocks

There are different ways how to safely shut down blocks:

- Software or hardware

- o Driver software schedules the power down operations

- o Hardware timers are used

- Dedicated power management controller

- Switch off by using external power supply for long term

- Use CMOS switches for smaller duration switch off

- A power switch (either to VDD header switch, PMOS or GND footer switch, NMOS) is added to supply rails to shut-down logic. MTCMOS switches are used.

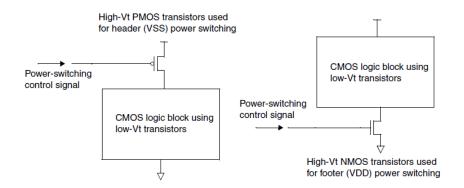

#### 3.10.3 Power switches

A block that can be powered down must receive its power through a power-switching network, consisting of a larger number of transistors with source-to-drain connections between the always-on power supply rail and the power pins of the cells. The power switches are distributed physically around or within the block. The network, when switched on, connects the power to the logic gates in the block. When switched off, the power supply is effectively disconnected from the logic gates in the block.

High-Vt transistors from a Multiple-Threshold CMOS (MTCMOS) technology are used for the power switches because they minimize leakage and their switching speed is not critical. PMOS header switches can be placed between VDD and the block power supply pins, or NMOS footer switches can be placed between VSS and the block ground pins, as shown in Figure 1-8. The number, drive strength, and placement of switches should be chosen to give in an acceptable voltage drop during peak power usage in the block.

Figure 24: Power-switching Network Transistors

(Synopsys, 2010)

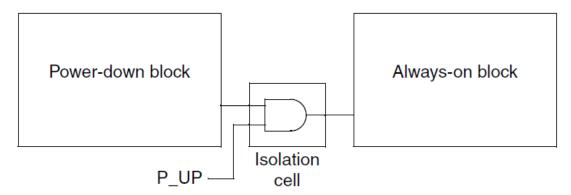

#### 3.10.4 Isolation cells

Isolation cells isolate the power gated block from the always-on-block. It can hold logic 1 or logic 0 or it can hold the signal value latched at the time of the power-down event. Isolation cells must be powered during power-down periods to hold the saved value.

Any use of power switching requires isolation cells where signals leave a powered-down block and enter a block that is always on (or currently powered up). An isolation cell provides a known, constant logic value to an always-on block when the power-down block has no power, thereby preventing unknown or intermediate values that could cause crowbar currents.

One simple implementation of an isolation cell is shown in Figure 25. When the block on the left is powered up, the signal P\_UP is high and the output signal passes through the isolation cell unchanged (except for a gate delay). When the block on the left

is powered down, P\_UP is low, holding the signal constant going into the always-on block. Isolation cells must themselves have power during block power-down periods.

Figure 25: Use of isolation cell

(Synopsys, 2010)

#### 3.10.5 Enable level shifter

An enable level shifter acts as a level shifter and an isolation cell at the same time. This is shown on Figure 26. That means that the interface cells between different blocks must perform both level shifting and isolation functions.

(Murali, 2009)

The power switching can be combined with multi voltage operation. Different blocks can be designed to operate at different voltages and also to be separately powered down when they are not needed. In that case, the interface cells between different blocks must perform both level shifting and isolation functions, depending on whether the two blocks are operating at different voltages or one is shut down. A cell that performs both functions is called an enable level shifter. This cell must have two separate power supplies, just like any other level shifter.

(Synopsys, 2010)

Figure 26: Level shifter

(Murali, 2009)

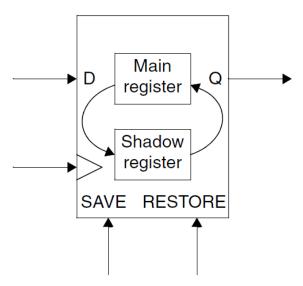

# 3.10.6 Retention registers

Retention registers are always powered up. Special low leakage flip-flops are used to hold the data of the main register of the power gated clock. A power gating controller controls the retention mechanism.

Figure 27: Retention register

When a block is powered down and then powered back up, it is often desirable for the block to be restored to the state it was in prior to the power-down event. A possible strategy is to use retention registers in the power-down block. A retention register can retain data during power-down by saving the data into a shadow register (also known as the bubble register) prior to power-down. Upon power-up, it restores the data from the shadow register to the main register. The shadow register has an always-on power supply, but it is constructed with high-Vt transistors to minimize leakage during the power-down period. The main register is built with fast but leaky low-Vt transistors.

One type of retention register implementation is shown in Figure 27. The SAVE signal saves the register data into the shadow register prior to power-down and the RESTORE signal restores the data after power-up. Instead of using separate, edge-sensitive SAVE and RESTORE signals, a retention register could use a single level-sensitive control signal.

A retention register occupies a larger area than an ordinary register, and it requires an always-on power supply connection for the shadow register in addition to the power-down supply used by the rest of the device. However, restoring the data to the registers after power-up is fast and simple compared with other strategies.

(Synopsys, 2010)

Figure 28: Connection of retention register signals

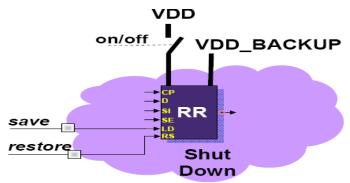

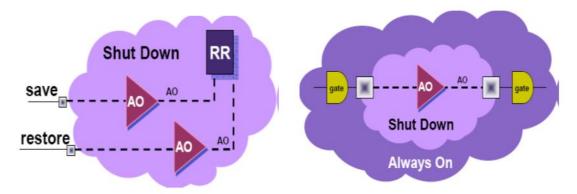

# 3.10.7 Always on logic

There's always some logic that needs to stay active during the shut-down period. The basic principle is shown on Figure 29. Examples of always-on-logic are the following:

- Internal enable pins (ISO/ELS)

- Power switches

- Retention registers

- User-specific cells

Figure 29: Always on logic

(Murali, 2009)

# 3.11 Conclusion of the listed low-power techniques

# 3.11.1 Clock gating and clock tree gating

Clock gating (automatic clock gating during synthesis) is a very easy but at the same time effective way how to implement a low-power technique in the design. The only thing that needs to be done is changing one command in the synthesis script. This method is often used.

Clock tree gating on a level by manually placing clock gating cells on RTL level is a way that can be used when the designed knows the power consumption modes of the device and approximately how much time the device spends in these modes.

These techniques show to be useful in the IP developed in this project.

# 3.11.2 Multi Vdd, SVS

These techniques are used as techniques in the physical design. This technique is used in SoC design to provide different voltages for different voltage islands.

## 3.11.3 DVS, MVS, DVFS, AVS

These techniques are an extension of Multi Vdd technique. Again, it's a matter of physical design and they're used in SoCs.

# 3.11.4 Power gating, Power Shut-Off

This is a technique used in physical design. Multiple-Vt transistors are usually used for this technique. It requires use of different extra blocks and the assignment would be too complicated.

#### 3.11.5 Pipelining

Pipelining is an architectural technique used with advantage in processors. However it is not useful in this kind of design that my master's project is focused on.

# 3.11.6 Asynchronous design

Asynchronous design is a advanced and hard-to-design technique. It is not suitable for this kind of design.

#### 3.11.7 Conclusion

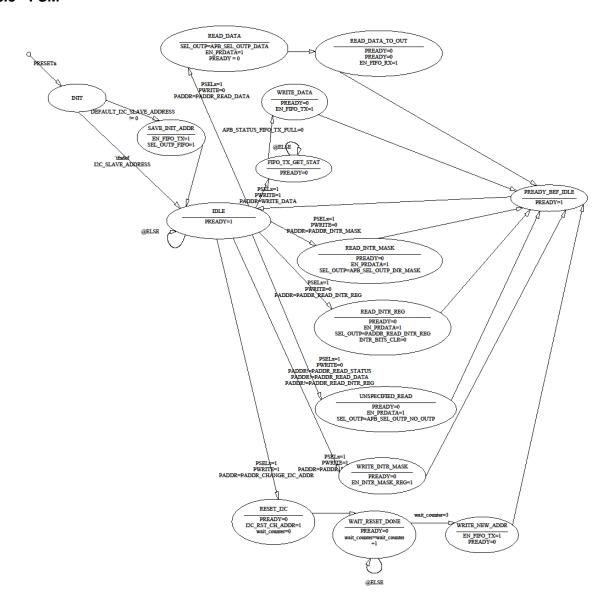

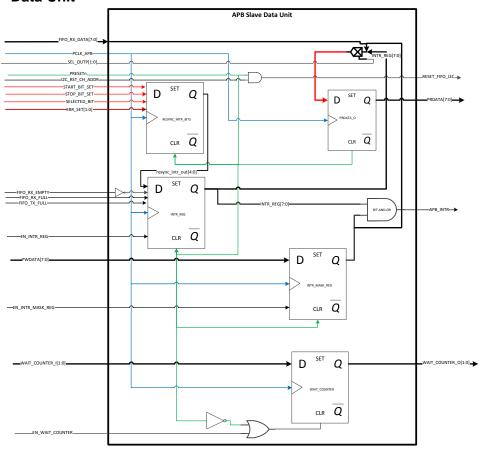

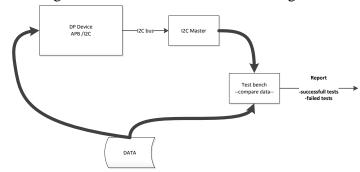

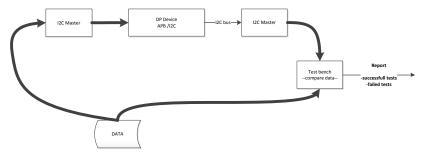

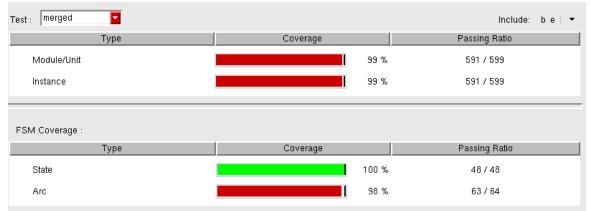

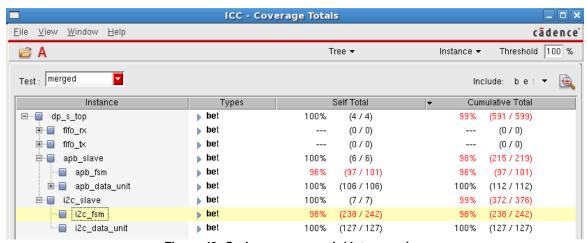

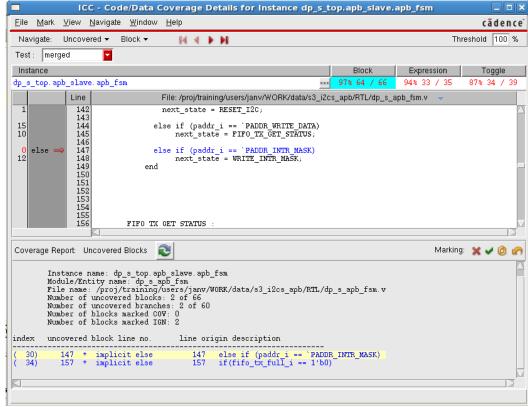

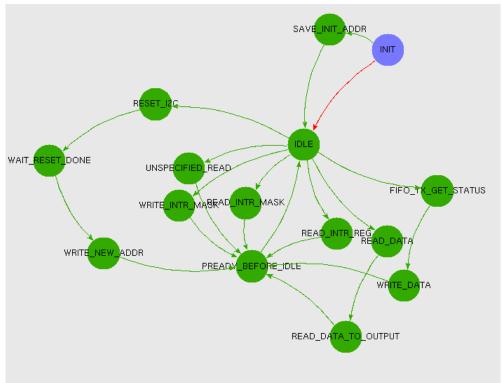

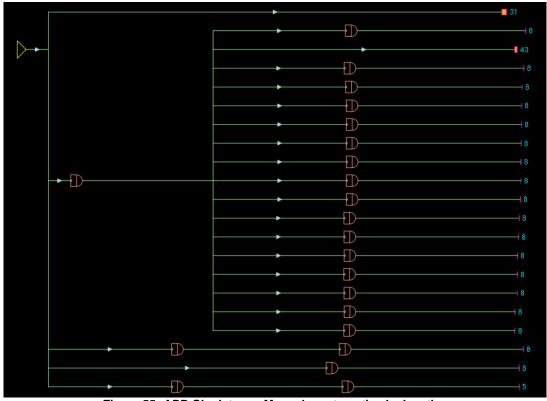

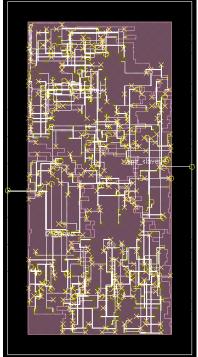

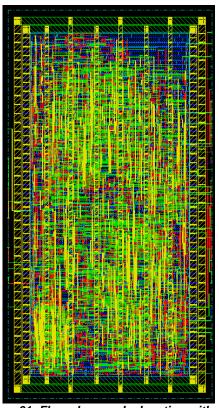

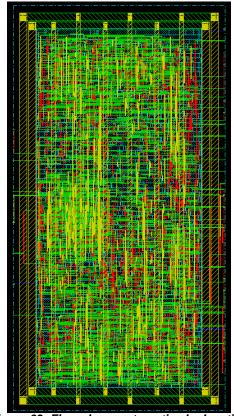

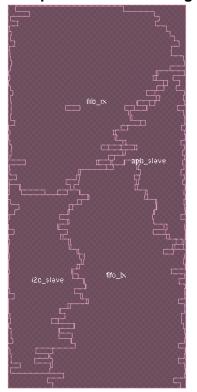

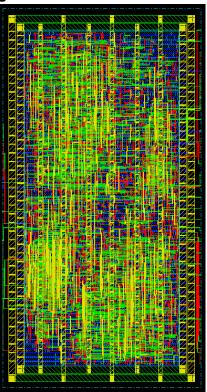

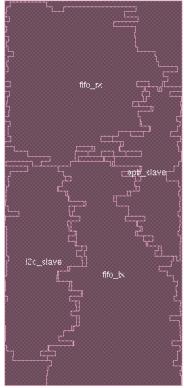

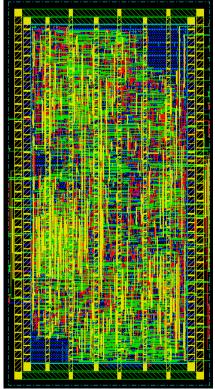

Clock gating and Clock tree gating turns out to be the best implementable and useable technique in this design although it does effect only dynamic power consumption.