# cPCI-3510 Series

Performance 3U CompactPCI® PlusIO Intel® Core™ i7/i5 Processor Blade

#### **User's Manual**

Manual Rev.: 2.01

Revision Date: November 17, 2014

**Part No:** 50-15095-1010

**Advance Technologies; Automate the World.**

# **Revision History**

| Revision | Release Date | Description of Change(s)                  |  |  |  |

|----------|--------------|-------------------------------------------|--|--|--|

| 2.00     | 26/03/2014   | Initial release                           |  |  |  |

| 2.01     | 17/11/2014   | Correct Block Diagram SATA device support |  |  |  |

ii Revision History

# **Preface**

#### Copyright 2014 ADLINK Technology Inc.

This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer.

#### Disclaimer

The information in this document is subject to change without prior notice in order to improve reliability, design, and function and does not represent a commitment on the part of the manufacturer.

In no event will the manufacturer be liable for direct, indirect, special, incidental, or consequential damages arising out of the use or inability to use the product or documentation, even if advised of the possibility of such damages.

#### **Environmental Responsibility**

ADLINK is committed to fulfill its social responsibility to global environmental preservation through compliance with the European Union's Restriction of Hazardous Substances (RoHS) directive and Waste Electrical and Electronic Equipment (WEEE) directive. Environmental protection is a top priority for ADLINK. We have enforced measures to ensure that our products, manufacturing processes, components, and raw materials have as little impact on the environment as possible. When products are at their end of life, our customers are encouraged to dispose of them in accordance with the product disposal and/or recovery programs prescribed by their nation or company.

#### **Trademarks**

Product names mentioned herein are used for identification purposes only and may be trademarks and/or registered trademarks of their respective companies.

Preface iii

#### **Using this Manual**

#### **Audience and Scope**

The cPCI-3510 User's Manual is intended for hardware technicians and systems operators with knowledge of installing, configuring and operating industrial grade single board computers.

#### Manual Organization

This manual is organized as follows:

**Chapter 1, Introduction:** Introduces the cPCI-3510, its features, block diagrams, and package contents.

**Chapter 2, Specifications:** Presents detailed specification information, power consumption, and technical drawings.

**Chapter 3, Functional Description:** Describes the cPCI-3510 main functions.

**Chapter 4, Board Interfaces:** Describes the cPCI-3510 board interfaces.

**Chapter 5, Getting Started:** Describes the installation of components to the cPCI-3510 and rear transition modules.

**Chapter 6, Driver Installation:** Provides information on how to install the cPCI-3510 device drivers under Windows 7.

**Chapter 7, Watchdog Timer:** Describes the watchdog timer of the cPCI-3510.

**Chapter 8, BIOS Setup Utility:** Describes basic navigation for the AMI EFI BIOS setup utility.

**Chapter 9, IPMI User Guide:** Provides information on the base-board management controller (BMC) of the Intelligent Platform Management Interface (IPMI).

**Important Safety Instructions:** Presents safety instructions all users must follow for the proper setup, installation and usage of equipment and/or software.

**Getting Service:** Contact information for ADLINK's worldwide offices.

iv Preface

#### Conventions

Take note of the following conventions used throughout this manual to make sure that users perform certain tasks and instructions properly.

Additional information, aids, and tips that help users perform tasks.

Information to prevent *minor* physical injury, component damage, data loss, and/or program corruption when trying to complete a task.

Information to prevent **serious** physical injury, component damage, data loss, and/or program corruption when trying to complete a specific task.

Preface v

This page intentionally left blank.

vi Preface

# **Table of Contents**

| R  | evisi | on History                               | . ii |

|----|-------|------------------------------------------|------|

| Pı | refac | e                                        | iii  |

| Li | st of | Figures                                  | χi   |

| Li | st of | Tables                                   | xiii |

| 1  | Intro | oduction                                 | . 1  |

|    | 1.1   | Overview                                 | 1    |

|    | 1.2   | Features                                 | 2    |

|    | 1.3   | Model Number Decoder                     | 3    |

|    | 1.4   | Package Contents                         | 5    |

| 2  | Spe   | cifications                              | . 7  |

|    | 2.1   | cPCI-3510 Processor Blade Specifications | 7    |

|    | 2.2   | cPCI-R3P00(T) RTM Specifications         | 11   |

|    | 2.3   | Block Diagrams                           | 12   |

|    | 2.4   | I/O Connectivity Table                   | 19   |

|    | 2.5   | Power Requirements                       | 21   |

| 3  | Fun   | ctional Description                      | 23   |

|    | 3.1   | Processors                               | 23   |

|    | 3.2   | Platform Controller Hub                  | 25   |

|    | 3.3   | PMC/XMC                                  | 25   |

|    | 3.4   | Intel® Turbo Boost Technology            | 26   |

|    | 3.5   | Intel® Hyper-Threading Technology        | 26   |

|    | 3.6   | Trusted Platform Module                  | 26   |

|    | 3.7   | Battery                                  | 27   |

| 4  | Boa   | rd Interfaces                            | 29   |

|   | 4.1   | cPCI-3510 Series Board Layout               | 29  |

|---|-------|---------------------------------------------|-----|

|   | 4.2   | cPCI-3510 Blade Assembly Layout             | 31  |

|   | 4.3   | cPCI-3510D Blade Assembly Layout            | 32  |

|   | 4.4   | cPCI-3510G Blade Assembly Layout            | 33  |

|   | 4.5   | cPCI-3510L Blade Assembly Layout            | 34  |

|   | 4.6   | cPCI-3510M Blade Assembly Layout            | 35  |

|   | 4.7   | cPCI-3510, cPCI-3510D, cPCI-3510G Faceplate | 36  |

|   | 4.8   | cPCI-3510L, cPCI-3510M Front Panel          | 37  |

|   | 4.9   | cPCI-R3P00(T) RTM Board Layout              | 39  |

|   | 4.10  | cPCI-R3P00(T) RTM Faceplate                 | 40  |

|   | 4.11  | Connector Pin Assignments                   | 41  |

|   | 4.12  | Jumper Settings                             | 66  |

| 5 | Getti | ng Started                                  | 67  |

|   | 5.1   | CPU and Heatsink                            | 67  |

|   | 5.2   | SATA Drive Installation                     | 68  |

|   | 5.3   | Installing a CFast Card                     | 71  |

|   | 5.4   | Installing the cPCI-3510 to the Chassis     | 72  |

|   | 5.5   | RTM Installation - cPCI-R3P00(T)            | 73  |

| 6 | Drive | er Installation                             | 75  |

|   | 6.1   | cPCI-3510 Drivers                           | 75  |

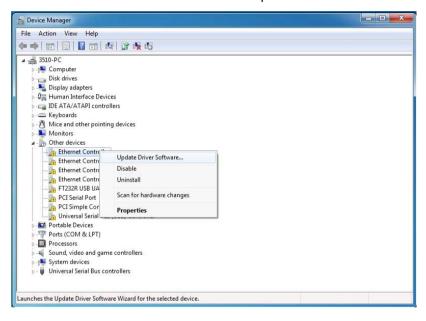

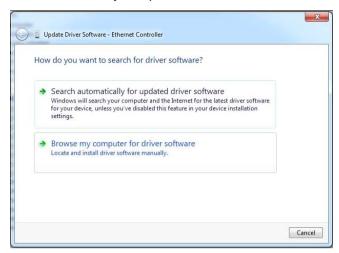

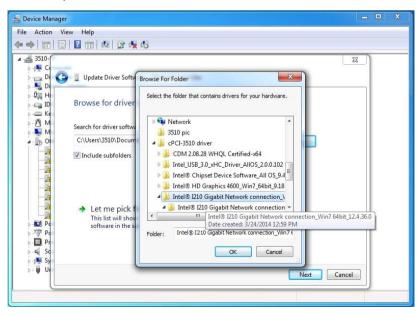

|   | 6.2   | Ethernet Controller Driver                  | 76  |

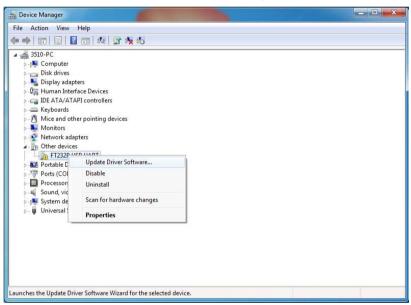

|   | 6.3   | USB-to-Serial Converter Driver (RTM)        | 78  |

| 7 | Watc  | hdog Timer                                  | 81  |

|   | 7.1   | Setting the Watchdog by IPMI Commands       | 81  |

| 8 | BIOS  | Setup Utility                               | 87  |

|   | 8.1   | Starting the BIOS                           | 87  |

|   | 8.2   | Main Setup                                  | 92  |

|   | 8.3   | Advanced BIOS Setup                         | 93  |

|   | 8.3   | 3.1 ACPI Settings                           | .94 |

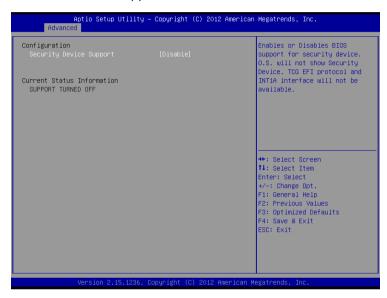

|   | 8.3   | 3.2 Trusted Computing                       | 95  |

|          | 8.3    | 3.3  | CPU Configuration                            | 96    |

|----------|--------|------|----------------------------------------------|-------|

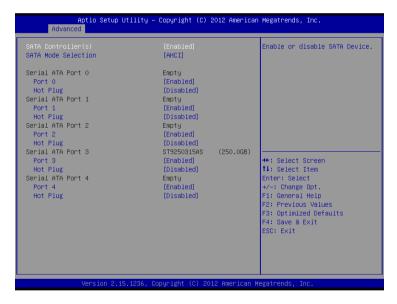

|          | 8.3    | 3.4  | SATA Configuration                           | 97    |

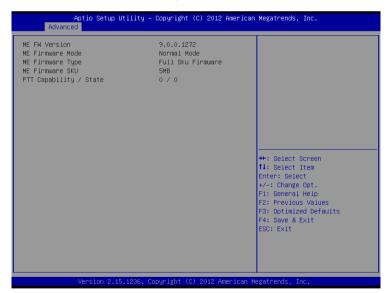

|          | 8.3    | 3.5  | PCH-FW Configuration                         | 98    |

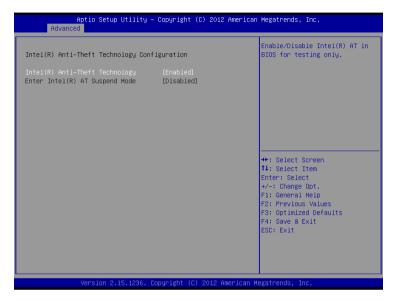

|          | 8.3    | 3.6  | Intel ® Anti-Theft Technology Configuration  | 99    |

|          | 8.3    | 3.7  | AMT Configuration                            | . 100 |

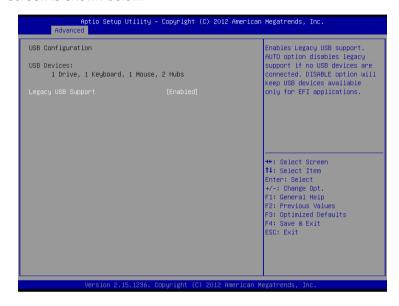

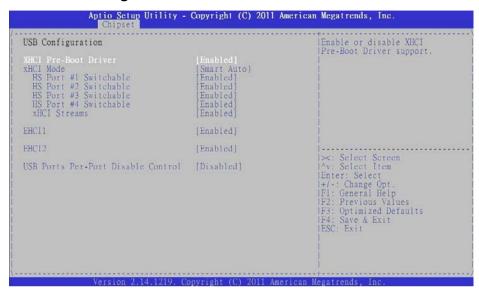

|          | 8.3    | 3.8  | USB Configuration                            | . 101 |

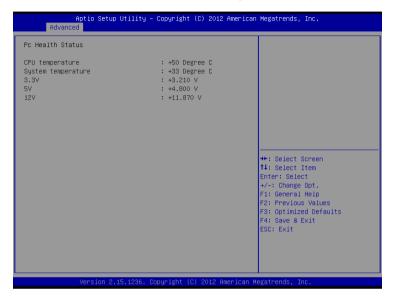

|          | 8.3    | 3.9  | Hardware Monitor                             | . 102 |

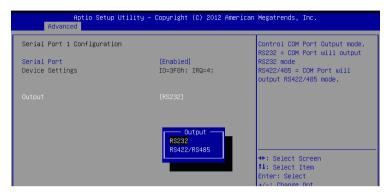

|          | 8.3    | 3.10 | Super IO Configuration                       | . 103 |

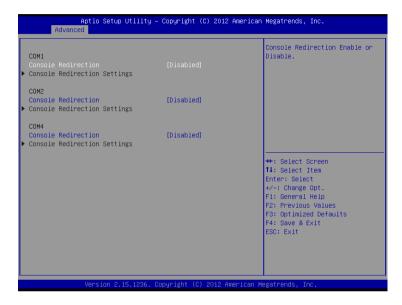

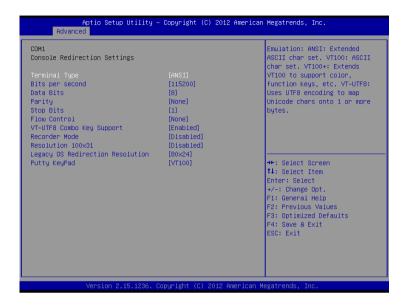

|          | 8.3    | 3.11 | Console Redirection                          | . 105 |

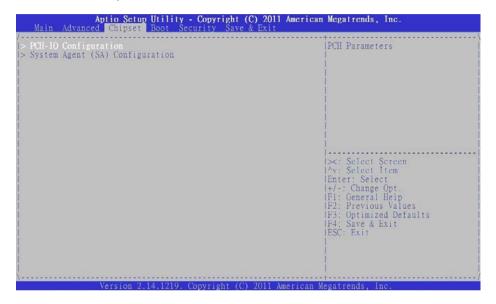

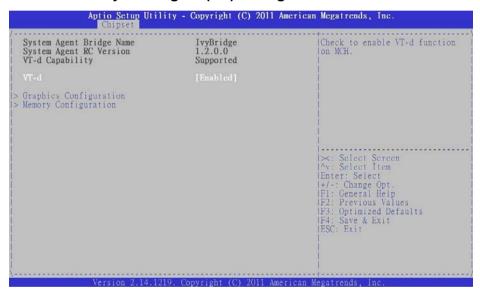

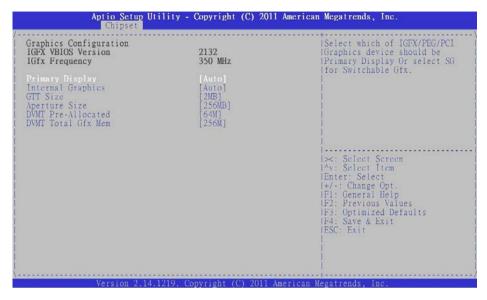

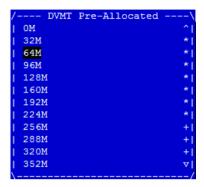

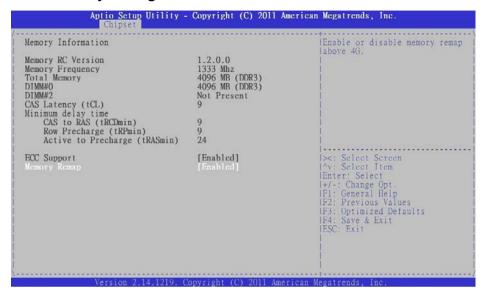

|          | 8.4    | Ch   | nipset Setup                                 | 108   |

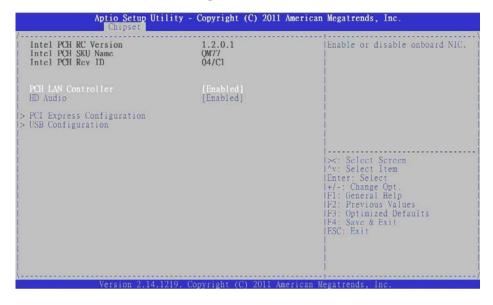

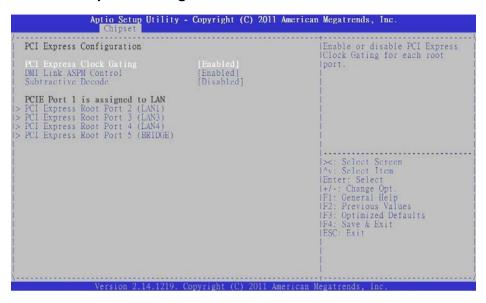

|          | 8.4    | 4.1  | PCH-IO Configuration                         | . 109 |

|          | 8.4    | 4.2  | System Agent (SA) Configuration              | . 112 |

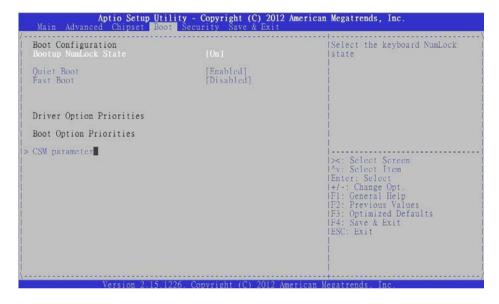

|          | 8.5    | Во   | oot Settings                                 | 116   |

|          | 8.     | 5.1  | CSM Parameter                                | . 117 |

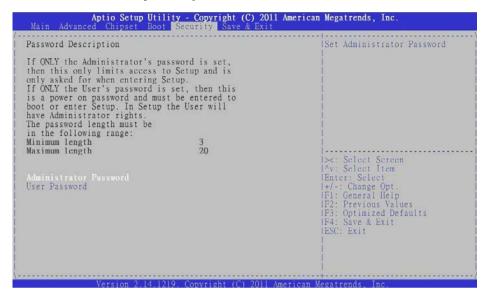

|          | 8.6    | Se   | curity Setup                                 | 119   |

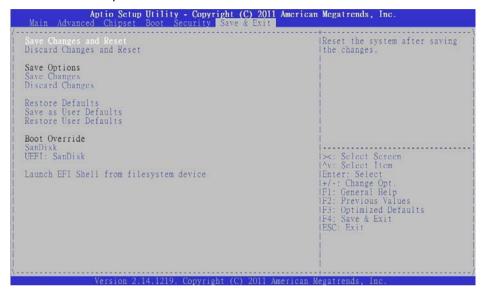

|          | 8.7    | Sa   | ve & Exit Menu                               | 120   |

| 9        | IPMI   | Us   | er Guide                                     | 123   |

|          | 9.1    | Int  | roduction                                    | 123   |

|          | 9.2    | Su   | mmary of Commands Supported by BMR-AVR-cPCI. | 123   |

|          | 9.3    | OE   | EM Commands Summary Table                    | 125   |

|          | 9.4    | Co   | mpactPCI Address Map                         | 128   |

|          | 9.5    | Co   | mmunications with IPMC                       | 129   |

|          | 9.6    | ΙΡΙ  | MI Sensors List                              | 129   |

|          | 9.7    | Re   | elevant Documents                            | 130   |

| ln       | porta  | int  | Safety Instructions                          | 131   |

| <u>م</u> | ettina | Se   | arvice                                       | 122   |

This page intentionally left blank.

# **List of Figures**

| Figure 2-1:  | cPCI-3510 Blade Functional Block Diagram        | .12  |

|--------------|-------------------------------------------------|------|

| Figure 2-2:  | DB-3610L2 Daughter Board Functional Block Diag  | 13   |

| Figure 2-3:  | DB-3970L2 Daughter Board Functional Block Diag  | 14   |

| Figure 2-4:  | DB-LANL2-S Daughter Board Functional Block Diag | 15   |

| Figure 2-5:  | DB-Max Daughter Board Functional Block Diagram  | .16  |

| Figure 2-6:  | cPCI-R3P00 RTM Functional Block Diagram         | .17  |

| Figure 2-7:  | cPCI-R3P00T RTM Functional Block Diagram        | 18   |

| Figure 4-1:  | cPCI-3510 Series Board Layout (component side)  | 29   |

| Figure 4-2:  | cPCI-3510 Series Board Layout (solder side)     | 30   |

| Figure 4-3:  | cPCI-3510 Blade Assembly Layout                 | 31   |

| Figure 4-4:  | cPCI-3510D Blade Assembly Layout                | 32   |

| Figure 4-5:  | cPCI-3510G Blade Assembly Layout                | . 33 |

| Figure 4-6:  | cPCI-3510L Blade Assembly Layout                | 34   |

| Figure 4-7:  | cPCI-3510M Blade Assembly Layout                | 35   |

| Figure 4-8:  | cPCI-3510, cPCI-3510D/G Front Panel Layout      | 36   |

| Figure 4-9:  | cPCI-3510L, cPCI-3510M Front Panel Layout       | 37   |

| Figure 4-10: | cPCI-R3P00(T) RTM Board Layout                  | 39   |

| Figure 4-11: | cPCI-R3P00(T) RTM Front Panel                   | 40   |

| Figure 7-1:  | Example procedure for WDT over serial console   | 85   |

List of Figures xi

This page intentionally left blank.

xii List of Figures

# **List of Tables**

| Table 2-1:  | cPCI-3510 Processor Blade Specifications          | 7  |

|-------------|---------------------------------------------------|----|

| Table 2-2:  | cPCI-R3P00(T) RTM Specifications                  | 11 |

| Table 2-3:  | cPCI-3510 I/O Connectivity                        | 19 |

| Table 4-1:  | cPCI-3510 Front Panel System LED Descriptions     | 38 |

| Table 4-2:  | USB 2.0 Pin Definition                            | 41 |

| Table 4-3:  | VGA Pin Definition                                |    |

| Table 4-4:  | DisplayPort Pin Definition                        |    |

| Table 4-5:  | DVI-I Connector Pin Definition                    | 43 |

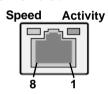

| Table 4-6:  | RJ-45 GbE Pin Definitions                         |    |

| Table 4-7:  | LAN LED Status Definitions                        |    |

| Table 4-8:  | PS/2 Keyboard/Mouse Pin Definition                |    |

| Table 4-9:  | cPCI-3510D/P COM1 (DB-9) Pin Definition           |    |

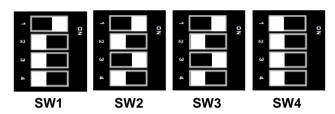

| Table 4-10: | cPCI-3510D/P COM1 Mode Selection Switch Settings. | 46 |

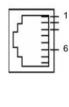

| Table 4-11: | cPCI-3510G/T COM1 (RJ-45) Pin Definition          |    |

| Table 4-12: | cPCI-3510G/T COM1 (DB-9 adapter) Pin Definition   | 47 |

| Table 4-13: | RS-422/485 Adapter Dongle Pin Definition          | 48 |

| Table 4-14: | cPCI-3510G/T COM1 with Dongle Pin Def'n           | 48 |

| Table 4-15: | cPCI-3510G/T COM2 Pin Header Definition           | 49 |

| Table 4-16: | cPCI-R3P00 RTM COM4 Pin Definition                | 49 |

| Table 4-17: | cPCI-R3P00(T) RTM COM5 Pin Definition             | 50 |

| Table 4-18: | cPCI-R3P00(T) RTM COM5 with Dongle Pin Def'n      | 50 |

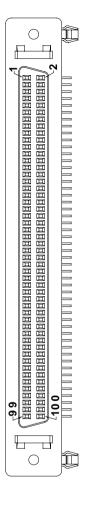

| Table 4-19: | cPCI-3510M 100-pin I/O Connector Pin Definition   | 51 |

| Table 4-20: | SATA Connector on RTM                             | 53 |

| Table 4-21: | SATA Connector on DB-3610L2/3970L2 Pin Def'n      | 53 |

| Table 4-22: | CFast Socket Pin Definition                       | 54 |

| Table 4-23: | DB-3610L2 Connector Pin Definition                | 55 |

| Table 4-24: | DB-3CFAST Connector Pin Definition                | 56 |

| Table 4-25: | DB-3970L2 Connector Pin Definition                | 57 |

| Table 4-26: | DB-3UMC Connector Pin Definition                  | 58 |

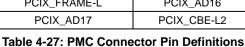

| Table 4-27: | PMC Connector Pin Definitions                     | 59 |

| Table 4-28: | XMC Connector Pin Definition                      | 61 |

| Table 4-29: | CompactPCI J1 Connector Pin Definition            | 62 |

| Table 4-30: | CompactPCI J2 Connector Pin Definition            | 63 |

| Table 4-31: | cPCI-R3P00 rJ2 Connector Pin Definition           | 64 |

| Table 4-32: | cPCI-R3P00T rJ2 Connector Pin Definition          | 65 |

| Table 4-33: | Load BIOS Default Jumper Settings                 | 66 |

| Table 4-34: | XMC VPWR Select Jumper Settings                   |    |

| Table 4-35: | PMC V(I/O) Select Jumper Settings                 |    |

List of Tables xiii

This page intentionally left blank.

xiv List of Tables

# 1 Introduction

#### 1.1 Overview

The ADLINK cPCI-3510 Series is a 3U CompactPCI® PlusIO compatible processor blade with soldered DDR3L-1600 ECC memory up to 8GB. The ADLINK cPCI-3510 features an Intel® Core™ i7 processor with Mobile Intel® QM87 Express Chipset.

The cPCI-3510 Series is a 3U CompactPCI blade available in single-slot (4HP), dual-slot (8HP) or triple-slot (12HP) width form factors with various daughter boards to provide a broad range of I/O requirements. Front panel I/O in the single-slot (4HP) version includes 1x DVI-I, 2x GbE and 1x USB 3.0 port (these I/O are common to all versions). Front panel I/O in the dual-slot (8HP) version includes additional 2x USB 2.0, 1x COM, 1x KB/MS and Line-in/Line-out on the cPCI-3510D or additional 2x DisplayPorts, 1x COM in RJ-45 connector, 1x KB/MS and 1x additional USB2.0 port on the cPCI-3510G. Two more dual-slot options are the cPCI-3510L with additional 2x GbE, 1x COM and 2x USB and the cPCI-3510M with one 100-pin high density connector supporting additional 2x DVI-I/DP, 2x USB 2.0, 2x COM, 2x KB/MS and Line-in/Line-out ports.

Graphics support is integrated on the CPU and allows 3 independent displays on the front panel by selecting the cPCI-3510G with additional 2x DisplayPorts. Storage includes a CFast slot or a 32GB SSD (optional) and 2.5" SATA HDD on the layer 2 riser card (cPCI-3510D/P/L/M). One optional PCI 32-bit/66 MHz PMC site or PCIe x1 XMC site is available on the 8HP or 12HP versions (cPCI-3510S or cPCI-3510P/T).

Rear I/O signals to J2 include 4x PCle x1, 3x SATA 3 Gb/s, and 3x USB 2.0. GPIO and SMBus signals are also routed to the J2 connector. The optional Rear Transition Module (RTM) provides 3x SATA, 2x GbE, 2x USB, 1x COM (Tx/Rx) and 1x VGA port.

The cPCI-3510 is a high performance solution for factory automation and other industrial applications that require superior data transfer capability and advanced computing power. The ADLINK cPCI-3510 provides high manageability, supports Satellite mode operation as a standalone blade in peripheral slots, and IPMI for

system health monitoring. A GbE port on the faceplate supports Intel® AMT 9.0 for remote monitoring.

#### 1.2 Features

- ▶ 3U CompactPCI blade in 4HP, 8HP or 12HP width form factor

- Intel® Core™ i7-4700EQ Processor (4 cores, 8 threads, 6M cache, 2.4 GHz)

- ▶ Graphics and memory controllers integrated in processor

- ► Compatible with PICMG 2.30 PlusIO (3x SATA, 4x PCle x1, 3x USB, 2x GbE to J2)

- Dual channel DDR3L-1600 soldered SDRAM with ECC, up to 8GB

- 32bit/ 33, 66MHz CompactPCI Interface based on PCI specifications, universal V(I/O)

- Supports Satellite mode operation as a standalone blade in peripheral slots

- ▶ Optional 32-bit/66MHz PMC or PCIe x1 XMC site

- Supports IPMI for system health monitoring

- DVI-I port on front with VGA switchable to rear I/O by BIOS setting

- Additional two DisplayPorts on 8HP daughter board (cPCI-3510G)

- ▶ Supports 3 independent displays with DirectX 11.1, OpenGL 3.2

- ► Two PCIe Gigabit Ethernet egress ports, one supporting Intel iAMT 9.0

- ► Two additional PCIe Gigabit Ethernet Controllers routed to RTM (cPCI-R3P00)

- Additional two Gigabit Ethernet ports on 80mm RTM (cPCI-R3P00T)

- ► Line-in and Line-out ports on front panel (cPCI-3510D)

- ► CFast socket for SATA interface storage

- Optional onboard SSD for SATA interface storage (shares space with CFast socket)

- ▶ 2.5" SATA drive onboard on 8HP/12HP versions at 6 Gb/s (cPCI-3510/D/G/M/L)

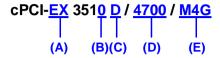

# 1.3 Model Number Decoder Blades

#### (A) Operating Temperature Code

- $\triangleright$  Blank = -20°C to +70°C

- $\triangleright$  **ET** = -40°C to +85°C (for CPUs with TDP below 37W only)

#### (B) J2 Connector Type Code

- 0 = HM connector

#### (C) Configuration Code

- Blank = Single slot width with CFast socket, 1x DVI-I, 1x USB 3.0, 2x GbE

- D = Dual slot width with CFast socket, 1x DVI-I, 1x USB 3.0, 2x GbE on layer 1; 2x USB, COM (RS-232/422/485), PS/2 KB/MS, Line-in, Line-out ports and 2.5" SATA drive space on layer 2 DB-3610L2

- □ Dual slot width with CFast socket, 1x DVI-I, 1x USB 3.0, 2x GbE on layer 1; 2x DisplayPort, RJ-45 COM (RS-232/422/485), PS/2 KB/MS, USB ports, onboard SATA connector and 2.5" SATA drive space on layer 2 DB-3970L2

- ▶ L = Dual slot width with CFast socket, 1x DVI-I, 1x USB 3.0, 2x GbE on layer 1; 2x GbE, 1x DB-9 COM (RS-232/422/485), 1x USB2.0 at front panel, 1x onboard USB port and 2.5" SATA drive space on layer 2 DB-LAN2-S

- M = Dual slot width with CFast socket, 1x DVI-I, 1x USB 3.0, 2x GbE on layer 1; 1x 100-pin high density connector supports 2xDVI/DP, 2x USB2.0, 2x COM (RS-232/422/485), 1x KB/MS, audio and 2.5" SATA drive space on layer 2 DB-Max

- S = Dual slot width with CFast socket, 1x DVI-I, 1x USB 3.0, 2x GbE on layer 1; PMC/XMC site on layer2 DB-3UMC

- P =Triple slot width with CFast socket, 1x DVI-I, 1x USB 3.0, 2x GbE on layer 1; 2x USB, COM (RS-232/422/485), PS/2 KB/MS, Line-in, Line-out ports and 2.5" SATA drive space on layer 2 DB-3610L2; PMC/XMC site in layer 3 DB-3UMC

- ➤ T = Triple slot width with CFast socket, 1x DVI-I, 1x USB 3.0, 2x GbE on layer 1; 2x DisplayPort, RJ-45 COM, PS/2 KB/MS, USB ports, onboard SATA connector and 2.5" SATA drive space on layer 2 DB-3970L2; PMC/XMC site on layer 3 DB-3UMC

- Other = ODM/OEM project code

#### (D) CPU Code

▶ 4700EQ = Quad Core Intel® i7-4700EQ processor

#### (E) Memory Size Code

- → M8G = 2x 4GB DDR3L-1600 soldered SDRAM

#### **RTMs**

#### (A) Model Code

- Blank = dual slot width, 50mm depth 3U RTM with 2x COM, 2x USB, 3x SATA, VGA, 2x GbE (switched from front CPU blade)

- □ T = dual slot width, 80mm depth 3U RTM with 2x COM, 2x USB, 3x SATA, VGA, 2x GbE (independent from front CPU blade)

## 1.4 Package Contents

The cPCI-3510 is packaged with the following components. If any of the following items are missing or damaged, retain the shipping carton and packing material and contact the dealer for inspection. Please obtain authorization before returning any product to ADLINK. The packing contents of cPCI-3510 Series non-standard configurations will vary depending on customer requests.

#### CPU module

- ▶ The cPCI-3510 Series Processor Blade

- CPU and memory specifications will differ depending on options selected

- Thermal module is assembled on the board.

- ➤ Y-cable for PS/2 combo port (8HP/12HP version only)

- ▶ 2.5" HDD accessory pack (8HP/12HP version only)

- ► RJ-45 to DB-9 COM adapter cable (cPCI-3510G version only)

- ► RS-422/485 DB-9-to-DB-9 dongle (cPCI-3510G version only)

- ▶ DisplayPort to DVI adapter cable (cPCI-3510G version only)

- ADLINK All-in-One DVD

- User's manual

No I/O cables are included with the cPCI-3510M version.

#### **Rear Transition Module**

- ▶ cPCI-R3P00 or cPCI-R3P00T RTM

- ► RS-422/485 DB-9-to-DB-9 dongle

#### **Optional Accessories**

- ▶ DB-3SSD adapter for onboard SSD 32GB

- ▷ DB-3SSD/B (P/N 30-37581-200E)

- ▷ DB-3SSD/NTPM (P/N 30-37581-100E)

(B: "coin cell battery", NTPM: "no TPM")

- ▶ DisplayPort to DVI adapter cable (P/N 30-01120-0000)

- ▶ DisplayPort to VGA adapter cable (P/N 30-01119-0000)

- ▶ DisplayPort to HDMI adapter cable (P/N 30-01121-0000)

The contents of non-standard cPCI-3510 configurations may vary depending on the customer's requirements.

This product must be protected from static discharge and physical shock. Never remove any of the components except at a static-free workstation. Use the anti-static bag shipped with the product when putting the board on a surface. Wear an anti-static wrist strap properly grounded on one of the system's ESD ground jacks when installing or servicing system components.

# 2 Specifications

# 2.1 cPCI-3510 Processor Blade Specifications

| PICMG® 2.0 CompactPCI® Rev. 3.0 PICMG® 2.1 Hot Swap Specification Rev. 2.0 PICMG® 2.3 System Management Rev. 1.0 PICMG® 2.30 CompactPCI® PlusIO  Mechanical Standard 3U CompactPCI® Board size: 100mm x 160mm Single slot (4HP, 20.32mm); Dual slot (8HP, 40.64mm); Triple-slot (12HP, 60.96 mm) CompactPCI® with HM type J1 connector, UHM type J2 connector  Processor Intel® Core™ i7-4700EQ Processor, 2.4 GHz, 6MB LLC cache, TDP 45W Passive heatsink  Chipset Memory Dual channel DDR3L-1600 ECC soldered memory Up to 8GB  CompactPCI Bus PCI 32bit/ 33MHz; 3.3V, 5V universal V I/O Supports operation in system slot as master or in peripheral slot as standalone blade without connectivity to CompactPCI bus (Satellite mode)  Gigabit Ethernet PCI Sthemmer Standard Shams Standalone blade without connectivity to CompactPCI bus (Satellite mode)  One PCIe x1 Intel® 1217 GbE PHY and three PCIe x1 Intel® 1210 Gigabit Ethernet controllers Two egress 10/100/1000BASE-T ports on front panel, one supporting Intel® AMT 9.0 by 1217 controller Two egress 10/100/1000BASE-T ports routed to rear transition module  Graphics  Integrated on Intel® Core™ processor DVI-I port on front panel, VGA switchable to J2 (RTM) by BIOS setting Analog monitor support up to QXGA 2048x1536 @75Hz, 32-bit Two DisplayPorts on front panel with resolution up to 2560x1600 @60Hz (cPCI-3510G only) Up to three IJSR front panel ports |            | <u> </u>                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Board size: 100mm x 160mm Single slot (4HP, 20.32mm); Dual slot (8HP, 40.64mm); Triple-slot (12HP, 60.96 mm) CompactPCI® with HM type J1 connector, UHM type J2 connector  Intel® Core™ i7-4700EQ Processor, 2.4 GHz, 6MB LLC cache, TDP 45W Passive heatsink  Chipset Memory Dual channel DDR3L-1600 ECC soldered memory Up to 8GB PCI 32bit/ 33MHz; 3.3V, 5V universal V I/O Supports operation in system slot as master or in peripheral slot as standalone blade without connectivity to CompactPCI bus (Satellite mode)  Gigabit Ethernet One PCIe x1 Intel® I217 GbE PHY and three PCIe x1 Intel® I210 Gigabit Ethernet controllers Two egress 10/100/1000BASE-T ports on front panel, one supporting Intel® AMT 9.0 by I217 controller Two egress 10/100/1000BASE-T ports routed to rear transition module  Graphics  Integrated on Intel® Core™ processor DVI-I port on front panel, VGA switchable to J2 (RTM) by BIOS setting Analog monitor support up to QXGA 2048x1536 @75Hz, 32-bit Two DisplayPorts on front panel with resolution up to 2560x1600 @60Hz (cPCI-3510G only) Up to three independent display                                                                                                                                                                                                                                                                                                                        | -          | <ul> <li>PICMG® 2.1 Hot Swap Specification Rev. 2.0</li> <li>PICMG® 2.9 System Management Rev. 1.0</li> </ul>                                                                                                                                                 |

| cache, TDP 45W Passive heatsink  Chipset  Mobile Intel® QM87 Express Chipset  Dual channel DDR3L-1600 ECC soldered memory Up to 8GB  CompactPCI Bus  PCI 32bit/ 33MHz; 3.3V, 5V universal V I/O Supports operation in system slot as master or in peripheral slot as standalone blade without connectivity to CompactPCI bus (Satellite mode)  Gigabit Ethernet  One PCIe x1 Intel® I217 GbE PHY and three PCIe x1 Intel® I210 Gigabit Ethernet controllers Two egress 10/100/1000BASE-T ports on front panel, one supporting Intel® AMT 9.0 by I217 controller Two egress 10/100/1000BASE-T ports routed to rear transition module  Graphics  Integrated on Intel® Core™ processor DVI-I port on front panel, VGA switchable to J2 (RTM) by BIOS setting Analog monitor support up to QXGA 2048x1536 @75Hz, 32-bit Two DisplayPorts on front panel with resolution up to 2560x1600 @60Hz (cPCI-3510G only) Up to three independent display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Mechanical | <ul> <li>Board size: 100mm x 160mm</li> <li>Single slot (4HP, 20.32mm); Dual slot (8HP, 40.64mm);<br/>Triple-slot (12HP, 60.96 mm)</li> <li>CompactPCI® with HM type J1 connector, UHM type J2</li> </ul>                                                     |

| <ul> <li>Dual channel DDR3L-1600 ECC soldered memory</li> <li>Up to 8GB</li> <li>PCI 32bit/ 33MHz; 3.3V, 5V universal V I/O</li> <li>Supports operation in system slot as master or in peripheral slot as standalone blade without connectivity to CompactPCI bus (Satellite mode)</li> <li>One PCIe x1 Intel® I217 GbE PHY and three PCIe x1 Intel® I210 Gigabit Ethernet controllers</li> <li>Two egress 10/100/1000BASE-T ports on front panel, one supporting Intel® AMT 9.0 by I217 controller</li> <li>Two egress 10/100/1000BASE-T ports routed to rear transition module</li> <li>Integrated on Intel® Core™ processor</li> <li>DVI-I port on front panel, VGA switchable to J2 (RTM) by BIOS setting</li> <li>Analog monitor support up to QXGA 2048x1536 @75Hz, 32-bit</li> <li>Two DisplayPorts on front panel with resolution up to 2560x1600 @60Hz (cPCI-3510G only)</li> <li>Up to three independent display</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Processor  | cache, TDP 45W                                                                                                                                                                                                                                                |

| <ul> <li>Up to 8GB</li> <li>PCI 32bit/ 33MHz; 3.3V, 5V universal V I/O</li> <li>Supports operation in system slot as master or in peripheral slot as standalone blade without connectivity to CompactPCI bus (Satellite mode)</li> <li>One PCIe x1 Intel® I217 GbE PHY and three PCIe x1 Intel® I210 Gigabit Ethernet controllers         <ul> <li>Two egress 10/100/1000BASE-T ports on front panel, one supporting Intel® AMT 9.0 by I217 controller</li> <li>Two egress 10/100/1000BASE-T ports routed to rear transition module</li> </ul> </li> <li>Graphics         <ul> <li>Integrated on Intel® Core™ processor</li> <li>DVI-I port on front panel, VGA switchable to J2 (RTM) by BIOS setting</li> <li>Analog monitor support up to QXGA 2048x1536 @75Hz, 32-bit</li> <li>Two DisplayPorts on front panel with resolution up to 2560x1600 @60Hz (cPCI-3510G only)</li> <li>Up to three independent display</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Chipset    | Mobile Intel® QM87 Express Chipset                                                                                                                                                                                                                            |

| <ul> <li>Supports operation in system slot as master or in peripheral slot as standalone blade without connectivity to CompactPCI bus (Satellite mode)</li> <li>One PCle x1 Intel® I217 GbE PHY and three PCle x1 Intel® I210 Gigabit Ethernet controllers         <ul> <li>Two egress 10/100/1000BASE-T ports on front panel, one supporting Intel® AMT 9.0 by I217 controller</li> <li>Two egress 10/100/1000BASE-T ports routed to rear transition module</li> </ul> </li> <li>Graphics         <ul> <li>Integrated on Intel® Core™ processor</li> <li>DVI-I port on front panel, VGA switchable to J2 (RTM) by BIOS setting</li> <li>Analog monitor support up to QXGA 2048x1536 @75Hz, 32-bit</li> <li>Two DisplayPorts on front panel with resolution up to 2560x1600 @60Hz (cPCI-3510G only)</li> <li>Up to three independent display</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Memory     | ,                                                                                                                                                                                                                                                             |

| Ethernet  I210 Gigabit Ethernet controllers  • Two egress 10/100/1000BASE-T ports on front panel, one supporting Intel® AMT 9.0 by I217 controller  • Two egress 10/100/1000BASE-T ports routed to rear transition module  Graphics  • Integrated on Intel® Core™ processor  • DVI-I port on front panel, VGA switchable to J2 (RTM) by BIOS setting  • Analog monitor support up to QXGA 2048x1536 @75Hz, 32-bit  • Two DisplayPorts on front panel with resolution up to 2560x1600 @60Hz (cPCI-3510G only)  • Up to three independent display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | =          | <ul> <li>Supports operation in system slot as master or in peripheral<br/>slot as standalone blade without connectivity to CompactPCI</li> </ul>                                                                                                              |

| <ul> <li>DVI-I port on front panel, VGA switchable to J2 (RTM) by BIOS setting</li> <li>Analog monitor support up to QXGA 2048x1536 @75Hz, 32-bit</li> <li>Two DisplayPorts on front panel with resolution up to 2560x1600 @60Hz (cPCI-3510G only)</li> <li>Up to three independent display</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | <ul> <li>I210 Gigabit Ethernet controllers</li> <li>Two egress 10/100/1000BASE-T ports on front panel, one supporting Intel® AMT 9.0 by I217 controller</li> <li>Two egress 10/100/1000BASE-T ports routed to rear</li> </ul>                                 |

| IISR • Up to three USB front panel ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Graphics   | <ul> <li>DVI-I port on front panel, VGA switchable to J2 (RTM) by BIOS setting</li> <li>Analog monitor support up to QXGA 2048x1536 @75Hz, 32-bit</li> <li>Two DisplayPorts on front panel with resolution up to 2560x1600 @60Hz (cPCI-3510G only)</li> </ul> |

| - Op to three OOB horiz paner ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | USB        | Up to three USB front panel ports                                                                                                                                                                                                                             |

Table 2-1: cPCI-3510 Processor Blade Specifications

| Serial Ports                       | <ul> <li>Up to four serial ports</li> <li>One RS-232/422/485 serial port on 8HP front panel (cPCI-3510D/G/L)</li> <li>Additional RS-232 10-pin header on layer-2 board (cPCI-3510G only)</li> <li>Up to two RS-232/422/485 COM port (cPCI-3510M only)</li> </ul>                                                                                                                                                                                                                                                      |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PMC/XMC                            | One 32-bit/66MHz PMC site or PCle x1 XMC site if<br>DB-3UMC daughter board is installed                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Audio                              | Line-in/Line-out on front panel by Realtek ALC262 High Definition Audio codec (cPCI-3510D only)  Line-in/Line-out on front panel by 100-pin connector (cPCI-3510M only)                                                                                                                                                                                                                                                                                                                                               |

| TPM                                | Atmel AT97SC3204 TPM (upon request) supporting:  Over/Under voltage detection  Low/High frequency sensor/filter  Reset filter  Memory encryption/decryption                                                                                                                                                                                                                                                                                                                                                           |

| Storage<br>Interfaces <sup>1</sup> | <ul> <li>CFast socket on daughter board</li> <li>Optional onboard SSD on daughter board</li> <li>One SATA 6Gb/s direct connector for 2.5" onboard HDD/SDD (8HP/12HP version only)</li> </ul>                                                                                                                                                                                                                                                                                                                          |

| BIOS                               | AMI® EFI BIOS, 64Mbit SPI flash memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OS<br>Compatibility                | <ul> <li>Microsoft Windows 7 32/64-bit</li> <li>Microsoft Windows 8 32/64-bit</li> <li>Red Hat Enterprise Linux 6.4, 64-bit</li> <li>Fedora 14, 32-bit</li> <li>VxWorks 6.9</li> <li>Real Time RTX (MSI)</li> <li>Other OS support upon request</li> </ul>                                                                                                                                                                                                                                                            |

| Environmental                      | <ul> <li>Operating Temperature (with forced air flow)<sup>2</sup>:         Standard: -20°C to 70°C         Extreme temperature: -40°C to +85°C (for Intel® Core™         i5 and Intel® Core™ i7-4700EQ processor with cTDP         down and forced air flow)</li> <li>Storage Temperature: -50°C to 100°C</li> <li>Humidity: 95% @60°C non-condensing</li> <li>Shock: 20G peak-to-peak, 11ms duration, non-operating</li> <li>Vibration<sup>3</sup>: 2Grms, 5-500Hz, each axis, operating (w/o hard drive)</li> </ul> |

| ЕМІ                                | CE EN55022     FCC Class A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Table 2-1: cPCI-3510 Processor Blade Specifications

#### Faceplate I/O 4HP (cPCI-3510) • 1x USB 3.0 ports • 2x 10/100/1000BASE-T Ethernet ports 1x DVI-I port 8HP (cPCI-3510D) 1x USB 3.0 ports 2x 10/100/1000BASE-T Ethernet ports • 1x DVI-I port 2x USB 2.0 ports DB-9 RS-232/422/485/485+ port PS/2 Keyboard/Mouse combo port Line-in and Line-out port 8HP (cPCI-3510G) 1x USB 3.0 ports • 2x 10/100/1000BASE-T Ethernet ports • 1x DVI-I port 2x DisplayPort • 1x USB 2.0 ports RJ-45 RS-232/422/485 port<sup>3</sup> PS/2 Keyboard/ Mouse combo port 8HP (cPCI-3510L) 1x USB 3.0 ports • 1x DVI-I port • 4x 10/100/1000BASE-T Ethernet ports 1x USB 2.0 ports DB-9 RS-232/422/485 port 8HP (cPCI-3510M) • 1x USB 3.0 ports 1x DVI-I port • 2x 10/100/1000BASE-T Ethernet ports 1x 100-pin connector supports 2x DVI/DP, Line-in/Line-out, 2x USB 2.0, 2x RS-232/422/485 COM, 1x KB/MS 8HP (cPCI-3510S) 1x USB 3.0 ports 2x 10/100/1000BASE-T Ethernet ports

Table 2-1: cPCI-3510 Processor Blade Specifications

1x DVI-I portPMC/XMC site

| Faceplate I/O | 12HP (cPCI-3510P)                                       |

|---------------|---------------------------------------------------------|

| •             | 1x USB 3.0 ports                                        |

|               | 2x 10/100/1000BASE-T Ethernet ports                     |

|               | 1x DVI-I port                                           |

|               | 2x USB 2.0 ports                                        |

|               | • DB-9 RS-232/422/485/485+ port                         |

|               | PS/2 Keyboard/Mouse combo port                          |

|               | Line-in and Line-out port                               |

|               | PMC/XMC site                                            |

|               | 12HP (cPCI-3510T)                                       |

|               | • 1x USB 3.0 ports                                      |

|               | <ul> <li>2x 10/100/1000BASE-T Ethernet ports</li> </ul> |

|               | 1x DVI-I port                                           |

|               | 2x DisplayPort                                          |

|               | 1x USB 2.0 ports                                        |

|               | • RJ-45 RS-232/422/485 port1                            |

|               | PS/2 Keyboard/ Mouse combo port                         |

#### Table 2-1: cPCI-3510 Processor Blade Specifications

PMC/XMC site

- The storage device limits the operational vibration tolerance. When the application requires higher specification for anti-vibration, it is recommended to use a flash storage device.

- ADLINK-certified thermal design. The thermal performance is dependent on the chassis cooling design. Sufficient forced air-flow is required.

Temperature limits of optional mass storage devices may also affect the thermal specification.

- A DB-9-to-DB-9 dongle to convert the cPCI-3510G RS-422/485 pin definitions to common pin definitions is included in the package ("cPCI-3510G/T Serial Ports" on page 47).

# 2.2 cPCI-R3P00(T) RTM Specifications

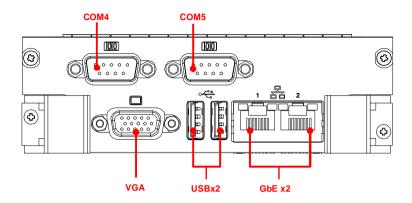

| Mechanical            | Board Size  • cPCI-R3P00: 100mm x 50mm  • cPCI-R3P00T: 100mm x 80mm  Dual-slot (8HP, 40.64mm)  (optional single slot upon request)                                                                 |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Gigabit<br>Ethernet   | <ul> <li>cPCI-R3P00: Two GbE ports switched from cPCI-3510 2x independent controller i210</li> <li>cPCI-R3P00T: Two GbE ports from independent Intel 82580DB GbE controller<sup>1</sup></li> </ul> |

| Serial Ports          | <ul> <li>Two serial ports on I/O panel from pin header</li> <li>One port converted from USB supporting RS-232/422/485<sup>1</sup></li> <li>One port provides Tx, Rx signals only</li> </ul>        |

| Storage<br>Interfaces | Three 7-pin Serial ATA ports                                                                                                                                                                       |

| Faceplate I/O         | <ul> <li>2x USB 2.0 ports</li> <li>2x 10/100/1000BASE-T Ethernet ports</li> <li>Analog DB-15 VGA port</li> <li>2x COM ports</li> </ul>                                                             |

## Table 2-2: cPCI-R3P00(T) RTM Specifications

A DB-9-to-DB-9 dongle to convert the cPCI-R3P00 RS-422/485 pin definitions to common pin definitions is included in the package ("COM5 Connector (DB-9)" on page 50).

Specifications are subject to change without prior notice.

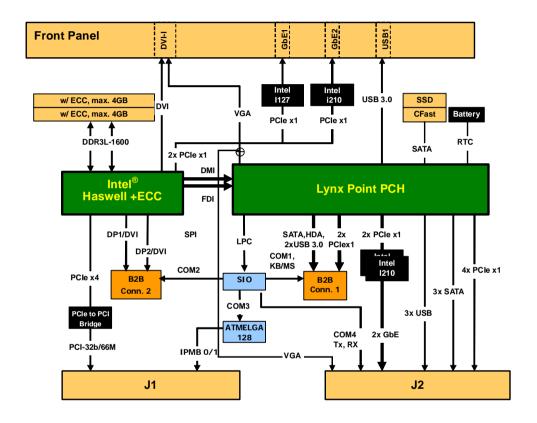

# 2.3 Block Diagrams

#### cPCI-3510 Blade

Figure 2-1: cPCI-3510 Blade Functional Block Diagram

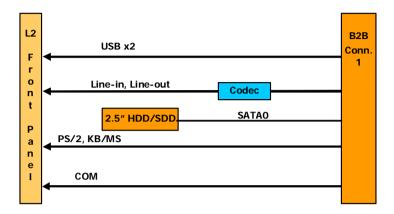

# **DB-3610L2 Daughter Board**

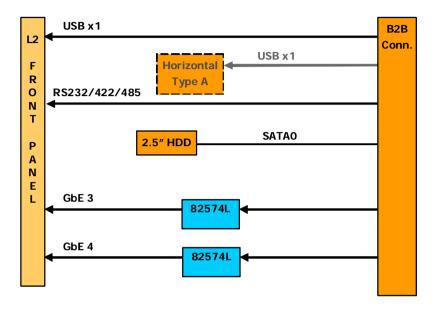

Figure 2-2: DB-3610L2 Daughter Board Functional Block Diagram

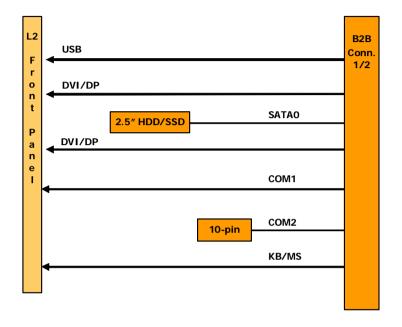

# **DB-3970L2 Daughter Board**

Figure 2-3: DB-3970L2 Daughter Board Functional Block Diagram

# **DB-LANL2-S Daughter Board**

(cPCI-3510L versions)

Figure 2-4: DB-LANL2-S Daughter Board Functional Block Diagram

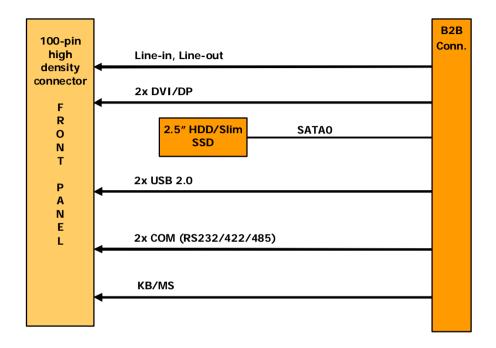

# **DB-Max Daughter Board**

(cPCI-3510M versions)

Figure 2-5: DB-Max Daughter Board Functional Block Diagram

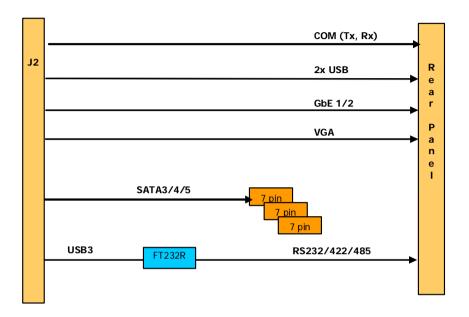

#### cPCI-R3P00 RTM

Figure 2-6: cPCI-R3P00 RTM Functional Block Diagram

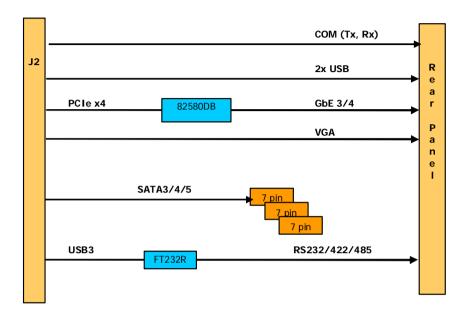

## cPCI-R3P00T RTM

Figure 2-7: cPCI-R3P00T RTM Functional Block Diagram

# 2.4 I/O Connectivity Table

| Function         | cPCI-3510 (4HP) |         | cPCI-3510D (8HP) |                    | cPCI-3510G (8HP) |                       |

|------------------|-----------------|---------|------------------|--------------------|------------------|-----------------------|

| Function         | Faceplate       | Onboard | Faceplate        | Onboard            | Faceplate        | Onboard               |

| Gigabit Ethernet | Y x2            |         | Y x2             |                    | Y x2             |                       |

| СОМ              |                 |         | Y (DB-9)         |                    | Y (RJ-45)        | Y (10-pin)            |

| USB 3.0          | Yx1             |         | Yx1              |                    | Yx1              |                       |

| USB 2.0          |                 |         | Y x2             |                    | Y x1             |                       |

| DVI-I            | Υ               |         | Υ                |                    | Υ                |                       |

| VGA              |                 |         |                  |                    |                  |                       |

| DisplayPort      |                 |         |                  |                    | Y x2             |                       |

| Serial ATA       |                 |         |                  | Y (for 2.5" drive) |                  | Y (for<br>2.5" drive) |

| CFast            |                 | Y       |                  | Y                  |                  | Υ                     |

| PS/2 KB/MS       |                 |         | Υ                |                    | Υ                |                       |

| Line-in/out      |                 |         | Υ                |                    |                  |                       |

| System LEDs      | Y x5            |         | Y x5             |                    | Y x5             |                       |

| Reset Button     | Υ               |         | Υ                |                    | Υ                |                       |

Table 2-3: cPCI-3510 I/O Connectivity

| Function         | cPCI-351  | 0L (8HP)              | cPCI-3510M (8HP) |                       | R3P00(T) (RTM)      |                 |

|------------------|-----------|-----------------------|------------------|-----------------------|---------------------|-----------------|

| Tunction         | Faceplate | Onboard               | Faceplate        | Onboard               | Faceplate           | Onboard         |

| Gigabit Ethernet | Yx4       |                       | Yx2              |                       | Y x2 <sup>(1)</sup> |                 |

| СОМ              | Y (DB-9)  |                       | Yx2              |                       | Y x2                |                 |

| USB 3.0          | Yx1       |                       | Yx1              |                       |                     |                 |

| USB 2.0          | Yx1       |                       | Y2x              |                       | Y x2                |                 |

| DVI-I            | Υ         |                       | Υ                |                       |                     |                 |

| VGA              |           |                       |                  |                       | Y <sup>(2)</sup>    |                 |

| DisplayPort      |           |                       |                  |                       |                     |                 |

| Serial ATA       |           | Y (for<br>2.5" drive) |                  | Y (for<br>2.5" drive) |                     | Y x3<br>(7-pin) |

| CFast            |           | Υ                     |                  | Υ                     |                     |                 |

| PS/2 KB/MS       |           |                       | Υ                |                       |                     |                 |

| Line-in/out      |           |                       | Υ                |                       |                     |                 |

| System LEDs      | Y x5      |                       | Y x5             |                       |                     |                 |

| Reset Button     | Υ         |                       | Υ                |                       |                     |                 |

Table 2-3: cPCI-3510 I/O Connectivity (cont'd)

- Routed from CPU blade front ports for cPCI-R3P00, ports independent from front panel for cPCI-R3P00T.

- 2. VGA switched from front panel.

## 2.5 Power Requirements

In order to guarantee a stable functionality of the system, it is recommended to provide more power than the system requires. An industrial power supply unit should be able to provide at least twice as much power as the entire system requires of each voltage. An ATX power supply unit should be able to provide at least three times as much power as the entire system requires of each voltage.

The tolerance of the voltage lines described in the CompactPCI specification (PICMG 2.0 R3.0) is +5%-3% for 5, 3.3 V and  $\pm5\%$  for  $\pm12$ V. This specification is for power delivered to each slot and it includes both the power supply and the backplane tolerance.

| Voltage                           | Nominal<br>Value      | Tolerance | Max. Ripple<br>(P - P) |

|-----------------------------------|-----------------------|-----------|------------------------|

| 5V                                | +5.0 VDC              | +5% / -3% | 50 mV                  |

| 3.3V                              | +3.3 VDC              | +5% / -3% | 50 mV                  |

| +12V                              | +12 VDC               | +5% / -5% | 240 mV                 |

| -12V                              | -12 VDC               | +5% / -5% | 240 mV                 |

| V I/O (PCI I/O<br>Buffer Voltage) | +3.3 VDC or<br>+5 VDC | +5% / -3% | 50 mV                  |

| GND                               |                       |           |                        |

#### **Power Consumption**

This section provides information on the power consumption of cPCI-3510 Series when using the Intel® Core™ i7 processors with 4GB DDR3L-1600 ECC soldered memory and onboard 64GB SATA flash disk. The cPCI-3510 is powered by 5V and 3.3V. Power consumption at 100% CPU usage was measured using the Intel Thermal Analysis Tool (TAT).

| Intel® Core™i7-4700EQ       |            |              |                    |  |  |

|-----------------------------|------------|--------------|--------------------|--|--|

| OS/Mode                     | Current 5V | Current 3.3V | <b>Total Power</b> |  |  |

| DOS/Idle mode               | 3.79 A     | 0.73 A       | 21.4 W             |  |  |

| Windows XP/Idle mode        | 3.56 A     | 0.71 A       | 20.1 W             |  |  |

| Windows® XP, CPU 100% Usage | 6.97 A     | 0.71 A       | 37.2 W             |  |  |

# 3 Functional Description

The following sections describe the cPCI-3510 Series features and functions

#### 3.1 Processors

The Mobile 4th Generation Intel® Core™ Processor Family are state of the art, 64-bit, multi-core mobile processor built on 22 nanometer process technology. Based on a new micro-architecture, the processor is designed for a two-chip platform. The two-chip platform consists of a processor and Platform Controller Hub (PCH). The platform enables higher performance, lower cost, easier validation, and improved x-y footprint. The processor includes an Integrated Display Engine, Processor Graphics and Integrated Memory Controller.

The cPCI-3510 Series supports Intel® Core™ i7/i5 processors. The table below lists the general specifications and power ratings of the CPUs supported by the cPCI-3510 Series.

| Features                                | Core™ i7-<br>4700EQ | Core™ i5-<br>I5-4400E | Core™ i5-<br>4402E |

|-----------------------------------------|---------------------|-----------------------|--------------------|

| Clock                                   | 2.4GHz              | 2.7GHz                | 1.6 GHz            |

| Max. Single Core<br>Turbo Freq.         | 3.4GHz              | -                     | -                  |

| Last Level Cache                        | 6MB                 | 3MB                   | 3MB                |

| No. of Core(s)                          | 4/8                 | 2/4                   | 2/4                |

| Max. Power (TDP <sup>1</sup> )          | 47W                 | 37W                   | 25W                |

| DMI                                     | 5 GT/s              | 5 GT/s                | 5 GT/s             |

| T <sub>junction, MAX</sub> <sup>2</sup> | 100°C               | 100°C                 | 100°C              |

- The highest expected sustainable power while running known power intensive applications. TDP is not the maximum power that the processor can dissipate.

- 2. The maximum supported operating temperature.

## **Supported Technologies**

| Features                                                        | Core™ i7-<br>4700EQ | Core™ i5-<br>I5-4400E | Core™ i5-<br>4402E |

|-----------------------------------------------------------------|---------------------|-----------------------|--------------------|

| Intel® Virtualization Technology for Directed I/O (Intel® VT-d) | Yes                 | Yes                   | Yes                |

| Intel® Virtualization Technology (Intel® VT-x)                  | Yes                 | Yes                   | Yes                |

| Intel® VT-x with Extended Page Tables (EPT)                     | Yes                 | _                     | _                  |

| Intel® Hyper-Threading<br>Technology                            | Yes                 | Yes                   | Yes                |

| Intel® 64 Architecture                                          | Yes                 | Yes                   | Yes                |

| Execute Disable Bit                                             | Yes                 | Yes                   | Yes                |

| Intel® Turbo Boost Technology                                   | 2.0                 | Yes                   | Yes                |

| Intel® vPro Technology                                          | Yes                 | Yes                   | Yes                |

| Enhanced Intel SpeedStep® Technology                            | Yes                 | Yes                   | Yes                |

| Thermal Monitoring<br>Technologies                              | Yes                 | Yes                   | Yes                |

| Intel® Identity Protection<br>Technology                        | Yes                 | _                     | _                  |

#### Interfaces

- ► Two channels of DDR3L-1333/1600 memory

- ▶ DDR3 memory data transfer rates of 1333 MT/s and 1600 MT/s

- ▶ 64-bit wide channels

- ▶ DDR3L I/O voltage of 1.35V

- ▶ 2Gb and 4Gb DDR3 DRAM technologies are supported for x8 and x16 devices (using 4Gb device technologies, the largest memory capacity possible is 8 GB, assuming dual-channel mode with x8, dual-ranked ECC SDRAM)

- ► PCI Express ports are fully-compliant with the PCI Express Base Specification, Revision 2.0.

- ▶ 5 GT/s point-to-point DMI interface to PCH is supported

#### 3.2 Platform Controller Hub

The Mobile Intel® QM87 Express Chipset provides extensive I/O support. Functions and capabilities include:

- ► The QM87 PCH provides extensive I/O support, functions and capabilities including:

- ► PCI Express Base Specification, Revision 2.0 support for up to eight ports with transfers up to 5 GT/s

- ► ACPI Power Management Logic Support, Revision 4.0a

- Enhanced DMA controller, interrupt controller, and timer functions

- ► Integrated Serial ATA host controllers with independent DMA operation on up to six ports

- ▶ USB host interface with two EHCI high-speed USB 2.0 Host controllers and two rate matching hubs provide support for up to fourteen USB 2.0 ports

- ► Integrated 10/100/1000 Gigabit Ethernet MAC with System Defense

- ➤ System Management Bus (SMBus) Specification, Version 2.0 with additional support for I2C devices

- ► Supports Intel® High Definition Audio

- ► Supports Intel® Rapid Storage Technology

- ► Supports Intel® Virtualization Technology for Directed I/O

- ► Integrated Clock Controller

- ► Analog and Digital Display ports

- ► Low Pin Count (LPC) interface

- ► Firmware Hub (FWH) interface support

- ► Serial Peripheral Interface (SPI) support

### 3.3 PMC/XMC

The cPCI-3510P/S/T models support one PMC or XMC site for front panel I/O expansion. The PMC site provides a maximum 32-bit/66MHz PCI bus link using a Pericom PI7C9X130 PCI-Express-to-PCI bridge and PCI-Express x1 link. The PMC site supports +3.3V signaling only. The XMC site provides a PCI Express x1 lane.

## 3.4 Intel® Turbo Boost Technology

Intel® Turbo Boost Technology is a feature that allows the processor to opportunistically and automatically run faster than its rated operating core and/or render clock frequency when there is sufficient power headroom, and the product is within specified temperature and current limits. The Intel Turbo Boost Technology feature is designed to increase performance of both multi-threaded and single-threaded workloads. The processor supports a Turbo mode where the processor can use the thermal capacity associated with package and run at power levels higher than TDP power for short durations. This improves the system responsiveness for short, bursty usage conditions.

Turbo Mode availability is independent of the number of active cores; however, the Turbo Mode frequency is dynamic and dependent on the instantaneous application power load, the number of active cores, user configurable settings, operating environment, and system design. If the power, current, or thermal limit is reached, the processor will automatically reduce the frequency to stay with its TDP limit.

## 3.5 Intel® Hyper-Threading Technology

Intel® Hyper-Threading Technology allows an execution core to function as two logical processors. While some execution resources (such as caches, execution units, and buses) are shared, each logical processor has its own architectural state with its own set of general-purpose registers and control registers. This feature must be enabled using the BIOS and requires operating system support. Intel recommends enabling Hyper-Threading Technology with Microsoft Windows 7, Vista, and XP, and disabling Hyper-Threading Technology using the BIOS for all previous versions of Windows operating systems.

#### 3.6 Trusted Platform Module

The cPCI-6530 is optionally equipped with an Atmel AT97SC3204 Trusted Platform Module (TPM). The TPM is a secure controller with added cryptographic functionality to provide users a secure environment in e-commerce transactions and Internet communications.

The key features Trusted Platform Module (TPM) offers are:

- ► Fully compliant to the Trusted Computing Group (TCG)

Trusted Platform Module (TPM) version 1.2 specification

- ▶ Hardware hash accelerator for SHA-1 algorithm

- ▶ Advanced Crypto Engine (ACE) for asymmetric key operations(up to 2048-bit key length) to make hardware protection.

- ► Tick counter to extend the time required to decipher the key

- ▶ In addition to encryption key created by user. it also provide some security features to protect the integrated circuit itself:

- ▶ Over/Under-voltage detection to monitor the system stability. If the voltage fluctuates dramatically, this function can block the data transfer and lock the chip.

- ► Low/High frequency sensor to detect the IC clock frequency. If the frequency fluctuates dramatically, this function can block the data transfer and lock the chip.

- Reset filter to filter reset signal in order to break the time set by tick counter is received

- ▶ Memory encryption to protect memory

- Physical shield in the IC to protect the die from intruding or hacking by matching the data transferred on the 2 layer metal shield on the IC. If the data is not matched, the IC may be blocked.

## 3.7 Battery

The cPCI-3510 is equipped with a 3.0V "coin cell" lithium battery for the Real Time Clock (RTC). The battery socket is equipped on the DB-3CFAST daughter board. The lithium battery must be replaced with an identical battery or a battery type recommended by the manufacturer. A Rayovac BR2032 is equipped on board by default, and can be optionally equipped with a Gold Capacitor (Panasonic EECS5R5H105).

This page intentionally left blank.

## 4 Board Interfaces

This chapter illustrates the board layout, connector pin assignments, and jumper settings to familiarize users with the cPCI-3510 Series.

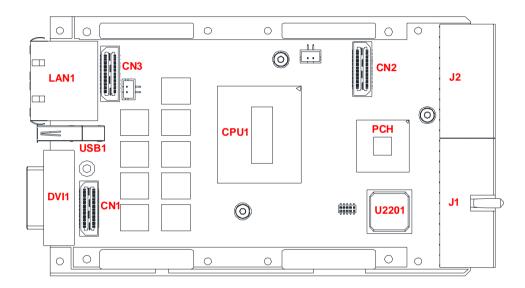

## 4.1 cPCI-3510 Series Board Layout

| CPU   | Intel® Core <sup>™</sup> Processor | J1    | CompactPCI Connector J1  |

|-------|------------------------------------|-------|--------------------------|

| PCH   | Intel® QM87 PCH                    | J2    | cPCI J2 (UHM/HM)         |

| CN4/5 | Stacked SO-CDIMM socket            | LAN1  | Dual Ethernet connectors |

| CN1   | DB-3610L2/DB-3970L2 connector      | DVI1  | DVI connector            |

| CN2   | DB-3CFAST connector                | USB1  | USB port                 |

| CN3   | DB-3970L2 connector                | U2201 | Pericom PI7C9X130        |

Figure 4-1: cPCI-3510 Series Board Layout (component side)

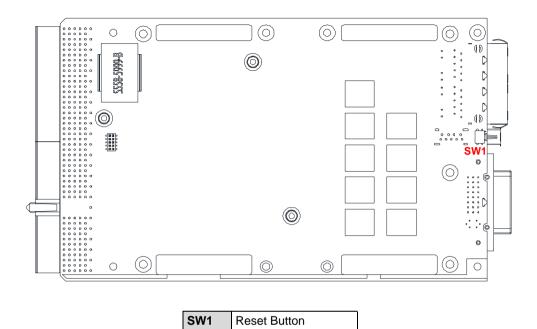

Figure 4-2: cPCI-3510 Series Board Layout (solder side)

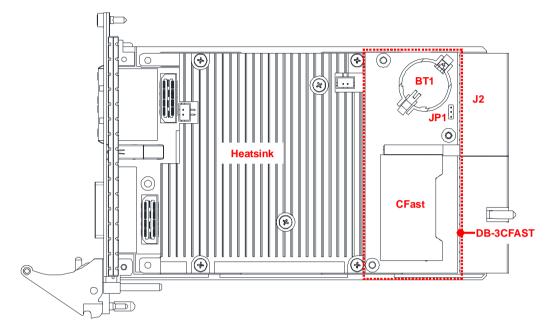

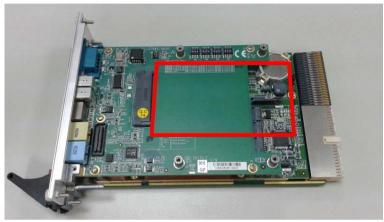

## 4.2 cPCI-3510 Blade Assembly Layout

This section describes the final assembly layout of the single slot cPCI-3510 Blade.

Figure 4-3: cPCI-3510 Blade Assembly Layout

| BT1 | Battery           | CFast | CFast socket     |

|-----|-------------------|-------|------------------|

| JP1 | Clear CMOS Jumper | J2    | cPCI J2 (UHM/HM) |

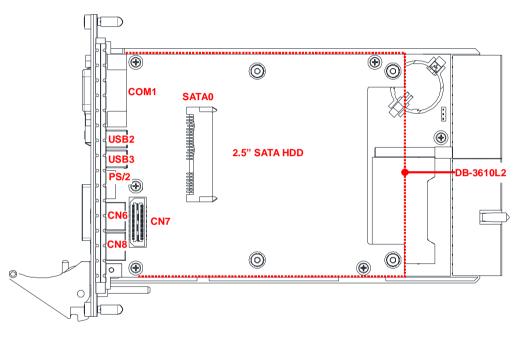

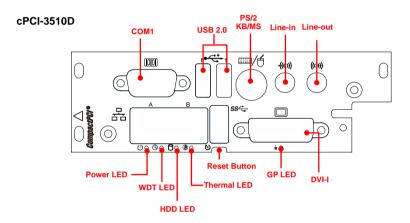

# 4.3 cPCI-3510D Blade Assembly Layout

The dual-slot width cPCI-3510D Blade is comprised of the cPCI-3510 single-slot main board and the DB-3610L2 riser card to expand I/O connectivity with PS/2, COM, 2x USB ports, Line-in, and Line-out ports .

| COM1   | DB-9 COM port         | CN7 | DB-3UMC connector |

|--------|-----------------------|-----|-------------------|

| USB2/3 | USB connectors        | CN6 | Line-in port      |

| PS2    | PS/2 KB/Ms Combo port | CN8 | Line-out port     |

| SATA0  | 22-pin SATA connector |     |                   |

Figure 4-4: cPCI-3510D Blade Assembly Layout

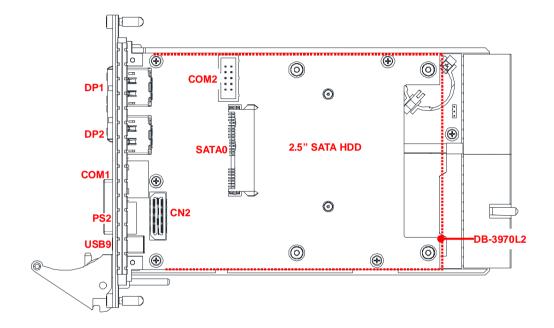

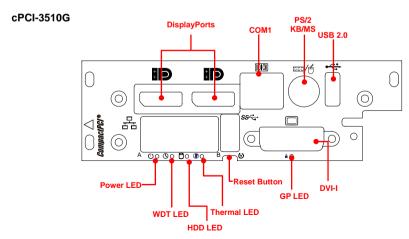

## 4.4 cPCI-3510G Blade Assembly Layout

The dual-slot width cPCI-3510G Blade is comprised of the cPCI-3510 single-slot main board and the DB-3970L2 riser card to expand I/O connectivity with PS/2, COM, USB ports, and 2x DisplayPorts.

| COM1  | RJ-45 COM port        | CN2   | DB-3UMC connector      |

|-------|-----------------------|-------|------------------------|

| COM2  | 10-pin COM port       | DP1/2 | DisplayPort connectors |

| USB9  | USB connector         | PS2   | PS/2 KB/MS Combo port  |

| SATA0 | 22-pin SATA connector |       |                        |

Figure 4-5: cPCI-3510G Blade Assembly Layout

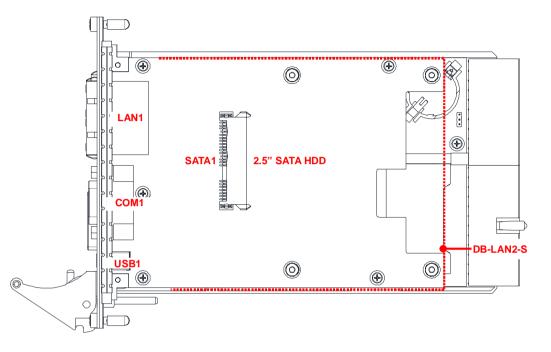

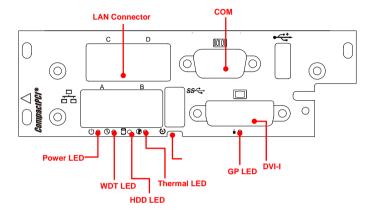

## 4.5 cPCI-3510L Blade Assembly Layout

The dual-slot width cPCI-3510L Blade is comprised of the cPCI-3510 single-slot main board and the DB-LAN2-S daughter board, expanding I/O connectivity with 2x LAN, COM, USB.

| LAN1 | GbE RJ-45 ports | USB1  | USB connector         |

|------|-----------------|-------|-----------------------|

| COM1 | DB-9 COM port   | SATA1 | 22-pin SATA connector |

Figure 4-6: cPCI-3510L Blade Assembly Layout

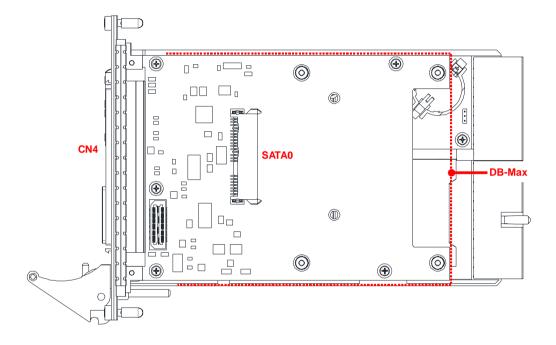

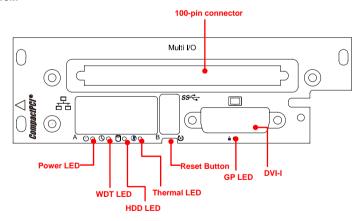

## 4.6 cPCI-3510M Blade Assembly Layout

The dual-slot width cPCI-3510M Blade is comprised of the cPCI-3510 single-slot main board and the DB-Max daughter board, expanding I/O connectivity with a 100-pin high density connector.

| CN4 | 100-pin high density | SATA0 | 22-pin SATA connector |

|-----|----------------------|-------|-----------------------|

|     | connector            |       |                       |

Figure 4-7: cPCI-3510M Blade Assembly Layout

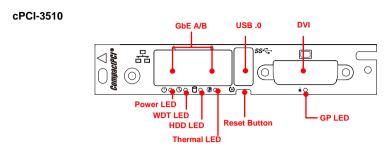

## 4.7 cPCI-3510, cPCI-3510D, cPCI-3510G Faceplate

Figure 4-8: cPCI-3510, cPCI-3510D, cPCI-3510G Front Panel Layout

## 4.8 cPCI-3510L, cPCI-3510M Front Panel

#### cPCI-3510L

#### cPCI-3510M

Figure 4-9: cPCI-3510L, cPCI-3510M Front Panel Layout

## **System LEDs**

| LED                                     | Color         | Condition   | Indication                                           |

|-----------------------------------------|---------------|-------------|------------------------------------------------------|

| Power <sup>1</sup>                      | 0 /           | OFF         | System is off                                        |

| ٠,                                      | Green/<br>Red | Red         | System Power ready (PWGD)                            |

| Ф                                       | 1100          | Green       | Post OK                                              |

| WDT <sup>1</sup>                        |               | OFF         | No Watchdog event                                    |

| Q                                       | Orange        | Blinking    | Watchdog event alert                                 |

| HDD                                     |               | OFF         | No CFast/SATA HDD activity                           |

| Blue                                    |               | Blinking    | Data read/write in process for CF/CFast/<br>SATA HDD |

| Overheat <sup>1</sup>                   |               | OFF         | CPU T <sub>junction</sub> temperature is under 100°C |

| ℯ                                       | Red           |             | CPU T <sub>junction</sub> temperature exceeds 100°C  |

| GP<br>(General<br>Purpose) <sup>1</sup> | Yellow        | OFF         | No activity                                          |

| Ô                                       | TEIIOW        | ON/Blinking | Defined by user                                      |

Table 4-1: cPCI-3510 Front Panel System LED Descriptions

1. Power, WDT, Overheat, GP LEDs are connected to GPIO pins of IPMC. The Power, WDT, Thermal LEDs can be programmed by the user as general purpose LEDs.

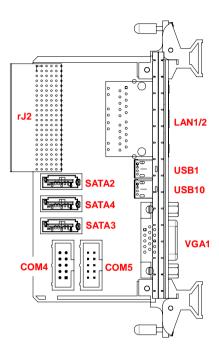

## 4.9 cPCI-R3P00(T) RTM Board Layout

| COM5*     | RS-232/422/485 port<br>(converted from USB) | LAN1/2  | Dual Ethernet ports |

|-----------|---------------------------------------------|---------|---------------------|

| COM4      | RS-232 port (Tx, Rx only)                   | VGA1    | VGA port            |

| SATA2/3/4 | SATA ports                                  | USB1/10 | USB ports           |

| rJ2       | CompactPCI connector                        |         |                     |

(cPCI-R3P00 is 50mm deep and cPCI-R3P00T is 80mm deep)

Figure 4-10: cPCI-R3P00(T) RTM Board Layout

\*COM5 is incorrectly labeled COM3 on the A1 vers. PCB silkscreen.

# 4.10 cPCI-R3P00(T) RTM Faceplate

Figure 4-11: cPCI-R3P00(T) RTM Front Panel

# **4.11 Connector Pin Assignments**

### **USB 2.0 Connectors**

| Pin# | Signal Name |

|------|-------------|

| 1    | Vcc         |

| 2    | UV0-        |

| 3    | UV0+        |

| 4    | GND         |

Table 4-2: USB 2.0 Pin Definition

#### **USB 3.0 Connectors**

| Pin# | Signal Name |

|------|-------------|

| 1    | USB3.0_P5VA |

| 2    | USB2_CMAN   |

| 3    | USB2_CMAP   |

| 4    | GND         |

| 5    | USB3A_CMRXN |

| 6    | USB3A_CMRXP |

| 7    | GND         |

| 8    | USB3A_CMTXN |

| 9    | USB3A_CMTXP |

#### **DB-15 VGA Connector**

| Signal Name | Pin# | Pin# | Signal Name |

|-------------|------|------|-------------|

| Red         | 1    | 2    | Green       |

| Blue        | 3    | 4    | N.C.        |

| GND         | 5    | 6    | GND         |

| GND         | 7    | 8    | GND         |

| +5V.        | 9    | 10   | GND         |

| N.C.        | 11   | 12   | CRTDATA     |

| HSYNC       | 13   | 14   | VSYNC       |

| CRTCLK      | 15   |      |             |

Table 4-3: VGA Pin Definition

## **DisplayPort Connectors**

| Pin # | Signal   | Pin# | Signal   |

|-------|----------|------|----------|

| 1     | CN_DP0_P | 2    | Ground   |

| 3     | CN_DP0_N | 4    | CN_DP1_P |

| 5     | Ground   | 6    | CN_DP1_N |

| 7     | CN_DP2_P | 8    | Ground   |

| 9     | CN_DP2_N | 10   | CN_DP3_P |

| 11    | Ground   | 12   | CN_DP3_N |

| 13    | CN_CAD-L | 14   | CN_CEC   |

| 15    | CN_AUX_P | 16   | Ground   |

| 17    | CN_AUX_N | 18   | DDP_HPD  |

| 19    | Ground   | 20   | P3V3     |

**Table 4-4: DisplayPort Pin Definition**

#### **DVI-I Connector**

| Pin# | Signal               | Pin # | Signal                 |

|------|----------------------|-------|------------------------|

| 1    | TMDS Data2-          | 16    | Hot Plug Detect        |

| 2    | TMDS Data2+          | 17    | TMDS Data0-            |

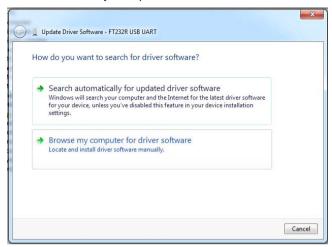

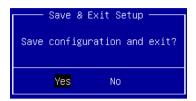

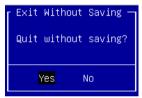

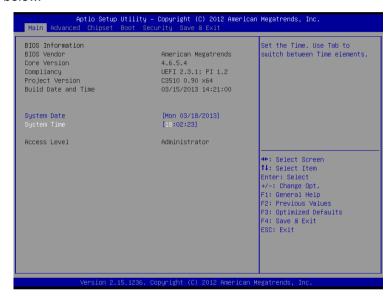

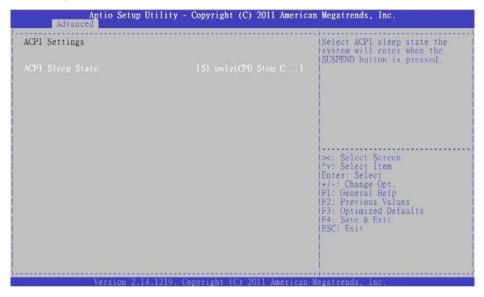

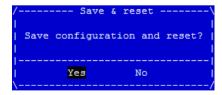

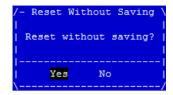

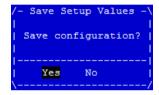

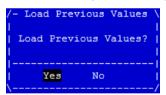

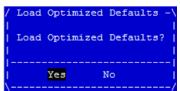

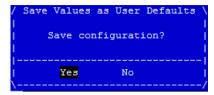

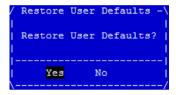

| 3    | GND                  | 18    | TMDSData0+             |