System architecture

**Nicolas Lacaille**

# Presentation

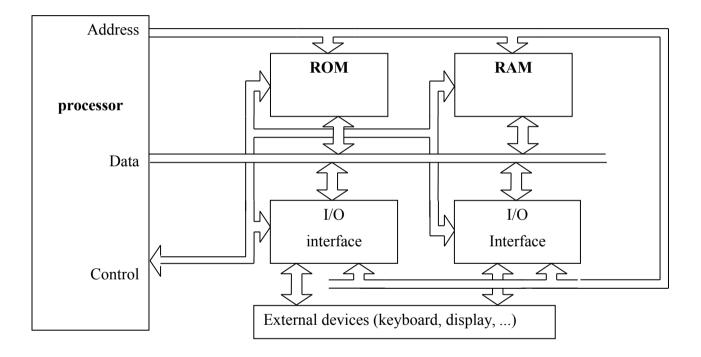

- Computer system is made up of

- > Microprocessor

- ≻ Clock

- > Memory

- For each cycle processor

- > Fetch an instruction from memory (program)

- Execute instruction

- Instruction can do

- Data processing

- Move data from/to memory

- > Branch to an other address in memory

## **External communication**

- Since a microprocessor can only move data to/from memory external communication can only be done with special memory device : interfaces

- To exchange data with external peripherals, processor need interfaces

- Processor side interface are memory device called I/O port or memory mapped registers

- User side interface are specialized device for specific peripheral

- Applications control peripheral through the I/O port of interfaces (exchange data, control the device, knowing the state of the device, ...)

# Simple system

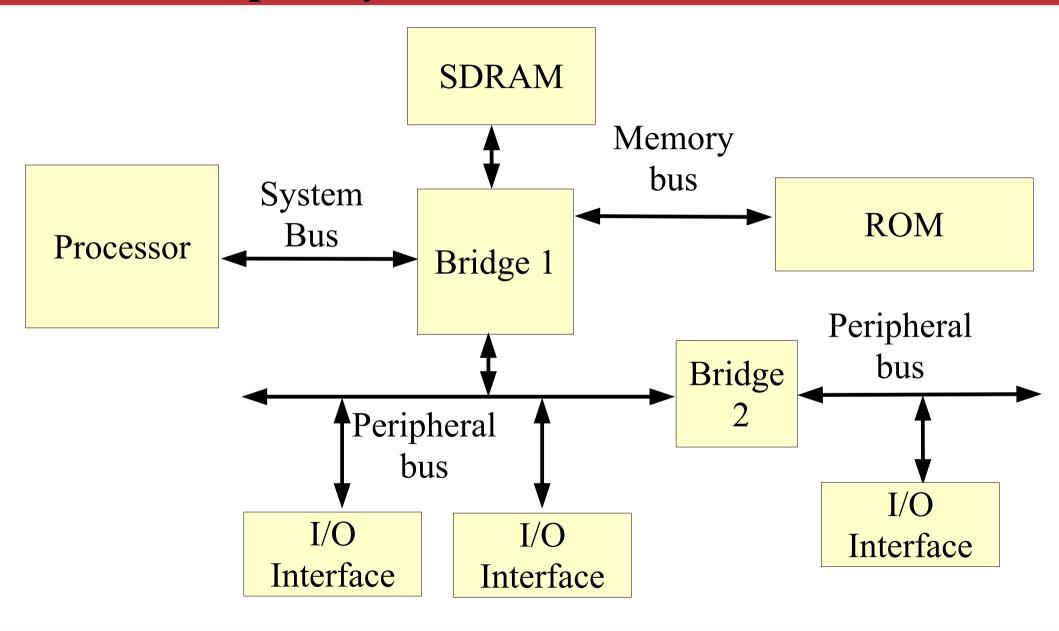

# More complex system

# Example

- An embedded system control an industrial process

- > On one side you have captor connected to input ports

- On the other side you have motor unit connected to output ports

- The application do cycle made up of

- Reading data from the input port (at a known memory address)

- Computing the data

- > Writing new data to the output port

## Memory mapped register

- Input / output port are device register that can be acceded in the physical memory map

- >Memory mapped register

- Memory mapped register, most of time, don't work like standard memory use for variable

- Read only (RO) or Write only (WO) registers

- Variable size (8, 16, 32 bits)

- > Values can change outside the running application

- The correct type must be used in C language

- The 'volatile' term must be used (signals compiler that the variable can be changed outside the program)

### Samples

#### • Using a simple pointer to access the I/O port

volatile unsigned \*port = (unsigned int \*) 0x40000000; /\*for an output port \*/ \*port = value ; /\* for an input port \*/ variable = \*port;

#### C macro

#define port \*(volatile unsigned int \*) 0x4000000

port = value ; /\* or value = port \*/

### Using a macro provided by the kernel

> *HAL\_WRITE\_UINT32(address, value)* or *inl(int)* or ...

• Using structure

struct port {

volatile unsigned config;

volatile unsigned data;

} \*portA;

portA = (struct port \*) 0x40000000; portA->config = value1; value2 = portA->data;

# ARM7TDM microprocessor

## Presentation

- 32 bits general purpose architecture

- 3 stages pipeline RISC architecture

- 32 bits instructions (ARM mode) or 16 bits instructions for code compression (THUMB mode)

- Register to register and load/store architecture

- Single bus for instruction and data

- Low consumption (for embedded system)

## **Execution modes**

- 7 execution modes

- User (usr)

- Supervisor (svc) privilieged for OS

- FIQ (fiq) : Fast Interrupt

- >IRQ (irq) : Normal Interrupt

- System (sys) privileged for OS

- > Abort (abt) addressing's fault

- Undefined : not defined instruction

- Changed are done by software or on special event (exceptions)

- Modes out of usr are privileged modes

# Registers

- 31 general purpose registers

- Only 16 registers can be used in each mode

> r0 → r15

- In all mode

- r15 is program counter (pc)

- r14 is the link register (lr)

- r13 is the stack pointer (sp)

- By convention (AAPCS/EABI)

- > r4 to r11 are variable registers (v1 to v8)

- > r0 to r3 are scratch/argument registers (a1 to a4)

|      |                  |                 | Modes   |           |           |                |  |  |  |  |

|------|------------------|-----------------|---------|-----------|-----------|----------------|--|--|--|--|

|      | Privileged modes |                 |         |           |           |                |  |  |  |  |

|      |                  | Exception modes |         |           |           |                |  |  |  |  |

| User | System           | Supervisor      | Abort   | Undefined | Interrupt | Fast interrupt |  |  |  |  |

| R0   | R0               | R0              | R0      | R0        | R0        | R0             |  |  |  |  |

| R1   | R1               | R1              | R1      | R1        | R1        | R1             |  |  |  |  |

| R2   | R2               | R2              | R2      | R2        | R2        | R2             |  |  |  |  |

| R3   | R3               | R3              | R3      | R3        | R3        | R3             |  |  |  |  |

| R4   | R4               | R4              | R4      | R4        | R4        | R4             |  |  |  |  |

| R5   | R5               | R5              | R5      | R5        | R5        | R5             |  |  |  |  |

| R6   | R6               | R6              | R6      | R6        | R6        | R6             |  |  |  |  |

| R7   | R7               | R7              | R7      | R7        | R7        | R7             |  |  |  |  |

| R8   | R8               | R8              | R8      | R8        | R8        | R8_fiq         |  |  |  |  |

| R9   | R9               | R9              | R9      | R9        | R9        | R9_fiq         |  |  |  |  |

| R10  | R10              | R10             | R10     | R10       | R10       | R10_fiq        |  |  |  |  |

| R11  | R11              | R11             | R11     | R11       | R11       | R11_fiq        |  |  |  |  |

| R12  | R12              | R12             | R12     | R12       | R12       | R12_fiq        |  |  |  |  |

| R13  | R13              | R13_svc         | R13_abt | R13_und   | R13_irq   | R13_fiq        |  |  |  |  |

| R14  | R14              | R14_svc         | R14_abt | R14_und   | R14_irq   | R14_fiq        |  |  |  |  |

| PC   | PC               | PC              | PC      | PC        | PC        | PC             |  |  |  |  |

| CPSR | CPSR | CPSR     | CPSR     | CPSR     | CPSR     | CPSR     |

|------|------|----------|----------|----------|----------|----------|

|      |      | SPSR_svc | SPSR_abt | SPSR_und | SPSR_irq | SPSR_fiq |

indicates that the normal register used by User or System mode has been replaced by an alternative register specific to the exception mode

# PSR

- PSR : program state register

- > cpsr : current program state register

- > spsr : saved program state register (only present in privileged mode)

- CPSR contains

- >ALU flags (C,V,Z, N)

- > I and F flags for allowing interrupts

- Processor mode

### **PSR**

| 31 | 30 | 29 | 28 | 27 | 26 25 | 24 | 23 20    | 19 16   | 15       | 10 | 9 | 8 | 7 | 6 | 5 | 4              | 0 |

|----|----|----|----|----|-------|----|----------|---------|----------|----|---|---|---|---|---|----------------|---|

| N  | z  | С  | v  | Q  | Res   | J  | RESERVED | GE[3:0] | RESERVED |    | E | A | Ι | F | Т | <b>M</b> [4:0] |   |

| Mode       | <i>M[4:0]</i> |

|------------|---------------|

| User       | 10000         |

| FIQ        | 10001         |

| IRQ        | 10010         |

| Supervisor | 10011         |

| Abort      | 10111         |

| Undefined  | 11011         |

| System     | 11111         |

# **3 stages pipeline**

- 3 operations per cycles (instructions parallelism)

- Fetch : instructions fetch

- Decode : operands fetch

- Execute : integer operation and store

- PC points 2 instructions forward the executing one (fetch)

- No branch prediction

## **ARM** instruction set

- 32 bits RISC instructions :

- Register to register or register to immediate operand operations

- > CPSR flags are not changed except if explicitly asked

- Load/store instruction for moving data from register to/from memory (register based addressing)

- Most instructions can be conditionally executed

# **ARM** instructions

| Cond | 0 | 0 | Ι | 0 | )рс | od  | e   | S | Rn      |                          | F   | td |   |   |   |     |        | Oţ                  | ber | an | d 2 |        | Data Processing /<br>PSR Transfer           |

|------|---|---|---|---|-----|-----|-----|---|---------|--------------------------|-----|----|---|---|---|-----|--------|---------------------|-----|----|-----|--------|---------------------------------------------|

| Cond | 0 | 0 | 0 | 0 | 0   | 0   | A   | s | Rd      |                          | F   | ۲n |   |   | F | ١s  |        | 1                   | 0   | 0  | 1   | Rm     | Multiply                                    |

| Cond | 0 | 0 | 0 | 0 | 1   | U   | A   | s | RdHi    |                          | Ro  | Lo |   |   | F | ۲n  |        | 1                   | 0   | 0  | 1   | Rm     | Multiply Long                               |

| Cond | 0 | 0 | 0 | 1 | 0   | В   | 0   | 0 | Rn      |                          | F   | łd |   | 0 | 0 | 0   | 0      | 1                   | 0   | 0  | 1   | Rm     | Single Data Swap                            |

| Cond | 0 | 0 | 0 | 1 | 0   | 0   | 1   | 0 | 1 1 1 1 | 1                        | 1   | 1  | 1 | 1 | 1 | 1   | 1      | 0                   | 0   | 0  | 1   | Rn     | Branch and Exchange                         |

| Cond | 0 | 0 | 0 | Ρ | U   | 0   | w   | L | Rn      |                          | F   | ₹d |   | 0 | 0 | 0   | 0      | 1                   | s   | н  | 1   | Rm     | Halfword Data Transfer:<br>register offset  |

| Cond | 0 | 0 | 0 | Ρ | U   | 1   | w   | L | Rn      |                          | F   | ld |   |   | С | ffs | et     | 1                   | s   | Н  | 1   | Offset | Halfword Data Transfer:<br>immediate offset |

| Cond | 0 | 1 | I | Ρ | U   | В   | w   | L | Rn      |                          | F   | łd |   |   |   |     |        |                     | Off | se | t   |        | Single Data Transfer                        |

| Cond | 0 | 1 | 1 |   |     |     |     |   |         | 1                        |     |    |   |   |   |     |        | Undefined           |     |    |     |        |                                             |

| Cond | 1 | 0 | 0 | Ρ | U   | s   | W   | L | Rn      | Rn Register List         |     |    |   |   |   |     |        | Block Data Transfer |     |    |     |        |                                             |

| Cond | 1 | 0 | 1 | L |     |     |     |   |         | Offset                   |     |    |   |   |   |     | Branch |                     |     |    |     |        |                                             |

| Cond | 1 | 1 | 0 | Ρ | U   | N   | w   | L | Rn      |                          | С   | Rd |   |   | C | P#  |        |                     |     |    | Off | íset   | Coprocessor Data<br>Transfer                |

| Cond | 1 | 1 | 1 | 0 | C   | P   | Op  | c | CRn     |                          | CRd |    |   |   | C | P#  |        |                     | CF  | )  | 0   | CRm    | Coprocessor Data<br>Operation               |

| Cond | 1 | 1 | 1 | 0 | CF  | ° C | )pc | L | CRn     |                          | F   | λd |   |   | C | P#  |        |                     | CF  | )  | 1   | CRm    | Coprocessor Register<br>Transfer            |

| Cond | 1 | 1 | 1 | 1 |     |     |     |   |         | Ignored by processor Sof |     |    |   |   |   |     |        | Software Interrupt  |     |    |     |        |                                             |

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

*>*...

## **THUMB** instruction set

- I6 bits : instructions are more constrained

- > Only 8 registers are code reachable

- Shortest immediate operands

- Flags are always updated (no more explicitly)

- Only branch instruction can be conditional

## **THUMB** instruction

|    | 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8    | 7         | 6   | 543      | 2 1 0 | _                                          |

|----|----|----|----|----|----|----|-----|------|-----------|-----|----------|-------|--------------------------------------------|

| 1  | 0  | 0  | 0  | С  | )p |    | 0   | ffse | t5        |     | Rs       | Rd    | Move shifted register                      |

| 2  | 0  | 0  | 0  | 1  | 1  | Т  | Op  | Rn   | /offs     | et3 | Rs       | Rd    | Add/subtract                               |

| 3  | 0  | 0  | 1  | С  | )p |    | Rd  |      |           |     | Offset8  |       | Move/compare/add<br>/subtract immediate    |

| 4  | 0  | 1  | 0  | 0  | 0  | 0  |     | С    | )p        |     | Rs       | Rd    | ALU operations                             |

| 5  | 0  | 1  | 0  | 0  | 0  | 1  | С   | )p   | H1        | H2  | Rs/Hs    | Rd/Hd | Hi register operations<br>/branch exchange |

| 6  | 0  | 1  | 0  | 0  | 1  |    | Rd  |      |           |     | Word8    |       | PC-relative load                           |

| 7  | 0  | 1  | 0  | 1  | L  | в  | 0   |      | Ro        |     | Rb       | Rd    | Load/store with register<br>offset         |

| 8  | 0  | 1  | 0  | 1  | н  | s  | 1   |      | Ro        |     | Rb       | Rd    | Load/store sign-extended<br>byte/halfword  |

| 9  | 0  | 1  | 1  | в  | L  |    | 0   | ffse | et5 Rb Rd |     |          |       | Load/store with immediate<br>offset        |

| 10 | 1  | 0  | 0  | 0  | L  |    | O   | ffse | et5 Rb Rd |     |          |       | Load/store halfword                        |

| 11 | 1  | 0  | 0  | 1  | L  |    | Rd  |      |           |     | Word8    |       | SP-relative load/store                     |

| 12 | 1  | 0  | 1  | 0  | SP |    | Rd  |      |           |     | Word8    |       | Load address                               |

| 13 | 1  | 0  | 1  | 1  | 0  | 0  | 0   | 0    | s         |     | SWor     | d7    | Add offset to stack pointer                |

| 14 | 1  | 0  | 1  | 1  | L  | 1  | 0   | R    |           |     | Rlist    |       | Push/pop registers                         |

| 15 | 1  | 1  | 0  | 0  | L  |    | Rb  |      |           |     | Rlist    |       | Multiple load/store                        |

| 16 | 1  | 1  | 0  | 1  |    | Co | ond |      |           |     | Soffset8 | }     | Conditional branch                         |

| 17 | 1  | 1  | 0  | 1  | 1  | 1  | 1   | 1    |           |     | Value8   |       | Software Interrupt                         |

| 18 | 1  | 1  | 1  | 0  | 0  |    | I   | I    | I         | Of  | fset11   |       | Unconditional branch                       |

| 19 | 1  | 1  | 1  | 1  | н  |    |     |      |           | C   | Offset   |       | Long branch with link                      |

|    | 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8    | 7         | 6   | 543      | 2 1 0 | 1                                          |

# **ARM7 exceptions**

| Exception                   | Description                                              |

|-----------------------------|----------------------------------------------------------|

| Reset                       | Reset pin activated                                      |

| Undefined<br>Instruction    | Special instruction code                                 |

| Software Interrupt<br>(SWI) | Instruction code used to generate exception, system call |

| Prefetch Abort              | Memory access violation during fetch                     |

| Data Abort                  | Data memory access violation                             |

| IRQ                         | IRQ pin activated                                        |

| FIQ                         | FIQ pin activated                                        |

# Principe

- When an exception occurs

- PC-4 is saved in lr\_mode

- CPSR is saved in SPSR\_mode

- > CPSR is changed

- Mode becomes : svc, irq, fiq, data or prefetch abort depending the exception

- I bit is set (IRQ not allowed) for all exceptions

- F bit is set if the exception is a FIQ or reset

- > PC is loaded with exception vector

- Address between 0x0 (reset) to 0x1C (FIQ)

# **Exception vectors**

| address | Exception                | Processor's mode | Priority |

|---------|--------------------------|------------------|----------|

|         |                          |                  |          |

| 0x00    | Reset                    | Supervisor (svc) | 1        |

| 0x04    | Undefined Instruction    | Undef            | 6        |

| 0x08    | Software Interrupt (SWI) | Supervisor (svc) | 6        |

| 0x0C    | Prefetch Abort           | Abort            | 5        |

| 0x10    | Data Abort               | Abort            | 2        |

| 0x14    | Reserved                 |                  |          |

| 0x18    | IRQ (Interrupt)          | irq              | 4        |

| 0x1C    | FIQ (Fast Interrpt)      | fiq              | 3        |

• For arm processor each mode has their own stack pointer

- Allow the exception handler to save data in its own memory area without corrupting the application data

- During the execution of the exception handler no interrupt are allowed

- No peripheral or system services can be serviced without re-enable interrupt

- Exception handler are architecture specific and differs from standard function

- Exception routine need special entry and exit code that can be written in asm or provided by a library

## **Code example**

; Exception Vectors

; Mapped to Address 0.

Absolute addressing mode must be used.

; Dummy Handlers are implemented as infinite loops which can be modified.

| Vectors   | LDR<br>LDR<br>LDR<br>LDR<br>NOP<br>LDR<br>LDR | PC, Reset_A<br>PC, Undef_<br>PC, SWI_A<br>PC, PAbt_A<br>PC, DAbt_A<br>PC, IRQ_A<br>PC, FIQ_A | Addr<br>ddr<br>ddr<br>Addr<br>; Reserved Vector<br>ddr |

|-----------|-----------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Reset Add | ſ                                             | DCD                                                                                          | Reset Handler                                          |

| Undef_Add | r                                             | DCD                                                                                          | Undef_Handler                                          |

| SWI_Addr  |                                               | DCD                                                                                          | SWI_Handler                                            |

| PAbt_Addr |                                               | DCD                                                                                          | PAbt_Handler                                           |

| DAbt_Add  | [                                             | DCD                                                                                          | DAbt_Handler                                           |

| DCD 0 : Reserved Address | <br><u> </u> |                    |

|--------------------------|--------------|--------------------|

| , ,                      | DCD 0        | ; Reserved Address |

IRQ Addr DCD DCD

FIQ Addr

IRQ Handler

FIQ Handler

#### I/O interface -25

# **ARM** architecture evolution

ARM7TDMI ARM922T

Thumb instruction set

ARM926EJ-S ARM946E-S ARM966E-S

Improved ARM/Thumb Interworking DSP instructions Extensions:

Jazelle (5TEJ)

ARM1136JF-S ARM1176JZF-S ARM11 MPCore

SIMD Instructions Unaligned data support Extensions: Thumb-2 (6T2)

TrustZone (6Z)

Multicore (6K)

Cortex-A8/R4/M3/M1 Thumb-2 Extensions: v7A (applications) – NEON

The (upplications) Theory

v7R (real time) – HW Divide

V7M (microcontroller) – HW Divide and Thumb-2 only

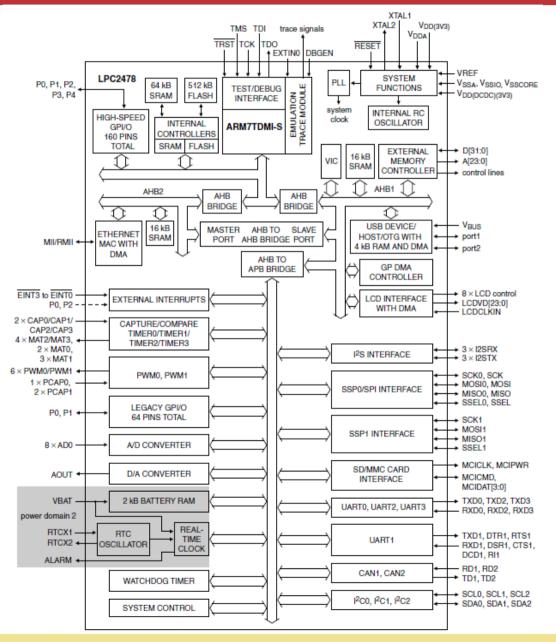

# NXP - LPC2478

**Nicolas Lacaille**

# **Présentation**

- Microcontroler from nxp with ARM7TDMI-S core

- Running up to 80MHz

- 64 kbyte of SRAM

- 518 kbyte of flash program memory

- External memory interface

- An external memory controller is present to connect static or dynamic RAM or FLASH

- Peripherals

- >AHB peripherals (VIC, ethernet, usb, memory, FastGPIO)

- > APB peripherals (sérial, Timer, PWM, ADC, RT clock, ...)

# **Block diagram**

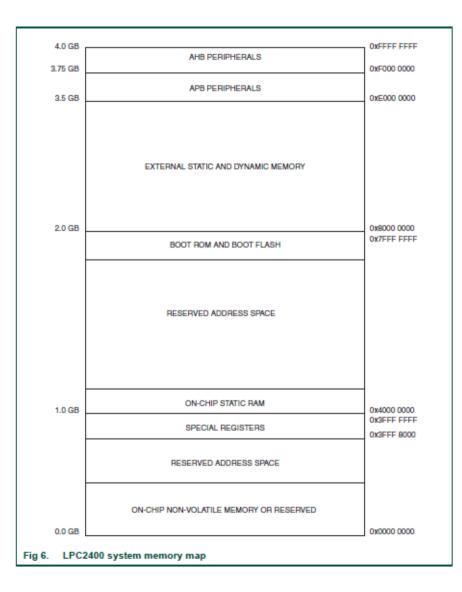

# Memory map

# Memory map

| Address range                 | General use          | Address range details and descrip  | tion                  |

|-------------------------------|----------------------|------------------------------------|-----------------------|

| 0x0000 0000 to                | On-chip non-volatile | 0x0000 0000 - 0x0007 FFFF          | Flash Memory (512 kB) |

| 0x3FFF FFFF                   | memory and Fast I/O  | 0x3FFF C000 - 0x3FFF FFFF          | Fast GPIO registers   |

| 0x4000 0000 to                | On-chip RAM          | 0x4000 0000 - 0x4000 FFFF          | RAM (64 kB)           |

| 0x7FFF FFFF                   |                      | 0x7FE0 0000 - 0x7FE0 3FFF          | Ethernet RAM (16 kB)  |

|                               |                      | 0x7FD0 0000 - 0x7FD0 3FFF          | USB RAM (16 kB)       |

| 0x8000 0000 to                | Off-Chip Memory      | Four static memory banks, 16 MB ea | ch                    |

| 0xDFFF FFFF                   |                      | 0x8000 0000 - 0x80FF FFFF          | Static memory bank 0  |

|                               |                      | 0x8100 0000 - 0x81FF FFFF          | Static memory bank 1  |

|                               |                      | 0x8200 0000 - 0x82FF FFFF          | Static memory bank 2  |

|                               |                      | 0x8300 0000 - 0x83FF FFFF          | Static memory bank 3  |

|                               |                      | Four dynamic memory banks, 256 Mi  | B each                |

|                               |                      | 0xA000 0000 - 0xAFFF FFFF          | Dynamic memory bank 0 |

|                               |                      | 0xB000 0000 - 0xBFFF FFFF          | Dynamic memory bank 1 |

|                               |                      | 0xC000 0000 - 0xCFFF FFFF          | Dynamic memory bank 2 |

|                               |                      | 0xD000 0000 - 0xDFFF FFFF          | Dynamic memory bank 3 |

| 0xE000 0000 to<br>0xEFFF FFFF | APB Peripherals      | 36 peripheral blocks, 16 kB each   |                       |

| 0xF000 0000 to<br>0xFFFF FFFF | AHB peripherals      |                                    |                       |

# Remapping

- ARM exception vectors are at address  $0x0 \rightarrow 0x1C$

- Remapping on LPC2478 consists in changing some memory address to map vector address (64 byte from 0x0 to 0x3F)

- Modes :

| Activation                                | Usage                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Hardware<br>activation by<br>any Reset    | The Boot Loader <b>always</b> executes after any reset. The Boot ROM interrupt vectors are mapped to the bottom of memory to allow handling exceptions and using interrupts during the Boot Loading process. A sector of the flash memory (the Boot flash) is available to hold part of the Boot Code. |  |  |  |  |  |  |

| Software<br>activation by<br>Boot code    | For LPC2400 parts with flash only. Activated by the Boot Loader when<br>a valid User Program Signature is recognized in memory and Boot<br>Loader operation is not forced. Interrupt vectors are not re-mapped<br>and are found in the bottom of the flash memory.                                     |  |  |  |  |  |  |

| Software<br>activation by<br>User program | Activated by a User Program as desired. Interrupt vectors are<br>re-mapped to the bottom of the Static RAM.                                                                                                                                                                                            |  |  |  |  |  |  |

| Software<br>activation by<br>user code    | For LPC2400 parts with flash. Interrupt vectors are re-mapped to external memory bank 0.[1]                                                                                                                                                                                                            |  |  |  |  |  |  |

| Software<br>activation by<br>boot code    | For flashless parts LPC2420/60/70 only. Interrupt vectors are re-mapped to external memory bank 0.[2]                                                                                                                                                                                                  |  |  |  |  |  |  |

|                                           | Hardware<br>activation by<br>any Reset<br>Software<br>activation by<br>Boot code<br>Software<br>activation by<br>User program<br>Software<br>activation by<br>user code<br>Software<br>activation by<br>user code                                                                                      |  |  |  |  |  |  |

# **MEMMAP Register**

| Table 20.      |       | Memory mapping control registers                                                                                                             |                                                                                          |                                                                                                            |             |           |         |                |  |  |

|----------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------|-----------|---------|----------------|--|--|

| Name<br>MEMMAP |       | DescriptionAccessReset<br>valueAddre<br>valueMemory mapping control. Selects whether the<br>ARM interrupt vectors are read from the Boot<br> |                                                                                          |                                                                                                            |             |           | Addre   | ss             |  |  |

|                |       |                                                                                                                                              |                                                                                          |                                                                                                            |             |           | F C040  |                |  |  |

| Table          | e 21. |                                                                                                                                              | mory N<br>scriptio                                                                       | lapping control register (MEMMAP - ac                                                                      | ddress 0xE  | 01F C04   | 40) bit |                |  |  |

| Bit            | Symb  | ool                                                                                                                                          | Value                                                                                    | Description                                                                                                |             |           |         | Reset<br>value |  |  |

| 1:0            | MAP   |                                                                                                                                              | 00                                                                                       | Boot Loader Mode. Interrupt vectors are                                                                    | e re-mappe  | d to Boot | ROM.    | 00             |  |  |

|                |       |                                                                                                                                              | 01                                                                                       | User Flash Mode. Interrupt vectors are not re-mapped and reside in Flash.                                  |             |           |         |                |  |  |

|                |       |                                                                                                                                              |                                                                                          | Remark: This mode is for parts with flash only. Value 01 is<br>reserved for flashless parts LPC2420/60/70. |             |           |         |                |  |  |

|                |       |                                                                                                                                              | 10                                                                                       | User RAM Mode. Interrupt vectors are r                                                                     | re-mapped t | to Static | RAM.    | -              |  |  |

|                |       |                                                                                                                                              | 11                                                                                       | User External Memory Mode. Interrupt v<br>external memory bank 0.                                          | vectors are | re-mapp   | ed to   | _              |  |  |

|                |       |                                                                                                                                              | Warning: Improper setting of this value may result in incorrect operation of the device. |                                                                                                            |             |           |         |                |  |  |

| 7:2            | -     |                                                                                                                                              | -                                                                                        | Reserved, user software should not writ<br>The value read from a reserved bit is no                        |             | eserved   | bits.   | NA             |  |  |

## Flash bootloader

- Provide initial operation after reset and means to programs user flash memory

- At reset, with certain conditions an ISP handler is invoked (In System Programming)

- ➢ P2.10 sampled low

- Watchdog flag not set

- If P2.10 is sampled High, the boot loader search for a valid user program in flash

- A checksum of exception vector is done (signature in 0x14 added with the sum of other exception vectors must be 0)

- > If checksum is valid the user program is launch otherwise no

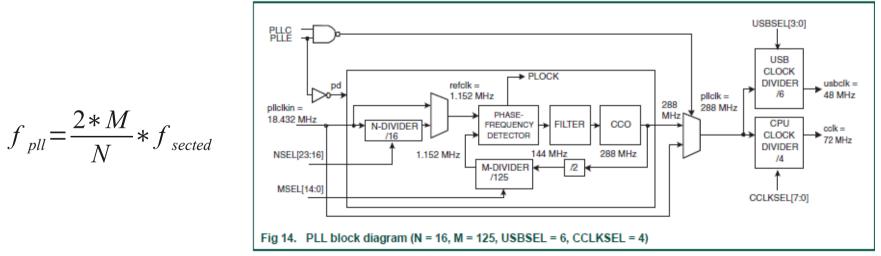

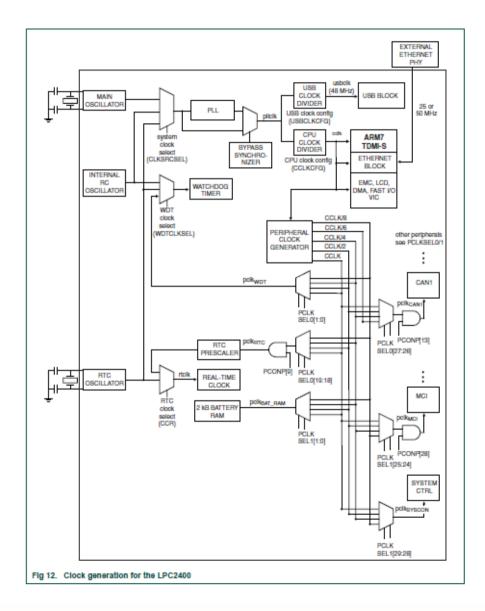

# Clock

- 3 oscillators

- Main oscillator : 1 to 24 MHz (12MHz)

- Internal RC oscillator (4MHz)

- RTC oscillator

- All oscillator can drive a PLL and subsequently the CPU

- PLL allow to choose the CPU clock frequency from the clock source

## Clock

# **Selecting clock**

- At startup, the internal RC oscillator is used and PLL is bypassed

- User boot can activate the main oscillator (SCS : system Control ans Status Register)

- When main oscillator is stabilized user program can use it as clock source for the PLL (CLKSRCSEL register) and activate it with specific value (PLLCFG to choose M and N)

- CPU (CCLKCFG) and USB (USBCLKCFG) divider are set

- Peripheral clocks are set (PCLKSEL0 and 1)

# **Example : ConfigurePLL() (framework.c)**

void ConfigurePLL ( void ) {

unsigned int MValue, NValue;

| <pre>if ( PLLSTAT &amp; (1 &lt;&lt; 25) ){     PLLCON = 1;     PLLFEED = 0xaa;     PLLFEED = 0x55;</pre> | /* Enable PLL, disconnected */                               |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| <pre>} PLLCON = 0; PLLFEED = 0xaa; PLLFEED = 0x55;</pre>                                                 | /* Disable PLL, disconnected */                              |

| SCS  = 0x20;<br>while( !(SCS & 0x40) );                                                                  | /* Enable main OSC */<br>/* Wait until main OSC is usable */ |

| CLKSRCSEL = 0x1;                                                                                         | /* select main OSC, 12MHz, as the PLL clock source */        |

| PLLCFG = PLL_MValue   (PLL_NVa<br>PLLFEED = 0xaa;<br>PLLFEED = 0x55;                                     | alue << 16);                                                 |

| PLLCON = 1;<br>PLLFEED = 0xaa;<br>PLLFEED = 0x55;                                                        | /* Enable PLL, disconnected */                               |

| CCLKCFG = CCLKDivValue;                                                                                  | /* Set clock divider */                                      |

| <pre>#if USE_USB<br/>USBCLKCFG = USBCLKDivValue;<br/>#endif</pre>                                        | /* usbclk = 288 MHz/6 = 48 MHz */                            |

| while ( ((PLLSTAT & (1 << 26))                                                                           | == 0) ); /* Check lock bit status */                         |

| MValue = PLLSTAT & 0x00007FF<br>NValue = (PLLSTAT & 0x00FF000<br>while ((MValue != PLL_MValue)           | 00) >> 16;                                                   |

| PLLCON = 3;<br>PLLFEED = 0xaa;<br>PLLFEED = 0x55;<br>PLLFEED = 0x55;                                     | /* enable and connect */                                     |

| while ( ((PLLSTAT & (1 << 25)) = }                                                                       | == 0) ); /* Check connect bit status */                      |

|                                                                                                          |                                                              |

# **Peripheral clocks**

Table 57. Peripheral Clock Selection register 1 (PCLKSEL1 - address 0xE01F C1AC) bit description

| Bit   | Symbol       | Description                                               | Reset<br>value |

|-------|--------------|-----------------------------------------------------------|----------------|

| 1:0   | PCLK_BAT_RAM | Peripheral clock selection for the battery supported RAM. | 00             |

| 3:2   | PCLK_GPIO    | Peripheral clock selection for GPIOs.                     | 00             |

| 5:4   | PCLK_PCB     | Peripheral clock selection for the Pin Connect block.     | 00             |

| 7:6   | PCLK_I2C1    | Peripheral clock selection for I2C1.                      | 00             |

| 9:8   | -            | Unused, always read as 0.                                 | 00             |

| 11:10 | PCLK_SSP0    | Peripheral clock selection for SSP0.                      | 00             |

| 13:12 | PCLK_TIMER2  | Peripheral clock selection for TIMER2.                    | 00             |

| 15:14 | PCLK_TIMER3  | Peripheral clock selection for TIMER3.                    | 00             |

| 17:16 | PCLK_UART2   | Peripheral clock selection for UART2.                     | 00             |

| 19:18 | PCLK_UART3   | Peripheral clock selection for UART3.                     | 00             |

| 21:20 | PCLK_I2C2    | Peripheral clock selection for I2C2.                      | 00             |

| 23:22 | PCLK_I2S     | Peripheral clock selection for I2S.                       | 00             |

| 25:24 | PCLK_MCI     | Peripheral clock selection for MCI.                       | 00             |

| 27:26 | -            | Unused, always read as 0.                                 | 00             |

| 29:28 | PCLK_SYSCON  | Peripheral clock selection for the System Control block.  | 00             |

| 31:30 | -            | Unused, always read as 0.                                 | 00             |

#### Table 58. Peripheral Clock Selection register bit values

| PCLKSEL0 and PCLKSEL1<br>individual peripheral's clock<br>select options | Function                                                                                                                                | Reset<br>value |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 00                                                                       | PCLK_xyz = CCLK/4                                                                                                                       | 00             |

| 01                                                                       | PCLK_xyz = CCLK <sup>[1]</sup>                                                                                                          |                |

| 10                                                                       | PCLK_xyz = CCLK/2                                                                                                                       |                |

| 11                                                                       | Peripheral's clock is selected to PCLK_xyz = CCLK/8<br>except for CAN1, CAN2, and CAN filtering when '11'<br>selects PCLK_xyz = CCLK/6. |                |

For PCLK\_RTC only, the value '01' is illegal. Do not write '01' to the PCLK\_RTC. Attempting to write '01' results in the previous value being unchanged.

### PCLKSEL0 PCLKSEL1

# Power

- 4 special modes of power reduction :

- > Idle

- Clocks core stopped

- Resume on reset or interrupt

- > Sleep

- Main oscillator powered down and all clock stopped

- Wake up on reset or interrupt

- PLL must be reconfigured

- Power-down

- All clock powered down

- Flash is powered down (unlike sleep)

- Deep power-down

- Power regulator turned off (register values are not retained)

# **Peripheral power control**

• Each peripheral can be turned off (clock disable)

Control of power peripheral done through PCONP reg.

| Bit   | Symbol  | Description                                                                                                        | Reset<br>value |

|-------|---------|--------------------------------------------------------------------------------------------------------------------|----------------|

| 0     | -       | Unused, always 0                                                                                                   | 0              |

| 1     | PCTIM0  | Timer/Counter 0 power/clock control bit.                                                                           | 1              |

| 2     | PCTIM1  | Timer/Counter 1 power/clock control bit.                                                                           | 1              |

| 3     | PCUART0 | UART0 power/clock control bit.                                                                                     | 1              |

| 4     | PCUART1 | UART1 power/clock control bit.                                                                                     | 1              |

| 5     | PCPWM0  | PWM0 power/clock control bit.                                                                                      | 1              |

| 6     | PCPWM1  | PWM1 power/clock control bit.                                                                                      | 1              |

| 7     | PCI2C0  | The I <sup>2</sup> C0 interface power/clock control bit.                                                           | 1              |

| 8     | PCSPI   | The SPI interface power/clock control bit.                                                                         | 1              |

| 9     | PCRTC   | The RTC power/clock control bit.                                                                                   | 1              |

| 10    | PCSSP1  | The SSP1 interface power/clock control bit.                                                                        | 1              |

| 11    | PCEMC   | External Memory Controller                                                                                         | 1              |

| 12    | PCAD    | A/D converter (ADC) power/clock control bit.                                                                       | 0              |

|       |         | Note: Clear the PDN bit in the AD0CR before clearing this bit, and set this bit before setting PDN.                |                |

| 13    | PCCAN1  | CAN Controller 1 power/clock control bit.                                                                          | 0              |

| 14    | PCCAN2  | CAN Controller 2 power/clock control bit.                                                                          | 0              |

| 18:15 | -       | Reserved, user software should not write ones to reserved bits. The value read from a reserved bit is not defined. |                |

| 19    | PCI2C1  | The I <sup>2</sup> C1 interface power/clock control bit.                                                           | 1              |

| 20    | PCLCD   | LCD controller power control bit.                                                                                  | 0              |

| 21    | PCSSP0  | The SSP0 interface power/clock control bit.                                                                        | 1              |

| Bit | Symbol  | Description                                           | Reset<br>value |

|-----|---------|-------------------------------------------------------|----------------|

| 22  | PCTIM2  | Timer 2 power/clock control bit.                      | 0              |

| 23  | PCTIM3  | Timer 3 power/clock control bit.                      | 0              |

| 24  | PCUART2 | UART 2 power/clock control bit.                       | 0              |

| 25  | PCUART3 | UART 3 power/clock control bit.                       | 0              |

| 26  | PCI2C2  | I <sup>2</sup> S interface 2 power/clock control bit. | 1              |

| 27  | PCI2S   | I <sup>2</sup> S interface power/clock control bit.   | 0              |

| 28  | PCSDC   | SD card interface power/clock control bit.            | 0              |

| 29  | PCGPDMA | GP DMA function power/clock control bit.              | 0              |

| 30  | PCENET  | Ethernet block power/clock control bit.               | 0              |

| 31  | PCUSB   | USB interface power/clock control bit.                | 0              |

1 : enable

0 : disable

### If peripheral is disable, read or write register are not valid

# **Peripheral power control**

• Each peripheral can be turned off (clock disable)

Control of power peripheral done through PCONP reg.

| Bit   | Symbol  | Description                                                                                                        | Reset<br>value |

|-------|---------|--------------------------------------------------------------------------------------------------------------------|----------------|

| 0     | -       | Unused, always 0                                                                                                   | 0              |

| 1     | PCTIM0  | Timer/Counter 0 power/clock control bit.                                                                           | 1              |

| 2     | PCTIM1  | Timer/Counter 1 power/clock control bit.                                                                           | 1              |

| 3     | PCUART0 | UART0 power/clock control bit.                                                                                     | 1              |

| 4     | PCUART1 | UART1 power/clock control bit.                                                                                     | 1              |

| 5     | PCPWM0  | PWM0 power/clock control bit.                                                                                      | 1              |

| 6     | PCPWM1  | PWM1 power/clock control bit.                                                                                      | 1              |

| 7     | PCI2C0  | The I <sup>2</sup> C0 interface power/clock control bit.                                                           | 1              |

| 8     | PCSPI   | The SPI interface power/clock control bit.                                                                         | 1              |

| 9     | PCRTC   | The RTC power/clock control bit.                                                                                   | 1              |

| 10    | PCSSP1  | The SSP1 interface power/clock control bit.                                                                        | 1              |

| 11    | PCEMC   | External Memory Controller                                                                                         | 1              |

| 12    | PCAD    | A/D converter (ADC) power/clock control bit.                                                                       | 0              |

|       |         | Note: Clear the PDN bit in the AD0CR before clearing this bit, and set this bit before setting PDN.                |                |

| 13    | PCCAN1  | CAN Controller 1 power/clock control bit.                                                                          | 0              |

| 14    | PCCAN2  | CAN Controller 2 power/clock control bit.                                                                          | 0              |

| 18:15 | -       | Reserved, user software should not write ones to reserved bits. The value read from a reserved bit is not defined. |                |

| 19    | PCI2C1  | The I <sup>2</sup> C1 interface power/clock control bit.                                                           | 1              |

| 20    | PCLCD   | LCD controller power control bit.                                                                                  | 0              |

| 21    | PCSSP0  | The SSP0 interface power/clock control bit.                                                                        | 1              |

| Bit | Symbol  | Description                                           | Reset<br>value |

|-----|---------|-------------------------------------------------------|----------------|

| 22  | PCTIM2  | Timer 2 power/clock control bit.                      | 0              |

| 23  | PCTIM3  | Timer 3 power/clock control bit.                      | 0              |

| 24  | PCUART2 | UART 2 power/clock control bit.                       | 0              |

| 25  | PCUART3 | UART 3 power/clock control bit.                       | 0              |

| 26  | PCI2C2  | I <sup>2</sup> S interface 2 power/clock control bit. | 1              |

| 27  | PCI2S   | I <sup>2</sup> S interface power/clock control bit.   | 0              |

| 28  | PCSDC   | SD card interface power/clock control bit.            | 0              |

| 29  | PCGPDMA | GP DMA function power/clock control bit.              | 0              |

| 30  | PCENET  | Ethernet block power/clock control bit.               | 0              |

| 31  | PCUSB   | USB interface power/clock control bit.                | 0              |

1 : enable

0 : disable

### If peripheral is disable, read or write register are not valid

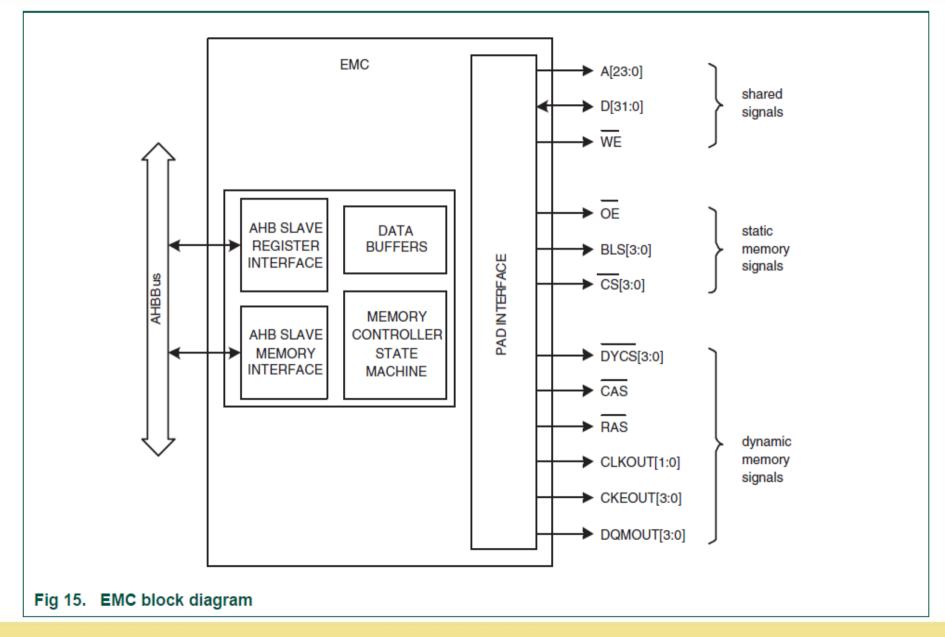

# **External Memory Controller**

- Dynamic memory interface support including Single Data Rate SDRAM.

- Asynchronous static memory device support including RAM, ROM, and Flash, with or without asynchronous page mode.

- Low transaction latency.

- · Read and write buffers to reduce latency and to improve performance.

- 8 bit, 16 bit, and 32 bit wide static memory support.

- 16 bit and 32 bit wide chip select SDRAM memory support.

- Static memory features include:

- Asynchronous page mode read

- Programmable wait states

- Bus turnaround delay

- Output enable and write enable delays

- Extended wait

- Four chip selects for synchronous memory and four chip selects for static memory devices.

- Power-saving modes dynamically control CKE and CLKOUT to SDRAMs.

- · Dynamic memory self-refresh mode controlled by software.

- Controller supports 2 kbit, 4 kbit, and 8 kbit row address synchronous memory parts. That is typical 512 MB, 256 MB, and 128 MB parts, with 4, 8, 16, or 32 data bits per device.

- · Separate reset domains allow the for auto-refresh through a chip reset if desired.

Note: Synchronous static memory devices (synchronous burst mode) are not supported.

# EMC

# LPC2478 board : external memory

- External NOR FLASH (32 MBit = 4 MByte in size) addressed by CS0 (address range: 0x8000 0000 – 0x80FF FFFF). Accessed via 16-bit databus.

- External NAND FLASH (1 GBit = 128 MByte in size) addressed by CS1 (address range: 0x8100 0000 – 0x81FF FFFF). Accessed via 8-bit databus.

- External SDRAM (256 MBit = 32 MByte in size) addressed by DYCS0 (address range: 0xA000 0000 – 0xA1FF FFFF). Accessed via 32-bit databus

# **Memory Accelerator Module**

- Small SRAM memory between flash and core

- Allow fast instruction access

- Direct access to flash is limited to 20MHz (50ns access time)

- Load 4 arm instructions from flash

- > 2 buffers are alternatively used to maintain prefetch rate

- Include a branch trail buffer for loops

```

/* Set memory accelerater module*/

MAMCR = 0;

#if Fcclk < 2000000

MAMTIM = 1;

#else

#if Fcclk < 40000000

MAMTIM = 2;

#else

MAMTIM = 3;

#endif

#endif

#endif

MAMCR = MAM SETTING; //0=disabled, 1=partly enabled (enabled for code prefetch, but not for data), 2=fully enabled

```

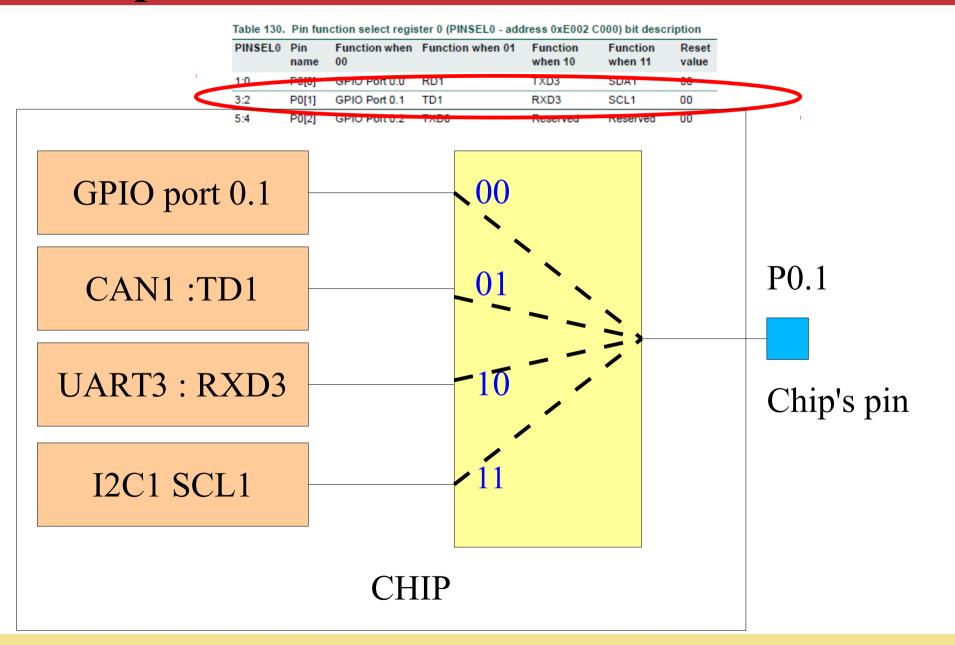

# PIN

To reduce number of pins on chip, pins are multiplexed

Different functions can use the pins

Registers which are controlling pin function are

PINSEL (PINSEL0 to PINSEL11)

PINMODE (PINMODE0 to PINMODE9)

Table 130. Pin function select register 0 (PINSEL0 - address 0xE002 C000) bit description

| PINSEL0 | Pin<br>name | Function when 00 | Function when 01 | Function<br>when 10 | Function<br>when 11 | Reset<br>value |

|---------|-------------|------------------|------------------|---------------------|---------------------|----------------|

| 1:0     | P0[0]       | GPIO Port 0.0    | RD1              | TXD3                | SDA1                | 00             |

| 3:2     | P0[1]       | GPIO Port 0.1    | TD1              | RXD3                | SCL1                | 00             |

| 5:4     | P0[2]       | GPIO Port 0.2    | TXD0             | Reserved            | Reserved            | 00             |

PINSEL controls pin multiplexer

Table 146. Pin Mode select register 0 (PINMODE0 - address 0xE002 C040) bit description

| PINMODE0 | Symbol    | Value | Description                                         | Reset<br>value |

|----------|-----------|-------|-----------------------------------------------------|----------------|

| 1:0      | P0.00MODE |       | PORT0 pin 0 on-chip pull-up/down resistor control.  | 00             |

|          |           | 00    | P0.00 pin has a pull-up resistor enabled.           | -              |

|          |           | 01    | Reserved. This value should not be used.            |                |

|          |           | 10    | P0.00 pin has neither pull-up nor pull-down.        |                |

|          |           | 11    | P0.00 has a pull-down resistor enabled.             | _              |

|          |           |       |                                                     |                |

| 31:30    | P0.15MODE |       | PORT0 pin 15 on-chip pull-up/down resistor control. | 00             |

### PINMODE define electrical pin connexion

# Exemple

# **GPIO : General Purpose I/O**

- 5 general purpose 32 bits port

- GPIO controller are located on the local bus for fast controlling

- Port0 and Port1 can also be controlled by legacy control register on APB bus (slow)

- Port0 and Port2 can generate interrupts on individual change of individual pin

- Each individual pin can be configured as input or out put (FIOxDIR)

- Each individual pin can be masked (FIOxMASK) for reading and writing (read 0 and no effects on write)

# Registers

| Table 159.      | Summary of GPIO registers (local bus accessible registers                                                                                                                                                                                                                                                                                                                                                         | - enhanc | ed GPIO | features)                                                                                                                      |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|--------------------------------------------------------------------------------------------------------------------------------|

| Generic<br>Name | Description                                                                                                                                                                                                                                                                                                                                                                                                       | Access   |         | PORTn Register<br>Address & Name                                                                                               |

| FIODIR          | Fast GPIO Port Direction control register. This register<br>individually controls the direction of each port pin.                                                                                                                                                                                                                                                                                                 | R/W      | 0x0     | FIO0DIR - 0x3FFF C000<br>FIO1DIR - 0x3FFF C020<br>FIO2DIR - 0x3FFF C040<br>FIO3DIR - 0x3FFF C060<br>FIO4DIR - 0x3FFF C080      |

| FIOMASK         | Fast Mask register for port. Writes, sets, clears, and reads to<br>port (done via writes to FIOPIN, FIOSET, and FIOCLR, and<br>reads of FIOPIN) alter or return only the bits enabled by zeros<br>in this register.                                                                                                                                                                                               | R/W      | 0x0     | FIO0MASK - 0x3FFF C010<br>FIO1MASK - 0x3FFF C030<br>FIO2MASK - 0x3FFF C050<br>FIO3MASK - 0x3FFF C070<br>FIO4MASK - 0x3FFF C090 |

| FIOPIN          | Fast Port Pin value register using FIOMASK. The current state<br>of digital port pins can be read from this register, regardless of<br>pin direction or alternate function selection (as long as pins are<br>not configured as an input to ADC). The value read is masked<br>by ANDing with inverted FIOMASK. Writing to this register<br>places corresponding values in all bits enabled by zeros in<br>FIOMASK. | R/W      | 0x0     | FIO0PIN - 0x3FFF C014<br>FIO1PIN - 0x3FFF C034<br>FIO2PIN - 0x3FFF C054<br>FIO3PIN - 0x3FFF C074<br>FIO4PIN - 0x3FFF C094      |

|                 | <b>Important:</b> if a FIOPIN register is read, its bit(s) masked with 1 in the FIOMASK register will be set to 0 regardless of the physical pin state.                                                                                                                                                                                                                                                           |          |         |                                                                                                                                |

| FIOSET          | Fast Port Output Set register using FIOMASK. This register controls the state of output pins. Writing 1s produces highs at the corresponding port pins. Writing 0s has no effect. Reading this register returns the current contents of the port output register. Only bits enabled by 0 in FIOMASK can be altered.                                                                                               | R/W      | 0x0     | FIO0SET - 0x3FFF C018<br>FIO1SET - 0x3FFF C038<br>FIO2SET - 0x3FFF C058<br>FIO3SET - 0x3FFF C078<br>FIO4SET - 0x3FFF C098      |

| FIOCLR          | Fast Port Output Clear register using FIOMASK0. This register controls the state of output pins. Writing 1s produces lows at the corresponding port pins. Writing 0s has no effect. Only bits enabled by 0 in FIOMASK0 can be altered.                                                                                                                                                                            | WO       | 0x0     | FIO0CLR - 0x3FFF C01C<br>FIO1CLR - 0x3FFF C03C<br>FIO2CLR - 0x3FFF C05C<br>FIO3CLR - 0x3FFF C07C<br>FIO4CLR - 0x3FFF C09C      |

# Writing on a pin

- To configure pin as output a 1 must be written on the corresponding pin in FIOxDIR (0 is for input)

- To set or clear a pin Two register can be used

- > FIOxSET : set the pin by writing a 1 on the corresponding bit

- FIOxCLEAR : clear the bin by writing a 1 on the corresponding bit

- Writing a value in FIOxPIN can also be used

- Corresponding bit in FIOxMASK must be 0

- ♦ Ex

FIO0DIR = 0x2; // set direction for bit 1 FIO0SET = 0x2; // set P0.1 FIO0CLEAR = 0x2; // clear P0.1

FIO0DIR = 0x2 ; FIO0PIN |= 0x2; // set P0.1 FIO0PIN &= ~0x2; // clear P0.1

# **Interrupt with GPIO**

- Port0 and 2 can be configured to generate interrupt

- 2 pairs of enable/status registers are present : one for a rising edge and one for falling edge

- InEnF/R : enable corresponding pin for interrupt

- > IntStatF/R (RO) : to verify which pin has generate interrupt

- Interrupt must be cleared through IntClr register

| Generic<br>Name | Description                             | Access | Reset<br>value <mark>[1]</mark> | PORTn Register<br>Address & Name                       |

|-----------------|-----------------------------------------|--------|---------------------------------|--------------------------------------------------------|

| IntEnR          | GPIO Interrupt Enable for Rising edge.  | R/W    | 0x0                             | IO0IntEnR - 0xE002 8090<br>IO2IntEnR - 0xE002 80B0     |

| IntEnF          | GPIO Interrupt Enable for Falling edge. | R/W    | 0x0                             | IO0IntEnR - 0xE002 8094<br>IO2IntEnR - 0xE002 80B4     |

| IntStatR        | GPIO Interrupt Status for Rising edge.  | RO     | 0x0                             | IO0IntStatR - 0xE002 8084<br>IO2IntStatR - 0xE002 80A4 |

| IntStatF        | GPIO Interrupt Status for Falling edge. | RO     | 0x0                             | IO0IntStatF - 0xE002 8088<br>IO2IntStatF - 0xE002 80A8 |

| IntClr          | GPIO Interrupt Clear.                   | WO     | 0x0                             | IO0IntClr - 0xE002 808C<br>IO2IntClr - 0xE002 80AC     |

| IntStatus       | GPIO overall Interrupt Status.          | RO     | 0x00                            | IOIntStatus - 0xE002 8080                              |

#### Table 160. GPIO interrupt register map

# Exemple

```

void led210 init(void){

// Power control

//GPIO cannot be turned off

// CLOCK

PCLKSEL1 &= \sim (0 \times 3 \ll 2); //3:2 = 0b00 (CCLK / 4)

// PIN :

// function select for P2.10 (GPI0) in PINSEL4 (PINSEL4[21..20] = 0b00) (RW)

PINSEL4 &= \sim(3 << 20) ;

// connect mode selection for pin (00 = pull up resistor selected) (RW)

PINMODE4 &= \sim(3 << 20);

//PI0

// direction mode selection : output = 1 et input = 0 (out selected) (R/W)

FI02DIR |= (1 << 10);

// to allowed read an write on the selected pin (0 = enable)

FI02MASK &= \sim (1 <<10):

}

void led210 turn on(void){

FI02CLR = 1 << 10;

}

void led210 turn off(void){

FI02SET = 1 << 10;

}

```

# Clock for pio :chap4 p59 & 60

Table 57. Peripheral Clock Selection register 1 (PCLKSEL1 - address 0xE01F C1AC) bit description

| Bit   | Symbol       | Description                                               | Reset<br>value |

|-------|--------------|-----------------------------------------------------------|----------------|

| 1:0   | PCLK_DAT_RAM | Peripheral clock selection for the battery supported DAM. | 00             |

| 3:2   | PCLK_GPIO    | Peripheral clock selection for GPIOs.                     | 00             |

| 5:4   | PCLK_PCB     | Peripheral clock selection for the Fin Connect block.     | 00             |

| 7:6   | PCLK_I2C1    | Peripheral clock selection for I2C1.                      | 00             |

| 9:8   | -            | Unused, always read as 0.                                 | 00             |

| 11:10 | PCLK_SSP0    | Peripheral clock selection for SSP0.                      | 00             |

| 13:12 | PCLK_TIMER2  | Peripheral clock selection for TIMER2.                    | 00             |

| 15:14 | PCLK_TIMER3  | Peripheral clock selection for TIMER3.                    | 00             |

| 17:16 | PCLK_UART2   | Peripheral clock selection for UART2.                     | 00             |

| 19:18 | PCLK_UART3   | Peripheral clock selection for UART3.                     | 00             |

| 21:20 | PCLK_I2C2    | Peripheral clock selection for I2C2.                      | 00             |

| 23:22 | PCLK_I2S     | Peripheral clock selection for I2S.                       | 00             |

| 25:24 | PCLK_MCI     | Peripheral clock selection for MCI.                       | 00             |

| 27:26 | -            | Unused, always read as 0.                                 | 00             |

| 29:28 | PCLK_SYSCON  | Peripheral clock selection for the System Control block.  | 00             |

| 31:30 | -            | Unused, always read as 0.                                 | 00             |

#### Table 58. Peripheral Clock Selection register bit values

| PCLKSEL0 and PCLKSEL1<br>individual peripheral's clock<br>select options | Function                                                                                                                                | Reset<br>value |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 00                                                                       | PCLK_xyz = CCLK/4                                                                                                                       | 00             |

| 01                                                                       | PCLK_xyz = CCLK <sup>[1]</sup>                                                                                                          |                |

| 10                                                                       | PCLK_xyz = CCLK/2                                                                                                                       |                |

| 11                                                                       | Peripheral's clock is selected to PCLK_xyz = CCLK/8<br>except for CAN1, CAN2, and CAN filtering when '11'<br>selects PCLK_xyz = CCLK/6. |                |

For PCLK\_RTC only, the value '01' is illegal. Do not write '01' to the PCLK\_RTC. Attempting to write '01' results in the previous value being unchanged. PCLKSEL1 &=  $\sim (0 \times 3 << 2);$

The 2 bits 3:2 are cleared, selecting a clock of CCLK/4 for the GPIO

## **PINconnect**

| Table 135. | <ul> <li>LPC2420/60/68/70/78 pin function select register 4 (PINSEL4 - address<br/>0xE002 C010) bit description</li> </ul> |                     |                     |                     |                                                     |                |  |

|------------|----------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|---------------------|-----------------------------------------------------|----------------|--|

| PINSEL4    | Pin<br>name                                                                                                                | Function when<br>00 | Function<br>when 01 | Function<br>when 10 | Function when<br>11                                 | Reset<br>value |  |

| 11:10      | P2[5]                                                                                                                      | GPIO Port 2.5       | PWM1[6]             | DTR1                | TRACEPKT0[1]/<br>LCDLP                              | 00             |  |

| 13:12      | P2[6]                                                                                                                      | GPIO Port 2.6       | PCAP1[0]            | RI1                 | TRACEPKT1[1]/<br>LCDVD[0]/<br>LCDVD[4]              | 00             |  |

| 15:14      | P2[7]                                                                                                                      | GPIO Port 2.7       | RD2                 | RTS1                | TRACEPKT2 <sup>[1]</sup> /<br>LCDVD[1]/<br>LCDVD[5] | 00             |  |

| 17:16      | P2[8]                                                                                                                      | GPIO Port 2.8       | TD2                 | TXD2                | TRACEPKT3[1]/<br>LCDVD[2]/<br>LCDVD[6]              | 00             |  |

| 19:18      | P2[9]                                                                                                                      | GPIO Port 2.9       | USB_CONN<br>ECT1    | RXD2                | EXTINO <sup>[1]</sup> /<br>LCDVD[3]/<br>LCDVD[7]    | 00             |  |

| 21:20      | P2[10]                                                                                                                     | GPIO Port 2.10      | EINT0               | Reserved            | Reserved                                            | 00             |  |

| 23:22      | P2[11]                                                                                                                     | CPIO Port 2.11      | EINT1/<br>LCDCLKIN  | MCIDAT1             | I2GTX_CLK                                           | 00             |  |

/\* function select for P2.10 (GPI0) in PINSEL4

(PINSEL4[21..20] = 0b00 ) (RW) \*/

PINSEL4 &= ~(3 << 20) ;</pre>

# **General purpose timer**

- The LPC2478 includes four 32-bit Timer/Counters

- Count cycles of the system derived clock or an externally-supplied clock

- Include programmable 32-bit prescaler

- Can optionally generate interrupts or perform other actions at specified timer values, based on four match registers

- Set LOW on match, Set HIGH on match, Toggle on match, Do nothing on match.

- The Timer/Counter also includes four capture inputs to trap the timer value when an input signal transitions

- > A capture event may also optionally generate an interrupt

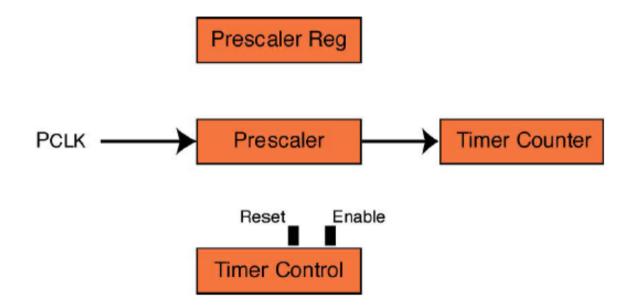

### Prescaler

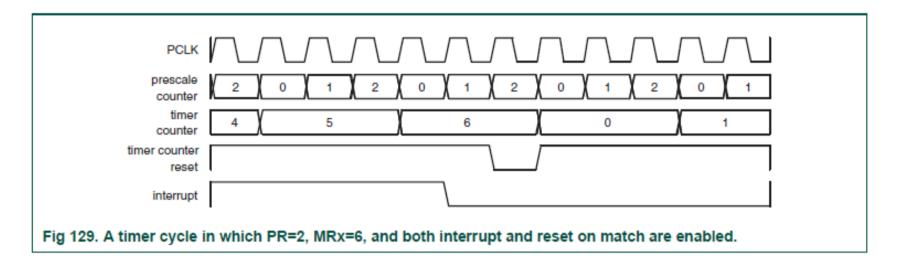

## **Prescaler and Timer counter control**

- Prescaler :

- > Each PCLK edge the prescaler counter is incremented

- When the prescaler counter equals the prescaler register the timer counter is incremented and the prescaler counter is cleared

- Timer Control register :

- > Enable or disable the 2 counter (prescaler and timer)

- > reset of the timer counter and the prescaler counter

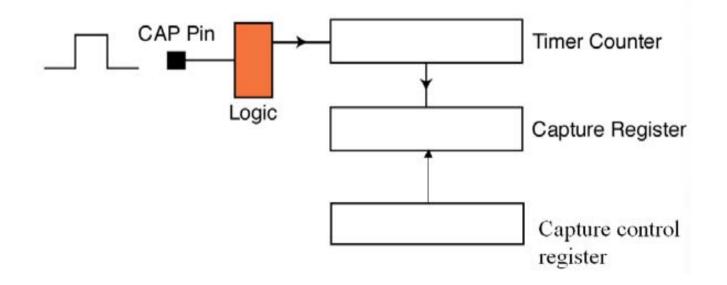

## **Capture mode**

- Use to measure pulse duration

- Counter captured on external events on CAP pin

- Rising edge, falling edge, toggle

- > Interrupt request can be generated by a capture

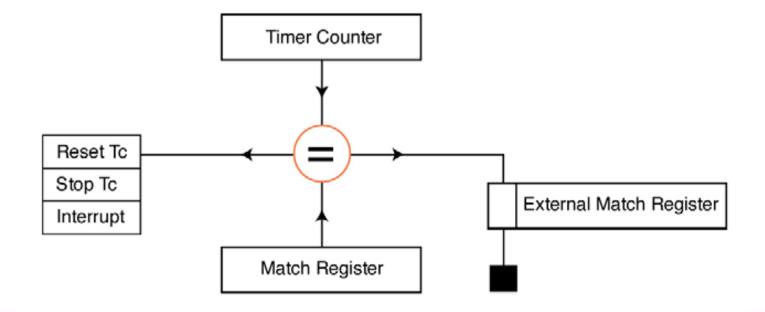

# Match mode

- Used to control the counter

- Disable or reset the counters

- Can generate an interrupt request on match

- The pin level can be changed on match (external match register)

> Set, cleared, toggle

# Timing on match

| PCLK                                                                                          |       |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------|-------|--|--|--|--|--|--|

| prescale counter                                                                              |       |  |  |  |  |  |  |

| timer counter                                                                                 | 4 5 6 |  |  |  |  |  |  |

| TCR[0]<br>(counter enable)                                                                    |       |  |  |  |  |  |  |

| interrupt                                                                                     |       |  |  |  |  |  |  |

| Fig 130. A timer Cycle in Which PR=2, MRx=6, and both interrupt and stop on match are enabled |       |  |  |  |  |  |  |

### User manual

#### Table 548: Timer Control Register (TCR, TIMERn: TnTCR - addresses 0xE000 4004, 0xE000 8004, 0xE007 0004, 0xE007 4004) bit description

| Bit | Symbol         | Description                                                                                                                                                                          | Reset Value |

|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 0   | Counter Enable | When one, the Timer Counter and Prescale Counter are<br>enabled for counting. When zero, the counters are<br>disabled.                                                               | 0           |

| 1   | Counter Reset  | When one, the Timer Counter and the Prescale Counter<br>are synchronously reset on the next positive edge of<br>PCLK. The counters remain reset until TCR[1] is<br>returned to zero. | 0           |

| 7:2 | -              | Reserved, user software should not write ones to reserved bits. The value read from a reserved bit is not defined.                                                                   | NA          |

### Table 550: Match Control Register (T[0/1/2/3]MCR - addresses 0xE000 4014, 0xE000 8014, 0xE007 0014, 0xE007 4014) bit description

| Bit | Symbol | Value | Description                                                                                   | Reset<br>Value |

|-----|--------|-------|-----------------------------------------------------------------------------------------------|----------------|

| 0   | MR0I   | 1     | Interrupt on MR0: an interrupt is generated when MR0 matches the value in the TC.             | 0              |

|     |        | 0     | This interrupt is disabled                                                                    |                |

| 1   | MR0R   | 1     | Reset on MR0: the TC will be reset if MR0 matches it.                                         | 0              |

|     |        | 0     | Feature disabled.                                                                             |                |

| 2   | MR0S   | 1     | Stop on MR0: the TC and PC will be stopped and TCR[0] will be set to 0 if MR0 matches the TC. | 0              |

|     |        | 0     | Feature disabled.                                                                             |                |

# Lab Example

```

static void mdelay(unsigned int ms)

{

T1TCR = 0x02; // stop and reset timer

T1PR = 0x00; // set prescaler to zero

T1MR0 = ms * (Fpclk / 1000); // Fpclk = 36000000

T1MCR = 0x04; // stop timer on match

T1TCR = 0x01; // start timer

```

//wait until delay time has elapsed : test the 'enable' bit while(T1TCR & 0x01)

```

;

}

```

# I2C

- Inter Integrated Circuit (Two Wire Interface)

- Two wire communication bus (synchronous serial transmission)

- Multimaster

- 400kbit/s (for slow devices)

- Each device has an address (8 or 10 bits) which is used when addressed in slave mode

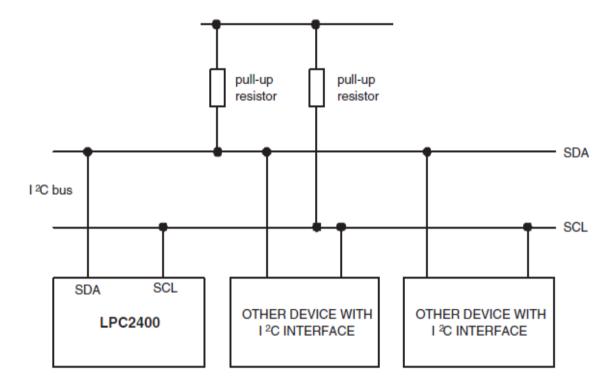

# **I2C bus connection**

Fig 111. I<sup>2</sup>C bus configuration

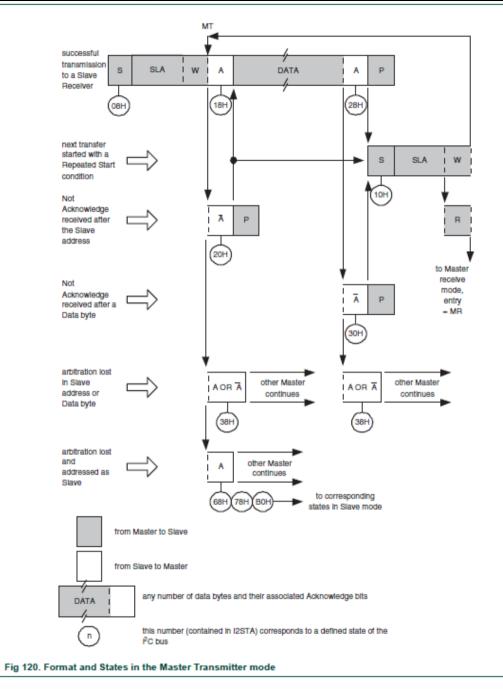

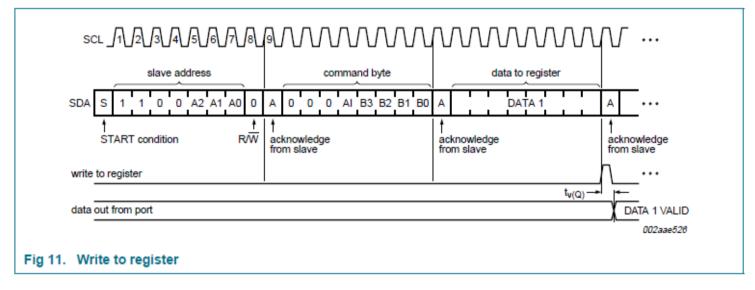

# Transfer

- Master drives the clocks and initiate transfer

- Slave respond to master request

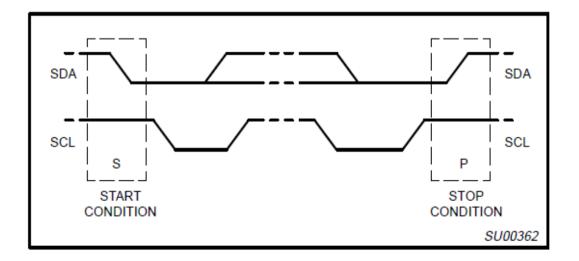

- A Transmission is started by a "start" sequence

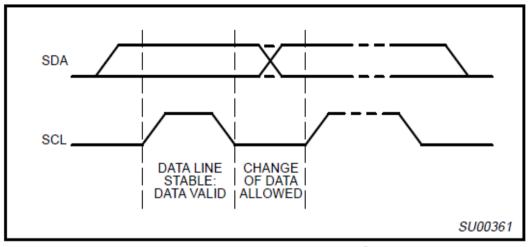

- Data are transferred in sequence of 8 bits (from/to master) MSb first

- Data are changed during low edge of clock

- > Data must be stable during high edge of clock

- Transmission ends with a "stop" sequence

- For each 8 bits data receiver must acknowledge sender by sending an "ack" bit (low level)

# **Start and stop conditions**

Figure 5. Bit transfer on the I<sup>2</sup>C-bus

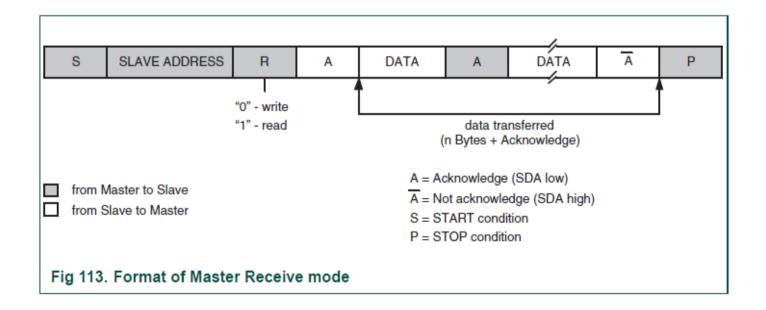

## **Transfers**

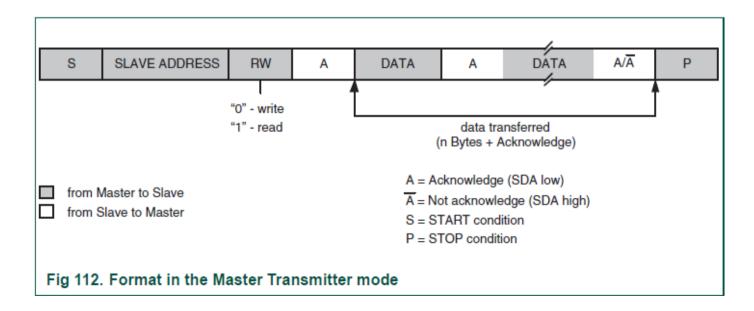

- Transfer from master to slave

- > First byte transmitted by master is slave address (7 bits)

- > The 8<sup>th</sup> bit is low signaling a write to the device

- > Next follows a numbers of data bytes

- > Slave returns an ACK bit after each received byte

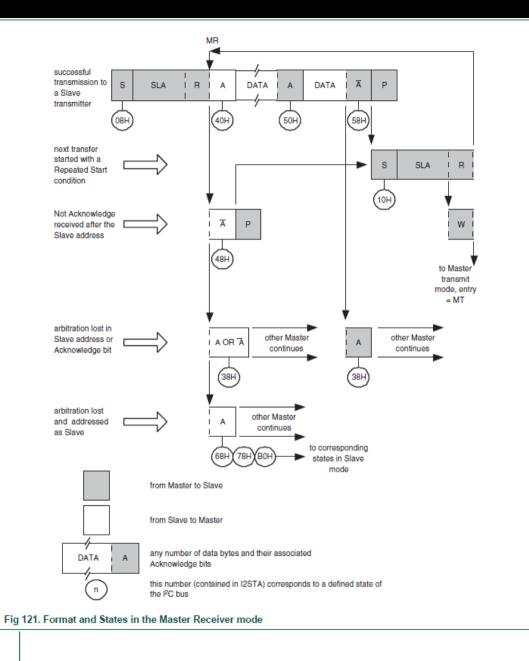

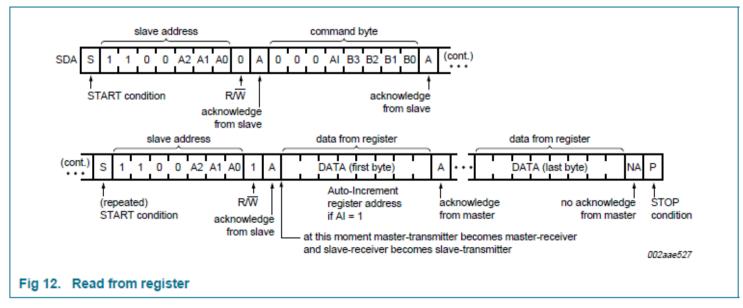

## Transfers

- Transfer from slave to master

- > First byte transmitted by master is slave address (7 bits)

- > The 8<sup>th</sup> bit is high signaling a read from the device

- > Next follows a numbers of data bytes send by the slave

- > The master send a NACK to stop the reading

# LPC I2C interface

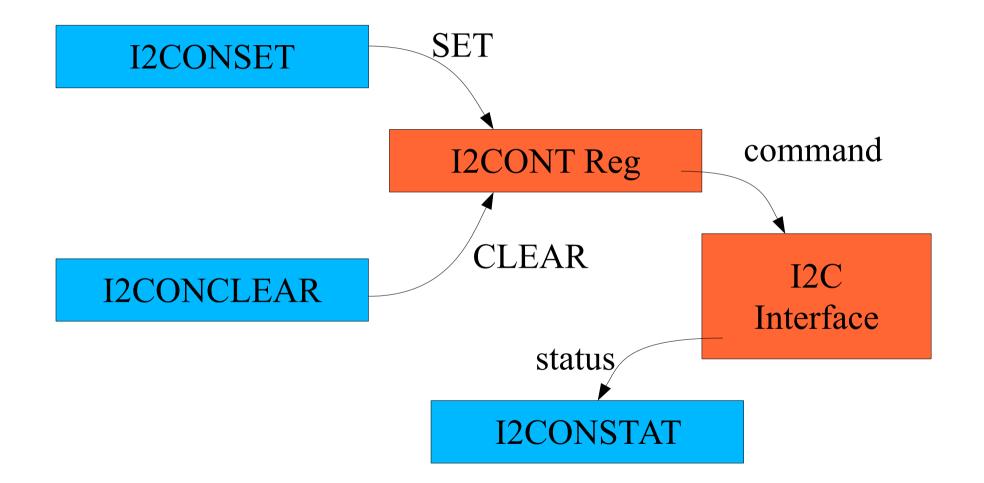

Table 512. Summary of I<sup>2</sup>C registers

| Generic<br>Name | Description                                                                                                                                                                                                                                                        | Access |      | I <sup>2</sup> Cn Register<br>Name & Address                                     |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|----------------------------------------------------------------------------------|

| I2CONSET        | I2C Control Set Register. When a one is written to a bit of this register, the corresponding bit in the $I^2C$ control register is set. Writing a zero has no effect on the corresponding bit in the $I^2C$ control register.                                      | R/W    | 0x00 | I2C0CONSET - 0xE001 C000<br>I2C1CONSET - 0xE005 C000<br>I2C2CONSET - 0xE008 0000 |

| I2STAT          | I2C Status Register. During I <sup>2</sup> C operation, this register provides detailed status codes that allow software to determine the next action needed.                                                                                                      | RO     | 0xF8 | I2C0STAT - 0xE001 C004<br>I2C1STAT - 0xE005 C004<br>I2C2STAT - 0xE008 0004       |