# CIC61508

Safety Monitor

User's Manual Release v2.2

Microcontrollers

Edition Nov 2012 Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2012. All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Document Change History |         |                        |                                                                                                                                                                                                                 |  |

|-------------------------|---------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Date                    | Version | Changed By             | Change Description                                                                                                                                                                                              |  |

| 2010-10-21              | 0.1     | Viswanath.R            | Initial Version                                                                                                                                                                                                 |  |

| 2010-11-08              | 0.2     | Viswanath.R            | Modules prepared Introduction, Error<br>State Monitor, Voltage Monitor and<br>Task Monitor                                                                                                                      |  |

| 2010-11-09              | 0.3     | Viswanath.R            | Opcode test sequencer is added                                                                                                                                                                                  |  |

| 2010-11-09              | 0.4     | Viswanath.R, Bharatesh | Updated all the sections                                                                                                                                                                                        |  |

| 2010-11-12              | 0.5     | Viswanath.R, Bharatesh | Added acronyms and the abbreviations and edited all the sections.                                                                                                                                               |  |

| 2010-11-15              | 0.6     | Viswanath.R, Bharatesh | updated as per Daryl's comments                                                                                                                                                                                 |  |

| 2010-11-17              | 0.7     | Viswanath.R, Bharatesh | Added the application use case                                                                                                                                                                                  |  |

| 2010-11-17              | 0.8     | Viswanath.R            | Modified with the proper page breaks and with proper formats                                                                                                                                                    |  |

| 2010-11-26              | 0.9     | Ashish K               | Incorporated review comments from<br>Mike Beach and Christophe Bouquet                                                                                                                                          |  |

| 2010-12-10              | 0.94    | M. Beach/A. Wenlock    | Proofing and minor additions                                                                                                                                                                                    |  |

| 2011-01-19              | 1.0     | Ashish K               | Modified Cover Page Template and<br>updated the formula in Section 2.6.3<br>Added disclaimer for customization of<br>DFLASH configuration                                                                       |  |

| 2011-03-22              | 1.1     | Ashish K               | Removed some confusing terms like<br>"opcode test sequencer" and replaced<br>them with standard terms                                                                                                           |  |

| 2011-03-23              | 1.2     | Ashish K               | Review comments incorporated.<br>Update with respect to usage of<br>TARDISS tool.                                                                                                                               |  |

| 2011-03-24              | 1.3     | M Beach                | Review and minor reformatting                                                                                                                                                                                   |  |

| 2011-03-25              | 1.4     | M. Beach/A. Wenlock    | Proofing                                                                                                                                                                                                        |  |

| 2011-04-11              | 1.5     | Bharatesh              | Corrected SYSDISA, SYSDISB parameters in section 2.7.1                                                                                                                                                          |  |

| 2011-04-21              | 1.6     | Bharatesh              | Updated section 2.3.1 - SPI<br>Communication Protocol                                                                                                                                                           |  |

| 2012-01-18              | 1.7     | Bharatesh              | UTP AI00064054: Added section 5.1 -<br>Selecting CIC61508 system clock<br>frequency                                                                                                                             |  |

| 2012-04-24              | 1.8     | Bharatesh              | Incorporated review comment of<br>REV_003314. Added section 5.1 -<br>Selecting CIC61508 system clock<br>frequency.<br>Updated sections 2.1.1.1 - ROM /                                                          |  |

|                         |         |                        | PFLASH checksum check. 2.2.1 –<br>Correction of CIC state. 2.3.2 - SPI<br>Error Handling. 2.6.1 - Wake-up Timer<br>Operation, 2.6.3 - Wake-up Timer<br>calibration. 3 - Tuning the DFLASH<br>NVM Configuration. |  |

| 2012-05-28              | 1.9     | Bharatesh              | UTP AI00064054:Updated section 2.3 -<br>SPI. Added 7 - Configuration guidelines                                                                                                                                 |  |

| 2012-05-29              | 2.0     | Arjun Muddaiah         | Updated the Table 7 in section 2.3.2                                                                                                                                                                            |  |

| Document Change History |         |                |                                                                                                        |  |

|-------------------------|---------|----------------|--------------------------------------------------------------------------------------------------------|--|

| Date                    | Version | Changed By     | Change Description                                                                                     |  |

|                         |         |                | with worst case leading and trailing delay.                                                            |  |

| 2012-07-10              | 2.1     | Arjun Muddaiah | UTP AI00061900: Updated section 2.2.1 - Error Counters                                                 |  |

| 2012-11-26              | 2.2     | Arjun Muddaiah | UTP AI00127297: Updated the UM to follow the proper naming conventions for Error State Monitor module. |  |

#### We Listen to Your Comments

Is there any information within this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your comments (including a reference to this document) to: mailto:mcdocu.comments@infineon.com Thank you.

#### **Table of Contents**

| Page |

|------|

|------|

| 1        | Introduction                                       | 0  |

|----------|----------------------------------------------------|----|

| I<br>1.1 | Scope                                              |    |

| 1.1      | Acronyms, Abbreviations and Definitions            |    |

| 1.2.1    | Abbreviations                                      |    |

| 1.2.1    | Definitions                                        |    |

| 1.2.2    | References                                         |    |

| 1.3      | Overview of Safety Architecture                    |    |

| 1.4      | Description of the CIC61508 Safety Monitor         |    |

| 1.6      | Feature Summary                                    | 11 |

| 1.7      | Special Function Register (SFR) Mapping            |    |

| 1.7      | NVM (Non-Volatile Memory) Address Mapping          |    |

| 1.0      |                                                    |    |

| 2        | Functional Description                             | 16 |

| 2.1      | Built-In Self-Tests (BIST)                         |    |

| 2.1.1    | Start-Up BIST                                      |    |

| 2.1.1.1  | ROM / PFLASH checksum check                        | 16 |

| 2.1.1.2  | Opcode check                                       | 16 |

| 2.1.1.3  | IRAM check                                         | 16 |

| 2.1.1.4  | XRAM check                                         | 16 |

| 2.1.1.5  | DFLASH check                                       |    |

| 2.1.1.6  | DFLASH configuration check                         | 16 |

| 2.1.2    | Runtime BIST (Background BIST)                     |    |

| 2.1.2.1  | DFLASH Runtime Slice Check                         | 17 |

| 2.1.2.2  | Opcode Check                                       | 17 |

| 2.1.2.3  | System Heartbeat Check                             | 17 |

| 2.1.3    | BIST Failure                                       | 17 |

| 2.2      | Integrity Monitor                                  | 18 |

| 2.2.1    | Pass Counters (PASSCNTXX)                          | 18 |

| 2.2.2    | System State Machine                               | 19 |

| 2.2.3    | State Transition                                   |    |

| 2.2.3.1  | RESET -> NOT READY                                 | 21 |

| 2.2.3.2  | NOT READY -> READY                                 | 21 |

| 2.2.3.3  | NOT READY-> Secure SPI                             | 21 |

| 2.2.3.4  | READY -> NOT READY                                 | 21 |

| 2.2.3.5  | READY -> ACTIVE                                    | 21 |

| 2.2.3.6  | ACTIVE -> TRIPPING 1                               |    |

| 2.2.3.7  | TRIPPING 1 -> TRIPPING 2 -> TRIPPING 3 -> DISABLED | 21 |

| 2.2.3.8  | DISABLED-> Secure SPI                              | 21 |

| 2.2.3.9  | DISABLED-> RESET                                   | 22 |

| 2.2.3.10 | <state name=""> -&gt; DISABLED</state>             | 22 |

| 2.2.4    | Integrity Monitor Configuration                    | 22 |

| 2.2.4.1  | Integrity Monitor Increment and Decrement Value    | 22 |

| 2.2.4.2  | Monitor Function Enable                            | 23 |

| 2.2.4.3  | Trip Time                                          | 23 |

| 2.2.5    | Integrity Monitor Registers                        | 23 |

| 2.3      | Serial Peripheral Interface                        |    |

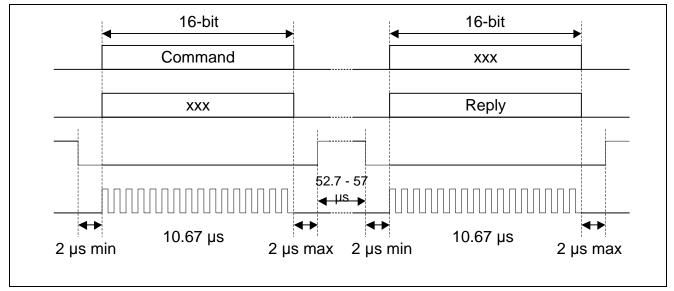

| 2.3.1    | SPI Communication Protocol                         | 29 |

| 2.3.2    | SPI Error Handling                                 | 30 |

| 2.3.3    | SPI Command Format                                 | 30 |

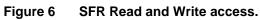

| 2.4      | Sequencer                                          | 32 |

| 2.4.1    | Sequencer Operation                                | 32 |

| 2.4.2    | Sequencer Configuration                            |    |

| 2.4.3    | Sequencer Registers                                |    |

| 2.5      | Supply Voltage Monitor                             |    |

| 2.5.1    | Supply Voltage Monitored Operation                 |    |

| 2.5.2    | Coherent Read                                      |    |

| 2.5.3    | Voltage Injection                                  |    |

| 2.5.4    | Supply Voltage Monitor Registers                   |    |

| 2.5.5    | Supply Voltage Monitor Configuration               |    |

|          |                                                    |    |

| Table of C  | ontents                                                     | Page |

|-------------|-------------------------------------------------------------|------|

| 2.6         | Wake-Up Timer                                               | 40   |

| 2.6.1       | Wake-up Timer Operation                                     |      |

| 2.6.2       | CIC61508 Reset Operation                                    | 40   |

| 2.6.3       | Wake-up Timer calibration                                   |      |

| 2.6.4       | Wake-Up Timer Registers                                     | 41   |

| 2.7         | Safety Path Control                                         | 43   |

| 2.7.1       | Safety Path Control Configuration                           | 43   |

| 2.7.2       | Real Time SYSDISx Pin Behaviour                             | 44   |

| 2.8         | Secure SPI Mode                                             | 46   |

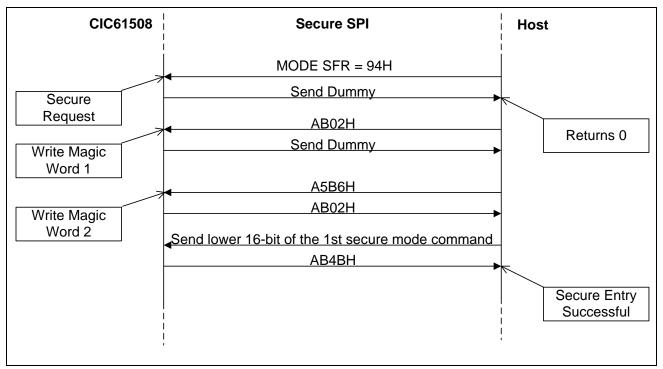

| 2.8.1       | Secure Mode Entry                                           | 46   |

| 2.8.2       | Secure SPI Mode Operation                                   | 46   |

| 2.8.3       | Secure SPI Mode Error Handling                              |      |

| 2.8.4       | Secure SPI Mode Synchronization To Host                     |      |

| 2.8.5       | Secure SPI Mode Exit                                        |      |

| 2.9         | Task Monitor                                                |      |

| 2.9.1       | Task Monitor Operation                                      |      |

| 2.9.2       | Task Monitor Configuration                                  |      |

| 2.9.3       | Task Monitor Registers                                      |      |

| 2.10        | Data Comparator                                             |      |

| 2.10.1      | Data Comparator Operation                                   |      |

| 2.10.2      | Data Comparator Configuration                               |      |

| 2.10.3      | Data Comparator Registers                                   |      |

| 2.11        | Scheduling Task Start Events                                |      |

| 3           | Tuning the DFLASH NVM Configuration                         | 59   |

| 3.1         | TARDISS Installation                                        |      |

| 3.2         | TARDISS Configuration (with microcontroller support)        | 59   |

| 3.2.1       | Connection to CIC61508                                      |      |

| 3.2.2       | Edit and Program the DFLASH Configuration                   |      |

| 3.3         | TARDISS Configuration (without microcontroller support)     |      |

| 3.3.1.1     | Import DFLASH Contents from a Spreadsheet                   |      |

| 3.3.1.2     | Export DFLASH Data to a C File                              |      |

| 3.4         | TARDISS Troubleshooting                                     |      |

| 3.5         | DFLASH Binary Generation (FLASH based CIC61508)             |      |

| 3.6         | Programming DFLASH                                          | 60   |

| 4           | Flashing Procedure                                          | 61   |

| 4.1         | FLOAD Tool                                                  | 61   |

| 4.1.1       | Installation                                                |      |

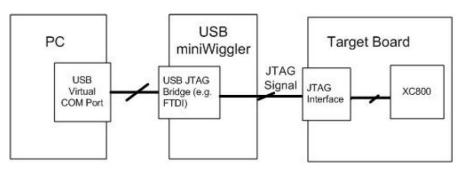

| 4.1.2       | Hardware connection between PC Host and Target              | 61   |

| 4.1.3       | FLASH Settings and Commands                                 | 62   |

| 5           | Software Build Environment                                  | 63   |

| <b>5</b> .1 | Selecting CIC61508 system clock frequency                   |      |

| 5.1         |                                                             |      |

| 6           | Application Use Case                                        |      |

| 6.1         | Description                                                 |      |

| 6.2         | Sample Procedure to move the CIC61508 into the ACTIVE State |      |

| 6.2.1       | Steps to move the Sequencer into the Maintain State         |      |

| 6.2.2       | Steps to get the VoltageX Monitors into the MAINTAIN State  |      |

| 6.3         | Example Configuration Settings                              |      |

| 6.3.1.1     | Integrity Monitor Configuration                             |      |

| 6.3.1.2     | Sequencer                                                   |      |

| 6.3.1.3     | Voltage Monitor Configuration                               | 69   |

| 7           | Configuration Guidelines                                    |      |

| 7.1         | Logical Monitoring                                          |      |

| 7.2         | Temporal Monitoring                                         |      |

| 7.3         | Configuring the Sequencer Table                             |      |

|             |                                                             |      |

#### List of Figures

#### Page

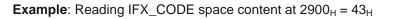

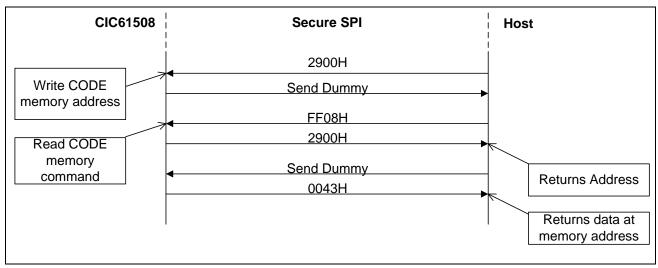

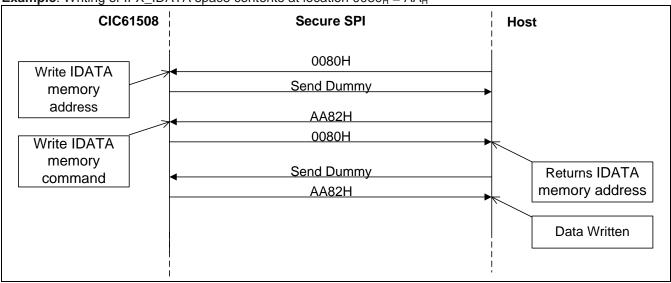

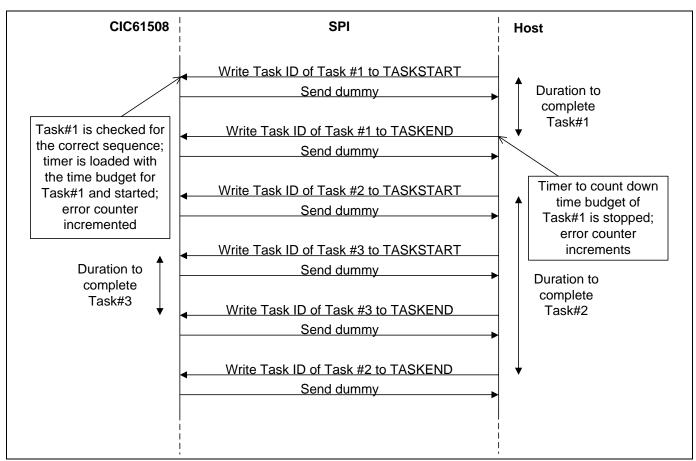

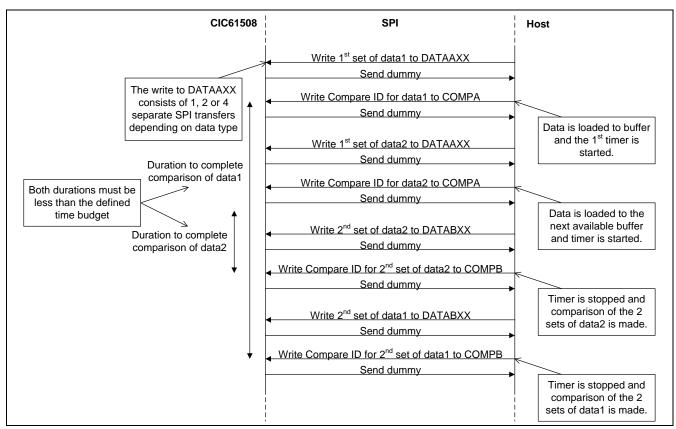

| Figure 1<br>Figure 2<br>Figure 3<br>Figure 4<br>Figure 5<br>Figure 6<br>Figure 7<br>Figure 8<br>Figure 9<br>Figure 10<br>Figure 11 | Block Diagram of the Safety System<br>Block Diagram of CIC61508<br>Integrity Monitor – The Eight Pass Counters<br>Integrity Monitor – System State Machine<br>SPI communication Protocol<br>SFR Read and Write access<br>Sequencer's Operational Sequence<br>Entry to Secure SPI Operation<br>Secure SPI Read operation<br>Secure SPI Read operation<br>Example of a Task Sequence | 12<br>18<br>20<br>29<br>31<br>33<br>46<br>48<br>48<br>51 |

|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Figure 12                                                                                                                          | Examples of Two Data Comparisons<br>FLOAD – Hardware Connection between PC and Target                                                                                                                                                                                                                                                                                              | 55                                                       |

|                                                                                                                                    | FLOAD – GUI Interface                                                                                                                                                                                                                                                                                                                                                              |                                                          |

#### List of Tables

## Page

|                                               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SFR Mapping                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pass Counter Increment and Decrement value    | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Monitor Function Enable                       | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Trip Time                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SPI Timing specification (Typical)            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Sequencer Parameter Addresses                 | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Voltage Monitor Configuration                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Safety Path Control Configuration for SYSDISC | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Logical monitoring description                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Sequencer Table example                       | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                               | NVM Address Mapping<br>Pass Counter Increment and Decrement value<br>Monitor Function Enable<br>SPI Timing specification (Typical)<br>Sequencer Parameter Addresses<br>Voltage Monitor Configuration<br>Wake-Up Time Interval per WAKEPRESCALAR value<br>Safety Path Control Configuration for SYSDISC<br>Safety Path Control Configuration for SYSDISC And SYSDISB<br>Typical Safety Path Pin State Sequence (with timings)<br>Secure SPI mode commands and operation spaces<br>Secure SPI mode error codes<br>Example of a Time Budget Table<br>Comparison Criteria and Data Type Definition<br>Data Comparator Parameter Addresses<br>TARDISS - Troubleshooting<br>FLOAD Installation Files<br>SPI Message Sequence from NOT_READY to ACTIVE state<br>Pass Counter Increment and Decrement Values<br>Monitor Function Enable<br>Tripping Time<br>Sequencer Configuration |

## 1 Introduction

## 1.1 Scope

The Safety Monitor CIC61508 Release is intended to support the CIC61508 with TriCore Architecture only. Hence all references to Safety Architecture will be with respect to TriCore Microcontroller Architecture.

## **1.2** Acronyms, Abbreviations and Definitions

#### 1.2.1 Abbreviations

| Abbreviation     | Comment                                                            |  |

|------------------|--------------------------------------------------------------------|--|

| ASIC             | Application Specific Integrated Circuit                            |  |

| AUTOSAR          | Automotive Open System Architecture                                |  |

| BIST             | Built-in Self-Test                                                 |  |

| CIC              | Companion IC                                                       |  |

| CPU              | Central Processing Unit                                            |  |

| CS               | Chip Select                                                        |  |

| EPS              | Electrical Powered Steering                                        |  |

| MRST             | Master Receive Slave Transmit                                      |  |

| MTSR             | Master Transmit Slave Receive                                      |  |

| NVM              | Non-Volatile Memory                                                |  |

| PCP              | Peripheral Controller Processor                                    |  |

| PORST            | Power-on Reset                                                     |  |

| RAM              | Random Access Memory                                               |  |

| ROM              | Read Only Memory                                                   |  |

| SBST             | Software Based Self Tests                                          |  |

| SCLK             | Serial Clock                                                       |  |

| SFR              | Special Function Register                                          |  |

| SPI              | Serial Peripheral Interface                                        |  |

| SW               | Software                                                           |  |

| TARDISS          | CIC61508 Test and Rapid Development for the Infineon Safety System |  |

| f <sub>sys</sub> | CIC61508 System Clock Frequency                                    |  |

## 1.2.2 Definitions

| Definition | Comment                                                                                                                                                                                                                              |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Event      | The condition(s) to be met to make a transition from a state to another state                                                                                                                                                        |  |

| Heartbeat  | All measurements are done in terms of heartbeat and this is the atomic unit of time for the CIC61508. One heartbeat is calibrated and is equal to $600\mu$ s.All the timing measurements in the CIC61508 are in terms of heartbeats. |  |

| Definition     | Comment                                                                                                                                                                                                                                 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Open window    | In the Sequencer module, the open window is defined as the time period in which the test is initiated.                                                                                                                                  |

| Closed window  | In the Sequencer module, the closed window is defined as the Idle time when the CIC61508 does not expect the Sequencer trigger command (Write to OTRHH).                                                                                |

| Maintain State | This state indicates that the specific monitor function has reached a safe state. This state is achieved if the pass counter of the respective monitor function has crossed the threshold value of $40_{\rm H}$ .                       |

| Error State    | This state indicates that the specific monitor function is not functioning properly to reach a safe state. This state is achieved if the pass counter of the respective monitor function is below the threshold value of $40_{\rm H}$ . |

## 1.3 References

[TARDISS] TARDISS\_v2\_9 User's Manual v1.6

## **1.4** Overview of Safety Architecture

In a safety-related system, safety integrity is based on a Challenge/Response Architecture controlled by a Safety Monitor independent of the microcontroller.

The Challenge/Response Architecture is built upon a system containing two processors. This allows it to have a layered hardware/software architecture that can be used to implement safety monitoring loops and fulfill the required hardware fault tolerance of the system. The cross-monitoring between the microcontroller and the safety monitor must be designed so that if a dangerous failure affects either the microcontroller or the safety monitor, then the safety-related system must enter the safe state, thus providing a hardware fault tolerance of one.

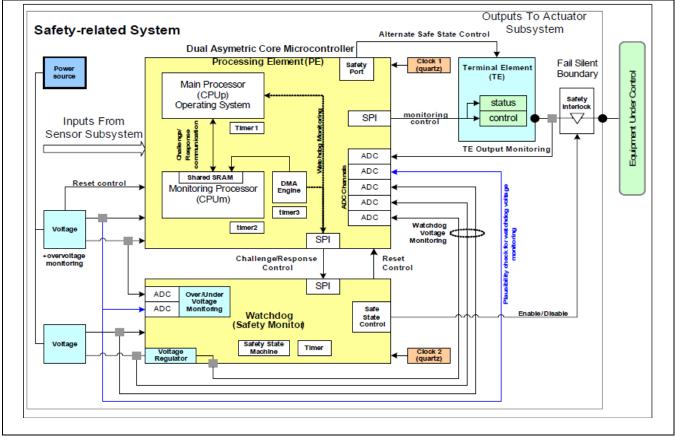

Figure 1 Block Diagram of the Safety System

The architecture presented in Figure 1 shows the situation where the two processors (CPUp and CPUm), are inside the same microcontroller. This is similar to the TriCore microcontrollers where CPUp is the TriCore main CPU and CPUm is the Peripheral Controller Processor (PCP). The processor (CPUp) is responsible for the execution of all safety-related applications covering all the safety loops. The second processor (CPUm) acts as monitoring processor covering the execution integrity (mainly program sequence monitoring) of the main processor. Because both CPUp and CPUm are in the same silicon, some situations exist where the monitoring may fail because of common cause failures. Because of that possibility an external Safety Monitor is required to monitor the execution of CPUm. The Safety Monitor itself can be a microcontroller or an ASIC. The three components CPUp, CPUm and Safety Monitor participate in a closed monitoring loop.

## **1.5** Description of the CIC61508 Safety Monitor

The CIC61508 is a Companion Safety Monitor Chip to build up functional safety applications; examples include airbag, Electrical Powered Steering (EPS) and damping systems. The chip is responsible for monitoring the host microcontroller's behaviour. It can monitor the host microcontroller's power supply and verify the host microcontroller's requests. It therefore serves as a diagnostic monitoring device to allow the host microcontroller system to be SIL3 safety compliant.

The CIC61508 includes several modules such as a Sequencer, a Data Comparator, a Task Monitor, an Integrity Monitor, Built-in Self Test (BIST), 4 Voltage Monitors and Reset Path Control by Wake-up Timer. In addition to these, CIC61508 will monitor the communication between the CIC61508 and the Host.

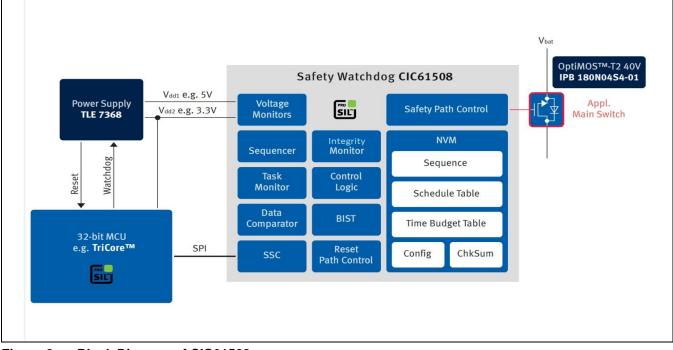

#### Figure 2 Block Diagram of CIC61508

The Sequencer is responsible for monitoring the sequence of answers generated by the Host. The answers generated by the Host are in response to the challenges initiated by CIC61508; these answers verify the Host Processor's integrity. The Host responds to the CIC61508 by sequentially sending a defined series of answers periodically within a defined timeframe. The Sequencer Monitor System will verify the answers against the static table stored in the CIC61508.

A Data Comparator compares two data variables delivered within a determined time period to check for an equal, greater or less than condition, based on a predefined mask value.

A Task Monitor uses a defined schedule table to check the dispatch of critical tasks running on the Host Microcontroller with predefined execution budgets. Such task deadline enforcements will allow, for example, the AutoSAR and OSEK operating systems to be used in safety applications.

Through the Voltage Monitors, the CIC61508 is also capable of detecting under- and over-voltage of the supply to the monitored microcontroller.

Communication between the Host and the CIC61508 is through the Serial Peripheral Interface (SPI). The CIC61508 screens for communication disturbances between the two.

To allow a low quiescent current for the Host Microcontroller System, the CIC61508 provides the function to wake up the Host at pre-defined intervals through a Wake-up Timer. The Wake-up Timer also provides a means to immediately reset the CIC61508 chip.

For added security, user-defined configuration parameters stored in the Non-Volatile Memory (NVM) of the CIC61508 are duplicated for redundancy. The CIC61508 also executes Built-In Self Tests (BIST) on start-up and during runtime, to ensure the correct operation of the CIC61508 chip.

The Integrity Monitor maintains the machine state of the CIC61508 based on all the other modules' functionality.

In the case of the TriCore's safety solution, the Task Monitor and Data Comparator Monitor are redundant, as the PCP controller in the Host Microcontroller (TriCore) is used instead. Hence, these 2 modules' monitoring needs to be disabled for the TriCore's safety solution. Please refer to <u>Section 2.2.4.2</u> to disable monitoring of certain modules.

## **1.6** Feature Summary

The CIC61508 has the following features supported by software:

· Power Supply Monitor for over- and under-voltage

Sequencer

- Task Monitor

- Data Comparison and Verification Functions

- SPI Communication Monitor

- Safety Path Control (enable/disable)

- Configurable Wake-Up Timer

## **1.7** Special Function Register (SFR) Mapping

CIC61508 will provide 8-bit SFRs to control and indicate the status of the CIC61508. The SFRs are mapped to 7-bit SFR addresses and accessed through SPI commands.

The SFR address mapping is as shown in Table 1.

| Address | SFR Name        | SFR Group                                                                 | Read<br>Command | Write<br>Command |

|---------|-----------------|---------------------------------------------------------------------------|-----------------|------------------|

| 0       | OTRHH           | Sequencer Registers                                                       | 00 <sub>H</sub> | 80 <sub>H</sub>  |

| 1       | OTRHL           |                                                                           | 01 <sub>H</sub> | 81 <sub>H</sub>  |

| 2       | OTRLH           |                                                                           | 02 <sub>H</sub> | 82 <sub>H</sub>  |

| 3       | OTRLL           |                                                                           | 03 <sub>H</sub> | 83 <sub>H</sub>  |

| 4       | WINMAX          |                                                                           | 04 <sub>H</sub> | -                |

| 5       | WINMIN          |                                                                           | 05 <sub>H</sub> | -                |

| 6       | SEQ             |                                                                           | 06 <sub>H</sub> | -                |

| 7       | SYSTEMINTEGRITY | Integrity Monitor     0       Registers     0       0     0       0     0 | 07 <sub>H</sub> | -                |

| 8       | PASSCNTSEQ      |                                                                           | 08 <sub>H</sub> | -                |

| 9       | PASSCNTVA       |                                                                           | 09 <sub>H</sub> | -                |

| 10      | PASSCNTVB       |                                                                           | 0A <sub>H</sub> | -                |

| 11      | PASSCNTVC       |                                                                           | 0B <sub>H</sub> | -                |

| 12      | PASSCNTVD       |                                                                           | 0C <sub>H</sub> | -                |

| 13      | PASSCNTTASK     |                                                                           | 0D <sub>H</sub> | -                |

| 14      | PASSCNTCOMPARE  |                                                                           | 0E <sub>H</sub> | -                |

| 15      | PASSCNTCOMM     |                                                                           | 0F <sub>H</sub> | -                |

| 16      | SUM0            |                                                                           | 10 <sub>H</sub> | -                |

| 17      | SUM1            |                                                                           | 11 <sub>H</sub> | -                |

| 18      | INT             |                                                                           | 12 <sub>H</sub> | -                |

| 19      | MODE            |                                                                           | 13 <sub>H</sub> | 93 <sub>H</sub>  |

| 20      | VOLTMONAH       | Voltage Monitor                                                           | 14 <sub>H</sub> | 94 <sub>H</sub>  |

| 21      | VOLTMONAL       | Registers                                                                 | 15 <sub>H</sub> | 95 <sub>H</sub>  |

| 22      | VOLTMONBH       |                                                                           | 16 <sub>H</sub> | 96 <sub>H</sub>  |

| 23      | VOLTMONBL       |                                                                           | 17 <sub>H</sub> | 97 <sub>H</sub>  |

| 24      | VOLTMONCH       |                                                                           | 18 <sub>H</sub> | 98 <sub>H</sub>  |

| 25      | VOLTMONCL       |                                                                           | 19 <sub>H</sub> | 99 <sub>H</sub>  |

| 26      | VOLTMONDH       |                                                                           | 1A <sub>H</sub> | 9A <sub>H</sub>  |

| 27      | VOLTMONDL       | 1                                                                         | 1B <sub>H</sub> | 9B <sub>H</sub>  |

| 28      | TASKSTART       | Task Monitor                                                              | 1C <sub>H</sub> | 9C <sub>H</sub>  |

| 29      | TASKEND         | Registers                                                                 | 1D <sub>H</sub> | 9D <sub>H</sub>  |

| 30      | WAKERELOAD      | Wake-up Timer                                                             | 1E <sub>H</sub> | 9E <sub>H</sub>  |

#### Table 1 SFR Mapping

| Address | SFR Name      | SFR Group       | Read<br>Command | Write<br>Command |

|---------|---------------|-----------------|-----------------|------------------|

| 31      | WAKEPRESCALAR | Registers       | 1F <sub>H</sub> | 9F <sub>H</sub>  |

| 32      | DATAAHH       | Data Comparator | 20 <sub>H</sub> | A0 <sub>H</sub>  |

| 33      | DATAAHL       | Registers       | 21 <sub>H</sub> | A1 <sub>H</sub>  |

| 34      | DATAALH       |                 | 22 <sub>H</sub> | A2 <sub>H</sub>  |

| 35      | DATAALL       |                 | 23 <sub>H</sub> | A3 <sub>H</sub>  |

| 36      | COMPA         | _               | 24 <sub>H</sub> | A4 <sub>H</sub>  |

| 37      | DATABHH       |                 | 25 <sub>H</sub> | A5 <sub>H</sub>  |

| 38      | DATABHL       |                 | 26 <sub>H</sub> | A6 <sub>H</sub>  |

| 39      | DATABLH       |                 | 27 <sub>H</sub> | A7 <sub>H</sub>  |

| 40      | DATABLL       |                 | 28 <sub>H</sub> | A8 <sub>H</sub>  |

| 41      | СОМРВ         |                 | 29 <sub>H</sub> | A9 <sub>H</sub>  |

| 42      | Reserved      | -               | -               | -                |

| 43      | Reserved      | -               | -               | -                |

| 44      | SVER          | Miscellaneous   | 2C <sub>H</sub> | -                |

| 45      | HVER          | Registers       | 2D <sub>H</sub> | -                |

## **1.8** NVM (Non-Volatile Memory) Address Mapping

To configure the functionality of each CIC61508 monitor, the CIC61508 has 4-Kbytes of memory space (NVM). Of the 4-Kbytes memory 2-Kbytes ( $A000_H - A7FF_H$ ) is used as a main copy and the remaining 2-Kbytes ( $A800_H - AFFF_H$ ) is used as a redundant copy. Parameters used for the configuration of the CIC61508 are stored in the main copy of the NVM. The redundant copy is the inverted value of the main copy parameters. This NVM will be shared among the functions of the CIC61508. The user is required to configure the main copy of the NVM.

The 4-Kbyte memory space mapping is as shown in <u>Table 2</u>.

| Monitor Function                          | Address range of<br>main copy         | Address range of<br>Redundant copy    | Number of Bytes |

|-------------------------------------------|---------------------------------------|---------------------------------------|-----------------|

| Sequencer                                 | A000 <sub>H</sub> – A142 <sub>H</sub> | A800 <sub>H</sub> – A942 <sub>H</sub> | 323             |

| Reserved                                  | A143 <sub>H</sub> – A15F <sub>H</sub> | A943 <sub>H</sub> – A95F <sub>H</sub> | -               |

| Data Comparator                           | A160 <sub>H</sub> – A461 <sub>H</sub> | A960 <sub>H</sub> – AC61 <sub>H</sub> | 770             |

| Reserved                                  | A462 <sub>H</sub> – A47F <sub>H</sub> | AC62 <sub>H</sub> – AC7F <sub>H</sub> | -               |

| Task Monitor                              | A480 <sub>H</sub> – A67E <sub>H</sub> | AC80 <sub>H</sub> – AE7E <sub>H</sub> | 511             |

| Reserved                                  | A67F <sub>H</sub> – A69F <sub>H</sub> | AE7F <sub>H</sub> -AE9F <sub>H</sub>  | -               |

| Voltage Monitors                          | A6A0 <sub>H</sub> – A6AF <sub>H</sub> | AEA0 <sub>H</sub> – AEAF <sub>H</sub> | 16              |

| Reserved                                  | A6B0 <sub>H</sub> – A6BF <sub>H</sub> | AEB0 <sub>H</sub> – AEBF <sub>H</sub> | -               |

| Pass Counter<br>Increment/Decrement Value | A6C0 <sub>H</sub> – A6CD <sub>H</sub> | AEC0 <sub>H</sub> – AECD <sub>H</sub> | 14              |

| Monitor Function Enable                   | A6CE <sub>H</sub> – A6D3 <sub>H</sub> | AECE <sub>H</sub> – AED3 <sub>H</sub> | 6               |

| Trip Time                                 | A6D4 <sub>H</sub> – A6D6 <sub>H</sub> | AED4 <sub>H</sub> – AED6 <sub>H</sub> | 3               |

| Safety Path Control                       | A6D7 <sub>H</sub> – A6F6 <sub>H</sub> | AED7 <sub>H</sub> – AEF6 <sub>H</sub> | 32              |

| Reserved                                  | A6F7 <sub>H</sub> – A7FF <sub>H</sub> | AEF7 <sub>H</sub> – AFFF <sub>H</sub> | -               |

#### Table 2 NVM Address Mapping

## 2 Functional Description

## 2.1 Built-In Self-Tests (BIST)

Built-In Self-Tests are implemented in the CIC61508 to ensure system integrity at start-up (Start-up BIST) and also throughout its run-time (Background BIST). BIST ensures that the CIC61508 is fit to run and act as a safety monitor. It then performs continuous background tests to ensure that it remains operational.

## 2.1.1 Start-Up BIST

Start-up BIST is executed at Start-up when CIC61508 is in a RESET state.

The following tests are performed by Start-up BIST:

## 2.1.1.1 ROM / PFLASH checksum check

This check performs a CRC8 checksum which is calculated from the base of PFLASH/ROM address  $0000_{H}$  till 2FFE<sub>H</sub> ROM memory and compared against the checksum stored at 2FFF<sub>H</sub>. The checksum value at 2FFF<sub>H</sub> needs to be updated for any code changes in the PFLASH.

## 2.1.1.2 Opcode check

This check performs 8051 opcode integrity tests.

## 2.1.1.3 IRAM check

This check performs the MARCH C test from address  $00_H$  till FF<sub>H</sub>.

#### 2.1.1.4 XRAM check

This check performs the MARCH C test from address  $F000_H$  till  $F1FF_H$ .

## 2.1.1.5 DFLASH check

During Start-up BIST, the NVRAM parameters will be compared against the inverted copy.

## 2.1.1.6 DFLASH configuration check

This test checks for the plausibility of the NVRAM configurations.

- Valid Range of Sequencer table length (Min: 08<sub>H</sub>, Max: 40<sub>H</sub>).

- Sequencer Minimum Window (Min: 00<sub>H</sub>, Max: 63<sub>H</sub>), Maximum Window (Min: 01<sub>H</sub>, Max: 64<sub>H</sub>).

- Task Monitor table length should be of a maximum 255 monitored tasks.

- Data Comparator table length should be of a maximum 128 comparison tasks.

- Data Comparator, table length (Min: 0, Max: 128), Data Type (Min: 0, Max: 6) and Compare Type (Min: 0, Max: 2).

- Tripping Timeout range (Min: 00<sub>H</sub>, Max: FF<sub>H</sub>)

- Wakeup Prescalar Max: 0B<sub>H</sub>

- Voltage Monitor (Min: 0, Max: 1023)

- Checks for control bits corresponding to SYSDISA, SYSDISB (Only Port 3 bits 1 & 0 can be set), SYSDISC (Only Port 0 bit 2 can be set).

- Pass Increments (Min: 00<sub>H</sub>, Max: 3F<sub>H</sub>) and Fail Decrements (Min: 00<sub>H</sub>, Max: 3F<sub>H</sub>).

User's Manual

## 2.1.2 Runtime BIST (Background BIST)

Upon successful completion of Start-up BIST, the CIC61508 moves out of the RESET state. Henceforth, Runtime BIST is executed in the background whenever the CIC61508 is idle (after servicing its heartbeat service interrupt).

The following tests are performed by Runtime BIST:

## 2.1.2.1 DFLASH Runtime Slice Check

The Runtime BIST partitions the DFLASH main copy (lower 2K of DFLASH area) into 128 slices, where each slice is of 16 bytes. In each slice, the NVRAM parameters are compared against the corresponding inverted copy (upper 2K half of the DFLASH area). The comparison result, positive and negative, is reported to the Integrity Monitor. During every run of Runtime BIST, the incremented new slice is tested sequentially (wrap-around to the first slice at the end of the last slice).

## 2.1.2.2 Opcode Check

Refer to Section 2.1.1.2 for details.

## 2.1.2.3 System Heartbeat Check

If, for any reason, the main system heartbeat interrupt is delayed such that it becomes pending while a previous instance is still executing, a FATAL timing budget overrun event is flagged in INT SFR for the BIST. The CIC65108 then enters the DISABLED state. However, unlike other entry routes to this state, SPI communications become read-only and only a power-on reset can restart the device. Typically, the system heartbeat check is violated by SPI traffic that does not conform to the 8 messages per heartbeat limit.

#### 2.1.3 BIST Failure

If any of the above Start-up/Runtime BIST tests detects any failure, it is a FATAL error and the system will be brought immediately into the Disabled State. A FATAL event will also be flagged in INT SFR. The pin states of SysDisA, SysDisB and SysDisC will be set to DISABLED start.

## 2.2 Integrity Monitor

## 2.2.1 Pass Counters (PASSCNTXX)

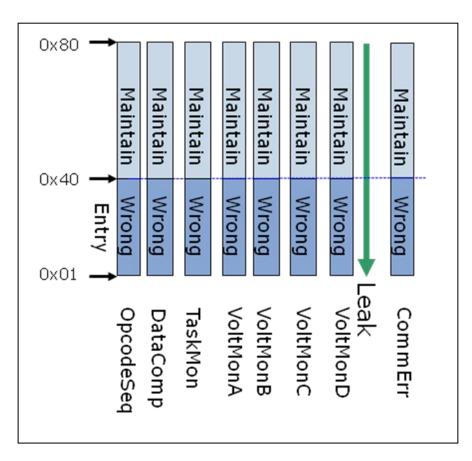

The Integrity Monitor is at the heart of the CIC61508. It will monitor all the CIC61508 functions. It consists of eight pass counters which monitor the five main functions of the CIC61508:

- Sequencer

- Data Comparator

- Task Monitor

- Four Voltage Monitors

- SPI Communication Monitor

These counters will increment and decrement according to the pass or fail conditions of respective functions. The pass counters are initialized at 1 and run between counts of 1 and 128 ( $80_H$ ), but they will never underflow nor overflow. Therefore, incrementing (or decrementing) an pass counter that has the value  $80_H$  (or  $01_H$ ) will see the pass counter still retaining the value  $80_H$  (or  $01_H$ ), since an overflow (or underflow) is not possible. These pass counters will be associated with the eight pass counter registers. The current Counter Value for each monitor function can be obtained from the respective PASSCNTXXX SFRs. These Counter SFRs are updated every 600µs (heartbeat).

#### Figure 3 Integrity Monitor – The Eight Pass Counters

During the execution of the monitor functions, the pass counters are incremented / decremented by a predetermined configured value in the NVM, which may be different for each pass counter, when a pass or fail event for the respective function occurs. This happens irrespective of any state other than the RESET and Secure SPI state. The SPI Communication Monitor counter will never increment, but will be decremented by  $01_{\rm H}$  upon the SPI communication error. The SPI Communication counter value can be set to

$80_{H}$  by the Host writing the SPI Reset Request to the Mode SFR. If this is not done, the Ready state can never be reached as the SPI communications pass counter will remain at 0x01.

In order to ensure that all the functions will happen periodically, the CIC61508 will provide an aging mechanism, so that pass counters will be decremented by  $01_H$  regardless of pass or fail conditions. Autodecay will happen in every heartbeat for Voltage Monitors. For the rest of the monitoring functions, it will happen for every four heartbeats. This auto-decay mechanism will not happen for the SPI Communication Monitor Counter.

If the value of the respective pass counters is equal to or above  $64(40_{\text{H}})$ , the monitor function's state will be in Maintain. The status of the system can be detected by using the following SFRs:

- SystemIntegrity

- INT

- SUM0

- SUM1

For details refer to Section 2.2.5

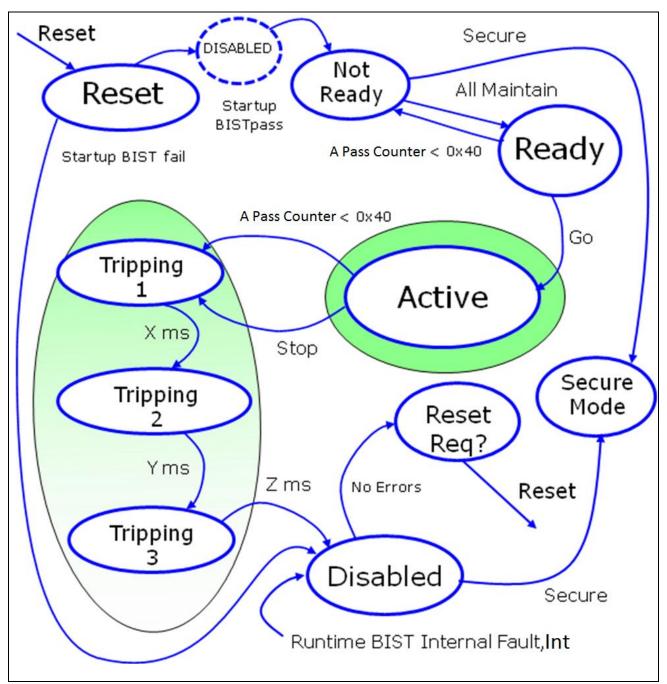

## 2.2.2 System State Machine

An overview of the System State Machine is shown in <u>Figure 4</u>. The System State Machine consists of the following states:

- Reset state

- Not Ready state

- Ready state

- Active state

- Tripping states

- Tripping state1

- Tripping state 2

- Tripping state 3

- Disabled state

- Reset Request state

- SPI Secure Mode state

Figure 4 Integrity Monitor – System State Machine

## 2.2.3 State Transition