# **RUBY-MM-1616 Family**

PC/104 I/O Module with 4, 8 or 16 16-bit Analog Outputs and 48 GPIO

Rev A.0 June 2013

| Revision | Date      | Comment         |

|----------|-----------|-----------------|

| A.0      | 6/13/2013 | Initial release |

FOR TECHNICAL SUPPORT PLEASE CONTACT:

support@diamondsystems.com

© Copyright 2013 Diamond Systems Corporation 555 Ellis Street Mountain View, CA 94043 USA Tel 1-650-810-2500 Fax 1-650-810-2525 www.diamondsystems.com

# TABLE OF CONTENTS

| 1.  | Important Safe Handling Information                         | 3  |

|-----|-------------------------------------------------------------|----|

| 2.  | Introduction                                                |    |

| 2.  | 1 Description                                               | 4  |

| 2.  | 2 Features                                                  | 4  |

| 2.  | 3 Available Models                                          | 5  |

| 3.  | Functional Overview                                         | 5  |

| 3.  | 1 Functional Block Diagram                                  | 5  |

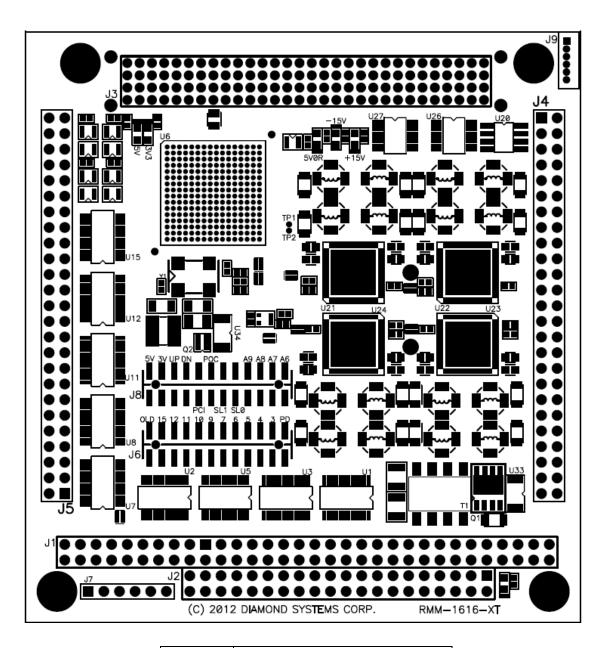

| 3.  | 2 Board Drawing                                             | 6  |

| 4.  | Connector Pinout                                            | 7  |

| 4.  |                                                             | 7  |

| 4.  |                                                             |    |

| 4.  | ······································                      |    |

| 4.  |                                                             |    |

| 4.  | 5 5 ( )                                                     |    |

| 5.  | Board Configuration                                         |    |

| 5.  |                                                             |    |

| 5.  |                                                             |    |

| 5.  |                                                             |    |

| 5.  |                                                             |    |

| 5.  |                                                             |    |

| 5.  |                                                             |    |

| 5.  |                                                             |    |

| 6.  | Theory of Operation                                         |    |

| 6.  | 1 Analog Functionality                                      |    |

|     | 6.1.1 D/A Functions                                         |    |

|     | 6.1.2 Waveform Generator Circuit                            |    |

|     | 6.1.3 D/A Calibration                                       |    |

| 6.  | 2 Digital I/O Functionality                                 |    |

|     | 6.2.1 Digital I/O                                           |    |

|     | 6.2.2 Counter/Timers                                        |    |

|     | 6.2.3 Pulse Width Modulators                                |    |

| 7.  | Register MAP                                                |    |

|     | 1 I/O Map Summary                                           |    |

| 7.  |                                                             | 16 |

| 7.  |                                                             |    |

| 7.  |                                                             |    |

| 7.  |                                                             |    |

| 7.  |                                                             |    |

| 7.  | 7 Interrupt, Configuration, and ID Registers Block (page 7) | 20 |

| 7.  |                                                             |    |

| 8.  | D/A Circuit                                                 |    |

| 9.  | Waveform Generator                                          |    |

|     | EEPROM Interface                                            |    |

|     | Digital I/O                                                 |    |

|     | Counters/Timers                                             |    |

|     | Pulse Width Modulation                                      |    |

|     | Miscellaneous Functions                                     |    |

|     | Internal Signals and Functions                              |    |

|     | 5.1 Interrupts                                              |    |

|     | 5.2 EEPROM Reload                                           |    |

|     | 5.3 Reset                                                   | -  |

|     | Bus Interface                                               |    |

| 17. | Specifications                                              | 55 |

# **1. IMPORTANT SAFE HANDLING INFORMATION**

# WARNING!

### **ESD-Sensitive Electronic Equipment**

Observe ESD-safe handling procedures when working with this product.

Always use this product in a properly grounded work area and wear appropriate ESD-preventive clothing and/or accessories.

Always store this product in ESD-protective packaging when not in use.

### Safe Handling Precautions

This board contains a high density connector with many connections to sensitive electronic components. This creates many opportunities for accidental damage during handling, installation and connection to other equipment. The list here describes common causes of failure found on boards returned to Diamond Systems for repair. This information is provided as a source of advice to help you prevent damaging your Diamond (or any vendor's) embedded computer boards.

**ESD damage** – This type of damage is usually almost impossible to detect, because there is no visual sign of failure or damage. The symptom is that the board eventually simply stops working, because some component becomes defective. Usually the failure can be identified and the chip can be replaced. To prevent ESD damage, always follow proper ESD-prevention practices when handling computer boards.

**Damage during handling or storage** – On some boards we have noticed physical damage from mishandling. A common observation is that a screwdriver slipped while installing the board, causing a gouge in the PCB surface and cutting signal traces or damaging components.

Another common observation is damaged board corners, indicating the board was dropped. This may or may not cause damage to the circuitry, depending on what is near the corner. Most of our boards are designed with at least 25 mils clearance between the board edge and any component pad, and ground / power planes are at least 20 mils from the edge to avoid possible shorting from this type of damage. However these design rules are not sufficient to prevent damage in all situations.

A third cause of failure is when a metal screwdriver tip slips, or a screw drops onto the board while it is powered on, causing a short between a power pin and a signal pin on a component. This can cause overvoltage / power supply problems described below. To avoid this type of failure, only perform assembly operations when the system is powered off.

Sometimes boards are stored in racks with slots that grip the edge of the board. This is a common practice for board manufacturers. However our boards are generally very dense, and if the board has components very close to the board edge, they can be damaged or even knocked off the board when the board tilts back in the rack. Diamond recommends that all our boards be stored only in individual ESD-safe packaging. If multiple boards are stored together, they should be contained in bins with dividers between boards. Do not pile boards on top of each other or cram too many boards into a small location. This can cause damage to connector pins or fragile components.

**Power supply wired backwards** – Our power supplies and boards are not designed to withstand a reverse power supply connection. This will destroy each IC that is connected to the power supply (i.e. almost all ICs). In this case the board will most likely will be unrepairable and must be replaced. A chip destroyed by reverse power or by excessive power will often have a visible hole on the top or show some deformation on the top surface due to vaporization inside the package. **Check twice before applying power!**

**Overvoltage on digital I/O line** – If a digital I/O signal is connected to a voltage above the maximum specified voltage, the digital circuitry can be damaged. On most of our boards the acceptable range of voltages connected to digital I/O signals is 0-5V, and they can withstand about 0.5V beyond that (-0.5 to 5.5V) before being damaged. However logic signals at 12V and even 24V are common, and if one of these is connected to a 5V logic chip, the chip will be damaged, and the damage could even extend past that chip to others in the circuit

# 2. INTRODUCTION

### 2.1 Description

The Ruby-MM-1616 is a family of PC/104 I/O modules featuring 4, 8 or 16 16-bit analog voltage and current outputs, and 48 digital I/O lines. The module uses the Analog Devices AD5711 16-channel 16-bit DAC chip for the D/A outputs and an FPGA with level-shifting transceivers for the DIO lines. A 50-pin connector provides access to the 16 analog outputs, and another 50-pin connector provides access to the 48 DIO lines. The board operates over the industrial temperature range of -40°C to +85°C and is supported by Diamond Systems' Universal Driver software. Models are available with either PC/104 or PC/104-*Plus* I/O expansion buses.

### 2.2 Features

#### **Board Features**

- 4, 8 or 16 analog outputs with 16-bit D/A resolution

- Programmable voltage output ranges: 0-5V, 0-10V, ±5V, ±10V, 0-20mA, 4-20mA, 0-24mA

- Independent output range for each channel

- Waveform generator on up to 8 channels

- Simultaneous update of any combination of channels

- HART signal handling capability (channels 0 3 only)

- Multi-channel simultaneous waveform output capability with up to 100KHz waveform update rate

- Output current limit +/-5mA per channel in voltage mode

- Autocalibration of D/A circuits using the internal offset and gain registers for each channel

- ◆ 40 byte-wide and 8 bit-wide digital I/O lines with programmable direction

- 2 32-bit programmable counter / timers

- 4 24-bit pulse width modulators

- PC/104 ISA 16-bit bus interface or PC/104-Plus (ISA + PCI) 32-bit bus interface

#### Software Support

Diamond's Universal Driver software with functions including:

- D/A output

- D/A waveform generator

- Calibration

- Digital I/O bit and byte-wide

- ◆ Digital I/O PWM

#### Mechanical, Electrical, and Environmental

- PC/104 compliant form factor

- Dimensions: 90 x 96mm (3.55 x 3.775")

- ♦ +5VDC input voltage

- → -40°C to +85°C operating temperature

- RoHS compliant

### 2.3 Available Models

The following models are available offering a selection of analog outputs for each bus configuration.

| Model Number  | Description                                                                                                     |

|---------------|-----------------------------------------------------------------------------------------------------------------|

| RMM-1616AP-XT | 16 Channel 16-bit Analog Output PC/104- <i>Plus</i> Module with 48 Digital I/O, extended temperature            |

| RMM-816AP-XT  | 8 Channel 16-bit Analog Output PC/104- <i>Plus</i> Module with 48 Digital I/O, extended temperature             |

| RMM-416AP-XT  | 4 Channel 16-bit Analog Output PC/104- <i>Plus</i> Module with 48 Digital I/O, extended temperature (MOQ of 50) |

| RMM-1616A-XT  | 16 Channel 16-bit Analog Output PC/104 Module with 48 Digital I/O, extended temperature                         |

| RMM-816A-XT   | 8 Channel 16-bit Analog Output PC/104 Module with 48 Digital I/O, extended temperature                          |

| RMM-416A-XT   | 4 Channel 16-bit Analog Output PC/104 Module with 48 Digital I/O, extended temperature (MOQ of 50)              |

# 3. FUNCTIONAL OVERVIEW

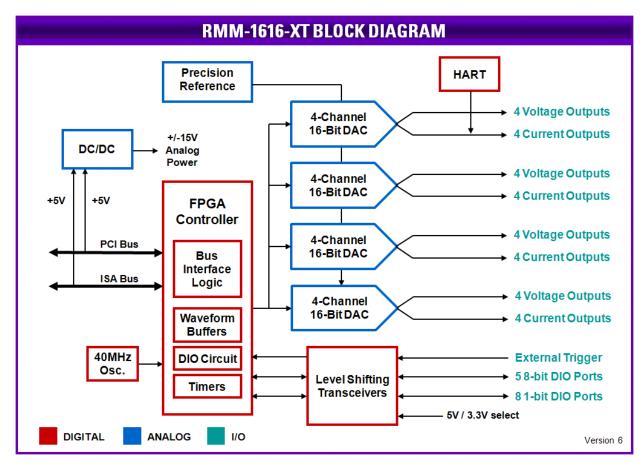

### 3.1 Functional Block Diagram

| J1 & J2 | PC/104 connectors         |  |  |  |

|---------|---------------------------|--|--|--|

| J3      | PCI connector             |  |  |  |

| J4      | Analog connector          |  |  |  |

| J5      | Digital connector         |  |  |  |

| J6      | IRQ jumper block          |  |  |  |

| J8      | Base Address jumper block |  |  |  |

| J9      | 4-channel HART connector  |  |  |  |

# 4. CONNECTOR PINOUT

## 4.1 PC/104 (J1, J2)

Connectors J1 and J2 provide the standard PC/104 16-bit ISA bus.

### View from Top of Board

#### J1: PC/104 8-bit bus connector

| A1  | B1                                                                                                                                                                                                                                                                                                                                                                                                                  | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A2  | B2                                                                                                                                                                                                                                                                                                                                                                                                                  | RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A3  | B3                                                                                                                                                                                                                                                                                                                                                                                                                  | +5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A4  | B4                                                                                                                                                                                                                                                                                                                                                                                                                  | IRQ9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A5  | B5                                                                                                                                                                                                                                                                                                                                                                                                                  | -5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A6  | B6                                                                                                                                                                                                                                                                                                                                                                                                                  | DRQ2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A7  | B7                                                                                                                                                                                                                                                                                                                                                                                                                  | -12V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A8  | B8                                                                                                                                                                                                                                                                                                                                                                                                                  | 0WS-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A9  | B9                                                                                                                                                                                                                                                                                                                                                                                                                  | +12V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A10 | B10                                                                                                                                                                                                                                                                                                                                                                                                                 | Key                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A11 | B11                                                                                                                                                                                                                                                                                                                                                                                                                 | SMEMW-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A12 | B12                                                                                                                                                                                                                                                                                                                                                                                                                 | SMEMR-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A13 | B13                                                                                                                                                                                                                                                                                                                                                                                                                 | IOW-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A14 | B14                                                                                                                                                                                                                                                                                                                                                                                                                 | IOR-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A15 | B15                                                                                                                                                                                                                                                                                                                                                                                                                 | DACK3-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A16 | B16                                                                                                                                                                                                                                                                                                                                                                                                                 | DRQ3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A17 | B17                                                                                                                                                                                                                                                                                                                                                                                                                 | DACK1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A18 | B18                                                                                                                                                                                                                                                                                                                                                                                                                 | DRQ1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A19 | B19                                                                                                                                                                                                                                                                                                                                                                                                                 | Refresh-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A20 | B20                                                                                                                                                                                                                                                                                                                                                                                                                 | SYSCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A21 | B21                                                                                                                                                                                                                                                                                                                                                                                                                 | IRQ7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A22 | B22                                                                                                                                                                                                                                                                                                                                                                                                                 | IRQ6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A23 | B23                                                                                                                                                                                                                                                                                                                                                                                                                 | IRQ5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A24 | B24                                                                                                                                                                                                                                                                                                                                                                                                                 | IRQ4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A25 | B25                                                                                                                                                                                                                                                                                                                                                                                                                 | IRQ3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A26 | B26                                                                                                                                                                                                                                                                                                                                                                                                                 | DACK2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A27 | B27                                                                                                                                                                                                                                                                                                                                                                                                                 | TC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A28 | B28                                                                                                                                                                                                                                                                                                                                                                                                                 | BALE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A29 | B29                                                                                                                                                                                                                                                                                                                                                                                                                 | +5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A30 | B30                                                                                                                                                                                                                                                                                                                                                                                                                 | OSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A31 | B31                                                                                                                                                                                                                                                                                                                                                                                                                 | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A32 | B32                                                                                                                                                                                                                                                                                                                                                                                                                 | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | A2         A3         A4         A5         A6         A7         A8         A9         A10         A11         A12         A13         A14         A15         A16         A11         A12         A13         A14         A15         A16         A17         A18         A19         A20         A21         A22         A23         A24         A25         A26         A27         A28         A29         A30 | A2         B2           A3         B3           A4         B4           A5         B5           A6         B6           A7         B7           A8         B8           A9         B9           A10         B10           A11         B11           A12         B12           A13         B13           A14         B14           A15         B15           A16         B16           A17         B17           A18         B18           A19         B19           A20         B20           A21         B17           A18         B18           A19         B19           A20         B20           A21         B21           A22         B22           A23         B23           A24         B24           A25         B25           A26         B26           A27         B27           A28         B28           A29         B20           A30         B30 |

| J2: | PC/104 | 16-bit | bus | connector |

|-----|--------|--------|-----|-----------|

|-----|--------|--------|-----|-----------|

|          |     |     | -      |

|----------|-----|-----|--------|

| Ground   | D0  | C0  | Ground |

| MEMCS16- | D1  | C1  | SBHE-  |

| IOCS16-  | D2  | C2  | LA23   |

| IRQ10    | D3  | C3  | LA22   |

| IRQ11    | D4  | C4  | LA21   |

| IRQ12    | D5  | C5  | LA20   |

| IRQ15    | D6  | C6  | LA19   |

| IRQ14    | D7  | C7  | LA18   |

| DACK0-   | D8  | C8  | LA17   |

| DRQ0     | D9  | C9  | MEMR-  |

| DACK5-   | D10 | C10 | MEMW-  |

| DRQ5     | D11 | C11 | SD8    |

| DACK6-   | D12 | C12 | SD9    |

| DRQ6     | D13 | C13 | SD10   |

| DACK7-   | D14 | C14 | SD11   |

| DRQ7     | D15 | C15 | SD12   |

| +5V      | D16 | C16 | SD13   |

| MASTER-  | D17 | C17 | SD14   |

| Ground   | D18 | C18 | SD15   |

| Ground   | D19 | C19 | Key    |

|          |     |     |        |

DIAMOND SYSTEMS

# 4.2 PC/104-Plus PCI Bus Connector (J3)

Connector J3 provides the standard PC/104-Plus 32-bit PCI bus and is keyed for 3.3V only.

| A1  | GND/KEY5 | B1  | Reserved | C1  | +5V    | D1  | AD00     |

|-----|----------|-----|----------|-----|--------|-----|----------|

| A2  | VI/O     | B2  | AD02     | C2  | AD01   | D2  | +5V      |

| A3  | AD05     | B3  | GND      | C3  | AD04   | D3  | AD03     |

| A4  | C/BE0*   | B4  | AD07     | C4  | GND    | D4  | AD06     |

| A5  | GND      | B5  | AD09     | C5  | AD08   | D5  | GND      |

| A6  | AD11     | B6  | VI/O     | C6  | AD10   | D6  | M66EN    |

| A7  | AD14     | B7  | AD13     | C7  | GND    | D7  | AD12     |

| A8  | +3.3V    | B8  | C/BE1*   | C8  | AD15   | D8  | +3.3V    |

| A9  | SERR*    | B9  | GND      | C9  | SB0*   | D9  | PAR      |

| A10 | GND      | B10 | PERR*    | C10 | +3.3V  | D10 | Reserved |

| A11 | STOP*    | B11 | +3.3V    | C11 | LOCK*  | D11 | GND      |

| A12 | +3.3V    | B12 | TRDY*    | C12 | GND    | D12 | DEVSEL*  |

| A13 | FRAME*   | B13 | GND      | C13 | IRDY*  | D13 | +3.3V    |

| A14 | GND      | B14 | AD16     | C14 | +3.3V  | D14 | C/BE2*   |

| A15 | AD18     | B15 | +3.3V    | C15 | AD17   | D15 | GND      |

| A16 | AD21     | B16 | AD20     | C16 | GND    | D16 | AD19     |

| A17 | +3.3V    | B17 | AD23     | C17 | AD22   | D17 | +3.3V    |

| A18 | IDSEL0   | B18 | GND      | C18 | IDSEL1 | D18 | IDSEL2   |

| A19 | AD24     | B19 | C/BE3*   | C19 | VI/O   | D19 | IDSEL3   |

| A20 | GND      | B20 | AD26     | C20 | AD25   | D20 | GND      |

| A21 | AD29     | B21 | +5V      | C21 | AD28   | D21 | AD27     |

| A22 | +5V      | B22 | AD30     | C22 | GND    | D22 | AD31     |

| A23 | REQ0*    | B23 | GND      | C23 | REQ1*  | D23 | VI/O     |

| A24 | GND      | B24 | REQ2*    | C24 | +5V    | D24 | GNT0*    |

| A25 | GNT1*    | B25 | VI/O     | C25 | GNT2*  | D25 | GND      |

| A26 | +5V      | B26 | CLK0     | C26 | GND    | D26 | CLK1     |

| A27 | CLK2     | B27 | +5V      | C27 | CLK3   | D27 | GND      |

| A28 | GND      | B28 | INTD*    | C28 | +5V    | D28 | RST*     |

| A29 | +12V     | B29 | INTA*    | C29 | INTB*  | D29 | INTD*    |

| A30 | -12V     | B30 | REQ3*    | C30 | GNT3*  | D30 | GND/KEY3 |

# 4.3 Analog Output (J4)

Connector J4 brings the analog output signals to a pin header.

| Vout 0   | 1  | 2  | lout 0  |

|----------|----|----|---------|

| Agnd     | 3  | 4  | Vout 1  |

| lout 1   | 5  | 6  | Agnd    |

| Vout 2   | 7  | 8  | lout 2  |

| Agnd     | 9  | 10 | Vout 3  |

| lout 3   | 11 | 12 | Agnd    |

| Vout 4   | 13 | 14 | lout 4  |

| Agnd     | 15 | 16 | Vout 5  |

| lout 5   | 17 | 18 | Agnd    |

| Vout 6   | 19 | 20 | lout 6  |

| Agnd     | 21 | 22 | Vout 7  |

| lout 7   | 23 | 24 | Agnd    |

| Vout 8   | 25 | 26 | lout 8  |

| Agnd     | 27 | 28 | Vout 9  |

| lout 9   | 29 | 30 | Agnd    |

| Vout 10  | 31 | 32 | lout 10 |

| Agnd     | 33 | 34 | Vout 11 |

| lout 11  | 35 | 36 | Agnd    |

| Vout 12  | 37 | 38 | lout 12 |

| Agnd     | 39 | 40 | Vout 13 |

| lout 13  | 41 | 42 | Agnd    |

| Vout 14  | 43 | 44 | lout 14 |

| Agnd     | 45 | 46 | Vout 15 |

| lout 15  | 47 | 48 | Agnd    |

| Ext Trig | 49 | 50 | Dgnd    |

|          |    |    |         |

Connector type: 0.1" pitch 50-pin (2x25) dual row right-angle pin header with gold flashing.

# 4.4 Digital I/O (J5)

Connector J5 brings the 48 digital I/O signals to a pin header. These lines have 3.3V logic levels with 5V input tolerance.

| DIOA0  | 1  | 2  | DIO A1 |

|--------|----|----|--------|

| DIO A2 | 3  | 4  | DIO A3 |

| DIO A4 | 5  | 6  | DIO A5 |

| DIO A6 | 7  | 8  | DIO A7 |

| DIO B0 | 9  | 10 | Dio B1 |

| DIO B2 | 11 | 12 | DIO B3 |

| DIO B4 | 13 | 14 | DIO B5 |

| DIO B6 | 15 | 16 | DIO B7 |

| DIO C0 | 17 | 18 | DIO C1 |

| DIO C2 | 19 | 20 | DIO C4 |

| DIO C4 | 21 | 22 | DIO C6 |

| DIO C6 | 23 | 24 | DIO C7 |

| DIOD0  | 25 | 26 | DIO D1 |

| DIO D2 | 27 | 28 | DIO D3 |

| DIO D4 | 29 | 30 | DIO D5 |

| DIO D6 | 31 | 32 | DIO D7 |

| DIO E0 | 33 | 34 | Dio E1 |

| DIO E2 | 35 | 36 | DIO E3 |

| DIO E4 | 37 | 38 | DIO E5 |

| DIO E6 | 39 | 40 | DIO E7 |

| DIO F0 | 41 | 42 | DIO F1 |

| DIO F2 | 43 | 44 | DIO F4 |

| DIO F4 | 45 | 46 | DIO F6 |

| DIO F6 | 47 | 48 | DIO F7 |

| +5VDC  | 49 | 50 | Dgnd   |

Connector type: 0.1" pitch 50-pin (2x25) dual row right-angle pin header with gold flashing.

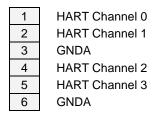

## 4.5 HART Programming Connector (J9)

Connector J9 allows communication with other devices in up to 4 HART networks when the D/A converter for channels 0 - 3 is equipped with HART functionality.

Connector type: 0.1" pitch 6-pin (1x6) single row right-angle pin header with gold flashing

# 5. BOARD CONFIGURATION

This section describes how to configure the RMM-1616AP-XT using jumper blocks J6 and J8.

### 5.1 Base Address

The board's base address is set with jumper block J8. The jumper locations labeled A9 – A6 are used for the base address. These lines correspond to ISA bus address lines SA9 – SA4. The lowest 4 address bits, SA3 – SA0, are assumed to be 0 for the base address. The upper address lines SA15 – SA10 are always decoded as 0 for the base address. The following table lists the valid base address settings. When a jumper is installed, the corresponding address line must be 0, and when a jumper is removed, the corresponding address line must be 1. Addresses below 100 hex are considered invalid and should not be configured. Valid base addresses are shown in the table below.

|     |           |     |     | Base    |         |

|-----|-----------|-----|-----|---------|---------|

| A9  | <b>A8</b> | A7  | A6  | Address |         |

| In  | Out       | In  | In  | 100     |         |

| In  | Out       | In  | Out | 140     |         |

| In  | Out       | Out | In  | 180     |         |

| In  | Out       | Out | Out | 1C0     |         |

| Out | In        | In  | In  | 200     |         |

| Out | In        | In  | Out | 240     |         |

| Out | In        | Out | In  | 280     |         |

| Out | In        | Out | Out | 2C0     |         |

| Out | Out       | In  | In  | 300     | default |

| Out | Out       | In  | Out | 340     |         |

| Out | Out       | Out | In  | 380     |         |

| Out | Out       | Out | Out | 3C0     |         |

|     |           |     |     |         |         |

### 5.2 IRQ Selection

The ISA bus interrupt level for the interrupt on change of state function is selected with jumper block J6 from among levels 3, 4, 5, 6, 7, 9, 10, 11, 12, and 15. The 1K ohm pull-down resistor is also enabled with jumper position PD on jumper block J6. The default is IRQ 7.

### 5.3 Digital I/O Logic Level

The logic level for the digital I/O can be set to either +5V or +3.3V on jumper block J8 using either the 5V or 3V jumper location. The default is +5V.

## 5.4 Digital I/O Pull-Up/Down

The digital I/O lines are tied to pull-up/down resistors which may be jumpered to either +3.3V or ground using locations UP or DN on jumper block J8 respectively. The default is pull-up to +3.3V.

## 5.5 PCI Slot ID

The PCI slot ID has two jumpers, SL1 and SL0, on jumper block J8. These are used to select 1 of 4 PCI slots for configuration purposes per the table below. The default is no jumpers installed to set PCI slot ID=00.

### 5.6 Auto Bus Select

The Ruby-MM-1616 can be set in auto-bus select mode, meaning that models with the PC/104-*Plus* connectors communicate over the PCI bus and models with only the PC/104 connector communicate over the ISA bus. This is the default configuration and is set by the PCI jumper on jumper block J8. If this jumper is removed, the board with always communicate over the ISA bus.

### 5.7 D/A Converter Power On Clear

When jumper POC on jumper block J8 is installed, and the power to the board is cycled, the D/A converter clear their outputs to 0V. The default configuration is power on clear enabled with a jumper installed on POC.

#### DIAMOND SYSTEMS

# 6. THEORY OF OPERATION

This chapter provides an orientation to the functional architecture of the board. Additional details are in the register programming section and specific chapters on various blocks.

### 6.1 Analog Functionality

#### 6.1.1 D/A Functions

The RMM-1616AP-XT provides up to 16 16-bit analog voltage or current outputs derived from the Analog Devices AD5755-1 chips (4 outputs per chip). Output ranges are programmable for each chip (4 outputs) using a precision reference circuit on the board plus a precision resistor ladder network.

The outputs may be updated in simultaneous mode or in single channel mode. Simultaneous mode works across all channels in use, i.e. up to 16 channels if desired. In simultaneous update mode, the data for each channel is written to the channel's DAC, and then a single update command causes all selected channels to update simultaneously. In single channel update mode, a single channel can be updated at any time.

The voltage outputs are powered by an on-board discrete DC/DC power supply with a capacity of at least 200mA at +/-15V or 6 watts. They are not isolated from system ground. However the analog side of the board has a separated ground plane that is connected to the digital ground plane at a single point at the DC/DC supply. The current outputs are powered by supplies integrated into the AD5755-1 chip and powered by the board's main 5V supply.

Provision is made to mount an optional heat sink on the board to improve cooling for the AD5755-1 chips in the case of high power current output operating conditions using the mounting holes located vertically between the D/A converter ICs.

There is a jumper block that enables the power on clear (POC) when installed whenever the board is powered up.

#### 6.1.2 Waveform Generator Circuit

Up to 4 channels (channel numbers 0-3) can be programmed for output waveform capability. A waveform for each channel is downloaded to a waveform table in the FPGA. A counter/timer may be programmed for the desired data rate, or the samples may be controlled by an external trigger or a software command. Each trigger event will cause the next sequential value or set of values in the waveform table to be output for each selected channel. Output update is simultaneous for all waveform-enabled channels.

The maximum update rate is at least 100KHz per channel. The waveform table depth is at least 512 16-bit samples per D/A channel.

When waveform generation is enabled, the D/A outputs do not change. On the first clock pulse, the first value in the waveform table(s) is/are output to the corresponding D/A channel(s).

#### 6.1.3 D/A Calibration

The D/A calibration circuitry uses calibration registers for each channel inside the D/A converter ICs. Although this can eliminate the need for trim circuitry the drawback is the possible loss of LSB steps at the ends of the digital-to-analog transfer function, resulting in D/A codes that are invalid because of offset and scale adjustments. If this turns out to be a problem or there is a need for nonstandard D/A ranges, trim circuitry that includes the use of TrimDACs is included for each bank of 4 D/A channels to allow for hardware trimming or nonstandard D/A ranges for groups of 4 channels. All calibration settings are stored in an on-board EEPROM for instant automatic recall each time the board powers up. All analog outputs power up to 0V for safety.

## 6.2 Digital I/O Functionality

An FPGA on the board provides the main control of all functions and also is the source of all digital I/O and counter/timer features. It includes the waveform buffer for the D/A waveform generator function.

The FPGA is a flash-based device that loads its program from an internal flash memory during power-up. During this loading time the I/O pins are not driven, so all I/O pins that affect the I/O connectors must have external pull-up or pull-down resistors to drive them to their inactive states to prevent oscillations, glitches, short circuits, or other undesirable behavior.

#### 6.2.1 Digital I/O

The board offers 48 digital I/O lines grouped into 6 8-bit ports. 5 ports have their directions programmable for the entire 8-bit port, and one port has its direction programmable bit by bit. All ports have 5V or 3.3V selectable input and output logic levels. All I/O lines have pull-up/down resistors with jumper-selectable polarity. On power up, all I/O lines are in input mode and the I/O pins are pulled to the selected logic level. When a port is programmed for output mode, its initial state is all zeroes, resulting in an output of "0V" on all lines for that port. For parallel I/O with latching, DIO port F has the latch and acknowledge signals for handshaking operations when enabled.

#### 6.2.2 Counter/Timers

The FPGA design includes 2 32-bit programmable counter/timers that can be used to control D/A waveform output or programmable interrupts. DIO port F has optional control inputs and outputs that can connect to the counter/timers for external timer applications when enabled.

#### 6.2.3 Pulse Width Modulators

The FPGA design includes 4 24-bit PWM circuits that have outputs connected to DIO port F when enabled.

# 7. REGISTER MAP

### 7.1 I/O Map Summary

The register map consists of 8 16-byte pages that are accessed via a 16-byte window on the ISA I/O address space or the PCI I/O address space depending on the state of the bit P\_BUSSEL (0 = PCI, 1 = ISA). Each block is a (mostly) standalone functional block, although there is some interconnectedness in functionality, such as counter control of A/D and D/A timing or multiplexing control signals onto digital I/O pins. Not all bits or all registers in each page are defined.

| Block | Range Dec | Range Hex | Function                    |  |

|-------|-----------|-----------|-----------------------------|--|

| 0     | 0-15      | 0-F       | Not Used                    |  |

| 1     | 16-31     | 10-1F     | D/A                         |  |

| 2     | 32-47     | 20-2F     | DIO                         |  |

| 3     | 48-63     | 30-3F     | Counters                    |  |

| 4     | 64-79     | 40-4F     | Not Used                    |  |

| 5     | 80-95     | 50-5F     | EEPROM                      |  |

| 6     | 96-111    | 60-6F     | Not Used                    |  |

| 7     | 112-127   | 70-7F     | Interrupts, Misc., and ID   |  |

| 8     | 128-143   | 80-8F     | Not Used                    |  |

| 9     | 144-159   | 90-9F     | Not Used                    |  |

| 10    | 160-175   | A0-AF     | Not Used                    |  |

| 11    | 176-191   | B0-BF     | Not Used                    |  |

| 12    | 192-207   | C0-CF     | Not Used                    |  |

| 13    | 208-223   | D0-DF     | Not Used                    |  |

| 14    | 224-239   | E0-EF     | Not Used                    |  |

| 15    | 240-255   | F0-FF     | Capabilities / Page Control |  |

# 7.2 PCI Configuration Space Usage

The base address of the PCI I/O space is defined by the contents of the Base Address Register A (BARA) in the PCI configuration space block.

| 1      |     |                                            |      |

|--------|-----|--------------------------------------------|------|

| BASE + | R/W | REGISTER NAME                              | USED |

| 0      | R   | PCI Device / Vendor ID                     | YES  |

| 4      | R/W | PCI Command / Status                       | YES  |

| 8      | R   | PCI Class Code / Revision ID               | YES  |

| 12     | R/W | BIST, Header Type, Latency and Cache       | YES  |

| 16     | R/W | Base Address Register 0 (BAR0)             | YES  |

| 20     | R/W | Base Address Register 1 (BAR1)             | NO   |

| 24     | R/W | Base Address Register 2 (BAR2)             | NO   |

| 28     | R/W | Base Address Register 3 (BAR3)             | NO   |

| 32     | R/W | Base Address Register 4 (BAR4)             | NO   |

| 36     | R/W | Base Address Register 5 (BAR5)             | NO   |

| 40     | R/W | Cardbus CIS Pointer                        | NO   |

| 44     | R   | Subsystem ID, Subsystem Vendor ID Register | YES  |

| 48     | R/W | Expansion ROM Base Register                | NO   |

| 52     | N/A | RESERVED                                   | NO   |

| 56     | N/A | RESERVED                                   | NO   |

| 60     | R/W | Latency, Grant and Interrupt Register      | YES  |

NOTES:

- 1. The address range of the register BAR0 (Offset 16) is set at 256 bytes.

- 2. The addressing logic to the operational register map is to consist of adding an offset to the contents of the BAR0 register to generate the actual address of the register to be accessed.

- 3. The Vendor ID (Offset 0) is to defined as 0xnnnn.

- 4. The Device ID (Offset 2) is to be defined as 0x0A00.

# 7.3 D/A Block (page 1)

The D/A block is designed to work with the Analog Devices AD5755(-1) D/A converter. It includes an arbitrary waveform generator for up to 8 channels.

| Offset | 7       | 6       | 5       | 4          | 3           | 2       | 1       | 0       |  |

|--------|---------|---------|---------|------------|-------------|---------|---------|---------|--|

| 0 (W)  |         | DA7-0   |         |            |             |         |         |         |  |

| 0 (R)  |         |         |         | D/A statu  | s bits 7-0  |         |         |         |  |

| 1 (W)  |         |         |         | DA         | 15-8        |         |         |         |  |

| 1 (R)  |         |         |         | D/A status | s bits 15-8 |         |         | -       |  |

| 2      | RD/~WR  | DA_D1   | DA_D0   | DA_R2      | DA_R1       | DA_R0   | DA_A1   | DA_A0   |  |

| 3      |         |         |         |            |             |         |         |         |  |

| 4      | DAOSYND | DAOSYNC | DAOSYNB | DAOSYNA    | DAOLDD      | DAOLDC  | DAOLDB  | DAOLDA  |  |

| 5      | DAOVRD  |         |         |            |             |         |         | DASIM   |  |

| 6 (C)  | DASIMUP |         |         |            | DALDD       | DALDC   | DALDB   | DALDA   |  |

| 6 (R)  | DAWAIT  |         |         |            |             |         |         |         |  |

| 7 (C)  | DARESET |         |         |            | DACLRD      | DACLRC  | DACLRB  | DACLRA  |  |

| 7 (R)  | DABUSYD | DABUSYC | DABUSYB | DABUSYA    | FAULTD      | FAULTC  | FAULTB  | FAULTA  |  |

| 8      | WGBA7   | WGBA6   | WGBA5   | WGBA4      | WGBA3       | WGBA2   | WGBA1   | WGBA0   |  |

| 9      | WGCH3   | WGCH2   | WGCH1   | WGCH0      |             | WGBA10  | WGBA9   | WGBA8   |  |

| 10     | WGCYCLE |         | WGFR3   | WGFR2      | WGFR1       | WGFR0   | WGSRC1  | WGSRC0  |  |

| 11     |         |         |         |            | WGINC       | WGRESET | WGPAUSE | WGSTART |  |

| 12     | WGFRC7  | WGFRC6  | WGFRC5  | WGFRC4     | WGFRC3      | WGFRC2  | WGFRC1  | WGFRC0  |  |

| 13     |         |         |         |            | WGFRC11     | WGFRC10 | WGFRC9  | WGFRC8  |  |

| 14     | DADLY7  | DADLY6  | DADLY5  | DADLY4     | DADLY3      | DADLY2  | DADLY1  | DADLY0  |  |

| 15     |         |         |         |            | PAGE3       | PAGE2   | PAGE1   | PAGE0   |  |

# 7.4 Digital I/O Block (page 2)

The DIO circuit contains 5 8-bit ports with byte-wide direction control and one 8-bit port with individual bit direction control. Register 8 is added to multiplex special functions onto port E.

| Offset | 7     | 6       | 5     | 4     | 3      | 2      | 1      | 0      |  |

|--------|-------|---------|-------|-------|--------|--------|--------|--------|--|

| 0      |       | DIOA7-0 |       |       |        |        |        |        |  |

| 1      |       |         |       | DIO   | B7-0   |        |        |        |  |

| 2      |       |         |       | DIO   | C7-0   |        |        |        |  |

| 3      |       |         |       | DIO   | D7-0   |        |        |        |  |

| 4      |       |         |       | DIO   | E7-0   |        |        |        |  |

| 5      |       | DIOF7-0 |       |       |        |        |        |        |  |

| 6 (W)  |       |         |       | PORT2 | PORT1  | PORT0  | MODE   | DIR    |  |

| 6 (R)  |       |         |       |       | LATCHD | LATCHC | LATCHB | LATCHA |  |

| 7      | DIRF7 | DIRF6   | DIRF5 | DIRF4 | DIRF3  | DIRF2  | DIRF1  | DIRF0  |  |

| 8      | SF7   | SF6     | SF5   | SF4   | SF3    | SF2    | SF1    | SF0    |  |

| 9      |       |         |       |       |        |        |        |        |  |

| 10     |       |         |       |       |        |        |        |        |  |

| 11     |       |         |       |       |        |        |        |        |  |

| 12     |       |         |       |       |        |        |        |        |  |

| 13     |       |         |       |       |        |        |        |        |  |

| 14     |       |         |       |       |        |        |        |        |  |

| 15     |       |         |       |       | PAGE3  | PAGE2  | PAGE1  | PAGE0  |  |

# 7.5 Counter and PWM Block (page 3)

The counter block contains 2 32-bit counters and 4 24-bit PWMs.

| Offset | 7       | 6       | 5       | 4       | 3      | 2     | 1     | 0     |  |  |

|--------|---------|---------|---------|---------|--------|-------|-------|-------|--|--|

| 0      |         | CTRD7-0 |         |         |        |       |       |       |  |  |

| 1      |         |         |         | CTRE    | D15-8  |       |       |       |  |  |

| 2      |         |         |         | CTRD    | 23-16  |       |       |       |  |  |

| 3      |         |         |         | CTRD    | 31-24  |       |       |       |  |  |

| 4 (W)  |         |         |         | CTR     | N7-0   |       |       |       |  |  |