# CML147786CX cpuModule™User's Manual

**RTD Enhanced Award BIOS Versions 6.00.xx**

$> \sqrt{}$ (Real Time Devices) ||||W|

RTD Embedded Technologies, Inc.

"Accessing the Analog World"®

ISO9001 and AS9100 Certified

BDM-610000059 Rev C

CML147786CX cpuModule<sup>™</sup> User's Manual

**RTD Embedded Technologies, Inc.** 103 Innovation Blvd. State College, PA 16803-0906

> Phone: +1-814-234-8087 FAX: +1-814-234-5218

<u>E-mail</u> sales@rtd.com techsupport@rtd.com

web site http://www.rtd.com

#### **Revision History**

| Rev A | Initial Release                                                                                                                                                                      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev B | Added <i>Quick Boot Description</i> on page 57. Added <i>Onboard PCI Devices</i> on page 93. Revised <i>Real Time Clock and CMOS Memory</i> on page 81. Updated board diagrams.      |

| Rev C | Updated Mechanical Drawing in <i>Mechanical Dimensions</i> on page 94. Added EIDE specifications to <i>Specifications</i> on page 6. Updated <i>Operating environment</i> on page 8. |

Published by:

RTD Embedded Technologies, Inc. 103 Innovation Blvd. State College, PA 16803-0906

Copyright 2002-2007 by RTD Embedded Technologies, Inc. All rights reserved Printed in U.S.A.

The RTD Logo is a registered trademark of RTD Embedded Technologies. cpuModule and utilityModule are trademarks of RTD Embedded Technologies. PS/2, PC/XT, PC/AT and IBM are trademarks of International Business Machines Inc. MS-DOS, Windows, Windows 95, Windows 98 and Windows NT are trademarks of Microsoft Corp. PC/104 is a registered trademark of PC/104 Consortium. All other trademarks appearing in this document are the property of their respective owners.

| Chapter 1: | Introduction                                        | 3  |

|------------|-----------------------------------------------------|----|

|            | The CML147786CX cpuModule                           |    |

|            | Specifications                                      | 0  |

| Chapter 2: | Getting Started                                     | 9  |

|            | Basic Connector Locations                           | 10 |

|            | Fail safe boot ROM                                  |    |

|            | Cable Kits                                          | 12 |

|            | Connecting Power                                    | 13 |

|            | Connecting the utility cable                        | 14 |

|            | Connecting a Keyboard                               | 15 |

|            | Connecting to the PC/104 Bus                        | 16 |

|            | Connecting to the PC/104-Plus PCI Bus               | 17 |

|            | Booting the cpuModule for the First Time            |    |

|            | Booting to Boot Block Flash with Fail Safe Boot ROM |    |

|            | If You Misconfigure the cpuModule                   |    |

|            | For More Information                                | 22 |

| Chapter 3: | Connecting the cpuModule                            | 23 |

|            | Connector Locations                                 |    |

|            | Auxiliary Power CN3                                 |    |

|            | Serial Ports, CN7 and CN8                           |    |

|            | multiPort, CN6 - Parallel Port Mode                 |    |

|            | multiPort, CN6 - aDIO Mode                          |    |

|            | multiPort, CN6 - Floppy Controller Mode             |    |

|            | Multifunction Connector, CN5                        | 35 |

|            | VGA Video Connector, CN18                           | 37 |

|            | TTL Flat Panel Video Connector, CN19                | 38 |

|            | EIDE Connector, CN9                                 |    |

|            | ATA/IDE Disk Chip Socket, U8                        | 41 |

|            | Bus Mouse Connector, CN4                            |    |

|            | USB Connector, CN17                                 |    |

|            | 10/100 Base T and TX Connector, CN20                |    |

|            | Audio, CN11                                         |    |

|            | PC/104 Bus, CN1 and CN2                             |    |

|            | PC/104-Plus PCI Bus, CN16                           | 51 |

| Chapter 4: | Configuring the cpuModule (BIOS Setup)              | 55 |

|            | Disabling Fail Safe Boot ROM                        | 56 |

|            | Quick Boot Description                              |    |

|            | Configuring with the RTD Enhanced Award BIOS        |    |

| Chapter 5: | Using the cpuModule                                 | 59 |

|            | Memory Map                                          |    |

|            | Input/Output Address Map                            |    |

|            | Hardware Interrupts                                 |    |

|            | The RTD Enhanced Award BIOS                         |    |

|            | Thermal Throttling                           | .66  |

|------------|----------------------------------------------|------|

|            | Direct Hardware Control                      | .67  |

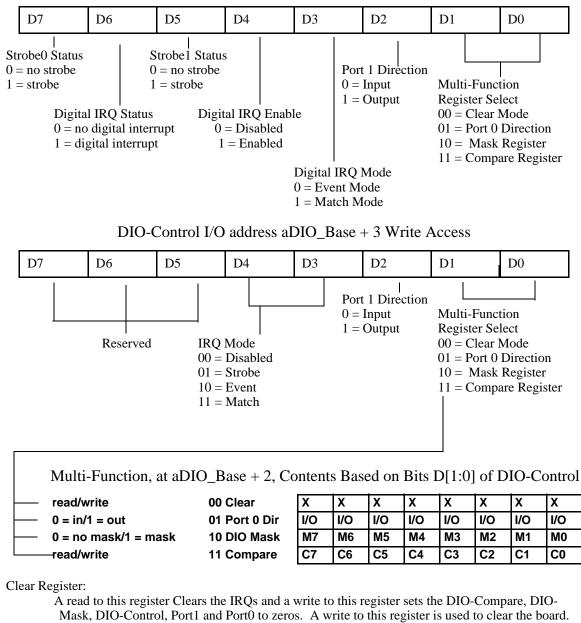

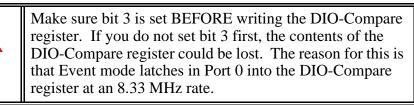

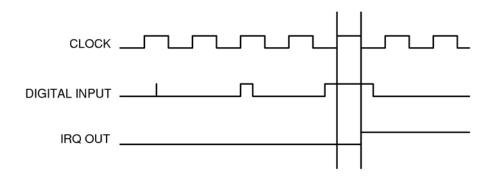

|            | Advanced Digital I/O Ports (aDIO)            | .68  |

|            | Basic Interrupt Information for Programmers: | .74  |

|            | Watchdog Timer Control                       |      |

|            | Multi-Color LED                              |      |

|            | Real Time Clock and CMOS Memory              | .81  |

|            | Parallel Port Control                        |      |

|            | Storing Applications On-board                |      |

|            | Configuring the ATA/IDE Disk Chip Socket     | .86  |

| Chapter 6: | Hardware Reference                           | 87   |

|            | Jumpers and Solder Jumper Settings           | .88  |

|            | Onboard PCI Devices                          |      |

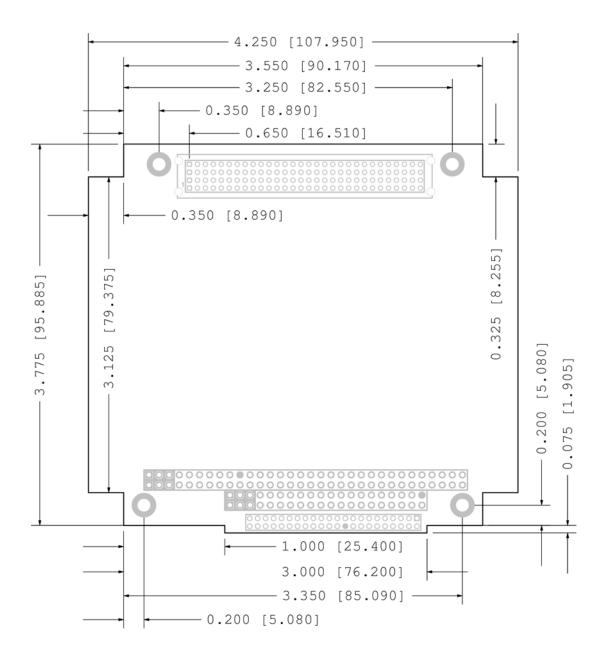

|            | Mechanical Dimensions                        | .94  |

|            | Processor Thermal Management                 | .95  |

| Chapter 7: | Troubleshooting                              | 97   |

|            | Common Problems and Solutions                | .98  |

|            | Troubleshooting a PC/104 System              | .101 |

|            | How to Obtain Technical Support              |      |

| Chapter 8. | Limited Warranty                             | 103  |

# Table Of Figures

| CML147786CX Block Diagram             | 5  |

|---------------------------------------|----|

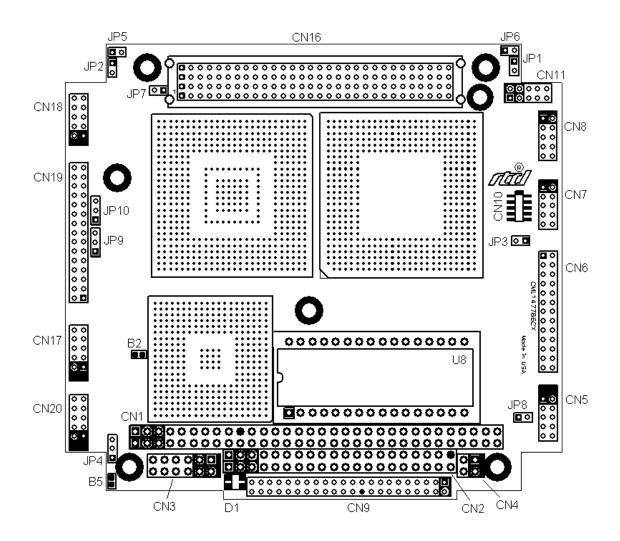

| CML147786CX Basic Connector Locations |    |

| CML147786CX Connector Locations       | 24 |

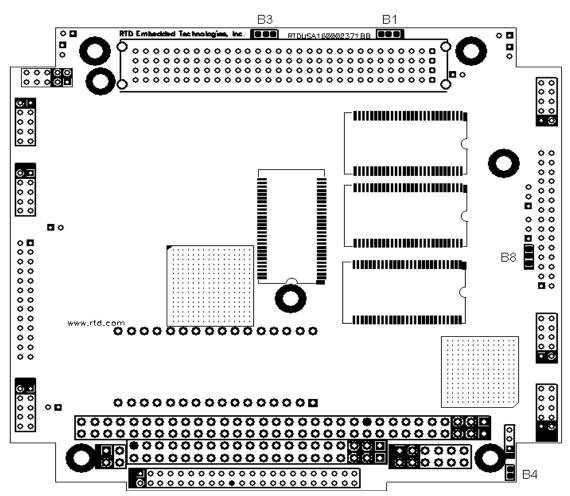

| CML147786CX Jumper Locations - Top    |    |

| CML147786CX Jumper Locations - Bottom | 90 |

## **Table Of Tables**

| Power Consumption                                   |     |

|-----------------------------------------------------|-----|

| CML147786CX Connectors                              | .25 |

| Auxiliary Power Connector CN3                       | .26 |

| Serial Port Base Address and IRQ Options            | .28 |

| Serial Port in RS-232 Mode                          | .28 |

| RS-422 Serial Port Connections                      | .29 |

| RS-485 Serial Port Connections                      | .29 |

| Serial Port in RS-422/485 Mode                      |     |

| multiPort Parallel Port Connector Pinout CN6        | .31 |

| multiPort Advanced Digital I/O Connector Pinout CN6 | .32 |

| multiPort Connector Floppy Pinout CN6               |     |

| Multifunction Connector CN5                         |     |

| Keyboard Connector Pins on CN5                      | .36 |

| VGA Video Connector CN18                            | .37 |

| Supported Video Resolutions and BIOS Settings       | .37 |

| TTL Flat Panel Video Connector CN19                 | .38 |

| EIDE Connector CN9                                  |     |

| ATA/IDE Disk Chip Socket U8                         | .41 |

| Bus Mouse Connector CN4                             | .43 |

| USB Connector CN17                                  | .44 |

| 10/100 Base T and TX Connector CN20                 | .45 |

| Audio Connector CN11                                | .46 |

| PC/104 XT Bus Connector, CN1                        | .47 |

| PC/104 AT Bus Connector, CN2                        | .48 |

| PC/104 Bus Signals                                  | .48 |

| PC/104-Plus Bus Signal Assignments                  | .51 |

| BIOS Setup Utility Keys                             | .58 |

| First Megabyte Memory Map                           | .60 |

| I/O Addresses Reserved for the cpuModule            | .61 |

| Hardware Interrupts Used on the cpuModule           | .63 |

| LED Colors                                          |     |

| Manual LED Colors                                   | .80 |

| Real Time Clock Registers                           | .81 |

| Jumpers and Default Settings                        | .91 |

| Solder Jumpers and Default Settings                 | .91 |

| Onboard PCI Devices                                 | .93 |

# **CHAPTER 1: INTRODUCTION**

This manual is meant for users developing with the CML147786CX cpu-Module. It contains information on hardware and software of the cpu-Module.

READ THE SPECIFICATIONS FIRST.

The manual is organized as follows:

| Chapter 1: | Introduction                                                                                                                                                                                                                                       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Introduces main features and specifications.                                                                                                                                                                                                       |

| Chapter 2: | Getting Started                                                                                                                                                                                                                                    |

|            | Provides abbreviated instructions to get started.                                                                                                                                                                                                  |

| Chapter 3: | Connecting the cpuModule                                                                                                                                                                                                                           |

|            | Provides information on connecting the cpuModule to peripherals.                                                                                                                                                                                   |

| Chapter 4: | Configuring the cpuModule                                                                                                                                                                                                                          |

|            | Provides information on configuring hardware and software.                                                                                                                                                                                         |

| Chapter 5: | Using the cpuModule                                                                                                                                                                                                                                |

|            | Provides information needed to develop applications for the cpuModule.<br>The chapter includes general information on the cpuModule, plus de-<br>tailed information on storing applications and system functions, and us-<br>ing utility programs. |

| Chapter 6: | Hardware Reference                                                                                                                                                                                                                                 |

|            | Lists jumpers and their locations and mechanical dimensions.                                                                                                                                                                                       |

| Chapter 7: | Troubleshooting                                                                                                                                                                                                                                    |

|            | Offers advice on debugging problems with your system.                                                                                                                                                                                              |

| Chapter 8: | Warranty                                                                                                                                                                                                                                           |

### The CML147786CX cpuModule

The PC/104 cpuModules described in this manual are designed for industrial applications which require:

- software and hardware compatibility with the PC/AT world

- high-speed "number-crunching" operation

- low power consumption

- small physical dimensions

- high reliability

- good noise immunity

This cpuModule is highly integrated, combining all major functions of a PC/AT computer on one compact board. It integrates all primary I/O functions of a AT compatible computer:

- SVGA controller

- Analog SVGA output

- 18 bit Digital TFT Output

- UltraDMA 33/66/100 EIDE Controller

- a keyboard interface

- parallel port

- two versatile RS232/422/485 serial ports

- a Real Time Clock

- a speaker port

- a PS/2 mouse port

- two USB ports

- AC97 and Sound Blaster compatible audio port

- One twisted pair 10/100 Base T and TX connection based on an Intel 82559ER PHY

It also enhances standard AT-compatible computer systems by adding:

- ATA/IDE Disk Chip socket

- Non-volatile configuration without a battery

- Watchdog Timer

- Fail Safe Boot ROM

- A multiPort that can be configured as an ECP/EPP Parallel Port, 18 bit digital I/O, or Floppy Drive port

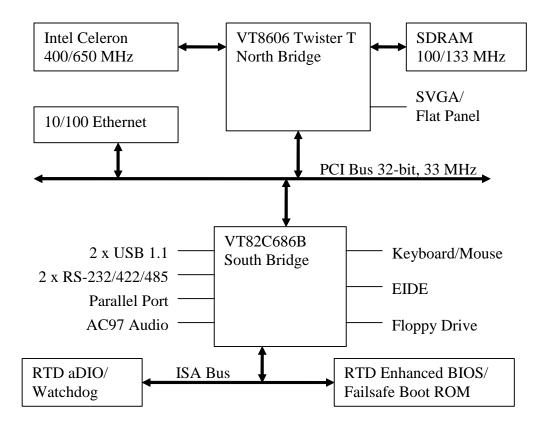

A simplified block diagram of the cpuModule is shown in Figure 1

#### Figure 1: CML147786CX Block Diagram

You can easily customize the cpuModule by stacking PC/104 modules such as video controllers, modems, LAN controllers, or analog and digital data acquisition modules. Stacking PC/104 modules on the cpuModule avoids expensive installations of backplanes and card cages and preserves the module's compactness.

RTD Enhanced Award BIOS is also implemented in the cpuModule. This BIOS supports ROM-DOS<sup>TM</sup>, MS-DOS, Linux, and Windows operating systems. Drivers in the BIOS allow booting from floppy disk, hard disk, ATA/IDE Disk Chip, or boot block flash, thus enabling the system to be used with traditional disk drives or non-mechanical drives.

The cpuModule and BIOS are also compatible with most real-time operating systems for PC compatible computers, although these may require creation of custom drivers to use the watchdog timer.

### **Specifications**

### CML147786CX

- Intel Celeron CPU with Twister-T Chipset

- 400 MHz to 650 MHz clock speed.

- 0.95/1.10 V processor supply (provided on-board)

- 32 kB L1 Cache

- 256 kB L2 Cache

- Math coprocessor

- 100 MHz Front Side Bus

#### **Memory Configurations**

- 66/100/133 MHz SDRAM (selectable in BIOS)

- Available Memory Sizes:

- 32MB

- 128MB

- 256MB

- 512MB

#### Video Controller

- AGP S3 Savage SVGA Controller

- Analog SVGA Output

- 18 bit TTL Digital TFT Output

- 2 / 4 / 8 / 16 / 32 MB Frame Buffer

#### **DMA**, Interrupts, Timers

- Six (6) DMA channels (8237 compatible)

- Fifteen (15) interrupt channels (8259 compatible)

- Three (3) counter/timers (8254 compatible)

- Advanced Programmable Interrupt Controller (APIC)

#### **USB** ports

- 2 USB 1.1 ports

- Boot to USB devices

- Floppy

- Hard Drive

- CD-ROM

- Flash Key

- ZIP Drive

#### Ultra-DMA 100/66/33 EIDE Controller

- Transfer rate up to 100M/sec using UltraDMA.

- Support ATAPI compliant devices including DVD drives.

- 48-bit LBA support for hard drives larger than 137 GB (Support up to 2.2 tera-Bytes)

### Advanced Digital I/O (aDIO)

- Two 8 bit, TTL compatible, programmable Digital I/O Ports plus two Strobe inputs.

- One port is bit direction programmable and the other is byte direction programmable.

- Advanced Interrupt modes

- Interrupt on change

- Interrupt on match

- Interrupt on strobe

#### Watchdog Timer

- Selectable reset time-out of 2sec, 1sec, 0.75 sec., 0.50 sec.

- Can generate an interrupt after 1sec, 0.75 sec., 0.50 sec., 0.25 sec.

- Watchdog Refresh and Active registers are accessible from Window

#### Fail-safe Boot ROM

- Surface mount Flash chip that holds ROM-DOS<sup>™</sup>

- Provides an operating system with nothing else attached

#### ATA/IDE Disk Chip Socket

- 32 pin ATA/IDE Disk Chip Socket supports miniature ATA/IDE Flash Disk Chips

- Supports capacities up to 4GB<sup>1</sup>

- Natively supported by all major operating systems

#### Peripherals

- Two serial ports software configurable for RS232/422/485

- Baud rates from 50 to 115200 baud.

- Parallel port with SPP, ECP, EPP capability and selectable interrupts and DMA channel

- PC/AT standard keyboard port

- A PS/2 mouse port

- PC speaker port

- Real Time Clock (requires user-supplied external battery for date and time backup)

#### BIOS

- RTD Enhanced Award BIOS

- User-configurable using built-in Setup program

- Nonvolatile configuration without a battery

- Can boot from floppy disk, hard disk, ATA/IDE Disk Chip, fail-safe boot ROM, or USB.

#### Connections

- AT bus, per PC/104 specifications (64-pin CN1, 40-pin CN2)

- PCI bus, per PC/104-Plus specifications (120-pin CN16)

- Auxiliary Power Connector (12-pin CN3)

- PS/2 Mouse Connector (4-pin CN4)

- Multifunction connector (10-pin CN5)

- multiPort connector (26-pin CN6)

- Serial port 1 connector (10-pin CN7)

- Serial port 2 connector (10-pin CN8)

- SVGA Monitor connector (10-pin CN18)

- TTL Flat Panel connector (30-pin CN19)

- Dual USB port connector(10-pin CN17)

- EIDE Hard Drive Connector (44-pin CN9)

- 10/100 Base T and TX connector(10-pin CN18)

- AC97 Audio input and output (10-pin CN11)

- CMOS Battery Connector (2-pin JP8)

- Fan Power Connectors (2-pin JP3 and JP7)

#### **Physical Characteristics**

- Dimensions: 4.25 x 3.850 x 0.6 inches (108.0 x 97.8 x 16mm)

- Weight (mass): 4.5 ounces (130 grams)

- PCB: 14-layer, mixed surface-mount and through-hole

<sup>&</sup>lt;sup>1.</sup> During the time of this manual's publication, 4GB was the largest available ATA/IDE Disk Chip capacity.

#### **Operating environment**

- Power supply: 5V +/- 5%, 20 Watts

- Operating temperature: -40 to +85 degrees C case (with proper cooling) See *Processor Thermal Management* on page 105

- Storage temperature: -55 to +125 degrees C.

- Operating relative humidity: 0 to 95%, non-condensing

#### **Power Consumption**

Exact power consumption depends on the peripherals connected to the board, the selected ATA/IDE Disk Chip configuration and the memory configuration.

The table below lists power consumption for typical configurations and clock speeds:

| Module      | Speed   | RAM         | Disk Chip | Consumption,<br>Typical | Consumption<br>Maximum |

|-------------|---------|-------------|-----------|-------------------------|------------------------|

| CML147786CX | 400 MHz | 32 - 512 MB | None      | 7.6 W                   | 11.6 W                 |

| CML147786CX | 650 MHz | 32 - 512 MB | None      | 9.1 W                   | 14.5 W                 |

### **Table 1: Power Consumption**

## **CHAPTER 2: GETTING STARTED**

For many users, the factory configuration of the cpuModule can be used to get a PC/104 system operational. If you are one of these users, you can get your system up and running quickly by following a few simple steps described in this chapter. Briefly, these steps are:

- Connect power.

- Connect the utility cable.

- Connect a keyboard.

- Default BIOS Configuration

- Fail Safe Boot ROM

- Connect a VGA monitor to the SVGA connector.

Refer to the remainder of this chapter for details on each of these steps.

### **Basic Connector Locations**

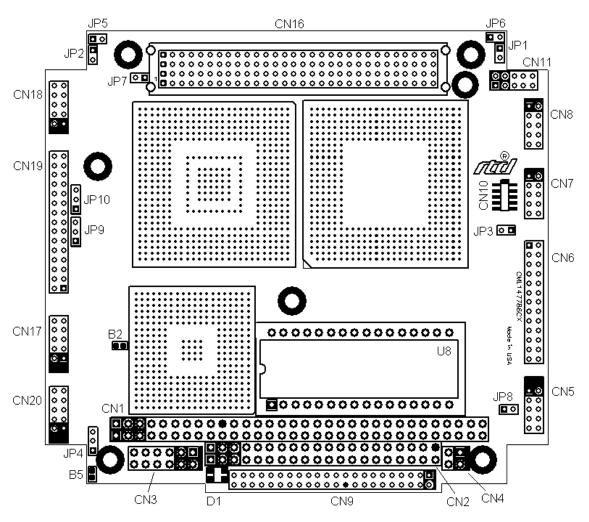

The following figure and table show the connectors used in this chapter

Figure 2: CML147786CX Basic Connector Locations

For a complete listing of connectors, please refer to Connector Locations on page 24.

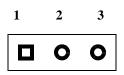

| Pin 1 of each connector is indicated by a square solder pad<br>on the bottom of the PC board and a white square silk- |

|-----------------------------------------------------------------------------------------------------------------------|

| screened on the top of the board.                                                                                     |

CML147786CX

### Fail safe boot ROM

Fail Safe Boot ROM is supplied with the board. This feature is programmed into a surface mount flash chip. The programmed boot ROM is ROM-DOS<sup>TM</sup>. Fail Safe Boot ROM allows the system to boot without any attached storage devices. i.e. floppy, IDE, ATA/IDE Disk Chip. Installing jumper JP5 will force the cpuModule to use fail safe boot ROM, as well as load the default BIOS settings. This configuration allows you to boot to non-volatile onboard ROM-DOS<sup>TM</sup>.

### **Cable Kits**

For maximum flexibility, cables are not provided with the cpuModule. You may wish to purchase our cable kit for the cpuModule.

The XK-CM43 cable kit contains the following:

- Utility Board Cable (keyboard, mouse, battery, reset, speaker, SVGA, COM ports, Multi-٠ Function Port)

- .

- ٠

- IDE Cable (for 3.5" Hard Drive) IDE Cable (for 2.5" Hard Drive) 10/100 base T and TX (10 Pin DIL TO RJ-45) ٠

- Audio Adapter (10 Pin DIL to 3 mini-jack connectors) ٠

- Power cable (DIL12 to wire leads) ٠

- Dual USB cable •

### **Connecting Power**

| WARNING! | If you improperly connect power, the module will almost                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------------------------|

|          | certainly be <i>damaged</i> or <i>destroyed</i> . Such damage is not warranted! Please verify connections to the module <i>before</i> |

|          | applying power.                                                                                                                       |

Power is normally supplied to the cpuModule through the PC/104 bus, connectors CN1 and CN2. If you are placing the cpuModule onto a PC/104 stack that has a power supply, you do not need to make additional connections to supply power.

If you are using the cpuModule without a PC/104 stack or with a stack that does not include a power supply, refer to *Auxiliary Power CN3* on page 26 for more details.

### Connecting the utility cable

The Multifunction connector, CN5, implements the following interfaces:

- AT keyboard

- Speaker output

- System reset input

- Battery input

To use these interfaces, you must connect to the Multifunction connector, making sure the orientation of pin 1 is correct. If you are using the Multifunction cable from our cable kit, the cable provides a small speaker, a 5-pin PS/2 connector for the keyboard, a push-button for resetting the PC/104 system, and a lithium battery to provide backup power to the Real Time Clock.

To connect individual devices to the Multifunction connector, please see *Multifunction Connector*, *CN5* on page 35.

### Connecting a Keyboard

You may plug a PC/AT compatible keyboard directly into the circular DIN connector of the Multifunction cable in our cable kit. The cable kit uses a "mini-DIN," or PS/2 style keyboard connector.

| NOTE! | Some older keyboards use a larger DIN connector; you will<br>need an adapter to plug these keyboards into the cpuMod-<br>ule.                                                                                               |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Older keyboards can be switched between PC/XT and AT operating modes, with the mode usually selected by a switch on the back or bottom of the keyboard. For correct operation with this cpuModule, you must select AT mode. |

### Connecting to the PC/104 Bus

The PC/104 bus connectors of the cpuModule are simply plugged onto a PC/104 stack to connect to other devices.

We recommend you follow the procedure below to ensure that stacking of the modules does not damage connectors or electronics.

| Do not force the module onto the stack! Wiggling the mod-<br>ule or applying too much pressure may damage it. If the    |

|-------------------------------------------------------------------------------------------------------------------------|

| module does not readily press into place, remove it, check<br>for bent pins or out-of-place keying pins, and try again. |

- Turn off power to the PC/104 system or stack.

- Select and install standoffs to properly position the cpuModule on the PC/104 stack.

- Touch a grounded metal part of the rack to discharge any buildup of static electricity.

- Remove the cpuModule from its anti-static bag.

- Check that keying pins in the bus connector are properly positioned.

- Check the stacking order; make sure an XT bus card will not be placed between two AT bus cards or it will interrupt the AT bus signals.

- Hold the cpuModule by its edges and orient it so the bus connector pins line up with the matching connector on the stack.

- Gently and evenly press the cpuModule onto the PC/104 stack.

### Connecting to the PC/104-Plus PCI Bus

The cpuModule is simply plugged onto a PC/104 stack. Other PC/104-*Plus* boards may then connect to the cpuModule's PC/104-*Plus* bus connector. Supplying power to the PCI bus is provided by the cpuModule.

We recommend you follow the procedure described for the PC/104 bus.

There are three additional considerations when using the PCI bus; PCI Bus signaling level, the slot selection switches on add in boards, and 3.3 volt power source for the expansion cards.

### **PCI Bus Signaling Levels**

The PCI bus can operate at 3.3 or 5 volt signaling levels. This is controlled by solder blob jumper B1 and is configured at the factory for 3.3 volts from on board. If you desire to use 5 volt signaling, because you are connecting cards to the bus that require 5 volt signaling, you have to change the solder blob jumper B1. See *Jumpers and Solder Jumper Settings* on page 88 for details.

| WARNING! | The bus can only operate as 3.3 Volt signaling <b>OR</b> 5 volt |

|----------|-----------------------------------------------------------------|

|          | signaling, not both. You will have to ensure that all your ex-  |

|          | pansion card can operate together at a single signaling level.  |

### **Slot Selection Switches**

Unlike PC/104 cards, PC/104 *Plus* expansion cards have a "slot" selection switch or jumpers. In total, there are 4 PCI cards that can be stacked onto the cpuModule with switch positions 0 through 3. The distance from the CPU determines these switch settings. The card closest to the CPU is said to be in slot 0, the next closest slot 1 and so on to the final card as slot 3.

| This requirement means that all PC/104 <i>Plus</i> cards must be stacked either on the top or the bottom of the CPU, not on both sides |

|----------------------------------------------------------------------------------------------------------------------------------------|

| both sides.                                                                                                                            |

The "slot" setting method may vary from manufacturer to manufacturer, but the concept is the same. The CPU is designed to provide the correct delay to the clock signals to compensate for the bus length. The correct switch setting ensures the proper clock delay setting, interrupt assignment, and bus grant/request channel assignment. Refer to the expansion board's manual for the proper settings. Each expansion card must be in a different slot.

### **PCI Bus Expansion Card Power**

### +5 *Volt DC*

The +5 volt power pins on the PC/104 Plus PCI bus are directly connected to the +5 volt pins on the PC/104 connector and the power connector CN3 (pins 2 and 8). +5 volt expansion boards can be powered directly from these pins.

### +3.3 Volt DC

The default source for the +3.3 volt power pins on the PC/104 Plus PCI bus is the power connector CN3, or a PC/104 Plus power supply. The +3.3V can also be supplied from an on board power converter. The on-board +5 volt to +3.3 volt converter is capable of suppling a maximum of 2 Amps of 3.3 volts to the PCI bus. To use the on-board power supply, change solder blob B3. See *Jumpers and Solder Jumper Settings* on page 88 for details.

### Booting the cpuModule for the First Time

You can now apply power to the cpuModule. You will see a greeting message from the VGA BIOS and then:

- the cpuModule BIOS version information

- a message requesting you press {Del.} to enter the Setup program

If you don't press {Del.}, the cpuModule will try to boot from the current settings.

If you press {Del.}, the cpuModule will enter Setup. Once you have configured the cpuModule using Setup, save your changes and reboot.

| By default, boards are shipped with fail safe boot ROM enable.             |

|----------------------------------------------------------------------------|

| When Fail Safe Boot ROM is enabled the system will boot to it exclusively. |

### Booting to Boot Block Flash with Fail Safe Boot ROM

The Fail Safe Boot ROM is a special build of ROM-DOS<sup>TM</sup> located inside a surface mounted Boot Block Flash chip that is memory mapped to the SSD window. Boot Block Flash is a write protected flash device that contains the BIOS and extra room where the Fail Safe Boot ROM is stored in the ROM DISK. The build is special because it can understand the ROM DISK format on the flash chip. Additionally, Fail Safe Boot ROM is an emergency interface accessible by an external computer. The ROM DISK contains REMDISK and REMSERVE for remote access to the system's disk drives. Due to the size of the flash chip, Fail Safe Boot ROM contains an abbreviated selection of the ROM-DOS<sup>TM</sup> utilities, however, the complete ROM-DOS<sup>TM</sup> is contained on a CD shipped with the board.

The purpose of the Fail Safe Boot ROM is to make the board bootable when the customer receives the cpuModule. Fail Safe Boot ROM can be used as an indicator of the board's functionality when booting problems arise with another operating system. This test can be accomplished by installing JP5. Installing JP5 forces the cpuModule to boot to Fail Safe Boot ROM, as well as load the default BIOS settings. The ROM DISK that contains the Fail Safe Boot ROM acts as an example of what can be programmed into the flash chip. Last, Fail Safe Boot ROM allows files to be transferred on or off the storage devices in the system by use of REMSERV and REMDISK, two ROM-DOS<sup>TM</sup> utilities.

If the user would need remote access to the system run REMSERV on the target system and REM-DISK on the host system. The end result would be that the storage devices on the target system would appear as additional drives on the host system. Information could then be transferred between hard disks by using a standard NULL Modem cable over a serial port. REMSERV makes the connection appear as an additional drive to the user. For details concerning this type of access, please refer to the ROM-DOS<sup>TM</sup> user's guide shipped with your board

| NOTE! | By default, boards are shipped with fail safe boot ROM enable.             |

|-------|----------------------------------------------------------------------------|

|       | When Fail Safe Boot ROM is enabled the system will boot to it exclusively. |

The first time, your system will boot to the DOS prompt at the first available drive letter. If you do not intend to use REMSERV or REMDISK or you intend to boot from another device, you will need to disable Fail Safe Boot ROM. See the steps below for the method to disable it.

- Reset the system by either shutting it off and turning it on or by using the reset button.

- while the system is booting repeatedly press the DEL key to enter the BIOS setup.

- Choose INTEGRATED PERIPHERALS using the arrow keys and enter.

- Once in INTEGRATED PERIPHERALS set Fail Safe Boot ROM: Disabled

### If You Misconfigure the cpuModule

It is possible that you may incorrectly configure the cpuModule using Setup. If this happens the correct procedure is:

- Start Re-booting the cpuModule.

- While the system is re-booting repeatedly press the {Del.} key until the cpuModule enters Setup.

- Change the parameters to correctly match your system.

If the above fails:

- Insert jumper JP5. This will force the cpuModule to boot using the default configuration.

- Boot the cpuModule.

- Press the {Del.} key to enter Setup, or allow the cpuModule to boot to Failsafe

### For More Information

This chapter has been intended to get the typical user up and running quickly. If you need more details, please refer to the following chapters for more information on configuring and using the cpu-Module.

> Phone: 814-234-8087 Fax: 814-234-5218

RTD Embedded Technologies, Inc. 103 Innovation Blvd. State College PA 16803-0906 USA

Our website: www.rtd.com Our e-mail: techsupport@rtd.com

# CHAPTER 3: CONNECTING THE CPUMODULE

This chapter contains necessary information for any of the connectors on the cpuModule.

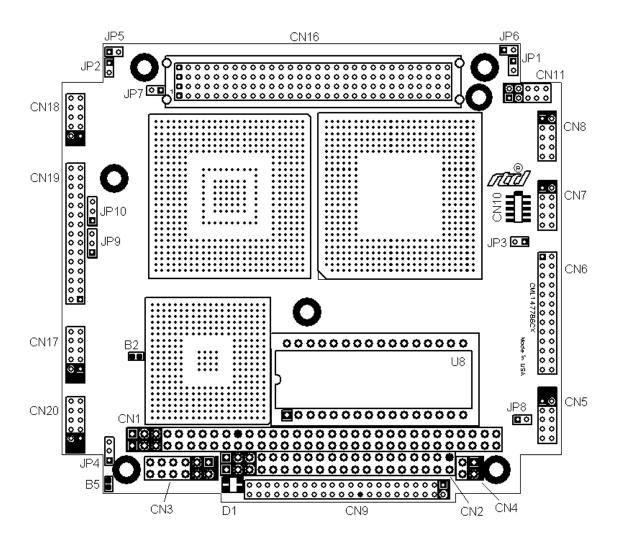

### **Connector Locations**

The figure and table below show all connectors and the ATA/IDE Disk Chip sockets of the cpuModule.

CML147786CX

| Connector | Function                                  | Size             |

|-----------|-------------------------------------------|------------------|

| CN1       | PC/104 XT Bus                             | 64 Pin, 0.1 inch |

| CN2       | PC/104 AT Bus                             | 40 Pin, 0.1 inch |

| CN3       | Auxiliary Power                           | 12 pin, 0.1 inch |

| CN4       | Bus Mouse                                 | 4 pin, 0.1 inch  |

| CN5       | Multifunction                             | 10 pin, 2mm      |

| CN6       | multiPort                                 | 26 pin, 2mm      |

| CN7       | Serial port 1                             | 10 pin, 2mm      |

| CN8       | Serial port 2                             | 10 pin, 2mm      |

| CN9       | EIDE Connector                            | 44 pin, 2mm      |

| CN11      | Audio connector                           | 10 pin, 2mm      |

| CN16      | PC/104-Plus PCI Bus                       | 120 pin, 2mm     |

| CN17      | 2 USB ports                               | 10 pin, 2mm      |

| CN18      | Video                                     | 10 pin, 2mm      |

| CN19      | Flat Panel Video                          | 30 pin, 2mm      |

| CN20      | 10/100 Base T and TX                      | 10 pin, 2mm      |

| U8        | ATA/IDE Disk Chip<br>Socket               | 32 pin           |

| JP3       | Switched Fan Power<br>(1=5V, 2=GND)       | 2 Pin, 2mm       |

| JP4       | Disk Chip Power<br>(1-2 = 5V, 2-3 = 3.3V) | 3 Pin, 2mm       |

| JP7       | Continuous Fan Power<br>(1=5V, 2=GND)     | 2 Pin, 2mm       |

| JP8       | RTC Battery<br>(1=Vbatt, 2=GND)           | 2 Pin, 2mm       |

### Table 2: CML147786CX Connectors

### **Auxiliary Power** CN3

| If you improperly connect power, the module will almost    |

|------------------------------------------------------------|

| certainly be destroyed. Please verify power connections to |

| the module <i>before</i> applying power.                   |

The power supply can be conveyed to the module either through the PC/104 *Plus* bus (CN1, CN2, CN16) or through the Auxiliary Power Connector, CN3. The cpuModule only uses +5 VDC and ground. +12 VDC, -12 VDC and -5 VDC may be required on other PC/104 boards in the system.

| Pin | Signal | Function      |

|-----|--------|---------------|

| 1   | GND    | Ground        |

| 2   | +5 V   | +5 Volts DC   |

| 3   | N/C    | Not Connected |

| 4   | +12 V  | +12 Volts DC  |

| 5   | -5 V   | -5 Volts DC   |

| 6   | -12 V  | -12 Volts DC  |

| 7   | GND    | Ground        |

| 8   | +5 V   | +5 Volts DC   |

| 9   | GND    | Ground        |

| 10  | +3.3 V | See Note      |

| 11  | N/C    | Not Connected |

| 12  | +3.3 V | See Note      |

Table 3: Auxiliary Power Connector CN3

| NOTE! | The +3.3V pins (10 and 12) on the auxiliary power connector (CN3) are connected to the +3.3V pins of the PC/104-<br><i>Plus</i> bus by default. These pins are also configured to supply +3.3V to $FP_VCC$ on the Flat Panel Video connector (CN19). |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | For more information on configuring the +3.3V pins on the auxiliary power connector (CN3), the Flat Panel Video connector (CN19), or the PCI bus connector (CN16), contact RTD Technical Support.                                                    |

Insufficient current supply will prevent your cpuModule from booting. The gauge and length of the wire used for connecting power to the cpuModule must be taken into consideration. Some power connectors have clip leads on them and may have significant resistance. Make sure that the input voltage does not drop below 4.8V at the 5V power pins. A good rule of thumb is to use wire that can supply twice the power your system requires.

| -5 VDC, +12 VDC and -12 VDC voltages are not used by       |

|------------------------------------------------------------|

| the module, but are connected to the PC/104 bus connectors |

| CN1 and CN2.                                               |

Facing the connector pins, the pinout of the Auxiliary Power connector is:

| 11    | 9     | 7   | 5    | 3    | 1   |

|-------|-------|-----|------|------|-----|

| N/C   | GND   | GND | -5V  | N/C  | GND |

| 3.3 V | 3.3 V | +5V | -12V | +12V | +5V |

| 12    | 10    | 8   | 6    | 4    | 2   |

| NOTE! | Connect two separate wires to the $+5V$ pins (2 and 8) on the<br>power connector to ensure a good power supply. We rec-<br>ommend that no less than 18 gauge wire be used and the<br>length of this wire should not exceed 3 ft. Always measure<br>the voltage drop from your power supply to the power pins<br>on the cpuModule. The voltage at pins (2 and 8) should be<br>+5V. |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

### Serial Ports, CN7 and CN8

The two serial ports are implemented on connectors CN7 and CN8 respectively. Each port is normally configured as a PC compatible full-duplex RS232 port, but you may use the Setup program to re-configure it is as full-duplex RS422 or half-duplex RS485. The I/O address and corresponding interrupt must also be selected using Setup. The available I/O addresses and the corresponding interrupts are shown in the following table

| I/O Address | IRQ  |

|-------------|------|

| 03F8H       | IRQ4 |

| 02F8H       | IRQ3 |

| 03E8H       | IRQ4 |

| 02E8H       | IRQ3 |

**Table 4: Serial Port Base Address and IRQ Options**

### Serial Port UART

The serial port is implemented with a 16550-compatible UART (Universal Asynchronous Receiver/ Transmitter). This UART is capable of baud rates up to 115.2 kbaud in 16450 and 16550A compatible mode, and includes a 16-byte FIFO. Please refer to any standard PC-AT hardware reference for the register map of the UART.

### RS232 Serial Port (Default)

The full-duplex RS232 mode is the default setting on the cpuModule. With this mode enabled, the serial port connector must be connected to RS232 compatible devices. The following table gives the connector pinout and shows how to connect to an external serial connector, either DB25 or DB9 compatible.

| Pin  | Signal | Function            | in/out | DB25 | DB9 |

|------|--------|---------------------|--------|------|-----|

| 1    | DCD    | Data Carrier Detect | in     | 8    | 1   |

| 2    | DSR    | Data Set Ready      | in     | 6    | 6   |

| 3    | RXD    | Receive Data        | in     | 3    | 2   |

| 4    | RTS    | Request To Send     | out    | 4    | 7   |

| 5    | TXD    | Transmit data       | out    | 2    | 3   |

| 6    | CTS    | Clear To Send       | in     | 5    | 8   |

| 7    | DTR    | Data Terminal Ready | out    | 20   | 4   |

| 8    | RI     | Ring Indicate       | in     | 22   | 9   |

| 9,10 | GND    | Signal Ground       |        | 7    | 5   |

| Table 5: Serial Port in RS-232 Mode | <b>Table</b> : | 5: | Serial | Port in | <b>RS-232</b> | Mode |

|-------------------------------------|----------------|----|--------|---------|---------------|------|

|-------------------------------------|----------------|----|--------|---------|---------------|------|

Facing the serial port's connector pins, the pinout is:

| 9   | 7   | 5   | 3   | 1   |

|-----|-----|-----|-----|-----|

| GND | DTR | TXD | RXD | DCD |

| GND | RI  | CTS | RTS | DSR |

| 10  | 8   | 6   | 4   | 2   |

## RS422 or RS485 Serial Port

You may use BIOS Setup to configure the serial port as RS422 or RS485. In this case, you must connect the serial port to an RS422 or RS485 compatible device.

When using RS422 or RS485 mode, you can use the port in either half-duplex (two-wire) or fullduplex (four-wire) configurations. For half-duplex (2-wire) operation, you must connect RXD+ to TXD+, and connect RXD- to TXD-.

| NOTE! | A 120 ohm termination resistors is provided on the cpuModule. Termi-<br>nation is usually necessary on all RS422 receivers and at the ends of the<br>RS485 bus. |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | If the termination resistor is required, it can be enabled by closing jumper JP1 for Serial Port 1, or JP2 for Serial Port 2.                                   |

When using full-duplex (typically in RS-422 mode) connect the ports as shown in the table below.

| Port 1 | Port 2 |

|--------|--------|

| RXD+   | TXD+   |

| TXD+   | RXD+   |

| RXD-   | TXD-   |

| TXD-   | RXD-   |

Table 6: RS-422 Serial Port Connections

When using half-duplex in RS-485 connect the ports as shown in the table below.

| From        | То          |

|-------------|-------------|

| Port 1 TXD+ | Port 1 RXD+ |

| Port 1 TXD- | Port 1 RXD- |

| Port 1 TXD+ | Port 2 RXD+ |

| Port 1 RXD- | Port 2 TXD- |

## **RS422 and RS485 Mode Pinout**

The following table gives the pinout of the serial port connector when RS422 or RS485 modes are enabled.

| Pin  | Signal | Function          | in/out | DB9 |

|------|--------|-------------------|--------|-----|

| 1    |        | Reserved          |        | 1   |

| 2    |        | Reserved          |        | 6   |

| 3    | RXD-   | Receive Data (-)  | in     | 2   |

| 4    | TXD+   | Transmit Data (+) | out    | 7   |

| 5    | TXD-   | Transmit Data (-) | out    | 3   |

| 6    | RXD+   | Receive Data (+)  | in     | 8   |

| 7    |        | Reserved          |        | 4   |

| 8    |        | Reserved          |        | 9   |

| 9,10 | GND    | Signal ground     | out    | 5   |

## Table 8: Serial Port in RS-422/485 Mode

Facing the serial port connector, the pinout is:

| 9   | 7    | 5    | 3    | 1    |

|-----|------|------|------|------|

| GND | Rsvd | TXD- | RXD- | Rsvd |

| GND | Rsvd | RXD+ | TXD+ | Rsvd |

| 10  | 8    | 6    | 4    | 2    |

| NOTE! | when using RS485 Mode                                                                                                                                                                                                                                                                                                                     |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | When using the serial port in RS485 mode, the serial transmitters are<br>enabled and disabled under software control. The transmitters are en-<br>abled by manipulating the Request To Send (RTS*) signal of the serial<br>port controller. This signal is controlled by writing bit 1 of the Modem<br>Control Register (MCR) as follows: |

|       | <ul> <li>If MCR bit 1 = 1, then RTS* = 0, and serial transmitters are disabled</li> <li>If MCR bit 1 = 0, then RTS* = 1, and serial transmitters are enabled</li> </ul>                                                                                                                                                                   |

|       | For more information on the serial port registers, including the MCR, please refer to a standard PC-AT hardware reference for the 16550-type UART.                                                                                                                                                                                        |

# multiPort, CN6 - Parallel Port Mode

The parallel port is available on connector CN6. Make sure the BIOS setup sets the multiPort to parallel port. You can use the BIOS Setup to select the parallel port's address, associated interrupt, and choose between its operational modes (SPP, ECP, EPP 1.7 and EPP 1.9).

The pinout of the connector allows a ribbon cable to directly connect it to a DB25 connector, thus providing a standard PC compatible port.

The following tables lists the parallel port signals and explains how to connect it to a DB25 connector to obtain a PC compatible port.

| NOTE! | For correct operation, keep the length of the cable connect- |

|-------|--------------------------------------------------------------|

|       | ing the cpuModule and parallel device less than 3 meters     |

|       | (10 feet).                                                   |

| 1STBStrobe Dataout12AFDAutofeedout143PD0Printer Data 0 (LSB)out24ERRPrinter Errorin155PD1Parallel Data 1out36INITInitialize printerout167PD2Printer Data 2out48SLINSelect printerout179PD3Printer Data 3out510GNDSignal ground1811PD4Printer Data 4out612GNDSignal ground1913PD5Printer Data 5out714GNDSignal ground2117PD7Printer Data 7 (MSB)out918GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein1326RSVReserved-Do Not Connect | Pin | Signal | Function                | in/out | DB25 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-------------------------|--------|------|

| 3PD0Printer Data 0 (LSB)out24ERRPrinter Errorin155PD1Parallel Data 1out36INITInitialize printerout167PD2Printer Data 2out48SLINSelect printerout179PD3Printer Data 3out510GNDSignal ground1811PD4Printer Data 4out612GNDSignal ground1913PD5Printer Data 5out714GNDSignal ground2015PD6Printer Data 7 (MSB)out918GNDSignal ground2219ACKAcknowledgein1020GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                         | 1   | STB    | Strobe Data             | out    | 1    |

| 4ERRPrinter Errorin155PD1Parallel Data 1out36INITInitialize printerout167PD2Printer Data 2out48SLINSelect printerout179PD3Printer Data 3out510GNDSignal ground1811PD4Printer Data 4out612GNDSignal ground1913PD5Printer Data 5out714GNDSignal ground2015PD6Printer Data 6out816GNDSignal ground2117PD7Printer Data 7 (MSB)out918GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                  | 2   | AFD    | Autofeed                | out    | 14   |

| 5PD1Parallel Data 1out36INITInitialize printerout167PD2Printer Data 2out48SLINSelect printerout179PD3Printer Data 3out510GNDSignal ground1811PD4Printer Data 4out612GNDSignal ground1913PD5Printer Data 5out714GNDSignal ground2015PD6Printer Data 6out816GNDSignal ground2117PD7Printer Data 7 (MSB)out918GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                       | 3   | PD0    | Printer Data 0 (LSB)    | out    | 2    |

| 6INITInitialize printerout167PD2Printer Data 2out48SLINSelect printerout179PD3Printer Data 3out510GNDSignal ground1811PD4Printer Data 4out612GNDSignal ground1913PD5Printer Data 5out714GNDSignal ground2015PD6Printer Data 6out816GNDSignal ground2117PD7Printer Data 7 (MSB)out918GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                              | 4   | ERR    | Printer Error           | in     | 15   |

| 7PD2Printer Data 2out48SLINSelect printerout179PD3Printer Data 3out510GNDSignal ground1811PD4Printer Data 4out612GNDSignal ground1913PD5Printer Data 5out714GNDSignal ground2015PD6Printer Data 6out816GNDSignal ground2117PD7Printer Data 7 (MSB)out918GNDSignal ground2219ACKAcknowledgein1020GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                  | 5   | PD1    | Parallel Data 1         | out    | 3    |

| 8SLINSelect printerout179PD3Printer Data 3out510GNDSignal ground1811PD4Printer Data 4out612GNDSignal ground1913PD5Printer Data 5out714GNDSignal ground2015PD6Printer Data 6out816GNDSignal ground2117PD7Printer Data 7 (MSB)out918GNDSignal ground2219ACKAcknowledgein1020GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                                        | 6   | INIT   | Initialize printer      | out    | 16   |

| 9PD3Printer Data 3out510GNDSignal ground1811PD4Printer Data 4out612GNDSignal ground1913PD5Printer Data 5out714GNDSignal ground2015PD6Printer Data 6out816GNDSignal ground2117PD7Printer Data 7 (MSB)out918GNDSignal ground2219ACKAcknowledgein1020GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                                                                | 7   | PD2    | Printer Data 2          | out    | 4    |

| 10GNDSignal ground1811PD4Printer Data 4out612GNDSignal ground1913PD5Printer Data 5out714GNDSignal ground2015PD6Printer Data 6out816GNDSignal ground2117PD7Printer Data 7 (MSB)out918GNDSignal ground2219ACKAcknowledgein1020GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                                                                                      | 8   | SLIN   | Select printer          | out    | 17   |

| 11PD4Printer Data 4out612GNDSignal ground1913PD5Printer Data 5out714GNDSignal ground2015PD6Printer Data 6out816GNDSignal ground2117PD7Printer Data 7 (MSB)out918GNDSignal ground2219ACKAcknowledgein1020GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                                                                                                          | 9   | PD3    | Printer Data 3          | out    | 5    |

| 12GNDSignal ground1913PD5Printer Data 5out714GNDSignal ground2015PD6Printer Data 6out816GNDSignal ground2117PD7Printer Data 7 (MSB)out918GNDSignal ground2219ACKAcknowledgein1020GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                                                                                                                                 | 10  | GND    | Signal ground           |        | 18   |

| 13PD5Printer Data 5out714GNDSignal ground2015PD6Printer Data 6out816GNDSignal ground2117PD7Printer Data 7 (MSB)out918GNDSignal ground2219ACKAcknowledgein1020GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                                                                                                                                                     | 11  | PD4    | Printer Data 4          | out    | 6    |

| 14GNDSignal ground2015PD6Printer Data 6out816GNDSignal ground2117PD7Printer Data 7 (MSB)out918GNDSignal ground2219ACKAcknowledgein1020GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                                                                                                                                                                            | 12  | GND    | Signal ground           |        | 19   |

| 15PD6Printer Data 6out816GNDSignal ground2117PD7Printer Data 7 (MSB)out918GNDSignal ground2219ACKAcknowledgein1020GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                                                                                                                                                                                                | 13  | PD5    | Printer Data 5          | out    | 7    |

| 16GNDSignal ground2117PD7Printer Data 7 (MSB)out918GNDSignal ground2219ACKAcknowledgein1020GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                                                                                                                                                                                                                       | 14  | GND    | Signal ground           |        | 20   |

| 17PD7Printer Data 7 (MSB)out918GNDSignal ground2219ACKAcknowledgein1020GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                                                                                                                                                                                                                                           | 15  | PD6    | Printer Data 6          | out    | 8    |

| 18GNDSignal ground2219ACKAcknowledgein1020GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                                                                                                                                                                                                                                                                        | 16  | GND    | Signal ground           |        | 21   |

| 19ACKAcknowledgein1020GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                                                                                                                                                                                                                                                                                            | 17  | PD7    | Printer Data 7 (MSB)    | out    | 9    |

| 20GNDSignal ground2321BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                                                                                                                                                                                                                                                                                                                | 18  | GND    | Signal ground           |        | 22   |

| 21BSYBusyin1122GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                                                                                                                                                                                                                                                                                                                                    | 19  | ACK    | Acknowledge             | in     | 10   |

| 22GNDSignal ground2423PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                                                                                                                                                                                                                                                                                                                                                 | 20  | GND    | Signal ground           |        | 23   |

| 23PEPaper Endin1224GNDSignal ground2525SLCTReady To Receivein13                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21  | BSY    | Busy                    | in     | 11   |

| 24GNDSignal ground2525SLCTReady To Receivein13                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22  | GND    | Signal ground           |        | 24   |

| 25 SLCT Ready To Receive in 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23  | PE     | Paper End               | in     | 12   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24  | GND    | Signal ground           |        | 25   |

| 26 RSV Reserved-Do Not Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25  | SLCT   | Ready To Receive        | in     | 13   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26  | RSV    | Reserved-Do Not Connect |        |      |

## Table 9: multiPort Parallel Port Connector Pinout CN6

# multiPort, CN6 - aDIO Mode

Pin 1 is indicated by a square solder pad on the pin. This connector is located on the edge of the cpuModule along the PC/104 bus.

| CN6 Pin | Function | DB25           |

|---------|----------|----------------|

| 1       | strobe 0 | 1              |

| 2       | P0-4     | 14             |

| 3       | P1-0     | 2              |

| 4       | P0-5     | 15             |

| 5       | P1-1     | 3              |

| 6       | P0-6     | 16             |

| 7       | P1-2     | 4              |

| 8       | P0-7     | 17             |

| 9       | P1-3     | 5              |

| 10      | strobe 1 | 18             |

| 11      | P1-4     | 6              |

| 12      | GND      | 19             |

| 13      | P1-5     | 7              |

| 14      | GND      | 20             |

| 15      | P1-6     | 8              |

| 16      | GND      | 21             |

| 17      | P1-7     | 9              |

| 18      | GND      | 22             |

| 19      | P0-0     | 10             |

| 20      | GND      | 23             |

| 21      | P0-1     | 11             |

| 22      | GND      | 24             |

| 23      | P0-2     | 12             |

| 24      | GND      | 25             |

| 25      | P0-3     | 13             |

| 26      | Reserved | Do not connect |

# Table 10: multiPort Advanced Digital I/O Connector Pinout CN6

# multiPort, CN6 - Floppy Controller Mode

The MultiPort can be configured to be a floppy drive controller. This is selected in the BIOS Setup under Integrated Peripherals. Only one floppy drive can be connected to the MultiPort, and it is configured as the second drive.

| NOTE! | <ul> <li>To boot the CPU from the MultiPort Floppy, the following steps must be taken:</li> <li>Drive A must be set to "1.44 MB" in the "Standard CMOS Settings" section of BIOS Setup.</li> <li>Onboard MultiPort set to "Floppy" in the "Integrated Peripherals" section of BIOS Setup.</li> <li>Swap Floppy Drive set to "Enabled" in the "Advanced BIOS Features" section of BIOS Setup.</li> <li>First Boot Device set to "Floppy" in the "Advanced BIOS Features" section of BIOS Setup.</li> </ul> |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Pin 1 is indicated by a square solder pad on the pin. This connector is located on the edge of the cpuModule along the PC/104 bus. The following table shows the pin assignments to connect a floppy drive to the multiPort.

| CN6 Pin | Function | DB25 | Floppy Drive<br>Pin |

|---------|----------|------|---------------------|

| 1       | -        | 1    | -                   |

| 2       | DR0      | 14   | 2                   |

| 3       | INDEX#   | 2    | 8 *                 |

| 4       | HDSEL#   | 15   | 32                  |

| 5       | TRK0#    | 3    | 26 *                |

| 6       | DIR#     | 16   | 18                  |

| 7       | WRTPRT#  | 4    | 28 *                |

| 8       | STEP#    | 17   | 20                  |

| 9       | RDATA#   | 5    | 30 *                |

| 10      | GND      | 18   |                     |

| 11      | DSKCHG   | 6    | 34 *                |

| 12      | GND      | 19   | odd pins            |

| 13      | -        | 7    |                     |

| 14      | GND      | 20   | odd pins            |

| 15      | -        | 8    |                     |

| 16      | GND      | 21   | odd pins            |

| 17      | -        | 9    |                     |

| 18      | GND      | 22   | odd pins            |

| 19      | DS1#     | 10   | 12                  |

| 20      | GND      | 23   | odd pins            |

| 21      | MTR#     | 11   | 16                  |

| 22      | GND      | 24   | odd pins            |

| 23      | WDATA#   | 12   | 22                  |

Table 11: multiPort Connector Floppy Pinout CN6

| 24 | GND    | 25 | odd pins |

|----|--------|----|----------|

| 25 | WGATE# | 13 | 24       |

| 26 | +5V    | -  |          |

Table 11: multiPort Connector Floppy Pinout CN6 (Continued)

\* These signals must be pulled to 5V with separate 470 Ohm resistors

# Multifunction Connector, CN5

The Multifunction connector implements the following functions:

- Speaker output

- AT keyboard

- System reset input

- Battery Input

The following table gives the pinout of the Multifunction connector.

| Pin | Signal | Function                             | in/out |

|-----|--------|--------------------------------------|--------|

| 1   | SPKR+  | Speaker output (open collec-<br>tor) | out    |

| 2   | SPKR-  | Speaker output (+5 volts)            | out    |

| 3   | RESET# | Manual push button reset             | in     |

| 4   | PWRSW# | Power / Standby Switch               |        |

| 5   | KBD    | Keyboard Data                        | in     |

| 6   | КВС    | Keyboard Clock                       | out    |

| 7   | GND    | Ground                               |        |

| 8   | KBP    | Keyboard Power (+5 volts)            | out    |

| 9   | BAT    | Battery input                        | in     |

| 10  |        | Not Connected                        |        |

Table 12: Multifunction Connector CN5

Facing the connector pins, the pinout is:

| 9   | 7   | 5   | 3     | 1     |

|-----|-----|-----|-------|-------|

| BAT | GND | KBD | RESET | SPKR+ |

|     | KBP | KBC |       | SPKR- |

| 10  | 8   | 6   | 4     | 2     |

## Speaker

A speaker output is available on pins 1 and 2 of the Multifunction connector. These outputs are controlled by a transistor to supply 0.1 watt of power to an external speaker. The external speaker should have 8 ohm impedance and be connected between pins 1 and 2.

## Keyboard

An AT compatible keyboard can be connected to the Multifunction connector. Usually PC keyboards come with a cable ending with a 5-pin male PS/2 connector. The following table lists the relationship between the Multifunction connector pins and a standard PS/2 keyboard connector.

| Pin | Signal | Function                  | PS/2 |

|-----|--------|---------------------------|------|

| 5   | KBD    | Keyboard Data             | 1    |

| 6   | KBC    | Keyboard Clock            | 5    |

| 7   | GND    | Ground                    | 3    |

| 8   | KBP    | Keyboard Power (+5 Volts) | 4    |

**Table 13: Keyboard Connector Pins on CN5**

# System Reset

Pin 3 of the multifunction connector allows connection of an external push-button to manually reset the system. The push-button should be normally open, and connect to ground when pushed.

## **Power Switch**

Pin 4 of the multifunction connector allows connection of an external push-button switch to act as an ATX power switch, or standby switch. The push-button should be normally open, and connect to ground when pushed.

## **Battery**

Pin 9 of the multifunction connector is the connection for an external backup battery (in the range 2.40 V to 4.15 V; typically 3.0 or 3.6 V). This battery is used by the cpuModule when system power is removed, to preserve the date and time in the Real Time Clock.

# VGA Video Connector, CN18

The following table gives the pinout of the video connector.

| Pin | Signal | Function                                      | in/out | DB15 |

|-----|--------|-----------------------------------------------|--------|------|

| 1   | VSYNC  | Vertical Sync                                 | out    | 14   |

| 2   | HSYNC  | Horizontal Sync                               | out    | 13   |

| 3   | DDCSCL | Monitor communications clock                  | in/out | 15   |

| 4   | RED    | Red analog output                             | out    | 1    |

| 5   | DDCSDA | Monitor communications data                   | bidir  | 12   |

| 6   | GREEN  | Green analog output                           | out    | 2    |

| 7   | DDC_5V | +5V for Monitor Communica-<br>tions (2A fuse) | out    | nc   |

| 8   | BLUE   | Blue analog output                            | out    | 3    |

| 9   | GND    | Ground                                        | out    | 5-7  |

| 10  | GND    | Ground                                        | out    | 8,10 |

## **Table 14: VGA Video Connector CN18**

Facing the connector pins of CN18, the pinout is:

| 9   | 7      | 5      | 3      | 1     |

|-----|--------|--------|--------|-------|

| GND | DDC_5V | DDCSDA | DDCSCL | VSYNC |

| GND | BLUE   | GREEN  | RED    | HSYNC |

| 10  | 8      | 6      | 4      | 2     |

# **Table 15: Supported Video Resolutions and BIOS Settings**

| Resolution  | Colors Bits | Minimum Frame Buffer Size |

|-------------|-------------|---------------------------|

| 640 x 480   | 8/16/32     | 2 MB                      |

| 800 x 600   | 8/16        | 2 MB                      |

| 800 x 600   | 32          | 4 MB                      |

| 1024 x 768  | 8/16        | 2 MB                      |

| 1024 x 768  | 32          | 4 MB                      |

| 1280 x 1024 | 8           | 2 MB                      |

| 1280 x 1024 | 16          | 4 MB                      |

| 1280 x 1024 | 32          | 8 MB                      |

| 1600 x 1200 | 8/16        | 8 MB                      |

# TTL Flat Panel Video Connector, CN19

The following table gives the pinout of the flat panel video connector. FP\_VCC can be either 5V or 3V, and is selected with JP10. FP\_VBKLT can be either 5V or 12V, and can be selected with JP9. See *Jumpers and Solder Jumper Settings* on page 88 for more details.

| Pin | Signal              | Function                         | in/out |

|-----|---------------------|----------------------------------|--------|

| 1   | FP_VCC <sup>a</sup> | Power for flat panel electronics | out    |

| 2   | FP_VBKLT            | Power for flat panel backlight   | out    |

| 3   | FP_VDDEN            | Enable for flat panel power      | out    |

| 4   | FP_ENABLK           | Enable for Backlight Power       | out    |

| 5   | GND                 | Ground                           | GND    |

| 6   | FP_DISPEN           | Display Enable                   | out    |

| 7   | GND                 | Ground                           | GND    |

| 8   | FP_HSYNC            | Horizontal Sync                  | out    |

| 9   | FP_VSYNC            | Vertical Sync                    | out    |

| 10  | GND                 | Ground                           | GND    |

| 11  | FP_CLK              | Clock                            | out    |

| 12  | GND                 | Ground                           | GND    |

| 13  | FP_BLUE0            | Blue bit 0 (LSB)                 | out    |

| 14  | FP_BLUE1            | Blue bit 1                       | out    |

| 15  | FP_BLUE2            | Blue bit 2                       | out    |

| 16  | FP_BLUE3            | Blue bit 3                       | out    |

| 17  | FP_BLUE4            | Blue bit 4                       | out    |

| 18  | FP_BLUE5            | Blue bit 5 (MSB)                 | out    |

| 19  | FP_GREEN0           | Green bit 0 (LSB)                | out    |

| 20  | FP_GREEN1           | Green bit 1                      | out    |

| 21  | FP_GREEN2           | Green bit 2                      | out    |

| 22  | FP_GREEN3           | Green bit 3                      | out    |

| 23  | FP_GREEN4           | Green bit 4                      | out    |

| 24  | FP_GREEN5           | Green bit 5 (MSB)                | out    |

| 25  | FP_RED0             | Red bit 0 (LSB)                  | out    |

| 26  | FP_RED1             | Red bit 1                        | out    |

| 27  | FP_RED2             | Red bit 2                        | out    |