High Performance 32-bit Digital I/O

PCI-HPDI32A PCI64-HPDI32 PMC-HPDI32A PMC64-HPDI32

# Software Development Kit SDK 5.0.0 Reference Manual

Manual Revision: August 18, 2005

General Standards Corporation 8302A Whitesburg Drive Huntsville, AL 35802 Phone: (256) 880-8787 Fax: (256) 880-8788 URL: http://www.generalstandards.com/ E-mail: sales@generalstandards.com HPDI32, Software Development Kit, Reference Manual

## Preface

#### Copyright ©2005, General Standards Corporation

Additional copies of this manual or other literature may be obtained from:

#### **General Standards Corporation**

8302A Whitesburg Drive Huntsville, Alabama 35802 Phone: (256) 880-8787 FAX: (256) 880-8788 URL: http://www.generalstandards.com/ E-mail: sales@generalstandards.com

**General Standards Corporation** makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Although extensive editing and reviews are performed before release to ECO control, General Standards Corporation assumes no responsibility for any errors that may exist in this document. No commitment is made to update or keep current the information contained in this document.

General Standards Corporation does not assume any liability arising out of the application or use of any product or circuit described herein, nor is any license conveyed under any patent rights or any rights of others.

General Standards Corporation assumes no responsibility for any consequences resulting from omissions or errors in this manual or from the use of information contained herein.

**General Standards Corporation** reserves the right to make any changes, without notice, to this product to improve reliability, performance, function, or design.

#### ALL RIGHTS RESERVED.

The Purchaser of this software may use or modify in source form the subject software, but not to re-market or distribute it to outside agencies or separate internal company divisions. The software, however, may be embedded in the Purchaser's distributed software. In the event the Purchaser's customers require the software source code, then they would have to purchase their own copy of the software.

**General Standards Corporation** makes no warranty of any kind with regard to this software, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose and makes this software available solely on an "as-is" basis. **General Standards Corporation** reserves the right to make changes in this software without reservation and without notification to its users.

The information in this document is subject to change without notice. This document may be copied or reproduced provided it is in support of products from **General Standards Corporation**. For any other use, no part of this document may be copied or reproduced in any form or by any means without prior written consent of **General Standards Corporation**.

GSC is a trademark of General Standards Corporation.

PLX and PLX Technology are trademarks of PLX Technology, Inc.

## **Table of Contents**

| 1. Introduction                                            | 9  |

|------------------------------------------------------------|----|

| 1.1. Purpose                                               | 9  |

| 1.2. Acronyms                                              |    |

| 1.3. Definitions                                           | 9  |

| 1.4. Installation                                          | 9  |

| 1.5. Application Programming Interface                     |    |

| 1.6. Software Overview                                     |    |

| 1.6.1. Software Overview<br>1.6.1. Software Architecture   |    |

| 1.7. Hardware Overview                                     |    |

| 1.8. Code Samples                                          |    |

| 1.9. Performance Factors                                   |    |

| 1.10. Reference Material                                   | 12 |

|                                                            |    |

| 2. Operation                                               |    |

| 2.1. Transmitter Operation                                 |    |

| 2.1.1. Data Organization                                   |    |

| 2.1.2. Cable Signals - continuous unstructured data stream |    |

| 2.1.2.1. Tx Clock                                          |    |

| 2.1.2.2. Tx Data                                           |    |

| 2.1.2.3. Tx Enabled                                        |    |

| 2.1.2.4. Tx Ready<br>2.1.2.5. Frame Valid                  |    |

| 2.1.2.5. Frame vand                                        |    |

| 2.1.2.0. Ellie Valid                                       |    |

| 2.1.2.7. Status Vanu                                       |    |

| 2.1.2.6. IX Ready                                          |    |

| 2.1.3.1 Enable                                             |    |

| 2.1.3.2. Auto Start                                        |    |

| 2.1.3.3. Auto Stop                                         |    |

| 2.1.3.4. Flow Control                                      |    |

| 2.1.3.5. Remote Throttle                                   |    |

| 2.1.3.6. Tx Overrun                                        |    |

| 2.1.3.7. Tx/Rx Enabled Tri-State                           |    |

| 2.2. Transmitter Setup                                     | 21 |

| 2.3. Transmitter Configuration                             | 21 |

| 2.4. Receiver Operation                                    | 22 |

| 2.4.1. Data Organization                                   |    |

| 2.4.2. Cable Signals - continuous unstructured data stream |    |

| 2.4.2.1. Rx Clock                                          |    |

| 2.4.2.2. Rx Data                                           |    |

| 2.4.2.3. Rx Enabled                                        |    |

| 2.4.2.4. Frame Valid                                       |    |

| 2.4.2.5. Line Valid                                        |    |

| 2.4.2.6. Status Valid<br>2.4.2.7. Rx Ready                 |    |

| 2.7.2.1. NA INTAUY                                         |    |

| 2.4.3. Control Options - continuous unstructured data stream |                                        |

|--------------------------------------------------------------|----------------------------------------|

| 2.4.3.1. Enable                                              |                                        |

| 2.4.3.2. Rx Overrun                                          |                                        |

| 2.4.3.3. Rx Under Run                                        |                                        |

| 2.4.3.4. Tx/Rx Enabled Tri-State                             |                                        |

| 2.5. Receiver Setup                                          |                                        |

| 2.6. Receiver Configuration                                  |                                        |

| 2.7. Data Transfer Issues                                    |                                        |

| 2.7.1. Tx vs. Rx Defaults                                    |                                        |

| 2.7.2. I/O Abort Requests                                    |                                        |

| 2.7.3. I/O Data Buffers                                      |                                        |

| 2.7.4. General DMA Parameters                                |                                        |

| 2.7.6. PIO Threshold                                         |                                        |

| 2.7.7. I/O Timeout                                           |                                        |

| 2.7.8. I/O Data Transfer Modes                               |                                        |

| 2.7.8.1. DMA (Manual)                                        |                                        |

| 2.7.8.2. Demand Mode DMA                                     |                                        |

| 2.7.9. FIFO Almost Levels                                    |                                        |

| 2.7.10. Flow Control                                         |                                        |

| 2.7.11. Direct Register Access                               |                                        |

| 2.8. Event Notification                                      |                                        |

| 2.8.1. Event Callback                                        |                                        |

| 2.8.1.1. Interrupt Notification Callback                     |                                        |

| 2.8.1.2. I/O Completion Notification Callback                |                                        |

| 2.8.2. Event Waiting                                         |                                        |

| 3. Macros                                                    |                                        |

| 3.1. API Version Number                                      |                                        |

| 3.2. Common Parameter Assignment Values                      |                                        |

| 3.3. Discrete Data Type Options                              |                                        |

| 3.4. I/O Status Fields                                       |                                        |

| 3.5. Maximum Number of Open Handles                          |                                        |

| 3.6. Parameter Access "Which" Bits                           |                                        |

| 3.7. Registers                                               |                                        |

| 3.7.1. GSC Registers                                         |                                        |

| 3.7.2. PLX PCI9080 PCI Configuration Registers               |                                        |

| 3.7.3. PLX PCI9080 Feature Set Registers                     |                                        |

| 3.7.4. PLX PCI9656 PCI Configuration Registers               |                                        |

| 3.7.5. PLX PCI9656 Feature Set Registers                     |                                        |

| 3.8. Version Data Selectors                                  | 46                                     |

| 4. Data Types                                                |                                        |

| 4.1. Discrete Data Types                                     |                                        |

| 4.2. hpdi32_callback_func_t                                  |                                        |

| 4.3. Status Values                                           |                                        |

| IIVI MUUUT I AIUUT IIIIIIIIIIIIIIIIIIIIIIIIIII               | ······································ |

| 5. Functions                                                                                         |    |

|------------------------------------------------------------------------------------------------------|----|

| 5.1. hpdi32_api_status()                                                                             | 49 |

| 5.2. hpdi32_board_count()                                                                            |    |

| 5.3. hpdi32_close()                                                                                  | 51 |

| 5.4. hpdi32_config()                                                                                 | 51 |

| 5.5. hpdi32_gpio_mod()                                                                               | 53 |

| 5.6. hpdi32_gpio_read()                                                                              | 54 |

| 5.7. hpdi32_gpio_write()                                                                             |    |

| 5.8. hpdi32_init()                                                                                   |    |

| 5.9. hpdi32_io_wait()                                                                                |    |

| 5.10. hpdi32_irq_wait()                                                                              |    |

| 5.11. hpdi32_open()                                                                                  |    |

| 5.12. hpdi32 read()                                                                                  | 60 |

| 5.13. hpdi32 reg mod()                                                                               | 61 |

| 5.14. hpdi32 reg read()                                                                              |    |

| 5.15. hpdi32 reg write()                                                                             | 63 |

| 5.16. hpdi32 reset()                                                                                 | 64 |

| 5.17. hpdi32_status_text()                                                                           | 65 |

| 5.18. hpdi32 version get()                                                                           |    |

| 5.19. hpdi32_write()                                                                                 | 67 |

| 6. Configuration Parameters                                                                          |    |

| 6.1. Parameter Macros                                                                                |    |

| 6.1.1. Parameter Definitions                                                                         |    |

| 6.1.2. Value Definitions                                                                             |    |

| 6.1.3. Service Definitions                                                                           |    |

| 6.1.3.2. Which Bits: w                                                                               |    |

| 6.1.3.3. Set Value: s                                                                                |    |

| 6.1.3.4. Get Value: g                                                                                |    |

| 6.2. Cable Parameters                                                                                |    |

| 6.2.1. Cable Parameter: Clock State                                                                  |    |

| <ul><li>6.2.2. Cable Parameter: Command Mode</li><li>6.2.3. Cable Parameter: Command State</li></ul> |    |

|                                                                                                      |    |

| 6.3. FIFO Parameters                                                                                 |    |

| 6.3.2. FIFO Parameter: Reset                                                                         |    |

| 6.3.3. FIFO Parameter: Size                                                                          |    |

| 6.3.4. FIFO Parameter: Status                                                                        |    |

| 6.3.5. FIFO Parameter: Transfer Size                                                                 |    |

| 6.4. I/O Parameters                                                                                  |    |

| 6.4.1. I/O Parameter: Abort                                                                          |    |

| 6.4.2. I/O Parameter: Aborted                                                                        | 77 |

| 6.4.3. I/O Parameter: Buffer Pointer                                                                    |  |

|---------------------------------------------------------------------------------------------------------|--|

| 6.4.4. I/O Parameter: Buffer Size                                                                       |  |

| 6.4.5. I/O Parameter: Callback Argument                                                                 |  |

| 6.4.6. I/O Parameter: Callback Function                                                                 |  |

| 6.4.7. I/O Parameter: Data Size                                                                         |  |

| 6.4.8. I/O Parameter: DMA Channel Select                                                                |  |

| 6.4.9. I/O Parameter: DMA Control Mode                                                                  |  |

| 6.4.10. I/O Parameter: DMA Priority                                                                     |  |

| 6.4.11. I/O Parameter: Mode                                                                             |  |

| 6.4.12. I/O Parameter: Overlap Enable                                                                   |  |

| 6.4.13. I/O Parameter: PIO Threshold                                                                    |  |

| 6.4.14. I/O Parameter: Single Cycle                                                                     |  |

| 6.4.15. I/O Parameter: Status                                                                           |  |

| 6.4.16. I/O Parameter: Timeout                                                                          |  |

| 6.5. Interrupt Parameters                                                                               |  |

| 6.5.1. Interrupt Parameter: Callback Argument                                                           |  |

| 6.5.2. Interrupt Parameter: Callback Function                                                           |  |

| 6.5.3. Interrupt Parameter: Enable                                                                      |  |

| 6.5.4. Interrupt Parameter: State                                                                       |  |

| 6.5.5. Interrupt Parameter: Trigger Configuration                                                       |  |

| 6.6. Miscellaneous Parameters                                                                           |  |

| 6.6.1. Miscellaneous Parameters.                                                                        |  |

| 6.6.2. Miscellaneous Parameter: Favor Tx                                                                |  |

| 6.6.3. Miscellaneous Parameter: Features                                                                |  |

| 6.6.4. Miscellaneous Parameter: GSC Register Mapping                                                    |  |

| 6.6.5. Miscellaneous Parameter: GSC Register Mapping Pointer                                            |  |

| 6.6.6. Miscellaneous Parameter: PLX Register Mapping Fonder                                             |  |

| 6.6.7. Miscellaneous Parameter: PCI Bus Width                                                           |  |

| 6.6.8. Miscellaneous Parameter: Strict Arguments                                                        |  |

| 6.6.9. Miscellaneous Parameter: Strict Configuration                                                    |  |

| 6.6.10. Miscellaneous Parameter: Tx/Rx Tri-State                                                        |  |

| 6.7. Receiver Parameters                                                                                |  |

|                                                                                                         |  |

| 6.7.1. Receiver Parameter: Rx Enable                                                                    |  |

| 6.7.3. Receiver Parameter: Row Count                                                                    |  |

| 6.7.4. Receiver Parameter: State                                                                        |  |

| 6.7.5. Receiver Parameter: Status Count                                                                 |  |

| 6.7.6. Receiver Parameter: Rx Under Run                                                                 |  |

|                                                                                                         |  |

| 6.8. Transmitter Parameters                                                                             |  |

| 6.8.1. Transmitter Parameter: Auto Start                                                                |  |

| 6.8.2. Transmitter Parameter: Auto Stop                                                                 |  |

| 6.8.3. Transmitter Parameter: Tx Clock Divider                                                          |  |

| 6.8.4. Transmitter Parameter: Tx Enable                                                                 |  |

| 6.8.5. Transmitter Parameter: Flow Control                                                              |  |

| 6.8.6. Transmitter Parameter: Line Valid Off Count                                                      |  |

| 6.8.7. Transmitter Parameter: Line Valid On Count                                                       |  |

| 6.8.8. Transmitter Parameter: Tx Overrun.                                                               |  |

| 6.8.9. Transmitter Parameter: Remote Throttle                                                           |  |

| 6.8.10. Transmitter Parameter: Remote Throttle State                                                    |  |

| 6.8.11. Transmitter Parameter: Tx State                                                                 |  |

| 6.8.12. Transmitter Parameter: Status Valid Count<br>6.8.13. Transmitter Parameter: Status Valid Mirror |  |

|                                                                                                         |  |

| Document History                                                                                        |  |

## **Table of Figures**

| Figure 1 A depiction of the HPDI32 Transmitter.                                                     | 14 |

|-----------------------------------------------------------------------------------------------------|----|

| Figure 2 A simple continuous unstructured data stream cable configuration.                          | 15 |

| Figure 3 Tx Data is synchronized with Tx Clock.                                                     | 16 |

| Figure 4 The Tx Enabled signal reflects the transmitter enable state (default configuration).       | 16 |

| Figure 5 The Tx Ready signal reflects the Tx FIFO empty state                                       | 17 |

| Figure 6 The Frame Valid signal reflects the data transmission process.                             | 17 |

| Figure 7 The Line Valid signal reflects valid transmit data being presented at the cable interface  | 18 |

| Figure 8 The Status Valid signal reflects valid status data being presented at the cable interface. | 18 |

| Figure 9 The receiving device can drive the Rx Ready signal to control data flow.                   | 19 |

| Figure 10 A depiction of the HPDI32 Receiver                                                        | 22 |

| Figure 11 A simple continuous unstructured data stream cable configuration.                         | 23 |

| Figure 12 Rx Data is synchronized with Rx Clock                                                     | 24 |

| Figure 13 The Rx Enabled signal reflects the receiver enable state (default configuration).         | 24 |

| Figure 14 The Frame Valid signal reflects the data reception process.                               | 25 |

| Figure 15 The Line Valid signal reflects valid transmit data being presented at the cable interface | 25 |

|                                                                                                     |    |

| Figure 17 The receiver drives the Tx Ready signal to control data flow.                             |    |

## 1. Introduction

This reference manual applies to SDK release version 5.0.0.

## 1.1. Purpose

The purpose of this document is to describe the Application Programming Interface to the HPDI32 Software Development Kit. This software provides the interface between "Application Software" and the HPDI32 board. The interface provided by the SDK is based on the board's functionality.

## 1.2. Acronyms

The following is a list of commonly occurring acronyms used throughout this document.

| Acronyms | Description                                                                             |

|----------|-----------------------------------------------------------------------------------------|

| API      | Application Programming Interface (This is sometimes used synonymously with SDK or API  |

|          | Library.)                                                                               |

| DMA      | Direct Memory Access                                                                    |

| DMDMA    | Demand Mode DMA                                                                         |

| GPIO     | General Purpose Input/Output                                                            |

| GSC      | General Standards Corporation                                                           |

| PCI      | Peripheral Component Interconnect                                                       |

| PIO      | Programmed I/O                                                                          |

| PMC      | PCI Mezzanine Card                                                                      |

| SDK      | Software Development Kit (This is sometimes used synonymously with API or API Library.) |

## 1.3. Definitions

The following is a list of commonly occurring terms used throughout this document.

| Term                   | Definition                                                                                                                                                                                                                                       |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| API Buffer             | A physically contiguous block of memory allocated via the API.                                                                                                                                                                                   |  |

| API Library            | This refers to the library implementing the application level HPDI32 interface. (This is sometimes used synonymously with SDK or API.)                                                                                                           |  |

| Application            | This refers to user mode processes.                                                                                                                                                                                                              |  |

| Application<br>Buffers | These are memory buffers allocated and maintained entirely by the application, and which are used for reading data from and writing data to the HPDI32's FIFOs.                                                                                  |  |

| Device Driver          | This refers to the driver executable component of the HPDI32 driver package.                                                                                                                                                                     |  |

| Driver                 | This refers to the device driver, which runs under control of the operating system.                                                                                                                                                              |  |

| PLX                    | This refers to the company PLX Technology, Inc., who is the supplier of the PCI bridge chip used on the HPDI32.                                                                                                                                  |  |

| Rx                     | This is a general reference to the receiver portion of the board. This includes reception of data over the cable, either to the FIFOs or from GPIO, data I/O read operations from the receive FIFO, and any and all associated settings.         |  |

| Тх                     | This is a general reference to the transmitter portion of the board. This includes transmission of data over the cable, either from the FIFOs or from GPIO, data I/O write operations to the transmit FIFO, and any and all associated settings. |  |

## 1.4. Installation

Installation instructions for the SDK are provided in separate, operating system specific setup guides.

## **1.5. Application Programming Interface**

The SDK API is defined in the four header files listed below. These C language headers are C++ compatible. The only header that need be included by HPDI32 applications is hpdi32\_api.h. The API consists of macros, data types, function calls and parameter definitions. These are described in other sections of this document. The headers define numerous items in addition to those described in this document. These additional items are provided without documentation. All software components of the API begin with a prefix of HPDI32 or GSC (both appear with upper and lower case letters). The table below indicates where to look for any particular item's definition.

| File Name     | Description                                                                                   |  |

|---------------|-----------------------------------------------------------------------------------------------|--|

| hpdi32_api.h  | This header contains the bulk of the API, including function calls, data types and numerous   |  |

|               | macros. All items defined here include the prefix "HPDI32" or "hpdi32".                       |  |

| gsc_common.h  | This header contains status definitions, a few data type definitions and a variety of macros. |  |

|               | All items defined here have a prefix of "GSC" or "gsc".                                       |  |

| gsc_pci9080.h | This header contains register definitions for the PCI9080, which is the PCI interface chip    |  |

|               | used on HPDI32s with 32-bit PCI interfaces. All items defined here have a prefix of "GSC"     |  |

|               | or "gsc" and include "9080".                                                                  |  |

| gsc_pci9656.h | This header contains register definitions for the PCI9656, which is the PCI interface chip    |  |

|               | used on HPDI32s with 64-bit PCI interfaces. All items defined here have a prefix of "GSC"     |  |

|               | or "gsc" and include "9656".                                                                  |  |

## 1.6. Software Overview

The software interface to the HPDI32 consists of a Device Driver and an API Library; the primary components of the SDK. The Device Driver operates under control of the operating system and must be loaded and running in order to access any installed HPDI32 devices. The interface provided by the API Library is based on the board's functionality and is organized around the HPDI32's set of main hardware features. The general categories are as follows and permit access to and manipulation of virtually every feature available on the board.

- General Access Services (API Status, Version Numbers, Board Count, Open, Close, ...)

- Cable Interface Configuration

- FIFO Configuration

- Data Input and Output Configuration

- General Purpose Input and Output Configuration

- Interrupt Configuration

- Other Miscellaneous Configuration

- Register read and write operations

- Receiver Configuration

- Transmitter Configuration

All HPDI32 features are individually accessible via a generalized configuration service. For each parameter, as appropriate, the API includes a set of support macros. These include setting options (i.e. defaults and acceptable values), quick access retrieval macros, and quick access manipulation macros. All are described later in this document.

#### 1.6.1. Software Architecture

An application communicates with an HPDI32 using the driver and library described briefly above. Any number of applications may make simultaneous use of the library and each use is totally independent, unless specifically designed to do otherwise. Each instance provides access to at most 32 different HPDI32 devices. The diagram below describes the components and how they fit together.

| Application                                                   | This is any application written to communicate with one or more HPDI32 devices using the driver and library provided in the SDK. |  |  |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|

| API Library                                                   | This library presents an HPDI32 feature based interface to applications wishing to communicate with HPDI32 devices.              |  |  |

| Device Driver                                                 | The driver provides access to HPDI32 devices.                                                                                    |  |  |

| HPDI32 This refers to any number of installed HPDI32 devices. |                                                                                                                                  |  |  |

**NOTE:** While multiple applications can gain access to the same device, this is discouraged since the driver maintains resources and settings per device rather than per application or device handle.

## 1.7. Hardware Overview

The HPDI32 is a high-performance 32-bit parallel digital I/O interface board. The host side connection is PCI based and is either 32-bit or 64-bit according to the model ordered. The external I/O interface varies per model ordered. The board is capable of transmitting or receiving data at up to 200 Mbytes per second over an external I/O interface, depending on the model ordered. Onboard transmit and receive FIFOs of up to 128k data values each, buffer transfer data between the PCI bus and the cable interface. This allows the HPDI32 to maintain maximum bursts on the cable interface (at least up to the depth of the FIFOs) independent of the PCI bus interface. The onboard FIFOs can also be used to buffer data between the cable interface and the PCI bus to maintain a sustained data throughput for real-time applications.

The HPDI32 offers a half-duplex external I/O interface. The board can either transmit or receive data, but it cannot do both simultaneously. In addition to the 32 synchronous data I/O lines, the external interface includes a set of configurable flow control signals. Some of these can also be configured as discrete I/O. The board accommodates a wide range of applications. This range extends from sending or receiving relatively small blocks of data on demand, to sending or receiving large continuous streams of data for an extended period. Once a data link is established, the data is transferred to/from host memory by simply writing to or reading from the onboard FIFOs. The board has an advanced PCI interface engine, which provides for increased data throughput via DMA.

**NOTE:** PCI form factor boards with a 32-bit PCI interface can be used interchangeably in 64-bit PCI slots, and vise-versa. However, the performance improvements associated with the 64-bit PCI interface can be achieved only when a 64-bit board is used in a 64-bit slot.

## 1.8. Code Samples

All of the code samples in this manual are included in the hpdi32\_dsl library along with their C source files. The examples given are notably simplistic, but are provided to illustrate use rather than accomplishment of broader tasks.

## **1.9. Performance Factors**

The HPDI32 is designed for high performance data transfer. In many instances the form factor, the cable clock rate and the external interface transceivers are dictated by the application. The performance variables that remain are the PCI Bus width and the FIFO sizes. If the application doesn't mandate the PCI bus width, then going with an HPDI32 with a 64-bit bus has the potential for better performance and/or higher bus utilization efficiency. The peak

transfer rates across the PCI bus are 528MB/S for the 64-bit PCI bus and 132MB/S for the 32-bit bus (64-bits @ 66MHz vs. 32-bits @ 33MHz). Actual performance can be drastically different for many reasons. Otherwise, the remaining performance variable is the FIFO size. As FIFO sizes increase, so do throughput rates. In many cases a 32-bit board with larger FIFOs outperforms 64-bit boards with smaller FIFOs. The processor board the HPDI32 is plugged into, and its supporting chip set, also have significant affects on performance.

## 1.10. Reference Material

The following reference material may be of particular benefit in using the HPDI32 and this SDK. The specifications provide the information necessary for an in-depth understanding of the specialized features implemented on this board.

- The applicable HPDI32 User Manual from General Standards Corporation.

- The *PCI9080 PCI Bus Master Interface Chip* data handbook from PLX Technology, Inc. (for 32-bit PCI interface boards) \*

- The *PCI9656 PCI Bus Master Interface Chip* data handbook from PLX Technology, Inc. (for 64-bit PCI interface boards) \*

\* PLX data books are available from PLX at the following location.

PLX Technology Inc. 870 Maude Avenue Sunnyvale, California 94085 USA Phone: 1-800-759-3735 WEB: http://www.plxtech.com/

## 2. Operation

The purpose of this section is to provide information on the operation of the HPDI32 and the API. This is not intended to be comprehensive. It is intended to give a basic understanding of the board and the software while addressing some issues relating to their use.

## 2.1. Transmitter Operation

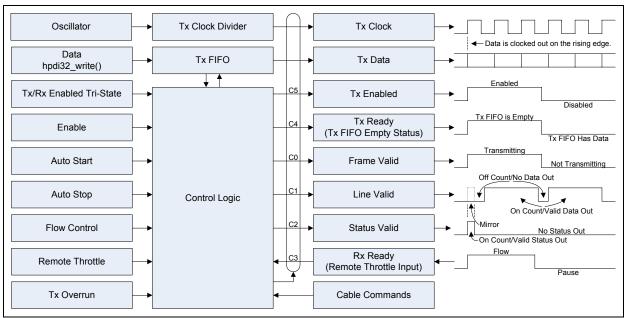

The transmitter is that portion of the HPDI32 responsible for sending data out over the cable interface. The transmitter consists of numerous hardware features that operate under control of the SDK and the application. The hardware portion includes a clock, data FIFOs, firmware registers, control logic, and cable signal transceivers. The SDK portion consists of function calls, parameter identifiers, and parameter values. Together these components permit applications to feed data to the transmitter, and give applications control over how the transmitter controls data flow out the cable interface. An overall depiction is given in Figure 1. Some general guidelines for using the transmitter are as follows. Each of these steps is further explained in subsequent paragraphs.

- 1. Identify the basic nature of the data's organization; continuous stream or a sequence of frames.

- 2. Identify the cable signals needed, how each will be used, and how each will operate.

- 3. Configure the cable signals according to how each will be used.

- 4. Configure the cable signal parameters so that each signal has the desired operating characteristics.

- 5. Identify how overall data flow will be started and stopped; remote, local (automatic and/or manual).

- 6. Configure the device according to how overall data flow will be started and stopped.

- 7. Configure the I/O write parameters.

- 8. Enable the transmitter.

- 9. Write data to the device.

- 10. As appropriate, perform any manual steps to start or stop data flow.

Figure 1 A depiction of the HPDI32 Transmitter.

#### 2.1.1. Data Organization

The HPDI32 transmitter supports two basic data organization schemes; a structured stream of frames divided into lines, and an unstructured continuous data stream. The structured format divides the overall data stream into a series of data frames, with each frame further divided into a series of data lines. Each line may be preceded by a fixed time delay in which no data is transmitted. In the unstructured format, data appears on the cable when it is available for transmission without delay. By far, most HPDI32 applications have employed an unstructured data stream. For this reason the cable signal descriptions that follow assume the use of an unstructured data stream.

#### 2.1.2. Cable Signals - continuous unstructured data stream

For continuous unstructured data streams, some cable signals are required and some can be ignored or used for GPIO. The Tx Clock and Tx Data signals are always required. The Frame Valid signal is needed while the Line Valid and Status valid signals can be ignored or used for GPIO. If the remote device will be controlling data flow, then the Rx Ready signal must be used as the Remote Throttle input. Otherwise the Rx Ready signal can be ignored or used to indicate when the transmitter is enabled, if desired, or it can be ignored or used as GPIO. Also, the Tx Ready signal can be used to indicate when the transmitter has data, if desired, or it too can be ignored or used as GPIO.

The simplest configuration usable for a continuous unstructured data stream is illustrated in Figure 2. This configuration uses the Tx Clock, Tx Data and Frame Valid signals, while all of the other transmitter signals are unused. Even in this simplest configuration the unused signals must be configured, though they are configured so that they are unused by the transmitter. The easiest way to do this is to configure the unused signals as general purpose inputs. Signal configuration is described below.

| Tx Clock 🔶            |                          |

|-----------------------|--------------------------|

| Tx Data 🔶             |                          |

| Tx Enabled 🔶 optional |                          |

| Tx Ready 🔶 optional   |                          |

| Frame Valid 🔶         |                          |

| Line Valid            |                          |

| Status Valid 🔶 unused |                          |

| Rx Ready 🔶 optional   | Remote throttling input. |

Figure 2 A simple continuous unstructured data stream cable configuration.

#### 2.1.2.1. Tx Clock

The Tx Clock output signal is the clock that synchronizes the transmitter logic and which clocks data out the cable interface. This clock is derived from the on-board oscillator, which is fed through the Tx Clock Divider. If the divider is zero, then the Tx Clock frequency equals the on-board oscillator frequency. Otherwise the Tx Clock frequency is governed by the formula  $F_{TxC} = F_{Osc} / (Div * 2)$ . In the formula,  $F_{TxC}$  is the Tx Clock frequency,  $F_{Osc}$  is the on-board oscillator frequency, and Div is the Tx Clock Divider value. The Tx Clock signal is driven on the cable interface only when the transmitter is enabled. When the transmitter is disabled the signal is not driven by the HPDI32. For enabling and disabling the transmitter, refer to "Enable" on page 19.

The Tx Clock Divider is configurable. For details on setting the divider refer to "Transmitter Parameter: Tx Clock Divider" on page 98. The divider can most easily be set using the utility macro HPDI32\_TX\_CLOCK\_DIVIDER\_SET(h, s). In the macro, h is the device handle obtained from hpdi32\_open() (page 59). Also, s is the divider value to apply and is limited to the range zero to  $0 \times FFFF$ . A return value of GSC\_SUCCESS indicates that the operation was successful. Using the above formula with a 20MHz on-board oscillator, a divider value of two will produce a Tx Clock frequency of 5MHz. Likewise, a divider of ten will result in a 1MHz Tx Clock.

#### 2.1.2.2. Tx Data

The Tx Data output signals are synchronized with the Tx Clock to transmit 32-bits of parallel data. The transmitter clocks out the data on Tx Clock's rising edge. See Figure 3. The transmitter hardware has a 32-bit data path, including the FIFOs and the cable transceivers. When the source data is less than 32-bits wide, it is aligned with the D0 bit and passed through the transmitter as full 32-bit data words. When the source data is 8-bits wide it appears on cable signals D0 through D7. The upper 24 data signals can be ignored, though they are driven by the transmitter. When the source data is 16-bits wide it appears on cable signals D0 through D15. The upper 16 data signals can be ignored, though they are driven by the transmitter. The Tx Data signals are driven on the cable interface only when the transmitter is enabled. When the transmitter is disabled the signals are not driven by the HPDI32. For enabling and disabling the transmitter, refer to "Enable" on page 19.

| Tx Clock                                                                  |  |  |  |

|---------------------------------------------------------------------------|--|--|--|

| <ul> <li>← The transmitter clocks data out on the rising edge.</li> </ul> |  |  |  |

| Tx Data                                                                   |  |  |  |

Figure 3 Tx Data is synchronized with Tx Clock.

The cable data size is configurable. For details refer to "I/O Parameter: Data Size" on page 80. The data size can most easily be set via the utility macros HPDI32\_IO\_DATA\_SIZE\_\_TX\_32/16/8 (h) to specify the data size as 32, 16 or eight bits, respectively. In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful.

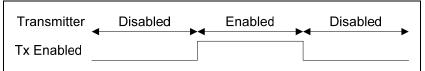

#### 2.1.2.3. Tx Enabled

The Tx Enabled output signal reflects the enabled state of the transmitter. This signal is not required for Flow Control of continuous unstructured data streams so applications may instead configure it as GPIO so that it is ignored by the transmitter. As a Flow Control signal, Tx Enabled is driven high when the transmitter is enabled and is driven low when disabled (see the note below for alternation operation). The signal changes state as the transmitter is enabled and is not synchronized with Tx Clock. Refer to Figure 4. For enabling and disabling the transmitter, refer to "Enable" on page 19.

Figure 4 The Tx Enabled signal reflects the transmitter enable state (default configuration).

**NOTE:** An alternative option configures Tx Enabled so that it is tri-stated when the transmitter is disabled. Refer to "Tx/Rx Enabled Tri-State" on page 20.

The Tx Enabled signal refers to the Cable Command 5 signal when configured to operate in its Flow Control mode. For details on setting the mode refer to "Cable Parameter: Command Mode" on page 72. The mode can most easily be set via the utility macros HPDI32\_CABLE\_COMMAND\_MODE\_\_TE\_FC/IN/LOW/HI (h) to set the mode to Flow Control (Tx Enabled), a general purpose input, a general purpose output driven low, or a general purpose output driven high, respectively. In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful. To configure the signal so that it can be ignored altogether, configure it as a general purpose input.

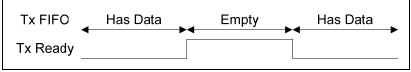

#### 2.1.2.4. Tx Ready

The Tx Ready output signal reflects the availability of data from the transmitter. This signal is not required for Flow Control of continuous unstructured data streams so applications may instead configure it as GPIO so that it is ignored by the transmitter. As a Flow Control signal, Tx Ready is driven high when the Tx FIFO is empty and is driven low when the Tx FIFO has data. Refer to Figure 5. The signal state changes are not synchronized with Tx Clock. The Tx Ready signal is driven on the cable interface only when the transmitter is enabled. When the transmitter is disabled the signal is not driven by the HPDI32. For enabling and disabling the transmitter, refer to "Enable" on page 19.

Figure 5 The Tx Ready signal reflects the Tx FIFO empty state.

The Tx Ready signal refers to the Cable Command 4 signal when configured to operate in its Flow Control mode. For details on setting the mode refer to "Cable Parameter: Command Mode" on page 72. The mode can most easily be set via the utility macros HPDI32\_CABLE\_COMMAND\_MODE\_\_TR\_FC/IN/LOW/HI(h) to set the mode to Flow Control (Tx Ready), a general purpose input, a general purpose output driven low, or a general purpose output driven high, respectively. In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful. To configure the signal so that it can be ignored altogether, configure it as a general purpose input.

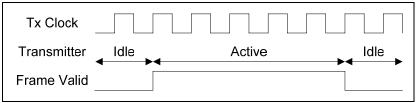

#### 2.1.2.5. Frame Valid

The Frame Valid output signal reflects the activity of the data transmission process. When the Line Valid and Status Valid signals are not used for Flow Control, then Frame Valid effectively reflects valid transmit data being presented at the cable interface. The Frame Valid signal is required for Flow Control of continuous unstructured data streams so applications <u>must not</u> configure it as GPIO. As a Flow Control signal, Frame Valid is driven high when the transmission process is active and is driven low when the transmission process is idle. Refer to Figure 6. The signal is synchronized with Tx Clock and changes state on the clock's rising edge. The Frame Valid signal is driven on the cable interface only when the transmitter is enabled. When the transmitter is disabled the signal is not driven by the HPDI32. For enabling and disabling the transmitter, refer to "Enable" on page 19.

Figure 6 The Frame Valid signal reflects the data transmission process.

The Frame Valid signal refers to the Cable Command 0 signal when configured to operate in its Flow Control mode. For details on setting the mode refer to "Cable Parameter: Command Mode" on page 72. The mode can most easily be set via the utility macros HPDI32\_CABLE\_COMMAND\_MODE\_\_FV\_FC/IN/LOW/HI (h) to set the mode to Flow Control (Frame Valid), a general purpose input, a general purpose output driven low, or a general purpose output driven high, respectively. In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful. To configure the signal so that it can be ignored altogether, configure it as a general purpose input.

#### 2.1.2.6. Line Valid

The Line Valid signal output reflects valid transmit data being presented at the cable interface. This signal is not required for Flow Control of continuous unstructured data streams so applications <u>should</u> configure it as GPIO so that it is ignored by the transmitter. As a Flow Control signal, Line Valid is driven high when valid transmit data is presented at the cable interface and is driven low otherwise (see below for additional information). Refer to Figure 7. The signal is synchronized with Tx Clock and changes state on the clock's rising edge. The Line Valid signal is driven on the cable interface only when the transmitter is enabled. When the transmitter is disabled the signal is not driven by the HPDI32. For enabling and disabling the transmitter, refer to "Enable" on page 19.

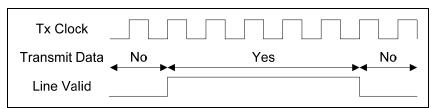

Figure 7 The Line Valid signal reflects valid transmit data being presented at the cable interface.

The Line Valid signal refers to the Cable Command 1 signal when configured to operate in its Flow Control mode. For details on setting the mode refer to "Cable Parameter: Command Mode" on page 72. The mode can most easily be set via the utility macros HPDI32\_CABLE\_COMMAND\_MODE\_LV\_FC/IN/LOW/HI (h) to set the mode to Flow Control (Line Valid), a general purpose input, a general purpose output driven low, or a general purpose output driven high, respectively. In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful. To configure the signal so that it can be ignored altogether, configure it as a general purpose input. When configured for Flow Control, the Line Valid timing must be configured. For details refer to "Transmitter Parameter: Line Valid On Count" (page 100) and "Transmitter Parameter: Line Valid Off Count" (page 100). The operation of Line Valid is also affected by the configuration of the Status Valid signal (see the next subsection).

#### 2.1.2.7. Status Valid

The Status Valid output signal reflects valid status data being presented at the cable interface. This signal is not required for Flow Control of continuous unstructured data streams so applications <u>should</u> configure it as GPIO so that it is ignored by the transmitter. As a Flow Control signal, Status Valid is driven high when valid status data is presented at the cable interface and is driven low otherwise (see below for additional information). Refer to Figure 8. The signal is synchronized with Tx Clock and changes state on the clock's rising edge. The Status Valid signal is driven on the cable interface only when the transmitter is enabled. When the transmitter is disabled the signal is not driven by the HPDI32. For enabling and disabling the transmitter, refer to "Enable" on page 19.

Figure 8 The Status Valid signal reflects valid status data being presented at the cable interface.

The Status Valid signal refers to the Cable Command 2 signal when configured to operate in its Flow Control mode. For details on setting the mode refer to "Cable Parameter: Command Mode" on page 72. The mode can most easily be set via the utility macros HPDI32\_CABLE\_COMMAND\_MODE\_\_SV\_FC/IN/LOW/HI (h) to set the mode to Flow Control (Status Valid), a general purpose input, a general purpose output driven low, or a general purpose output driven high, respectively. In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful. To configure the signal so that it can be ignored altogether, configure it as a general purpose input. When configured for Flow Control, the Status Valid signal must be configured. For details refer to "Transmitter Parameter: Status Valid Count" (page 102) and "Transmitter Parameter: Status Valid Mirror" (page 103). The configuration of the Status Valid signal has an affect on the Line Valid signal (see the previous subsection).

#### 2.1.2.8. Rx Ready

The Rx Ready input signal may be used by receiving devices to pause the flow of data from the HPDI32 transmitter. This signal is optional for Flow Control of continuous unstructured data streams so applications may instead configure it as GPIO so that it is ignored by the transmitter. As a Flow Control signal, Rx Ready is driven high to permit data flow and is driven low to pause data flow (see below for additional information). Refer to Figure 9. The

signal is synchronized with Tx Clock such that state changes are clocked in on the clock's rising edge. The Rx Ready input signal is driven by the receiving device, and not by the HPDI32 transmitter.

| Tx Clock           |      |       |

|--------------------|------|-------|

| Transmission Pause | Flow | Pause |

| Rx Ready           |      |       |

Figure 9 The receiving device can drive the Rx Ready signal to control data flow.

The Rx Ready signal refers to the Cable Command 3 signal when configured to operate in its Flow Control mode. For details on setting the mode refer to "Cable Parameter: Command Mode" on page 72. The mode can most easily be set via the utility macros HPDI32\_CABLE\_COMMAND\_MODE\_\_RR\_FC/IN/LOW/HI (h) to set the mode to Flow Control (Rx Ready), a general purpose input, a general purpose output driven low, or a general purpose output driven high, respectively. In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful. To configure the signal so that it can be ignored altogether, configure it as a general purpose input. When configured for Flow Control, the transmitter must be configured to utilize Rx Ready. Otherwise, the transmitter will ignore the Rx Ready input. For additional details refer to "Remote Throttle" on page 20.

#### 2.1.3. Control Options - continuous unstructured data stream

The following transmitter control options are discussed from the perspective of sending data via a continuous, unstructured data stream.

#### 2.1.3.1. Enable

This option is used to enable and disable the transmitter. When enabled, the transmitter is able to send data out over the cable interface, and will do so according to related control options. That is, the transmitter will send data when directed to do so. The related control options are discussed below. When disabled, the transmitter is unable to transmit data over the cable interface. If data is being transmitted at the time the transmitter becomes disabled, then data transmission will stop. The transmitter can most easily be enabled and disabled via the utility macros HPDI32\_TX\_ENABLE\_YES(h) and HPDI32\_TX\_ENABLE\_NO(h), respectively (see "Transmitter Parameter: Tx Enable" on page 99). In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful.

#### 2.1.3.2. Auto Start

This control option is used to tell the API to automatically begin data transmission over the cable interface when data is written to the HPDI32. If this option is enabled and the transmitter is enabled (see "Enable" on page 19), then the API will automatically initiate data transmission as data is being written (see hpdi32\_write() on page 67). The Auto Start feature uses the "Flow Control" *enable* option (page 20) to initiate data transmission. If Auto Start is disabled, then data flow must be controlled either manually via the "Flow Control" option (page 20) or remotely via the "Remote Throttle" option (page 20). Auto Start can most easily be enabled and disabled via the utility macros HPDI32\_TX\_AUTO\_START\_YES(h) and HPDI32\_TX\_AUTO\_START\_NO(h), respectively (see "Transmitter Parameter: Auto Start" on page 97). In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful.

#### 2.1.3.3. Auto Stop

This control option is available on current firmware versions, and <u>should always be disabled</u>. This option is presented here for completeness sake only. When the Auto Stop feature is available in firmware, disabling it could interfere with proper data flow. This option can most easily be enabled and disabled via the utility macros

HPDI32\_TX\_AUTO\_STOP\_YES(h) and HPDI32\_TX\_AUTO\_STOP\_NO(h), respectively (see "Transmitter Parameter: Auto Stop" on page 98). In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful.

#### 2.1.3.4. Flow Control

This option is used for local, manual control to permit or pause data flow over the cable interface. If the transmitter is enabled (see "Enable" on page 19) and data is in the Tx FIFO (see hpdi32\_write() on page 67), then data transmission over the cable interface will begin when this option is enabled. Data transmission will pause when this option is disabled. This option can most easily be used to start and stop data flow via the utility macros HPDI32\_TX\_FLOW\_CONTROL\_START(h) and HPDI32\_TX\_FLOW\_CONTROL\_STOP(h), respectively (see "Transmitter Parameter: Flow Control" on page 99). In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful.

**NOTE:** This option operates in parallel with the "Remote Throttle" option (page 20). These two features should generally not be used at the same time.

#### 2.1.3.5. Remote Throttle

This option configures the transmitter to use or not use the "Rx Ready" cable signal (page 18). If this option is enabled, and the "Rx Ready" signal is configured for Flow Control, then the transmitter will use that signal to either permit or pause data transmission over the cable interface. This makes it possible for the receiving device to pause data transfer as needed. When properly configured, the receiving device must drive the "Rx Ready" signal appropriately to affect the flow of data. This option can most easily be enabled and disabled via the utility macros HPDI32\_TX\_REMOTE\_THROTTLE\_ENABLE(h) and HPDI32\_TX\_REMOTE\_THROTTLE\_\_DISABLE(h), respectively (see "Transmitter Parameter: Remote Throttle" on page 101). In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful.

**NOTE:** For the remote throttling feature to function properly this option must be enabled and the "Rx Ready" signal (page 18) must be configured for Flow Control. Otherwise, the remote throttling feature will not operate properly.

**NOTE:** This option operates in parallel with the "Flow Control" option (page 20). These two features should generally not be used at the same time.

#### 2.1.3.6. Tx Overrun

This control option is available via the API, though it is rarely needed or used. This option is presented here for completeness sake only. This option is used to report cases where data has been written to the Tx FIFO when it was already full. This circumstance can occur only when applications write directly to the Tx FIFO or when applications use non-Demand Mode DMA (page 82) with the Manual DMA Control Mode option (page 81). Otherwise, the API prevents the Tx FIFO from being overfilled. This option can both report the overflow condition and clear the condition. This option can most easily be used to query for an overflow via the utility macro HPDI32\_TX\_OVERRUN\_GET(h,g) (see "Transmitter Parameter: Tx Overrun" on page 101). If the value returned for g equals HPDI32\_TX\_OVERRUN\_YES, then an overflow has occurred. An overflow can most easily be cleared via the utility macro HPDI32\_TX\_OVERRUN\_YES, the an overflow has occurred. An overflow can most easily be cleared via the utility macro HPDI32\_TX\_OVERRUN\_YES, the an overflow has occurred. An overflow can most easily be cleared via the utility macro HPDI32\_TX\_OVERRUN\_CLEAR(h). In the macros, h is the device handle obtained from hpdi32\_open() (page 59), and g is the value reported for a query. A return value of GSC\_SUCCESS indicates that the operation was successful.

#### 2.1.3.7. Tx/Rx Enabled Tri-State

This option controls how the "Tx Enabled" signal (page 16) is driven when the transmitter is disabled. Ordinarily, the signal is driven all the time, even when the transmitter is disabled. With this control option however, the signal

can be tri-stated when the transmitter is disabled. The signal's state when the transmitter is disabled can most easily be tri-stated or driven low via the utility macros HPDI32\_MISC\_TX\_RX\_TRI\_STATE\_YES(h) and HPDI32\_MISC\_TX\_RX\_TRI\_STATE\_NO(h), respectively (see "Miscellaneous Parameter: Tx/Rx Tri-State" on page 94). In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful.

**NOTE:** This option affects both the "Tx Enabled" signal (page 16) and the "Rx Enabled" signal (page 24).

#### 2.2. Transmitter Setup

The below outlines the basic steps needed to setup the HPDI32 for transmission to a receiving device. Follow these simple steps to help establish communications between the HPDI32 as a transmission device and a remote data reception device.

- 1. Configure the HPDI32 for data transmission as outlined in the following subsection. This includes enabling the transmitter.

- 2. Configure the remote device as needed for data reception operations.

- 3. The remote device should now be ready to receive data.

- 4. Initiate data transmission from the HPDI32 as appropriate.

## 2.3. Transmitter Configuration

The below guidelines give an overview of the programming steps needed to configure the HPDI32 transmitter to send data out over the cable interface.

- 1. Return the API and the device to a known state by calling hpdi32\_init() (page 55). This places the API and the HPDI32 in the same state it was in when first opened.

- 2. Configure the Miscellaneous Parameters, which can be done using the many HPDI32\_MISC\_XXX() macros (page 89).

- 3. Configure the Cable Parameters, which can be done using the many HPDI32\_CABLE\_XXX() macros (page 71).

- 4. Configure the FIFO Parameters, which can be done using the many HPDI32\_FIFO\_XXX() macros (page 73).

- 5. Configure the I/O Parameters, which can be done using the many HPDI32 IO XXX() macros (page 76).

- 6. Configure the Transmitter Parameters, which can be done using the many HPDI32\_TX\_XXX() macros (page 97). Enabling the transmitter is generally a very last step.

- 7. Configure the Interrupt Parameters, which can be done using the many HPDI32\_IRQ\_XXX() macros (page 86).

- 8. Write the desired data to the device. Refer to hpdi32 write () on page 67.

## 2.4. Receiver Operation

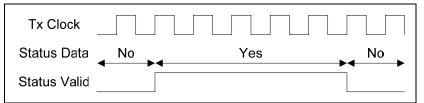

The receiver is that portion of the HPDI32 responsible for receiving data in from the cable interface. The receiver consists of numerous hardware features that operate under control of the SDK and the application. The hardware portion includes data FIFOs, firmware registers, control logic, and cable signal transceivers. The SDK portion consists of function calls, parameter identifiers, and parameter values. Together these components permit applications to retrieve data from the receiver as it is captured over the cable interface. An overall depiction is given in Figure 10. Some general guidelines for using the receiver are as follows. Each of these steps is further explained in subsequent paragraphs.

- 1. Identify the basic nature of the data's organization; continuous stream or a sequence of frames.

- 2. Identify the cable signals needed, how each will be used, and how each will operate.

- 3. Configure the cable signals according to how each will be used.

- 4. Configure the cable signal parameters so that each signal has the desired operating characteristics.

- 5. Identify if and how overall data flow will be permitted or paused.

- 6. Configure the device according to how overall data flow will be permitted or paused.

- 7. Configure the I/O read parameters.

- 8. Enable the receiver.

- 9. Read data from the device.

Figure 10 A depiction of the HPDI32 Receiver.

#### 2.4.1. Data Organization

The HPDI32 receiver supports two basic data organization schemes; a structured stream of frames divided into lines, and an unstructured continuous data stream. The structured format divides the overall data stream into a series of data frames, with each frame further divided into a series of data lines. In the unstructured format, data is captured without regard to such boundaries. By far, most HPDI32 applications have employed an unstructured data stream. For this reason the cable signal descriptions that follow assume the use of an unstructured data stream.

#### 2.4.2. Cable Signals - continuous unstructured data stream

For continuous unstructured data streams, some cable signals are required and some can be ignored or used for GPIO. The Rx Clock and Rx Data signals are always required. The Frame Valid signal is needed while the Line Valid and Status valid signals can be ignored or used for GPIO. If the remote device can be paused, then the Rx Ready signal may be used as the Remote Throttle output. Otherwise the Rx Ready signal can be ignored or used as GPIO.

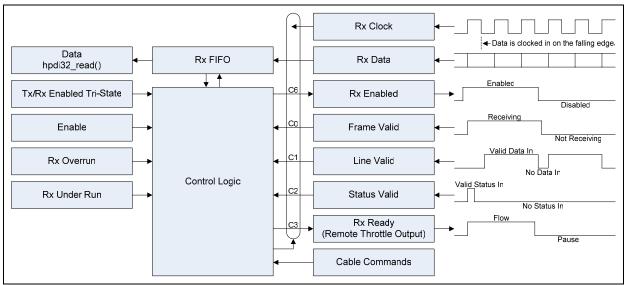

The simplest configuration usable for a continuous unstructured data stream is illustrated in Figure 11. This configuration uses the Rx Clock, Rx Data and Frame Valid signals, while all of the other receiver signals are unused. Even in this simplest configuration the unused signals must be configured, though they are configured so that they are unused by the receiver. The easiest way to do this is to configure the unused signals as general purpose inputs. Signal configuration is described below.

Figure 11 A simple continuous unstructured data stream cable configuration.

#### 2.4.2.1. Rx Clock

The Rx Clock input signal is the clock that synchronizes the receiver logic and which clocks data in from the cable interface. The Rx Clock must be provided by the remote transmitting device. The input is ignored when the receiver is disabled and must be driver when the receiver is enabled. For enabling and disabling the receiver, refer to "Enable" on page 26.

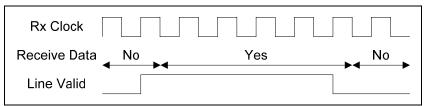

#### 2.4.2.2. Rx Data

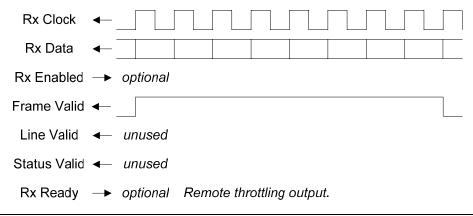

The Rx Data input signals are synchronized with the Rx Clock to record 32-bits of parallel data. The receiver clocks in the data on Rx Clock's falling edge. The transmitting device clocks out the data on the clock's rising edge. See Figure 12. The receiver hardware has a 32-bit data path, including the FIFOs and the cable transceivers. When the source data is less than 32-bits wide, it is aligned with the D0 bit and passed through the receiver as full 32-bit data words. When the source data is 8-bits wide it appears on cable signals D0 through D7. The upper 24 data signals are recorded, but can be ignored. When the source data is 16-bits wide it appears on cable signals D0 through D15. The upper 16 data signals are recorded, but can be ignored. The Rx Data signals are ignored when the receiver is disabled and must be driver when the receiver is enabled. For enabling and disabling the receiver, refer to "Enable" on page 26.

|                                                     | - |

|-----------------------------------------------------|---|

| The receiver clocks data<br>in on the falling edge. |   |

| Rx Data                                             | - |

Figure 12 Rx Data is synchronized with Rx Clock.

The cable data size is configurable. For details refer to "I/O Parameter: Data Size" on page 80. The data size can most easily be set via the utility macros HPDI32\_IO\_DATA\_SIZE\_\_RX\_32/16/8 (h) to specify the data size as 32, 16 or eight bits, respectively. In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful.

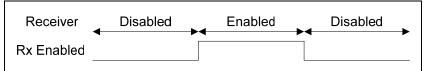

#### 2.4.2.3. Rx Enabled

The Rx Enabled output signal reflects the enabled state of the receiver. This signal is not required for Flow Control of continuous unstructured data streams so applications may instead configure it as GPIO so that it is ignored by the receiver. As a Flow Control signal, Rx Enabled is driven high when the receiver is enabled and is driven low when disabled (see the note below for alternation operation). The signal changes state as the receiver is enabled or disabled and is not synchronized with Rx Clock. Refer to Figure 13. For enabling and disabling the receiver, refer to "Enable" on page 26.

Figure 13 The Rx Enabled signal reflects the receiver enable state (default configuration).

**NOTE:** An alternative option configures Rx Enabled so that it is tri-stated when the receiver is disabled. Refer to "Tx/Rx Enabled Tri-State" on page 27.

The Rx Enabled signal refers to the Cable Command 6 signal when configured to operate in its Flow Control mode. For details on setting the mode refer to "Cable Parameter: Command Mode" on page 72. The mode can most easily be set via the utility macros HPDI32\_CABLE\_COMMAND\_MODE\_\_RE\_FC/IN/LOW/HI(h) to set the mode to Flow Control (Rx Enabled), a general purpose input, a general purpose output driven low, or a general purpose output driven high, respectively. In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful. To configure the signal so that it can be ignored altogether, configure it as a general purpose input.

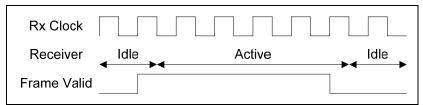

#### 2.4.2.4. Frame Valid

The Frame Valid input signal reflects the activity of the data reception process. When the Line Valid and Status Valid signals are not used for Flow Control, then Frame Valid effectively reflects valid receive data being available at the cable interface. The Frame Valid signal is required for Flow Control of continuous unstructured data streams so applications <u>must not</u> configure it as GPIO. As a Flow Control signal, Frame Valid is driven high when the reception process is active and is driven low when the reception process is idle. Refer to Figure 14. The signal is synchronized with Rx Clock. Frame Valid signal is ignored when the receiver is disabled and must be driver when the receiver is enabled. For enabling and disabling the receiver, refer to "Enable" on page 26.

Figure 14 The Frame Valid signal reflects the data reception process.

The Frame Valid signal refers to the Cable Command 0 signal when configured to operate in its Flow Control mode. For details on setting the mode refer to "Cable Parameter: Command Mode" on page 72. The mode can most easily be set via the utility macros HPDI32\_CABLE\_COMMAND\_MODE\_\_FV\_FC/IN/LOW/HI (h) to set the mode to Flow Control (Frame Valid), a general purpose input, a general purpose output driven low, or a general purpose output driven high, respectively. In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful. To configure the signal so that it can be ignored altogether, configure it as a general purpose input.

#### 2.4.2.5. Line Valid

The Line Valid input signal reflects valid receive data being presented at the cable interface. This signal is not required for Flow Control of continuous unstructured data streams so applications <u>should</u> configure it as GPIO so that it is ignored by the receiver. As a Flow Control signal, Line Valid is driven high when valid transmit data is presented at the cable interface and is driven low otherwise (see below for additional information). Refer to Figure 15. The signal is synchronized with Rx Clock. Line Valid should change state on the clock's rising edge as it is clocked in on the clock's falling edge. The Line Valid signal is ignored when the receiver is disabled and must be driver when the receiver is enabled. For enabling and disabling the receiver, refer to "Enable" on page 26.

Figure 15 The Line Valid signal reflects valid transmit data being presented at the cable interface.

The Line Valid signal refers to the Cable Command 1 signal when configured to operate in its Flow Control mode. For details on setting the mode refer to "Cable Parameter: Command Mode" on page 72. The mode can most easily be set via the utility macros HPDI32\_CABLE\_COMMAND\_MODE\_LV\_FC/IN/LOW/HI(h) to set the mode to Flow Control (Line Valid), a general purpose input, a general purpose output driven low, or a general purpose output driven high, respectively. In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful. To configure the signal so that it can be ignored altogether, configure it as a general purpose input.

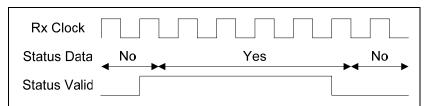

#### 2.4.2.6. Status Valid

The Status Valid input signal reflects valid status data being presented at the cable interface. This signal is not required for Flow Control of continuous unstructured data streams so applications <u>should</u> configure it as GPIO so that it is ignored by the receiver. As a Flow Control signal, Status Valid is driven high when valid status data is presented at the cable interface and is driven low otherwise (see below for additional information). Refer to Figure 16. The signal is synchronized with Rx Clock and is clocked in on the clock's falling edge. The Status Valid signal is ignored when the receiver is disabled and must be driver when the receiver is enabled. For enabling and disabling the receiver, refer to "Enable" on page 26.

Figure 16 The Status Valid signal reflects valid status data being presented at the cable interface.

The Status Valid signal refers to the Cable Command 2 signal when configured to operate in its Flow Control mode. For details on setting the mode refer to "Cable Parameter: Command Mode" on page 72. The mode can most easily be set via the utility macros HPDI32\_CABLE\_COMMAND\_MODE\_\_SV\_FC/IN/LOW/HI (h) to set the mode to Flow Control (Status Valid), a general purpose input, a general purpose output driven low, or a general purpose output driven high, respectively. In the macros, h is the device handle obtained from hpdi32\_open() (page 59). A return value of GSC\_SUCCESS indicates that the operation was successful. To configure the signal so that it can be ignored altogether, configure it as a general purpose input.

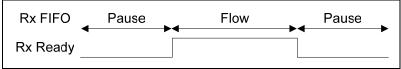

#### 2.4.2.7. Rx Ready

The Rx Ready output signal may be used by the receiver to pause the flow of data from the remote transmitting device. This signal is optional for Flow Control of continuous unstructured data streams so applications may instead configure it as GPIO so that it is ignored by the receiver. As a Flow Control signal, Rx Ready is driven high to permit data flow and is driven low to pause data flow. Refer to Figure 17. The signal reflects the Rx FIFO Almost Full Status. The signal is not synchronized with Rx Clock and changes state as the FIFO fill level changes. The Rx Ready signal is driven when the receiver is enabled and is tri-stated when the receiver is disabled. For enabling and disabling the receiver, refer to "Enable" on page 26.

Figure 17 The receiver drives the Tx Ready signal to control data flow.