## **User Manual**

# CC10C – ARM® i.MX 6 Rugged COM Express®

and CC10 COM Express®

### CC10C - Rugged COM Express® (VITA 59 RCE) with ARM® i.MX 6

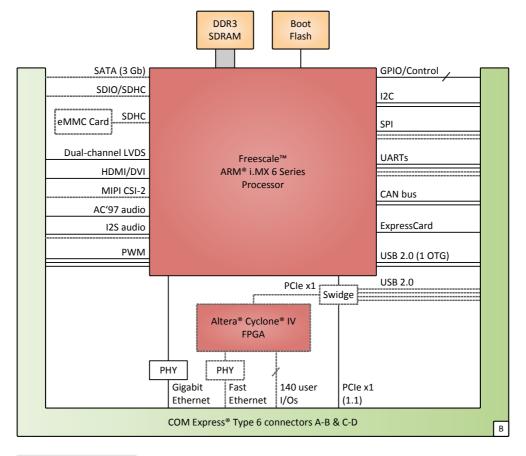

The CC10C is a Rugged COM Express® module (RCE) built around the Freescale<sup>TM</sup> ARM® i.MX 6 series of processors with a Cortex®-A9 architecture. Supporting different types of the i.MX 6Solo, 6DualLite, 6Dual and 6Quad families, the computer-on-module is widely scalable, e.g., to processing or graphics requirements. Where less performance is needed, you can optimize costs by choosing a single- or dual-core processor instead of a quad core.

Rugged COM Express® modules are 100% compatible to COM Express® but conform to the new VITA 59 standard (in process) which specifies the mechanics to make COM Express® modules suitable for operation in harsh environments. The CC10C is based on the "Compact", 95 x 95 mm form factor and Type 6 connector pin-out, and can even be semi-customized to become a standard COM Express® module, without much additional design effort.

With RCE-compliant mechanics for conduction cooling, the module's size extends to  $105 \times 105$  mm. It is embedded in a covered frame ensuring EMC protection and allowing efficient conductive cooling. Air cooling is also possible by applying a heat sink on top of the cover. Its optimized mechanics let the CC10C support an extended operating temperature range of -40 to +85°C.

The exclusive use of soldered components ensures that the COM withstands shock and vibration. The design is optimized for conformal coating.

Adding to its rugged design, the computer-on-module's range of supported functions leave almost nothing to wish for. With a maximum of 4 GB DDR3 RAM and an onboard eMMC device, the CC10C covers all basic memory needs. 3-Gbit SATA is provided for external mass storage.

One of the biggest strengths of the CC10C lies in its I/O flexibility. The i.MX 6 provides an abundance of onchip controllers and interfaces, including Gigabit Ethernet, USB 2.0 (also with OTG/client support) and PCI Express®. Different video outputs like LVDS and HDMI/DVI, audio and an optional camera interface make the card fit for multimedia applications. Other serial ports provide UARTs or CAN bus.

Where the processor's standard functions are not a perfect match, an onboard FPGA opens up 140 signal pins for user I/O. As IP cores are easy to integrate, the CC10C becomes a semi-custom solution with the suitable functionality even for more specialized applications.

The resulting I/O functionality in the ordered version depends on the customer's requirements and will always be a tailored combination of i.MX 6 and FPGA-based I/O, without the need for a completely new design.

For evaluation and development purposes a microATX carrier board, the XC15, is available.

For more information see the XC15 carrier board data sheet.

### **Diagram**

### **Technical Data**

### **CPU**

- Freescale<sup>TM</sup> ARM® i.MX 6 Series (ARM® Cortex®-A9 architecture)

- The following CPU types are available:

- i.MX6S (i.MX 6Solo family)

- i.MX6DL (i.MX 6DualLite family)

- i.MX6D (i.MX 6Dual family)

- i.MX6Q (i.MX 6Quad family)

See Table 1, Processor core options on CC10C, on page 24 for processor options and a feature matrix of the i.MX 6 series.

### Memory

- System Memory

- Soldered DDR3

- 1 GB, 2 GB, or 4 GB

- Boot Flash

- 4 MB, 8 MB, or 16 MB

### **Mass Storage**

- The following mass storage devices can be assembled:

- eMMC device, soldered; different sizes available

### **Graphics**

- Integrated in i.MX 6 processor

- Multi-stream-capable HD video engine delivering up to 1080p60 decode, 1080p30 encode and 3D video playback in HD

- Maximum resolution: 1920 x 1200 pixels (WUXGA)

- Superior 3D graphics performance with up to four shaders performing 200 Mt/s and OpenCL<sup>TM</sup> support

- Separate 2D and/or OpenVG Vertex acceleration engines for optimal user interface experience

- Stereoscopic image sensor support for 3D imaging

### **Onboard Interfaces**

- Available via COM Express® connectors

- Video

- One HDMI/DVI interface

- One LVDS interface, dual-channel

- One MIPI CSI-2 camera serial host interface; optional

- Andio

- One AC'97 audio interface

- One I2S audio interface

- SATA

- One channel, SATA Revision 2.x (3 Gbit/s); only with i.MX6D or i.MX6Q

- SDIO/SDHC

- One channel for MMC/SD/SDIO cards

- USB

- Two host channels, USB 2.0 (480 Mbit/s), or

- Six host channels, USB 2.0 (480 Mbit/s)

- One channel always implemented as OTG (On-The-Go) host/client port

- Ethernet

- One channel, 1000BASE-T (1 Gbit/s)

- One channel, 100BASE-T (100 Mbit/s); optional

- Two link and activity LED signals per channel

- PCI Express

- One x1 link (250 MB/s per link), PCIe® 1.1 (2.5 Gbit/s per lane)

- ExpressCard

- One interface

- CAN bus

- Two CAN bus channels, 2.0B CAN protocol, 1 Mbit/s

- Two additional CAN bus channels, 2.0A/B CAN protocol, 1 Mbit/s; with FPGA; optional

- External transceivers to be implemented on carrier board

- UART

- Up to six interfaces, up to 4 Mbit/s

- Physical interfaces RS232 or RS422/RS485 depending on interface controller and implementation on carrier board

- PWM

- Three PWM interfaces

- I2C

- Up to four I2C interfaces

- SPI

- Up to three SPI interfaces

- COM Express® control signals

- Four COM Express® control signals

- GPIO

- 9 GPIO lines, 4 GPO lines, 3 GPI lines

- 64 GPIO lines; with FPGA; optional

See Chapter 2.6 Customization Capabilities on page 26 for an overview of configurable I/O functions.

### **FPGA**

- No FPGA assembled, with custom configuration of i.MX 6 I/O interfaces, or

- FPGA Altera® Cyclone® IV, with custom IP core and i.MX 6 I/O configuration

- Total available pin count: 140 pins on COM Express® connectors

The IP cores that make sense and/or can be implemented depend on the board model, available pin counts and number of logic elements. Please contact MEN for information on feasibility.

### Supervision and Control

- · Power supervision and watchdog

- Temperature measurement

- i.MX 6 temperature measurement

- Additional onboard temperature sensor; optional

- Real-time clock, with supercapacitor or battery backup on the carrier board

### Computer-On-Module Standard

- CC10C: VITA 59 RCE: Rugged COM Express® in process

- With conduction cooling cover and frame

- Rugged COM Express® Compact, Module Pin-out Type 6

- CC10: PICMG COM.0 COM Express® Module Base Specification

- COM Express® Compact, Module Pin-out Type 6

### **Electrical Specifications**

- Supply voltage

- +12 V (9 to 16 V)

- Power consumption

- 12 W, measured in stress test using 15CC10C00, i.MX6Q quad-core @ 1.0 GHz

- 7.4 W, measured in test (activity on Gb Ethernet and 1 USB interface) using 15CC10C00, i.MX6Q quad-core @ 1.0 GHz

- 5 W, measured in test (activity on Gb Ethernet and 1 USB interface) using 15CC10-00, i.MX6S single-core @ 800 MHz

### **Mechanical Specifications**

- Dimensions

- CC10C: 105 mm x 105 mm x 18 mm (conforming to VITA 59 RCE Compact format, PCB mounted between a cover and a frame)

- CC10: 95 mm x 95 mm (conforming to PICMG COM.0 COM Express® Compact format)

- Weight

- CC10C: 356 g (model 15CC10C00)

- CC10: 40 g (model 15CC10-00)

### **Environmental Specifications**

- Temperature range (operation)

- 40°C to +85°C Tcase (VITA 59 cover/frame) (qualified components) (model 15CC10C00)

- -40°C to +85°C (qualified components) (model 15CC10-00)

- Temperature range (storage): -40°C to +85°C

- Cooling concept

- CC10C: Conduction-cooled according to VITA 59 RCE: Rugged COM Express® in process, PCB with conduction cooling wings, mounted between a cover and a frame

- CC10: Air-cooled according to PICMG COM.0 COM Express® standard

- Relative humidity (operation): max. 95% non-condensing

- Relative humidity (storage): max. 95% non-condensing

- Altitude: -300 m to +3000 m

- Shock: 50 m/s<sup>2</sup>, 30 ms (EN 61373)

- Vibration (function): 1 m/s<sup>2</sup>, 5 Hz to 150 Hz (EN 61373)

- Vibration (lifetime): 7.9 m/s<sup>2</sup>, 5 Hz to 150 Hz (EN 61373)

- Conformal coating; optional

### Reliability

- MTBF

- 652 986 h @ 40°C according to IEC/TR 62380 (RDF 2000) (model 15CC10C00)

- 1 233 470 h @ 40°C according to IEC/TR 62380 (RDF 2000) (model 15CC10-00)

### Safety

- Flammability

- UL 94V-0

### **EMC**

- EMC behavior generally depends on the system and housing surrounding the COM module.

- The Rugged COM Express® module in its cover and frame supports the system to meet the requirements of

- EN 55022 (radio disturbance)

- IEC 61000-4-2 (ESD)

- IEC 61000-4-3 (electromagnetic field immunity)

- IEC 61000-4-4 (burst)

- IEC 61000-4-5 (surge)

- IEC 61000-4-6 (conducted disturbances)

### **Software Support**

- Linux

- VxWorks®

For more information on supported operating system versions and drivers, please see the online data sheet.

### **BIOS**

• U-Boot Universal Boot Loader

For available standard configurations see the online data sheet.

### **Product Safety**

### **Electrostatic Discharge (ESD)**

Computer boards and components contain electrostatic sensitive devices. Electrostatic discharge (ESD) can damage components. To protect the board and other components against damage from static electricity, you should follow some precautions whenever you work on your computer.

- Power down and unplug your computer system when working on the inside.

- Hold components by the edges and try not to touch the IC chips, leads, or circuitry.

- Use a grounded wrist strap before handling computer components.

- Place components on a grounded antistatic pad or on the bag that came with the component whenever the components are separated from the system.

- Only store the board in its original ESD-protected packaging. Retain the original packaging in case you need to return the board to MEN for repair.

### **About this Document**

This user manual is intended only for system developers and integrators, it is not intended for end users.

It describes the hardware functions of the board, connection of peripheral devices and integration into a system. It also provides additional information for special applications and configurations of the board.

The manual does not include detailed information on individual components (data sheets etc.). A list of literature is given in the appendix.

### **Product Naming**

'CC10C' is used throughout this document to name the products described. However, descriptions are generally valid for the CC10 COM Express module, too. Specific differences will be mentioned explicitly.

### **History**

| Issue | Comments    | Date       |

|-------|-------------|------------|

| E1    | First issue | 2014-12-05 |

### **Conventions**

Indicates important information or warnings concerning proper functionality of the product described in this document.

in/out

The globe icon indicates a hyperlink that links directly to the Internet, where the latest updated information is available.

When no globe icon is present, the hyperlink links to specific elements and information within this document.

*italics* Folder, file and function names are printed in *italics*.

**bold Bold** type is used for emphasis.

mono A monospaced font type is used for hexadecimal numbers, listings, C function descriptions or wherever appropriate. Hexadecimal numbers

are preceded by "0x".

comments embedded into coding examples are shown in green text.

IRQ# Signal names followed by a hashtag "#" or preceded by a forward slash "/" indicate that this signal is either active low or that it becomes active at a falling edge.

Signal directions in signal mnemonics tables generally refer to the corresponding board or component, "in" meaning "to the board or component", "out" meaning "from it the board or component".

Blue vertical lines in the outer margin indicate sections where changes have been made to this version of the document.

MEN Mikro Elektronik GmbH 20CC10C00 E1 - 2014-12-05

### **Legal Information**

#### Changes

MEN Mikro Elektronik GmbH ("MEN") reserves the right to make changes without further notice to any products herein

### Warranty, Guarantee, Liability

MEN makes no warranty, representation or guarantee of any kind regarding the suitability of its products for any particular purpose, nor does MEN assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including, without limitation, consequential or incidental damages. TO THE EXTENT APPLICABLE, SPECIFICALLY EXCLUDED ARE ANY IMPLIED WARRANTIES ARISING BY OPERATION OF LAW, CUSTOM OR USAGE, INCLUDING WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE OR USE. In no event shall MEN be liable for more than the contract price for the products in question. If buyer does not notify MEN in writing within the foregoing warranty period, MEN shall have no liability or obligation to buyer hereunder.

The publication is provided on the terms and understanding that:

- 1. MEN is not responsible for the results of any actions taken on the basis of information in the publication, nor for any error in or omission from the publication; and

- 2. MEN is not engaged in rendering technical or other advice or services.

MEN expressly disclaims all and any liability and responsibility to any person, whether a reader of the publication or not, in respect of anything, and of the consequences of anything, done or omitted to be done by any such person in reliance, whether wholly or partially, on the whole or any part of the contents of the publication.

#### **Conditions for Use, Field of Application**

The correct function of MEN products in mission-critical and life-critical applications is limited to the environmental specification given for each product in the technical user manual. The correct function of MEN products under extended environmental conditions is limited to the individual requirement specification and subsequent validation documents for each product for the applicable use case and has to be agreed upon in writing by MEN and the customer. Should the customer purchase or use MEN products for any unintended or unauthorized application, the customer shall indemnify and hold MEN and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim or personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that MEN was negligent regarding the design or manufacture of the part. In no case is MEN liable for the correct function of the technical installation where MEN products are a part of.

#### **Trademarks**

All products or services mentioned in this publication are identified by the trademarks, service marks, or product names as designated by the companies which market those products. The trademarks and registered trademarks are held by the companies producing them. Inquiries concerning such trademarks should be made directly to those companies.

### Conformity

MEN products are no ready-made products for end users. They are tested according to the standards given in the Technical Data and thus enable you to achieve certification of the product according to the standards applicable in your field of application.

### **RoHS**

Since July 1, 2006 all MEN standard products comply with RoHS legislation.

Since January 2005 the SMD and manual soldering processes at MEN have already been completely lead-free. Between June 2004 and June 30, 2006 MEN's selected component suppliers have changed delivery to RoHS-compliant parts. During this period any change and status was traceable through the MEN ERP system and the boards gradually became RoHS-compliant.

### **WEEE Application**

The WEEE directive does not apply to fixed industrial plants and tools. The compliance is the responsibility of the company which puts the product on the market, as defined in the directive; components and sub-assemblies are not subject to product compliance.

In other words: Since MEN does not deliver ready-made products to end users, the WEEE directive is not applicable for MEN. Users are nevertheless recommended to properly recycle all electronic boards which have passed their life cycle.

Nevertheless, MEN is registered as a manufacturer in Germany. The registration number can be provided on request.

Copyright © 2014 MEN Mikro Elektronik GmbH. All rights reserved.

Germany MEN Mikro Elektronik GmbH

Neuwieder Straße 3-7 90411 Nuremberg Phone +49-911-99 33 5-0 Fax +49-911-99 33 5-901 E-mail info@men.de www.men.de France

MEN Mikro Elektronik SAS 18, rue René Cassin ZA de la Châtelaine 74240 Gaillard Phone +33 (0) 450-955-312 Fax +33 (0) 450-955-211 E-mail info@men-france.fr www.men-france.fr USA

MEN Micro Inc.

860 Penllyn Blue Bell Pike

Blue Bell, PA 19422

Phone (215) 542-9575

Fax (215) 542-9577

E-mail sales@menmicro.com

www.menmicro.com

### **Contents**

| 1 | Getting  | started                                          | 18 |

|---|----------|--------------------------------------------------|----|

|   | 1.1      | Map of the Board                                 | 18 |

|   |          | 1.1.1 CC10C Rugged COM Express                   | 18 |

|   |          | 1.1.2 CC10 COM Express                           | 19 |

|   | 1.2      | First Operation.                                 |    |

|   | 1.3      | Installing Operating System Software             | 21 |

|   | 1.4      | Installing Driver Software                       | 21 |

| 2 | Function | onal Description                                 | 22 |

|   | 2.1      | Power Supply and Control                         | 22 |

|   | 2.2      | Board Supervision and Management                 | 22 |

|   |          | 2.2.1 Temperature and Voltage                    | 22 |

|   |          | 2.2.2 Watchdog                                   | 22 |

|   | 2.3      | Reset                                            | 23 |

|   | 2.4      | Real-Time Clock (RTC)                            | 23 |

|   | 2.5      | Processor Core.                                  |    |

|   |          | 2.5.1 Thermal Considerations                     |    |

|   | 2.6      | Customization Capabilities                       |    |

|   |          | 2.6.1 FPGA I/O                                   |    |

|   |          | 2.6.2 ARM i.MX 6 I/O                             |    |

|   |          | 2.6.3 Interface Configurability Overview         |    |

|   | 2.7      | Memory                                           |    |

|   |          | 2.7.1 DRAM System Memory                         |    |

|   |          | 2.7.2 Boot Flash                                 |    |

|   | 2.8      | Mass Storage                                     |    |

|   |          | 2.8.1 Serial ATA (SATA)                          |    |

|   |          | 2.8.2 eMMC Multimedia Card (SDHC Interface)      |    |

|   |          | 2.8.3 SDIO/SDHC Interface                        |    |

|   | 2.9      | Multimedia                                       |    |

|   |          | 2.9.1 Video                                      |    |

|   | 2.10     | 2.9.2 Audio                                      |    |

|   |          | USB                                              |    |

|   | 2.11     | Ethernet                                         |    |

|   |          | 2.11.1 Ethernet MAC Addresses                    |    |

|   | 2.12     | 2.11.2 Ethernet Status LEDs                      |    |

|   |          | PCI Express                                      |    |

|   |          | ExpressCard Interface                            |    |

|   |          | CAN Bus                                          |    |

|   |          | UART Interfaces                                  |    |

|   |          | PWM                                              |    |

|   | 2.1/     | 2.17.1 I2C Interfaces Controlled by i.MX 6       |    |

|   |          | 2.17.1 I2C Interfaces Controlled by Onboard FPGA |    |

|   |          |                                                  |    |

|   | 2.18   | SPI     |                                           | 39 |

|---|--------|---------|-------------------------------------------|----|

|   | 2.19   | GPIO.   |                                           | 40 |

|   |        | 2.19.1  | GPIO Lines Controlled by i.MX 6           | 40 |

|   |        | 2.19.2  | GPIO Lines Controlled by Onboard FPGA     |    |

|   | 2.20   | Rugged  | COM Express (VITA 59)                     | 41 |

|   |        | 2.20.1  | Module Form Factors                       | 41 |

|   |        | 2.20.2  | Thermal Concept                           | 41 |

|   |        | 2.20.3  | COM Express Connectors                    | 43 |

|   |        | 2.20.4  | COM Express Control Signals               | 55 |

| 3 | U-Boot | Boot Lo | oader                                     | 56 |

|   | 3.1    |         | L                                         |    |

|   | 3.2    |         | Started: Setting Up Your Operating System |    |

|   | 0.2    | 3.2.1   | Setting Up the Boot File                  |    |

|   |        | 3.2.2   | Setting Up the Boot and TFTP Parameters   |    |

|   |        | 3.2.3   | Starting Up the Operating System          |    |

|   | 3.3    |         | ing with U-Boot.                          |    |

|   |        | 3.3.1   | Setting Up a Console Connection           |    |

|   |        | 3.3.2   | Entering the U-Boot Command Line          |    |

|   |        | 3.3.3   | User Interface Basics                     |    |

|   | 3.4    | U-Boot  | Images and Start-Up                       |    |

|   |        | 3.4.1   | Images                                    | 63 |

|   |        | 3.4.2   | Booting an Operating System               | 63 |

|   | 3.5    | Updatir | ng the Boot Flash                         | 67 |

|   |        | 3.5.1   | Update via the Serial Console             | 67 |

|   |        | 3.5.2   | Update via Network                        | 67 |

|   |        | 3.5.3   | Update via USB                            | 67 |

|   |        | 3.5.4   | Performing an Update                      | 67 |

|   |        | 3.5.5   | Updating U-Boot Image 1                   | 69 |

|   | 3.6    | Workin  | g with Interfaces and Devices             | 70 |

|   |        | 3.6.1   | PCI                                       | 70 |

|   |        | 3.6.2   | USB                                       | 70 |

|   |        | 3.6.3   | eMMC/SDHC                                 | 71 |

|   |        | 3.6.4   | I2C                                       | 71 |

|   |        | 3.6.5   | PWM                                       | 72 |

|   |        | 3.6.6   | Watchdog                                  | 72 |

|   | 3.7    | Diagno  | stic Tests                                | 73 |

|   | 3.8    | U-Boot  | Configuration and Organization            | 74 |

|   |        | 3.8.1   | Boot Flash Memory Map                     | 74 |

|   |        | 3.8.2   | Environment Variables                     | 74 |

|   | 3.9    |         | Commands                                  |    |

|   | 3.10   | Hardwa  | re Interfaces Not Supported by U-Boot     | 80 |

| 4 | Organi | ization o     | f the Board                                           | <b>81</b> |

|---|--------|---------------|-------------------------------------------------------|-----------|

|   | 4.1    | Global        | Address Map                                           | 81        |

|   | 4.2    | PCI De        | vices                                                 | 81        |

|   | 4.3    | <b>SMB</b> us | Devices                                               | 81        |

| 5 | Appen  | dix           | • • • • • • • • • • • • • • • • • • • •               | 82        |

|   | 5.1    |               | re and Web Resources                                  |           |

|   |        | 5.1.1         | COM Express                                           | 82        |

|   |        | 5.1.2         | Rugged COM Express                                    |           |

|   |        | 5.1.3         | CPU                                                   | 82        |

|   |        | 5.1.4         | eMMC                                                  | 82        |

|   |        | 5.1.5         | SATA                                                  | 82        |

|   |        | 5.1.6         | LVDS                                                  | 83        |

|   |        | 5.1.7         | DVI                                                   | 83        |

|   |        | 5.1.8         | USB                                                   | 83        |

|   |        | 5.1.9         | Ethernet                                              | 83        |

|   |        | 5.1.10        | PCI Express                                           | 83        |

|   |        | 5.1.11        | AC'97 Audio                                           | 83        |

|   |        | 5.1.12        | CAN Bus                                               | 84        |

|   |        | 5.1.13        | I2C Bus                                               | 84        |

|   | 5.2    | Finding       | out the Product's Article Number, Revision and Serial |           |

|   |        | Number        | r                                                     | 84        |

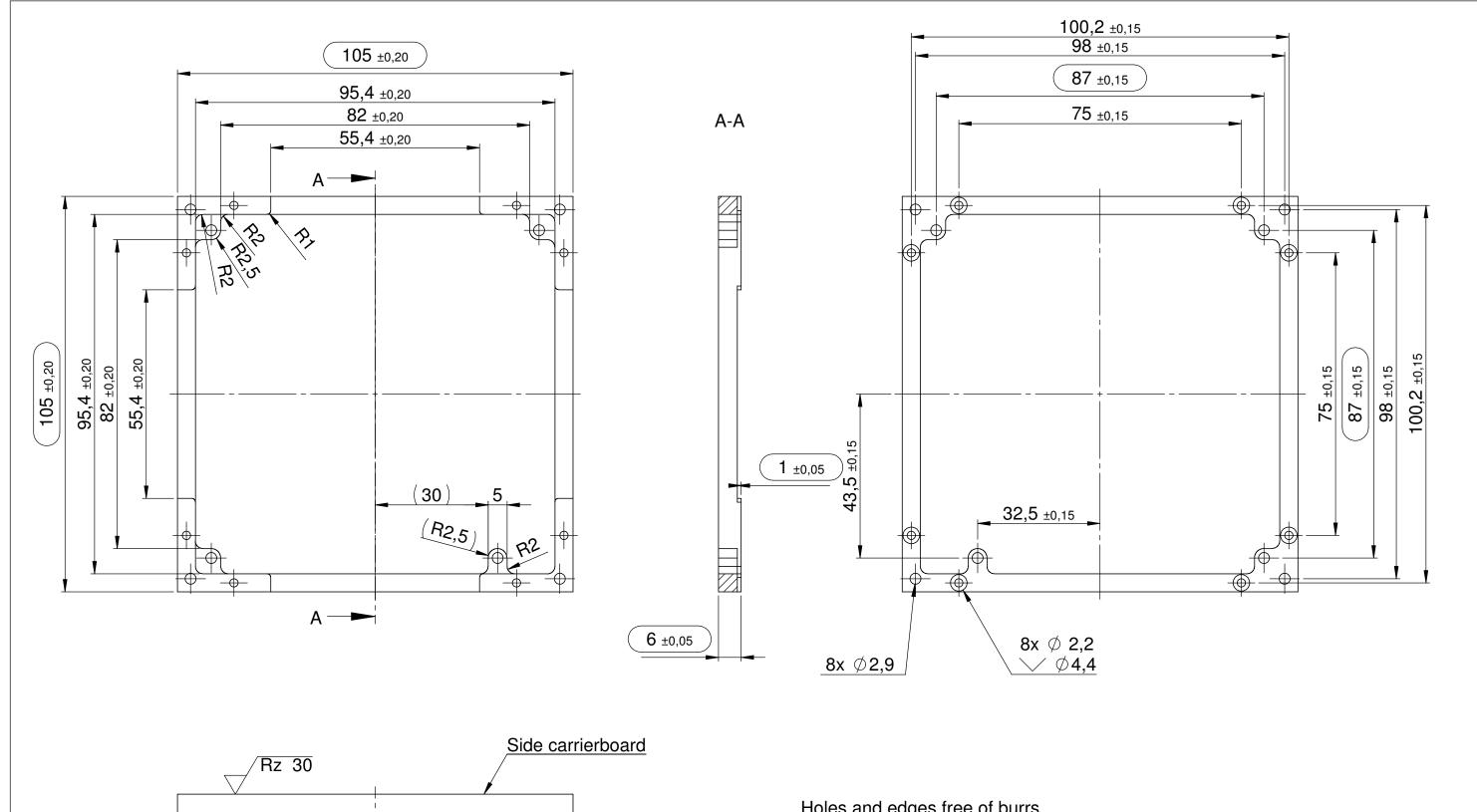

|   | 5.3    | Dimens        | ions of CC10C Rugged COM Express Compact Module       | 84        |

### **Figures**

| _         | 1,                                                                                 |    |

|-----------|------------------------------------------------------------------------------------|----|

| Figure 2. | Map of the board (CC10 COM Express)                                                | 19 |

| Figure 3. | Rugged COM Express Compact module with cooling wings (PCB without frame and cover) | 42 |

| Figure 4. | Labels giving the product's article number, revision and serial number             | 84 |

| Tablas    |                                                                                    |    |

| Tables    |                                                                                    |    |

| Table 1.  | Processor core options on CC10C                                                    | 24 |

| Table 2.  | Interface configurability overview (COM Express connectors)                        | 27 |

| Table 3.  | Multiplexed interfaces for i.MX 6 or FPGA use                                      | 29 |

| Table 4.  | Ethernet status LED modes                                                          |    |

| Table 5.  | UART interface control and configurability                                         |    |

| Table 6.  | Form factors defined for Rugged COM Express                                        |    |

| Table 7.  | Pin assignment of COM Express connectors J1 and J2 – CC10C                         | 43 |

| Table 8.  | Pin assignment of COM Express connectors J1 and J2 – CC10                          | 47 |

| Table 9.  | Signal Mnemonics                                                                   |    |

| Table 10. | U-Boot – Boot Flash memory map                                                     | 74 |

| Table 11. | U-Boot – Environment variables – OS boot.                                          | 74 |

| Table 12. | U-Boot – Environment variables – Network                                           | 75 |

| Table 13. | U-Boot – Environment variables – Console                                           | 76 |

| Table 14. | U-Boot – Environment variables – Other.                                            | 76 |

| Table 15. | U-Boot – Command reference                                                         | 77 |

| Table 16. | Global address map                                                                 | 81 |

|           | PCI devices.                                                                       |    |

| Table 18. | SMBus devices                                                                      | 81 |

### 1 Getting Started

This chapter gives an overview of the board and some hints for first installation.

### 1.1 Map of the Board

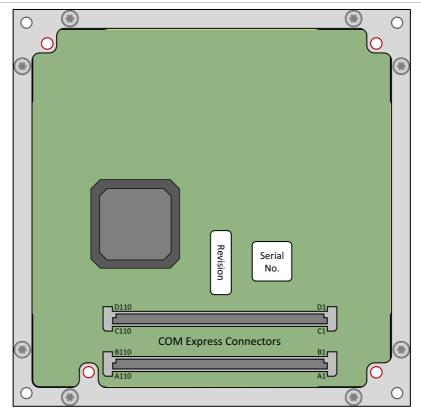

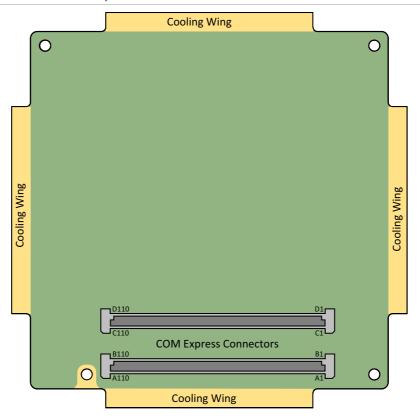

### 1.1.1 CC10C Rugged COM Express

The following board map shows the board inside the cover and frame from its connector side (bottom). The cover includes holes for mounting the Rugged COM Express module onto a carrier.

If you want to use a Rugged COM Express (RCE) module together with a COM Express carrier or other custom carrier board, please make sure that the carrier provides appropriate 'landing zones' for the RCE frame.

For the exact dimensions of CC10C, see Chapter 5.3 Dimensions of CC10C Rugged COM Express Compact Module on page 84.

Figure 1. Map of the board (CC10C Rugged COM Express)

- OM Express screw holes for installation on the carrier board.

- Screws connecting the frame and cover of the module. Do not remove.

- O Holes for optional carrier board fixing when used as wall-mount assembly

For more information on Rugged COM Express mechanics see the VITA 59 specification: Chapter 5.1.2 Rugged COM Express on page 82.

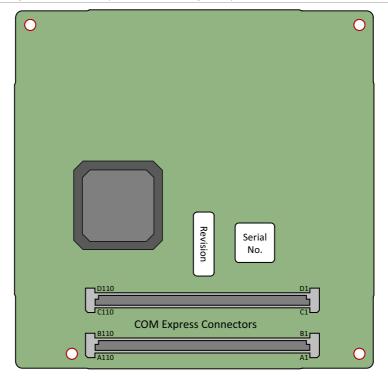

### 1.1.2 CC10 COM Express

The following board map shows the COM.0 CC10 board from its connector side (bottom).

For the dimensions of COM Express Compact modules, please see the COM Express COM.0 specification. See Chapter 5.1.1 COM Express on page 82.

Figure 2. Map of the board (CC10 COM Express)

OM Express screw holes for installation on the carrier board.

### 1.2 First Operation

You can use the following check list when installing the board for the first time and with minimum configuration using a Windows host PC.

The U-Boot firmware is preinstalled on the CC10C and is preconfigured for the board.

- ☑ Power down the system.

- ☑ If you use a Rugged COM Express (RCE) module embedded into an aluminum frame together with a COM Express carrier or other custom carrier board, please make sure that the carrier provides appropriate 'landing zones' for the RCE frame.

For the exact dimensions of CC10C, see Chapter 5.3 Dimensions of CC10C Rugged COM Express Compact Module on page 84.

- ☑ Plug the CC10C on your carrier board, making sure that the COM Express connectors are properly aligned.

- ☑ Fasten the four screws connecting the COM Express module to the carrier (marked in red in Figure 1, Map of the board (CC10C Rugged COM Express) on page 18 and Figure 2, Map of the board (CC10 COM Express) on page 19).

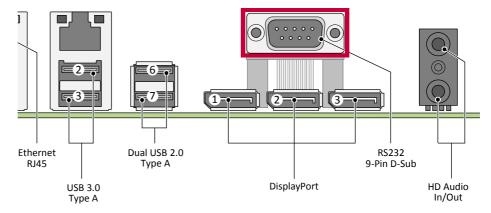

To provide a better example, we assume that you are using MEN's standard evaluation carrier, XC15, which provides the necessary connections for a Windows host PC.

You can find more information on the XC15 in the XC15 User Manual, which is available for download on MEN's website.

☑ Connect a Windows PC to the RS232 interface of XC15.

- ☑ Power-up the system.

- ☑ Start up a terminal program on your Windows PC, e.g., HyperTerm, and open a terminal connection.

- ☑ Set your terminal connection to the following protocol:

- 115 200 baud data transmission rate

- 8 data bits

- 1 stop bit

- No parity

☑ U-Boot will load and then display a command line. The terminal displays a message similar to the following:

```

U-Boot 2013.01 (Sep 10 2014 - 17:58:33) MEN CC10-Quad VO.4 (standard)

Freescale i.MX6Q rev1.2 at 984 MHz

Reset cause: POR

Board: MEN CC10

I2C:

ready

RAM Configuration:

Bank #0: 10000000 2 GiB

WARNING: Caches not enabled

MMC: FSL_SDHC: 0, FSL_SDHC: 1

SF: Detected N25Q032 with page size 64 KiB, total 4 MiB

auto-detected panel HDMI

enable_hdmi: setup HDMI monitor

Display: HDMI (1024x768)

In:

serial

Out: serial

Err:

serial

Thermal fuse is 0x59e4ec7d, raw_25c=1438 raw_hot=1260 hot_temp=125 C scale=0.56

Temperature raw=1378 temperature= 58.70 C

Net: using phy at Nr.3, phy_id=0x221622

FEC [PRIME]

=>

```

☑ Now you can make configurations for your operating system in the U-Boot boot loader.

See the detailed description in Chapter 3 U-Boot Boot Loader on page 56.

### 1.3 Installing Operating System Software

The board supports Linux and VxWorks.

By default, no operating system is installed on the board. Please refer to the respective manufacturer's documentation on how to configure your operating system image!

- You can find any BSP software available on the CC10C pages on MEN's website.

- The U-Boot Chapter of this manual describes the first steps of how to get your operating system running, see Chapter 3.2 Getting Started: Setting Up Your Operating System on page 57.

### 1.4 Installing Driver Software

For a detailed description on how to install driver software please refer to the respective documentation of the software package to be installed.

You can find any driver software available for download on the CC10C pages on MEN's website.

### 2 Functional Description

The following describes the individual functions of the board and their configuration on the board. There is no detailed description of the individual controller chips and the CPU. They can be obtained from the data sheets or data books of the semiconductor manufacturer concerned.

See Chapter 5.1 Literature and Web Resources on page 82.

Please note: The board BSPs for the different operating systems may not support all the functions of the CC10C. For more information on hardware support please see the respective BSP data sheet on MEN's website.

### 2.1 Power Supply and Control

The CC10C board is supplied with +12 V (9 to 16 V) only via COM Express connectors J1/J2. All other required voltages are generated on the board.

The CC10C supports the *PWR\_OK* signal (input from main power supply) available at the COM Express connector according to the PICMG COM.0 standard.

The CC10C supports the i.MX 6 processors' power down modes to reduce power consumption.

### 2.2 Board Supervision and Management

### 2.2.1 Temperature and Voltage

The board supports temperature measurement and voltage monitoring as integrated in the i.MX 6 processor.

A voltage monitor supervises all onboard core voltages and holds the CPU in reset condition until the supply voltage is within its nominal values.

As an option, the board is also available with an additional onboard temperature sensor.

### 2.2.2 Watchdog

The CC10C supports the watchdog integrated in the i.MX 6 processor.

The watchdog can be enabled or disabled and can be triggered by a software application. This function is supported by the CC10C board support packages.

The watchdog provides timeout periods from 0.5 to 128 seconds with a time resolution of 0.5 seconds.

### 2.3 Reset

The CC10C provides the reset signals *CB\_RESET#* (carrier board reset) and *SYS\_RESET#* (reset button input) which are available at the COM Express connector according to the PICMG COM.0 standard.

You can find the pinout for the reset signals in Chapter 2.20.3 COM Express Connectors on page 43.

### 2.4 Real-Time Clock (RTC)

The board includes a real-time clock inside the i.MX 6 processor. For data retention during power off the RTC can be backed up by a supercapacitor or battery installed on the carrier.

For back-up voltage supply from the carrier board, the board supports a 3 V input using J1 pin *VCC\_RTC* (J1-A47).

Also see pinout in Chapter 2.20.3 COM Express Connectors on page 43.

You can set the system date and time through the U-Boot firmware.

### 2.5 Processor Core

The computer-on-module is built around Freescale's i.MX 6 scalable multicore platform, which includes single-, dual- and quad-core families based on the ARM Cortex-A9 architecture. The i.MX 6 series combines the power-efficient processing capabilities of ARM Cortex-A9 with 3D and 2D graphics as well as high-definition video, providing multimedia performance next to serial connectivity.

Table 1. Processor core options on CC10C

| Family                | Cores | Core<br>Frequency     | L2 Cache | DDR3 Width and Clock | Video                                                                                       | SATA     |

|-----------------------|-------|-----------------------|----------|----------------------|---------------------------------------------------------------------------------------------|----------|

| i.MX6S<br>(Solo)      | 1     | 800 MHz or<br>1.0 GHz | 512 KB   | 32 bits, 400 MHz     | 3D graphics with one<br>shader, 2D graphics<br>engine, two MIPI CSI-2<br>data lanes         | -        |

| i.MX6DL<br>(DualLite) | 2     | 800 MHz or<br>1.0 GHz | 512 KB   | 64 bits, 400 MHz     | 3D graphics with one<br>shader, 2D graphics<br>engine, two MIPI CSI-2<br>data lanes         | -        |

| i.MX6D<br>(Dual)      | 2     | 850 MHz or<br>1.0 GHz | 1 MB     | 64 bits, 533 MHz     | 3D graphics with four<br>shaders, two 2D graphics<br>engines, four MIPI CSI-2<br>data lanes | 3 Gbit/s |

| i.MX6Q<br>(Quad)      | 4     | 850 MHz or<br>1.0 GHz | 1 MB     | 64 bits, 533 MHz     | 3D graphics with four<br>shaders, two 2D graphics<br>engines, four MIPI CSI-2<br>data lanes | 3 Gbit/s |

Further options such as higher core frequencies are available on request, using processors from Freescale's "Consumer" category. However, these processors do not support extended operating temperature ranges.

The processor families above support -40 to +85°C.

The CC10C supports the i.MX 6 processors' power down modes to reduce power consumption.

### 2.5.1 Thermal Considerations

The power dissipation of CC10C heavily depends on its processor and I/O configuration and on the workload.

As measured during a stress test (e.g., with busy Ethernet and graphics functions), the CC10C generates a typical 12 W of power dissipation with an i.MX6Q quadcore processor operated at 1.0 GHz.

If stripped down to a single-core processor and with lower I/O load, the COM's power dissipation reduces to approx. 5 W, as measured in a test with activity on the Gigabit Ethernet interface and on one USB interface.

**Rugged COM Express modules (VITA 59)** are enclosed inside a cover and frame and therefore provides a flexible thermal interface that can be used as needed to fulfill the thermal needs of the application. Typically you should use it for conduction cooling or convection cooling. It depends on the system configuration and airflow if an additional heat sink is needed or not. In any case you should check your thermal conditions and implement appropriate cooling.

See also Chapter 2.20.2 Thermal Concept on page 41.

Please note that if you do not use the cover and frame supplied by MEN and/or no heat sink, warranty on functionality and reliability of the CC10C may cease. If you have any questions or problems regarding thermal behavior, please contact MEN.

**COM Express modules (COM.0)** may also need additional cooling facilities, depending on the configuration of the board and the general system design, i.e. integration of the computer-on-module into the system. Implementation is up to the customer.

A general heat spreader solution, e.g., for evaluation purposes, is available from MEN as an accessory for CC10 (part number 05CC10-00).

See the CC10C pages on MEN's website for ordering information.

### 2.6 Customization Capabilities

The CC10C has the capability of implementing all kinds of storage and I/O functions on a wide scale. Two main components control I/O on the board:

- ARM i.MX 6 processor

- Onboard FPGA

The signals are available at the COM Express connector. Many pins are multiplexed to be driven by **either** i.MX 6 **or** FPGA signals.

For an overview of signals multiplexed to use either i.MX 6 or FPGA I/O, see Chapter 2.6.3.1 Multiplexed Interfaces for i.MX 6 or FPGA I/O on page 29.

MEN offers different configurations with and without FPGA as standard versions. Depending on your I/O needs, MEN can provide a semi-custom version of the board with the functions desired.

While the CC10C is extremely flexible in its I/O configuration, line routing is also complex and not all combinations are possible. The configuration of the available standard versions of the COM reflect both the i.MX 6 and FPGA capabilities, as can be seen in the standard COM Express connector pinouts.

You can find the pinouts for different standard board versions, with and without an FPGA, in Chapter 2.20.3 COM Express Connectors on page 43.

#### 2.6.1 FPGA I/O

With an Altera Cyclone IV FPGA assembled, the CC10C provides 140 FPGA-controlled I/O pins. While some interfaces are implemented by standard with an FPGA assembled, IP cores with the desired functionality are integrated as needed for all free pins.

The CC10C FPGA can be updated in the field. This is supported by the available BSPs and by a software tool for FPGA Flash updates provided by MEN.

You can find any BSP and driver software available for download on the CC10C pages on MEN's website.

You can find the pinout of FPGA-controlled signals in Table 7, Pin assignment of COM Express connectors J1 and J2 – CC10C on page 43.

More information on FPGA technology and usable IP cores is available on the MEN website in the "User I/O in FPGA" section.

### 2.6.2 ARM i.MX 6 I/O

Since the i.MX 6 series of processors come with an abundance of I/O functions, no FPGA may be needed for many applications.

### 2.6.3 Interface Configurability Overview

This chapter gives an overview of the board's interface options. In any case we recommend that you contact our sales team for semi-custom configuration of CC10C for your requirements.

Contact MEN's sales team for further information.

The following table relates to the pinout of the COM Express connectors. It gives an interface list to show what is configurable on the board.

It does **not** give a full list of options of the board. E.g., assembly of an eMMC is a storage option, but eMMC signals are not relevant for the connector pinout.

Please see Table 1, Processor core options on CC10C, on page 24 for a feature matrix of the i.MX 6 series.

Table 2. Interface configurability overview (COM Express connectors)

| Function             | Configura-<br>bility                 | i.MX6<br>I/O | FPGA<br>I/O | Configurable | Standard<br>CC10C (RCE<br>VITA 59)<br>Configuration | Standard<br>CC10 (COM.0)<br>Configuration | Comment                                                                               |

|----------------------|--------------------------------------|--------------|-------------|--------------|-----------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------|

| Storage              |                                      |              |             |              |                                                     |                                           |                                                                                       |

| SATA                 | 1 interface                          | х            |             | Х            | 1                                                   | -                                         | Depends on i.MX 6 processor type                                                      |

| SDIO/SDHC            | 1 interface                          | х            |             |              | 1                                                   | 1                                         |                                                                                       |

| Multimedia           |                                      |              |             |              |                                                     |                                           |                                                                                       |

| LVDS                 | 1 dual-<br>channel<br>interface      | х            |             |              | 1                                                   | 1                                         |                                                                                       |

| HDMI/DVI             | 1 interface                          | х            |             |              | 1                                                   | 1                                         |                                                                                       |

| MIPI CSI-2<br>camera | 1 interface, 2<br>or 4 data<br>lanes | х            |             | х            | -                                                   | 1<br>(2 data lanes)                       | Data lanes depend on i.MX 6 processor type                                            |

| AC'97 audio          | 1 interface                          | х            |             |              | 1                                                   | 1                                         |                                                                                       |

| I2S audio            | 1 interface                          | х            |             |              | 1                                                   | 1                                         |                                                                                       |

| I/O                  |                                      |              |             |              |                                                     |                                           |                                                                                       |

| USB 2.0              | 2 or 6 interfaces                    | х            |             | х            | 6                                                   | 2                                         |                                                                                       |

| Ethernet             | 1 interface,<br>1000BASE-T           | х            |             |              | 1                                                   | 1                                         |                                                                                       |

|                      | 1 interface,<br>100BASE-T            |              | х           | х            | 1                                                   | -                                         | Dedicated FPGA I/O,<br>with Ethernet PHY (in<br>addition to 140<br>configurable pins) |

| PCI Express<br>1.1   | 1 x1 link                            | х            |             |              | 1                                                   | 1                                         |                                                                                       |

| ExpressCard          | 1 interface                          | х            |             |              | 1                                                   | 1                                         |                                                                                       |

| Function                  | Configura-<br>bility                                                  | i.MX6<br>I/O | FPGA<br>I/O | Configurable          | Standard<br>CC10C (RCE<br>VITA 59)<br>Configuration | Standard<br>CC10 (COM.0)<br>Configuration | Comment                                                                                                                                                           |

|---------------------------|-----------------------------------------------------------------------|--------------|-------------|-----------------------|-----------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UARTS                     | Up to 4<br>interfaces<br>with different<br>handshake<br>configuration | х            |             | х                     | 2 (without<br>handshake<br>lines)                   | 4 (2 with<br>handshake<br>lines)          |                                                                                                                                                                   |

|                           | Up to 4<br>interfaces<br>with different<br>handshake<br>configuration |              | х           | х                     | 4 (with<br>handshake<br>lines)                      | -                                         |                                                                                                                                                                   |

| CAN bus                   | 2 channels<br>2.0B CAN<br>protocol                                    | х            |             |                       | 2                                                   | 2                                         |                                                                                                                                                                   |

|                           | 2 channels<br>2.0A/B CAN<br>protocol                                  |              | х           | х                     | 2                                                   | -                                         |                                                                                                                                                                   |

| GPIOs                     | 9 GPIOs,<br>4 GPOs,<br>3 GPIs                                         | х            |             |                       | 9 GPIOs,<br>4 GPOs,<br>3 GPIs                       | 9 GPIOs,<br>4 GPOs,<br>3 GPIs             |                                                                                                                                                                   |

|                           | 64 GPIOs                                                              |              | х           | х                     | 64                                                  | -                                         | More lines possible with custom FPGA configuration                                                                                                                |

| PWM                       | 3 interfaces                                                          | х            |             |                       | 3                                                   | 3                                         | A fourth PWM signal is used for LVDS backlight control                                                                                                            |

| I2C                       | 2 interfaces                                                          | х            |             | x<br>(see<br>Comment) | 2<br>(without MIPI<br>CSI-2 support)                | 2<br>(with MIPI CSI-<br>2 support)        | Specific MIPI CSI-2<br>device support optional                                                                                                                    |

|                           | 2 interfaces                                                          |              | х           | x                     | 2                                                   | -                                         |                                                                                                                                                                   |

| SPI                       | Up to 3 interfaces                                                    | х            |             | х                     | 1                                                   | 3                                         |                                                                                                                                                                   |

| COM<br>Express<br>Signals | 4 control signals                                                     | Х            |             |                       | 4                                                   | 4                                         | Other COM.0 defined control signals may be usable through GPIOs                                                                                                   |

| FPGA-<br>controlled I/O   | Up to 140<br>signals                                                  |              | х           | x                     | 140                                                 | -                                         | This gives the total number of signals available for free configuration. For standard versions they already include some interfaces implemented through the FPGA. |

### 2.6.3.1 Multiplexed Interfaces for i.MX 6 or FPGA I/O

The following interfaces are multiplexed to be driven by **either** i.MX 6 **or** FPGA.

Table 3. Multiplexed interfaces for i.MX 6 or FPGA use

| : MV C Function                  | FP               | COM O Croup                                    |             |  |

|----------------------------------|------------------|------------------------------------------------|-------------|--|

| i.MX 6 Function                  | I/O Signals      | Default Function                               | COM.0 Group |  |

| UART1 (SER1)<br>CTS and RTS      | FPGA_IO[17:18]   |                                                | DDI2_CTRL   |  |

| UART2 (SER2)<br>with CTS and RTS | FPGA_IO[77:80]   | UART2 (SER2)<br>with CTS and RTS               | PEG         |  |

| UART3 (SER3)                     | FPGA_IO[83:84]   | UART3 (SER3)                                   |             |  |

| MIPI CSI I2C                     | FPGA_IO[81:82]   | UART3 (SER3)<br>handshake lines<br>DSR and DTR |             |  |

| MIPI CSI                         | FPGA_IO[89:90]   | UART4 (SER4)<br>RTS and CTS                    |             |  |

|                                  | FPGA_IO[91:92]   | UART3 (SER3)<br>DCD and RI                     |             |  |

|                                  | FPGA_IO[93:94]   | UART5 (SER5)                                   |             |  |

|                                  | FPGA_IO[96:97]   | UART5 (SER5)<br>CTS and RTS                    |             |  |

|                                  | FPGA_IO[98:99]   |                                                |             |  |

|                                  | FPGA_IO[101:102] |                                                |             |  |

| SPI2/3                           | FPGA_IO[34:38]   |                                                |             |  |

|                                  | FPGA_IO[42:43]   |                                                |             |  |

|                                  | FPGA_IO[45:46]   |                                                |             |  |

For a complete overview of configurable UARTs and handshake lines, see Chapter Table 5. UART interface control and configurability on page 37.

### 2.6.3.2 Standard CC10C FPGA Configuration

The following MEN IP cores are implemented in the standard CC10C FPGA (board version 15CC10C00):

- 16Z087\_ETH Ethernet controller (10/100Base-T)

- 16Z125\_UART UART controller (four UARTs)

- 16Z029\_CAN CAN controller (two channels)

- 16Z127\_GPIO GPIO controller (64 lines)

- 16Z001\_SMB SMBus controller (two I2C interfaces)

### 2.7 Memory

### 2.7.1 DRAM System Memory

The board provides up to 4 GB onboard, soldered DDR3 (double data rate) SDRAM. Depending on the processor family used, the memory bus is up to 64 bits wide and operates with up to 533 MHz.

### 2.7.2 Boot Flash

The boot Flash memory contains the U-Boot/operating system bootstrapper and U-Boot environment variables. It can also contain an operating system image and application software.

The size of the boot Flash is scalable up to 16 MB, with a default size of 4 MB.

See also Chapter 3.8.1 Boot Flash Memory Map on page 74.

### 2.8 Mass Storage

### 2.8.1 Serial ATA (SATA)

The CC10C provides one SATA port controlled by the i.MX 6 processor at the COM Express connector using pin group SATA 0 according to the PICMG COM.0 standard.

The interface is compliant with SATA Revision 2.x and supports transfer rates of 3.0 Gbit/s.

The SATA activity indicator (SATA\_ACT#) according to COM.0 is also supported.

You can find the pinout for the SATA signals in Chapter 2.20.3 COM Express Connectors on page 43.

This interface type may be implemented differently on every board version. Board versions assembled with the i.MX6S (Solo) or i.MX6DL (DualLite) **do not provide** the SATA interface.

### 2.8.2 eMMC Multimedia Card (SDHC Interface)

The CC10C comes with a 4-GB eMMC multimedia device already soldered on the board. Higher capacities are available as hardware options.

The eMMC is controlled by the i.MX 6 uSDHC Controller (Ultra Secured Digital Host Controller).

### 2.8.3 SDIO/SDHC Interface

CC10C supports an additional SDIO/SDHC interface controlled by the i.MX 6 processor at the COM Express connector according to the PICMG COM.0 standard.

You can find the pinout for the SDIO/SDHC signals in Chapter 2.20.3 COM Express Connectors on page 43.

### 2.9 Multimedia

### 2.9.1 Video

One of the i.MX 6 processors' strengths are next-generation graphics and high-definition video capabilities. Controlling all of the CC10C's graphics functions, the i.MX 6 processor supports the following features:

- Multi-stream-capable HD video engine delivering up to 1080p60 decode, 1080p30 encode and 3D video playback in HD

- Maximum resolution: 1920 x 1200 pixels (WUXGA+)

- Superior 3D graphics performance with up to four shaders performing 200 Mt/s and OpenCL<sup>TM</sup> support

- Separate 2D and/or OpenVG Vertex acceleration engines for optimal user interface experience

- Stereoscopic image sensor support for 3D imaging

- For processor options and the main differences in graphics capability, compare Table 1, Processor core options on CC10C on page 24.

- For a detailed description of each i.MX 6 family's graphics subsystem, please refer to the respective Freescale reference manual.

The CC10C supports the following interfaces to/from the graphics subsystem:

- HDMI/DVI, standard for all versions

- LVDS, dual-channel, standard for all versions

- MIPI CSI camera interface, standard for CC10

You can find the pinout for the graphics signals in Chapter 2.20.3 COM Express Connectors on page 43.

### 2.9.1.1 HDMI/DVI

The CC10C uses Digital Display Interface DDI1 at the COM Express connector according to the PICMG COM.0 standard to provide an HDMI/DVI interface. The interface uses TMDS signaling.

This interface also supports additional I2C device communication.

Also see Chapter 2.17.1 I2C Interfaces Controlled by i.MX 6 on page 38.

### 2.9.1.2 LVDS

The CC10C supports one dual-channel LVDS interface at the COM Express connector according to the PICMG COM.0 standard.

The interface supports one port with up to 165 Mpixels/s or two single-channel ports up to 85 Mpixels/s (e.g., WUXGA+ at 60Hz) each. The maximum resolution is WUXGA+ with 1920 by 1200 pixels.

The LVDS ports may be used as follows:

- One single-channel output

- One dual channel output: single input, split to two output channels

- Two identical outputs: single input sent to both output channels

- Two independent outputs: two inputs sent, each, to a different output channel

This interface also supports additional I2C device communication.

### 2.9.1.3 MIPI CSI-2 Camera Interface

The CC10C supports one MIPI CSI-2 camera interface at the COM Express connector. The signals are implemented in place of PCI Express Graphics (PEG) signals on the COM Express connector and are multiplexed with FPGA I/O signals.

This interface also supports additional I2C device communication.

Also see Chapter 2.17.1 I2C Interfaces Controlled by i.MX 6 on page 38.

This interface type is configurable and may be implemented differently on every board version. See Table 2, Interface configurability overview (COM Express connectors).

For an overview of signals multiplexed to use either i.MX 6 or FPGA I/O, see Chapter 2.6.3.1 Multiplexed Interfaces for i.MX 6 or FPGA I/O on page 29.

### 2.9.2 Audio

The CC10C supports AC'97 audio and I2S audio. All audio functions are controlled by the i.MX 6 processor.

A codec for either interface type must be provided on the carrier board.

You can find the pinout for the audio signals in Chapter 2.20.3 COM Express Connectors on page 43.

### 2.9.2.1 AC'97

The CC10C provides one AC'97 audio interface at the COM Express connector according to the PICMG COM.0 standard.

### 2.9.2.2 I2S

The CC10C provides one I2S audio interface.

### 2.10 USB

The CC10C provides up to six USB 2.0 host ports at the COM Express connector according to the PICMG COM.0 standard.

USB 0 is implemented as a USB 2.0 OTG (On-The-Go) host/client port. The additional OTG signal is implemented using a reserved pin of the COM.0 standard.

Interfaces USB 0 and USB 1 are controlled by an FSL-EHCI controller in the i.MX 6 processor which also supports USB 1.1.

Four additional USB 2.0 interfaces are driven by controllers inside an onboard PCIe Swidge with an integrated EHCI and OHCI controller.

You can find the pinout for the USB signals in Chapter 2.20.3 COM Express Connectors on page 43.

This interface type is configurable and may be implemented differently on every board version. See Table 2, Interface configurability overview (COM Express connectors).

### 2.11 Ethernet

The CC10C provides one Gigabit Ethernet interface controlled by the i.MX 6 processor at the COM Express connector according to the PICMG COM.0 standard. The interface is controlled by the Ethernet MAC controller inside the CPU. It supports 10 Mbit/s up to 1000 Mbit/s as well as full-duplex operation.

Board models with an onboard FPGA provide an additional, Fast Ethernet interface at the COM Express connector. It supports 10 Mbit/s and 100 Mbit/s in half-duplex and full-duplex operation.

Note: While the two possible Ethernet interfaces are called GBE0 and GBE1, only GBE0 conforms to the PICMG COM.0 standard and supports Gigabit connection

You can find the pinout for the Ethernet signals in Chapter 2.20.3 COM Express Connectors on page 43.

This interface type is configurable and may be implemented differently on every board version. See Table 2, Interface configurability overview (COM Express connectors).

### 2.11.1 Ethernet MAC Addresses

The unique MAC address is set at the factory and should not be changed. Any attempt to change this address may create node or bus contention and thereby render the board inoperable.

The naming of the interfaces may differ depending on the operating system. The MAC addresses on CC10C are:

```

CC10C, port 0: 0x 00 C0 3A CA 00 00 - 0x 00 C0 3A CA 7F FF

CC10C, port 1: 0x 00 C0 3A CA 80 00 - 0x 00 C0 3A CA FF FF

CC10, port 0: 0x 00 C0 3A CB 00 00 - 0x 00 C0 3A CB 7F FF

CC10, port 1: 0x 00 C0 3A CB 80 00 - 0x 00 C0 3A CB FF FF

```

where "00 C0 3A" is the MEN vendor code. The last six digits describe the range from which the addresses for the board are taken. The serial number is added by the last three digits in the range:

Serial number 42 (CC10C, port 1):  $0 \times 8000 + 0 \times 002A = 0 \times 802A$ .

Also see Chapter 5.2 Finding out the Product's Article Number, Revision and Serial Number on page 84.

### 2.11.2 Ethernet Status LEDs

The CC10C supports two control signals per Ethernet interface for the Ethernet status LEDs at the COM Express connector according to the definition of PICMG COM.0 standard: *GBE[0:1]\_LINK#* and *GBE[0:1]\_ACT#*.

Control signals GBE[0:1]\_LINK1000# and GBE[0:1]\_LINK100# are not supported.

Table 4. Ethernet status LED modes

| Signal         | Mode | On      | Off         | Blinking       |

|----------------|------|---------|-------------|----------------|

| GBE[0:1]_LINK# | LINK | Link up | No link     | n/a            |

| GBE[0:1]_ACT#  | ACT  | n/a     | No activity | Tx/Rx activity |

### 2.12 PCI Express

The CC10C provides one PCI Express x1 link controlled by the i.MX 6 processor at the COM Express connector using pin group PCIE 0 according to the PICMG COM.0 standard.

The port supports the PCIe 1.1 standard; i.e. data rates up to 250 MB/s in each direction (2.5 Gbit/s per lane).

You can find the pinout for the PCI Express signals in Chapter 2.20.3 COM Express Connectors on page 43.

### 2.13 ExpressCard Interface

The CC10C provides one ExpressCard interface controlled by the i.MX 6 processor at the COM Express connector according to the PICMG COM.0 standard.

ExpressCard is a small form factor expansion card for mobile systems that uses PCI Express or USB as the interface. The CC10C provides ExpressCard signals *EXCD0\_PERST#* and *EXCD0\_CPPE#*, but no PCI Express or USB link is specifically allocated to ExpressCard use.

You can find the pinout for the PCI Express Card signals in Chapter 2.20.3 COM Express Connectors on page 43.

### 2.14 CAN Bus

The CC10C provides two CAN bus interfaces controlled by the i.MX 6 processor at the COM Express connector, and an additional, optional two interfaces driven by the onboard FPGA.

The physical interfaces (transceivers) are implemented on the carrier board for each channel.

Main features of i.MX 6 controlled interfaces:

- CAN 2.0B protocol

- Data rates up to 1 Mbit/s

- Flexible Controller Area Network (FLEXCAN) controller

Main features of FPGA controlled interfaces:

- CAN 2.0A/B protocol

- Data rates up to 1 Mbit/s

The CAN interfaces are implemented in place of COM.0 LPC signals.

You can find the pinout for the CAN bus signals in Chapter 2.20.3 COM Express Connectors on page 43.

This interface type is configurable and may be implemented differently on every board version. See Table 2, Interface configurability overview (COM Express connectors).

# 2.15 UART Interfaces

The CC10C provides up to six UART interfaces controlled by the i.MX 6 processor and/or the onboard FPGA at the COM Express connector. The physical layers are defined on the carrier board for each channel.

Main features of i.MX 6 controlled interfaces:

- Data rates up to 4 Mbit/s per interface

- 64-byte transmit/receive buffer

- Handshake lines: none or CTS/RTS

Main features of FPGA controlled interfaces:

- Data rates up to 3 Mbit/s per interface

- 60-byte transmit/receive buffer (124-byte buffer on request)

- Handshake lines: CTS/RTS or full support (CTS, RTS, DSR, DTR, DCD, RI)

# **Configuration Varieties**

There are various configuration varieties for the CC10C's UART interfaces, with differing handshake lines.

In general, the UARTs are implemented as follows:

- UART0 and UART1 are always controlled by the i.MX 6 processor and are implemented according to the PICMG COM.0 standard, using the General Purpose Serial Interfaces RS1 and RS2.

- UART2 and UART3 can either be controlled by the i.MX 6 processor or by the onboard FPGA, with different handshake line support.

- UART4 and UART5 are always controlled by the onboard FPGA.

- The signal mnemonics for the UARTs is *SERn*, e.g., UART0 signals are called *SER0\_TX* and *SER0\_RX*.

Table 5. UART interface control and configurability

| UART # | Connector<br>Row | Configurable | Controlled by | Comments                                                                                        |

|--------|------------------|--------------|---------------|-------------------------------------------------------------------------------------------------|

| 0      | Α                |              | i.MX 6        |                                                                                                 |

| 1      | Α                |              | i.MX 6        |                                                                                                 |

|        | С                | х            | i.MX 6        | Additional handshake lines CTS and RTS                                                          |

| 2      | D                | х            | i.MX 6        | i.MX 6: With handshake lines CTS and RTS                                                        |

|        |                  |              | or<br>FPGA    | FPGA: With handshake lines CTS and RTS, on FPGA_IO[77:80]                                       |

| 3      | D                | х            | i.MX 6        | i.MX 6: No handshake lines                                                                      |

|        |                  |              | or<br>FPGA    | FPGA: With handshake lines CTS, RTS, DSR, DTR, DCD and RI, on FPGA_IO[81:86] and FPGA_IO[91:92] |

| 4      | D                | х            | FPGA          | With handshake lines CTS and RTS, on FPGA_IO[87:88] and FPGA_IO[89:90]                          |

| 5      | D                | х            | FPGA          | With handshake lines CTS and RTS, on FPGA_IO[93:94] and FPGA_IO[96:97]                          |

You can find the pinout for the UART signals in Chapter 2.20.3 COM Express Connectors on page 43.

This interface type is configurable and may be implemented differently on every board version. See Table 2, Interface configurability overview (COM Express connectors).

Related FPGA I/O lines are not fixed to UART functionality but can also be custom-configured with different functions.

For an overview of signals multiplexed to use either i.MX 6 or FPGA I/O, see Chapter 2.6.3.1 Multiplexed Interfaces for i.MX 6 or FPGA I/O on page 29.

#### 2.16 PWM

The CC10C provides three PWM (pulse-width modulation) signals controlled by the i.MX 6 processor at the COM Express connector.

PWM1 and PWM2 are implemented in place of COM.0 PEG signals.

PWM0 is implemented in place of COM.0 signal *FAN\_PWMOUT*, so this signal can be used as specified by the standard to control a fan's RPM.

Note: A fourth PWM signal is fixed to a specific function: it is used as backlight signal for LVDS (LVDS\_BKLT\_CTRL).

You can find the pinout for the PWM signals in Chapter 2.20.3 COM Express Connectors on page 43.

# 2.17 I2C

The CC10C provides two general-purpose I2C interfaces controlled by the i.MX 6 processor at the COM Express connector and can offer additional interfaces as implemented in the onboard FPGA.

You can find the pinout for the I2C signals in Chapter 2.20.3 COM Express Connectors on page 43.

# 2.17.1 I2C Interfaces Controlled by i.MX 6

The two interfaces driven by the i.MX 6 processor are used in different ways:

• I2C1: Used for onboard functions and for communication with the carrier board concerning board data. The signals are implemented according to the PICMG COM.0 standard.

Also see I2C.

• I2C2: Available for free use, but can also be connected specifically to MIPI CSI-2 and HDMI/DVI devices with dedicated signals in addition to the normal I2C signals. The normal I2C and HDMI/DVI signals are implemented according to the PICMG COM.0 standard (SMBus and DDI1\_CTRL signals). The additional MIPI CSI-2 signals are implemented in place of PCI Express Graphics (PEG) signals.

Also see I2C, HDMI1\_CTRLCLK and MIPI\_I2C\_SCL.

Also see Chapter 4.3 SMBus Devices on page 81.

# 2.17.2 I2C Interfaces Controlled by Onboard FPGA

Additional interfaces can be implemented using the onboard FPGA. By default, these signals are implemented in place of PCI Express signals on the COM Express connector.

Also see I2C.

This interface type is configurable and may be implemented differently on every board version. See Table 2, Interface configurability overview (COM Express connectors).

#### 2.18 SPI

The CC10C provides three SPI interfaces controlled by the i.MX 6 processor at the COM Express connector.

SPI1 is implemented according to the PICMG COM.0 standard.

SPI2 and SPI3 are implemented in place of COM.0 PEG signals and are multiplexed with FPGA I/O signals.

You can find the pinout for the SPI signals in Chapter 2.20.3 COM Express Connectors on page 43.

This interface type is configurable and may be implemented differently on every board version. See Table 2, Interface configurability overview (COM Express connectors).

For an overview of signals multiplexed to use either i.MX 6 or FPGA I/O, see Chapter 2.6.3.1 Multiplexed Interfaces for i.MX 6 or FPGA I/O on page 29.

# 2.19 GPIO

The CC10C provides nine GPIO, four GPO and three GPI lines controlled by the i.MX 6 processor at the COM Express connector and can offer additional GPIOs as implemented in the onboard FPGA.

You can find the pinout for GPIO signals in Chapter 2.20.3 COM Express Connectors on page 43.

GPIOs are accessible through driver software provided by the board support package (if i.MX 6 controlled) or other driver software (if FPGA controlled).

You can find any BSP and driver software available for download on the CC10C pages on MEN's website.

# 2.19.1 GPIO Lines Controlled by i.MX 6

A number of GPIOs controlled by the i.MX 6 processor are implemented in place of COM.0 control signals and may partly be used as control signals through special software support.

All GPIO lines are interrupt-capable.

- For a reference to COM.0-defined standard control signals see section GPIO of the mnemonics table.

- Also see Chapter 2.20.4 COM Express Control Signals on page 55.

Note that pins *GPO[0:3]* refer to i.MX 6 GPO lines. They are not to be confused with the COM.0 defined GPO pins of the same name, which are used for different functions on CC10C.

# 2.19.2 GPIO Lines Controlled by Onboard FPGA

Additional GPIO lines can be implemented using the onboard FPGA.

This interface type is configurable and may be implemented differently on every board version. See Table 2, Interface configurability overview (COM Express connectors).

Related FPGA I/O lines are not fixed to GPIO functionality but can also be custom-configured with different functions.

# 2.20 Rugged COM Express (VITA 59)

Rugged COM Express is a Computer-On-Module (COM/SOM) standard that is based on PICMG standard COM.0 or COM Express but is especially ruggedized and provides a high-performance, low-power architecture for harsh environments.

RCE modules are electrically compatible to standard COM Express (PICMG COM.0) boards. For this reason, MEN is able to provide every Rugged COM Express board also as a standard COM Express board without much development effort.

The RCE concept has been developed for applications that require highly robust electronics to ensure safe and reliable operation even in severe environments, e.g., in railways and avionics, industrial automation and medical engineering or mobile applications in general.

To make standard COM Express modules suitable for this kind of applications they were embedded in a frame and a cover which ensures 100% EMC protection. Only soldered components are used to withstand shock and vibration, and the design is optimized for conformal coating.

#### 2.20.1 Module Form Factors

Generally three form factors are defined for Rugged COM Express:

| Module Type | Length | Width  | Height | MEN Product Name<br>Convention |

|-------------|--------|--------|--------|--------------------------------|

| Mini        | 94 mm  | 65 mm  | 18 mm  | CMxxC                          |

| Compact     | 105 mm | 105 mm | 18 mm  | CCxxC                          |

105 mm

Table 6. Form factors defined for Rugged COM Express

135 mm

Related COM Express (COM.0) modules from MEN are named the same as Rugged COM Express modules but without the 'C' at the end, e.g., CB70 or CC10.

18 mm

**CBxxC**

The CC10C module has Rugged COM Express Compact format, the CC10 has COM Express Compact format.

# 2.20.2 Thermal Concept

**Basic**