# PAM-5002R Programmable Analog Module

# Technical User Manual

Version 2.4

© Copyright 2007 to Servenger LLC

# **Table of Contents**

| Overview of the PAM Board                                            | 5  |

|----------------------------------------------------------------------|----|

| Definitions                                                          | 5  |

| Block Diagram of PAM-5002R                                           | 7  |

| Power                                                                | 8  |

| LEDs                                                                 | 9  |

| Signal Connections                                                   | 10 |

| Analog Connector                                                     | 10 |

| Inputs                                                               | 10 |

| Stereo Input Connector                                               | 10 |

| PAM Inputs routed to Anadigm ASP Inputs                              | 11 |

| Outputs                                                              | 12 |

| Stereo Output Connector                                              | 12 |

| Anadigm ASP Outputs routed to PAM Outputs                            | 12 |

| Digital Connector                                                    | 13 |

| Configuration Adjustments                                            | 14 |

| Switches                                                             | 14 |

| Input Termination                                                    | 14 |

| Differential or Single Ended Mode                                    | 15 |

| Termination Impedance                                                | 16 |

| Balance Adjustment                                                   | 16 |

| Anadigm ASP Mode Selection                                           | 17 |

| Microcontroller Control Options                                      | 18 |

| Modifying the Input and Output Filters                               | 19 |

| Buffered Inputs                                                      | 20 |

| Unbuffered Inputs                                                    | 21 |

| Outputs                                                              | 22 |

| Configuring the PAM with AnadigmDesigner®2                           | 23 |

| Obtaining the AnadigmDesigner®2 software                             | 23 |

| Connecting the Programmable Analog Module (PAM) to AnadigmDesigner®2 | 24 |

| Creating and downloading a sample Anadigm ASP audio signal source    | 25 |

| Storing a Serial EEPROM Copy of a Downloaded Configuration file      | 26 |

| Configuring the PAM with a Serial EEPROM                             | 27 |

| Am 0002R 050 Manda                                                |    |

|-------------------------------------------------------------------|----|

| Accessories                                                       | 28 |

| Specifications                                                    |    |

| Mechanical Specifications                                         |    |

| Electrical Specifications                                         | 32 |

| Signal Pinouts                                                    |    |

| PAM-5002 Series Digital and Analog Board Level Connector Pin Outs |    |

| Digital Connector Pin Assignment and Function Details             | 34 |

| Analog Connector Pin Assignment and Function Details              | 35 |

| Appendix                                                          | 37 |

| Index                                                             | 39 |

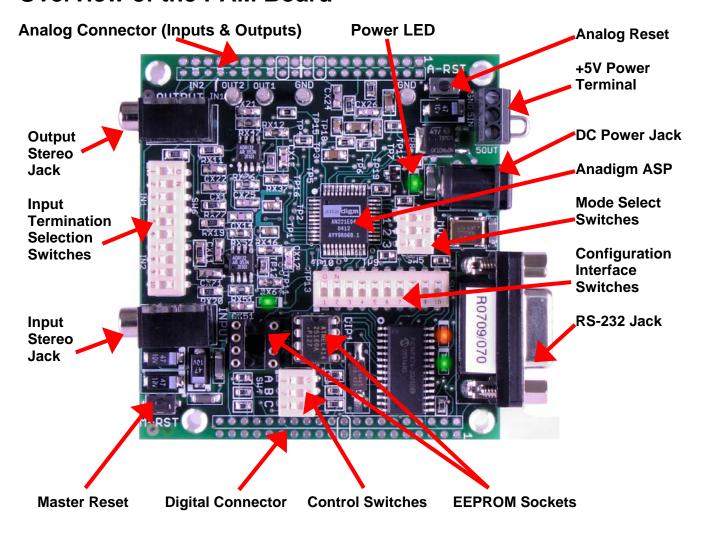

#### Overview of the PAM Board

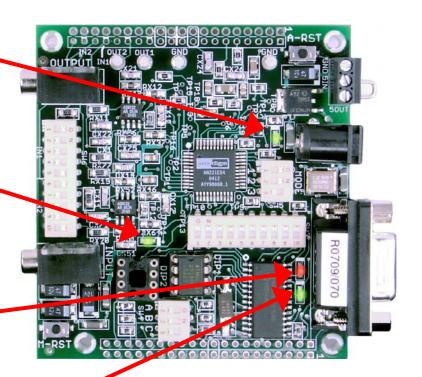

#### **Definitions (clockwise from upper left)**

**Analog Connector** Where the analog inputs and outputs connect to the host.

Also allows powering the PAM board from the host system,

and the Analog Reset function.

For specific information refer to the connector pin list.

**Power LED** Indicates with green light that the +5 Volt power is active.

**Analog Reset** Push button that causes the Anadigm Analog Signal Processor (ASP) IC to

initiate a Power Up Reset Cycle (does not affect the microcontroller).

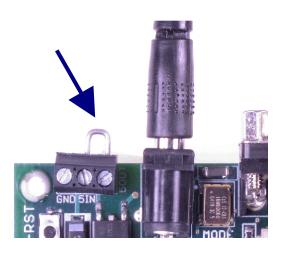

+5 V Power Terminal Strap 5VOUT to 5VIN as shown to operate from the on-board +5 Volt regulator,

or connect the GND and 5VIN terminals to a separate power source.

**DC Power Jack** Input for power from a 120 VAC to 9 VDC adapter.

**Anadigm ASP** Anadigm programmable Analog Signal Processor (ASP).

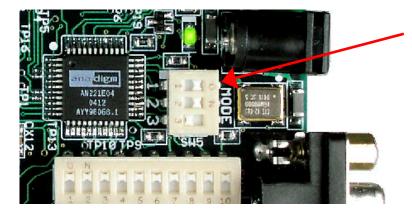

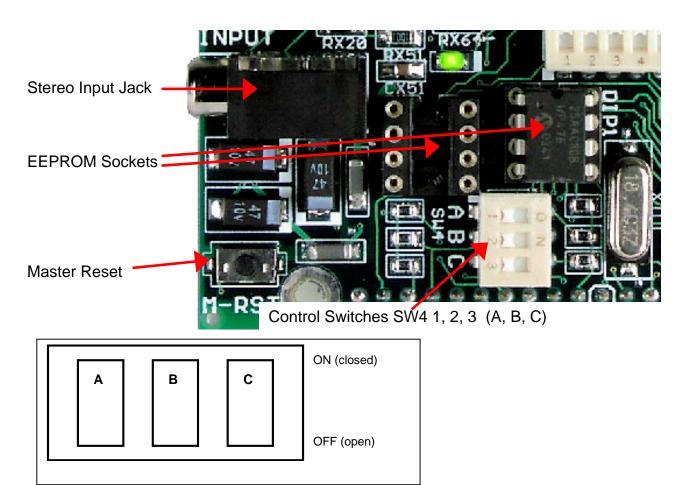

#### **Mode Select Switches**

Use these switches to select between "Run from EEPROM Mode" or "Dynamic Configuration Mode." "Dynamic Configuration Mode" is the typical usage for operating the PAM unit from the host PC through the RS-232 serial port at the DB-9 connector. (Also called Switch 5 or SW5.)

#### **Configuration Interface Switches**

For isolating the Anadigm ASP during factory testing and to shut down the microcontroller when not needed for the "Run from EEPROM Mode" (Also called Switch 3 or SW3).

**RS-232 Jack (DB-9)** For configuring the Anadigm ASP from the AnadigmDesigner<sup>®</sup>2 Software running on the connected host PC.

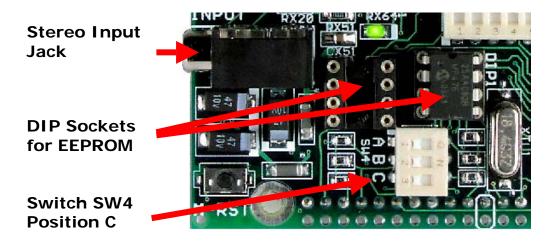

**EEPROM Sockets** Used for the "Run from EEPROM Mode" of the Anadigm ASP

Dip Socket #1 near to the RS-232 Jack is connected to the microcontroller. Dip Socket #2 far from the RS-232 Jack is connected to the Anadigm ASP IC.

**Control Switches** Controls copying configuration into the on-board EEPROM and setting RS-232

hardware flow control or software flow control.

**Digital Connector** Allows for configuring the PAM and the Anadigm ASP IC from the host,

as well as status and control lines. The RS-232 Jack pins are duplicated here.

For specific information refer to the connector pin list.

Master Reset Causes reset of the microcontroller. When the Configuration Interface Switches

are closed, also resets the Anadigm ASP IC.

**Input Stereo Jack** A signal path for analog signals into the Anadigm ASP IC.

For specific information refer to the pinout list.

#### **Termination Selection Switches**

For selecting the many different input signal termination options provided.

**Output Stereo Jack** A signal path for analog signals out of the Anadigm ASP IC.

For specific information refer to the pinout list.

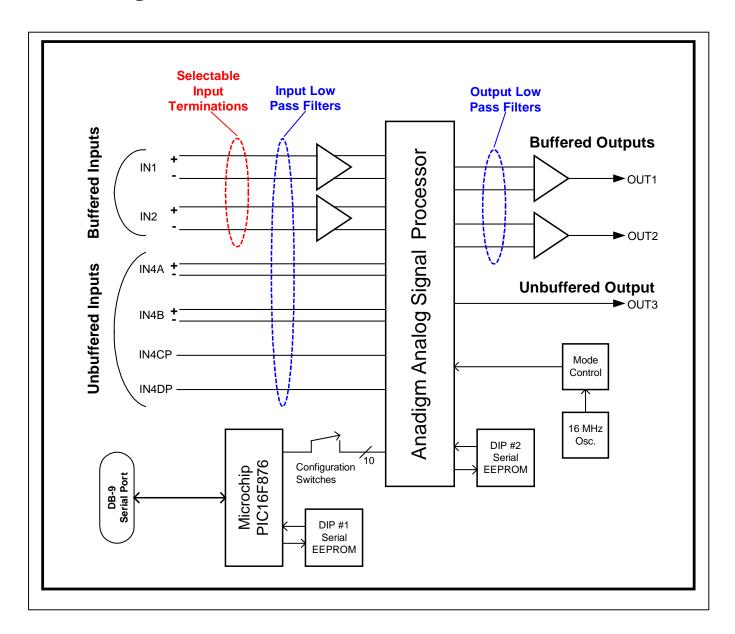

## **Block Diagram of PAM-5002R**

The schematic design with the circuit and component details is included in the information CD shipped with the PAM unit.

#### **Power**

The PAM-5002 Series modules operate with +5 Volts DC power. Like a Field Programmable Gate Array (FPGA) device, the Anadigm Field Programmable Analog Array (FPAA) has a much higher initial turn-on current than run time current. The power supply will need to provide at least 1200 mA for the first approximately 100 ms to accommodate the Anadigm ASP IC initial turn-on current (see Note below). At maximum load, a fully configured PAM will consume less than 250mA, typically 120 to 190mA.

#### Note:

Not having an adequate power supply may leave the part stuck after turn-on at a few volts of applied voltage sinking a significant amount of power supply current indefinitely (the identical risk situation exists with the digital FPGA devices).

If using a low noise bench power supply or a Host System, the input voltage range is 4.75V to 5.25 V (5V +/-5%).

An on-board generator creates –5 Volt DC voltage to be used by the input and output buffer amplifiers. The negative 5 Volts is not available for export off of the PAM module.

Power is routed into a PAM from one of three options:

- The DC Power Jack to supply the on-board +5 Volt linear regulator as shown in the picture below at left. It requires an external AC power adapter with rated output of 9 VDC. A regulated 120VAC to 9VDC power unit is supplied with the PAM-5002 unit. To use this option, install a small wire strap between 5VOUT and 5VIN to route the regulated +5V to the active circuitry on the PAM as indicated by the arrow in the picture. If a replacement AC adapter is needed see the Appendix.

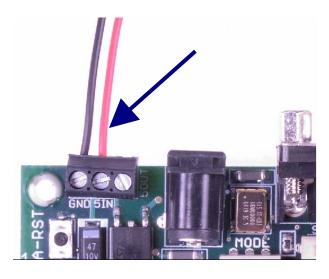

- The +5V Power Terminal connected to a low noise +5V bench power supply rated for 1200mA or greater. Connect the PAM to the bench supply as is shown in the picture on the right. First remove the external wire strap between the 5VOUT and 5VIN pins of the Power Terminal. The red (right) wire in the picture is the +5Volt and the black (left) wire is ground.

- The Host System through the Analog Connector using the board mount connectors supplied. To use this option remove the external wire strap between the 5VOUT and 5VIN pins of the Power Terminal. See the Accessories section for information on ordering these connectors.

When power is applied and +5 Volts DC is present on the PAM the Power LED will be illuminated with a continuous green.

#### LEDs on the PAM-5002R

#### There are four LED indicators on the PAM:

Power LED – A green LED that indicates +5V Power is present

Anadigm ASP ON – a green LED indicates that the Anadigm ASP IC is successfully configured and operating.

Microcontroller Status LEDs:

A Red LED here indicates that the microcontroller has received an improper command or that a configuration download attempt has failed to complete properly.

A Green LED here indicates that the microcontroller has received and executed a correct command.

## **Signal Connections**

#### THE ANALOG CONNECTOR

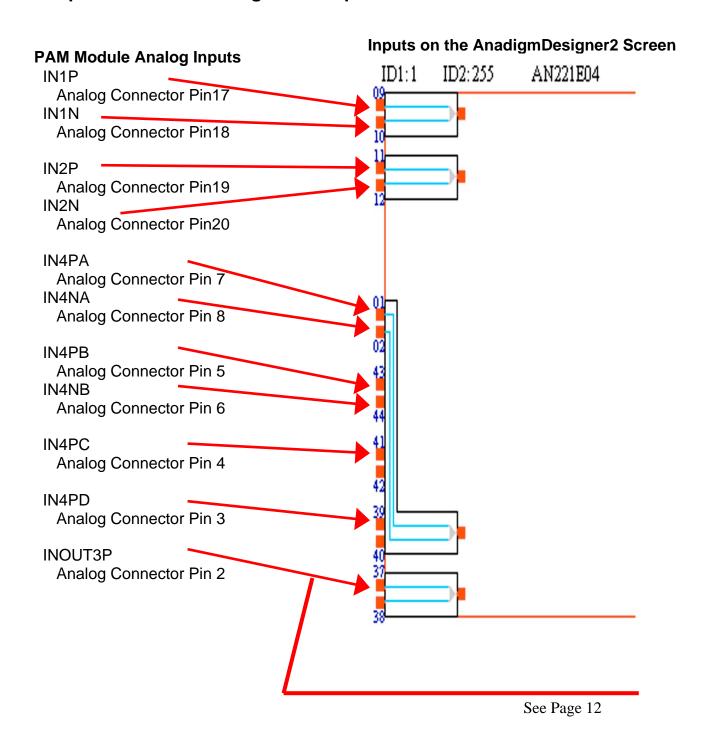

The signals on this connector are the analog inputs and outputs of the Anadigm ASP IC, the +5 VDC Power, Ground, and the Analog reset control. The diagram on the following page shows the pin assignments associated with the input and output signals that appear in the AnadigmDesigner<sup>®</sup>2 design window.

The circuit and component details for signals into and out of the PAM, the on-board buffers, microprocessor and power supplies is given on the schematic pages included in the information CD shipped with the PAM unit.

#### **Inputs**

There are four different configurations of inputs: (refer also to the Block Diagram)

- DC coupled buffered Inputs (Differential or Single Ended) are the pairs IN1P & IN1N and IN2P & IN2N. These inputs have Selectable Terminations: 50 ohm, 600 ohm or maximum impedance (approximately 2 kohm). They are the most accessible inputs because the on-board buffers level shift ground referenced signals from outside the PAM to the +2V mid-range reference of the Anadigm ASP IC.

- AC coupled unbuffered Differential Input pairs IN4PA & IN4NA and IN4PB & IN4NB These pairs have 10 k Ohm + 1 uF termination as the input impedance. They can also be used for single ended signals by attaching a grounding resistor to the negative input signals: IN4NA or IN4NB. The AC coupling relieves the user from dealing with the +2 V mid-range reference requirement of the Anadigm ASP.

- AC coupled unbuffered Single Ended inputs IN4PC and IN4PD have 10k Ohm + 1 uF termination impedance. The AC coupling relieves the user from dealing with the +2 V mid-range reference level requirement of the Anadigm ASP.

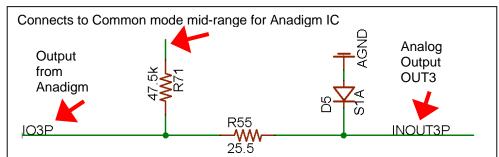

- DC coupled input/output at IO3P direct to the Anadigm IC through 25 ohms plus a 47.5 resistor to

the +2V mid-range reference of the Anadigm ASP IC. The user must bias signals applied to this

input pin at +2 VDC mid-range with +/- 1.75 V<sub>PEAK</sub> max signals around the +2 VDC mid-range

level. This signal path, IO3P, is treated as OUT3 for the remainder of this manual but is available to

be used as an input.

Thus there are a maximum of four possible inputs:

- 1. IN1P & IN1N differentially (or IN1P single ended)

- 2. IN2P & IN2N differentially (or IN2P single ended)

- 3. INOUT3P single ended input/output with external level control

- 4. One of the multiplexed inputs IN4PA & IN4NA, IN4PB & IN4NB, IN4PC, or IN4PD.

#### STEREO INPUT CONNECTOR

The Stereo Input Connector allows for input via a 3.5-millimeter stereo plug for Single Ended signals into the IN1P and IN2P buffered inputs. The Termination Selection Switches must be set for Single Ended to correctly access the signals. Refer to the section on the Termination Selection Switches.

#### **PAM Inputs routed to Anadigm ASP Inputs**

Note the 4 to 1 analog multiplexer for IN4A / IN4B / IN4C / IN4D.

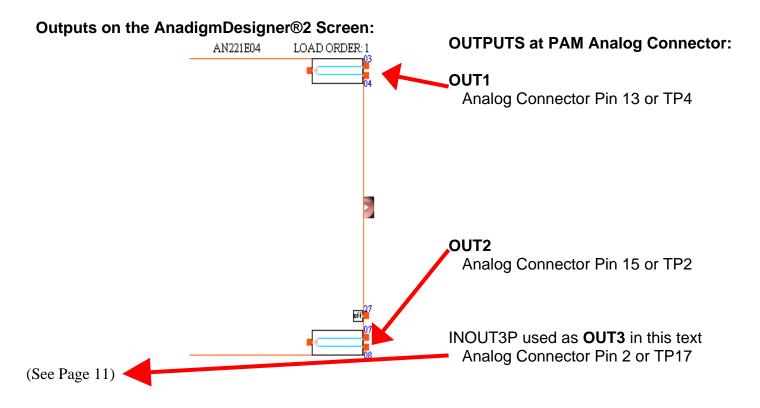

#### **Outputs**

Outputs OUT1 and OUT 2 come from the Anadigm ASP IC as differential signals referred to +2.0V. They are converted to single-ended signals by a differential to single-ended buffer. At the Analog Connector, Out 1 is Pin 13 and Out2 is Pin 15. The buffers also level shift the output signals from the Anadigm ASP to be Ground referenced as they leave the PAM unit (+/- around Ground instead of around +2.5 V).

Output OUT3 is a single ended signal directly connected from the output of the Anadigm ASP IC through a 25  $\Omega$  resistor. As such, there is no filtering and the signal is referenced to the +2.0V mid-range of the Anadigm IC. See also the table Analog Connector Pin Assignment and Functional Details and Note 6.

Five test points are provided on the PAM circuit board to access the analog output ports directly from the Anadigm ASP IC. Each test point is a plated through hole large enough to connect a 26 AWG wire. TP1 is O2N output. TP2 is O2P output. TP3 is O1N output. TP4 is O1P output. TP17 is the IO3P input/output.

#### STEREO OUTPUT CONNECTOR

The Stereo Output Connector allows the single ended outputs to be available via a 3.5-millimeter stereo plug and cable. (An example is to drive a set of computer stereo speakers.) Signal OUT1 is the left channel and signal OUT2 is the right channel. The on-board circuit includes a 25 ohm series resistor for a current limiter during a fault condition.

#### **Anadigm ASP Outputs Routed to PAM Outputs**

#### **The Digital Connector**

This connector enables communication from the PAM module to the host system. The pin assignments, in order are: (For full explanation see the Electrical Specifications)

| RS-232 Inputs and Outputs                                                                                                                               | Pins 1-6       |            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------|

| Anadigm ASP Control Signals:                                                                                                                            |                |            |

| ERRb                                                                                                                                                    | Pin 7          | Output     |

| ACTIVATE                                                                                                                                                | Pin 8          | Output     |

| EXECb                                                                                                                                                   | Pin 9          | Input      |

| Digital Ground                                                                                                                                          | Pin 10         | Power      |

| Digital VCC                                                                                                                                             | Pin 11         | Power      |

| M-RESETb = Low Asserted Master Reset                                                                                                                    | Pin 12         | Input      |

| Other inputs and outputs reserved for future                                                                                                            | use Pins 13-19 | Leave open |

| ONb                                                                                                                                                     | Pin 20         | Output     |

| Indicates that the Anadigm ASP IC has been successfully configured.  (A low output will be simultaneous with the green Anadigm ASP ON LED illuminated.) |                |            |

#### Important Note:

Pins 13-19 are reserved for factory use and future features. Leave these pins unconnected in the application especially pin 18 which controls the microcontroller firmware programming feature. A low signal applied to Pin 18 during a Power On Reset cycle will invoke an uncontrolled firmware programming sequence rendering the PAM unit inoperable.

One application of the PAM-5002R is for use as a system module under the control of an external host controller that communicates over an SPI data pathway though pins 13-17. The PAM-5002R is intended to function as an SPI slave unit for this application. Please contact the Servenger company for assistance with the application specific firmware to implement this feature in your system.

# **Configuration Adjustments**

#### **SWITCHES**

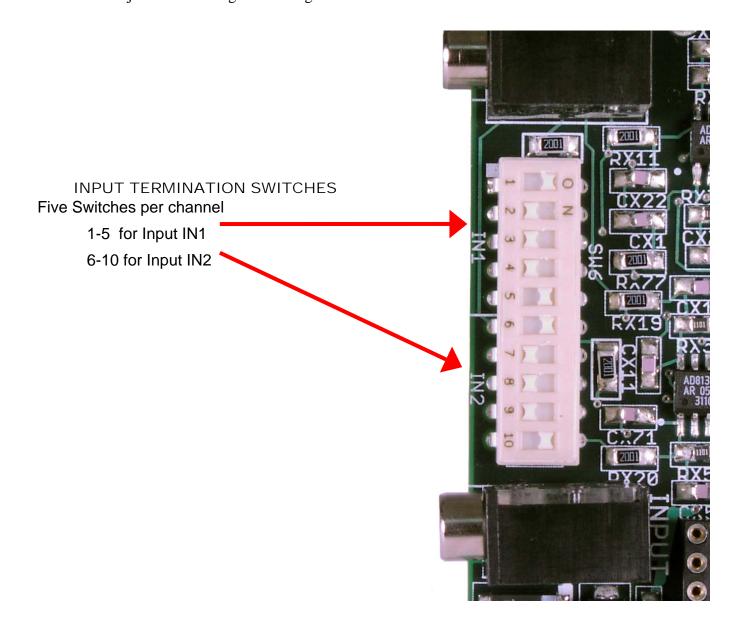

#### **Input Termination**

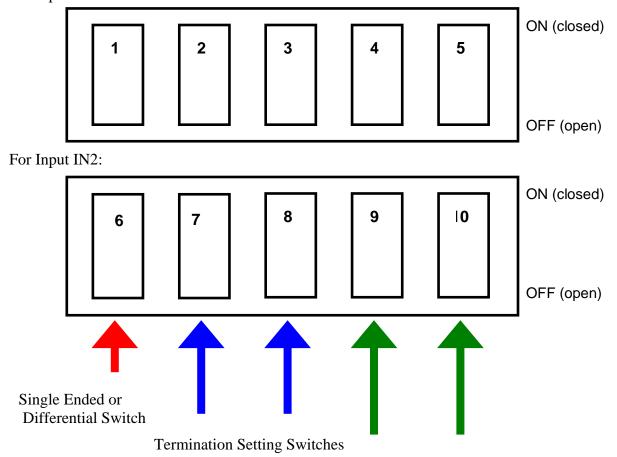

There are ten switches used to adjust termination of the buffered inputs IN1P & IN1N and/or IN2P & IN2N. The ten switches control three functions of the signal path of each input. The three functions are:

- Input termination impedance selection.

- Differential or single ended signal selection.

- Balance adjustment for single ended signals.

For Input IN1:

**Balance Adjustment Switches**

#### Differential vs. Single Ended Operating Modes (RED arrow)

Chosen by positions 1 and 6 of Switch SW6.

- Differential mode for IN1 when position 1 is set open (OFF)

- Single Ended for IN1 when position 1 is set closed (ON)

- o Works by shorting the input IN1N (analog connector position 18) to ground

- Differential mode for IN2 when position 6 is set open (OFF)

- Single Ended for IN2 when position 6 is set closed (ON)

- o Works by shorting the input IN2N (analog connector position 20) to ground

#### Termination Impedance (BLUE arrow)

Input Termination Impedance, for both Differential and Single Ended signals, is controlled by positions 2 & 3 for IN1 and by positions 7 & 8 for IN2. The three possible input impedances are: Maximum, 600 Ohms, and 50 Ohms. Each position set terminates one input path. Positions 2 & 3 terminate the signals for IN1 (IN1P & IN1N) and position 7 & 8 terminate the signals for IN2 (IN2P & IN2N).

- Maximum Impedance (approximately 2000 ohms per side) Both switches open (OFF)

- 50 Ohms close (ON) switch at position 2 for IN1 or position 7 for IN2.

- o Switch positions 3 and 8 open (OFF)

- 600 Ohms Close (ON) switch at position 3 for IN1 or position 8 for IN2.

- o Switch positions 2 and 7 open (OFF)

#### **Balance Adjustment (GREEN arrow)**

The input buffers on the PAM-5002 are designed to amplify differential signals. Accurate amplification of single ended signals requires a resistance in series with the grounded input to "balance" the source impedance of a single ended input signal.

To correctly set the "balance" for either input the switch positions 4 & 5 and 9 & 10 must be set with:

- For all Differential signals and for Single Ended Maximum Impedance:

- o Switch 4 open (OFF) and position 5 closed (ON) for IN1 or

- o Switch 9 open (OFF) and position 10 closed (ON) for IN2

- For a Single Ended 50 Ohm input impedance:

- o Switch 4 closed (ON) and position 5 open (OFF) for IN1 or

- o Switch 9 closed (ON) and position 10 open (OFF) for IN2

- For a Single Ended 600 Ohm both switches 4 & 5 or 9 & 10 are open (OFF).

#### **Examples:**

| 50 Ohm Differential         | 01001 | (OFF- ON-OFF-OFF- ON) |

|-----------------------------|-------|-----------------------|

| 50 Ohm Single Ended         | 11010 | (ON- ON-OFF- ON- OFF) |

| 600 Ohm Differential        | 00101 | (OFF-OFF- ON-OFF- ON) |

| 600 Ohm Single Ended        | 10100 | (ON -OFF- ON-OFF-OFF) |

| High Impedance Differential | 00001 | (OFF-OFF-OFF-ON)      |

| High Impedance Single Ended | 10001 | (ON- OFF-OFF-OF)      |

|                             |       |                       |

| Combination Not Used        | x11xx |                       |

| Combination Not Used        | xxx11 |                       |

The normal "as shipped" switch setting is for High Impedance Single Ended for the two buffered Input channels that are accessed through the Input Stereo Jack.

#### **Anadigm ASP Mode Selection (Switch SW5)**

For host PC software configuration operation (control through the on-board microcontroller via the RS-232 port, Anadigm ASP MODE 0), set Switch SW5 positions 1 & 2 ON (Closed) and position 3 OFF (OPEN).

For operation using a configuration file stored in an EEPROM in DIP Socket #2 (Anadigm ASP MODE 1) set Switch SW5 positions 1 & 2 OFF (Open) and position 3 ON (Closed)

# Anadigm ASP MODE Selection Switch (SW5)

Run from microcontroller: (MODE 0):

Position 1 2 3

(Closed Closed Open)

(ON ON OFF)

As shown in picture

Run from EEPROM: (MODE 1):

Position 1 2 3

(Open Open Closed)

(OFF OFF ON)

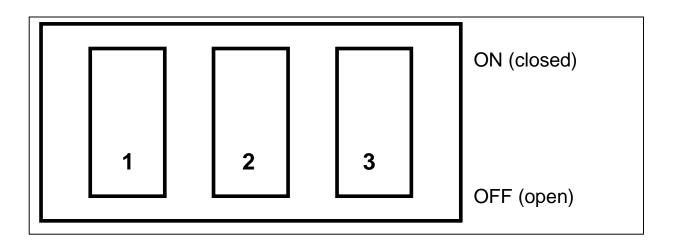

#### **Microcontroller Control Options**

Switch SW4 is used to control options in the microcontroller.

Closing SW4-Position C tells the microcontroller to make a copy of the Anadigm ASP configuration download file in the right most EEPROM socket (labeled 'DIP1'). With position-C open no copy is made. Note that the microcontroller will properly reformat the configuration file that goes into the EEPROM so that the EEPROM will function correctly in Anadigm ASP MODE 1.

Switch SW4-Position B is the communication flow control switch. PAM-5002R units are shipped with position B open (OFF) to provide RS-232 software flow control using the XON-XOFF command protocol. Putting this switch into the closed (ON) state changes to RS-232 hardware flow control using CTS and RTS signal line handshake protocol if needed for the application.

Position A is reserved for factory use. Leave in the OFF position.

#### **Modifying the Input and Output Filters**

The Anadigm ASP IC is a sampled system and thus is susceptible to aliasing, the phenomena where signals above the sampling frequency appear as part of the intended signal. Low pass filters are needed in the input signal path to prevent aliasing. Filters are needed in the output path to smooth the output and remove the out-of-band high frequency sampling energy.

Low pass filters are provided as part of the PAM-5002R unit as follows:

- Buffered Inputs (IN1 & IN2) Each input has two real poles nominally set to:

- 426 kHz

- 426 kHz

- Unbuffered, AC Coupled Inputs (IN4A, IN4B, IN4C, & IN4D) Each input has one real pole nominally set to:

- 212 kHz

• Output Buffer Amplifiers

Each output has one real pole nominally set to:

- 432 kHz

NOTE: Changing the resistance values in these locations does change the corner frequency but also changes the DC gain of the system. Changing the resistance values is not recommended.

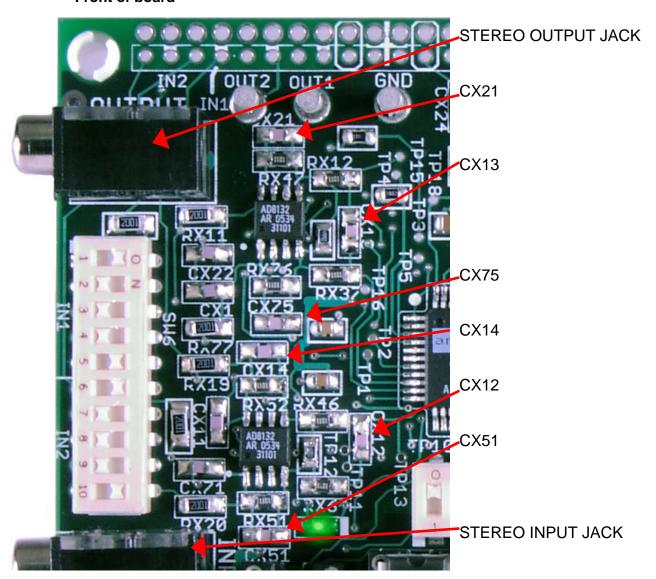

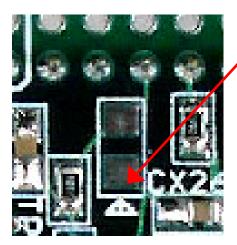

#### **Buffered Inputs**

The buffered inputs (IN1 and IN2) have two possible low pass poles to adjust: on the amplifier, and on the output of the amplifier on the way into the Anadigm ASP IC.

The amplifier break frequency is adjusted by changing capacitors CX21 and CX75 on IN1 or CX 51 and CX 14 on IN2. The selection equation for the capacitor value (CVAL) is:

CVAL =  $1/(2200 * [break frequency in Hz] * \pi)$

The output filter break frequency is adjusted by changing capacitor CX13 on IN1 or capacitor CX 12 on IN2. The selection equation for the capacitor value (CVAL) is:

CVAL =  $1/(2200 * [break frequency in Hz] * \pi)$

#### Front of board

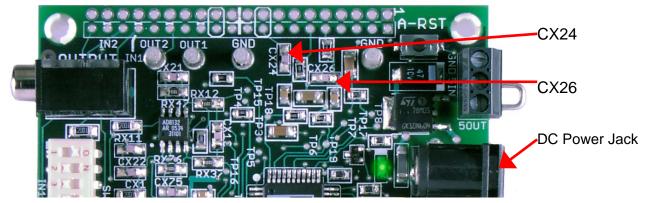

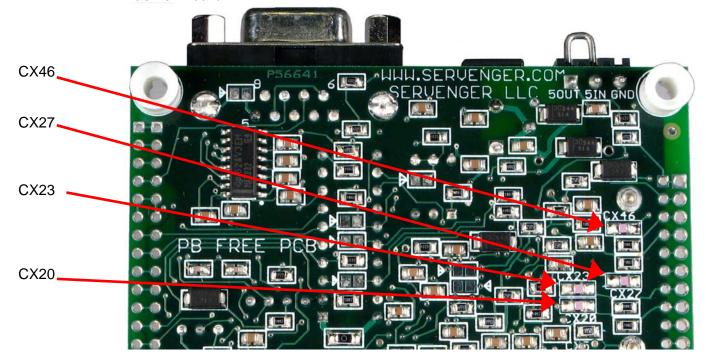

#### **Unbuffered Inputs**

The unbuffered inputs (IN4PA & IN4NA, IN4PB & IN4NB, IN4PC and IN4PD) have one possible low pass pole to adjust.

The input filter break frequency is adjusted by changing capacitors as follows:

IN4PC change CX27,

IN4PD change CX46,

IN4PA & IN4NA change CX20 and CX23,

IN4PB & IN4NB change CX24 and CX26,

The selection equation for the capacitor value (CVAL) is:

$CVAL = 1/(10000 * [break frequency in Hz] * \pi)$

#### Front of Board

**Back of Board**

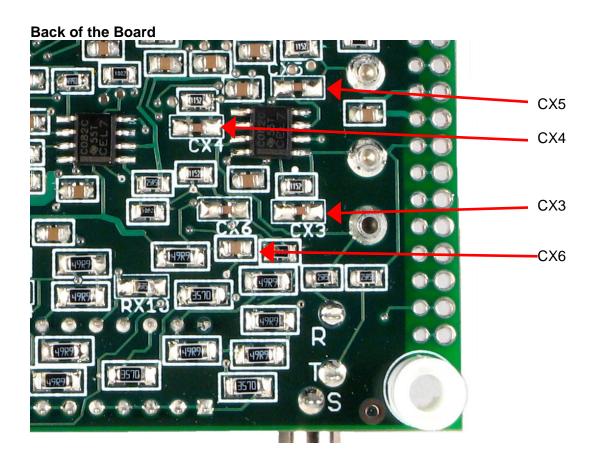

#### **Outputs**

The buffered outputs OUT1 and OUT2 have one low pass pole to adjust on the op-amp IC3. Note: Each of these *pairs must* be changed *together* and have the same value.

For output OUT1 the frequency is adjusted with CX3 and CX5. For output OUT2 the frequency is adjusted with CX4 and CX6

The selection equation for the capacitor value (CVAL) is:  $CVAL = 1/(20000 * [break frequency in Hz] * \pi)$

# Configuring the PAM with AnadigmDesigner2

(See also the Quick Start Guide.)

#### Obtaining the ANADIGMDESIGNER2 software and installing on a PC:

Note: AnadigmDesigner<sup>®</sup>2 is available only on Windows operating systems at this time.

To get a Trial copy of the software:

- Step1. Go to "www.anadigm.com" and click on the

FREE SOFTWARE DOWNLOAD

button on the home page.

Compatible Windows Operating Systems are

Windows 98, ME, NT, 2000 and XP.

AnadigmDesigner'2

- Step 2. A typical web account registration process will start. Enter a UserID and Password to use the website and to download the AnadigmDesigner<sup>®</sup>2. Save the account information, complete the registration, download and save the software. Anadigm will email a License ID and License Key. You may also use this information to access the additional Anadigm ASP website resources such as the useful Support Forum.

- Step 3. Double click on the saved Setup file to start the installation process. A typical Install Wizard will appear. Use the web account information and "**Trial**" as the License Key or the full License ID and License Key if available. The Install Wizard will conclude with a check box to "**Launch AnadigmDesiger2**". Click **Finish**.

This completes the download process. Software updates are issued several times a year. Check the Anadigm ASP website occasionally to get the latest version.

From the Anadigm website you can also download the AnadigmDesigner2 User Manual (84 pages, Adobe Acrobat format) or the Anadigmvortex Solutions Brochure (6 Pages, Adobe Acrobat format).

#### Connecting the Programmable Analog Module (PAM) to AnadigmDesigner®2

# Requirements: AnadigmDesigner2 (sometimes referred to as "AD2") design software installed on a Windows based PC. Looks like this when running RS-232 Serial Cable See notes below about RS-232 Serial Cable. DC power source: Refer to the Power section on page 8.

- Typical set of desktop PC stereo speakers with the 3.5 mm stereo plug connector.

- Step 1. Connect the DC power source, as discussed in the Power section on page 8.

The green **+5V ON** LED next to the DC Power Jack should be illuminated continuously. The two LEDs between the microprocessor and the DB-9 connector should flash RED and then GREEN in succession.

Step 2. Connect Serial Cable from PC to DB-9 RS-232 port on the PAM.

Note: If the RS-232 Serial cable is disconnected and then reconnected to the PAM after a configuration download, it may be necessary to save the design file and then restart the AD2 software to restore the logical connection between the AD2 and the Anadigm ASP IC on the PAM.

Step 3. Connect the 3.5 mm stereo cable into the stereo output jack (farthest corner from the DB-9 RS-232 connector). Make sure the PC speakers have power and are turned on.

Advisory on USB-to-Serial adapters, flow control and RS-232 Serial cables:

- 1. Use of the Servenger PAM-5002R is not recommended with a USB-to-Serial adapter. This arises from the high incidence of non-interoperability for reasons that Anadigm, Servenger and the user cannot control including the latest Microsoft Windows security patches. As shipped, the PAM-5002R is set to use RS-232 **SOFTWARE** flow control (XON-XOFF command character protocol) to be compatible with most desktop PCs. You can experiment with **HARDWARE** flow control (CTS-RTS signal line handshake) to see if this works better for your equipment by setting Switch 4 2 (labeled "B") to ON.

- 2. The "standard" serial cable from a PC to the RS-232 DB-9 connector on a PAM is equipped with 4-40 male hold-down screws that turn with built-in knobs. All USB-to-Serial adapters tested are made with fixed 4-40 female receptacles that collide with the fixed 4-40 female receptacles supplied on the PAM. A partial resolution is to remove the 4-40 jack screws from the DB-9 connector on the PAM. This is NOT recommended for permanent installations.

#### Creating and downloading a sample Anadigm ASP audio signal source:

- Step 1. Start AD2 and select **Target > Display Board Information**. A window will appear with the PAM software version information and the part number of the Anadigm ASP IC (typically AN221E04). Click **OK**.

- Step 2. Select **Edit > Insert New CAM**. The index to the library of CAMs will be displayed. Make sure the Library is correct for the Anadigm ASP IC (typically ANx21 Standard) and double click the Sinewave Oscillator CAM. This CAM will appear to be attached to the tip of the cursor. Drag it into the center of the square outline of the IC and click once to drop it.

- Step 3. The parameter set up window specific to this CAM will appear. Click **OK** to accept defaults for now.

- Step 4. Select **Settings >Active Settings> Clocks** tab to adjust the system clock parameters. Point to the **Clock 1** setting line and use the UP/DOWN arrows to set this clock to be divided down **400** times from the system clock frequency to be **40.0 kHz**. Leave all other clock settings unchanged and then click **OK**.

- Step 5. Point to the Sinewave Oscillator CAM icon, right click and select **CAM Settings**. Set the parameters as follows:

- Clock A to use Clock 1 at 40 kHz

- Oscillator frequency to be 0.44 kHz

- Click on **Peak Amplitude** to confirm **3.6 Volts** (default).

Click **OK**.

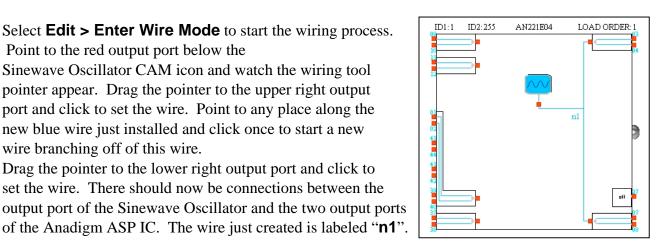

Step 6. Select **Edit > Enter Wire Mode** to start the wiring process. Point to the red output port below the Sinewave Oscillator CAM icon and watch the wiring tool pointer appear. Drag the pointer to the upper right output port and click to set the wire. Point to any place along the new blue wire just installed and click once to start a new wire branching off of this wire. Drag the pointer to the lower right output port and click to set the wire. There should now be connections between the output port of the Sinewave Oscillator and the two output ports

- Step 7. Point to the Download icon (it has a blue downward pointing arrow). Click once to download the configuration file representing this design into the Anadigm ASP IC on the PAM. The PAM should now show three green LEDs as ON with the 440 Hz Tuning-A tone coming out of the speakers.

- Step 8. The voltage output waveforms can be observed with an oscilloscope at the Analog connector Pin 13 for the right audio output channel and Pin 15 for the left audio output channel.

PAM-5002R User Manual

26

Note: some PC's will output a considerable amount of electromagnetic noise via both radiated and conducted pathways. If significant noise levels are seen with an oscilloscope or heard over the speakers, please do the following:

- Engage the typical 20 MHz Bandwidth Limit feature on the oscilloscope.

- Disconnect the RS-232 Serial cable from the PAM.

- Double check the noise level from the power source.

- Move the PAM and the oscilloscope away from the PC and away from its monitor.

Step 9. Select **Target > Display Board Information** to cause a soft reset of the Anadigm ASP IC and shut down the signal source. Alternatively, a power reset cycle for the Anadigm ASP IC can be done by pressing the small pushbutton next to the 2-pin +5V jumper for Analog Reset. Pushing the Master Reset button in the opposite corner resets both the Anadigm ASP IC and the microcontroller.

#### Storing a Serial EEPROM Copy of a Downloaded Configuration File

The Anadigm ASP IC operates in either MODE 0 or MODE 1 states. The PAM-5002R supports both:

- MODE 0 is under the control of a host controller for configuration updates. The on-board microcontroller assists with this process over the RS-232 serial communications pathway. Anadigm refers to this as the dynamic operating mode.

- MODE 1 is independent of external controllers with the Anadigm ASP IC loading a fixed configuration file from an attached Serial EEPROM on power up and after each analog reset. The onboard microcontroller has no role. Anadigm refers to this as the static operating mode.

The following procedure is used to store a copy of an Anadigm ASP configuration file into a Serial EEPROM during the typical MODE 0 development and download process. This EEPROM is then moved to the DIP socket connected to the Anadigm ASP IC to source the configuration file following a Power-On-Reset cycle in MODE 1. Once created, the EEPROM can be used as the permanent source for configuration files for all Anadigm ASP ICs used in MODE 1 including other Servenger products that support this operating MODE.

#### Needed:

- Servenger PAM-5002R series Programmable Analog Module and power source

- "Series 25" type SPI Serial EEPROM in 8 pin DIP format installed in DIP socket #1 (labeled 'DIP1') nearest to the microprocessor. The following have been tested for correct operation:

- Atmel AT25080A-10PI-2.7 (or larger capacity versions)

- Microchip 25AA080-I/P, 25AA080A-I/P, 25AA080B-I/P (or larger capacity versions)

- AnadigmDesigner<sup>®</sup>2 software running on a Windows PC with a serial cable to the RS-232 port. If you are using a USB-to-Serial converter unit connected to a laptop PC built without a serial port, please read the Advisory on USB-to-Serial adapters, flow control and RS-232 Serial cables in Step 3 of Connecting the Programmable Analog Module (PAM) to AnadigmDesigner<sup>®</sup>2.

- Step 1. Set up the PAM-5002 unit in MODE 0 (the normal download mode using AnadigmDesigner2): Set positions 1 & 2 of Switch SW5 (labeled 'MODE') to "ON" and position 3 to OFF. Close all 10 of the

Configuration Interface switch positions (Switch SW3). Apply power to the PAM and then connect the serial cable from the PC.

Step 2. Start and use the AnadigmDesigner2 design software in the normal manner to create and save an Anadigm configuration suitable for the application. Once completed testing, select the Control Switch Position 3 (labeled 'SW4 – C') to the ON position. Download the AnadigmDesigner2 configuration one more time exactly as before. The on-board microprocessor will reformat and store the configuration file into the Serial EEPROM ready to be used in the static operating MODE 1. A successful download of the intended configuration file is indicated by the Green Status LED being continuously ON. Save the design file and shut down AnadigmDesigner2. Go to next instruction.

#### Configuring the PAM with a Serial EEPROM

- Step 1. Remove the power from the PAM and set up for MODE 1 operation:

- Disconnect the RS-232 cable

- Remove the Serial EEPROM from socket labeled 'DIP1' and reinstall into the DIP socket farthest from the RS-232 DB-9 connector (labeled 'DIP2').

- Open all 10 of the Control Switches (SW3) on the Configuration Interface to isolate the microcontroller from the Anadigm ASP IC.

- Open positions 1 & 2 of the MODE Select Switch (SW5) and close position 3. For location of the switch refer to the photo Overview of the PAM on Page 5.

- Step 2. Reconnect the power to the PAM. The Anadigm ASP IC should immediately load the configuration file stored in the EEPROM and run. This can be repeated by pressing the Anadigm ASP Reset pushbutton that is in the upper right corner just above the DC Power Jack.

#### **Accessories**

If you wish to connect a PAM-5002R unit to a Host System using the Analog Connector and the Digital Connector requires soldering connectors onto the PAM unit and the host system. On the PAM unit install the connectors on the inner most row of holes. On the Analog Connector these are the smaller diameter holes.

The connector on the PAM unit is a 1 row by 20 position female connector which mates with 0.025 inch (0.635mm) pins on 0.100 inch (2.54mm) centers on the Host circuit board. Examples of these parts are:

Sullins Electronics Corp. Part Number PPPC201LFBM-RC Samtec Inc, Part Number SSW-120-01-SS

The connector to mate with this on the Host System is a 1 row by 20 position male connector with 0.025 inch (0.635 mm) pins on 0.100 inch (2.54mm) centers. Examples of these parts are:

Sullins Electronics Corp. Part Number PBC20SAAN

Samtec Inc, Part Number SSW-120-01-SS

These parts are available from several distributors including Digi-Key.

# **Specifications MECHANICAL SPECIFICATIONS**

#### **Mechanical Outlines and Clearance**

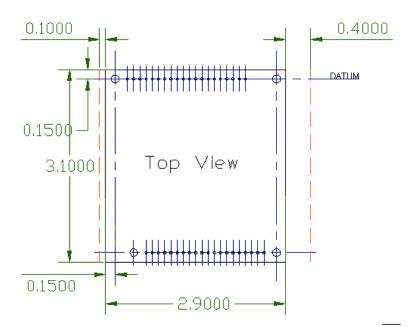

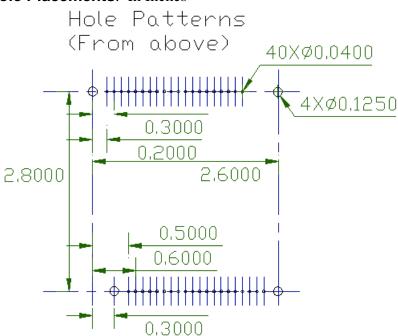

#### **PAM Mechanical Drawing, Top View**: (in Inches)

The figure to the left shows a view from above of the PAM board. The overall dimensions are 2.90 inches (73.7mm) parallel to the Analog Connector or the Digital Connector and 3.10 inches (78.7mm) perpendicular to these same connectors. In addition there is 0.4 inch (10.2mm) of clearance from the rightmost edge shown to allow for the right angle DB 9 (RS-232) connector (the rightmost red line.). There is also an additional 0.1 inch (2.54mm) clearance from the opposite edge to allow for the right angle Stereo Input and Output Connectors. (The leftmost red line.)

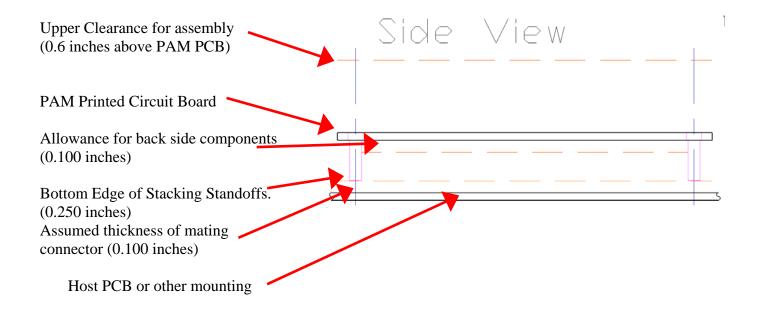

#### **PAM Mechanical Drawing, Side View** (in Inches)

The figure below shows the vertical situation of the PAM board, which will be dependent on the mating connector on the host system.

If installed, the 1 x 20 female connectors described in the **Accessories** section are just over three tenths of an inch high. (0.3337 inches or 8.56mm). The total clearance above the host circuit board is thus approximately one inch plus the thickness of the mating connector housings. Without these connectors, the white plastic Stacking Standoffs will hold the bottom of the PAM circuit board 0.250 inch (6.35mm) above the mounting surface.

There could be some useable space on the host board under the PAM board. This space is between the 1 x 20 connectors and is approximately two tenths of an inch (0.20 inch, 1.08 mm) high. This should be enough clearance for a socketed dip IC or equivalent height components.

#### **Mechanical Specifications for Connection to a Host PCB**

The Host PCB should use the following Input / Output and Mounting Hole placements to mate with the PAM printed circuit board.

There are white plastic Stacking Standoffs installed at the 4 corners. These Standoffs have an approximately 0.125 inch diameter through hole to allow a 4-40 screw to pass through to attach a PAM assembly onto a Host PCB. The Standoffs can be easily removed to use pressed-in studs in the Host PCB to mount the PAM. When the Standoffs are removed, the 4 corner holes in the PAM circuit board are 0.187 inch diameter.

#### **Hole Placements**: In Inches

#### **Electrical Specifications**

#### **Analog Input and Output Specifications**

| Direction | Buffering  | Rating                  | Precision          |

|-----------|------------|-------------------------|--------------------|

| Input     | Buffered   | +/- 3.0 Volts each side | High Precision     |

|           | Buffered   | +/- 3.8 Volts each side | Standard Precision |

| Input     | Unbuffered | +/- 3.0 Volts each side | High Precision     |

|           | Unbuffered | +/- 3.8 Volts each side | Standard Precision |

| Output    | Buffered   | +/- 3.0 Volts each side | High Precision     |

|           | Buffered   | +/- 3.8 Volts each side | Standard Precision |

| Output    | Unbuffered | +/- 1.5 Volts each side | High Precision     |

|           | Unbuffered | +/- 1.9 Volts each side | Standard Precision |

#### **Considerations for Usable Bandwidth**

The internal structure of the Anadigm ASP IC allows a maximum usable bandwidth of up to approximately 2 MHz with the most accurate analog signal processing up to approximately 250 KHz input signal frequency.

#### **Absolute Maximums**

Maximum input voltage (for 50 Ohm load) = 7 Volts peak, all inputs

Maximum Power Supply Voltage is 5.5 Volts from a bench supply or a Host PCB.

Maximum Power Supply Voltage supplied to the DC Power Jack is 12 Volts (limited by the thermal dissipation of the on-board LM78H05 linear regulator).

#### **SIGNAL PIN-OUTS**

#### PAM-5002 Series Digital and Analog Board Level Connector Pin-Outs

Connection is through two 1 x 20 position female connectors on secondary side to fit 0.025 square posts on 0.100 inch centers plus 0.040 inch diameter solder attachment holes next to each pin position. Naming convention includes trailing "b" to mean "BAR" for LOW assertion of signal.

| Digital 1 x 20 Connector |                                         |                            |  |  |

|--------------------------|-----------------------------------------|----------------------------|--|--|

|                          | Name                                    | Туре                       |  |  |

| 1                        | TXDATA-OUT                              | RS-232 Data Output         |  |  |

| 2                        | RXDATA-IN                               | RS-232 Data Input          |  |  |

| 3                        | CTS-IN                                  | RS-232 Flow Control Input  |  |  |

| 4                        | RTS-OUT                                 | RS-232 Flow Control Out    |  |  |

| 5                        | DTE-READY                               | Station Flow Control Input |  |  |

| 6                        | DCE-READY                               | Station Flow Control Out   |  |  |

| 7                        | ERRb                                    | Anadigm Error Output       |  |  |

| 8                        | ACTIVATE                                | Anadigm Activate Output    |  |  |

| 9                        | EXECb                                   | Anadigm Execute Input      |  |  |

| 10                       | Digital GND                             | Digital Ground             |  |  |

| 11                       | Digital VCC (+5V)                       | Digital Power              |  |  |

| 12                       | M-RESETb                                | Master Reset Input         |  |  |

| 13                       | (Reserved for future use)               |                            |  |  |

|                          |                                         |                            |  |  |

| 14                       | (Reserved for future use)               |                            |  |  |

|                          | (D. 10.0)                               |                            |  |  |

| 15                       | (Reserved for future use)               |                            |  |  |

| 16                       | (Reserved for future use)               |                            |  |  |

| 10                       | (Neservea jor juiure use)               |                            |  |  |

| 17                       | (Reserved for future use)               |                            |  |  |

| 17                       | (Neserveu joi juiure use)               |                            |  |  |

|                          |                                         |                            |  |  |

| 18                       | (Reserved for future use)               |                            |  |  |

|                          | (Reserved for future use)               |                            |  |  |

|                          |                                         |                            |  |  |

| 19                       | (Reserved for future use)               |                            |  |  |

|                          | , , , , , , , , , , , , , , , , , , , , |                            |  |  |

|                          |                                         |                            |  |  |

| 20                       | ONb                                     | Control Output indicating  |  |  |

|                          |                                         | Anadigm signal processing  |  |  |

|                          |                                         | is active                  |  |  |

|                          |                                         |                            |  |  |

| <u> </u>                |                  |                                            |  |

|-------------------------|------------------|--------------------------------------------|--|

| Analog 1 x 20 Connector |                  |                                            |  |

|                         | Name             | Туре                                       |  |

| 1                       | A-RESETb         | Anadigm Reset Input                        |  |

| 2                       | OUT3             | Unbuffered IO3 – Positive                  |  |

| 3                       | IN4PD            | Unbuffered IO4D - Positive                 |  |

| 4                       | IN4PC            | Unbuffered IO4C - Positive                 |  |

| 5                       | IN4PB            | <b>Unbuffered Differential IO4B – Pos.</b> |  |

| 6                       | IN4NB            | Unbuffered Differential IO4B – Neg.        |  |

| 7                       | IN4PA            | <b>Unbuffered Differential IO4A – Pos.</b> |  |

| 8                       | IN4NA            | Unbuffered Differential IO4A – Neg.        |  |

| 9                       | Analog GND       | Analog Ground                              |  |

| 10                      | Analog VCC (+5V) | Analog Power                               |  |

| 11                      | Analog VCC (+5V) | Analog Power                               |  |

| 12                      | Analog GND       | Analog Ground                              |  |

| 13                      | OUT1,            | Buffered Output 1 Single-Ended,            |  |

|                         |                  |                                            |  |

| 14                      | (open)           |                                            |  |

|                         |                  |                                            |  |

| 15                      | OUT 2,           | Buffered Output 2 Single-Ended,            |  |

|                         |                  |                                            |  |

| 16                      | (open)           |                                            |  |

| 15                      | TATED.           | D 66 11 41 D 44                            |  |

| 17                      | IN1P,            | Buffered Input 1 – Positive,               |  |

|                         | or               | or                                         |  |

| 10                      | ION1P            | Unbuffered I/O 1 - Positive                |  |

| 18                      | IN1N,            | Buffered Input 1 – Negative,               |  |

|                         | or               | or                                         |  |

| - 10                    | ION1N            | Unbuffered I/O 1 - Negative                |  |

| 19                      | IN2P,            | Buffered Input 2 – Positive,               |  |

|                         | or               | or                                         |  |

|                         | ION2P            | Unbuffered I/O 2 - Positive                |  |

| 20                      | IN2N,            | Buffered Input 2 – Negative,               |  |

|                         | or               | or                                         |  |

|                         | ION2N            | Unbuffered I/O 2 - Negative                |  |

# **Digital Connector Pin Assignment and Function Details**

|    | Name               | Туре          | Comment                                                               | Expected Voltage Levels                  |

|----|--------------------|---------------|-----------------------------------------------------------------------|------------------------------------------|

| 1  | TXDATA-OUT         | Output        | RS-232 Transmit Data toward external                                  |                                          |

| -  | TADATA GOT         | Output        | PC or other controller                                                | typically idles at approx -7V to -8V     |

| 2  | RXDATA-IN          | Input         | RS-232 Receive Data from external PC                                  | RS-232 +/- levels around 0V,             |

| _  | TOTAL TITLE        | Input         | or other controller                                                   | typically idles at approx -7V to -8V     |

| 3  | CTS-IN             | Input         | RS-232 hardware flow control Clear                                    | RS-232 +/- levels around 0V,             |

|    | CISIN              | Input         | To Send signal from external PC or                                    | typically idles at approx -7V to -8V     |

|    |                    |               | other controller                                                      | (CTS assertion is positive level)        |

| 4  | RTS-OUT            | Output        | RS-232 hardware flow control Request                                  | RS-232 +/- levels around 0V,             |

| -  | 1115 001           | o uspus       | To Send signal toward external PC or                                  | typically idles at approx -7V to -8V     |

|    |                    |               | other controller                                                      | (RTS assertion is positive level)        |

| 5  | DTE-READY          | Input         | External station signals to unit that it                              | RS-232 +/- levels around 0V              |

|    |                    | pu-           | is ready to communicate                                               |                                          |

| 6  | DCE-READY          | Output        | Unit informs external station that it is                              | RS-232 +/- levels around 0V              |

|    |                    | o ang an      | ready to communicate (hardware loop                                   |                                          |

|    |                    |               | through of DTE READY signal)                                          |                                          |

| 7  | ERRb               | Output        | ERRORb output signal from Anadigm                                     | Idles HI through 10kohm pull up          |

|    |                    | (Open Drain   | ASP IC. LOW means an error                                            | resistor. LOW during M-RESETb or         |

|    |                    | from Anadigm  | condition has occurred during                                         | A-RESETb then goes HI following          |

|    |                    | IC)           | attempted Anadigm configuration                                       | release of RESET input allowing power    |

|    |                    |               | cycle and that the analog outputs may                                 | up reset and configuration cycle to      |

|    |                    |               | not be valid                                                          | proceed. Stays HI unless a configuration |

|    |                    |               |                                                                       | error occurs or RESET input is asserted. |

| 8  | ACTIVATE           | Output        | ACTIVATE output signal from                                           | Idles HI through 47kohm pull up          |

|    |                    | (Open Drain   | Anadigm IC.                                                           | resistor. LOW during PORb and            |

|    |                    | from Anadigm  |                                                                       | Primary Configuration cycle then goes    |

|    |                    | IC)           |                                                                       | HI indicating successful end of Primary  |

|    |                    |               |                                                                       | Configuration cycle.                     |

|    | Input              |               | Forcing LOW will hold off completion of Configuration Programming cyc |                                          |

| 9  | EXECb              | Input         | EXECUTE input to Anadigm IC.                                          | Idles HI through 10kohm pull up          |

|    |                    |               | Used when configuration file is set up                                | resistor. Pull to GND to immediately     |

|    |                    |               | to wait for "EXECUTE" input to                                        | assert EXECUTE command to Anadigm.       |

|    |                    |               | transfer new file from Shadow RAM                                     | Controlled by ENDEXECUTE bit in          |

|    |                    |               | into Configuration RAM                                                | Control Byte of configuration file.      |

| 10 | Digital GND        | Digital GND   | Digital GND                                                           | Opening the 10 switches SW3 isolates     |

| 44 | DI II IIIGG        | B B           | Di tri large (c. 100)                                                 | from Anadigm GND power and plane.        |

| 11 | Digital VCC        | Digital Power | Digital VCC (+5V)                                                     | Opening the 10 switches SW3 isolates     |

| 10 | (+5V)              | -             |                                                                       | from Anadigm VCC power and plane.        |

| 12 | M-RESETb           | Input         | Master Reset of microcontroller and                                   | Idles HI through 10kohm pull up          |

| 12 | /D 10 0 :          | \             | Anadigm IC.                                                           | resistor. LOW to assert.                 |

| 13 | (Reserved for futu | re use)       |                                                                       |                                          |

| •  | ▼                  |               |                                                                       |                                          |

| 19 | (Reserved for futu |               |                                                                       |                                          |

| 20 | ONb                | Output        | Indicates that Anadigm IC is                                          | Idles HI through 10kohm pull up          |

|    |                    |               | configured and performing intended                                    | resistor. LOW when Anadigm analog        |

|    |                    |               | analog signal processing functions.                                   | signal processing is occurring.          |

|    |                    |               | ONb is asserted when "Anadigm ON"                                     |                                          |

|    |                    |               | green LED is illuminated.                                             |                                          |

# Analog Connector Pin Assignment and Function Details with Input and Output Buffers Installed

| 1  | A-RESETb            | Pull to zero volts externally to reset Anadigm IC and release to initiate power up reset process, microcontroller not affected (47kohm on-board resistor pull-up & 500 ohm series resistor) |                                                                                                                                                                                                                             |  |

|----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2  | OUT3                | Unbuffered Input/Output IO3-Positive, used as an Output in this text.                                                                                                                       | Direct coupled single-ended input/output to IO3-Positive; 25 Ω in series, 47.5 kΩ pull down to common mode midrange for Anadigm IC; Not filtered. (see Note 6)                                                              |  |

| 3  | IN4PD               | Unbuffered Input IO4D-Positive                                                                                                                                                              | AC coupled single-ended input to IO4 multiplexer pathway D-Positive; 20 KΩ terminated; 1/2 attenuation AC coupled to common mode mid-range for Anadigm IC; AC corner frequency set by installed RC values (see Notes 3 & 5) |  |

| 4  | IN4PC               | Unbuffered Input IO4C-Positive                                                                                                                                                              | AC coupled single-ended input to IO4 multiplexer pathway C-Positive; 20 KΩ terminated; 1/2 attenuation AC coupled to common mode mid-range for Anadigm IC; AC corner frequency set by installed RC values (see Note 3 & 5)  |  |

| 5  | IN4PB               | Unbuffered Input IO4B-Positive                                                                                                                                                              | AC coupled differential input to IO4 multiplexer pathway                                                                                                                                                                    |  |

| 6  | IN4NB               | Unbuffered Input IO4B-Negative                                                                                                                                                              | B; 20 KΩ terminated each side; 1/2 attenuation AC coupled to common mode mid-range for Anadigm IC; AC corner frequency set by installed RC values (see Note3 & 5)                                                           |  |

| 7  | IN4PA               | <b>Unbuffered Input IO4A-Positive</b>                                                                                                                                                       | AC coupled differential input to IO4 multiplexer pathway                                                                                                                                                                    |  |

| 8  | IN4NA               | Unbuffered Input IO4A-Negative                                                                                                                                                              | A; 20 KΩ terminated each side; 1/2 attenuation AC coupled to common mode mid-range for Anadigm IC; AC corner frequency set by installed RC values (see Note3 & 5)                                                           |  |

| 9  | Analog GND          | Analog Ground                                                                                                                                                                               | Remove Jumper 11 in series with on-board +5V linear                                                                                                                                                                         |  |

| 10 | Analog VCC<br>(+5V) | Analog Power                                                                                                                                                                                | regulator when +5V regulated power is supplied externally through this connector; -5V switching power                                                                                                                       |  |

| 11 | Analog VCC<br>(+5V) | Analog Power                                                                                                                                                                                | converter (when installed) runs in either case.                                                                                                                                                                             |  |

| 12 | Analog GND          | Analog Ground                                                                                                                                                                               |                                                                                                                                                                                                                             |  |

| 13 | OUT1                | Buffered Output 1 Single-Ended                                                                                                                                                              | DC coupled single-ended outputs; low source resistance                                                                                                                                                                      |  |

| 14 | (open)              |                                                                                                                                                                                             | (50 $\Omega$ series resistor can be installed, AC series coupling                                                                                                                                                           |  |

| 15 | OUT 2               | Buffered Output 2 Single-Ended                                                                                                                                                              | caps can be installed);                                                                                                                                                                                                     |  |

| 16 | (open)              |                                                                                                                                                                                             | With +/-5 V power supplies installed:<br>+/- 3 Volt max output at 50mA<br>With +5 V only power supply installed:<br>+1 to +3 V max output at 50mA.<br>See Note 4.                                                           |  |

| 17 | IN1P                | Buffered Input 1 – Positive                                                                                                                                                                 | DC coupled differential or single-ended inputs with 50 $\Omega$ ,                                                                                                                                                           |  |

| 18 | IN1N                | Buffered Input 1 – Negative                                                                                                                                                                 | 600 Ω or Hi-Z termination (Note 2 & 3); Amplifier gain of                                                                                                                                                                   |  |

| 19 | IN2P                | Buffered Input 2 – Positive                                                                                                                                                                 | 1/2; input buffer provides correct common mode to                                                                                                                                                                           |  |

| 20 | IN2N                | Buffered Input 2 – Negative                                                                                                                                                                 | Anadigm. With +/-5 V power supplies installed, accepts +/- 4.5V max input signals. With +5 V only power supply installed, accepts +0.5V to +4.5V input signals.                                                             |  |

(Notes on next page)

- Note 1: All Unbuffered Inputs can be reconfigured to be DC coupled with the user supplying common mode signal at +2.0V. All Unbuffered Inputs can also be reconfigured as unbuffered Outputs with either AC or DC coupling.

- Note 2: Buffered Inputs are provided with switches to select for:

- **Termination** values of 50  $\Omega$ , 600  $\Omega$  or Hi-Z (approximately 2,000  $\Omega$  per side or 4,000  $\Omega$  differentially).

- Differential (balanced) inputs or single-ended (unbalanced) inputs.

- **Balance** adjustment for 50  $\Omega$  or 600  $\Omega$  single-ended signals.

- Note 3: Buffered and unbuffered inputs have multi-pole R-C values installed to act as the anti-aliasing low pass filters required for correct sampled analog signal processing consult Factory with application frequencies to establish filter values or install new capacitor values per the instructions herein. The Anadigm internal programmable input voltage buffer/filters are usable as anti-aliasing filters with good performance below approximately 15kHz and +/- 1 Vpp.

- Note 4: Buffered outputs have single-pole R-C values installed to act as reconstruction filters to remove out-of-band higher frequency signals resulting from the sampled analog signal processing consult Factory with application frequencies to establish filter values or install new capacitor values per the instructions herein. The Anadigm internal programmable output voltage buffer/filters are usable as reconstruction filters with good performance below approximately 15kHz and +/- 1 Vpp.

- Note 5: The Anadigm IO4 input/output pathway is built as a 4:1 multiplexer only one of the A, B, C or D pathways into the interior of the IC can be selected at one time (selection is specified in the downloaded Configuration file).

Note 6: The circuit on OUT3 is as follows:

| Stereo Input Jack |                    |                                  |                                                           |  |

|-------------------|--------------------|----------------------------------|-----------------------------------------------------------|--|

| Tip               | Stereo Left        | Common with Pin 17,              | Stereo input left channel input; DC coupled single-ended  |  |

| _                 | Channel            | IN1P Buffered Input 1 - Positive | signal vs. GND                                            |  |

| Ring              | Stereo Right       | Common with Pin 19,              | Stereo input right channel input; DC coupled single-ended |  |

|                   | Channel            | IN2P Buffered Input 2 - Positive | signal vs. GND                                            |  |

| Sleeve            | Analog Ground      | Analog Ground                    | Stereo ground reference                                   |  |

|                   | Stereo Output Jack |                                  |                                                           |  |

| Tip               | Stereo Left        | Common with Pin 15, Buffered     | Stereo input left channel output; DC coupled single-ended |  |

| _                 | Channel            | Output 1 Single-Ended (OUT1)     | with 50 mA available current thru 25 ohms                 |  |

| Ring              | Stereo Right       | Common with Pin 13, Buffered     | Stereo input right channel output; DC coupled single-     |  |

|                   | Channel            | Output 2 Single-Ended (OUT2)     | ended with 50 mA available drive current thru 25 ohms     |  |

| Sleeve            | Analog Ground      |                                  | Stereo ground reference                                   |  |

| DC Power Jack                                                                                                          |                           |                                                   |  |

|------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------------------------------|--|

|                                                                                                                        | 2.1 mm I.D. x 5.5 mm O.D. |                                                   |  |

| Tip                                                                                                                    | +9VDC                     | +7.2VDC to +12VDC input to +5VDC linear regulator |  |

|                                                                                                                        | nominal                   |                                                   |  |

| Sleeve                                                                                                                 | Analog Ground             | Analog Ground                                     |  |

| Remove Jumper in series with on-board +5V linear regulator when +5V regulated power is supplied externally through the |                           |                                                   |  |

Remove Jumper in series with on-board +5V linear regulator when +5V regulated power is supplied externally through the 1 x 20 pin Analog connector; -5V switching power converter (when installed) runs in either case

## **Appendix**

#### What Does This Mean?

The white Arrow indicates that this position is intentionally left open for a reason that may be described below.

On a schematic the part value is either "NP" or "Not Placed".

#### Cable Shield to Board Ground

Adding a 100-Ohm resistor in position R11 connects the RS-232 Cable Shield to the PAM-5002 board ground. To completely isolate the shield from board ground leave this open.

R11, an 0805 size component.

#### Replacement AC Adapter

If a replacement AC adapter is needed, Radio Shack and other vendors sell several versions with replaceable connectors. Digi-Key, Newark Electronics and Jameco Electronics carry these under names similar to "Plug-In Power Supplies". The adapter must be fitted with a 2.1 mm ID x 5.5 mm OD power connector showing CENTER POSITIVE on a typical polarity illustration – sometimes called "Tip Positive".

If using Radio Shack's "M" end connector (with the blue insulation ring) it must be CENTER POSITIVE, installed with TIP next to the + sign.

# **Test Point List:**

The following is a list of the signals associated with each test point.

| Test Point ID | Signal Name |

|---------------|-------------|

| TP1           | O2N         |

| TP2           | O2P         |

| TP3           | O1N         |

| TP4           | O1P         |

| TP5           | IO4NA       |

| TP6           | IO4PA       |

| TP7           | IO4PC       |

| TP8           | IO4PD       |

| TP9           | VMRCMORE    |

| TP10          | VMRCLESS    |

| TP11          | VMRC        |

| TP12          | IO2P        |

| TP13          | IO2N        |

| TP14          | (unused)    |

| TP15          | IO1N        |

| TP16          | IO1P        |

| TP17          | IO3P        |

| TP18          | IO4NB       |

| TP19          | IO4PB       |

| TP20          | (unused)    |

|               |             |

# Index

| $\boldsymbol{A}$                                                                    |

|-------------------------------------------------------------------------------------|

| Accessories                                                                         |

| Inputs                                                                              |

| Analog Connector                                                                    |

| Appendix                                                                            |

| B                                                                                   |

| Block Diagram of PAM-5002R7                                                         |

| C                                                                                   |

| Configuration AdjustmentSee also Switches or Filters Configuring the PAM            |

| Storing a Serial EEPROM Copy of Configuration26 Creating and Downloading a Sample25 |

| D                                                                                   |

| Digital Connector 13<br>Pinout 34                                                   |

| $\boldsymbol{E}$                                                                    |

| Electrical Specifications                                                           |

| I                                                                                   |

| Indicators                                                                          |

| Inputs                                  | 10          |

|-----------------------------------------|-------------|

| Analog                                  | 10          |

| L                                       |             |

| LEDs                                    | 9           |

| M                                       |             |

| Mechanical Specifications               | 29          |

| Modifying the Input and Output Filters  |             |

| Buffered Inputs                         |             |

| Outputs                                 |             |

| Unbuffered Inputs                       |             |

| 0                                       |             |

| Outputs                                 |             |

| Analog                                  | 12          |

| Overview of the PAM board               | 5           |

| P                                       |             |

| PAM Inputs routed to Anadigm ASP Inputs | 11          |

| Power                                   | 8           |

| Power Connector                         |             |

| Power Connector Pinout                  | 36          |

| ProgrammingSee Configur                 | ing the PAM |

| S                                       |             |

| Signal Connections                      | 10          |

| Stereo Connector                        |             |

| Pinouts                                 | 36          |

| Stereo Input Connector                  |             |

| Input                                   | 10          |

| Stereo Output Connector                 |             |

| Switches                                | 14          |

| Anadigm ASP Mode Selection              |             |

| Termination Resistance                  | 16          |

| Balance Adjustment                      | 16          |

| Differential or Single Ended Mode       | 15          |

# Servenger LLC

515 NW Saltzman Rd., #904 Portland, Oregon 97229

Phone: 503-627-9930

Web: www.servenger.com Email: sales@servenger.com

Statement of Limited Warranty and Returns Policy: Servenger LLC warrants that its products will function as advertised when used according to the specifications, limitations and instructions provided in the User Manuals and associated Application Notes shipped with the products and/or downloaded from the Servenger website for 1 year from the invoice date. Performance under this warranty is limited to repair or like-for-like replacement with the same or equivalent product then in production. Additionally we will accept back and refund to you the purchase price less costs of shipping and merchant account fees for any reason for an undamaged Servenger product for the first 30 days from the invoice date. Servenger will ship products to you fully insured for transportation loss or damage. Returned items must also be fully insured for transportation loss or damage by you. Servenger reserves the right to change its products without notice.