ANSI C Compiler comes with Omniscient Code Generation™

### DENSER CODE in 1/2 the time

### HI-TECH C PRO for the PIC10/12/16 MCU

Family - Based on the reliable PICC<sup>™</sup> STD compiler, and supporting Microchip's PIC10/12/14/16/17 series of MCUs, the new HI-TECH C PRO for the PIC10/12/16 MCU Family ANSI C Compiler comes with Omniscient Code Generation.

### **OMNISCIENT CODE GENERATION**

Extracts information from multiple source files simultaneously, allowing more intelligent state-of-the-art code generation that:

- Automatically handles memory banking without requiring special qualifiers;

- Optimizes the size of each pointer variable in your code based on its usage;

- Eliminates the need for many nonstandard C qualifiers and compiler options;

- Produces more optimal interrupt context switching code;

- Customizes the functionality of the included printf library function;

- Automatically analyzes user assembly and object code files; and

- Is simple to use.

### DENSER CODE, IN HALF THE TIME.

Code compiled with HI-TECH C PRO for the PIC10/12/16 MCU Family can deliver up to 30% denser code than you are currently producing. Additionally, automatic memory and stack management could cut your development time in half.

### **FREE 45 DAY EVALUATION**

A fully functional 45 day trial version of the HI-TECH C PRO for the PIC10/12/16 MCU Family will be available, free of charge from HI-TECH's website. Order your demo at www.htsoft.com/portal/ccpiccpro.

### PRICE AND AVAILABILITY

HI-TECH C PRO for the PIC10/12/16 MCU Family includes, at no extra cost:

HI-TECH Priority Access<sup>™</sup> - 12 months access to updates and technical support; and

HI-TECH Satisfaction Guarantee - a hassle-free 30 day money back guarantee.

FOR RELEASE THIS MONTH

HI-TECH Software proudly supports the Microchip brand with industrial-strength software development tools and C compilers. PICC is licensed exclusively to HI-TECH Software by Microchip Technology Inc.

# Embedded Systems Design

DECEMBER 2007

VOLUME 20, NUMBER 12

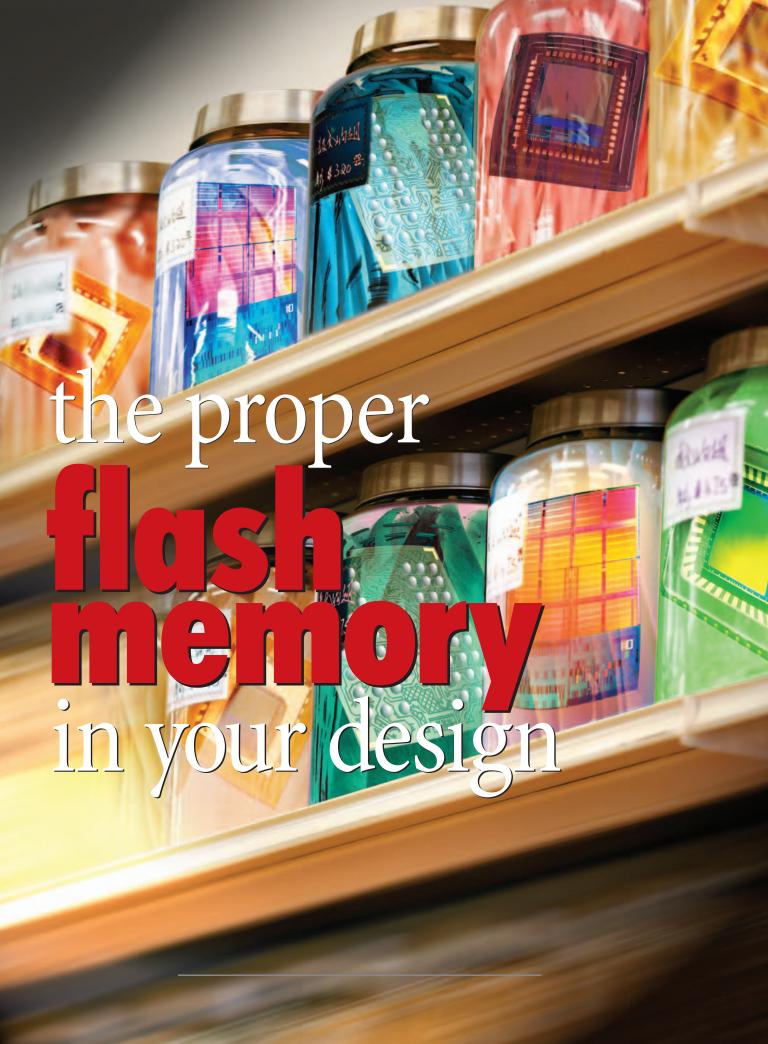

### Cover Feature: Employ the proper flash memory in your design

BY VIJAY K. DEVADIGA

To NAND or NOR. That is the question. Different applications and functions should be handled with different types of flash memory.

# Lower the cost of intelligent power control with FPGAs

BY WENDY LOCKHART

Combining a programmable solution with an industry-standard processor core can save time, money, and real estate.

**26**<sup>33</sup>

# The basics of embedded multitasking on a PIC

BY GAMAL ALI LABIB

High-end concepts typically aren't applied to an 8-bit MCU. But don't rule them out just yet.

**《**34

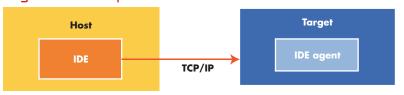

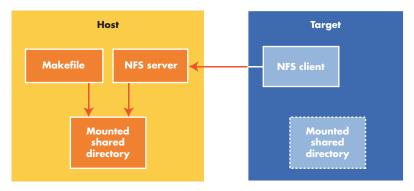

# Do-it-yourself embedded Linux development tools

BY ALEXANDER SIROTKIN

These key tools can be fine-tuned to fit your needs and your style of work.

EMBEDDED SYSTEMS DESIGN (ISSN 1558-2493 print; ISSN 1558-2507 PDF-electronic) is published monthly by CMP Media LLC., 600 Harrison Street,

5th floor, San Francisco, CA 94107, (415) 947-6000. Please direct advertising and editorial inquiries to this address.

SUBSCRIPTION RATE for the United States is \$55 for 12 issues. Canadian/Mexican orders must be accompanied by payment in U.S. funds with additional

postage of \$6 per year. All other foreign subscriptions must be prepaid in U.S. funds with additional postage of \$15 per year for surface mail and \$40 per year

for airmail. POSTMASTER: Send all changes to EMBEDDED SYSTEMS DESIGN, EO. Box 3404, Northbrook, IL 60065-9468. For customer service,

telephone toll-free (877) 676-9745. Please allow four to six weeks for change of address to take effect. Periodicals postage paid at San Francisco, CA

and additional mailing offices. EMBEDDED SYSTEMS DESIGN is a registered trademark owned by the parent company, CMP Media LLC. All material

published in EMBEDDED SYSTEMS DESIGN is Sopyright © 2005 by CMP Media LLC. All rights reserved. Reproduction of material appearing

in EMBEDDED SYSTEMS DESIGN is forbidden without permission.

### rolumos

### programmer's

**((11**

### Who needs matrices?

BY JACK W. CRENSHAW

If you can toss around

matrices as you might a

Frisbee, you're one of the

superheroes. If not, you're on

the sidelines, watching.

### break points

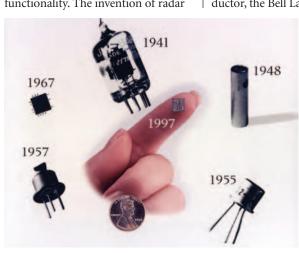

### The transistor: sixty years old and still switching

BY JACK G. GANSSLE

Sixty years ago this month, scientists at Bell Labs demonstrated the most important invention of the 20th century: the first real transistor.

### departments

### #include

**((** )

### Twenty years of Embedded

BY RICHARD NASS

The more things change, the more they stay the same.

### analyst's corner

(49

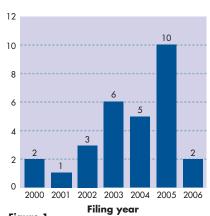

### Search for embedded Linux patents

BY DANNY R. GRAVES

In many cases, "free" isn't really free.

### parity bit

(()

### advertising index << 5

marketplace

**((**5

### in person

### **ESC Silicon Valley**

San Jose Convention Center April 14–18, 2008 www.embedded.com/esc/sv/

### on-line

### www.embedded.com

### Web archive:

www.embedded.com/archive

### **Article submissions:**

www.embedded.com/wriguide

### FAST-FORWARD TURNAROUND TIME.

The pursuit of perfection takes time. But you can speed up the unnecessary slowdowns. Windows® Embedded helps accelerate the creation of next-generation smart, connected devices by giving you access to an active global community: forums, newsgroups, tutorials, support, and the MSDN® Windows Embedded Developer Center. At the same time, Windows Embedded Partners are there to provide expert support and services to help get your devices delivered on time. Learn more about how to fast-forward device development at: windowsembedded.com/fastforward

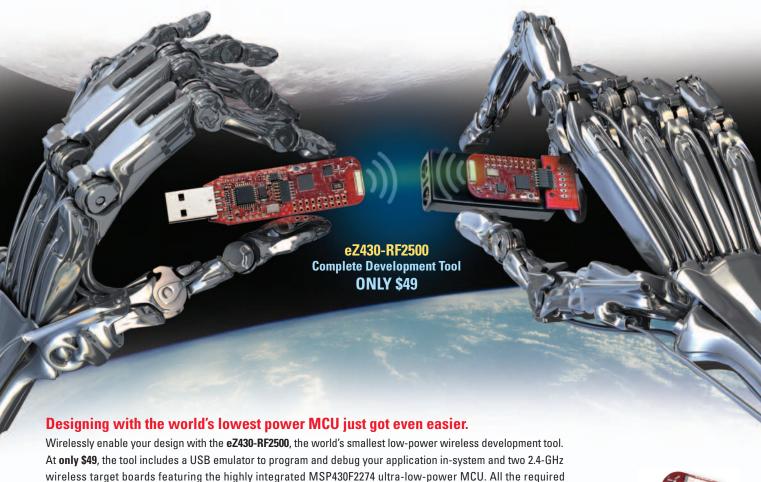

# MSP430 Goes Wireless

| software is included such as a complete integrated Development Environment and Simplici 11 <sup></sup> , a propriety low-power star network stack, enabling robust wireless networks out of the box. The MSP430F22x4 combines 16-MIPS performance with a 200-ksps 10-bit ADC and 2 op-amps and is paired with the CC2500 multi-channel RF transceiver designed for low-power wireless applications. |       |                    |         |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|---------|--|--|--|

| MCU: MSP430F2274                                                                                                                                                                                                                                                                                                                                                                                    |       | RF Transceiver: CC | 2500    |  |  |  |

| Flash                                                                                                                                                                                                                                                                                                                                                                                               | 32 KB | Frequency          | 2.4 GHz |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                     |       |                    |         |  |  |  |

| MCU: MSP430F2274 |                                           | RF Transceiver: CC2500 |          |  |

|------------------|-------------------------------------------|------------------------|----------|--|

| Flash            | 32 KB                                     | Frequency              | 2.4 GHz  |  |

| RAM              | 1 KB                                      | Sensitivity            | -101 dBm |  |

| Analog           | 10-bit ADC, 2 op amps                     | Max Data Rate          | 500 kbps |  |

| Communication    | UART/LIN, IrDA, (2) SPI, I <sup>2</sup> C | RX Current             | 13.3 mA  |  |

| Standby Current  | 0.7 μΑ                                    | TX Current             | 21.2 mA  |  |

Coming Soon!

Need to extend your network?

Additional eZ430-RF2500T target boards can be ordered for \$20 each.

www.ti.com/ez430-rf

Order Today! www.ti.com/ez430-rf or 800.477.8924, ext. 4037

Technology for Innovators, the red/black banner and SimpliciTI are trademarks of Texas Instruments

1880A0

# Embedded Systems Design

Richard Nass (201) 288-1904

### Managing Editor

Susan Rambo srambo@cmp.com

### Contributing Editors

Michael Barr John Canosa Jack W. Crenshaw Jack G. Ganssle Larry Mittag

### Art Director

drommel@cmp.com

### European Correspondent

colin.holland@htinternet.com

### Embedded.com Site Editor

bccole@acm.org

### Production Manager

Pete Scibilia pscibili@cmp.com

Kristi Cunningham kcunningham@cmp.com

### Subscription Customer Service

P.O. Box 2165, Skokie, IL 60076 (800) 577-5356 (toll free), Fax: (847) 763-9606 embeddedsystemsdesign@halldata.com www.embeddedsystemsdesigncustomerservice.com

### Back Issues

Kelly Minihan (800) 444-4881 (toll free). Fax: (785) 838-7566

### Article Reprints, E-prints, and Permissions

PARS International Corp. 102 West 38th Street, Sixth Floor (212) 221-9595, Fax: (212) 221-9195 reprints@parsintl.com www.magreprints.com.quickquote.asp

### Publisher

David Blaza dblaza@cmp.com

### Editorial Review Board

Jack W. Crenshaw Iack G. Ganssle Bill Gatliff Nigel Jones Niall Murphy Dan Saks Miro Samek

### Corporate

David Levin Adam Marder

Acting Chairman Executive Vice President and Chief Financial Officer President, CMP Business Technology

Tony Uphoff Robert Faletra

President, CMP Channel President, CMP Electronics Group President, CMP Game, Dobb's, ICMI

Paul Miller Philip Chapnick

Group Corporate Senior Vice President, Sales Senior Vice President, Human

Anne Marie Miller Marie Myers

Senior Vice President, Manufacturing Senior Vice President, Communications

Alexandra Raine

### **BY Richard Nass**

# 20 years of **Embedded**

he year 2008 marks two important milestones for our Embedded franchise, which consists Embedded.com, this magazine, and the Embedded Systems Conference. In April, we will hold the 20th Annual California-based Embedded Systems Conference. And then later in the year, November to be exact, we'll mark 20 years of publishing Embedded Systems Design magazine (although it was known as Embedded Systems Programming for its first 17 years).

There's a common phrase that definitely applies here: the more things change, the more they stay the same. Back in 1988, 8-bit microcontrollers were shipping in huge volumes, clearly dominating the micro scene in terms of units shipped. Today, while the 8-bit micros themselves have changed dramatically, they're still the leader, by a wide margin. And some of those same cores, like the 8051, are still in use.

Throughout 2008, we'll be sprinkling in various items to commemorate our 20-year anniversary. For example, in each issue, we'll reprint one item that appeared 20 years ago. But it's not for nostalgic reasons. It's because that information is as relevant today as it was 20 years ago. While most of the articles we publish are available on Embedded.com, the articles from 20 years ago are not. We didn't start posting articles until 1996.

Richard Nass is editor in chief of **Embedded Systems** Design. You can reach him at rnass@cmp.com.

In addition, we'll be looking for information from our readers. For example, what do you consider the most important achievement in the embedded space in the last 20 years? Who has been the most influential individual? Software vendor? Hardware vendor? Do you have an anecdotal story relating to your job in the embedded industry?

#include

What's the most significant thing that's happened to you at an Embedded Systems Conference (ESC) over the last 20 years? How many ESCs have you attended? Can you recall a career changing moment that occurred at an ESC?

We want to hear from you. Go into the Forums section on Embedded.com and let us hear from you. In addition, you'll be hearing stories from the folks on our team, discussing some of the most memorable "embedded" moments that have occurred over the past 20 years. We'll also be taking a peek into the future, giving you a clue as to what you can expect to see in the embedded space over the next 20 years.

Richard Nass, rnass@cmp.com

# The Newest Embedded Technologies

Network, USB, ZigBee<sup>®</sup>, WLAN, WiFi, RFID, Bluetooth™, GPS, and Embedded Control.

New Products from:

VDIP1 Module www.mouser.c

RCM4000

RabbitCore® Modules

www.mouser.com/

rabbitsemi/a

Senices ductor

MatchPort™ b/g

Embedded Device Server

www.mouser.com/

lantronix/a

LVNLSONIX

The ONLY New Catalog Every 90 Days

Experience Mouser's time-to-market advantage with no minimums and same-day shipping of the newest products from more than 335 leading suppliers.

a tti company

The Newest Products

For Your Newest Designs

(800) 346-6873

# **Don't forget the APIs**

n the article, "Use an MCU's low-power modes in foreground/back-ground systems," (*Miro Samek, October 2007, article ID: 202103425*) the Atmel AVR microprocessor was reviewed and example code for the WinAVR toolchain (GNU) was given.

I was disappointed to see that the author seemed to know nothing about the APIs that are available from AVR-LibC, the C library for the WinAVR (GNU) toolchain. The example code given in the article was inline assembly statements, which are ultimately not needed. The AVR-LibC documentation can be found online at <a href="https://www.nongnu.org/avr-libc/user-manu-al/">www.nongnu.org/avr-libc/user-manu-al/</a>. AVR-LibC provides an Interrupt API and a Sleep API, which provides an excellent example of usage and description <a href="https://www.nongnu.org/avr-libc/user-manual/group\_avr\_sleep.html">www.nongnu.org/avr-libc/user-manual/group\_avr\_sleep.html</a>:

```

#include <avr/interrupt.h>

#include <avr/sleep.h>

...

cli();

if (some_condition) {

sleep_enable();

sei();

sleep_cpu();

sleep_disable();

}

sei();

```

"This sequence ensures an atomic test of some\_condition with interrupts being disabled. If the condition is met, sleep mode will be prepared, and the SLEEP instruction will be scheduled immediately after an SEI instruction. As the instruction right after the SEI is guaranteed to be executed before an interrupt could trigger, it is sure the device will really be put to sleep."\*

An article that just skims the surface of the issue of low-power settings in micros does not do justice to what hardware and software features are truly available to the end-user.

—Eric Weddington Product Manager, Atmel Creator of WinAVR

\*Note: You can read all of Eric Weddington's comments at the end of the Samek article online.

The assumption that changes to the M16C interrupt flag are effective immediately is incorrect. Unless the flag is changed by an RETI instruction the changed status takes effect beginning with the next instruction; in other words, it works the same as the AVR.

This information is contained in the M16C Software Manual. It is important that those writing code for the M16C also read through all the technical notes available on the Renesas website. These contain a lot of extremely important information especially about interrupts and power management.

— Andrew Geard Senior Software Engineer (online comment)

### Quine-McClusky algorithm

The Quine-McClusky is NOT a reasonable algorithm for logic reduction.

Based on this article (*Jack Crenshaw*, "All about Quine-McClusky," article ID: 29111968), I implemented the algorithm and it turns out that the required memory and processing time explode if you use more than four or five variables. So I went back to the drawing board and designed a smarter algorithm that beats the pants off of QM. The new algorithm can easily handle 20+ variables and reduce the

table in a few milliseconds.

While I appreciate the spirit of the article, the Quine-McClusky was nothing but a waste of my time.

—Damon Bohls Software Engineer Austin, TX

Jack Crenshaw responds: The focus of my columns has never been to provide canned software or even canned algorithms. Rather, it's to educate. Even if I'm using a commercial tool, I still feel better if I know what it's doing inside. I feel better yet, knowing I could solve small problems by hand, if necessary. Most readers agree.

The problem of logic minimization is NP-complete, meaning that there's a combinatorial explosion as the number of inputs, N, grows. This is the nature of the problem, and there is no way out of it. Even so, the Quine-McCusky method remains as one of the most effective logic minimization algorithms. According to Wikipedia, "the runtime of the Quine-McCluskey algorithm grows exponentially with the input size. It can be shown that for a function of n variables the upper bound on the number of prime implicants is 3\n/n." You say that Q-M can't handle values of N larg*er than 4–5, but for* N = 6*, the number* of prime implicants is only about 120. Piece of cake, at that level. Have you considered that your implementation might have a problem?

Wikipedia goes on, "Functions with a large number of variables have to be minimized with potentially non-optimal heuristic methods..."

If you have truly devised a method that fully optimizes this problem for N >= 20, your future is assured.

Send your comments to Richard Nass at rnass@cmp.com or via the Embedded.com Forum, www.embedded.com/tigforums.

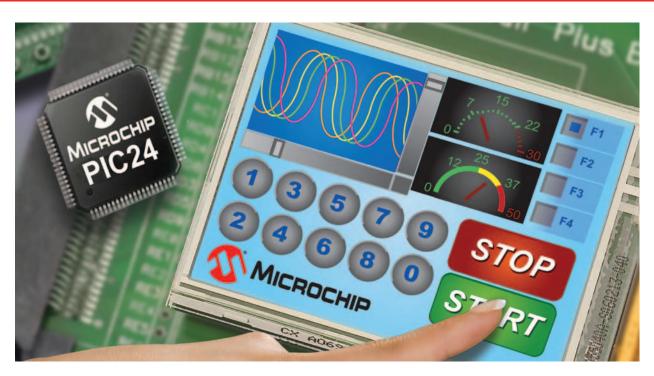

# **Low-Cost QVGA Graphics**

Add a graphical user interface to your product with Microchip's 16-bit MCUs, low-cost development tools and software library.

## Get started at www.microchip.com/graphics:

- View FREE web seminars, video demonstrations, application notes and more...

- Download FREE graphics library for fast and easy graphics implementation

- Buy LOW-COST, FULL-FEATURED development tools, including the Explorer 16 Development Board (DM240001) and the Graphics PICtail™ Plus Daughter Board (AC164127)

### **Graphics Features**

65,000 colors

320x240 (QVGA) Resolution

Line, Circle, Rectangle, Polygon, Button, Window, Check Box, Slider, Progress Bar, Meter, Image, Animation, Touch Screen, Keypad and More...

# Who needs matrices?

ow that we've completed the vector class, it's time to move on to the matrix (plural: matrices). In the worlds of math, engineering, and physics, it's the matrix that separates the men from the boys, the women from the girls, the heroes from the goats. If you can toss around matrices as you might a Frisbee, you're one of the superheroes. If not, you're on the sidelines, watching. Hint: if you say "matricee" as the singular of matrices, you're not even in the stadium.

I want to show you the C++ code that lets you toss around matrix-vector expressions, but at this point, I think it's much more important for me to give you the motivation.

- Why do I need a matrix?

- What good are they?

- How does matrix algebra help me?

If you can toss around matrices as you might a Frisbee, you're one of the superheroes. If not, you're on the sidelines, watching.

in John's hand, one in Mary's.

Maybe that one was too easy. Try this one:

- 1. Between them, John, Mary, and Sue have \$1.00.

- 2. Sue has 40 cents more than John.

- 3. Sue has as much money as John and Mary together.

Not so obvious this time, is it? As you may remember, the trick is to write down equations that capture the information in the problem. To keep it brief, let *J*, *M*, and *S* represent the money each child has. Fact #1 says:

$$J+M+S=100$$

(1)

The next one says:

$$S=J+40 \tag{2}$$

And finally:

$$S=J+M \tag{3}$$

### JOHN, MARY, ET AL.

Remember those word problems that used to drive you crazy in high school algebra? Here's an easy one, for old times' sake:

- 1. Between them, John and Mary have \$1.00

- 2. John has three times as much money as Mary.

- 3. How much money does each child have?

Now, if you've been thinking outside the box, instead of having your eyes glaze over at the phrase "word problem," you already know the answer. Think three quarters

Jack Crenshaw is a senior software engineer at General Dynamics and the author of Math Toolkit for Real-Time Programming, from CMP Books. He holds a PhD in physics from Auburn University. E-mail him at icrens@earthlink.net.

Now we need to solve for the individual values. As you may remember, the trick is to manipulate the equations so that we isolate a single variable, one at a time. For example, Equation 2 gives us a value for *S*. Let's substitute it into the other two equations, to get:

$$J+M+(J+40)=100$$

$J+40=J+M$  (4)

A little simplifying gives:

$$2J+M=60 (5)$$

$$40=M\tag{6}$$

Luckily, the terms in *J* in the last equation cancelled each other, isolating the value of *M*. We now know that Mary has 40 cents. Substituting that value into Equation 5 gives:

### programmer's toolbox

$$2J+40=60$$

$$2J=60-40=20$$

$$J=10$$

(7)

Now that we know the value of *J*, we can solve Equation 2 for *S*:

$$S=10+40$$

$S=50$  (8)

The problem is solved. John has 10 cents, Mary 40, and Sue, 50.

I should probably point out that the sequence of steps I used to solve the problem is not at all the only one, or even the best one.

Way back when, we used to call problems like this one a problem in "simultaneous equations." Simultane-

ous because, of course, the solution values must satisfy all of the given relationships—in this case Equations 1 through 3. As you remember this kind of problem, you will probably also remember that

Give me two equations in three unknowns, and I can't give you an answer.

But give me three, and I can be sure to solve the problem . . .

you must have as many equations as you have unknowns. Give me two equations in three unknowns, and I can't give you an answer. But give me three, and I can be sure to solve the problem (unless one of the equations gives us no new information). If you don't remember anything else about this kind of problem, at least remember this—it's the term "n equations in n unknowns." And, as you can see, the solution comes by trying to isolate the unknowns, one at a time. As you find the value for one of the unknowns, you now have n-1 equations in n-1 unknowns, and you can continue to whittle the problem down to size.

### A LITTLE ORDER, PLEASE

Mathematicians have been solving problems like this for, oh, a few thousand years, give or take. For a long time, they were satisfied to treat each problem as it presented itself, trying operations pretty much at random, until they got the answer. But that approach leaves us very much dependent upon our cleverness in deciding which unknown to eliminate first, and how. A process that depends on the cleverness of the mathematician may help pump up the ego of that mathematician, giving the same satisfaction that he might get from solving, say, a crossword or Sudoku puzzle. But we're not talking about feeding egos and giving satisfaction here. There are real problems to be solved, and we'd rather not depend on heroes to do it.

Over the years, I've learned an important fact about advanced methods of mathematics (it works for engineering and physics, too). It's a lesson that took a long time to

learn, and I'm giving it to you free: the whole point of advanced mathematics is not to feed egos, but to make goats look like heroes.

We often do that by devising systematic approaches that would and can be done the same by everyone. In other words, reduce a process that calls for cleverness to one that involves simply turning a figurative crank. That's the case with the kind of problem we've been studying here.

As a step in that direction, it was decided that we would always write down the equations with only terms involving the unknowns on the left of the equals sign, and known values on the right. In that format, our equations look like this:

$$J+M+S=100$$

(9a)

$$S - J = 40 \tag{9b}$$

$$J+M-S=0 (9c)$$

With the equations in this form, we can solve them very systematically by adding and subtracting the equa-

tions (scaled, if necessary) to/from each other. Adding equal values to both sides of an equation won't unbalance it. Everything will still balance as long as we remember to add both sides of the equations. As I do so for this example, I'm going to retain all three equations so you can see how they change at each step.

According to this turn-the-crank process, we always choose to eliminate the first variable first. For our example problem, let's add Equation 9a to 9b, and subtract it from 9c. The new equations are:

$$J+M+S=100$$

(10a)

$$2S+M=140$$

(10b)

$$-2S = -100$$

(10c)

As you can see, the unknown *J* now appears only in the first equation. Purely by happenstance, we managed to remove *M* from the third equation. But because I'm trying to follow a systematic approach here, I'm going to pretend I didn't notice, and go on. The next step, is to use Equation 10b to isolate *M*. Subtracting this equation from Equation 10a gives:

$$J - S = -40 \tag{11a}$$

$$2S+M=140$$

(11b)

$$-2S = -100$$

(11c)

Now M appears only in the second equation. To complete the job, we must eliminate S from the first two equations. First subtract  $\frac{1}{2}$  of Equation 11c from 11a,

Which path would you choose? Would you stick to the safer-looking,well-traveled route? Or would you choose the more rugged path — the one that may very well take you on an adventure?

What if you could do both? With new high-performance, low-power Intel embedded technology you get all of the familiar goodness of the most widely used processing architecture in the world. And now we've added advanced platform technologies that will help you blaze new trails and explore new ground. Like hardware-enabled virtualization and active management technology that allows for remote control of embedded platforms. All without adding more chips or increasing the complexity of your board designs.

With so much efficiency built right in, it's almost like going down two roads at the same time. And that's an adventure on a whole new level. Are you ready for it?

To learn more go to: http://developer.intel.com/design/info/906.htm

Intel Embedded Technology. Igniting Innovation

### programmer's toolbox

and add it to 11b. We get:

$$J - S + S = 50 - 40$$

(12a)

$$M=140-100$$

(12b)

$$-2S = -100$$

(12c)

or simply:

$$J=10$$

$M=40$

$S=50$

(13)

which agrees with our previous, more ad hoc solution.

You may have noticed that the more systematic solution can take more operations than we might take if we

were more clever. The price of making goats look like heroes is that the process may sometimes take a little longer. It's a price we tend to gladly pay, to keep us from falling short of hero status.

simple restatement, however disguised, of the other

In our example, I had three equations—statements of fact—involving the three unknowns *J*, *M*, and *S*. It should go without saying that a simular problem involving 37 equations in 37 unknowns will take longer to solve, but is no different, in principle. If we apply the same turn-the-crank approach (and if—a big if—we don't make a silly math error), we'll eventually get the answer. As my old major professor used to say, "Conceptually, there's no problem."

Before we leave this example, I want to show you how the problem of simultaneous linear equations morphs into a matrix equation. To begin, we first agree to write down all the possible terms in each equation,

> with explicit coefficients, including 1 and 0. If a given unknown doesn't appear in the equation, we put it in anyway, with a coefficient of

Over time I've observed that if we're able to attach a name to a problem, we're a long ways along toward solving it.

### LINEAR ALGEBRA

Over time I've observed that if we're able to attach a name to a problem, we're a long ways along toward solving it. If a doctor can say "you've got a virus" as opposed to, say, "you've got a hangnail," he knows which remedies are likely to work and which ones won't. A lawyer who says, "This is a case of personal liability" rather than a case of murder, can eliminate a lot of the books in his library, in search of a precedent.

It's the same way with math problems. The equations of the kind we've been looking at are of a special kind. Not only are they simultaneous equations, but they're simultaneous *linear* equations—linear because each of the unknowns appears only to the power one. There are no  $J^2$  terms or  $\sqrt{J}$  terms. The science of solving problems involving multiple linear equations in multiple unknowns is called linear algebra. Once we have recognized the word problem as one of linear algebra, we're very much farther than halfway to a solution.

Remember this: you always need as many equations as you have unknowns. If you have, say, three equations but four unknowns, the problem is under-specified. You can't solve the problem entirely. It's not that there is no solution to the problem, but rather that there's an infinity of them. The most you can hope for is to be able to express three of the unknowns in terms of the fourth one.

If, on the other hand, you have four equations in three unknowns, the problem is over-specified. In general, no solutions will satisfy all four equations. The exception is if one of the equations is in fact superfluous—a

zero. We also keep the unknowns in the same order throughout.

Following this rule, Equations 9a through 9c look like this:

$$1J+1M+1S=100

-1J+0M+1S=40

1J+1M-1S=0$$

(14)

Looking at this form, we begin to get the idea that the names of the unknowns doesn't matter. If we had called them x, y, and z, it wouldn't have changed the solution. In fact, the essence of the problem is in the array of coefficients themselves. If I give you that array, you are way far along in finding the solution. In our case, that array is:

$$\mathbf{A} = \begin{bmatrix} 1 & 1 & 1 \\ -1 & 0 & 1 \\ 1 & 1 & -1 \end{bmatrix} \tag{15}$$

At this point, I'm going to assert that this array is, in fact, a matrix. By convention matrices are denoted by uppercase, boldfaced characters, while vectors are lowercase and boldfaced. Without knowing anything about matrix-vector math, let's define the two vectors:

$$\mathbf{x} = \begin{bmatrix} J \\ M \\ S \end{bmatrix}; \ \mathbf{u} = \begin{bmatrix} 100 \\ 40 \\ 0 \end{bmatrix} \tag{16}$$

### programmer's toolbox

Then I can write the problem in the incredibly compact form:

$$\mathbf{A}\mathbf{x} = \mathbf{u} \tag{17}$$

There is no such thing as a division operator for matrices, but there is the next best thing: an inverse operator. So, conceptually, I can write:

$$\mathbf{x} = \mathbf{A}^{-1}\mathbf{u} \tag{18}$$

How does one compute the inverse of a matrix?

We've already done

it. The steps we took

in Equations 9

through 13 are nothing less than the

Gaussian elimination leading to the

inverse. This one

Many other pro

using matrix alge

the same pr

Many other problems look a lot easier using matrix algebra, and many others are the same problem, in disguise.

time, we did it the hard way, only one step removed from the high school way. If you never liked those word problems that ended up as simultaneous linear equations, rejoice: this is the last time you'll ever have to do it. Armed with a matrix inverse operator—all the commercial math aids have them, as will our C++ library—you can go from Equation 17 to 18 in a single step.

Hooray!

As a teaser, I'll just toss out there that, while the matrix division operator doesn't exist, I've appropriated the division operator in the C++ class. Thus, turning

Equation 18 into C++ code is as simple as writing:

$$x = u/A;$$

An important point may have slipped past you. As we solved the example problem, it was not at all obvious that the input or constraint vector, **u**, is practically immaterial to the solution. The matrix **A** is purely a matrix of the coefficients of the elements of **x**—in our case, *J*, *M*, and *S*. Therefore we can invert the matrix as a standalone entity, completely independently of **u**. In my statement of the problem, I could have substituted any con-

stant values whatever for the elements of **u**. While the resulting values for **x** would absolutely be different, the inverse of the matrix itself would be exactly the same. This

fact gives us a lot of leverage if we're looking at different values of **u** at different times. No matter how many such values there are, we only need to invert **A** once.

### OTHER MATRIX APPLICATIONS

Solving word problems is certainly not at all the only problems we can cast into matrix form. Many other problems look a lot easier using matrix algebra, and many others are the same problem, in disguise. A familiar one is linear regression, which in turn is a subset of polynomial regression, which is itself a subset of optimal

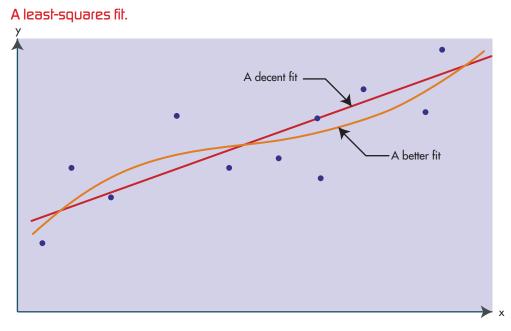

Figure 1

curve fitting. In Figure 1, I've shown a set of data points with a lot of scatter, which we probably got from a sensor beset with lots of noise. Our challenge is to fit a curve through the data.

Suppose I try to draw a straight line through the data. Clearly, it's not going to pass through all the points; chances are, it won't pass through any of them. The equation for a straight line is:

$$y(x) = ax + b \tag{19}$$

where a and b are coefficients to be determined. I can choose lots of different straight lines and *claim* that they're the best fit to the data, but which one is really best?

This is the problem of the leastsquares fit. For any of the points, we compare the value of y give by Equation 19, with the measured value. For want of a better criterion, I'm going to claim that the best fit is one that minimizes the sum of the squares of the errors. That's the least-squares fit.

I'm going to be covering this problem in detail in a later column. For now, I only want to say that we can write down the equations for the sum of the squares of the errors. Call it M for historical reasons. To minimize this sum, we end up taking the partial derivatives of M with respect to *a* and *b*. The optimal fit occurs when both partials vanish.

For a linear equation, the results are going to look like:

$$pa+qb=r$$

$$sa+tb=v$$

(20)

where the constants p, q, etc., depend only on the measurement values, not a or b. Does this look familiar? Yes, indeed, it's our old friend, the simultaneous linear equation. Using the

same techniques, we can easily solve for the coefficients of y(x).

When we get into the leastsquares problem, you'll see that the size of the array is completely independent of the number of data

When we get into the

least-squares

problem, . . . the size of the array

is completely

independent of the number of data points. points. We need at least two to fit a straight line through them, but two or 200,000, it makes no difference.

The matrix will be different, but

we're still only solving for two un-

What's more, if we like, we can assume a higher-order polyomial. The curve in Figure 1 looks like it might be a cubic, so will have four coefficients. The number of coefficients makes little difference. The only difference between them is the size (order) of the matrix. And even when we have many, many data points, the order is modest.

### THINGS TO COME

Simultaneous linear equations and the least-square fit. Seemingly unrelated problems, but they both fall before the might of the matrix inverse. But these two disciplines are not by any means the limit to the value of matrix algebra. Other areas include:

- Coordinate transformations.

- Rotational dynamics.

- Multivariate control theory.

- Optimal control theory, including the Kalman filter.

As we go through the steps to define a matrix class, I'll be showing you, as I did for the vector class, practical applications. I think you'll enjoy the trip.

To NAND or NOR. That is the question. Different applications and functions should be handled with different types of flash memory.

# Employ

BY VIJAY K. DEVADIGA

n their search for the perfect "universal memory," designers of embedded systems are like characters from the play Waiting for Godot. They're waiting for an off-stage character, "Godot," to come on stage, meanwhile speculating which of the current or new characters appearing on stage are Godot.

From it's inception in the 1970s, the embedded systems industry as we know it as always been waiting for an off-stage semiconductor-based character named "universal memory" to come along and replace the memory hierarchy inherited from mainframes, minicomputers, and desktop computers: nonvolatile hard disk drives for long term mass storage and backup, dynamic RAM for local fast memory access, and SRAM and ROM for extremely fast access and code storage.

This desire has been heightened and intensified as computing as become more embedded, mobile, and portable and candidates for the role of "universal memory" have come on stage. Some—such as EEPROMS, EPROMS, UV-EPROMS, ferroelectric RAMS, and various pseudo-RAM combinations—have been turned down. Others such as magnetic RAM are being considered, but are in doubt for a number of economic and technical reasons.

However, some of the current characters on the stage—particularly the various flavors of NAND and NOR flash EPROMs—are being touted by their vendors as that offstage character "universal memory," or at least a relative and "close personal friend" including OneNAND, OrNAND, iNAND, GBNAND, moviNAND, ManagedNAND and NANDrive. Giving the diversity of actors trying out for the role, choos-

### FANLESS PLATFORM

x86 Compatible Energy-Efficient Custom Integration

# EFFICIENT MAINBOARDS

Small Form Factor Intel, VIA & AMD CPUs Extensive I/O Options

# SOLID STATE ENDURANCE

Wear Leveling Industrial-Grade 2.5" ATA/SATA Flash

### LEADERS IN MINI-ITX

ing the right memory subsystem is much more complicated now, especially if you're adding more multimedia functions to mobile and embedded systems while shrinking physical size and reducing overall system cost. Not only could the code and data storage needs have increased in these systems, but you've got to do it all more reliably with less of everything.

Flash memory is the most practical solution, but knowing which type of flash fits best in a system is the key. Is NAND, NOR, managed NAND, or some hybrid the best choice?

The use of NAND flash, an inexpensive and high-density nonvolatile memory requiring defect management, to satisfy these growing code and data storage needs makes the memory subsystem even more complex. Add to that the need to support different memory types, interfaces, vendors, and vendor-specific features, and the memory subsystem even more complex.

A completely managed memory subsystem solution can be designed that uses an industry-standard RAM (PSRAM or SDR/DDR SDRAM) interface. This managed memory subsystem would provide seamless integration with the host chipset/processor and eliminate

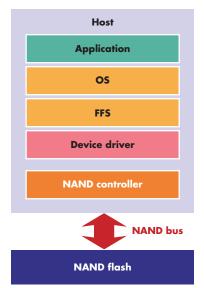

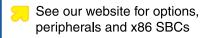

# This system has a host chip set that interfaces with standalone NAND flash.

Figure 1

the need for the host system to manage the complexity and deficiency of built-in memory devices.

Unlike NAND flash, NOR flash is one of the oldest and the most widely used memory types in current embedded systems. It's used for both code and data storage. Its main advantage is that the code is executed directly (execute-inplace) from the NOR flash memory. Also, NOR flash can directly interface with the host processor, which enables easy designin and fast time-to-market.

With the increased deployment of multimedia functions in embedded systems, the need for code and data storage is also increasing. For these applications, using higher density NOR flash for code and data storage becomes more expensive when compared with alternative solutions like NAND flash. In addition, the highest density NOR flash available today is 1 Gbit. Moreover, multimedia data storage requires both high read and write performance. As a result, system designers have turned to NAND flash for storing multimedia files as well as application code in many embedded applications, including high-end cell phones.

### NAND FOR CODE & DATA STORAGE

NAND flash is well suited for applications that require large code storage (such as operating system and applications) and large data storage because NAND flash is inexpensive and is also available in high densities (up to 16 Gbits in one die). Unlike NOR, NAND flash doesn't support execute in place (XIP) or random access. As a result, some systems that use NAND flash need a low-density NOR flash just for system boot-up and BIOS code execution. In other systems, a NAND flash controller, or an embedded boot ROM in the host processor, can provide the boot function. After system boot-up, the NAND-based systems use either code shadowing or demand paging for code execution. In the case of code shadowing, the entire operating system and applications are copied from the NAND flash into the system RAM, and in demand paging, a portion of the operating system and applications are

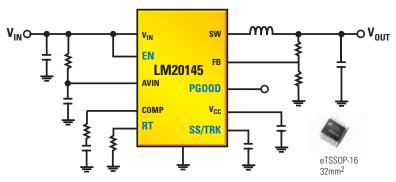

# Family of High-Efficiency, Full-Featured PowerWise® Synchronous Buck Regulators

national.com/switcher

### **Integrated Features for Optimized Power Supply Designs**

### **LM20xxx Family Features**

- · External soft-start

- Tracking

- Precision enable

- Power good

- Pre-biased start-up

- · Enhanced system reliability

- High accuracy current limit

- Over-voltage protection, under voltage lockout, and over-current protection

- Available in eTSSOP-16 packaging

### **Feature Options**

- Fixed and adjustable switching frequency

- Clock synchronization in

- · Clock synchronization out

Ideal for powering FPGAs, DSPs, and microprocessors in servers, networking equipment, optical networks, and industrial power supplies

### **Highest Power Density 5A Regulators**

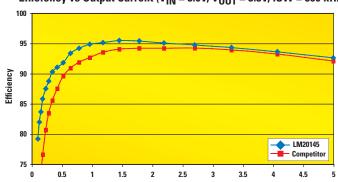

Efficiency vs Output Current ( $V_{IN} = 5.0V$ ,  $V_{OUT} = 3.3V$ , fSW = 500 kHz)

| Product Number | V <sub>IN</sub> (V) | I <sub>OUT</sub> | SYNC IN | Frequency Adjust | SYNC OUT | Frequency         |

|----------------|---------------------|------------------|---------|------------------|----------|-------------------|

| LM20123        | 2.95 to 5.5         | 3                |         |                  |          | 1.5 MHz           |

| LM20133        | 2.95 to 5.5         | 3                | ~       |                  |          | Sync              |

| LM20143        | 2.95 to 5.5         | 3                |         | <b>✓</b>         |          | 500 kHz - 1.5 MHz |

| LM20124        | 2.95 to 5.5         | 4                |         |                  |          | 1 MHz             |

| LM20134        | 2.95 to 5.5         | 4                | ~       |                  |          | Sync              |

| LM20144        | 2.95 to 5.5         | 4                |         | <b>✓</b>         |          | 500 kHz - 1.5 MHz |

| LM20154        | 2.95 to 5.5         | 4                |         |                  | <b>v</b> | 1 MHz             |

| LM20125        | 2.95 to 5.5         | 5                |         |                  |          | 500 kHz           |

| LM20145        | 2.95 to 5.5         | 5                |         | <b>✓</b>         |          | 250 kHz - 750 kHz |

| LM20242        | 4.5 to 36           | 2                |         | <b>✓</b>         |          | 250 kHz - 750 kHz |

For FREE samples, datasheets and more, visit:

national.com/switcher

Or call: 1-800-272-9959

### cover feature

copied into the system RAM as needed, where such code is then executed.

Though NAND flash is inexpensive and available in higher densities than NOR, NAND is less reliable and requires defect management, including error detection and correction, and wear-leveling to make it usable for many applications. These NAND flash management functions require complicated hardware and software. Figure 1 shows a system where the host chip set interfaces with standalone NAND flash. In this system, the defect management functions must be performed by the host chip set. Running such flash management functions on the host requires some software development and it also uses some of the host's CPU and memory resources, leading to a reduction in overall system performance.

As NAND flash vendors are moving to smaller process geometries, the ECC (error correction code) requirement for single-level cell (SLC) NAND flash has increased from 1 to 4 bits per 512-byte

sector, and for multi-level cell (MLC) NAND flash, it's increased from 4 to 8 bits per 512-byte sector. The page size has increased from 512 to 4,096 bytes. The endurance for some of the smaller geometry SLC NAND flash has changed from 100,000 to 50,000 cycles, and for MLC NAND flash it has changed from 10,000 to 5,000 cycles (and 3,000 cycles in some cases). To reduce the number of discrete components in the system, many chip set vendors have started integrating a NAND flash controller in their chip set, which can directly interface with standalone NAND flash. However, because of the long design cycle of a chip set, it's difficult for the chip set vendors to track the ever changing NAND flash technologies. Therefore, the functionality of an embedded NAND flash controller in the chip set will always lag the NAND flash technologies.

A few solutions are similar to standard NAND flash, but offer improved performance and functionality. For ex-

ample, OneNAND is a variation of NAND flash that combines RAM and standalone SLC NAND flash in one device to provide boot function and faster read access. OneNAND requires 1-bit ECC for each 512-byte sector and requires NAND flash management functions implemented either in the host chip set or in a separate standalone controller.

On the other hand, OrNAND combines MirrorBit NOR with a NAND flash interface, which offers faster write time than its predecessor NOR devices. OrNAND also requires 1-bit ECC implemented either in the host chip set or in a separate standalone controller to ensure reliable system boot-up. Moreover, the maximum density currently supported by OrNAND is only 1 Gbit, which is less than the maximum density of currently available NAND flash.

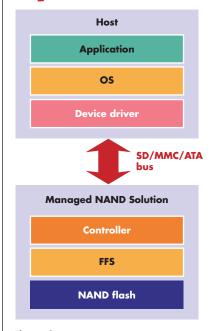

### MANAGED NAND FOR DATA

Due to the limitations of the embedded NAND controllers, many system design-

Managed NAND memory, used mainly for data storage, reduce system complexity by managing the built-in NAND flash with a NAND controller and flash file system integrated into the same device.

Figure 2

### cover feature

ers are looking at managed NAND solutions. Several vendors have come up with managed NAND memory products that alleviate the complexities of a conventional memory subsystem in embedded applications. These managed NAND memory products, including iNAND, GBNAND, moviNAND, Managed NAND, and NANDrive, are used mainly for data storage. They reduce system complexity by effectively managing the built-in NAND flash with a NAND controller and flash file system (FFS) integrated into the same device as shown in Figure 2. These products use a standard interface such as Secure Digital (SD), MultiMediaCard (MMC), or Advanced Technology Attachment (ATA) for easier integration. For example, iNAND and GBNAND offer the SD interface, moviNAND and Managed NAND offer the MMC interface, and NANDrive offers the ATA interface. These products don't offer XIP access and as a result, systems that use them may need a NOR flash for the boot function.

Using a managed NAND device eliminates the need for a complex NAND management function on the host. As a result, the chip-set vendors needn't worry about keeping up with the evolving NAND technologies, thus enabling vendors to focus more on their core competencies.

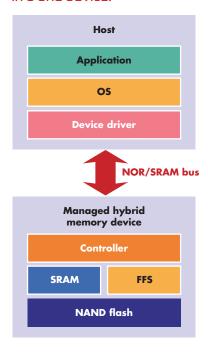

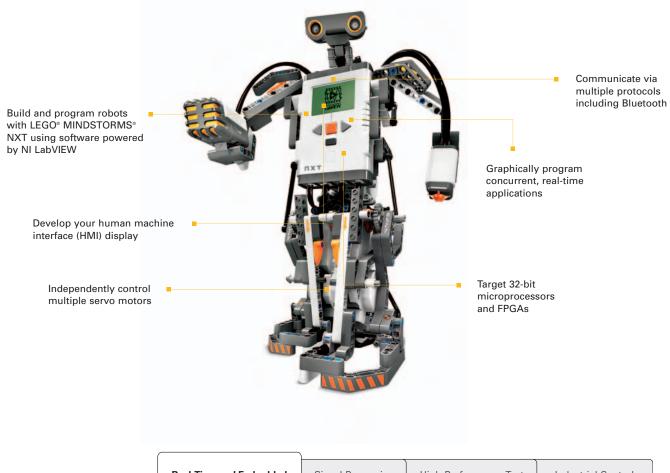

### MANAGED NAND HYBRID BOOTS

Because managed NAND flash doesn't provide boot capability, system designers still must use a higher cost NOR flash device for boot-up. However, hybrid products, including mDOC H3, are now available. These hybrids use RAM and managed NAND in a one device, as depicted in Figure 3, to simplify the conventional memory subsystem.

Hybrid products solve the boot issue associated with the managed NAND. They can boot directly from the NAND flash, eliminating the need for a higher cost boot NOR flash device, which may reduce the overall system cost. Managed NAND hybrids also help to reduce component count and save board space, which makes them suitable for space-sensitive applications like cell phones.

These solutions are available in higher densities because they use NAND flash for nonvolatile storage.

On the down side, NAND hybrids have a longer boot time because they must copy the boot code from the NAND into the boot RAM after poweron. Also, NAND hybrids are complex, difficult to integrate, and require an advanced operating system that supports demand paging on the host.

mDOC H3 uses a NOR-type bus to interface with the host processor and offers faster read performance than NAND flash and faster write performance than NOR. Due to the faster write performance, these devices are suited for storing multimedia.

Using a managed NAND or even a managed NAND hybrid with boot capability doesn't drastically reduce the memory subsystem's overall complexity. The system designers must still manage the complexity associated with different memory types, interfaces, vendors, vendor-specific features, and so forth. These types of memory subsystems require many components, more pins, and complex hardware and software development, resulting in increased system cost, board space, development time, and power consumption. At the same time, they increase the complexity of the external memory controller in the host processor. Therefore, these hybrids are less than complete. Today's systems need an easy-to-use, single-standard bus, completely managed memory subsystem for code and data storage and system RAM, all in one device.

What system designers need is a complete memory subsystem that offers hundreds of megabytes of XIP code storage and also satisfies the growing datastorage needs of today's multimedia applications. The solution should blend the key benefits of NOR (fast read), NAND (lower cost and higher density), and RAM (simple bus operation). This solution also must be easy to use, easy to design in, and completely managed. Thus, it requires minimal or no additional hardware or software development, offers a standard interface for seamless integration with the host chip set/proces-

sor without any glue logic, and makes memory subsystem access as simple and easy as an SRAM.

The built-in controller in this memory subsystem solution must implement ECC, bad block management, and wear-leveling to manage the defects in the built-in NAND flash. The controller must also manage the complexity and deficiency of all the built-in memories (NOR, NAND, and RAM) to off-load the host system from handling these complicated management functions.

Furthermore, this solution must address the total system cost by reducing the material, development, and manufacturing costs. In addition, it must address the time-to-market needs of system designers working on mobile and consumer electronic devices by offering a solution that's easy to integrate and is scaleable for future products.

### **NEXT GENERATION SUBSYSTEM**

Managed memory subsystem products are available today that offer all the features and benefits mentioned. For example, one such configuration shown in

# Some hybrid solutions use RAM and managed NAND in a one device.

Figure 3

- New unbrickable design- 3x faster

- Backward compatible w/ TS-72xx

- Low power 4W at 5V

- 128MB DDR RAM

- 512MB high-speed onboard Flash

- 12K LUT user-programmable FPGA

- Internal PCI Bus, PC/104 connector

- **2 USB 2.0 480 Mbps**

- Gigabit ethernet 2 SD sockets

- 10 serial ports

110 GPIO

- 5 10-bit ADC 2 SATA ports

- Sleep mode uses 200 microamps

- Boots Linux in < 2 seconds

- Linux 2.6 and Debian by default

Design your solution with one of our engineers

- Over 20 years in business

- Never discontinued a product

- Engineers on Tech Support

- Open Source Vision

- Custom configurations and designs w/ excellent pricing and turn-around time

- Most products stocked and available for next day shipping

We use our stuff.

visit our TS-7200 powered website at www.embeddedARM.com (480) 837-5200 All-in-OneMemory is an example of a managed memory subsystem. It consists of a memory controller with built-in boot NOR flash, NAND flash, and RAM, in one package (a). The controller handles on-demand paging and other memory management functions (b).

Figure 4

Figure 4 consists of a memory controller with built-in boot NOR flash, NAND flash and RAM, all in one package. Using the RAM cache in front of the NAND flash, the controller handles on-demand paging and other memory management functions. In addition, the RAM cache renders the memory subsystem addressable linearly, and as simple as an SRAM.

The RAM block is divided into two host-accessible, user-configured partitions: a cache partition for Pseudo-NOR (PNOR) and a system RAM partition for the host. The NAND block is used as nonvolatile storage for the PNOR area and the memory-mapped ATA NAND disk area. The configurable PNOR block emulates the NOR function by using RAM cache and NAND flash. Because NAND is used as the main nonvolatile storage media, this solution provides large XIP code storage that can effectively replace the traditional higher cost, high-density NOR flash. By using the industry standard ATA data-storage protocol on the standard RAM (PSRAM or SDR/DDR SDRAM) bus, this solution provides large ATA-like data storage for

the growing multimedia applications. In addition, the RAM cache in the PNOR block also helps to extend the endurance and reliability of the code and data storage area by minimizing direct read/write access to the NAND flash.

Because it's offered in a small-foot-print package, this managed memory subsystem may simplify the host interface, reduce system complexity, shorten design time, reduce overall system cost, and improve quality and reliability. Other benefits include the user-configurable XIP PNOR area; robust hardware error detection and correction for MLC and SLC NAND; and scalability to higher densities. With no complicated software and hardware development required, this type of managed memory subsystem could be the Godot we're all waiting for.

Vijay Devadiga is currently a senior staff product marketing engineer at Silicon Storage Technology Inc. in the NAND and Smartcard Module Business. In this role, he is responsible for product marketing of the company's All-in-OneMemory product line. He can be reached at vdevadiga@sst.com.

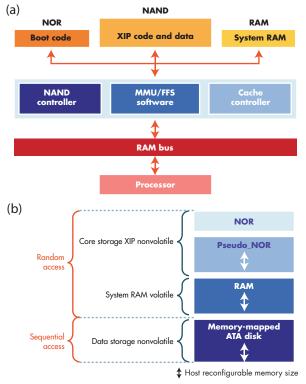

# **NI LabVIEW.**Limited Only by Your Imagination.

Real-Time and Embedded

Signal Processing

High-Performance Test

Industrial Control

### PRODUCT PLATFORM

LabVIEW Real-Time Module

LabVIEW FPGA Module

LabVIEW Microprocessor SDK

NI CompactRIO Embedded Hardware Platform When the LEGO Group needed parallel programming and motor control tools intuitive enough for children, it selected graphical software powered by NI LabVIEW. With LabVIEW graphical system design, domain experts can quickly develop complex, embedded real-time systems with FPGAs, DSPs, and microprocessors.

>> Expand your imagination with technical resources at ni.com/imagine

866 337 5041

feature

Combining a programmable solution with an industry-standard processor core can save time, money, and real estate.

# Lower the COS of intelligent power control with

BY WENDY LOCKHART

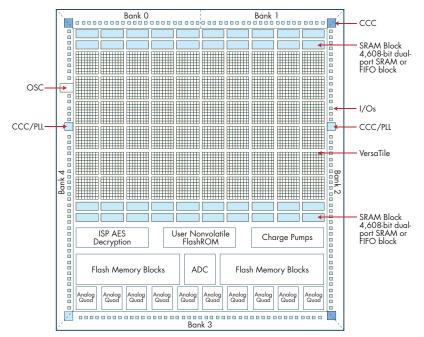

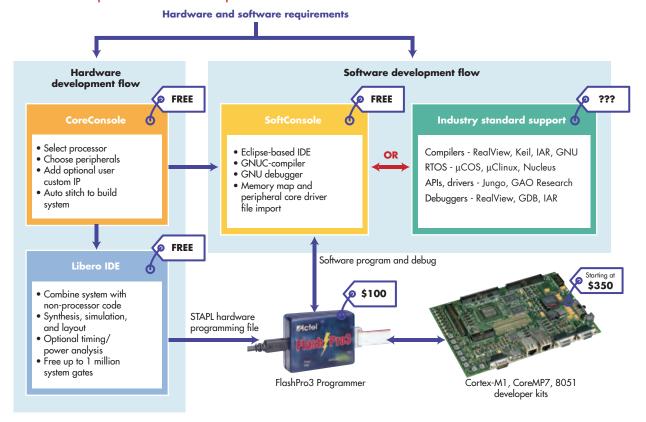

he availability of ARM's Cortex-M1 32-bit processor and single-chip, mixed-signal FPGAs make possible the development of intelligent power control that could dramatically reduce part count, board space, and system cost while increasing reliability, flexibility, and system availability. Methods exist for rapid prototyping and implementation of the hardware and software for server-based intelligent power; these methods can also be applied to a range of energy-management applications. System considerations include development resources; tools available for development with Cortex-M1 and mixed-signal programmable system chips (PSCs); and availability of power control boards. Lowering the cost of intelligent power control requires an understanding of FPGA implementation strategies, as well as a basic understanding of designing with ARM's Cortex-M1 microprocessor and FPGA implementation tools.

As the number of functions in a system grows, power to the system is no longer an afterthought. With time-to-market pressures and the need to support more features, designers must select peripherals from a standard set of components to meet their power and cost budgets. As a result, this may mean mixing an LCD with a 2.5-V supply and a keypad with a 1.8-V supply. With many devices, the core and I/O voltage within the device will also vary. So, within a single product, the power supply may need to generate multiple voltages and possibly different sequences of the same voltage.

In portable applications, the restrictions can be even greater, requiring power management to extend battery life. Designs can therefore become quite complex, featuring multiple supplies, controlled ramp rates, power sequencing, and complex supply manage-

### feature

ment where supplies are turned on and off as needed.

Intelligent power control has existed in some high-end systems as a custom implementation or more recently with standards, such as ATCA and Mi-

croTCA. With the market now demanding smaller, portable versions of many applications, the power control must be scaled down as well, creating a need for intelligent power control that's low cost, small form factor, and low power.

Intelligent power control involves the following basic aspects:

- Generating all the required system voltages.

- Sequencing each device's power up and down to maintain system integrity and prevent issues such as latch-up, inrush current, or I/O contention.

- Supporting the ability to switch off certain devices when not needed and power them back up for

seamless operation.

-----

Maintaining minimum functionality in standby, with the ability to wake at certain intervals or ondemand.

If the PSC can perform wake up from a watchdog timer or external trigger, the entire system can be shut down except for one device.

Implementing these functions in an application-specific standard product (ASSP) would require a standard power profile. The use of a programmable device, however, allows for adaptation to multiple system requirements. Programmable devices also allow for future system upgrades and fine tuning. A number of programmable power modules are available, but they still need to be combined with some form of brain to tell them when to turn each supply on and off.

As shown in Figure 1, mixed-signal

PSCs allow for the combination of programmable power generation with realtime analysis and control. Combining functions for power sequencing, monitoring, and control in a single chip results in significant cost savings in terms

of materials list, board space, and build costs. In addition, a single device consumes less power and can manage the power supplies for the rest of the system. And, if the PSC can

perform wake up from a watchdog timer or external trigger, the entire system can be shut down except for one device. Some PSCs can also manage smart battery charging, which is another intelligent way to enhance power control in the system.

Early adoption of PSCs in intelligent power control applications has been facilitated by the use of reference designs, some in the area of ATCA and others in the associated intellectual property (IP), such as Intelligent Platform Management Interface (IPMI).

### Example of a mixed-signal PSC architecture.

Figure 1

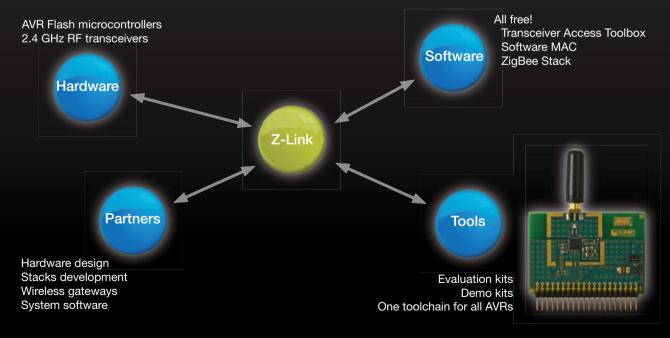

# Go wireless with AVR Z-Link

### The Z-Link Solution

Atmel®'s AVR Z-Link product line provides the best IEEE 802.15.4 compliant and ZigBee™ certified solution available. Based on the AVR RF family of radio transceivers, AVR microcontrollers, free software, reference designs and development kits, the solution enables deployment of large wireless networks with very low energy consumption.

RF radio transceivers provide the widest link budget available with -101 dBm receive sensitivity and 3 dBm transmit power. Combined with picoPower™ technology used by the AVR microcontrollers, the chipset achieves very low power consumption.

The AVR family of 8-bit RISC microcontrollers which features up to 256 KB Flash memory and rich peripherals, can easily handle both wireless communication and your main application.

This platform-based approach lets designers start from a known system and customize it, or use a fixed standard and work it into their system. Some system

management development kits also provide examples for a more custom approach to power control. This still requires a clear understanding of the PSC as well as a custom development environment.

Because the PSC's core includes standard flash-based FPGA gates, the Cortex-M1 core can be used as part of the design. This provides significant benefits to an existing ARM designer who must integrate intelligent power control without having to learn a full suite of analog tools. Cortex-M1 is ful-

ly backwards compatible with ARM's Thumb architecture, so designers can port existing application code to the PSC.

when the design tools are created by a silicon supplier, the motivation is to help the designer get to silicon as fast as possible.

Although implementing a Cortex-M1 design on a PSC might be a new challenge to some engineers, certain tools and techniques can make this a relatively painless design cycle.

> Although implementing a Cortex-M1 design on a PSC might be a new challenge to some engineers, certain tools and techniques can make this a relatively painless design cycle. Often the easy approach from a time-to-market point of view is the expensive approach from a cost point of view. But

### **IMPLEMENTING** INTELLIGENT POWER CONTROL

Standard FPGA design can take several different forms

- Full HDL code or schematic starting from scratch.

- Combination of existing versions of design plus some new code and features.

- Combination of purchased or custom IP, existing design, and new code.

### FPGA development flow with soft processor.

Figure 2

# Microcontroller Development Tools

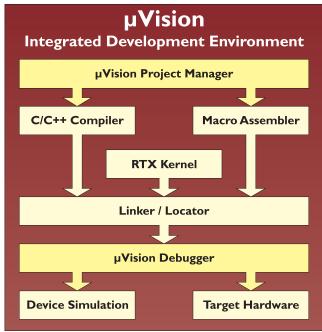

# Only 4 Steps...

...are required to generate efficient, reliable applications with the  $\mu Vision\ IDE$  and development tools from Keil.

# **Step 1.** Select Microcontroller and Specify Target Hardware

Use the Keil Device Database (<u>www.keil.com/dd</u>) to find the optimum microcontroller for your application.

In  $\mu Vision,$  select the microcontroller to pre-configure tools and obtain CPU startup code.

# **Step 2.** Configure the Device and Create Application Code

The µVision Configuration Wizard helps you tailor startup code to match your target hardware and application requirements.

Extensive program examples and project templates help you jump-start your designs.

# **Step 3.** Verify Program Execution with Device Simulation

High-speed simulation enables testing before hardware is available and helps you with features like instruction trace, code coverage, and logic analysis.

# **Step 4.** Download to Flash and Test Application

Once your application runs in simulation, use the Keil ULINK USB-JTAG Adapter for Flash programming and final application testing.

### **Keil Microcontroller Development Tools**

help you create embedded applications quickly and accurately. Keil tools are easy to learn and use, yet powerful enough for the most demanding microcontroller projects.

Components of Keil Microcontroller Development Kits

Keil makes C compilers, macro assemblers, real-time kernels, debuggers, simulators, evaluation boards, and emulators.

Over 1,200 MCU devices are supported for:

- 8-bit 8051 and extended 8051 variants

- 16-bit C166, XC166, and ST10

- 32-bit ARM7, ARM9, and Cortex-M3

Download an evaluation version from www.keil.com/demo

### feature

The same styles apply to both mixed-signal FPGAs and soft ARM processors on FPGAs.

The hardware and software implementation steps are shown in Figure 2. To simplify terms, the hardware implementation involves designing the processor and programming it to the FPGA. The software implementation involves developing code for the processor on the FPGA to complete the application.

First, the designer identifies available industry-standard processors (8051 or ARM, for example) for the design and then looks through offerings from each supplier to find the best list of peripherals for the design. If the perfect list of peripherals can't be found, then a CPLD or companion FPGA can be added to the board. When implementing a soft processor on an FPGA, the supplier should provide a list of available peripherals.

Ideally, the user selects the processor from a list. Then, the bus type, which is often dictated by the processor, is chosen. Once the bus is selected, the user simply drags and drops peripherals into the design. Peripherals may include interfaces such as serial peripheral interface, universal serial bus, timers, or UARTs. Unlike an ASSP processor, users can add any combination of peripherals until they run out of peripheral ports. The tool should provide the ability to auto-connect peripherals where possible and allow users to configure all other parameters and connections through a simple GUI.

Having designed the processor, users then generate and export to the FPGA layout tool. The processor may only be part of the FPGA design. The design may include additional glue logic or interfaces that aren't controlled by the processor. Using a simple block design tool, users can drop in the processor and any additional blocks to create a single top-level design for synthesis.

The design then follows a standard FPGA flow: synthesis, place and route, timing analysis, and so forth. Ideally, the Cortex-M1 processor should be delivered with a custom layout from the silicon vendor, indicating that timing analysis and optimization have been done. This ensures maximum performance in a minimum footprint. The layout should be customized to the device you plan to use. From here, the custom processor can be programmed to the PSC.

What you really want is to convince yourself that both the technology and your design have the ability and functional accuracy to eliminate the need to build custom prototypes—or at least skip the first round of prototyping.

### **BOARD OPTIONS**

------

The choice of development environment is important. Buying a "demo kit" usually means you can get the design or board to do what the supplier intended. What you really want is to convince yourself that both the technology and your design have the ability and functional accuracy to eliminate the need to build custom prototypes—or at least skip the first round of prototyping. Look for a board that has the interfaces built-in. and has enough I/O available with connectors to work with your regular platform or peripheral board. In addition, key components, such as crystals that can switch out, increase the board's usability as a true prototyping environment. You should also be able to program and debug on the development platform.

Software implementation is similar to a standalone processor. The tool that builds the processor should export the appropriate files required by the compiler to create the application. Existing functions can be exported and enable the ability to work from a library of functions to control the pe-

ripherals. Custom code can then be added on top of this. For many processors, including Cortex-M1, the GNU environment offers free tools including compilers and debuggers. However, extra money does get you more mileage. Generally, the more expensive compilers will provide either better performance or less code space. Still, free compilers will get you a functionally accurate design and a long way through prototyping. If you're working with a lot of library

functions, the functions should already be optimized, eliminating the need for expensive compilers.

Debug is the next phase of design. With a soft processor, the ability to debug both the hardware and software is important. Again, a preoptimized

version of the processor helps, as processor debug won't be necessary. Some tools are designed to coexist, such as ModelSim, which runs the hardware, and GNU, which runs the processor application. It's best to get these tools from your silicon supplier, because the PSC is unique and other debug tools won't be set up to handle the architecture. Also, with a standard ARM processor, existing ARM debug tools support debug of the processor application, but not any additional FPGA logic.

All of the methods and strategies described apply to intelligent power control, whether the application is a simple handheld portable device or for a multiserver rack system. The desire to conserve energy and cost will continue to drive electronics in this direction, while also driving designers to meet these challenges for years to come.

Wendy Lockhart is a principal engineer at Actel. She holds a master's degree in electronics from the University of Edinburgh, Scotland. Lockhart can be reached at wendy.lockhart@actel.com.

EMBEDD Unlock your future

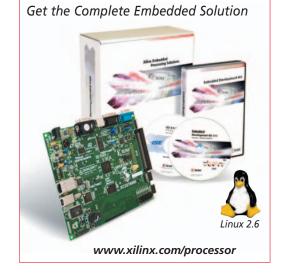

### Enter the New Era of Configurable Embedded Processing

Adapt to changing algorithms, protocols and interfaces, by creating your next embedded design on the world's most flexible system platform. With the latest processing breakthroughs at your fingertips, you can readily meet the demands of applications in automotive, industrial, medical, communications, or defense markets.

### Architect your embedded vision

- Choose MicroBlaze<sup>™</sup>, the only 32-bit soft processor with a configurable MMU, or the industry-standard 32-bit PowerPC® architecture

- Select the exact mix of peripherals that meet your I/O needs, and stitch them together with the new optimized CoreConnect™ PLB bus

### Build, program, debug . . . your way

- Port the OS of your choice including Linux 2.6 for PowerPC or MicroBlaze

- Reduce hardware/software debug time using Eclipse-based IDEs together with integrated ChipScope™ analyzer

### Eliminate risk & reduce cost

- No worry of processor obsolescence with Xilinx Embedded Processing technology and a range of programmable devices

- Reconfigure your design even after deployment, reducing support cost and increasing product life

Order your complete development kit today, and unlock the future of embedded design.

XILINX° www.xilinx.com/processor

At the Heart of Innovation

feature

High-end concepts typically aren't applied to an 8-bit MCU. But don't rule them out just yet.

# The basics of embedded multitasking on a PIC

pplying multitasking to an embedded system based on a PIC microcontroller may look appealing. It permits full use of the PIC resources by serving more than one task at a time rather than staying idle waiting for an external event to occur and reacting accordingly from within an application. However, multitasking can turn applications into memory-hungry monsters that barely fit in your PIC. Task reentrancy is one approach that tackles expanded memory tasks, especially in small to medium PICs.

In this, the first part one of a three part series about reentrant multitasking and how you can realize it with two working examples of a Microchip's PICmicro MCU, I begin with an introduction to multitasking. In part two and three, available on Embedded.com, I'll get more into the meat of multitasking on the PIC.

Embedded multitasking is not new. It goes back some 30 years. The Intel 8080, Zilog Z80, and Motorola 68000 were popular microcontrollers 30 years ago. Interestingly, they were very similar in processing capabilities to many of today's microcontrollers. Those ancient devices had multiple general-purpose and index registers that could perform arithmetic and logic operations, and supported vectored interrupts and I/O ports. They had data buses with widths up to 16 bits, and address buses up to 24-bits wide. They also had large and powerful instruction sets that gave way to efficient programming and ran at moderate speeds of around 10 MHz. What's changed over the years is that today, that same processor is packaged with RAM and EPROM. Adding analog-to-digital modules and EEPROM gives us today's "microcontrollers."

Thirty years ago, full-fledged real-time operating systems (RTOSs) existed and professional features like multitasking and

### feature

multiprocessing were applied and implemented. This brings up an interesting point: where exactly does multitasking fit with this technology? With a little research, I found that products are available to handle multitasking with an RTOS. Developers must then question whether the RTOS is really required for their application, or near-real-time would suffice.

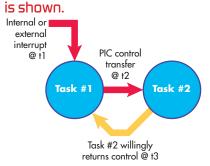

Back then, in the absence of multitasking, serial task execution was the only way to run embedded systems. Figure 1 shows two tasks running in a system. Task #1 executes until it concludes its operation, then passes control to Task #2. Task #2 runs and eventually terminates causing system operation to end.

By definition, multitasking allows an embedded system to share its resources between several programs running concurrently. The resources can be those of the processor itself

# Two tasks are running in a system.

# A simple form of multitasking

Figure 2

(such as internal registers, memory, and arithmetic logic units) or the peripherals attached to the embedded system (such as display, printer, sensors, and actuators).

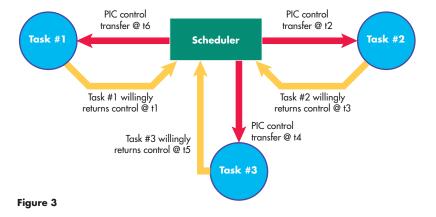

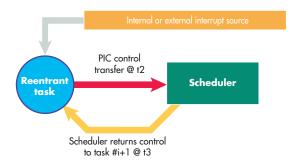

Figure 2 illustrates a simple form of multitasking. Here, Task #1 is the main task running in the system until some sort of interrupt or an event occurs at time t1. This causes the system to put that task on hold, passing its

Back then, in the absence of multitasking, serial task execution was the only way to run embedded systems.

control to another secondary Task #2, at time t2, to serve the event and willingly return system control to the main task at time t3. This kind of multitasking is based on cooperation between the running tasks, such that tasks are willing to give up system control at some point throughout their execution. Note that there's no mention of operating-system coordination between tasks; task delegation of system control is built in the task programs themselves. Nested subroutine calls and branching instructions are a means of implementing simple multitasking.

Multitasking in an operating-system environment is a different story. System resource sharing is realized under the operating system's control, rather than task delegation, by allocating those resources to a single task for a specific period of time before putting them temporarily on hold and switching the resources to another task. The task allocated time and frequency depend on "multitasking poli-

cy." Different policy schemes can be adopted, such as roundrobin (equal task rights) and priority-based (higher priority tasks use resources more frequently than

lower priority ones).

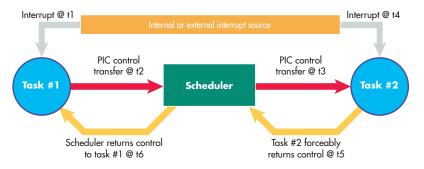

### COOPERATIVE VS. PREEMPTIVE MULTITASKING

The part of the operating system responsible for task switching is called the *task scheduler*. The scheduler enforces the multitasking policy whenever it regains system control from the user tasks. User tasks can be designed to either give up system control to the scheduler voluntarily (scenario #1) or forcibly (scenario #2).

Scenario #1, called *cooperative multitasking*, is where a breakpoint is implanted in the task program to

# As shown, the process gets more complicated when three tasks are implemented. This is called cooperative multitasking.

# SMILE, MARS!

### ThreadX® RTOS manages camera software critical to NASA mission

"We found ThreadX to be a proven solution based on its demonstrated success for the Deep Impact mission, so using it for the HiRISE instrument aboard the MRO was a logical decision. ThreadX delivered a first-rate performance for us and helped the MRO mission return extraordinary high-resolution images from Mars."