Coherent Accelerator Processor Interface User's Manual

# Advance

Version 1.2 29 January 2015

© Copyright International Business Machines Corporation 2014, 2015

Printed in the United States of America January 2015

IBM, the IBM logo, and ibm.com are trademarks or registered trademarks of International Business Machines Corp., registered in many jurisdictions worldwide. Other product and service names might be trademarks of IBM or other companies. A current list of IBM trademarks is available on the Web at "Copyright and trademark information" at <a href="http://www.ibm.com/legal/copytrade.shtml">www.ibm.com/legal/copytrade.shtml</a>.

Other company, product, and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this documents, and is presented as an illustration. The results obtained in other operating environments may vary.

While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

**Note:** This document contains information on products in the design, sampling and/or initial production phases of development. This information is subject to change without notice. Verify with your IBM field applications engineer that you have the latest version of this document before finalizing a design.

You may use this documentation solely for developing technology products compatible with Power Architecture<sup>®</sup>. You may not modify or distribute this documentation. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Systems and Technology Group 2070 Route 52, Bldg. 330 Hopewell Junction, NY 12533-6351

The IBM home page can be found at ibm.com®.

Version 1.2 29 January 2015

**Coherent Accelerator Processor Interface**

# Contents

| List of Tables                                                       | 7                                      |

|----------------------------------------------------------------------|----------------------------------------|

| List of Figures                                                      | 9                                      |

| Revision Log                                                         | . 11                                   |

| About this Document                                                  | . 13                                   |

| Who Should Read This Manual                                          | 13                                     |

| Document Organization                                                | 13                                     |

| Related Publications                                                 |                                        |

| Conventions Used in This Document                                    |                                        |

| Representation of Numbers                                            |                                        |

| Bit Significance                                                     |                                        |

| Other Conventions<br>References to Registers, Fields, and Bits       |                                        |

| Endian Order                                                         |                                        |

|                                                                      | 10                                     |

| 1. Coherent Accelerator Processor Interface Overview                 | . 17                                   |

| 1.1 Coherency                                                        | 17                                     |

| 1.2 POWER Service Layer                                              |                                        |

| 1.3 Application                                                      | 19                                     |

|                                                                      |                                        |

| 2. Introduction to Coherent Accelerator Interface Architecture       |                                        |

| 2.1 Organization of a CAIA-Compliant Accelerator                     |                                        |

| 2.1.1 POWER Service Layer                                            |                                        |

| 2.1.2 Accelerator Function Unit                                      |                                        |

| 2.2 Main Storage Addressing<br>2.2.1 Main Storage Attributes         |                                        |

| 2.2.1 Main Storage Attributes                                        | 23                                     |

| 3. Programming Models                                                | . 25                                   |

| 3.1 Dedicated-Process Programming Model                              |                                        |

| 3.1.1 Starting and Stopping an AFU in the Dedicated-Process Model    |                                        |

| 3.2 Shared Programming Models                                        | 29                                     |

| 3.2.1 Starting and Stopping an AFU in the Shared Models              | 31                                     |

| 3.3 Scheduled Processes Area                                         | 33                                     |

| 3.3.1 Process Element Entry                                          |                                        |

| 3.3.2 Software State Field Format                                    | 35                                     |

| 3.3.3 Software Command/Status Field Format                           | 35<br>36                               |

|                                                                      | 35<br>36<br>37                         |

| 3.4 Process Management                                               | 35<br>36<br>37<br>38                   |

| 3.4.1 Adding a Process Element to the Linked List by System Software | 35<br>36<br>37<br>38<br>39             |

| 3.4.1 Adding a Process Element to the Linked List by System Software | 35<br>36<br>37<br>38<br>39<br>42       |

| 3.4.1 Adding a Process Element to the Linked List by System Software | 35<br>36<br>37<br>38<br>39<br>42<br>43 |

### Advance

|    | 3.4.6 Resume a Process Element                             |    |

|----|------------------------------------------------------------|----|

|    | 3.4.7 Updating a Process Element in the Linked List        |    |

|    |                                                            |    |

| 4. | AFU Descriptor Overview                                    | 59 |

|    | 4.1 AFU Descriptor Format                                  | 59 |

|    |                                                            |    |

| 5. | PSL Accelerator Interface                                  | 63 |

|    | 5.1 Accelerator Command Interface                          | 63 |

|    | 5.1.1 Command Ordering                                     | 66 |

|    | 5.1.2 Reservation                                          |    |

|    | 5.1.3 Locks                                                |    |

|    | 5.1.4 Request for Interrupt Service                        |    |

|    | 5.1.5 Parity Handling for the Command Interface            |    |

|    | 5.2 Accelerator Buffer Interface                           | 69 |

|    | 5.3 PSL Response Interface                                 | 70 |

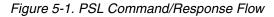

|    | 5.3.1 Command/Response Flow                                |    |

|    | 5.4 Accelerator MMIO Interface                             | 73 |

|    | 5.5 Accelerator Control Interface                          |    |

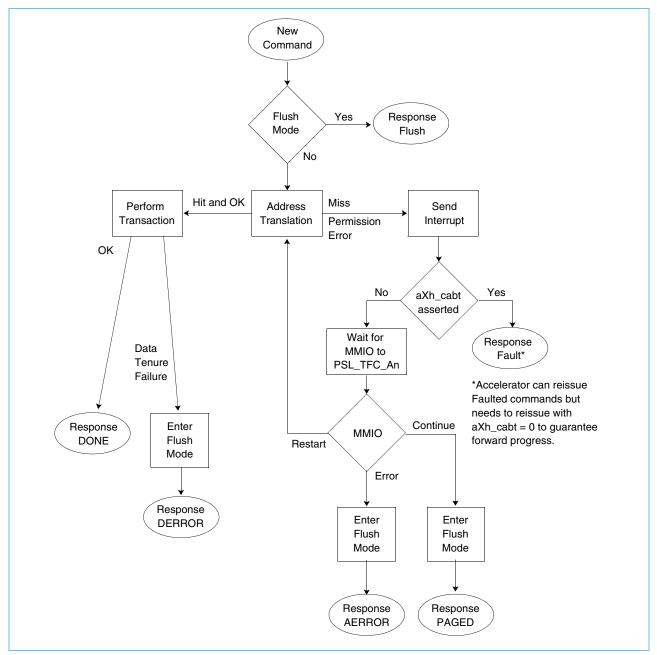

|    | 5.5.1 Accelerator Control Interface in the Non-Shared Mode |    |

|    | 5.5.2 Accelerator Control Interface for Timebase           | 77 |

|    |                                                            |    |

| 6. | . CAPI Low-Level Management (libcxl)                       | 79 |

|    | 6.1 Overview                                               | 79 |

|    | 6.2 CAPI Low-Level Management API                          | 80 |

|    | 6.2.1 Adapter Information and Availability                 | 80 |

|    | 6.2.2 Accelerated Function Unit Selection                  | 81 |

|    | 6.2.3 Accelerated Function Unit Management                 | 82 |

|    |                                                            |    |

| 7. | AFU Development and Design                                 | 87 |

|    | 7.1 High-Level Planning                                    | 87 |

|    | 7.2 Development                                            | 87 |

|    | 7.2.1 Design Language                                      | 87 |

|    | 7.2.2 High-Level Design of the AFU                         | 87 |

|    | 7.2.3 Application Development                              | 88 |

|    | 7.2.4 AFU Development                                      |    |

|    | 7.2.5 Develop Lab Test Plan for the AFU                    |    |

|    | 7.2.6 System Simulation of Application and AFU             |    |

|    | 7.2.7 Test                                                 |    |

|    | 7.3 Best Practices for AFU Design                          |    |

|    | 7.3.1 FPGA Considerations                                  |    |

|    | 7.3.2 General PSL Information                              |    |

|    | 7.3.3 Buffer Interface                                     |    |

|    | 7.3.4 PSL Interface Timing                                 |    |

|    | 7.3.5 Designing for Performance                            |    |

|    | 7.3.6 Simulation                                           |    |

|    | 7.3.7 Debug Considerations                                 |    |

|    | 7.3.8 Operating System Error Handling                      | 90 |

### **Coherent Accelerator Processor Interface**

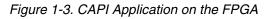

| 8. CAPI Developer Kit Card                                 | 93 |

|------------------------------------------------------------|----|

| 8.1 Supported CAIA Features                                | 93 |

| 8.2 CAPI Developer Kit Card Hardware                       |    |

| 8.3 FPGA Build Restrictions                                | 93 |

| 8.4 CAPI Developer Kit Card FPGA Build Flow                |    |

| 8.4.1 Structure of Quartus Project files                   |    |

| 8.4.2 Build the FPGA                                       | 94 |

| 8.4.3 Load FPGA .rbf File onto the CAPI Developer Kit Card | 95 |

| 8.4.4 Timing Closure Hints                                 |    |

| 8.4.5 Debug Information                                    | 95 |

| Glossary                                                   | 97 |

### **Coherent Accelerator Processor Interface**

# List of Tables

| Register References                                       | 15                                   |

|-----------------------------------------------------------|--------------------------------------|

| Sizes of Main Storage Address Spaces                      | 24                                   |

| Scheduled Processes Area Structure                        | 33                                   |

| Process Element Entry Format                              | 35                                   |

| AFU Descriptor                                            | 60                                   |

| Accelerator Command Interface                             | 63                                   |

| PSL Command Opcodes Directed at the PSL Cache             | 64                                   |

| PSL Command Opcodes That Do Not Allocate in the PSL Cache | 65                                   |

| PSL Command Opcodes for Management                        | 65                                   |

| aXh_cabt Translation Ordering Behavior                    | 66                                   |

| Accelerator Buffer Interface                              | 69                                   |

| PSL Response Interface                                    |                                      |

|                                                           |                                      |

| Accelerator MMIO Interface                                | 73                                   |

| Accelerator Control Interface                             | 74                                   |

| PSL Control Commands on haX_jcom                          | 74                                   |

| FPGA Resources Available for AFU                          | 88                                   |

|                                                           | Sizes of Main Storage Address Spaces |

### **Coherent Accelerator Processor Interface**

# List of Figures

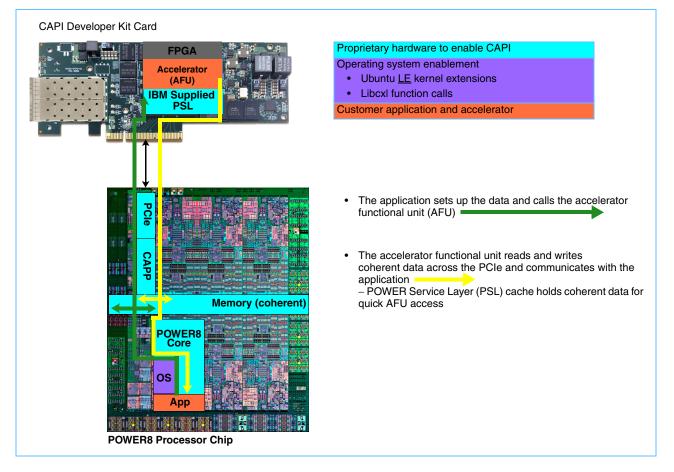

| Figure 1-1. | Coherent Accelerator Process Interface Overview               | 17 |

|-------------|---------------------------------------------------------------|----|

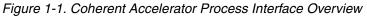

| Figure 1-2. | POWER Service Layer                                           | 18 |

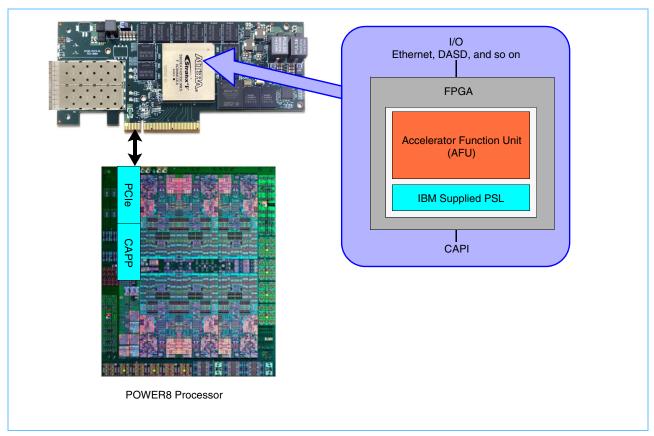

| Figure 1-3. | CAPI Application on the FPGA                                  | 19 |

| Figure 2-1. | CAIA-Compliant Processor System                               | 22 |

| Figure 3-1. | Accelerator Invocation Process in the Dedicated Process Model | 28 |

| Figure 3-2. | Accelerator Invocation Process in the Shared Model            | 32 |

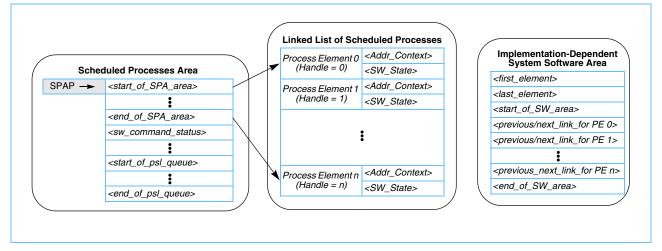

| Figure 3-3. | Structure for Scheduled Processes                             | 33 |

| Figure 5-1. | PSL Command/Response Flow                                     | 72 |

| Figure 5-2. | PSL Accelerator Control Interface Flow in Non-Shared Mode     | 76 |

# **Revision Log**

Each release of this document supersedes all previously released versions. The revision log lists all significant changes made to the document since its initial release. In the rest of the document, change bars in the margin indicate that the adjacent text was significantly modified from the previous release of this document.

| Revision Date    | Version | Contents of Modification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29 January 2015  | 1.2     | <ul> <li>Changed reference to the lwsync instruction to the sync instruction in the following sections:<br/>Section 3.4.1.1 on page 39, Section 3.4.3.1 on page 43, Section 3.4.4.1 on page 48,<br/>Section 3.4.5.1 on page 50, Section 3.4.6.1 on page 54, and Section 3.4.7.1 on page 56.</li> <li>Revised Section 5.1.2 Reservation on page 68.</li> <li>Revised Section 5.1.3 Locks on page 68.</li> <li>Revised Table 5-5 aXh_cabt Translation Ordering Behavior on page 66.</li> <li>Revised Table 5-6 Accelerator Buffer Interface on page 69.</li> <li>Revised Section 6.1 Overview on page 79.</li> <li>Added a note to Section 6.2.2.1 cxl_adapter_afu_next on page 81, Section 6.2.2.2 cxl_afu_next<br/>on page 81, Section 6.2.2.3 cxl_afu_devname on page 81, Section 6.2.2.4<br/>cxl_for_each_adapter_afu on page 82, Section 6.2.2.5 cxl_for_each_afu on page 82,<br/>Section 6.2.3.6 cxl_afu_open_h on page 83, Section 6.2.3.7 cxl_afu_fd on page 83,<br/>Section 6.2.3.8 cxl_afu_attach_full on page 83, and Section 6.2.3.9 cxl_afu_sysfs_pci on<br/>page 84.</li> <li>Added Section 6.2.3.11 cxl_mmio_unmap on page 83.</li> <li>Revised Section 6.2.3.12 cxl_afu_attach on page 83.</li> <li>Revised Section 6.2.3.12 cxl_afu_open_and_attach on page 83.</li> <li>Revised Section 6.2.3.12 cxl_afu_open on page 83.</li> <li>Revised Section 6.2.3.12 cxl_mmio_unmap on page 84.</li> <li>Revised Section 6.2.3.12 cxl_mmio_read on page 84.</li> <li>Revised Section 7.3.5 Designing for Performance on page 89.</li> </ul> |

| 20 November 2014 | 1.1     | <ul> <li>Revised Table 3-2 Process Element Entry Format on page 35.</li> <li>Revised Table 5-2 PSL Command Opcodes Directed at the PSL Cache on page 64.</li> <li>Revised Section 5.1.3 Locks on page 68.</li> <li>Revised Table 5-8 PSL Response Codes on page 71.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 06 November 2014 | 1.0     | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# **About this Document**

This user's guide describes the Coherent Accelerator Processor Interface (CAPI) for the IBM® POWER8<sup>™</sup> systems. This document is intended to assist users of CAPI implementations in designing applications for hardware acceleration. Maintaining compatibility with the interfaces described in this document, allows applications to migrate from one implementation to another with minor changes.

For a specific implementation of the CAPI, see the documentation for that accelerator.

## Who Should Read This Manual

This manual is intended for system software and hardware developers and application programmers who want to develop products that use CAPI. It is assumed that the reader understands operating systems, microprocessor system design, basic principles of reduced instruction set computer (RISC) processing, and details of the Power ISA.

## **Document Organization**

This CAPI User's Manual contains two types of information. First, it provides a general overview of CAPI, accelerator interfaces, and application library calls to use the accelerator. Second, it provides implementation-specific information about building an accelerator for the supported card, along with the architecture limitations of this implementation.

| Document Division                                              | Description                                                                                                                           |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| About this Document                                            | Describes this document, related documents, the intended audience, and other general information.                                     |

| Revision Log                                                   | Lists all significant changes made to the document since its initial release.                                                         |

| Introduction to Coherent Accelerator Interface<br>Architecture | Provides a high-level overview of the Coherent Accelerator Interface Architecture (CAIA) and the system-software programming models.  |

| PSL Accelerator Interface                                      | Describes the interface between the POWER® service layer (PSL) and the accelerator function unit (AFU).                               |

| CAPI Low-Level Management (libcxl)                             | Provides an overview, description of the low-level accelerator management, and some programming examples.                             |

| AFU Development and Design                                     | General information about developing an accelerator functional unit (AFU) and some best practices to consider when designing an AFU.  |

| CAPI Developer Kit Card                                        | Describes CAIA implementation details for the CAPI Developer Kit card and the <u>FPGA</u> build flow for the CAPI Developer Kit card. |

| Glossary                                                       | Defines terms and acronyms used in this document.                                                                                     |

## **Related Publications**

The following documents can be helpful when reading this specification. Contact your IBM representative to obtain any documents that are not available through <u>OpenPOWER Connect</u> or <u>Power.org</u>.

Power ISA User Instruction Set Architecture - Book I (Version 2.07) Power ISA Virtual Environment Architecture - Book II (Version 2.07) Power ISA Operating Environment Architecture (Server Environment) - Book III-S (Version 2.07) I/O Design Architecture v2 (IODA2) (Version 2.4+) Coherent Accelerator Processor Interface (CAPI) Education Package Coherent Accelerator Processor Interface (CAPI) for POWER8 Systems White Paper Coherent Accelerator Processor Interface (CAPI) for POWER8 Systems Decision Guide and Development Process Data Engine for NoSQL - IBM Power Systems™ Edition White Paper POWER8 Functional Simulator User's Guide

## **Conventions Used in This Document**

This section explains numbers, bit fields, instructions, and signals that are in this document.

### **Representation of Numbers**

Numbers are generally shown in decimal format, unless designated as follows:

- Hexadecimal values are preceded by an "x" and enclosed in single quotation marks. For example: x'0A00'.

- Binary values in sentences are shown in single quotation marks. For example: '1010'.

Note: A bit value that is immaterial, which is called a "don't care" bit, is represented by an "X."

### **Bit Significance**

In the documentation, the smallest bit number represents the most significant bit of a field, and the largest bit number represents the least significant bit of a field.

### **Other Conventions**

This document uses the following software documentation conventions:

- Command names or instruction mnemonics are written in **bold** type. For example: **afu\_wr** and **afu\_rd**.

- Variables are written in italic type. Required parameters are enclosed in angle brackets. Optional parameters are enclosed in brackets. For example: afu<f,b>\_wr[a].

This document uses the following symbols:

**Coherent Accelerator Processor Interface**

| &      | bitwise AND                                                                                  |

|--------|----------------------------------------------------------------------------------------------|

| I      | bitwise OR                                                                                   |

| ~      | bitwise NOT                                                                                  |

| %      | modulus                                                                                      |

| =      | equal to                                                                                     |

| ! =    | not equal to                                                                                 |

| ≥      | greater than or equal to                                                                     |

| ≤      | less than or equal to                                                                        |

| x >> y | shift to the right; for example, $6 >> 2 = 1$ ; least-significant y bits are dropped         |

| x << y | shift to the left; for example, $3 \ll 2 = 12$ ; least-significant y bits are replaced zeros |

| II     | Concatenate                                                                                  |

# **References to Registers, Fields, and Bits**

Registers are referred to by their full name or by their short name (also called the register mnemonic). Fields are referred to by their field name or by their bit position. *Table 1* describes how registers, fields, and bit ranges are referred to in this document and provides examples.

| Type of Reference                                                                                                  | Format                                                                    | Example                                |

|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------|

| Reference to a specific register and a<br>specific field using the register short<br>name and the field name       | Register_Short_Name[Field_Name]                                           | MSR[R]                                 |

| Reference to a field using the<br>ield name                                                                        | [Field_Name]                                                              | [R]                                    |

| Reference to a specific register and to<br>nultiple fields using the register short<br>name and the field names    | Register_Short_Name[Field_Name1, Field_Name2]                             | MSR[FE0, FE1]                          |

| Reference to a specific register and to<br>nultiple fields using the register short<br>name and the bit positions. | Register_Short_Name[Bit_Number, Bit_Number]                               | MSR[52, 55]                            |

| Reference to a specific register and to a                                                                          | Register_Short_Name[Bit_Number]                                           | MSR[52]                                |

| ield using the register short name and he bit position or the bit range.                                           | Register_Short_Name[Starting_Bit_Number:Ending_Bit_Number]                | MSR[39:44]                             |

| A field name followed by an equal sign<br>=) and a value indicates the value for<br>het field                      | Register_Short_Name[Field_Name]=n <sup>1</sup>                            | MSR[FE0]='1'<br>MSR[FE]=x'1'           |

| that field.                                                                                                        | Register_Short_Name[Bit_Number]=n <sup>1</sup>                            | MSR[52]='0'<br>MSR[52]=x'0'            |

|                                                                                                                    | Register_Short_Name[Starting_Bit_Number:Ending_Bit_Number]=n <sup>1</sup> | MSR[39:43]='10010'<br>MSR[39:43]=x'11' |

### Table 1. Register References

## **Endian Order**

The *Power ISA* supports both big-endian and little-endian byte-ordering modes. *Book I* of the *Power ISA* describes these modes.

The CAIA supports only big-endian byte ordering. Because the CAIA supports only big-endian byte ordering, the POWER service layer (PSL) does not implement the optional little-endian byte-ordering mode of the *Power ISA*. The data transfers themselves are simply byte moves, without regard to the numerical significance of any byte. Thus, the big-endian or little-endian issue becomes irrelevant to the actual movement of a block of data. The byte-order mapping only becomes significant when data is fetched or interpreted; for example, by an accelerator function.

# **1. Coherent Accelerator Processor Interface Overview**

The Coherent Accelerator Process Interface (CAPI) is a general term for the infrastructure of attaching a coherent accelerator to an IBM POWER® system. The main application is executed on the host processor with computation-heavy functions executing on the accelerator. The accelerator is a full peer to the host processor, with direct communication with the application. The accelerator uses an unmodified effective address with full access to the real address space. It uses the processor's page tables directly with page faults handled by system software. *Figure 1-1* shows an overview of CAPI.

# 1.1 Coherency

The Coherent Attached Processor Proxy (CAPP) in the multi-core POWER8<sup>™</sup> processor extends coherency to the attached accelerator. A directory on the CAPP provides coherency responses on behalf of the accelerator. Coherency protocol is tunneled over standard PCI Express links between the CAPP unit on the processor and the POWER service layer (PSL) on the accelerator card.

## **1.2 POWER Service Layer**

The PSL, provided by IBM, is used by the accelerator to interface with the POWER8 system. The PSL interface to the accelerator is described in *Section 5 PSL Accelerator Interface* on page 63. This interface provides the basis for all communication between the accelerator and the POWER8 system. The PSL provides address translation that is compatible with the Power Architecture® for the accelerator and provides a cache for the data being used by the accelerator. This provides many advantages over a standard I/O model, including shared memory, no pinning of data in memory for <u>DMA</u>, lower latency for cached data, and an easier, more natural programming model. *Figure 1-2* shows an overview of the FPGA with the PSL, the customer's AFU, the CAPI interface, and other available interfaces.

Figure 1-2. POWER Service Layer

## 1.3 Application

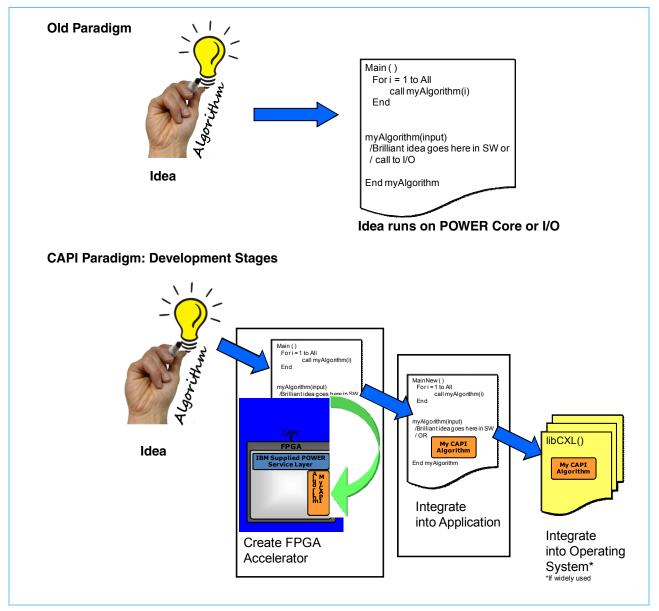

The application that runs on the <u>FPGA</u> can be a new solution or one ported from a software application or an I/O subsystem. The new host algorithm is far lighter compared to the old paradigm. The new paradigm offloads the processor or avoids device driver programming overhead. *Figure 1-3* compares the old paradigm with the CAPI paradigm.

The accelerator algorithm that resides on the FPGA is referred to as the accelerator functional unit (AFU). The AFU is created in a source language that can be synthesized by the FPGA tools. This source language must also be able to be compiled into a simulation environment of the user's choice. The host algorithm uses the off-loaded AFU through the library calls to an included library, libcxl. For more information about the AFU development cycle, see *Section 7 AFU Development and Design* on page 87.

Section 2 Introduction to Coherent Accelerator Interface Architecture on page 21 and Section 3 Programming *Models* on page 25 provide an overview of the architecture for coherent acceleration in a POWER8 system. These sections are provided as background to the programming models provided by the Coherent Accelerator Interface Architecture (CAIA). The facilities referenced are not fully described in these sections and are generally not required for an application developer.

Section 4 AFU Descriptor Overview on page 59 provides an overview of the AFU descriptor. The AFU descriptor is a set of registers within the problem state area that contains information about the capabilities of the AFU required by system software.

Section 5 PSL Accelerator Interface on page 63 describes the interface facilities provided by the POWER service layer (PSL) for the AFU. The interface facilities provide the AFU with the ability to read and write main storage, maintain coherency with the system caches, and perform synchronization primitives. Collectively, these facilities are called the accelerator unit interface (AUI).

Section 6 CAPI Low-Level Management (libcxl) on page 79 describes the low-level library interface (libcxl) for CAPI. The libcxl provides an application programming interface (API) for the allocation/de-allocation and communication with a CAPI accelerator.

*Section 7 AFU Development and Design* on page 87 provides some general information about developing an AFU and some best practices to consider when designing an AFU.

Section 8 CAPI Developer Kit Card on page 93 describes CAIA implementation details for the CAPI Developer Kit card and the FPGA build flow for the CAPI Developer Kit card.

# 2. Introduction to Coherent Accelerator Interface Architecture

The Coherent Accelerator Interface Architecture (CAIA) defines an accelerator interface structure for coherently attaching accelerators to the Power Systems using a standard <u>PCIe</u> bus. The intent is to allow implementation of a wide range of accelerators to optimally address many different market segments.

# 2.1 Organization of a CAIA-Compliant Accelerator

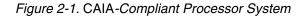

Logically, the CAIA defines two functional components: the PSL and the AFU. The PSL in a CAIA-compliant accelerator provides the interface to the host processor. Effective addresses from an AFU are translated to a physical address in system memory by the PSL. The PSL also provides miscellaneous management for the AFUs. Although the CAIA architecture defines interfaces for up to four AFUs per PSL, early implementations support only a single AFU. The AFU can be dedicated to a single application or shared between multiple applications. However, only the dedicated programming model is currently supported.

Physically, a CAIA-compliant accelerator can consist of a single chip, a multi-chip module (or modules), or multiple single-chip modules on a system board or other second-level package. The design depends on the technology used, and on the cost and performance characteristics of the intended design point.

*Figure 2-1* on page 22 illustrates a CAIA-compliant accelerator with several (n) AFUs connected to the PSL. All the AFUs share a single cache.

### 2.1.1 POWER Service Layer

A CAIA-compliant processor includes a POWER service layer (PSL). The PSL is the bridge to the system for the AFU, and provides address translation and system memory cache. In addition, the PSL provides miscellaneous facilities for the host processor to manage the virtualization of the AFUs, interrupts, and memory management.

The PSL consists of several functional units (such as the memory-protection tables). Hardware resources defined in the CAIA are mapped explicitly to the real address space seen by the host processor. Therefore, any host processor can address any of these resources directly, by using an appropriate effective address value. A primary function of the PSL is the physical separation of the AFUs so that they appear to the system as independent units.

### 2.1.2 Accelerator Function Unit

**Note:** The AFU functional definition is outside the scope of the CAPI User's Manual. The AFU functional definition is owned by the CAPI solution provider.

A CAIA-compliant processor includes one or more AFUs. The AFUs are user-defined functions for accelerating applications. They typically process data and initiate any required data transfers to perform their allocated tasks.

The purpose of an AFU is to provide applications with a higher computational unit density for hardware acceleration of functions to improve the performance of the application and off-load the host processor. Using an AFU for application acceleration allows for cost-effective processing over a wide range of applications.

When an application requests use of an AFU, a process element is added to the process-element linked list that describes the application's process state. The process element also contains a work element descriptor (WED) provided by the application. The WED can contain the full description of the job to be performed or a pointer to other main memory structures in the application's memory space. Several programming models are described providing for an AFU to be used by any application or for an AFU to be dedicated to a single application. See *Section 3 Programming Models* on page 25 for details.

## 2.2 Main Storage Addressing

The addressing of main storage in the CAIA is compatible with the addressing defined in the Power ISA. The CAIA builds upon the concepts of the Power ISA and extends the addressing of main storage to the AFU.

The AFU uses an effective address to access main storage. The effective address is computed by the AFU and is provided to the PSL. The effective address is translated to a real address according to the procedures described in the overview of address translation in Power ISA, Book III. The real address is the location in main storage that is referenced by the translated effective address.

All the AFUs share main storage with the host processors. This storage area can either be uniform in structure or can be part of a hierarchical cache structure. Programs reference this level of storage by using an effective address.

### 2.2.1 Main Storage Attributes

The main storage of a system typically includes both general-purpose and nonvolatile storage. It also includes special-purpose hardware registers or arrays used for functions such as system configuration, data-transfer synchronization, memory-mapped I/O, and I/O subsystems.

IBM

Table 2-1 lists the sizes of address spaces in main storage.

## Table 2-1. Sizes of Main Storage Address Spaces

| Address Space                                                       | Size                  | Description                                                                                                                                                                                                        |

|---------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Real Address Space                                                  | 2 <sup>m</sup> bytes  | where $m \leq 60$                                                                                                                                                                                                  |

| Effective Address Space                                             | 2 <sup>64</sup> bytes | An effective address is translated to a virtual address using the segment lookaside buffer (SLB).                                                                                                                  |

| Virtual Address Space                                               | 2 <sup>n</sup> bytes  | where $65 \le n \le 78$ A virtual address is translated to a real address using the page table.                                                                                                                    |

| Real Page (Base)                                                    | 2 <sup>12</sup> bytes |                                                                                                                                                                                                                    |

| Virtual Page                                                        | 2 <sup>p</sup> bytes  | where $12 \le p \le 28$<br>Up to eight page sizes can be supported simultaneously. A small 4 KB (p = 12) page is<br>always supported. The number of large pages and their sizes are implementation depen-<br>dent. |

| Segment Size                                                        | 2 <sup>s</sup> bytes  | where s = 28 or 40 The number of virtual segments is $2^{(n-s)}$ where $65 \le n \le 78$ .                                                                                                                         |

| Note: The values of "m," "n," and "p" are implementation dependent. |                       |                                                                                                                                                                                                                    |

# 3. Programming Models

The Coherent Accelerator Interface Architecture (CAIA) defines several programming models for virtualization of an acceleration function unit (AFU):

- Dedicated-process programming model (no AFU virtualization)

- Shared programming models, which include these two types:

- <u>PSL</u>-controlled shared programming models (AFU time-sliced virtualization)

- AFU-directed shared programming models (AFU-controlled process element selection virtualization)

### Architecture Note:

The AFU-directed programming model, where the AFU selects a context from the process element linked list to use for a transfer, is intended for the *Networking* and *Storage* market segments. For these types of applications, the required address context is selected based on a packet received from a network or which process is accessing storage. A CAIA-compliant device can also act as system memory or the lowest point of coherency (LPC). In this model, the process element and address translation are not required. The LPC model can also be used in combination with the other programming models but might not be supported by all devices.

**Note:** The shared programming models are for future releases only. Currently, libcxl only supports the dedicated-programming model. Additional programming models might be added in the future.

In the dedicated process model, the AFU is dedicated to a single application or process under a single operating system. The single application can act as an "Application as a Service" and funnel other application requests to the accelerator, providing virtualization within a partition.

In the PSL-controlled shared and AFU-directed shared programming models, the AFU can be shared by multiple partitions. The shared models require a system hypervisor to virtualize the AFU so that each operating system can access the AFU. For single-partition systems not running a hypervisor, the AFU is owned by the operating system. In both cases, the operating system can virtualize the AFU so that each process or application can access the AFU.

For the AFU-directed shared programming model, the AFU selects a process element using a process handle. The process handle is an implementation-specific value provided to the host process when registering its context with the AFU (that is, calling system software to add the process element to the process element linked list). While the process handle is implementation specific, the lower 16-bits of the process handle must be the offset of the process element within the process element linked list.

The "process element" contains the process state for the corresponding application. The work element descriptor (WED) contained in the process element can be a single job requested by an application or contains a pointer to a queue of jobs. In the latter case, the WED is a pointer to the job request queue in the application's address space.

This document does not cover all aspects of the programming models. The intent of this section is to provide a reference for how the AFUs can be shared by all or a subset of the processes in the system. This section defines the infrastructure for setting up the process state and sending a work element descriptor (WED) to an AFU to start a job in a virtualized environment. The function performed by an AFU is implementation dependent.

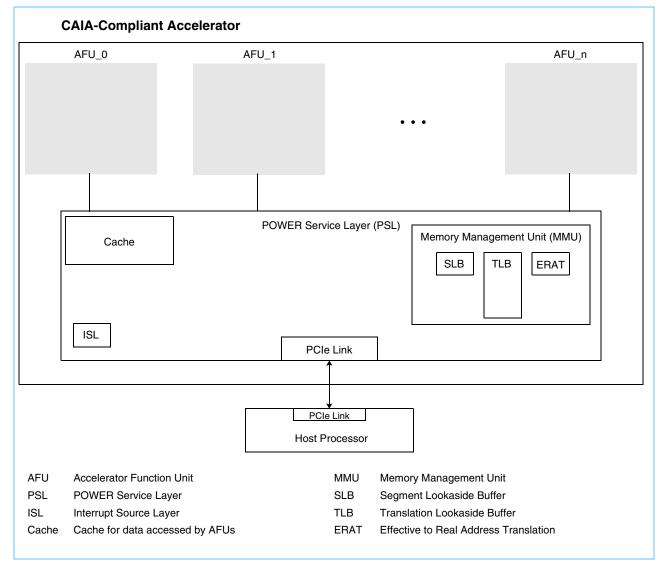

## 3.1 Dedicated-Process Programming Model

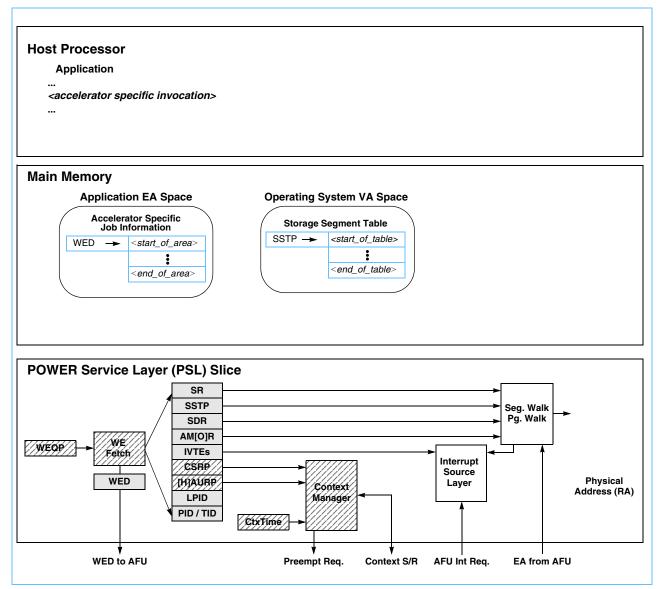

The dedicated-process programming model is implementation specific. *Figure 3-1 Accelerator Invocation Process in the Dedicated Process Model* on page 28 shows how an application invokes an accelerator under the dedicated-process programming model.

In this model, a single process owns the AFU. Because the AFU is dedicated to a single process, the programming model is not defined in this document. For more information, see the documentation for the specific implementation.

Because the AFU is owned by a single process, the hypervisor initializes the PSL for the owning partition and the operating system initializes the PSL for the owning process at the time when the AFU is assigned. The following information is initialized:

**Note:** The PSL architecture allows multiple AFUs (available in future implementations). These registers are duplicated for each AFU. Each of these duplicated registers is called a slice.

Registers initialized by the hypervisor:

- PSL Slice Control Register (PSL\_SCNTL\_An)

- Real Address (RA) Scheduled Processes Area Pointer (PSL\_SPAP\_An) {disable}

- PSL Authority Mask Override Register (PSL\_AMOR\_An)

- Interrupt Vector Table Entry Offset (PSL\_IVTE\_Offset\_An)

- Interrupt Vector Table Entry Limit (PSL\_IVTE\_Limit\_An)

- PSL State Register (PSL\_SR\_An)

- PSL Logical Partition ID (PSL\_LPID\_An)

- Real address (RA) Hypervisor Accelerator Utilization Record Pointer (HAURP\_An) {disable}

- PSL Storage Description Register (PSL\_SDR\_An)

Registers initialized by the operating system:

- PSL Process and Thread Identification (PSL\_PID\_TID\_An)

- Effective Address (EA) Context Save/Restore Pointer (CSRP\_An) {disable}

- Virtual Address (VA) Accelerator Utilization Record Pointer (AURP0\_An) and (AURP1\_An) {disable}

- Virtual Address (VA) Storage Segment Table Pointer (SSTP0\_An) and (SSTP1\_An)

- PSL Authority Mask (PSL\_AMR\_An)

- PSL Work Element Descriptor (PSL\_WED\_An)

### 3.1.1 Starting and Stopping an AFU in the Dedicated-Process Model

In a dedicated-process programming model, an AFU is started and stopped by system software (operating system or hypervisor). This section describes the sequence used by system software to start an AFU and is provided for reference only. An application simply calls libcxl with the desired WED, and libcxl performs the system software calls described in the following procedures. The WED is specific to each AFU. It contains all the information an AFU requires to do its work or it can be a pointer to a memory location where the application has set up a command queue of work to be completed. See *Section 6 CAPI Low-Level Management (libcxl)* on page 79 for additional information.

Use the following procedure to start an AFU.

1. System software must initialize the state of the PSL.

All the required Privileged 1, Privileged 1 Slice, and Privileged 2 Slice registers must be initialized so that the address context for the processes and other contexts such as the interrupt vector table entries can be used.

- 2. System software must set the AFU Slice Reset bit in the AFU\_Cntl\_An Register (AFU\_Cntl\_An[RA]). Setting the AFU Slice Reset starts a reset sequence for the corresponding AFU. Initiating a reset sequence also disables the AFU. The AFU does not respond to the problem state <u>MMIO</u> region while disabled.

- 3. System software must poll the AFU Slice Reset Status for the AFU Slice Reset Sequence to be complete (AFU\_Cntl\_An[RS]='10').

- 4. System software must set the WED if required by the AFU at start time. The WED is initialized by writing a 64-bit WED value to the PSL\_WED\_An Register. System software writes the WED that was passed to libcxl by the application.

- 5. System software must set the AFU Enable bit in the AFU\_Cntl\_An Register (AFU\_Cntl\_An[E]). The state of the AFU Enable Status must be a '00' before system software setting can set the AFU Enable bit to a '1' for a start command to be issued to the AFU by the PSL. The WED is passed to the AFU when the start command is issued.

- 6. System software must poll the AFU Enable Status for the AFU Slice Enabled (AFU\_Cntl\_An[ES]='10'). The AFU\_Cntl\_An[ES] field is set to '10' when the PSL and AFU are initialized, running, and able to accept MMIO. After the AFU is running, system memory accesses can be performed by the AFU and problem state MMIOs can be performed by software.

**Note:** If problem state registers are required to be initialized in the AFU before the application starts, the AFU must provide a mechanism for starting the accelerator and must not depend on the start command issued by the PSL.

Use the following procedure to stop an AFU.

- 1. System software must set the AFU Slice Reset bit in the AFU\_Cntl\_An Register (AFU\_Cntl\_An[RA]). Setting the AFU Slice Reset starts a reset sequence for the corresponding AFU. Initiating a reset sequence also disables the AFU. The AFU does not respond to the Problem State MMIO region while disabled.

- System software must poll the AFU Slice Reset Status for the AFU Slice Reset Sequence to be complete (AFU\_Cntl\_An[RS] = '10').

## 3.2 Shared Programming Models

**Note:** This section is for future releases only. Currently, libcxl only supports the dedicated programming model.

The shared programming models allow for all or a subset of processes from all or a subset of partitions in the system to use an AFU. There are two programming models where the AFU is shared by multiple processes and partitions; PSL time-sliced shared and AFU-directed shared.

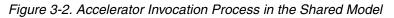

Figure 3-2 on page 32 shows how an application invokes an AFU under the shared programming model.

In this model, the system hypervisor owns the AFU and makes the function available to all operating systems. For an AFU to support virtualization by the system hypervisor, the AFU must adhere to the following requirements:

- An application's job request must be autonomous (that is, the state does not need to be maintained between jobs),

- -- OR --

The AFU must provide a context save and restore mechanism.

- An application's job request must be guaranteed by the AFU to complete in a specified amount of time, including any translation faults,

- -- OR --

The AFU must provide the ability to preempt the processing of the job.

• The AFU must be guaranteed fairness between processes when operating in the AFU-directed shared programming model.

In the case where an AFU can be preempted, the AFU can either require the current job to be restarted from the beginning, or it can provide a method to save and restore the context so that the current job can be restarted from the preemption point at a later time.

For the shared model, the application is required to make an operating-system system call with at least the following information:

An AFU type (AFU\_Type)

The AFU type describes the targeted acceleration function for the system call. The AFU\_Type is a system-specific value.

• A work element descriptor (WED)

This document does not define the contents of the WED. The WED is AFU implementation specific and can be in the form of an AFU command, an effective address pointer to a user-defined structure, an effective address pointer to a queue of commands, or any other data structure to describe the work to be done by the AFU.

• An Authority Mask Register (AMR) value

The AMR value is the AMR state to use for the current process. The value passed to the operating system is similar to an application setting the AMR in the processor by using <u>spr</u> 13 or by calling a system library. If the PSL and AFU implementations do not support a User Authority Mask Override Register (UAMOR), the operating system should apply the current UAMOR value to the AMR value before passing the AMR in the hypervisor call (hcall). The UAMOR is not described in this document. For more information about the UAMOR, see the *Power ISA, Book III*. The hypervisor can optionally apply the current Authority Mask Override Register (AMOR) value before placing the AMR into the process element. The PSL applies the PSL\_AMOR\_An when updating the PSL\_AMR\_An Register from the process element.

A Context Save/Restore Area Pointer (CSRP) The CSRP is the effective address of an area in the applications memory space for the AFU to save and restore the context state. This pointer is optional if no state is required to be saved between jobs or when a job is preempted. The context save/restore area must be pinned system memory.

Upon receiving the system call (syscall), the operating system verifies that the application has registered and been given the authority to use the AFU. The operating system then calls the hypervisor (hcall) with at least the following information:

- A work element descriptor (WED)

- An Authority Mask Register (AMR) value, masked with the current PSL\_AMOR\_An Register value by the PSL and optionally masked with the current UAMOR by the hypervisor.

- An effective address (EA) Context Save/Restore Area Pointer (CSRP)

- A process ID (PID) and optional thread ID (TID)

- A virtual address (VA) accelerator utilization record pointer (AURP)

- The virtual address of the storage segment table pointer (SSTP)

- A logical interrupt service number (LISN)

Upon receiving the hypervisor call (hcall), the hypervisor verifies that the operating system has registered and been given the authority to use the AFU. The hypervisor then puts the process element into the process element linked list for the corresponding AFU type. The process element contains at least the following information:

- A work element descriptor (WED)

- An Authority Mask Register (AMR) value, masked with the current AMOR

- An effective address (EA) Context Save/Restore Area Pointer (CSRP)

- A process ID (PID) and optional thread ID (TID)

- A virtual address accelerator utilization record pointer (AURP)

- The virtual address of the storage segment table pointer (SSTP)

- Interrupt vector table (IVTE\_Offset\_n, IVTE\_Range\_n), derived from the LISNs in the hypervisor call parameters.

- A state register (SR) value

- A logical partition ID (LPID)

- A real address (RA) hypervisor accelerator utilization record pointer (HAURP)

- The Storage Descriptor Register (SDR)

The hypervisor initializes the following PSL registers:

- PSL Control Register (PSL\_SCNTL\_An)

- Real address (RA) Scheduled Processes Area Pointer (PSL\_SPAP\_An)

- PSL Authority Mask Override Register (PSL\_AMOR\_An)

### 3.2.1 Starting and Stopping an AFU in the Shared Models

In the shared, PSL-controlled time-sliced programming model, the AFU is automatically started and stopped by the PSL. The PSL essentially follows the procedures defined in *Section 3.1.1 Starting and Stopping an AFU in the Dedicated-Process Model* on page 26.

In the AFU-directed shared programming model, starting and stopping an AFU process is an AFU implementation-specific procedure.

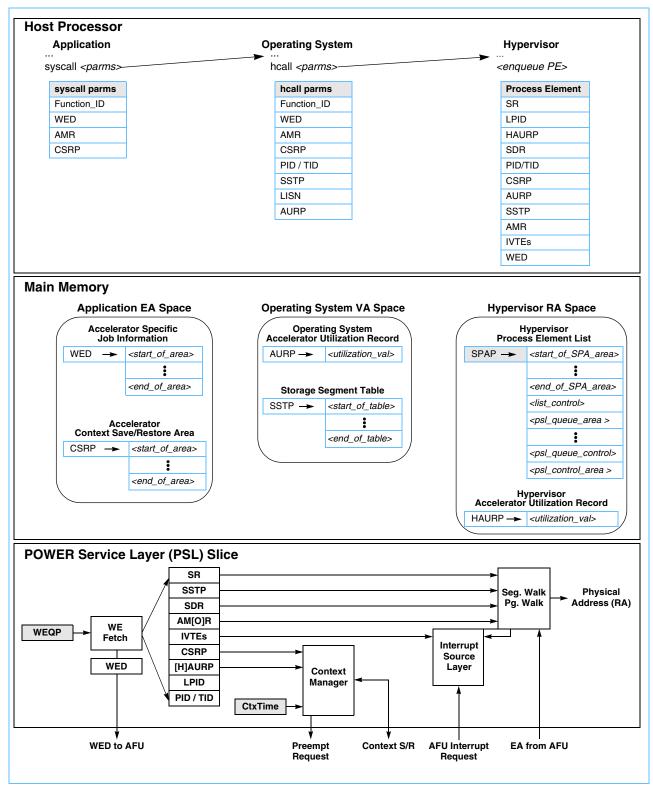

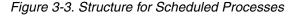

## **3.3 Scheduled Processes Area**

In the virtualization programming models, the PSL reads process elements from a structure located in system memory called the scheduled processes area (SPA). The SPA contains a list of processes to be serviced by the AFUs. The process elements contain the address context and other state information for the processes scheduled to run on the AFUs assigned to service the SPA structure. The SPA structure consists of two sections: a linked list maintained by system software and a circular queue maintained by the PSL. The circular queue section is only used for programming models where the context swaps are managed by the PSL. For all other programming models, the circular queue section is not used. *Figure 3-3* shows the structure that contains the processes scheduled for the AFUs.

*Table 3-1* defines the various fields and areas within the scheduled processes structure. The starting address of the area (SPA\_Base) is defined by the PSL Scheduled Processes Area Pointer Register (PSL\_SPAP\_An). The size of the area (PSL\_SPAP\_An[size]) determines the number of process elements supported by the structure and the amount of storage that must be allocated. The storage must be contiguous in the real address space and naturally aligned to the size of the scheduled processes area.

**Note:** The structure for the scheduled processes in *Figure 3-3* contains an implementation-dependent system software area. This area is used to maintain the linked list pointers for maintaining the list of active process elements and the free list of process elements. How these pointers are maintained is implementation specific and outside the scope of the CAIA.

| Mnemonic                  | Address (Byte)                                                                                  | Description                                                                                                                                                                                                                                                                   |

|---------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| start_of_linked_list_area | SPA_Base                                                                                        | This is the start of the area in system storage used by system<br>software to store the linked list of process elements scheduled<br>for the acceleration function units (AFUs).<br>The process elements in this area must never be cached by the<br>PSL in a modified state. |

| end_of_linked_list_area   | SPA_Base + $(n \times 128) - 1$ ;<br>where n = maximum number of process<br>elements supported. | This is the end of the area in system storage used by system software to store the linked list of process elements scheduled for the AFUs.                                                                                                                                    |

### Table 3-1. Scheduled Processes Area Structure (Sheet 2 of 2)

| Mnemonic                    | Address (Byte)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sw_command_status           | SPA_Base + $((n+3) \times 128)$ ;<br>where n = maximum number of process<br>elements supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Software command for the first PSL assigned to service the pro-<br>cess element. The last PSL assigned to service the process<br>elements returns the status.<br><b>Note:</b> This location must never be cached by the PSL in a mod-<br>ified state.                                                                                                                                                  |

| No                          | ote: Storage in the SPA above this addres                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ss must <u>not</u> be read by system software.                                                                                                                                                                                                                                                                                                                                                         |

| start_of_PSL_queue_<br>area | SPA_Base + ((n+4) $\times$ 128);<br>where n = maximum number of process<br>elements supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | This is the start of the area in system storage used by the PSLs for the queue of process elements waiting to run.                                                                                                                                                                                                                                                                                     |