| A Constant Function Example                                                                                                                                                  | Part 2-30<br>Suther I and<br><sup>H</sup> D <sub>L</sub> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| <pre>module ram (); parameter RAM_SIZE = 1024; parameter ADDRESS = 12; input [ADDRESS-1:0] address_bus;</pre>                                                                |                                                          |

| <pre>module ram (); parameter RAM_SIZE = 1024; input [clogb2(RAM_SIZE)-1:0] address_bus;</pre>                                                                               |                                                          |

| <pre>function integer clogb2 (input integer depth};     begin         for(clogb2=0; depth&gt;0; clogb2=clogb2+1)         depth = depth &gt;&gt; 1;     end endfunction</pre> |                                                          |

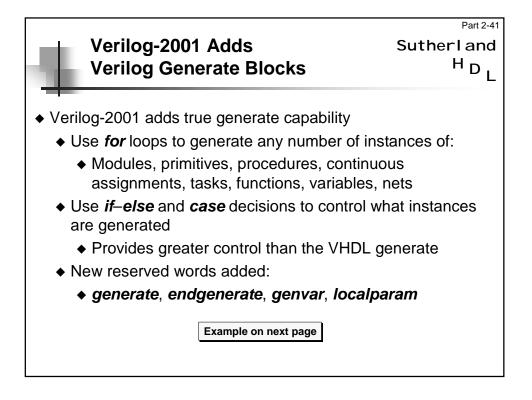

| Verilog Generate Example                                                                                                                                                                                                           | Part 2-4<br>Sutherland<br><sup>H</sup> D |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| <pre>module multiplier (a, b, product); parameter a_width = 8, b_width = 8; localparam product_width = a_width + b_width; input [a_width-1:0] a; input [b_width-1:0] b;</pre>                                                      |                                          |

| <pre>output [product_width-1:0] product;<br/>generate<br/>if ((a_width &lt; 8)    (b_width &lt; 8))<br/>CLA_multiplier #(a_width, b_width) u1 (a, b<br/>else<br/>WALLACE_multiplier #(a_width, b_width) u1 (<br/>endgenerate</pre> |                                          |

| endmodule                                                                                                                                                                                                                          |                                          |

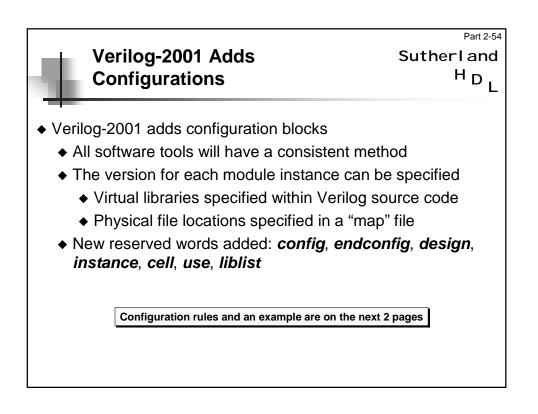

| Verilog Configuration Example                                                                                                                     |                                                                                                                                                                                                                                                                                                                                   |                                                                            |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|

| Verilog Design                                                                                                                                    | Configuration Block (part of Ver                                                                                                                                                                                                                                                                                                  | ilog source code)                                                          |  |

| <pre>module test;<br/><br/>myChip dut ();<br/><br/>endmodule<br/>module myChip();<br/><br/>adder a1 ();<br/>adder a2 ();<br/><br/>endmodule</pre> | <pre>/* define a name for this confi<br/>config cfg4<br/>/* specify where to find top<br/>design rtlLib.test<br/>/* set the default search or<br/>instantiated modules */<br/>default liblist rtlLib gateLi<br/>/* explicitly specify which i<br/>for the following module i<br/>instance test.dut.a2 liblist<br/>endconfig</pre> | <pre>level modules */ der for finding ib; library to use instance */</pre> |  |

| Library Map File                                                                                                                                  | <pre>/* location of RTL models (curre<br/>library rtlLib "./*.v";<br/>/* Location of synthesized model<br/>library gateLib "./synth_out/*.v</pre>                                                                                                                                                                                 | Ls */                                                                      |  |