## **USER MANUAL**

# **Accessory 51S**

High Resolution Interpolator Board

3A0-603674-xUxx

December 8, 2009

#### **Copyright Information**

© 2009 Delta Tau Data Systems, Inc. All rights reserved.

This document is furnished for the customers of Delta Tau Data Systems, Inc. Other uses are unauthorized without written permission of Delta Tau Data Systems, Inc. Information contained in this manual may be updated from time-to-time due to product improvements, etc., and may not conform in every respect to former issues.

To report errors or inconsistencies, call or email:

#### Delta Tau Data Systems, Inc. Technical Support

Phone: (818) 717-5656 Fax: (818) 998-7807

Email: <a href="mailto:support@deltatau.com">support@deltatau.com</a>

Website: <a href="http://www.deltatau.com">http://www.deltatau.com</a>

#### **Operating Conditions**

All Delta Tau Data Systems, Inc. motion controller products, accessories, and amplifiers contain static sensitive components that can be damaged by incorrect handling. When installing or handling Delta Tau Data Systems, Inc. products, avoid contact with highly insulated materials. Only qualified personnel should be allowed to handle this equipment.

In the case of industrial applications, we expect our products to be protected from hazardous or conductive materials and/or environments that could cause harm to the controller by damaging components or causing electrical shorts. When our products are used in an industrial environment, install them into an industrial electrical cabinet or industrial PC to protect them from excessive or corrosive moisture, abnormal ambient temperatures, and conductive materials. If Delta Tau Data Systems, Inc. products are directly exposed to hazardous or conductive materials and/or environments, we cannot guarantee their operation.

|      | REVISION HISTORY                                   |          |     |            |  |  |  |  |  |  |

|------|----------------------------------------------------|----------|-----|------------|--|--|--|--|--|--|

| REV. | DESCRIPTION                                        | DATE     | CHG | APPVD      |  |  |  |  |  |  |

| 1    | UPDATED +/- 12-15 VOLT REQUIREMENT, P. 1           | 02/13/08 | СР  | S. MILICI  |  |  |  |  |  |  |

| 2    | UPDATED CLIPPER SETUP DESCRIPTION, P. 16           | 12/08/09 | CP  | S. MILICI  |  |  |  |  |  |  |

| 3    | CORRECTED ADDRESSING FOR ACC-51S USED WITH CLIPPER | 10/01/10 | SS  | S. SATTARI |  |  |  |  |  |  |

|      |                                                    |          |     |            |  |  |  |  |  |  |

|      |                                                    |          |     |            |  |  |  |  |  |  |

|      |                                                    |          |     |            |  |  |  |  |  |  |

### **Table of Contents**

| INTRODUCTION                                                    | 1  |

|-----------------------------------------------------------------|----|

| Features                                                        | 1  |

| Board Configuration                                             | 1  |

| Options                                                         |    |

| Indicators                                                      |    |

| Jumpers                                                         | 2  |

| Installation                                                    |    |

| Connectors                                                      |    |

| ENCODER CONNECTIONS                                             | 3  |

| Sinusoidal Encoder Wiring                                       |    |

| Differential Format                                             |    |

| Single-Ended Format                                             |    |

| Type of Cable for Encoder Wiring                                |    |

| PHOTOS OF PMAC2A-PC/104 WITH ACC-51S                            |    |

| PRINCIPLE OF OPERATION                                          |    |

|                                                                 |    |

| ACC-51S PARAMETER SETUP                                         |    |

| Using ACC-51S Data for Feedback                                 |    |

| Using ACC-51S Data for Commutation Feedback                     |    |

| Motor x Software Position Capture and Trigger Mode              |    |

| Using ACC-51S Data for Servo Feedback                           |    |

| Setting the Conversion Table Entries with the Executive Program |    |

| Setting the Conversion Table Entries Manually                   |    |

| Using the Conversion Table Results                              |    |

| Using ACC-51S Data for Servo Feedback with the Clipper Board    |    |

| Setting the Conversion Table Entries with the Executive Program | 16 |

| Setting the Conversion Table Entries Manually                   |    |

| Using the Conversion Table Results                              |    |

| I-Variables for Clipper Processor                               |    |

| Encoder Decode Control I-Variables (17mn0)                      |    |

| Using ACC-51S Data for Commutation Feedback with Clipper        | 18 |

| Motor xx Counts per N Commutation Cycles (Ixx71)                | 19 |

| Motor xx Number of Commutation Cycles (N) (Ixx70)               | 19 |

| Commutation Position I-Variables (Ixx83)                        | 19 |

| A-D Converter Registers for the Clipper Board                   | 19 |

| OFFSET REGISTER MAPPING DEFINITIONS                             | 21 |

| DSPGATE1 Registers                                              | 21 |

| Viewing Actual Encoder Position                                 | 22 |

| A-D Converter Registers                                         | 22 |

| CONNECTOR DESCRIPTIONS                                          | 23 |

| J7 JMACH1 Encoder Quadrature Outputs                            | 23 |

| J7: JMACH1 – ENC Quadrature Outputs                             | 23 |

| J9, J10, J11, J12 Encoder Inputs                                |    |

| J9 (9-Pin DB9S Connector)                                       |    |

| J10 (9-Pin DB9S Connector)                                      |    |

| J11 (9-Pin DB9S Connector)                                      |    |

| J12 (9-Pin DB9S Connector)                                      |    |

| TB1 User Supplied Power                                         |    |

| JUMPER CONFIGURATIONS                                           | 27 |

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~                          |    |

| Table of Jumpers                                                              | 27 |

|-------------------------------------------------------------------------------|----|

| E1 – Select Card Address                                                      |    |

| E2 - Encoder Power Select                                                     |    |

| E3, E4, E5, E6, E7, E8 - Encoder Input Select Channel 1 and 2                 |    |

| E9, E10, E11, E12, E13, E14 - Encoder Input Select (Option 1- add 2 Channels) |    |

ii Table of Contents

### **INTRODUCTION**

Delta Tau's ACC-51S Interpolator Accessory is a sine wave input interpolator designed to interface analog quadrature encoders to the PMAC2A-PC/104.

The ACC-51S stacks on top of the PMAC2A-PC/104 or on top of the ACC-1P 5-8 axis board.

#### **Features**

The Interpolator accepts inputs from two (optionally four) sinusoidal or quasi-sinusoidal encoders and provides encoder position data to the PMAC. This interpolator creates 4,096 steps per sine-wave cycle.

The Interpolator can accept a voltage-source (1Vp-p) signal from the encoder. A jumper selects between unterminated or  $120\Omega$  input termination.

The maximum sine-cycle frequency input is 1.4MHz which gives a maximum speed of 5.734 billion steps per second.

When used with a 1000 line sinusoidal rotary encoder, there will be 4,096,000 discrete states per revolution (128,000 software counts). The maximum calculated electrical speed of this encoder will be 1,400 RPS or 84,000 RPM which exceeds the maximum physical speed of most encoders.

The ACC-51S sends quadrature and index signal to PMAC2A-PC/104 or ACC -1P through that board's JMACHA port. Other incremental encoders cannot be shared on the same JMACHA pins.

Note:

The ACC-51S requires version 1.17C (April 2004) or newer firmware in PMAC2A-PC/104 for proper operation.

The ACC-51S requires the attached PMAC2A-PC104 CPU card to have its +/-12-15 volts installed, otherwise a watchdog condition may occur.

### **Board Configuration**

The base version of the ACC-51S consists of a PC/104 form factor board with two sinusoidal encoder inputs for 1V p-p sinusoidal encoders.

#### **Options**

Option 1 300-603674-OPT Additional two channels (channel 3 and 4)

Option 1 provides the interface circuitry and connectors for two additional sinusoidal encoders for a total of four encoders on the ACC-51S.

Note:

The options described above must be installed at the factory.

#### **Indicators**

Refer to the layout diagram of the expansion port interpolator for the location of the indicators on the board.

#### D1, D2, {D3, D4 Opt 1} AQUAD Indicators

These LEDs indicate the A-channel quadrature input. When the encoder is operating normally, this indicator will flicker with a rate that is dependent upon the speed of the moving encoder.

D1 is input 1 and D2 is input 2. With ACC-51S option 1, D3 is input 3 and D4 is input 4.

Introduction 1

#### **Jumpers**

Jumper E1 controls whether the A/D converters on the ACC-51S are addressed as the first four channels (connecting pins 2 and 3) or the second four channels (connecting pins 1 and 2).

Jumper E2 controls whether the encoders are powered from the ACC-51S (connecting pins 1 and 2) or whether external power is required (connecting pins 2 and 3).

Jumpers E3-E14 control the termination of each of the 12 encoder input signal pairs. Connect pins 1 and 2 of each jumper to leave the input pair unterminated. Connect pins 2 and 3 of each jumper to terminate the signal pair through a  $120\Omega$  resistor.

#### Installation

The ACC-51S mounts directly on top of the PMAC2A-PC/104 board or ACC-1P board to which it interfaces. There are stacking connectors along two of the four edges; the prongs of the connectors of the ACC-51S board fit into the sockets of the matching connectors of the board below it.

#### **Connectors**

J9-J12 are DB9S connectors for the input of sinusoidal encoder signals for channels 1-4, respectively of the ACC-51S.

J7 provides the output of the generated digital quadrature signals to the PMAC2A-PC/104 board or the ACC-1P board immediately below the ACC-51S. A cable is provided for connection of these signals.

2 Introduction

### **ENCODER CONNECTIONS**

Be sure to use shielded, twisted pair cabling for sinusoidal encoder wiring. (Double insulated is recommended.) The sinusoidal signals are small and must be kept as noise free as possible. Avoid cable routing near a noisy motor or driver wiring.

The use of single-ended output style sinusoidal encoders at very slow speeds has been shown to provide large amounts of velocity-ripple. When very slow speeds are needed, use differential output style sinusoidal encoders.

#### **Sinusoidal Encoder Wiring**

Sinusoidal encoders operate on the concept that there are two analog signal outputs that have a profile that is 90° out of phase. They are available with different drive characteristics some of which are described below.

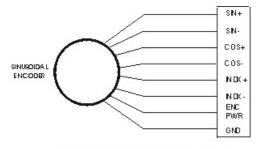

#### **Differential Format**

The differential format provides a means of using twisted pair wiring which allows for better noise immunity when wired into machinery.

There are two common output types available with differential style sinusoidal encoders. They are current mode and voltage mode style encoder output.

The current mode encoder output uses a high impedance 11µA pk-pk output. The voltage mode output encoder uses low impedance 1V pk-pk output.

The voltage mode encoder type is connected to the interpolator as shown. Usually, termination is selected by using jumpers on the interpolator board.

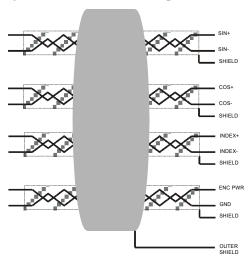

DIFFERENTIAL ENCODER CONNECTION

Note:

Voltage mode encoders are becoming the more popular choice for machine designs due to their lower impedance outputs. Lower impedance outputs represent better noise immunity. Therefore, more reliable encoder interfaces.

The ACC-51 uses only voltage mode encoders.

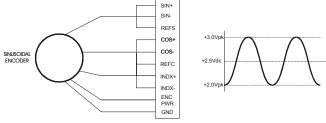

### **Single-Ended Format**

The single-ended format provides a simpler means of using a sinusoidal encoder. Typically, fewer wires are needed and the encoders are always the lower impedance voltage output type.

It should be noted that all the single-ended encoder formats shown here may have velocity-ripple effects at very slow speeds due to the effects of op-amp  $V_{io}$  offsets. These offsets cause the sinusoidal signal to be centered at a value that is slightly different than the reference or servo ground.

The diagram shown below is a simple single-ended encoder-wiring interface. This encoder has SIN and COS outputs that provide a 1V peak-to-peak output that has a voltage offset of 2.5Vdc. Note that the SIN-, COS-, and INDEX- lines are tied to the 2.5V internal references on the interpolator card.

SINGLE-ENDED ENCODER CONNECTION

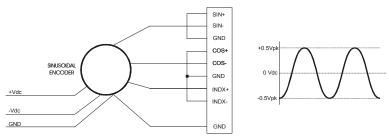

The diagram shown below is similar to the diagram above. This encoder has SIN and COS outputs that provide a 1V peak-to-peak output that has a voltage offset of 0.0Vdc. Note that the SIN-, COS-, and INDEX- lines are tied to the GND on the interpolator card and usually the encoder requires a bipolar supply.

ALTERNATE SINGLE-ENDED ENCODER CONNECTION

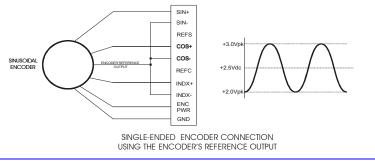

The diagram shown below is a single-ended encoder that provides a reference output. This encoder has SIN and COS outputs which provide a 1V peak-to-peak output that has a voltage offset which is provided as an output of the encoder. The SIN-, COS-, and INDEX- lines are tied to the encoder's reference output. This type of encoder connection is expected to be more precise than the typical single-ended encoder as shown in the first diagram above because the internal reference (usually set at 2.5Vdc) is the mechanism that establishes the offsets for the SIN+, COS+, and INDEX+ outputs.

Note:

Do not connect the reference output of the encoder to the REFS and REFC lines on the interpolator card. Doing so will cause the interpolator to function incorrectly.

#### Type of Cable for Encoder Wiring

Low capacitance shielded twisted pair cable is ideal for wiring differential encoders. The better the shield wires, the better the noise immunity to the external equipment wiring. Wiring practice for shielded cables is not an exact science. Different applications will present different sources of noise which may require experimentation to achieve the desired results.

If possible, the best cabling to use is a double-shielded twisted pair cable. Typically, there are four pairs used in a differential encoder's wiring. The picture below shows how the wiring may be implemented for a typical differential encoder using double-shielded twisted-pair cable.

EXAMPLE OF DOUBLE SHIELDED 4 TWISTED PAIR CABLE

The shielded wires should be tied to ground (Vcc return) at the interpolator end. It is acceptable to tie the shielded wires together if there are not enough terminals available. Keep the exposed wire lengths as close as possible to the terminals on the interpolator.

#### Note:

It has been observed that there is an inconsistency in the shielding styles that are used by different encoder manufacturers.

Be sure to check pre-wired encoders to ensure that the shielded wires are not connected at the encoder's side. Shielded wires should be connected only on one side of the cable.

If the encoder has shielded wires that are connected to the case ground of the encoder, make sure that the encoder and motor cases are sufficiently grounded and do not connect the shield at the interpolator end.

If the encoder has pre-wired double shielded cable that only has the outer shield connected at the encoder, then connect only the inner shielded wires to the interpolator. Be sure not to mix the shield interconnections.

One possible cable type for encoders is Belden 8164 or ALPHA 6318. This is a 4-pair individually shielded cable that has an overall shield. This double shielded cable has a relatively low capacitance and is a  $100\Omega$  impedance cable.

Cables for single-ended encoders need to be shielded for the best noise immunity. Single-ended encoder types cannot take advantage of the differential noise immunity that comes with twisted pair cables.

Note:

If noise is a problem in the application, careful attention must be given to the method of grounding that is used in the system. Amplifier and motor grounding can play a significant role in how noise is generated in a machine.

It is possible that noise may be reduced in a motor-based system by the use of inductors that are placed between the motor and the amplifier.

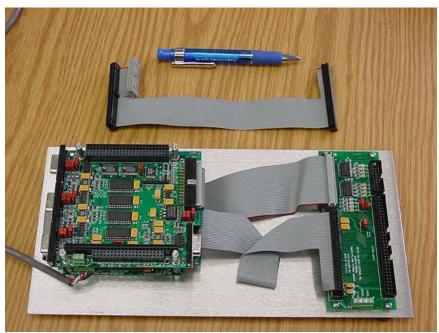

### PHOTOS OF PMAC2A-PC/104 WITH ACC-51S

4 - Axis PC-104 PMAC with 4-Axis Interpolator Attached

- 1. 8-inch adapter cable is shown at top of picture.

- 2. Breakout accessory card (p/n 603688) is shown for conversion to PMAC1 style JMACH connector at right side of mounting plate.

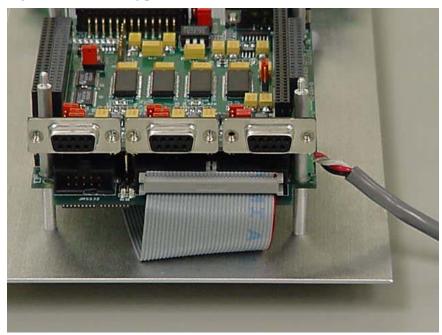

**End View of 4-Axis with Interpolator**

- 1. This view shows three D-SUB connectors for encoder inputs.

- 2. Ribbon cable is used for flag inputs.

3. Shown with power supplied at right side of bottom board.

**End View of PC-104**

- 1. End view of interpolator shows D-SUB for encoder connection.

- 2. Adapter board shows connections of the 50-pin JMACH1 and 34-pin JMACH2 ribbon cables. JMACH1 provides DAC outputs and JMACH2 provides limit switch inputs at PC-104 processor.

8-Axis PC-104 with Interpolator Attached

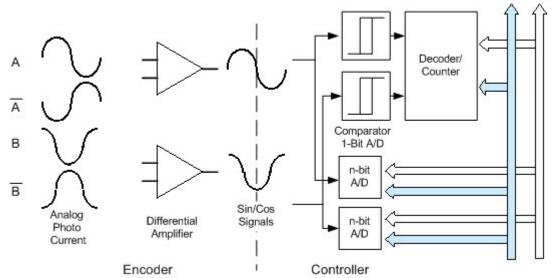

#### PRINCIPLE OF OPERATION

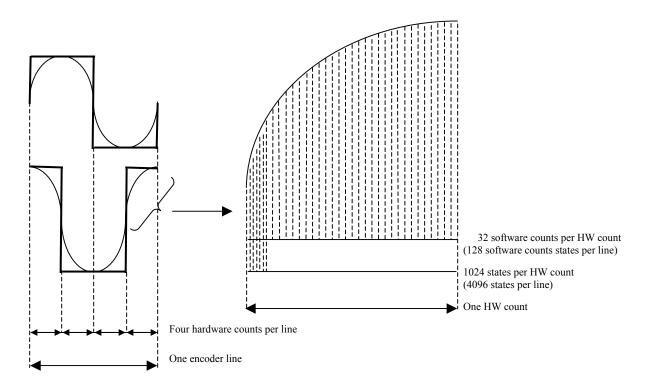

The sine and cosine signals from the encoder are processed in two ways in the ACC-51 board (see diagram). First, they are sent through comparators that square up the signals into digital quadrature and sent into the quadrature decoding and counting circuit of the Servo IC on the ACC-51. The decoding must be set up for quadrature times-4 decode (I9n0 or I7mn0 = 3 or 7) to generate four counts per line in the hardware counter.

The units of the hardware counter which are called hardware counts are ¼ of a line. Usually, this fact is an internal detail. However, there are two cases in which this is important.

- 1. If the sinusoidal encoder is used for PMAC-based brushless-motor commutation, the hardware counter, not the fully interpolated position value, will be used for the commutation position feedback. The units of Ixx71 will therefore be hardware counts.

- 2. If the hardware position-compare circuits in the Servo IC are used, the units of the compare register are hardware counts. (The same is true of the hardware position-capture circuits, but these scaling issues are often handled automatically through the move-until-trigger constructs).

The second, or parallel, processing of the sine and cosine signals is through analog-to-digital converters, which produce numbers proportional to the input voltages. These numbers are used to calculate mathematically an arctangent value that represents the location within a single line. This is calculated to 1/4096 of a line, so there are 4096 unique states per line, or 1024 states per hardware count.

For historical reasons, PMAC expects the position it reads for its servo feedback software to have units of 1/32 of a count. That is, it considers the least significant bit (LSB) of whatever it reads for position feedback to have a magnitude of 1/32 of a count for the purposes of its software scaling calculations. The resulting software units are called software counts and any software parameter that uses counts from the servo feedback (e.g. jog speed in counts/msec, axis scale factor in counts/engineering-unit) is using these software counts. In most cases, such as digital quadrature feedback, these software counts are equivalent to hardware counts.

However, with the added resolution produced by the ACC-51 interpolator, software counts and hardware counts are no longer the same. The LSB produced by the interpolator (through the encoder conversion table processing) is 1/1024 of a hardware count, but PMAC software considers it 1/32 of a software count. Therefore, with the ACC-51, a software count is 1/32 the size of a hardware count.

The following equations express the relationships between the different units when using the ACC-51:

Principle of Operation 9

```

1 line = 4 hardware counts = 128 software counts = 4096 states (LSBs)

1/4-line = 1 hardware count = 32 software counts = 1024 states (LSBs)

1/128-line = 1/32-hardware count = 1 software count = 32 states (LSBs)

1/4096-line = 1/1024-hardware count = 1/32-software count = 1 state (LSB)

```

Note that these are only naming conventions. Even the position data that is fractional in terms of software counts is real. The servo loop can see it and react to it and the trajectory generator can command to it.

#### Example 1:

A 4-pole rotary brushless motor has a sinusoidal encoder with 2000 lines. It directly drives a screw with a 5-mm pitch. The encoder is used for both commutation and servo feedback.

The commutation uses the hardware counter. There are 8000 hardware counts per revolution, and 2 commutation cycles per revolution of the 4-pole motor. Therefore, Ix70 will be set to 2, and Ix71 will be set to 8000. Ix83 will contain the address of the hardware counter's phase capture register.

For the servo, the interpolated results of the conversion table are used. There are 128 software counts per line, or 256,000 software counts per revolution. With each revolution corresponding to 5 mm on the screw, there are 51,200 software counts per millimeter. The measurement resolution, at 4096 states per line, is 1/8,192,000 of a revolution, or 1/1,638,400 of a millimeter (~0.6 nanometers/state).

10 Principle of Operation

#### Example 2:

A linear brushless motor has a commutation cycle of 60.96 mm (2.4 inches). It has a linear scale with a 20-micron line pitch. The scale is used for both commutation and servo feedback.

The commutation uses the hardware counter. There are 200 hardware counts per millimeter (5 microns per count), so 12,192 hardware counts per commutation cycle. Ix70 should be set to 1 and Ix71 should be set to 12,192.

The servo uses the interpolated results of the conversion table. With 128 software counts per line, and 50 lines per millimeter, there are 6400 software counts per millimeter (or 162,560 software counts per inch). The measurement resolution, at 4096 states per line, is 204,800 states per mm (~5 nanometers/state).

Principle of Operation 11

### **ACC-51S PARAMETER SETUP**

Note:

Use of the ACC-51S with the PMAC2A-PC/104 requires the use of V1.17C (dated April 2004) or newer firmware in the PMAC2A-PC/104.

#### **Using ACC-51S Data for Feedback**

The main purpose of the ACC-51S board is to provide feedback (or possibly master) position data for the PMAC's commutation and/or servo use. To be used by the servo loop, the ACC-51S data must be processed first by PMAC's Encoder Conversion Table (ECT). The ECT is executed at the beginning of each servo cycle to prepare the required feedback and master data for servo-loop use. It consists of a series of entries, each of which reads one or more raw feedback registers, processes the data by one of several available methods, and computes a single numerical result.

#### **Using ACC-51S Data for Commutation Feedback**

If using the sinusoidal encoder processed with the ACC-51S for the commutation position feedback, the fully interpolated position value is not used, only the quadrature hardware encoder counter position value which has four counts per line of the encoder. (These can be referred to as hardware counts – units of a hardware counter – to distinguish them from software counts, as explained below.) Motor variable Ix83 must contain the address of the phase position register for that encoder channel. The following table shows the values of Ix83 for each channel:

Ix83 Commutation Encoder Addresses for ACC-51S

| Channel | Address | Channel | Address | Channel | Address | Channel | Address |

|---------|---------|---------|---------|---------|---------|---------|---------|

| 1       | \$C001  | 3       | \$C011  | 5       | \$C021  | 7       | \$C031  |

| 2       | \$C009  | 4       | \$C019  | 6       | \$C029  | 8       | \$C039  |

Channels 1-4 of the ACC-51S correspond to PMAC channels 1-4 if the ACC-51S is connected to the main PMAC2A-PC/104 board; channels 1-4 of the ACC-51S correspond to PMAC channels 5-8 if the ACC-51S is connected to the ACC-1P board.

The Ix70 and Ix71 variables that set the size of the commutation cycle as Ix71/Ix70 counts should then use these hardware counts (1/4-line) as units. For example, with a 4-pole rotary motor with a 2000-line-per-revolution sinusoidal encoder, Ix70 would be set to 2 (four poles = two commutation cycles) and Ix71 would be set to 8000 ( $2000 \times 4$ ).

#### **Motor x Software Position Capture and Trigger Mode**

Ix03 is used to establish position capture (Index Position Input). Bit 16 of this variable must be set to 1 to function as software index capture. There is a background cycle delay (typically 2-3 msec) which limits the accuracy of the capture.

Ix25 is used for the address of the flags for the capture, as well as the limit flags and amplifier flags (all must be from the same channel number).

Note:

As of this manual revision, hardware capture is not available for the PMAC2.

#### **Using ACC-51S Data for Servo Feedback**

#### **Setting the Conversion Table Entries with the Executive Program**

ACC-51S data must be processed according to the high-resolution interpolation method. Create entries of this type using the PMAC Executive program or by entering the entries manually with on-line commands. To use the Executive Program, select Configure, then Conversion Table to get the setup menu for the ECT. For each entry, from the pick list for methods, select High-resolution interpolation. Then enter the encoder address and the ADC (analog/digital converter) address. The following tables show the addresses to be used:

**Encoder Addresses for ACC-51S**

| Channel | Address | Channel | Address | Channel | Address | Channel | Address |

|---------|---------|---------|---------|---------|---------|---------|---------|

| 1       | \$C000  | 3       | \$C010  | 5       | \$C020  | 7       | \$C030  |

| 2       | \$C008  | 4       | \$C018  | 6       | \$C028  | 8       | \$C038  |

Channels 1-4 of the ACC-51S correspond to PMAC channels 1-4 if the ACC-51S is connected to the main PMAC2A-PC/104 board; channels 1-4 of the ACC-51S correspond to PMAC channels 5-8 if the ACC-51S is connected to the ACC-1P board.

ADC Addresses for ACC-51S

| Channel | Entry  | Channel | Entry  | Channel | Entry  | Channel | Entry  |

|---------|--------|---------|--------|---------|--------|---------|--------|

| 1       | \$FFC0 | 3       | \$FFC4 | 5       | \$FFC8 | 7       | \$FFCC |

| 2       | \$FFC2 | 4       | \$FFC6 | 6       | \$FFCA | 8       | \$FFCE |

ACC-51S channels 1-4 become PMAC channels 1-4 if ACC-51S jumper E1 connects pins 2 and 3. ACC-51S channels 1-4 become PMAC channels 5-8 if ACC 51S jumper E1 connects pins 1 and 2.

#### **Setting the Conversion Table Entries Manually**

Encoder Channel Address: The first line of the two-line entry contains \$F in the first hex digit and the base address of the encoder channel to be read in the low 19 bits (bits 0 to 15). If bit 19 is set to 1 (making the second hex digit \$8), PMAC expects a PMAC2-style Servo IC for the interpolator, as in the ACC-51S for the PMAC2A-PC/104. The last four hex digits of the line contain the base address of the encoder channel used.

The following table shows the possible entries for the ACC-51S which uses the Servo ICs of the PMAC2A-PC/104 main board (Channels 1-4) and the ACC-1P Axis 5-8 board (Channels 5-8):

High-Resolution Interpolator Entry First Lines for ACC-51S

| Channel | Entry    | Channel | Entry    | Channel | Entry    | Channel | Entry    |

|---------|----------|---------|----------|---------|----------|---------|----------|

| 1       | \$F8C000 | 3       | \$F8C010 | 5       | \$F8C020 | 7       | \$F8C030 |

| 2       | \$F8C008 | 4       | \$F8C018 | 6       | \$F8C028 | 8       | \$F8C038 |

A/D Converter Address: The second line of the entry contains \$00 in the first two hex digits and the base address of the first of two A/D converters to be read in the low 16 bits (bits 0 to 15, the last four hex digits). The second A/D converter will be read at the next higher address. The following table shows the possible entries when the ACC-51S is used.

High- Resolution Interpolator Entry Second Lines for ACC-51S

| Channel | Entry    | Channel | Entry    | Channel | Entry    | Channel | Entry    |

|---------|----------|---------|----------|---------|----------|---------|----------|

| 1       | \$00FFC0 | 3       | \$00FFC4 | 5       | \$00FFC8 | 7       | \$00FFCC |

| 2       | \$00FFC2 | 4       | \$00FFC6 | 6       | \$00FFCA | 8       | \$00FFCE |

ACC-51S channels 1-4 become PMAC channels 1-4 if ACC-51S jumper E1 connects pins 2 and 3. ACC-51S channels 1-4 become PMAC channels 5-8 if ACC 51S jumper E1 connects pins 1 and 2.

**Example:** To set up the conversion table manually to process all eight channels of sinusoidal encoders, and nothing else, use the following command lines could be used:

```

WY:$0720,$F8C000,$00FFC0

; Ch. 1, result in X:$0721

WY:$0722,$F8C008,$00FFC2

; Ch. 2, result in X:$0723

WY:$0724,$F8C010,$00FFC4

; Ch. 3, result in X:$0725

WY: $0726, $F8C018, $00FFC6

Ch. 4, result in X:$0727

WY:$0728,$F8C020,$00FFC8

Ch. 5, result in X:$0729

WY:$072A,$F8C028,$00FFCA

Ch. 6, result in X:$072B

; Ch. 7, result in X:$072D

WY:$072C,$F8C030,$00FFCC

WY:$072E,$F8C038,$00FFCE

; Ch. 8, result in X:$072F

```

#### **Using the Conversion Table Results**

The result of the entry is in the X-register of the second line. The address of this register should be assigned to the servo-loop address variable for its particular uses: Ix03 (position-loop feedback address); Ix04 (velocity-loop feedback address); Ix05 (master position address).

The encoder conversion table starts at PMAC address \$0720. If nothing else precedes the high-resolution interpolator entries, and eight of these entries process the eight sinusoidal encoders in numerical order, the following table shows the addresses where the conversion table results can be found. The motor servo I-Variables should be set to the appropriate address.

Conversion Table Result Addresses

| Channel | Address | Channel | Address | Channel | Address | Channel | Address |

|---------|---------|---------|---------|---------|---------|---------|---------|

| 1       | \$0721  | 3       | \$0725  | 5       | \$0729  | 7       | \$072D  |

| 2       | \$0723  | 4       | \$0727  | 6       | \$072B  | 8       | \$072F  |

The results found in these addresses are 24-bit values. The least significant bit of the result is 1/4096 of a line of the encoder. PMAC software treats the data it reads for the servo loop as having units of 1/32 count, so for software purposes, a count is 1/128 of a line. This can be called a software count to distinguish it from units of the hardware counter. Subsequent calculations such as axis scaling, jog speeds, etc., should use this scaling of 128 (software) counts per line.

### Using ACC-51S Data for Servo Feedback with the Clipper Board

#### **Setting the Conversion Table Entries with the Executive Program**

ACC-51S data must be processed according to the high-resolution interpolation method. Create entries of this type using the PMAC Executive program or by entering the entries manually with on-line commands. To use the Executive Program, select Configure, then Conversion Table to get the setup menu for the ECT. For each entry, from the pick list for methods, select High-resolution interpolation. Then enter the encoder address and the ADC (analog/digital converter) address. The following tables show the addresses to be used:

Encoder Addresses for ACC-51S

| Channel<br>Entry | Channel<br>Entry | Channel<br>Entry | Channel<br>Entry |

|------------------|------------------|------------------|------------------|

| 1 \$78000        | 3 \$78010        | 5 \$78100        | 7 \$78110        |

| 2 \$78008        | 4 \$78018        | 6 \$78108        | 8 \$78118        |

Channels 1-4 of the ACC-51S correspond to PMAC channels 1-4 if the ACC-51S is connected to the main PMAC2A-PC/104 board; channels 1-4 of the ACC-51S correspond to PMAC channels 5-8 if the ACC-51S is connected to the ACC-1P board.

ADC Addresses for ACC-51S

| Channel<br>Entry | Channel<br>Entry | Channel<br>Entry | Channel<br>Entry |

|------------------|------------------|------------------|------------------|

| 1 \$78800        | 3 \$78804        | 5 \$78808        | 7 \$7880C        |

| 2 \$78802        | 4 \$78806        | 6 \$7880A        | 8 \$7880E        |

ACC-51S channels 1-4 become PMAC channels 1-4 if ACC-51S jumper E1 connects pins 2 and 3. ACC-51S channels 1-4 become PMAC channels 5-8 if ACC 51S jumper E1 connects pins 1 and 2.

#### **Setting the Conversion Table Entries Manually**

Encoder Channel Address: The first line of the two-line entry contains \$F in the first hex digit and the base address of the encoder channel to be read in the low 19 bits (bits 0 to 15). If bit 19 is set to 1 (making the second hex digit \$8), PMAC expects a PMAC2-style Servo IC for the interpolator, as in the ACC-51S for the PMAC2A-PC/104. The last four hex digits of the line contain the base address of the encoder channel used.

The following table shows the possible entries for the ACC-51S which uses the Servo ICs of the PMAC2A-PC/104 main board (Channels 1-4) and the ACC-1P Axis 5-8 board (Channels 5-8): High-Resolution Interpolator Entry First Lines for ACC-51S

| Channel<br>Entry | Channel<br>Entry | Channel<br>Entry | Channel<br>Entry |

|------------------|------------------|------------------|------------------|

| 1 \$FF8000       | 3 \$FF8010       | 5 \$FF8100       | 7 \$FF8110       |

| 2 \$FF8008       | 4 \$FF8018       | 6 \$FF8108       | 8 \$FF8118       |

A/D Converter Address: The second line of the entry contains \$00 in the first two hex digits and the base address of the first of two A/D converters to be read in the low 16 bits (bits 0 to 15, the last four hex digits). The second A/D converter will be read at the next higher address. The following table shows the possible entries when the ACC-51S is used.

High-Resolution Interpolator Entry Second Lines for ACC-51S

| <br>    |         |         |         |

|---------|---------|---------|---------|

| Channel | Channel | Channel | Channel |

| Entry     | Entry     | Entry     | Entry     |

|-----------|-----------|-----------|-----------|

| 1 \$78800 | 3 \$78804 | 5 \$78808 | 7 \$7880C |

| 2 \$78802 | 4 \$78806 | 6 \$7880A | 8 \$7880E |

ACC-51S channels 1-4 become PMAC channels 1-4 if ACC-51S jumper E1 connects pins 2 and 3. ACC-51S channels 1-4 become PMAC channels 5-8 if ACC 51S jumper E1 connects pins 1 and 2. **Example:** To set up the conversion table manually to process four channels of sinusoidal encoders, and nothing else, use the following command lines could be used:

| I8000=\$FF8000 |         |       |        |

|----------------|---------|-------|--------|

| I8001=\$078800 |         |       |        |

| I8002=\$0      | ;result | in    | \$3503 |

| I8003=\$FF8008 |         |       |        |

| 18004=\$078802 |         |       |        |

| 18005=\$0      | ;result | in    | \$3506 |

| I8006=\$FF8010 |         |       |        |

| 18007=\$078804 |         |       | 42500  |

| 18008=\$0      | result  | ın    | \$3509 |

| 18009=\$FF8018 |         |       |        |

| I8010=\$078806 | ;result | -1-20 | ¢3E0D  |

| I8011=\$0      | riesuit | Т11   | 9000B  |

#### **Using the Conversion Table Results**

The result of the entry is in the X-register of the second line. The address of this register should be assigned to the servo-loop address variable for its particular uses: Ix03 (position-loop feedback address); Ix04 (velocity-loop feedback address); Ix05 (master position address).

The encoder conversion table starts at PMAC address \$0720. If nothing else precedes the high-resolution interpolator entries, and eight of these entries process the eight sinusoidal encoders in numerical order, the following table shows the addresses where the conversion table results can be found. The motor servo IVariables should be set to the appropriate address. Refer to the table below:

|                       | Ixx03,Ix<br>x04<br>Value | Conversion<br>Table 1st Line<br>Entry | Conversion Table 2nd line Entry | Conversion Table 3rd line Entry |

|-----------------------|--------------------------|---------------------------------------|---------------------------------|---------------------------------|

| Processed Encoder #1  | \$3501                   | I8000                                 | n.a. (single-line e             |                                 |

| Processed Encoder #2  | \$3502                   | I8001                                 | n.a.                            |                                 |

| Processed Encoder #3  | \$3503                   | 18002                                 | n.a.                            |                                 |

| Processed Encoder #4  | \$3504                   | I8003                                 | n.a.                            |                                 |

| Processed Encoder #5  | \$3505                   | I8004                                 | n.a.                            |                                 |

| Processed Encoder #6  | \$3506                   | I8005                                 | n.a.                            |                                 |

| Processed Encoder #7  | \$3507                   | I8006                                 | n.a.                            |                                 |

| Processed Encoder #8  | \$3508                   | I8007                                 | n.a.                            |                                 |

| Processed Encoder #9  | \$350B                   | I8008=\$FF8000                        | I8009=\$78800                   | I8010=00                        |

| Processed Encoder #10 | \$350E                   | I80011=\$FF8008                       | I8012=\$78802                   | I8013=00                        |

| Processed Encoder #11 | \$3511                   | I80014=\$FF8010                       | I8015=\$78804                   | I8016=00                        |

| Processed Encoder #12 | \$3514                   | I80017=\$FF8018                       | I8018=\$78806                   | I8019=00                        |

| Processed Encoder #13 | \$3517                   | I8020=\$FF8100                        | I8021=\$78808                   | 18022=00                        |

| Processed Encoder #14 | \$351A                   | I8023=\$FF8108                        | I8024=\$7880A                   | 18025=00                        |

| Processed Encoder #15 | \$351D                   | I8026=\$FF8110                        | I8027=\$7880C                   | 18028=00                        |

The results found in these addresses are 24-bit values. The least significant bit of the result is 1/4096 of a line of the encoder. PMAC software treats the data it reads for the servo loop as having units of 1/32 count, so for software purposes, a count is 1/128 of a line. This can be called a software count to distinguish it from units of the hardware counter. Subsequent calculations such as axis scaling, jog speeds, etc., should use this scaling of 128 (software) counts per line.

These addresses are actually the default addresses used by Turbo PMACs for single-line encoder table references that represent axis 1 through 8. Processed encoders 9 through 12 represent sample entries for an ACC-51S with a Clipper Board.

#### Note:

The encoder table addressing starts at memory location \$3501. Turbo PMAC processes all table entries until it finds a first line entry set to 00 (unused). There must not be any address gaps between the first and last encoder table entry.

#### Note.

Due to timing constraints with the interpolator's conversion processes, the interpolator's encoder conversion table entries should be placed at the contiguous end of the table. The interpolator may place unnecessary wait states back to the Turbo PMAC's processor if the conversion table entries are placed at the beginning of the conversion table.

#### **I-Variables for Clipper Processor**

Refer to the Turbo PMAC Software Reference Manual for a more detailed description of the use of the I-Variables as described below.

To process the interpolator's data properly, several I-Variables must be set:

#### Encoder Decode Control I-Variables (I7mn0)

I7mn0 is used to establish encoder decoding. 'm' is the servo IC number as established by the Acc-51E mapping table (in the previous section); 'n' is the channel number, which is the same as the encoder number (1-4) on the Acc-51S board. The encoder decode control I-variable is set for each channel to which an interpolator is connected.

A value of 7 is used as default for CCW x4 Quadrature decode. Changing the decode direction requires the operator to save the Turbo PMAC's parameters and perform a \$\$\$ or cycle power.

#### Note:

Reset the PMAC if the encoder direction has been changed to prevent encoder instability.

### **Using ACC-51S Data for Commutation Feedback with Clipper**

If using the sinusoidal encoder processed with the ACC-51S for the commutation position feedback, the fully interpolated position value is not used, only the quadrature hardware encoder counter position value which has four counts per line of the encoder. (These can be referred to as hardware counts – units of a hardware counter – to distinguish them from software counts, as explained below.) Motor variable Ix83 must contain the address of the phase position register for that encoder channel. The following table shows the values of Ix83 for each channel:

Ix83 Commutation Encoder Addresses for ACC-51S

| Channel   | Channel   | Channel   | Channel   |

|-----------|-----------|-----------|-----------|

| Entry     | Entry     | Entry     | Entry     |

| 1 \$78001 | 3 \$78011 | 5 \$78101 | 7 \$78111 |

| 2 \$78009 | 4 \$78019 | 6 \$78109 | 8 \$78119 |

#### Motor xx Counts per N Commutation Cycles (Ixx71)

For a Turbo PMAC-commutated motor, this parameter defines the size of a commutation cycle in conjunction with Ixx70 (hardware counts/cycle = Ixx71/Ixx70. For example, if a sinusoidal encoder with 2000 lines is used, Ix71 will be set to 8000 hardware counts.

#### Motor xx Number of Commutation Cycles (N) (Ixx70)

For a PMAC-commutated motor (Ixx01=1), Ixx70 is used in combination with Ixx71 to define the size of the commutation cycle, as Ixx71/Ixx70 counts. For example, a 4-pole rotary brushless motor has a sinusoidal encoder with 2000 lines. There are 8000 hardware counts per revolution, and two commutation cycles per revolution of the 4-pole motor. Therefore, Ix70 will be set to 2, and Ix71 will be set to 8000. Ix83 will contain the address of the hardware counter's phase capture register.

#### Commutation Position I-Variables (Ixx83)

The Acc-51S contains a quadrature-based encoder register that may be used for commutation position. The PMAC2 does not use the Acc-51's full interpolation to track a motor's position.

The number of commutation counts per pole revolution or linear scale distance is related to the pitch of the encoder's sinusoidal output multiplied by 4. Therefore, commutation appears to the PMAC2 as if it were a quadrature-based encoder.

#### **A-D Converter Registers for the Clipper Board**

Ext ADC $_{\rm A}$  and Ext ADC $_{\rm B}$  are addresses to the same A-D converter. When accessed twice, the sine data is followed by the cosine data.

E1 in POS 2-3:

| Description           | Address   |

|-----------------------|-----------|

| Ext ADC1a             | y:\$78800 |

| Ext ADC1B             | y:\$78801 |

| Ext ADC2A             | y:\$78802 |

| Ext ADC2B             | y:\$78803 |

| Ext ADC3A             | y:\$78804 |

| Ext ADC3B             | y:\$78805 |

| Ext ADC4A             | y:\$78806 |

| Ext ADC4 <sub>B</sub> | y:\$78807 |

E1 in POS 1 – 2:

| Description | Address   |

|-------------|-----------|

| Ext ADC5A   | y:\$78808 |

| Ext ADC5B   | y:\$78809 |

| Ext ADC6A   | y:\$7880A |

| Ext ADC6B   | y:\$7880B |

| Ext ADC7A   | y:\$7880C |

| Ext ADC7B | y:\$7880D |

|-----------|-----------|

| Ext ADC8A | y:\$7880E |

| Ext ADC8B | y:\$7880F |

M variable definitions for the ADC read of the first 4 encoders:

M105->Y:\$78800,8,16,s

M106->Y:\$78801,8,16,s

M205->Y:\$78802,8,16,s

M206->Y:\$78803,8,16,s

M305->Y:\$78804,8,16,s

M306->Y:\$78805,8,16,s

M405->Y:\$78806,8,16,s

M406->Y:\$78807,8,16,s

### **OFFSET REGISTER MAPPING DEFINITIONS**

The registers in the table below are located inside the DSPGATE1 on the PC-104 PMAC2 processor board (part number 60370) or on the axis accessory card (part number 603671).

### **DSPGATE1 Registers**

|                 | ADDR         | X –Memory                    | Y-Memory                          |

|-----------------|--------------|------------------------------|-----------------------------------|

|                 | Base $+ 00h$ | Status Word 1                | Time Between Enc Counts (SCLKs)   |

|                 | Base $+ 01h$ | Phase Raw Count 1            | Time Since Last Enc Count (SCLKs) |

|                 | Base $+ 02h$ | Servo Count 1                | PWM A1                            |

| 1 <sup>st</sup> | Base $+ 03h$ | Flag Position Capture 1      | PWM B1                            |

| Channel         | Base $+ 04h$ | Global Clock Control 1-4     | PWM C1                            |

|                 | Base + 05h   | Control Word 1               | ADC1A (serial input)              |

|                 | Base + 06h   | Enc Compare Auto Increment 1 | ADC1B (serial input)              |

|                 | Base $+ 07h$ | Enc Compare Value B1         | Enc Compare Value B1              |

|                 | Base + 08h   | Status Word 2                | Time Between Enc Counts (SCLKs)   |

|                 | Base + 09h   | Phase Raw Count 2            | Time Since Last Enc Count (SCLKs) |

|                 | Base $+ 0Ah$ | Servo Count 2                | PWM A2                            |

| 2 <sup>nd</sup> | Base + 0Bh   | Flag Position Capture 2      | PWM B2                            |

| Channel         | Base + 0Ch   | DAC Strobe Output Word 1-4   | PWM C2                            |

|                 | Base + 0Dh   | Control Word 2               | ADC2A (serial input)              |

|                 | Base + 0Eh   | Enc Compare Auto Increment 2 | ADC2B (serial input)              |

|                 | Base + 0Fh   | Enc Compare Value B2         | Enc Compare Value B2              |

|                 | Base + 10h   | Status Word 3                | Time Between Enc Counts (SCLKs)   |

|                 | Base + 11h   | Phase Raw Count 3            | Time Since Last Enc Count (SCLKs) |

| l ,             | Base + 12h   | Servo Count 3                | PWM A3                            |

| 3 <sup>rd</sup> | Base + 13h   | Flag Position Capture 3      | PWM B3                            |

| Channel         | Base + 14h   | ADC Strobe Output Word 1-4   | PWM C3                            |

|                 | Base + 15h   | Control Word 3               | ADC3A (serial input)              |

|                 | Base + 16h   | Enc Compare Auto Increment 3 | ADC3B (serial input)              |

|                 | Base + 17h   | Enc Compare Value B3         | Enc Compare Value B3              |

|                 | Base + 18h   | Status Word 4                | Time Between Enc Counts (SCLKs)   |

|                 | Base + 19h   | Phase Raw Count 4            | Time Since Last Enc Count (SCLKs) |

|                 | Base + 1Ah   | Servo Count 4                | PWM A4                            |

| 4 <sup>th</sup> | Base + 1Bh   | Flag Position Capture 4      | PWM B4                            |

| Channel         | Base $+ 1Ch$ | PWM Freq/Dead time/PFM Width | PWM C4                            |

|                 |              | 1-4                          |                                   |

|                 | Base + 1Dh   | Control Word 4               | ADC4A (serial input)              |

|                 | Base + 1Eh   | Enc Compare Auto Increment 4 | ADC4B (serial input)              |

|                 | Base + 1Fh   | Enc Compare Value B4         | Enc Compare Value B4              |

Base address of DSPGATE1 on PMAC2A-PC/104 is \$C000. Base address of DSPGATE1 on ACC-1P is \$C020.

### **Viewing Actual Encoder Position**

When using the PMAC executive program to view position, the data returned from the PMAC does not include the fractional part. The following information will show how to display the complete position information in a watch window.

As a sub-count interpolator device, the interpolator input is seen as a whole number counter with three fractional digits. There are 32 sub-steps that occur per single whole number step. Each change of the data is seen by PMAC as 1/32th (0.03125) count. Since PMAC uses fractional arithmetic, the result will be represented with a resolution to 1/32 of a whole number step.

Refer to the recommended M-Variable definitions for Mx62 assignments. There should be a M-Variable assigned for each axis to be displayed. This variable points to the encoder actual position register.

Write a PLC that includes the following equation for each axis to be displayed as follows:

$$Px = Mx62 / (Ix08 * 32)$$

Where:

Ix08 is the gearing value for a particular axis (typically = 96)

Px is an available P-Variable.

Mx62 is a pointer PMAC's actual position register.

Note:

Normally (Ix08 \* 32) may be precalculated since gearing is not changed during program operation.

Put Px into the watch window. The value displayed should be the actual position including the fractional data.

#### **A-D Converter Registers**

Ext  $ADC_A$  and Ext  $ADC_B$  are addresses to the same A-D converter. When accessed twice, the sine data is followed by the cosine data.

E1 in POS 2-3:

| Description           | Address  |

|-----------------------|----------|

| Ext ADC1 <sub>A</sub> | y:\$ffc0 |

| Ext ADC1 <sub>B</sub> | y:\$ffc1 |

| Ext ADC2 <sub>A</sub> | y:\$ffc2 |

| Ext ADC2 <sub>B</sub> | y:\$ffc3 |

| Ext ADC3 <sub>A</sub> | y:\$ffc4 |

| Ext ADC3 <sub>B</sub> | y:\$ffc5 |

| Ext ADC4 <sub>A</sub> | y:\$ffc6 |

| Ext ADC4 <sub>B</sub> | y:\$ffc7 |

E1 in POS 1 – 2:

| Description           | Address  |

|-----------------------|----------|

| Ext ADC5 <sub>A</sub> | y:\$ffc8 |

| Ext ADC5 <sub>B</sub> | y:\$ffc9 |

| Ext ADC6 <sub>A</sub> | y:\$ffca |

| Ext ADC6 <sub>B</sub> | y:\$ffcb |

| Ext ADC7 <sub>A</sub> | y:\$ffcc |

| Ext ADC7 <sub>B</sub> | y:\$ffcd |

| Ext ADC8 <sub>A</sub> | y:\$ffce |

| Ext ADC8 <sub>B</sub> | y:\$ffcf |

### **CONNECTOR DESCRIPTIONS**

### **J7 JMACH1 Encoder Quadrature Outputs**

Typically, this connector is connected to JMACHA port on PMAC2A-PC104 baseboard (603670) or axis card (603671) with a 26-pin flat cable.

| J7: JMACH1 – ENC Quadrature Outputs (26-pin Header) |        |          | 25<br>26 1<br>2 2<br>Front View |                       |

|-----------------------------------------------------|--------|----------|---------------------------------|-----------------------|

| Pin #                                               | Symbol | Function | Description                     | Notes                 |

| 1                                                   | +5V    | Vcc      | Power Supply                    | To JMACHA pin1 +5V    |

| 2                                                   | +5V    | Vcc      | Power Supply                    | To JMACHA pin2 +5V    |

| 3                                                   | GND    | Common   | Power Supply Return             | To JMACHA pin3 GND    |

| 4                                                   | GND    | Common   | Power Supply Return             | To JMACHA pin4 GND    |

| 5                                                   | AQUAD1 | Output   | Phase A quadrature output       | To JMACHA pin5 CHA1+  |

| 6                                                   | AQUAD2 | Output   | Phase A quadrature output       | To JMACHA pin6 CHA2+  |

| 7                                                   | N.C.   |          | Not Connected                   | To JMACHA pin7 CHA1-  |

| 8                                                   | N.C.   |          | Not Connected                   | To JMACHA pin8 CHA2-  |

| 9                                                   | BQUAD1 | Output   | Phase B quadrature output       | To JMACHA pin9 CHB1+  |

| 10                                                  | BQUAD2 | Output   | Phase B quadrature output       | To JMACHA pin10 CHB2+ |

| 11                                                  | N.C.   |          | Not Connected                   | To JMACHA pin11 CHB1- |

| 12                                                  | N.C.   |          | Not Connected                   | To JMACHA pin12 CHB2- |

| 13                                                  | Index1 | Output   | Index output                    | To JMACHA pin13 CHC1+ |

| 14                                                  | Index2 | Output   | Index output                    | To JMACHA pin14 CHC2+ |

| 15                                                  | N.C.   |          | Not Connected                   | To JMACHA pin15 CHC1- |

| 16                                                  | N.C.   |          | Not Connected                   | To JMACHA pin16 CHC2- |

| 17                                                  | AQUAD3 | Output   | Phase A quadrature output       | To JMACHA pin17 CHA3+ |

| 18                                                  | AQUAD4 | Output   | Phase A quadrature output       | To JMACHA pin18 CHA4+ |

| 19                                                  | N.C.   |          | Not Connected                   | To JMACHA pin19 CHA3- |

| 20                                                  | N.C.   |          | Not Connected                   | To JMACHA pin20 CHA4- |

| 21                                                  | BQUAD3 | Output   | Phase B quadrature output       | To JMACHA pin21 CHB3+ |

| 22                                                  | BQUAD4 | Output   | Phase B quadrature output       | To JMACHA pin22 CHB4+ |

| 23                                                  | N.C.   |          | Not Connected                   | To JMACHA pin23 CHB3- |

| 24                                                  | N.C.   |          | Not Connected                   | To JMACHA pin24 CHB4- |

| 25                                                  | Index3 | Output   | Index output                    | To JMACHA pin25 CHC3+ |

| 26                                                  | Index4 | Output   | Index output                    | To JMACHA pin26 CHC4+ |

Connector Descriptions 23

### J9, J10, J11, J12 Encoder Inputs

These encoder connections use a 9-pin DSUB connector and provide accessibility through the rear of the computer.

J9 is for the first channel input and J10 is the second channel input.

J11 is for the third channel input and J12 is the fourth channel input, when option 1 is ordered.

| J9 (9-Pin DB9S Connector) |           | Top View (6, 9) |                      |                        |

|---------------------------|-----------|-----------------|----------------------|------------------------|

| Pin #                     | Symbol    | Function        | Description          | Notes                  |

| 1                         | SIN 1 +   | Analog Input    | Sinusoidal input+    |                        |

| 2                         | COS 1 +   | Analog Input    | Cosine input+        |                        |

| 3                         | INDEX 1 + | Input           | Index input          | Analog or TTL levels   |

| 4                         | ENCPWR    | Output          | Encoder power        | +5Vdc or user supplied |

| 5                         | GND       |                 | Digital ground       |                        |

| 6                         | SIN 1 -   | Analog Input    | Sinusoidal input-    |                        |

| 7                         | COS 1 -   | Analog Input    | Cosine input-        |                        |

| 8                         | INDEX 1 - | Input           | Index input          | Analog or TTL levels   |

| 9                         | VREF      | 2.5V Output     | A-D reference output |                        |

| J10 (9-Pin DB9S Connector) |           | Top View (6, 9) |                      |                        |

|----------------------------|-----------|-----------------|----------------------|------------------------|

| Pin #                      | Symbol    | Function        | Description          | Notes                  |

| 1                          | SIN 2 +   | Analog Input    | Sinusoidal input+    |                        |

| 2                          | COS 2 +   | Analog Input    | Cosine input+        |                        |

| 3                          | INDEX 2 + | Input           | Index input          | Analog or TTL levels   |

| 4                          | ENCPWR    | Output          | Encoder power        | +5Vdc or user supplied |

| 5                          | GND       |                 | Digital ground       |                        |

| 6                          | SIN 2 -   | Analog Input    | Sinusoidal input-    |                        |

| 7                          | COS 2 -   | Analog Input    | Cosine input-        |                        |

| 8                          | INDEX 2 - | Input           | Index input          | Analog or TTL levels   |

| 9                          | VREF      | 2.5V Output     | A-D reference output |                        |

| J11 (9-Pin DB9S Connector) |           | Top View (6, 9) |                      |                        |

|----------------------------|-----------|-----------------|----------------------|------------------------|

| Pin #                      | Symbol    | Function        | Description          | Notes                  |

| 1                          | SIN 3 +   | Analog Input    | Sinusoidal input+    |                        |

| 2                          | COS 3 +   | Analog Input    | Cosine input+        |                        |

| 3                          | INDEX 3 + | Input           | Index input          | Analog or TTL levels   |

| 4                          | ENCPWR    | Output          | Encoder power        | +5Vdc or user supplied |

| 5                          | GND       |                 | Digital ground       |                        |

| 6                          | SIN 3 -   | Analog Input    | Sinusoidal input-    |                        |

| 7                          | COS 3 -   | Analog Input    | Cosine input-        |                        |

| 8                          | INDEX 3 - | Input           | Index input          | Analog or TTL levels   |

| 9                          | VREF      | 2.5V Output     | A-D reference output |                        |

| J12 (9-Pin DB9S Connector) |           | Top View (69) |                      |                        |

|----------------------------|-----------|---------------|----------------------|------------------------|

| Pin #                      | Symbol    | Function      | Description          | Notes                  |

| 1                          | SIN 4 +   | Analog Input  | Sinusoidal input+    |                        |

| 2                          | COS 4 +   | Analog Input  | Cosine input+        |                        |

| 3                          | INDEX 4 + | Input         | Index input          | Analog or TTL levels   |

| 4                          | ENCPWR    | Output        | Encoder power        | +5Vdc or user supplied |

| 5                          | GND       |               | Digital ground       |                        |

| 6                          | SIN 4 -   | Analog Input  | Sinusoidal input-    |                        |

| 7                          | COS 4 -   | Analog Input  | Cosine input-        |                        |

| 8                          | INDEX 4 - | Input         | Index input          | Analog or TTL levels   |

| 9                          | VREF      | 2.5V Output   | A-D reference output |                        |

### **TB1 User Supplied Power**

Use this 2-pin connector to provide power externally.

Jumper E2 allows external power to be provided to the encoders through pin 4 and pin 5 on J9, J10, J11 and J12.

| Pin # | Symbol | Function | Description         | Notes                                                                  |

|-------|--------|----------|---------------------|------------------------------------------------------------------------|

| 1     | GND    | GND      | Power Supply Return |                                                                        |

| 2     | +Vdc   | +Vdc     | External ENC power  | E2 must be 2-3. This power must be suitable for encoder specification. |

Connector Descriptions 25

### **JUMPER CONFIGURATIONS**

#### **Table of Jumpers**

| Nomenclature  | Physical  | Description                       | Factory |

|---------------|-----------|-----------------------------------|---------|

|               | Layout    | •                                 | Default |

| E1            | 1 - 2 - 3 | Select card address.              | 2-3     |

|               |           | 1 - 2 addressing as second card   |         |

|               |           | 2 - 3 addressing as first card    |         |

| E2            | 1 - 2 - 3 | Encoder Power                     | 1-2     |

|               |           | 1 - 2 Use internal 5V             |         |

|               |           | 2 - 3 Use external power supply.  |         |

|               | 1 - 2 - 3 | Channel 1                         | 2-3     |

| E3, E4,E5     |           | 1 - 2 Unterminated encoder inputs |         |

|               |           | 2 - 3 Terminated encoder inputs   |         |

|               |           | (E5 is index termination)         |         |

| E6, E7, E8    | 1 - 2 - 3 | Channel 2                         | 2-3     |

|               |           | 1 – 2 Unterminated encoder inputs |         |

|               |           | 2-3 Terminated encoder inputs     |         |

|               |           | (E8 is index termination.)        |         |

| E9, E10, E11  | 1 - 2 - 3 | Channel 3 (opt 1 only)            | 2 - 3   |

|               |           | 1 − 2 Unterminated encoder inputs |         |

|               |           | 2 – 3 Terminated encoder inputs   |         |

|               |           | (E11 is index termination.)       |         |

| E12, E13, E14 | 1 - 2 - 3 | Channel 4 (opt 1 only)            | 2 - 3   |

|               |           | 1 – 2 Unterminated encoder inputs |         |

|               |           | 2 – 3 Terminated encoder inputs   |         |

|               |           | (E14 is index termination.)       |         |

#### E1 - Select Card Address

This jumper selects this care address if this card is set as first or second address.

#### **E2 - Encoder Power Select**

This jumper allows the use of internal Vcc (+5Vdc) to provide power to the encoders. External encoder power may be provided through Pin 2 on TB1 connector.

#### E3, E4, E5, E6, E7, E8 - Encoder Input Select Channel 1 and 2

Use these jumpers to select which type of input loading will be used for the encoder. A  $120\Omega$  termination is selectable. The inputs are approximately  $17k\Omega$  when not terminated.

# E9, E10, E11, E12, E13, E14 - Encoder Input Select (Option 1- add 2 Channels)

Use these jumpers to select which type of input loading will be used for the encoder. A  $120\Omega$  termination is selectable. The inputs are approximately  $17K\Omega$  when not terminated.

Jumper Configurations 27