# Design and implementation of the ELIQ Smart-plug system device

Master of Science Thesis in the Master Degree Programme

Embedded Electronic System Design

Yixin Liu

Department of Computer Science and Engineering

CHALMERS UNIVERSITY OF TECHNOLOGY

Göteborg, Sweden, 2014

The Author grants to Chalmers University of Technology and University of Gothenburg the non-exclusive right to publish the Work electronically and in a non-commercial purpose make it accessible on the Internet.

The Author warrants that he/she is the author to the Work, and warrants that the Work does not contain text, pictures or other material that violates copyright law.

The Author shall, when transferring the rights of the Work to a third party (for example a publisher or a company), acknowledge the third party about this agreement. If the Author has signed a copyright agreement with a third party regarding the Work, the Author warrants hereby that he/she has obtained any necessary permission from this third party to let Chalmers University of Technology and University of Gothenburg store the Work electronically and make it accessible on the Internet.

Design and implementation of the Smart-plug device system design Master of Science Thesis in the Master Degree Programme Embedded Electronic System Design

Yixin Liu

© Yixin Liu, July 2014.

Examiner: Per Larsson-Edefors

Chalmers University of Technology University of Gothenburg Department of Computer Science and Engineering SE-412 96 Göteborg Sweden Telephone + 46 (0)31-772 1000

[Cover: an explanatory caption for the (possible) cover picture with page reference to detailed information in this essay.]

Department of Computer Science and Engineering Göteborg, Sweden July 2014

### Abstract

The company Exibea AB plans to design and implement a new product called ELIQ Smart-plug device to help the households control the energy consumption at home more conveniently and intelligently. The expected function of the ELIQ Smart-plug device is to measure the power consumption value of the connected electrical appliance, send the measured value to the ELIQ Display Unit through RF wireless communication, switch on or switch off the power supply to the connected electrical appliance automatically and repeat the received ELIQ protocol RF message to work as a wireless repeater for other ELIQ devices in the company.

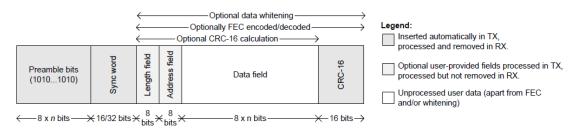

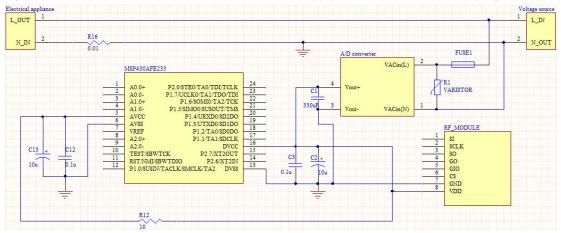

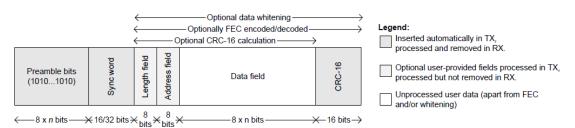

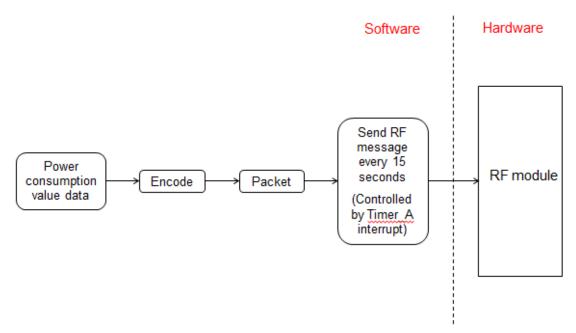

This master thesis explores the design process and the implementation method of the ELIQ Smart-plug system device including both of the hardware part and software part in depth. MSP430AFE233 is chosen to be the microcontroller unit used on the Smart-plug electrical board to control the whole system. In order to calculate the power consumption value, the RMS (Root Mean Square) values of both of the voltage and current on the connected appliance should be measured firstly, then the power consumption value will be obtained easily by multiplying the voltage RMS value and the current RMS value. The calculated power consumption value will be encoded and combined with some other specified bits such as preamble bits and header bits together into a data packet according to the ELIQ protocol. The data packet will be transmitted to the RF module on the Smart-plug electrical board through SPI communication firstly, then the wireless communication between the antenna of this RF module and the antenna of another RF module on the ELIQ Display Unit board will be implemented. The power consumption value will be displayed on the ELIQ Display Unit device to show the households the transient power consumption of the connected electrical appliance. The Smart-plug device can also switch on or switch off the power supply to the appliance automatically according to the measured power consumption value to achieve the aim of energy-saving in a house. In addition, this Smart-plug device system can repeat the received RF message from other ELIQ devices and then send the same RF message to the ELIQ Display Unit or the ELIQ Hub to work as a wireless repeater in order to extend the wireless transmission distance and amplify the power of the signal.

Furthermore, the comparison of selecting components for the Smart-plug electrical board and some important attentions need to be considered in both of the hardware design and software design are discussed in this master thesis.

The ELIQ Smart-Plug Design

## Acknowledgement

It is my pleasure to show my gratitude towards everyone who supported me during my master thesis.

Firstly, I would like to thank the company Exibea AB for offering this master thesis opportunity and especially Hakan Ludvigsson who was my supervisor at the company. He is very pleasant to work with. He provided me a good working environment and helped a lot about the component selection and producing the PCB board. Also I would give thanks to Olof Hartelius and Johan Salin at the company who were available for answering my questions and shared many technical knowledge and experience with me together.

I would like to acknowledge the helps from Per Larsson-Edefors, who was my supervisor and examiner at Chalmers University of Technology. He gave me a lot of valuable advice, feedback and comments about how to write this master thesis.

A special thanks to my parents and my girlfriend, who encouraged me a lot when I encountered with some difficulties in this master thesis project and provided me great impetus to overcome these difficulties.

Finally, I also appreciate for the effort that my master thesis opponent, Gongpei Cui made. His criticism and questions opened my eyes for the weak points in my master thesis.

The ELIQ Smart-Plug Design

### List of Abbreviations

- AC Alternating Current

- ACLK Auxiliary Clock

- A/D Analog to Digital

- ADC Analog to Digital Converter

- BCSCTLx Basic Clock System Control Register x

- CPU Central Processor Unit

- CS Chip Selection

- DC Direct Current

- DCO Digitally Controlled Oscillator

- EDA Electronic Design Automation

- FIFO First Input First Output

- FSR Full Scale Range

- GDO General Digital Output

- GFSK Gaussian Frequency-Shift Keying

- GIO General Input/Output

- GO General Output

- GUI Graphic User Interface

- I/O Input or Output

- ISR Interrupt Service Routine

- ISM Industrial, Scientific and Medical

- JTAG Joint Test Action Group

- LED Light Emitting Diode

- MCLK Main System Clock

- MCU Microcontroller Unit

- MSP Mixed Signal Processor

- NPN transistor Negative-Positive-Negative Transistor

- OSR Oversampling Ratio

- PCB Printed Circuit Board

- PWM Pulse Width Modulation

- PxDIR Px Direct Register

- PxIE Px Interrupt Enable Register

- PxIES Px Interrupt Edge Select Register

- PxIFG Px Interrupt Flag Register

- PxIN Px Input Register

- PxOUT Px Output Register

- PxREN Px Pullup/Pulldown Resistor Register

- RAM Random Memory

- RF Radio Frequency

- RISC Reduced Instruction Set Computer

- RMS Root Mean Square

- RX Receive, Receive Mode

- SCLK Serial Clock

- SD24\_A A/D Converter 24-bit sigma-delta Analog to Digital Converter

- SD24CTL SD24 Control Register

- SD24INTCTLx SD24 Channel x Input Control Register

- SD24CCTLx SD24 Channel x Control Register

- SD24MEMx SD24 Channel x Conversion Memory Register

- SI Serial Input

- SMCLK Sub Main System Clock

- SMD Surface Mounted Device

- SO Serial Output

- SPI Serial Peripheral Interface

- SPST Single Pole Single Throw

- SRAM Static Random Memory

- TACCRx Timer\_A Capture/Compare Register x

- TACCTLx Timer\_A Capture/Compare Control Register x

- TACTL Timer\_A Control Register

- TAR Timer\_A Counter Register

- TX Transmit, Transmit Mode

- UART Universal Asynchronous Receiver/Transmitter

- USART Universal Synchronous/Asynchronous Receiver/Transmitter

- USB Universal Serial Bus

- VCO Voltage Controlled Oscillator

- WDT Watchdog Timer

- WWF World Wide Fund for Nature

- XTAL Crystal

### **Table of Contents**

| 1. | Introduction                                                             | 1  |

|----|--------------------------------------------------------------------------|----|

|    | 1.1 Background                                                           | 1  |

|    | 1.2 Problem statement                                                    | 1  |

|    | 1.3 Specification                                                        | 2  |

|    | 1.4 Purpose                                                              | 2  |

|    | 1.5 Subcomponents                                                        | 2  |

|    | 1.6 Project procedure                                                    | 3  |

|    | 1.7 Scope                                                                | 3  |

|    | 1.8 Limitations                                                          | 3  |

|    | 1.9 Thesis outline                                                       | 3  |

| 2. | Theory                                                                   | 5  |

|    | 2.1 Basic design principle                                               | 5  |

|    | 2.2 Selection of MCU                                                     | 6  |

|    | 2.3 Introduction of MSP430AFE233                                         | 7  |

|    | 2.3.1 Description                                                        | 7  |

|    | 2.3.2 Features                                                           | 7  |

|    | 2.3.3 Digital I/O ports                                                  | 8  |

|    | 2.3.3.1 Digital I/O ports input register PxIN                            | 9  |

|    | 2.3.3.2 Digital I/O ports output register PxOUT                          | 9  |

|    | 2.3.3.3 Digital I/O ports direction register PxDIR                       | 9  |

|    | 2.3.3.4 Digital I/O ports pullup/pulldown resistor enable register PxREN | 9  |

|    | 2.3.3.5 Digital I/O ports interrupts                                     | 10 |

|    | 2.3.4 Basic clock module                                                 | 10 |

|    | 2.3.4.1 Basic clock module structure                                     | 10 |

|    | 2.3.4.2 Basic clock module registers                                     | 11 |

|    | 2.3.5 Timer_A                                                            | 12 |

|    | 2.3.5.1 Timer_A structure                                                | 12 |

|    | 2.3.5.2 Timer_A registers                                                | 13 |

|    | 2.3.6 SD24_A                                                             | 15 |

|    | 2.3.6.1 SD24_A structure                                                 | 15 |

|    | 2.3.6.2 SD24_A registers                                                 | 16 |

|    | 2.3.6.3 Analog-to-digital conversion in SD24_A                           |    |

|    | 2.3.6.4 Digital filter in SD24_A                                         | 19 |

| 3. | Materials                                                                | 21 |

|    | 3.1 Hardware components                                                  | 21 |

|    | 3.1.1 MCU                                                                | 21 |

|    | 3.1.2 RF module                                                          | 21 |

|    | 3.1.3 AC/DC Converter                                                    | 25 |

|    | 3.1.4 Relay                                                              | 25 |

|    | 3.1.5 NPN transistor                                                     | 26 |

|    | 3.1.6 Crystal                                                            | 26 |

|    | 3.1.7 Other components                                                   | 27 |

|     | 3.2 Software tools                                                             |           |

|-----|--------------------------------------------------------------------------------|-----------|

|     | 3.2.1 Altium Designer 6                                                        | 28        |

|     | 3.2.2 Switcher CAD III                                                         | 28        |

|     | 3.2.3 IAR Embedded Workbench                                                   | 28        |

|     | 3.2.4 Lite Fet-Pro430 MSP430 flash programmer                                  | 28        |

| 4.  | Hardware design                                                                |           |

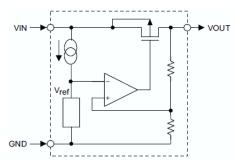

|     | 4.1 Power supply circuit design                                                |           |

|     | 4.2 Voltage sampling circuit design                                            | 31        |

|     | 4.3 Current sampling circuit design                                            | 32        |

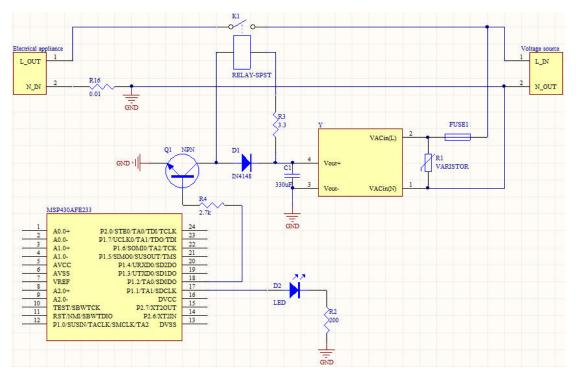

|     | 4.4 Switching on/off control unit circuit design                               | 35        |

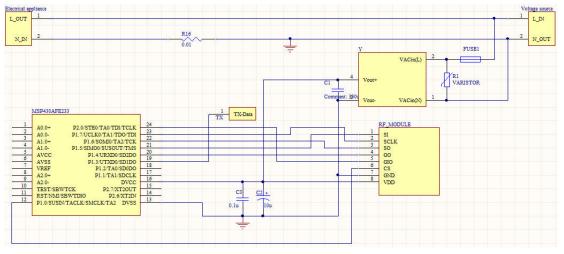

|     | 4.5 Communication between MCU and RF module                                    |           |

| 5.  | Software design methodology                                                    |           |

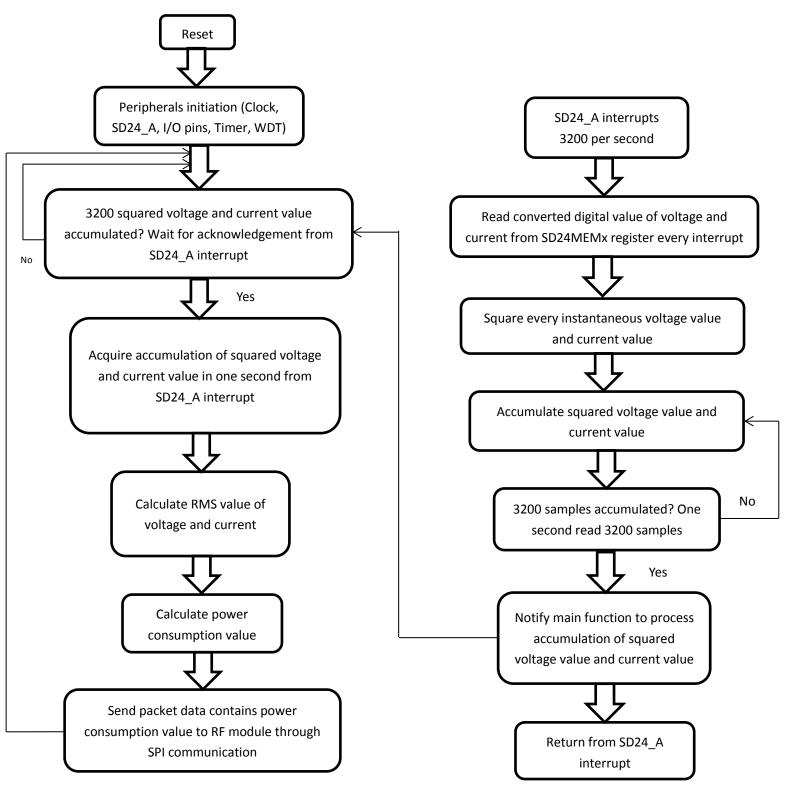

|     | 5.1 Power consumption value calculation                                        | 40        |

|     | 5.1.1 Peripherals initiation in MSP430AFE233                                   | 40        |

|     | 5.1.1.1 Clock system initiation                                                | 40        |

|     | 5.1.1.2 I/O ports initiation                                                   | 41        |

|     | 5.1.1.3 SD24_A A/D converter initiation                                        | 43        |

|     | 5.1.1.3.1 Configuring sampling frequency                                       | 43        |

|     | 5.1.1.3.2 Configuring analog-to-digital conversion parameters                  | 44        |

|     | 5.1.1.4 Timer_A initiation                                                     | 47        |

|     | 5.1.2 Sampling voltage and current value in one second                         | 49        |

|     | 5.1.3 RMS value calculation for voltage and current                            | 50        |

|     | 5.1.4 Power consumption value calculation                                      | 52        |

|     | 5.2 Control switch on or off status of connected appliance                     | 52        |

|     | 5.3 SPI communication to RF module                                             | 53        |

|     | 5.4 Wireless communication                                                     | 54        |

|     | 5.5 Working as a repeater                                                      | 55        |

| 6.  | Visual support                                                                 | 57        |

| 7.  | Results                                                                        | 59        |

| 8.  | Discussion                                                                     | 60        |

|     | 8.1 Appliance with small power consumption cannot be measured accurately       | 60        |

|     | 8.2 Sampling resistor with resistance tolerance 1% still influences the active | curacy of |

|     | measurement                                                                    | 61        |

|     | 8.3 Component selection for the control unit                                   | 62        |

|     | 8.4 A/D converter output need load                                             | 63        |

|     | 8.5 Acquiring relay components                                                 | 63        |

|     | 8.6 Width and thickness of the copper wire on the PCB board                    | 65        |

| 9.  | Conclusion                                                                     | 66        |

|     | 9.1 Summary                                                                    | 66        |

|     | 9.2 Future work                                                                | 66        |

| Bib | liography                                                                      | 68        |

## 1. Introduction

## 1.1 Background

Over the last decade, energy saving has been a hot topic across the whole world. Households always find it difficult to plan and handle their energy consumption at home. Unnecessary use of energy is not only an environmental issue but also affects the economy negatively for the consumers.

The company Exibea AB was founded in 2008 in Gothenburg, Sweden, with a focus on providing products to help the consumers to control and reduce their energy consumption. Now the company is planning to design and implement a new product called ELIQ Smart-plug device. This device is expected to detect the energy use and display the measured value on the company's flagship products ELIQ Energy Display Unit or ELIQ Energy Online to provide feedback to the consumers [1][2]. The Smart-plug device will be inserted between the power outlet and any household appliance to measure the energy use and switch on/off the power supply to the connected appliance, which can be also controlled by the user from the ELIQ Energy Online web GUI or the remote mobile phone, allowing the user to set up power on/off scheduling based on the current electricity price, room temperature or other parameters to help facilitating a more energy-conservative lifestyle.

## 1.2 Problem statement

Energy consumption in the world is on the rise, leading to a non-sustainable society in the long run. Lack of energy is a serious challenge for human beings in the future. Today the government in almost every country formulates a strategy to reduce the energy consumption in every field of the society. It is not only a matter for governments, but also boils down to a matter for every citizen of Earth: We all have the responsibility to save the electric energy in daily life in order to provide an ecological and sustainable society [3] for the coming generations.

Although electricity does not create any pollution where it is used, there may be carbon dioxide emission and other environmentally negative substances coming out at the production site. The WWF (World Wide Fund for Nature) states that if the carbon dioxide emission is kept on the same level as today, the global temperature will increase two degrees Celsius, which will lead to the severe global warming crisis and then a series of natural disasters in the world [4]. Wind power and hydropower almost do not produce any carbon dioxide emission, however, they can still create other negative environmental problems such as the disrupted water flows.

In order to create an ecological society, the electricity energy consumption of households is an important concern. Household energy consumption accounts for about 25% of the total energy consumption in the world [5]. One of the effective ways to decrease electricity energy consumption in households is by increasing consumers' awareness as people at least in the past have been careless about lowering electricity energy consumption even though lowering

electricity energy consumption could reflect well on their household budget.

Taking steps towards achieving the ecological and smart home, the new product ELIQ Smart-plug device which the company Exibea AB plans to develop is expected to manage home electricity energy consumption. This Smart-plug device system can provide functions such as measurement and visualization of the home energy consumption and automatic switch on/off control for home electrical appliances. In addition, it can be also connected to the network of a smart home to achieve efficient ecological operation.

Since the envisioned Smart-plug device is a new concept, this master thesis project work is concerned with conceiving, implementing, integrating and evaluating a Smart-plug device based on the different off-the-shelf subcomponents.

## **1.3 Specification**

The ELIQ Smart-plug device should provide the following functions:

- Measure the power consumption value of the connected appliances and send the value once every 15 seconds to the ELIQ Energy Display Unit or the ELIQ Energy Online web GUI through the ELIQ Hub to display to the households with using the RF-module in 868 MHz ISM band

- Switch on/off power supply to the connected appliances according to the measured power consumption value or by the user from the ELIQ Energy Online web GUI and indicate on/off status

- Repeat received ELIQ protocol RF communication, making the device work as a wireless extender or repeater for other ELIQ devices

## 1.4 Purpose

With the measurement and visualization of the home energy consumption by using this Smart-plug device system, the households can know the energy consumption value in a room instantly and directly then can manage the energy use of the house easily and conveniently. The automatic switch on/off control for the home appliances can achieve the automatic reduction of the household energy consumption. The hope is that with the help of this Smart-plug device system, household energy consumption can be lowered significantly, leading to not only better household economy but also to a sustainable society.

## 1.5 Subcomponents

The subcomponents the company has access to in this project are resistors, capacitors, diodes, relay, switching power supply device, ferrite beads, transient voltage suppressor, NPN transistor, crystal, fuse, varistor, LED, MCU, RF module, PCB board, plug and so on. The PCB board will be manufactured by the PCB factory according to the designed circuit drawn by the specified EDA software tool then the electrical subcomponents will be soldered on the PCB board. The Smart-plug board will be connected to a plug to be inserted between the power outlet and the

household appliance. The tools multimeter, soldering iron and soldering tin will be used to implement integrating these different off-the-shelf subcomponents into one testing product.

## 1.6 Project procedure

The electrical board of the Smart-plug device should be designed and implemented for testing before the products in mass production, including both hardware design and software design. For the hardware part, the electrical circuit design including the prototyping design and the selection of the MCU and other suitable off-the-shelf components should be completed firstly. Then the schematic and the PCB layout will be done by the specialized EDA tool. After the PCB board is produced by the factory, soldering the components on the PCB board will be the following step. The software task is to make programming for the MCU on the Smart-plug board to make the Smart-plug device achieve the expected targets successfully.

## 1.7 Scope

The knowledge of this master thesis is related to the fields of analog circuit, digital circuit, A/D mixed signal system, microcontroller unit, C code programming and wireless communication.

## 1.8 Limitations

There are some parts of this master thesis project left out due to the time reason. For instance, the power supply circuit that drives the MCU, the RF module and the relay will not be designed within this master thesis project work. Instead, a switching power supply device which can transfer the 230V AC input from the mains to the 3.3V DC output to be the working supply voltage is bought as the off-the shelf subcomponent. Since this temporary switching power supply device is quite expensive and bulky, the final product in mass production will need a different power solution on the Smart-plug electrical board to reduce cost and size. Secondly, the wireless communication between the Smart-plug board and the ELIQ Energy Unit board or the ELIQ Energy Hub does not need to be considered since this procedure is already done by the company Exibea AB according to the company's own RF protocol. In addition, on the ELIQ Energy Unit board, the procedure of decoding received data packet and displaying the value on the LCD display needs not to be mentioned as it has been also completed by the company.

Furthermore, the size, the exterior, the package, the manufacture, the process technology and the arts and crafts of the final product have also not been considered as the aim of this master thesis project is just designing a prototype.

## 1.9 Thesis outline

Chapter 2 introduces the theory of the basic design principle firstly, then the selection of the suitable type of MCU and the basic knowledge of the selected MCU are described in detail. That is vital for the readers to understand the following electrical circuits design and configurations in software. Then, chapter 3 introduces the materials used in this project, including both of the

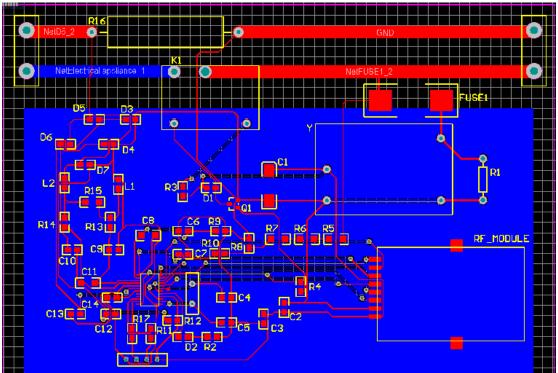

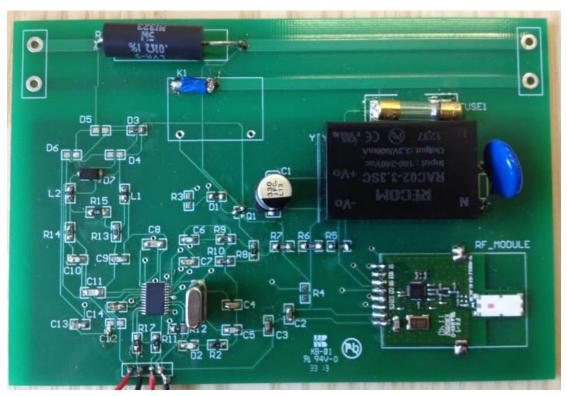

hardware tools and software tools. In chapter 4, the specific methodology of the hardware design is elaborated. The software methodology design including the software design process flowchart, the system setup initiation and the implementation of some special applications are described step by step in chapter 5. Some important graphs such as the schematic of the whole electrical circuits inside the Smart-plug device, the PCB layout of the Smart-plug electrical board and the real photo of this electrical board are presented to be the visual support for this master thesis in chapter 6. Chapter 7 will show the results of this project to the readers. In chapter 8, some issues such as the comparison of suitable selection for the control unit component or some conditions need be considered during the design will be discussed. Finally, in chapter 9, the findings and insights from this project will be reviewed overall.

# 2. Theory

## 2.1 Basic design principle

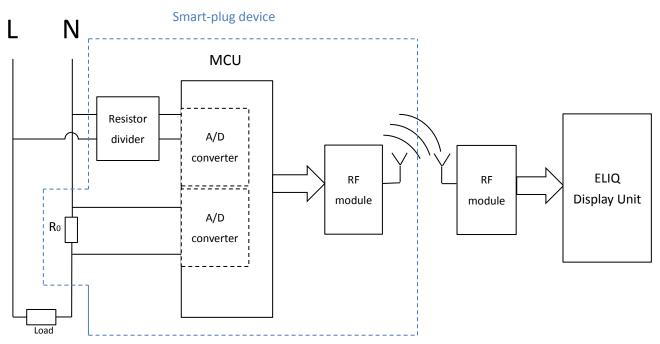

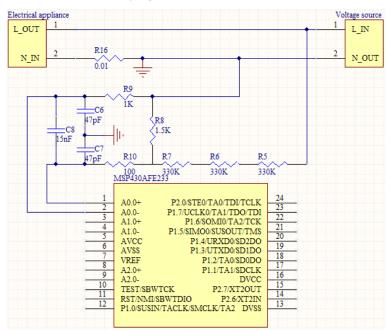

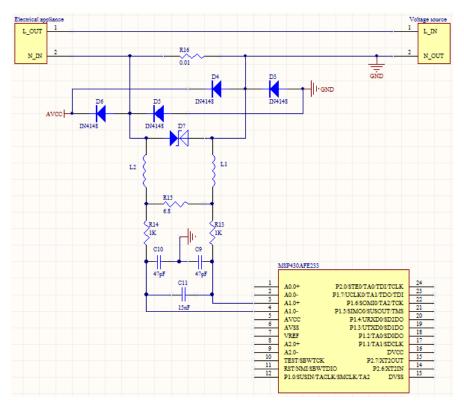

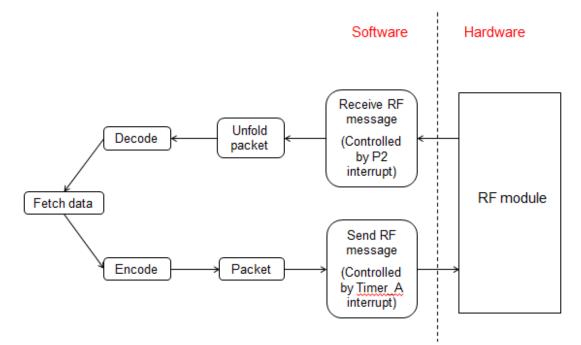

The basic design principle diagram of the Smart-plug device system is shown in Figure 2.1 below.

Figure 2.1 The diagram of the basic design of the Smart-plug system

As can be seen from Figure 2.1 above clearly, L means the live wire and N means the neutral wire from the household mains respectively. As the Smart-plug device needs to measure the power consumption value of the electrical appliance, the value of the current on the live wire and neutral wire of the circuit inside the smart-plug can be measured firstly in order to calculate the power consumption. R0 is a resistor with small resistance value set on the neutral wire of the circuit as the sampling resistor. The voltage value on R0 can be measured by connecting both sides of the resistor to the A/D converter module of the MCU. If the voltage on R0 is known, then the current value on the electrical appliance is easy to obtain by dividing the R0 resistance value. Load means the load resistor of the electrical appliance connected to the Smart-plug device. The voltage on the electrical appliance can also be measured by the A/D converter module of the MCU. The resistor divider circuitry needs to be added between Live, neutral wire and the MCU since the A/D converter of the MCU can only be convert small voltage values.

After sampling signal values during a specific time interval, both of the current effective value and voltage effective value on the electrical appliance can be calculated using the sampled value captured from the A/D converter, then the power consumption value can be calculated by multiplying the effective voltage value and the effective current value. The power consumption value will be transmitted to the ELIQ Display Unit via the respective RF module on both of the Smart-plug board and the ELIQ Energy Display Unit board.

In European countries, the voltage from the household mains is 230V AC. Since this Smart-plug device is designed mainly for the market of the European countries, the design of the circuit is based on the mains voltage equals to 230V AC. As the effective voltage value 230V from the mains in European countries is almost highest among that across the world, the hardware circuit design discussed in the later chapters will be also suitable for use in other regions outside Europe.

## 2.2 Selection of MCU

A series of considerations are necessary to choose the type of MCU. As the product size limitation and thermal regulation needs to be considered, the Texas Instruments MSP430 series ultra-low-power microcontrollers are the first choice for the company since these types of MCU possess the features of small size and ultra-low-power [6].

Initially, the MSP430F21x2 family MCUs, the MSP430G2x33 family MCUs and the MSP430AFE2x3 family MCUs have been considered to be the selections of the control MCU on the Smart-plug electrical board in this project. Since the voltage from the household mains is alternating from outside, the voltage on the sampling resistor is also alternating. The A/D converter in many types of MCU such as the MSP430F21x2 family MCUs and the MSP430G2x33 family MCUs can only detect the positive voltage value and the reference voltage on the A/D module is also positive value as same as the supply voltage. If choosing these types of MCU, the voltage polarity switching circuit need be added between the sampling resistor and MCU in order to do the voltage bipolar-unipolar conversion. The MSP430AFE2x3 family MCUs have the different analog-to-digital converters system can be input a pair of analog values. The differential value of the pair will be processed by the SD24\_A A/D converter. Therefore, if choosing the MSP430AFE2x3 family MCUs, the AC signals can be interfaced directly without the need of voltage bipolar-unipolar conversion.

The analog-to-digital converters in the MSP430F21x2 family MCUs and the MSP430G2x33 family MCUs can only transfer the analog decimal data to the 10 bits digital binary data, however, the MSP430AFE2x3 family MCUs with the SD24\_A modules can transfer the analog decimal data to the 16 bits digital binary data. That means the MSP430AFE2x3 family MCUs can implement the analog-to-digital conversion much more accurately than the MSP430F21x2 family MCUs and the MSP430G2x33 family MCUs with extremely higher resolution and smaller interval between each adjacent transferred digital binary data.

Thus, the MSP430AFE2x3 family MCUs are the better selections for this project. Among the different types of MCUs in the MSP430AFE2x3 family, in the overall consideration of the price, the size, the power dissipation, the flash memory size, the SRAM memory size, the number of ADC channels and the resolution of the ADC converter, the type MSP430AFE233 is chosen to be the working microcontroller unit on the Smart-plug electrical board.

## 2.3 Introduction of MSP430AFE233

### 2.3.1 Description

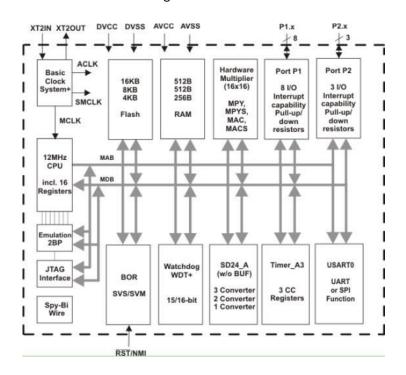

MSP430AFE233 is a type of mixed signal ultra-low-power microcontroller which consists of several devices featuring different sets of peripherals targeted for various applications [6]. The architecture is optimized to achieve extended battery life in portable measurement applications. The CPU inside this MCU is a 12MHz 16-bit RISC CPU including sixteen 16-bit registers and constant generators that contribute to maximum code efficiency [6]. Three independent 24-bit sigma-delta A/D converters, one 16-bit timer, one 16-bit hardware multiplier, one USART communication interface, one watchdog timer and eleven I/O pins are also integrated in this device.

### 2.3.2 Features

There are the basic features of MSP430AFE233 [6]:

- Low supply voltage range: 1.8 V to 3.6 V

- Ultra-low power consumption

-Active mode: 220 μA at 1 MHz, 2.2 V

-Standby mode: 0.5 μA

-Off mode (RAM retention): 0.1 μA

- Five power-saving modes

- Ultra-fast wake-up from standby mode in less than 1 μs

- 16-Bit RISC Architecture, up to 12-MHz system clock

- Basic clock module configurations

Internal frequencies up to 12 MHz

Internal low-power low-frequency (LF) oscillator

High-frequency (HF) crystal up to 16 MHz

Resonator

- -External digital clock source

- Basic clock module configurations

- Three 24-bit Sigma-Delta Analog-to-Digital (A/D) converters with differential programmable gain amplifier inputs

- 16-bit Timer A with three capture/compare registers

- Serial communication interface (USART), Asynchronous UART or Synchronous SPI selectable by software

- 16-bit hardware multiplier

- Serial onboard programming, no external programming voltage needed programmable code protection by security fuse

- On-chip emulation module

Figure 2.2 below shows the functional diagram of MCU MSP430AFE233.

Figure 2.2 The functional diagram of MSP430AFE233 [7]

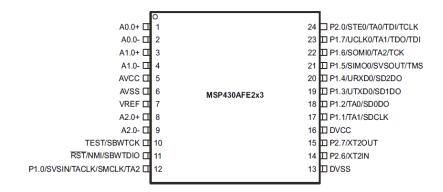

Figure 2.3 below shows the pin designation of MCU MSP430AFE233. The MSP430AFE233 has 24 pins totally.

Figure 2.3 The pin designation of MSP430AFE233 [7]

### 2.3.3 Digital I/O ports

MSP430AFE233 has two I/O ports, P1 and P2. P1 has 8 pins, P1.0 to P1.7, P2 has 3 pins, P2.0, P2.6 and P2.7. Each I/O pin can be individually configured in software for input or output direction and each I/O line can be individually read or written [8].

The digital I/O ports have interrupt capability and each interrupt for the P1 and P2 I/O lines can be enabled individually [8]. The P1 and P2 I/O lines can be configured to be provided an interrupt by the rising edge or falling edge of an input signal [8]. Each I/O port pin contains the independent input and output registers and the individually configurable pullup or pulldown resistors.

#### 2.3.3.1 Digital I/O ports input register PxIN

Each bit in each PxIN register reflects the value of the input signal at the corresponding I/O pin when the pin is configured as I/O function [8]. When the bit is set to be "0", the input signal to the corresponding I/O pin is low; when the bit is set to be "1", the input signal to the corresponding I/O pin is high.

#### 2.3.3.2 Digital I/O ports output register PxOUT

If the pullup/pulldown resistor of the corresponding pin is disabled by the PxREN register, the pin is configured as I/O function, and the bit in each PxOUT register will reflect the value of the output signal at the corresponding I/O [8]. When the bit is set to be "0", the output signal from the corresponding I/O pin is low; when the bit is set to be "1", the output signal from the corresponding I/O pin is high.

If the pullup/pulldown resistor of the corresponding pin is enabled by the PxREN register, the corresponding bit in the PxOUT register will select whether the pullup resistor or pulldown resistor is used [8]. When the bit is set to be "0", the pin is pulled down; when the bit is set to be "1", the pin is pulled up.

### 2.3.3.3 Digital I/O ports direction register PxDIR

Each bit in each PxDIR register will select the direction of the corresponding I/O pin [8]. When the bit is set to be "0", the corresponding pin is set to be input direction; when the bit is set to be "1", the corresponding pin is set to be output direction.

### 2.3.3.4 Digital I/O ports pullup/pulldown resistor enable

#### register PxREN

Each bit in each PxREN register can enable or disable the pullup/pulldown resistor of the corresponding I/O pin [8]. When the bit is set to be "0", the pullup/pulldown resistor of the corresponding I/O pin is disabled; when the bit is set to be "1", the pullup/pulldown resistor of the corresponding I/O pin is enabled, in this case, the corresponding bit in the PxOUT register will select whether the pullup resistor or pulldown resistor is used.

### 2.3.3.5 Digital I/O ports interrupts

Each pin in ports P1 and P2 have interrupt capability, which is configured with PxIFG, PxIE and PxIES registers individually and independently [8]. PxIFG is the Px interrupt flag register, PxIE is the interrupt enable register and PxIES is the interrupt edge select register. All of the P1 pins source the single interrupt vector and all of the P2 pins source a different single interrupt vector [8].

Each PxIE bit can enable the associated PxIFG bit which is the interrupt flag for its corresponding I/O pin. When one PxIE bit of the corresponding P1 port pin or P2 port pin is set to be "0", that means the I/O interrupt is disabled at thin pin; when one PxIE bit of the corresponding P1 port pin or P2 port pin is set to be "1", that means the I/O interrupt is enabled at thin pin.

Each PxIES bit will select which interrupt edge is used to control the PxIFGx flag of the corresponding I/O port pin. When one PxIES bit of the corresponding P1 port pin or P2 port pin is set to be "0", the associated PxIFGx flag is set with a low-to-high transition; when one PxIES bit of the corresponding P1 port pin or P2 port pin is set to be "1", the associated PxIFGx flag is set with a high-to-low transition [8]. It is important to notice that only transitions, not static levels, cause the interrupts.

Each PxIFGx bit is set when the selected input signal edge occurs at the pin. All of the PxIFGx interrupt flags request an interrupt when their corresponding PxIE bit and the GIE bit are set at the same time [8]. Each PxIFG flag must be reset with software. In addition, software can also set each PxIFG flag to generate a software initiated interrupt [8]. When one PxIFGx bit of the corresponding P1 port pin or P2 port pin is set to be "0", that means there is no interrupt pending at this port pin; when one PxIFGx bit of the corresponding P1 port pin or P2 port pin is set to be "1", that means there is an interrupt pending at this port pin.

## 2.3.4 Basic clock module

### 2.3.4.1 Basic clock module structure

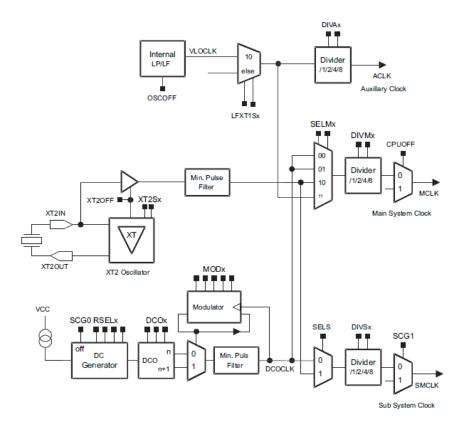

Figure 2.4 below shows the internal hardware structure of the basic clock module inside MCU MSP430AFE233.

Design and implementation of the ELIQ Smart-plug device system

Figure 2.4 The internal structure of the basic clock module in MSP430AFE233 [8]

### 2.3.4.2 Basic clock module registers

There are a series of registers in the basic clock module. The initial state of the internal circuits of the basic clock module needs to be set by configuring each bit of these registers firstly to determine the working clock for the task executed in the MCU when the system starts working.

In BCSCTL1, the basic clock system register 1, the XT2OFF bit which occupies bit 7 is used to choose whether the XT2 oscillator is turned on or turned off. If XT2OFF bit equals to "0", XT2 oscillator is turned on; if XT2OFF bit equals to "1", XT2 oscillator is turned off. Since XT2CLK needs to be used for MCLK and SMCLK, the XT2 oscillator should be turned on by clearing the XT2OFF bit.

| Table 2.1 below shows the function | of each bit in the BCSCTL1 register. |

|------------------------------------|--------------------------------------|

| Tuble 2.1 below shows the function | of each bit in the bescret register. |

| 7      | 6   | 5   | 4   | 3     | 3 2 1 0 |  |  |  |  |

|--------|-----|-----|-----|-------|---------|--|--|--|--|

| XT2OFF | XTS | DI\ | /Ax | RSELx |         |  |  |  |  |

Table 2.1 The function of each bit in the BCSCTL1 register [8]

In BCSCTL2, the basic clock system register 2, the SELMx bits which occupy bit 7 and bit 6 are used to select the clock source for the MCLK. The SELS bit which occupies bit 3 is used to select clock source for the SMCLK. The DIVMx bits which occupy bit 5 and bit 4 will determine the value

of the divider ratio for the MCLK. Similarly, the DIVSx bits which occupy bit 2 and bit 1 will determine the value of the divider ratio for the SMCLK. Table 2.2 below shows the function of each bit in the BCSCTL2 register.

| 7 6   |  | 5   | 4   | 3    | 2   | 1   | 0    |

|-------|--|-----|-----|------|-----|-----|------|

| SELMx |  | DIV | ′Mx | SELS | DIV | /Sx | DCOR |

Table 2.2 The function of each bit in the BCSCTL2 register [8]

In BCSCTL3, the basic clock system register 3, the XT2Sx bits which occupy bit 7 and bit 6 are used to select the frequency range for the XT2 clock. Table 2.3 below shows the function of each bit in the BCSCTL3 register.

| 7 | 6     | 5 | 5 4  |       | 3 2 |       | 0       |

|---|-------|---|------|-------|-----|-------|---------|

|   | XT2Sx |   | T1Sx | XCAPx |     | XT2OF | LFXT1OF |

Table 2.3 The function of each bit in the BCSCTL3 register [8]

### 2.3.5 Timer\_A

In the MCU MSP430AFE233, Timer\_A is a 16-bit timer/counter with multiple capture/compare registers. The 16-bit timer/counter can be chosen to work in four different operating modes. Timer\_A has a selectable clock source and configurable PWM outputs. It also has extensive interrupt capabilities. The interrupts can be generated from the overflow condition of the counter or from the capture/compare registers.

#### 2.3.5.1 Timer\_A structure

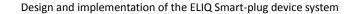

Figure 2.5 below shows the internal hardware structure of the Timer\_A module inside MCU MSP430AFE233.

Figure 2.5 The internal structure of Timer\_A in MSP430AFE233 [8]

#### 2.3.5.2 Timer\_A registers

There are also some registers in the Timer\_A module. Each bit of these registers needs to be configured firstly to give the initial state of the circuits inside the Timer\_A module when the system starts working.

Table 2.4 below shows the function of each bit in TACTL, the Timer\_A control register. The TASSELx bits which occupy bit 9 and bit 8 will select the Timer\_A clock source from TACLK, ACLK, SMCLK or INCLK. The IDx bits which occupy bit 7 and bit 6 will select the ratio of the divider to divide the frequency of the input clock signal from the Timer\_A clock source. The MCx bits which occupy bit 5 and bit 4 will be used to choose which operating mode for the Timer\_A to work with from the up mode, the continuous mode or the up/down mode. The TACLR bit which is bit 2 of the TACTL register is used to clear both of the count value in the TAR register and the ratio value of the timer clock divider. The TAIE bit which is bit 1 of the TACTL register is used to enable the Timer\_A interrupt. The TAIFG bit which is bit 0 of the TACTL register is the Timer\_A interrupt flag bit.

#### Design and implementation of the ELIQ Smart-plug device system

| 15 | 14     | 13 | 12 | 11 | 10 | 9 | 8 |  |  |

|----|--------|----|----|----|----|---|---|--|--|

|    | unused |    |    |    |    |   |   |  |  |

| 7   | 6 | 5 | 4  | 3      | 2     | 1    | 0     |

|-----|---|---|----|--------|-------|------|-------|

| IDx |   | М | Сх | unused | TACLR | TAIE | TAIFG |

Table 2.4 The function of each bit in the TACTL register [8]

Table 2.5 below shows the function of each bit in TAR, the Timer\_A register. The 16-bit count value of Timer\_A is stored into the TAR register, which occupies every bit of the TAR register.

| TARx | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|------|----|----|----|----|----|----|---|---|

|      |    |    |    |    |    |    |   |   |

| 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---|------|---|---|---|---|---|---|--|--|--|

|   | TARx |   |   |   |   |   |   |  |  |  |

Table 2.5 The function of each bit in the TAR register [8]

Table 2.6 below shows the function of each bit in TACCRx, the Timer\_A capture/compare register x. Whether the compare mode or the capture mode is used can be chosen by the CAP bit in the TACCTLx register. If choosing the compare mode, the data stored into the TACCRx register will be compared with the count value in the Timer\_A register. If choosing the copied into the TACCRx register when a capture is performed.

| 15     | 14 | 13 | 12 | 11 | 10 | 9 | 8 |  |  |

|--------|----|----|----|----|----|---|---|--|--|

| TACCRx |    |    |    |    |    |   |   |  |  |

|        |    |    |    |    |    |   |   |  |  |

| 7      | 6  | 5  | 4  | 3  | 2  | 1 | 0 |  |  |

TACCRx Table 2.6 The function of each bit in the TACCRx register [8]

Table 2.7 below shows the function of each bit in TACCTLx, the capture/compare control register x. The CAP bit which occupies bit 8 is used to choose whether the compare mode or the capture mode is employed for the TACCRx register. The CCIE bit which occupies bit 4 is to enable the capture/compare mode. The CCIFG bit which is bit 0 is the capture/compare interrupt flag bit.

| 15      | 15 14 13 |    |      | 11  | 10   | 9      | 8     |

|---------|----------|----|------|-----|------|--------|-------|

| CMx     |          | CC | ISx  | SCS | SCCI | unused | CAP   |

|         |          |    |      |     |      |        |       |

| 7       | 6        | 5  | 4    | 3   | 2    | 1      | 0     |

| OUTMODx |          |    | CCIE | CCI | OUT  | COV    | CCIFG |

Table 2.7 The function of each bit in the TACCTLx register [8]

### 2.3.6 SD24\_A

#### 2.3.6.1 SD24\_A structure

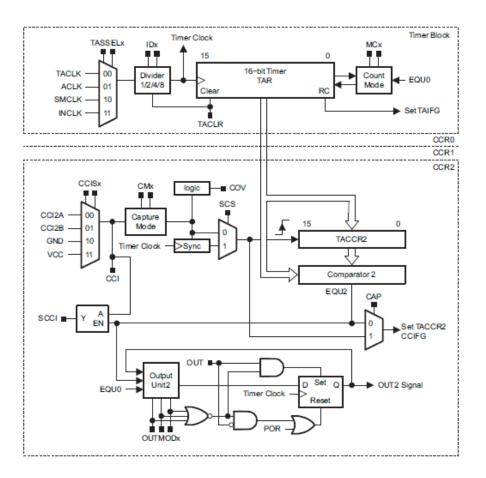

The MSP430AFE233 has three multichannel 24-bit sigma-delta analog-to-digital converters. Figure 2.6 below shows the internal structure of the multichannel SD24\_A analog-to-digital converters inside the MCU MSP430AFE233. There are eight fully differential multiplexed analog input pairs in each converter channel. Among the eight fully differential analog input pairs, A0 to A5 are used to accept the external input analog signal. A5 is used to measure the working supply voltage for the MCU with the resistive divider circuitry and A6 is used to measure the room temperature by connecting a temperature sensor inside the MCU. The analog input module is followed by the second-order oversampling sigma-delta modulator and the digital decimation filter. The input analog differential value will be converted to a 1 bit data stream by the single-bit comparator with the modulator frequency fM which can reach 1.1MHz inside the second-order sigma-delta modulator.

Figure 2.6 The internal structure of the multichannel SD24\_A analog-to-digital converters [8]

#### 2.3.6.2 SD24\_A registers

There are a series of registers inside the SD24\_A module. These registers also need be configured in software before the task starts.

Table 2.8 below shows the function of each bit in SD24CTL, the SD24 control register. The SD24SSELx bits which occupy bit 5 and bit 4 will select the clock source from MCLK, SMCLK, ACLK or external TACLK. Both of the SD24XDIVx bits which occupy bit 11 and bit 10 and the SD24DIVx bits which occupy bit 7 and bit 6 can divide the clock to generate the modulating frequency  $f_M$  for the sigma-delta modulator together. The SD24REFON bit which occupies bit 2 is used to select whether the on-chip reference voltage 1.2 V is turned on or turned off for each SD24\_A channel by setting SD24REFON = "1" or SD24REFON = "0".

| 15 | 14   | 13   | 12 | 11        | 10 | 9 | 8      |

|----|------|------|----|-----------|----|---|--------|

|    | rese | rved |    | SD24XDIVx |    |   | SD24LP |

|    |      |      |    |           |    |   | _      |

| 7                  | 6 | 5 | 4     | 3          | 2         | 1        | 0        |

|--------------------|---|---|-------|------------|-----------|----------|----------|

| SD24DIVx SD24SSELx |   |   | SSELx | SD24VMIDON | SD24REFON | SD24OVIE | reserved |

|                    |   |   |       |            |           |          |          |

Table 2.8 The function of each bit in the SD24CTL register [8]

Table 2.9 below shows the function of each bit in SD24INTCTLx, the SD24 channel x input control register. The SD24INCHx bits which occupy bit 2, bit 1 and bit 0 will select which differential input pair to be used in the corresponding SD24\_A channel. The SD24GAINx bits which occupy bit 5, bit 4 and bit 3 are used to choose the gain value of the preamplifier for the differential input AC signal from 1, 2, 4, 8, 16 or 32 before the differential input AC signal coming into the 2<sup>nd</sup> sigma-delta modulator. The SD24INTDLYx bits which occupy bit 7 and bit 6 are used to choose how many samples delay for the first interrupt after the analog-to digital conversion starts. The software variable will read the converted value from the SD24MEMx register in the SD24 interrupt service routine every time the SD24\_A interrupt triggers. It needs to consume some time to get the digital result from the analog-to-digital conversion, when the first interrupt generates immediately just after the analog-to-digital conversion starts, the software variable will read the conversion. Thus, adding this interrupt delay between the analog-to digital conversion and make the software work more stably.

| 7      | 6      | 5 | 4         | 3 | 2 | 1         | 0 |

|--------|--------|---|-----------|---|---|-----------|---|

| SD24II | NTDLYx |   | SD24GAINx |   |   | SD24INCHx |   |

Table 2.9 The function of each bit in the SD24INTCTLx register [8]

Table 2.10 below shows the function of each bit in SD24CCTLx, the SD24 channel x control register. The SD24UNI bit which occupies bit 12 is to select whether the bipolar mode or unipolar

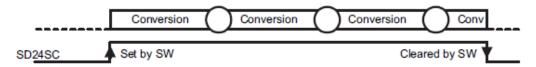

mode is used to accept the input AC signal. If choosing the unipolar mode, the analog input pair in the SD24 A can only be entered into the positive signal, while the bipolar mode can deal with both of the positive signal and negative signal. The SD24XOSR bit which occupies bit 11 and the SD24OSRx bits which occupy bit 9 and bit 8 will decide the oversampling ratio together to get the sampling frequency  $f_s$  from the modulating frequency  $f_M$  for the decimation digital filter. The SD24LSBACC bit which occupies bit 6 is used to choose whether the 16 most significant bits or the 16 least significant bits of the output conversion value from the decimation digital filter will come into the SD24MEMx register. The SD24LSBTOG bit which occupies bit 7 is used to choose whether the SD24LSBACC bit will be toggled or not be toggled each time the SD24MEMx register is read by software. The SD24IFG bit which occupies bit 2 is the SD24\_A interrupt flag bit, which is set every time the new conversion result data is written into the SD24MEMx register, that means the SD24\_A interrupt will be triggered every time the converted data from the digital filter output is stored into the SD24MEMx register. This bit will be cleared automatically after the data in the SD24MEMx register is read by the CPU. Nevertheless, it is better that SD24IFG is cleared by using the software code every time the SD24MEMx register is read by the CPU to avoid the data confusion conflict in the small time interval. The SD24GRP bit which occupies bit 0 is used to choose whether the corresponding channel works independently in single channel mode or the corresponding channel is grouped with higher channel to work together. The SD24SNGL bit which occupies bit 10 is used to select whether the single data conversion mode or the continuous data conversion mode is selected. If choosing single conversion mode, the SD24SC bit will be cleared automatically after one analog-to-digital conversion is completed then the conversion procedure will be stopped immediately, while the conversion will continue until the SD24SC bit is cleared by software in the continuous conversion mode. After the analog-to-digital conversion in the channel is stopped, the channel will be powered down and the corresponding digital filter will be turned off. Since the value in the SD24MEMx register can change when the analog-to-digital conversion is stopped, it is better that the conversion data is read by the SD24MEMx before the SD24SC bit is cleared to avoid reading an invalid result. The SD24BUFx bits which occupy bit 14 and bit 13 are used to choose whether the high impedance input buffer is enabled or disabled in the SD24\_A analog-to-digital converter. The SD24OVIFG bit which occupies bit 5 is the SD24\_A overflow interrupt flag to indicate whether the SD24 A overflow interrupt is pending or not pending in the channel. The SD24DF bit which is bit 4 will choose whether the SD24\_A conversion data is in offset binary format or in two's complement format by setting SD24DF = 0 or SD24DF = 1. The SD24IE bit which is bit 3 will enable the SD24\_A interrupt. The SD24SC bit which is bit 1 will start the analog-to-digital conversion.

| 15       | 14   | 13   | 12      | 11       | 10       | 9    | 8    |

|----------|------|------|---------|----------|----------|------|------|

| reserved | SD24 | BUFx | SD24UNI | SD24XOSR | SD24SNGL | SD24 | OSRx |

| 7          | 6          | 5         | 4      | 3      | 2       | 1      | 0       |

|------------|------------|-----------|--------|--------|---------|--------|---------|

| SD24LSBTOG | SD24LSBACC | SD240VIFG | SD24DF | SD24IE | SD24IFG | SD24SC | SD24GRP |

|            |            |           |        |        |         |        |         |

Table 2.10 The function of each bit in the SD24CCTLx register [8]

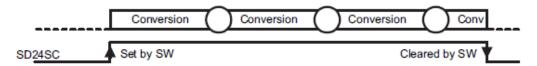

Figure 2.7 below shows the single channel operation by using the continuous conversion mode. It can be seen clearly that the conversion will continue until the SD24SC bit is cleared by software.

Figure 2.7 The diagram of the single channel operation using the continuous conversion mode [8]

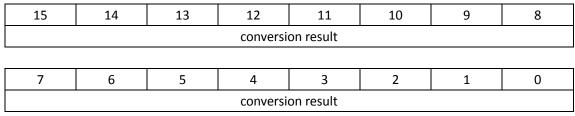

Table 2.11 below shows the function of each bit in the SD24MEMx, the SD24\_A channel x conversion memory register. This register will store the 16-bit converted digital data result from output of the digital filter. According to the value of the SD24LSBACC bit in the SD24CCTLx register, the 16 most significant bits or the 16 least significant bits of the conversion result data from the decimation digital filter output will be stored in the SD24MEMx register.

Table 2.11 The function of each bit in the SD24MEMx register [8]

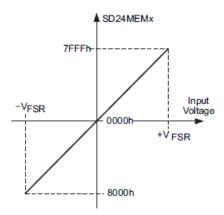

#### 2.3.6.3 Analog-to-digital conversion in SD24\_A

According to the different oversampling ratios set in the decimation filter, the output value from the filter ranges from 15 bits to 30 bits. When setting the oversampling ratio equal to 256 and SD24LSBACC = "1", the output value of the digital decimation filter is 24 bits and the 16 most significant bits will come into the SD24\_A conversion memory register. In the programmable gain amplifier, the value of gain can be selected from 1, 2, 4, 8, 16 or 32. The relation of the full scale input voltage range and the reference voltage is:

$$V_{FSR} = \frac{V_{REF/2}}{GAIN_{PGA}}$$

(2.1)

The resolution is :

resolution

$$\Delta = \frac{V_{FSR}}{2^{n-1}}$$

(2.2)

Figure 2.8 below shows the relationship of the digital output value and the input analog voltage value using the bipolar mode and 2's complement data conversion mode.

Figure 2.8 The relationship of the digital output value and the input analog voltage value

The converted digital value is:

converted digital value =

$$\frac{\text{differential value of analog input pair}}{\text{resolution }\Delta}$$

= (calculated analog value)<sub>2</sub> (2.3)

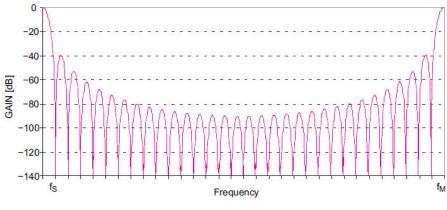

#### 2.3.6.4 Digital filter in SD24\_A

The digital filter will process the digital 1 bit data stream from the second-order sigma-delta modulator with using a  $SINC^3$  comb filter.

The transfer function in the Z-Domain is:

$$H(z) = \left(\frac{1}{OSR} \times \frac{1 - Z^{-OSR}}{1 - Z^{-1}}\right)^3$$

(2.4)

The transfer function in the frequency domain is:

$$H(f) = \left[\frac{\operatorname{sinc}\left(\operatorname{OSR}\times\pi\times\frac{f}{f_{M}}\right)}{\operatorname{sinc}\left(\pi\times\frac{f}{f_{M}}\right)}\right]^{3} = \left[\frac{1}{\operatorname{OSR}}\times\frac{\operatorname{sin}\left(\operatorname{OSR}\times\pi\times\frac{f}{f_{M}}\right)}{\operatorname{sin}\left(\pi\times\frac{f}{f_{M}}\right)}\right]^{3}$$

(2.5)

The oversampling ratio (OSR) is the ratio of the modulator frequency  $f_M$  to the sampling frequency  $f_S$ , thus  $OSR = \frac{f_M}{f_S}$ . Figure 2.9 below shows the frequency response of the digital filter in the SD24 A/D converter. The first filter notch is at  $f_S = \frac{f_M}{OSR}$ , as can be seen from Figure 2.9 below, every notch frequency is a multiple of the modulator frequency  $f_M$ .

#### Design and implementation of the ELIQ Smart-plug device system

Figure 2.9 The frequency response of the digital filter in the SD24\_A A/D converter [8]

The decimation of the digital bit-stream is completed in the digital filter in each enabled SD24\_A analog-to-digital channel. Then the digital filter can output the new conversion results to the corresponding SD24MEMx register at the sampling frequency  $f_S$ .

## 3. Materials

## 3.1 Hardware components

### 3.1.1 MCU

MSP430AFE233 is selected as the microcontroller unit to be used in the Smart-plug electrical board. MSP430AFE233 has been described in detail in chapter 2.

## 3.1.2 RF module

The RF module with the chip CC1101 is chosen to transmit and receive the RF message in this Smart-plug system as a series of advantageous the chip CC1101 possesses, such as small package size, just 4×4 mm QFN and cheap price. The chip CC1101 is a low-cost sub-1 GHz transceiver designed for low-power wireless applications [9]. The circuit inside the chip CC1101 is mainly intended for the ISM (Industrial, Scientific and Medical) frequency bands at 315MHz, 433MHz, 868MHz and 915MHz. In this project, the 868MHz ISM band is used for the wireless communication between the antennas of the RF modules in different ELIQ devices. Figure 3.1 below shows a photo of the RF module used in this project.

Figure 3.1 The photo of the RF module used in this project

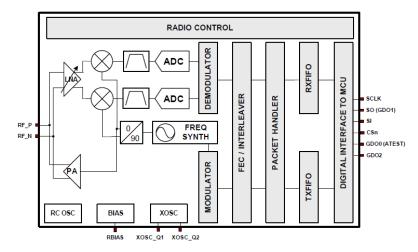

This RF transceiver is integrated with a highly configurable baseband modem. The modem supports various modulation formats and has a configurable data rate up to 600 kbps [9]. The chip CC1101 can provide extensive hardware support for packet handling, data buffering, burst transmissions, clear channel assessment, link quality indication and wake-on-radio [9].

The main operating parameters and the 64-byte transmit/receive FIFOs of CC1101 can be controlled via an SPI interface [9]. In a typical system, the CC1101 will be used together with a microcontroller and some other passive components.

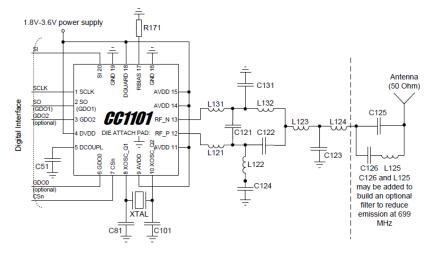

Figure 3.2 below shows the schematic of the chip CC1101 and the peripherals circuits comprised with the additional passive components such as resistors, inductors, capacitors and the crystal using the 868MHz ISM band.

Figure 3.2 The schematic of the chip CC1101 and peripheral circuits on the RF module [9]

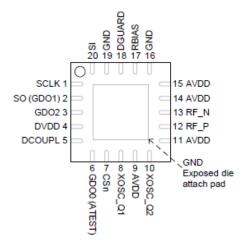

Figure 3.3 below shows the top view of the pin-out of the chip CC1101.

Figure 3.3 The top view of the pin-out of the chip CC1101 [9]

| Table 3.1 below shows the fund | ctional description of | each pin of the chip CC1101. |

|--------------------------------|------------------------|------------------------------|

|                                |                        |                              |

| Image: style         Image: style<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Pin # | Pin Name  | Pin type         | Description                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Defension         Optional general output pin when CSn is high           3         GDO2         Digital Output         Digital output pin for general use:<br><ul> <li>Test signals</li> <li>FIFO status signals</li> <li>Clear channel indicator</li> <li>Clock output, down-divided from XOSC</li> <li>Serial output RX data</li> </ul> 4         DVDD         Power (Digital)         1.8 - 3.6 V digital power supply for digital I/O's and for the digital core<br>voltage regulator           5         DCOUPL         Power (Digital)         1.6 - 2.0 V digital power supply output for decoupling<br>NOTE: This pin is intended for use with the <i>BETINI</i> only. It can not be use<br>to provide supply voltage to other devices           6         GDO0         Digital I/O         Digital output pin for general use:<br><ul> <li>Test signals</li> <li>Clear channel indicator</li> <li>Clock output X data</li> <li>Serial output RX data</li> <li>Serial output RX data</li> <li>Serial input TX data</li> <li>Also used as analog test I/O for prototype/production testing</li> </ul> <li>7</li> <li>CSn</li> <li>Digital input</li> <li>Serial configuration interface, chip select</li> <li>8</li> <li>XOSC_Q1</li> <li>Analog I/O</li> <li>Crystal oscillator pin 1, or external clock input</li> <li>9</li> <li>AVDD</li> <li>Power (Analog)</li> <li>1.8 - 3.6 V analog power supply connection</li> <li>10</li> <li>XOSC_Q2</li> <li>Analog I/O</li> <li>Crystal oscillator pin 2</li> <li>11</li> <li>AVDD</li> <li>Power (Analog)</li> <li>1</li>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1     | SCLK      | Digital Input    | Serial configuration interface, clock input                                                                                   |

| 3       GDO2       Digital Output       Digital output pin for general use: <ul> <li>Test signals</li> <li>FIFO status signals</li> <li>Clear channel indicator</li> <li>Clock output, down-divided from XOSC</li> <li>Serial output RX data</li> </ul> 4         DVDD         Power (Digital)         1.8 - 3.6 V digital power supply for digital I/O's and for the digital core voltage regulator           5         DCOUPL         Power (Digital)         1.6 - 2.0 V digital power supply output for decoupling NOTE: This pin is intended for use with the <i>Bettell</i> only. It can not be use to provide supply voltage to other devices           6         GDO0         Digital I/O         Digital output pin for general use:           (ATEST)         Visital VO         Digital output pin for general use:           (ATEST)         Visital output RX data         • Test signals           • FIFO status signals         • Clear channel indicator         • Clock output RX data           • Serial output RX data         • Serial output RX data         • Serial output RX data           • Serial output RX data         • Serial output RX data         • Serial output RX data           • Serial output RX data         • Serial output RX data         • Serial output RX data           • Serial output RX data         • Serial configuration interface, chip select         8           XOSC_Q1         Analog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2     | SO (GDO1) | Digital Output   | Serial configuration interface, data output                                                                                   |

| Image: Section of Sectio |       |           |                  | Optional general output pin when CSn is high                                                                                  |

| 9       AVDD       Power (Digital)       1.8 - 3.6 V digital power supply for digital I/O's and for the digital core voltage regulator         5       DCOUPL       Power (Digital)       1.8 - 3.6 V digital power supply output for decoupling NOTE: This pin is intended for use with the <i>definition</i> only. It can not be use to provide supply voltage to other devices         6       GDO0       Digital I/O       Digital output pin for general use: <ul> <li>Test signals</li> <li>Clear channel indicator</li> <li>Clock output, down-divided from XOSC</li> <li>Serial output pin for general use:</li> <li>Clear channel indicator</li> <li>Clear channel indicator</li> <li>Clear channel indicator</li> <li>Clock output, down-divided from XOSC</li> <li>Serial output RX data</li> <li>Serial output RX data</li> <li>Serial output X data</li> <li>Serial output TX data</li> <li>Also used as analog test I/O for prototype/production testing</li> </ul> <li>7</li> <li>CSn</li> <li>Digital Input</li> <li>Serial configuration interface, chip select</li> <li>XOSC_Q2</li> <li>Analog I/O</li> <li>Crystal oscillator pin 1, or external clock input</li> <li>9</li> <li>AVDD</li> <li>Power (Analog)</li> <li>1.8 - 3.6 V analog power supply connection</li> <li>11</li> <li>AVDD</li> <li>Power (Analog)</li> <li>1.8 - 3.6 V analog power supply connection</li> <li>12</li> <li>RF_P</li> <li>RF I/O</li> <li>Negative RF input signal to LNA in receive mode</li> <li>Positive RF input signal from PA in transmit mode</li> <li>13</li> <li>RF_N</li> <li>RF I/O</li> <li>Negative RF output signal from PA in t</li>                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3     | GDO2      | Digital Output   | Digital output pin for general use:                                                                                           |

| Image: Second |       |           |                  | Test signals                                                                                                                  |

| Image: Second |       |           |                  | FIFO status signals                                                                                                           |

| Image: space of the system  |       |           |                  | Clear channel indicator                                                                                                       |

| 4       DVDD       Power (Digital)       1.8 - 3.6 V digital power supply for digital I/O's and for the digital core voltage regulator         5       DCOUPL       Power (Digital)       1.6 - 2.0 V digital power supply output for decoupling NOTE: This pin is intended for use with the <i>Bettient</i> only. It can not be use to provide supply voltage to other devices         6       GDO0       Digital I/O       Digital output pin for general use: <ul> <li>Test signals</li> <li>FIFO status signals</li> <li>Clear channel indicator</li> <li>Clock output, down-divided from XOSC</li> <li>Serial output RX data</li> <li>Serial input TX data</li> <li>Also used as analog test I/O for prototype/production testing</li> </ul> <li>7</li> <li>CSn</li> <li>Digital Input</li> <li>Serial configuration interface, chip select</li> <li>XOSC_Q1</li> <li>Analog I/O</li> <li>Crystal oscillator pin 1, or external clock input</li> <li>Socc_Q2</li> <li>9 AVDD</li> <li>Power (Analog)</li> <li>1.8 - 3.6 V analog power supply connection</li> <li>12 RF_P</li> <li>RF I/O</li> <li>Positive RF input signal to LNA in receive mode</li> <li>Positive RF output signal from PA in transmit mode</li> <li>13 RF_N</li> <li>RF I/O</li> <li>Negative RF input signal for PA in transmit mode</li> <li>14 AVDD</li> <li>Power (Analog)</li> <li>1.8 - 3.6 V analog power supply connection</li> <li>15 AVDD</li> <li>Power (Analog)</li> <li>1.8 - 3.6 V analog power supply connection</li> <li>15 AVDD</li> <li>Power (Analog)</li> <li>1.8 - 3.6 V analog power supply connection</li> <li>15 AVDD</li> <li>Power (Analog)</li> <li>1.8 - 3.6 V analog power supply connectio</li>                                                                                                                                                                                                                                                                                                                                                                                          |       |           |                  | Clock output, down-divided from XOSC                                                                                          |

| Solution       Voltage regulator         Voltage regulator       Notes and solution of the solutis solution of the solutis solution of the solutis solution of the                                              |       |           |                  | Serial output RX data                                                                                                         |

| NOTE: This pin is intended for use with the <i>GETTOT</i> only. It can not be use to provide supply voltage to other devices           6         GDO0<br>(ATEST)         Digital I/O         Digital output pin for general use:<br>• Test signals<br>• FIFO status signals<br>• Clear channel indicator<br>• Clock output, down-divided from XOSC<br>• Serial output RX data<br>• Serial input TX data<br>Also used as analog test I/O for prototype/production testing           7         CSn         Digital Input         Serial configuration interface, chip select           8         XOSC_Q1         Analog I/O         Crystal oscillator pin 1, or external clock input           9         AVDD         Power (Analog)         1.8 - 3.6 V analog power supply connection           11         AVDD         Power (Analog)         1.8 - 3.6 V analog power supply connection           12         RF_P         RF I/O         Positive RF input signal to LNA in receive mode<br>Positive RF output signal from PA in transmit mode           13         RF_N         RF I/O         Negative RF input signal from PA in transmit mode           14         AVDD         Power (Analog)         1.8 - 3.6 V analog power supply connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4     | DVDD      | Power (Digital)  |                                                                                                                               |

| 6       GD00<br>(ATEST)       Digital I/O       Digital output pin for general use:<br>• Test signals<br>• FIFO status signals<br>• Clear channel indicator<br>• Clock output, down-divided from XOSC<br>• Serial output RX data<br>• Serial input TX data<br>Also used as analog test I/O for prototype/production testing         7       CSn       Digital Input       Serial configuration interface, chip select         8       XOSC_Q1       Analog I/O       Crystal oscillator pin 1, or external clock input         9       AVDD       Power (Analog)       1.8 - 3.6 V analog power supply connection         10       XOSC_Q2       Analog I/O       Crystal oscillator pin 2         11       AVDD       Power (Analog)       1.8 - 3.6 V analog power supply connection         12       RF_P       RF I/O       Positive RF input signal to LNA in receive mode<br>Positive RF output signal from PA in transmit mode         13       RF_N       RF I/O       Negative RF input signal from PA in transmit mode         14       AVDD       Power (Analog)       1.8 - 3.6 V analog power supply connection         15       AVDD       Power (Analog)       1.8 - 3.6 V analog power supply connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5     | DCOUPL    | Power (Digital)  | 1.6 - 2.0 V digital power supply output for decoupling                                                                        |

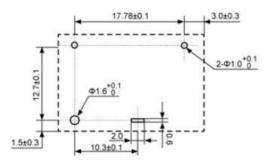

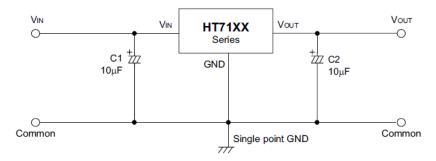

| ATEST) <ul> <li>Test signals</li> <li>Test signals</li> <li>FIFO status signals</li> <li>Clear channel indicator</li> <li>Clear channel indicator</li> <li>Clock output, down-divided from XOSC</li> <li>Serial output RX data</li> <li>Serial input TX data</li> <li>Also used as analog test I/O for prototype/production testing</li> </ul> <li>7 CSn Digital Input Serial configuration interface, chip select</li> <li>XOSC_Q1</li> <li>Analog I/O</li> <li>Crystal oscillator pin 1, or external clock input</li> <li>9 AVDD</li> <li>Power (Analog)</li> <li>1.8 - 3.6 V analog power supply connection</li> <li>XOSC_Q2</li> <li>Analog I/O</li> <li>Crystal oscillator pin 2</li> <li>AVDD</li> <li>Power (Analog)</li> <li>1.8 - 3.6 V analog power supply connection</li> <li>XOSC_Q2</li> <li>Analog I/O</li> <li>Crystal oscillator pin 2</li> <li>AVDD</li> <li>Power (Analog)</li> <li>1.8 - 3.6 V analog power supply connection</li> <li>RF_P</li> <li>RF I/O</li> <li>Positive RF input signal to LNA in receive mode</li> <li>Positive RF output signal from PA in transmit mode</li> <li>RF_N</li> <li>RF I/O</li> <li>Negative RF output signal from PA in transmit mode</li> <li>Negative RF output signal from PA in transmit mode</li> <li>AVDD</li> <li>Power (Analog)</li> <li>1.8 - 3.6 V analog power supply connection</li> <li>AVDD</li> <li>Power (Analog)</li> <li>1.8 - 3.6 V analog power supply connection</li> <li>AVDD</li> <li>Power (Analog)</li> <li>1.8 - 3.6 V analog power supply connection</li> <li>AVDD</li> <li>Power (Analog)</li> <li>1.8 - 3.6 V analog power supply connection</li>                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |           |                  | NOTE: This pin is intended for use with the <b>CC1101</b> only. It can not be used to provide supply voltage to other devices |