# **MELSEC A series**

# Programmable Controller User's Manual

**A68 AD**

## SAFETY PRECAUTIONS

(Read these precautions before using.)

When using Mitsubishi equipment, thoroughly read this manual and the associated manuals introduced in this manual. Also pay careful attention to safety and handle the module properly.

These precautions apply only to Mitsubishi equipment. Refer to the CPU module user's manual for a description of the PC system safety precautions.

These ● SAFETY PRECAUTIONS ● classify the safety precautions into two categories: "DANGER" and "CAUTION".

Depending on circumstances, procedures indicated by <u>A</u> **CAUTION** may also be linked to serious results. In any case, it is important to follow the directions for usage.

Store this manual in a safe place so that you can take it out and read it whenever necessary. Always forward it to the end user.

## DANGER

Safety circuits should be installed external to the programmable controller to ensure that the system as a

whole will continue to operate safely in the event of an external power supply malfunction or a

programmable controller failure.

Erroneous outputs and operation could result in an accident.

- The following circuitry should be installed outside the programmable controller:

Interlock circuitry for the emergency stop circuit protective circuit, and for reciprocal operations such as forward/reverse, etc., and interlock circuitry for upper/lower positioning limits, etc., to prevent machine damage.

- 2) When the programmable controller detects an abnormal condition, processing is stopped and all outputs are switched OFF. This happens in the following cases

- When the power supply module's over-current or over-voltage protection device is activated

- When an error (watchdog timer error, etc.) is detected at the PC CPU by the self-diagnosis function.

Some errors, such as input/output control errors, cannot be detected by the PC CPU, and there may be cases when all outputs are turned ON when such errors occur. In order to ensure that the machine operates safely in such cases, a failsafe circuit or mechanism should be provided outside the programmable controller. Refer to the CPU module user's manual for an example of such a failsafe circuit.

- 3) Outputs may become stuck at ON or OFF due to an output module relay or transistor failure. An external circuit should therefore be provided to monitor output signals whose incorrect operation could cause serious accidents.

- A circuit should be installed which permits the external power supply to be switched ON only after the

programmable controller power has been switched ON. Accidents caused by erroneous outputs and

motion could result if the external power supply is switched ON first.

- When a data link communication error occurs, the status shown below will be established at the faulty station. In order to ensure that the system operates safely at such times, an interlock circuit should be provided in the sequence program (using the communication status information).

Erroneous outputs and operation could result in an accident.

- 1) The data link data which existed prior to the error will be held.

- 2) All outputs will be switched OFF at MELSECNET (II, /B, /10) remote I/Ostations.

- 3) At the MELSECNET/MINI-S3 remote I/O stations, all outputs will be switched OFF or output statuses will be held, depending on the E.C. mode setting.

For details on procedures for checking faulty stations, and for operation statuses when such errors occur, refer to the appropriate data link manual.

## [System Design Precautions]

## / CAUTION

• Do not bundle control lines or communication wires together with main circuit or power lines, or lay them close to these lines.

As a guide, separate the lines by a distance of at least 100 mm, otherwise malfunctions may occur due to noise

When file register R that are outside the range are read, e.g. by a MOV instruction, the file register data will become  $\mathsf{FFFF}_H$  and use of this data will cause malfunctions. Take care not to use file registers that are outside the range when designing programs

For details on instructions, refer to the Programming Manual.

#### [Cautions on Mounting]

- Use the PC in an environment that conforms to the general specifications in the manual.

Using the PC in environments outside the ranges stated in the general specifications will cause electric shock, fire, malfunction, or damage to/deterioration of the product.

- Make sure that the module fixing projection on the base of the module is properly engaged in the

module fixing hole in the base unit before mounting the module.

Failure to mount the module properly will result in malfunction or failure, or in the module falling.

- Extension cables should be securely connected to base unit and module connectors. Check for loose connection after installation

A poor connection could result in contact problems and erroneous inputs/outputs.

- Plug the memory card firmly into the memory card mounting connector. Check for loose connection after installation. A poor connection could result in erroneous operation.

## ! DANGER

- Switch off the external power supply before staring installation and wiring work Failure to do so could result in electrical shocks and equipment damage.

- After installation and wiring is completed, be sure to attach the terminal cover before switching the power ON and starting operation

Failure to do so could result in electrical shocks.

## **!** CAUTION

- Be sure to ground the FG and LG terminals, carrying out at least class 3 grounding work with a ground exclusive to the PC.

- Otherwise there will be a danger of electric shock and malfunctions.

- Carry out wiring to the PC correctly, checking the rated voltage and terminal arrangement of the product.

Using a power supply that does not conform to the rated voltage, or carrying out wiring incorrectly, will cause fire or failure.

- Outputs from multiple power supply modules should not be connected in parallel. Failure to do so could cause the power supply module to overheat, resulting in a fire or module failure.

- Tighten the terminal screws to the stipulated torque.

Loose screws will cause short circuits, fire, or malfunctions.

- Make sure that no foreign matter such as chips or wiring offcuts gets inside the module. It will cause fire, failure or malfunction.

- Connectors for external connections should be crimped, pressure welded, or soldered in the correct manner using the correct tools

- For details regarding crimping and pressure welding tools, refer to the input/output module user's manual.

A poor connection could cause shorts, fire, and erroneous operation.

#### [Cautions on Startup and Maintenance]

## DANGER

- Do not touch terminals while the power is ON.

This will cause malfunctions.

- Make sure that the battery is connected properly. Do not attempt to charge or disassemble the battery,

do not heat the battery or place it in a flame, and do not short or solder the battery.

Incorrect handling of the battery can cause battery heat generation and ruptures which could result in

fire or injury.

- Switch the power off before cleaning or re-tightening terminal screws.

Carrying out this work while the power is ON will cause failure or malfunction of the module.

## / CAUTION

- In order to ensure safe operation, read the manual carefully to acquaint yourself with procedures for program changes, forced outputs, RUNSTOP, and PAUSE operations, etc., while operation is in progress. Incorrect operation could result in machine failure and injury.

- Do not disassemble or modify any module.

This will cause failure, malfunction, injuries, or fire.

- Switch the power OFF before mounting or removing the module.

Mounting or removing it with the power ON can cause failure or malfunction of the module.

- When replacing fuses, be sure to use the prescribed fuse.

A fuse of the wrong capacity could cause a fire.

#### [Cautions on Disposal]

## / CAUTION

• Dispose of this product as industrial waste.

#### **IMPORTANT**

- (1) Design the configuration of a system to provide an external protective or safety inter locking circuit for the PCs.

- (2) The components on the printed circuit boards will be damaged by static electricity, so avoid handling them directly. If it is necessary to handle them take the following precautions.

- (a) Ground your body and the work bench.

- (b) Do not touch the conductive areas of the printed circuit board and its electrical parts with non-grounded tools, etc.

Under no circumstances will Mitsubishi Electric be liable or responsible for any consequential damage that may arise as a result of the installation or use of this equipment.

All examples and diagrams shown in this manual are intended only as an aid to understanding the text, not to guarantee operation. Mitsubishi Electric will accept no responsibility for actual use of the product based on these illustrative examples.

Owing to the very great variety in possible applications of this equipment, you must satisfy yourself as to its suitability for your specific application.

## **REVISIONS**

\*The manual number is given on the bottom left of the back cover.

| Print Date | *Manual Number  | Revision                                                                   |  |

|------------|-----------------|----------------------------------------------------------------------------|--|

| Nov., 1985 | IB (NA) 66054-A | First edition                                                              |  |

| Jan., 1986 | IB (NA) 66054-B | Correction                                                                 |  |

|            |                 | Sections 2.2, 2.4, 4.1, 5.3.1, 6.3.1, 6.3.7, 8.2.3                         |  |

|            |                 | Addition                                                                   |  |

|            |                 | Section 3.3, IMPORTANT                                                     |  |

| Feb., 1986 | IB (NA) 66054-C | Correction                                                                 |  |

|            |                 | Sections 3.1, 4.1, 8.2.5                                                   |  |

| Aug., 1986 | IB (NA) 66054-D | Deletion                                                                   |  |

|            |                 | Sections 2.4, 5.1, 5.2                                                     |  |

|            |                 | Correction                                                                 |  |

|            |                 | Items are changed meeting A0J2CPU                                          |  |

| Jun., 1987 | IB (NA) 66054-E | Correction                                                                 |  |

|            |                 | Sections 2.1, 3.2.2, 4.2                                                   |  |

| Apr., 1988 | IB (NA) 66054-F | Correction                                                                 |  |

|            |                 | Sections 5.2.1, 5.3.1                                                      |  |

| May., 1988 | IB (NA) 66054-G | Applicable CPU model names are reviewed (A1N, A2N, A2N-S1, A3NCPU, A3HCPU) |  |

| Jul., 1988 | IB (NA) 66054-H | "Instructions for Strategic Materials" added                               |  |

| Mar., 1989 | IB (NA) 66054-I | Correction                                                                 |  |

|            |                 | Section 5.2.1                                                              |  |

| Jul., 1989 | IB (NA) 66054-J | Addition                                                                   |  |

|            |                 | Section 4.2                                                                |  |

|            |                 |                                                                            |  |

|            |                 |                                                                            |  |

|            |                 |                                                                            |  |

|            |                 |                                                                            |  |

|            |                 |                                                                            |  |

|            |                 |                                                                            |  |

|            |                 |                                                                            |  |

|            |                 |                                                                            |  |

|            |                 |                                                                            |  |

|            |                 |                                                                            |  |

|            |                 |                                                                            |  |

|            |                 |                                                                            |  |

## **INTRODUCTION**

Thank you for choosing the Mitsubishi MELSEC-A Series of General Purpose Programmable Controllers Please read this manual carefully so that the equipment is used to its optimum. A copy of this manual should be forwarded to the end user.

## Manual name : A68AD USERS IB(NA) 66054J

| Section   | Manual page<br>NO. | File name | Designer data file name                     |

|-----------|--------------------|-----------|---------------------------------------------|

| Revision  |                    | Revision  |                                             |

| Contents  |                    | Contents  |                                             |

| Intro     |                    | Intro     |                                             |

| important |                    | Important |                                             |

| Safety    |                    | Safety    |                                             |

| 1         | 1-1                | 010000jc  |                                             |

| 2         | 2-1 to 2-2         | 020000jc  | P4d2 da,db, dc, dd, df, dg, dh, dj          |

| 3         | 3-1                | 030000jc  |                                             |

|           | 3-3 to 3-10        | 030200ac  | g3-9                                        |

|           | 3-11 to 3-15       | 030300jc  |                                             |

| 4         | 4-1 to 4-2         | 040000jc  | P4d2                                        |

| 5         | 5-1                | 050000jc  | P4d4                                        |

|           | 6-1 to 6-7         | 060000jc  | L6-7n, L6-2, L6-5, L6-4, L6-6a, L6-6b, L6-7 |

| 6         | 7-1 to 7-3         | 070000ac  |                                             |

|           | 8-1 to 8-7         | 080000ac  |                                             |

|           | APP-1              | A10000ac  | Appd 2                                      |

## **CONTENTS**

| 1. | GEN  | 1 – 1                                                          |                |

|----|------|----------------------------------------------------------------|----------------|

| 2. | SYS  | TEM CONFIGURATION                                              | 2 – 1 ~ 2 – 2  |

|    | 2.1  | Overall Configuration                                          | 2 – 1          |

|    | 2.2  | Applicable System                                              | 2 – 2          |

|    | 2.3  | Precautions when Using One A68AD Module with Multiple Channels | 2 – 2          |

| 3. | SPE  | CIFICATIONS                                                    | 3 – 1 ~ 3 – 15 |

|    | 3.1  | General Specifications                                         | 3 – 1          |

|    | 3.2  | Performance Specifications                                     | 3 – 2          |

|    |      | 3.2.1 Specifications                                           | 3 – 2          |

|    |      | 3.2.2 I/O conversion characteristics                           | 3 – 3          |

|    |      | 3.2.3 Digital I/O system                                       | 3 – 7          |

|    | 3.3  | I/O List with Respect to Programmable Controller CPU           | 3 – 11         |

|    | 3.4  | Buffer Memory                                                  | 3 – 12         |

|    |      | 3.4.1 Assignment of buffer memory                              | 3 – 12         |

|    |      | 3.4.2 Contents and data configuration of buffer memory         | 3 – 13         |

| 4. | HAN  | DLING                                                          | 4 – 1 ~ 4 – 2  |

|    | 4.1  | Handling Instructions                                          | 4 – 1          |

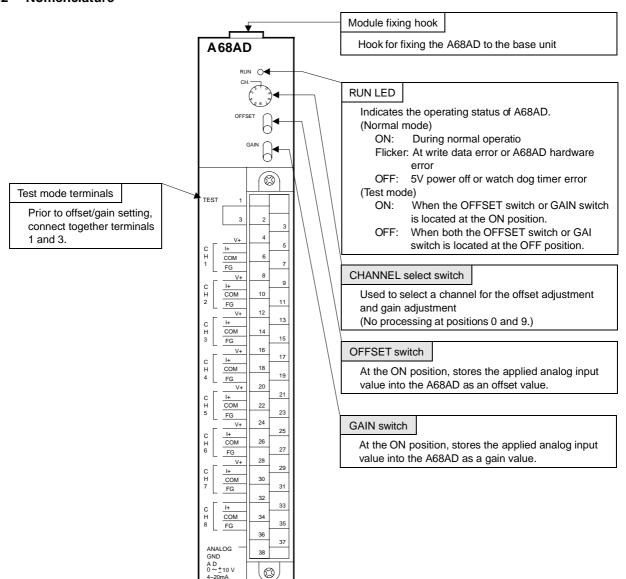

|    | 4.2  | Nomenclature                                                   | 4 – 2          |

| 5. | INST | TALLATION                                                      | 5 – 1          |

|    | 5.1  | Wiring                                                         | 5 – 1          |

|    |      | 5.1.1 Wiring instructions                                      | 5 – 1          |

|    |      | 5.1.2 Unit connection example                                  | 5 – 1          |

|    |      | 5.1.3 Maintenance and Inspection                               | 5 – 1          |

| 6. | PRO  | GRAMMING                                                       | 6 – 1 ~ 6 – 8  |

|    | 6.1  | Initial Setting                                                | 6 – 1          |

|    | 6.2  | Programming Instructions                                       | 6 – 3          |

|    |      | 6.2.1 Basic programs for read and write                        | 6 – 3          |

|    |      | 6.2.2 Setting the number of channels                           | 6 – 5          |

|    |      | 6.2.3 Setting of averaging time or averaging count             |                |

|    |      | 6.2.4 Averaging processing specification                       | 6 – 5          |

|    |      | 6.2.5 Read of digital output value                             |                |

|    |      | 6.2.6 Read and reset of write data error code                  |                |

|    |      | 6.2.7 Application circuit examples                             | 6 – 7          |

| 7. | TES  | T OPERATION AND CALIBRATION                                    | 7 – 1 ~ 7 – 3  |

|    | 7.1  | Offset/Gain Setting                                            | 7 – 1          |

|    | 7.2  | Checks before Staring                                          | 7 – 3          |

| 8.   | TRO     | JBLES                         | 100TING8 – 1 ~ 8 –                                                              | 7   |  |

|------|---------|-------------------------------|---------------------------------------------------------------------------------|-----|--|

|      | 8.1     | Write Data Error Code List8 - |                                                                                 |     |  |

|      | 8.2     | Trouble                       | eshooting8 -                                                                    | . 2 |  |

|      |         | 8.2.1                         | Troubleshooting flow chart8 -                                                   | . 2 |  |

|      |         | 8.2.2                         | Flow chart used when "RUN" LED has flickered8 -                                 | . 3 |  |

|      |         | 8.2.3                         | Flow chart used when "RUN" LED has turned off8 -                                | 4   |  |

|      |         | 8.2.4                         | Flow chart used when digital output value cannot be read8 -                     | . 5 |  |

|      |         | 8.2.5                         | Flow chart used when data, such as the number of channels, cannot be written8 - | . 7 |  |

| API  | PENDI   | X                             | APP -                                                                           | 1   |  |

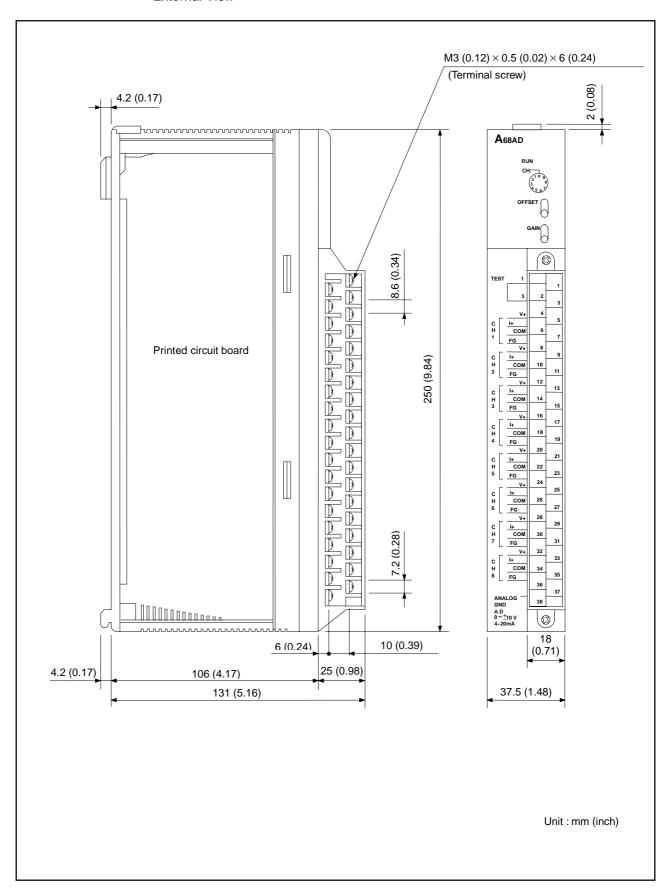

| Exte | ernal V | /iew                          | APP –                                                                           | . 1 |  |

#### 1. GENERAL DESCRIPTION

This User's Manual describes the specifications, handling programming procedures, etc. for the A68AD analog-digital converter module (hereinafter referred to as "A68AD") which is used in combination with the MELSEC-A series CPU module.

Refer to the following manuals as necessary when using the A68AD:

A1N, A2N, A3NCPU User's Manuals. ACPU Programming Manual A0J2 (CPU Module, I/O Module) User's Manual A0J2 Programming Manual Data Link System User's Manual

#### **POINT**

In this manual, the I/O allocation numbers of the A68AD as seen from the P CPU are those when a building block type CPU is used and the A68AD is loaded in slot No.0 of the main base unit.

If the A68AD is loaded in a slot other than slot No.0, or A0J2CPU is used, determine the allocation numbers of the A68AD using the I/O allocation method in the Programming Manual.

The following generic terms are used for CPU types in this manual.

(1) PC CPUs

A1, A2, A2-S1, A3CPU(P21/R21) A1N, A2N, A2N-S1, A3NCPU(P21/R21) A3HCPU(P21/R21) A0J2CPU(P23/R23)

(2) Building block type CPUs

A1, A2, A2-S1, A3CPU(P21/R21) A1N, A2N, A2N-S1, A3NCPU(P21/R21) A3HCPU(P21/R21)

(3) Compact type CPUs A0J2CPU(P23/R23)

(4) ACPU

A1, A2, A2-S1, A3CPU(P21/R21) A1N, A2N, A2N-S1, A3NCPU(P21/R21) A3HCPU(P21/R21) A0J2CPU(P23/R23)

## 2. SYSTEM CONFIGURATION

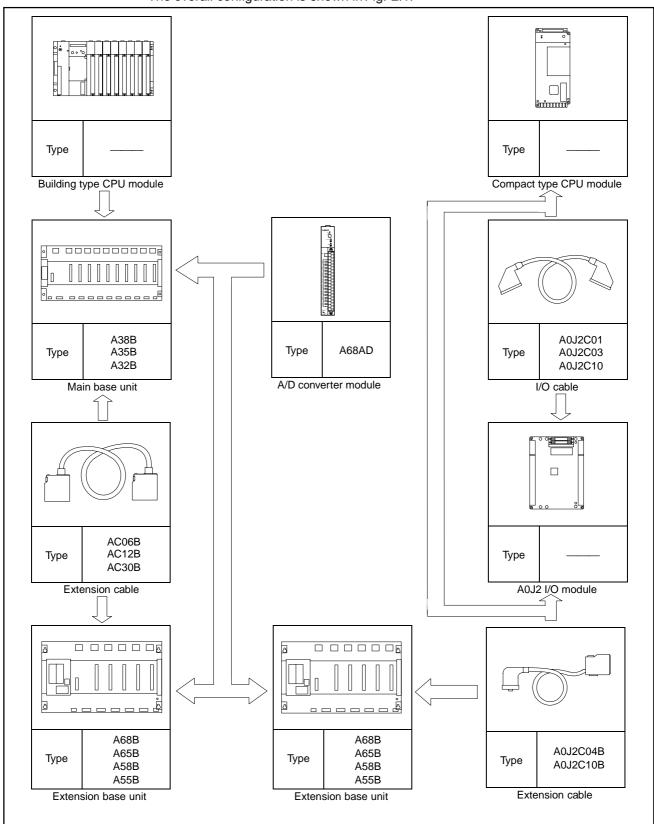

#### 2.1 Overall Configuration

The overall configuration is shown in Fig. 2.1.

Fig. 2.1 Overall Configuration Diagram

#### 2.2 Applicable System

The A68AD can be used with the following CPU modules:

| Applicable models | A0J2CPU<br>A1CPU<br>A2CPU<br>A2CPU-S1 | A1NCPU<br>A2NCPU<br>A2NCPU-S1 |  |

|-------------------|---------------------------------------|-------------------------------|--|

|                   | A3CPU<br>A3HCPU                       | A3NCPU                        |  |

The A68AD can be loaded into any slot of a base unit with the exceptions given below:

- (1) If possible, avoid loading the A68AD into an extension base unit without a power supply module (type A5 extension base units) because the power supply may be insufficient. If the A68AD is loaded in such a base unit, see the CPU module User's Manual for details on selecting an appropriate power supply module and extension cable.

- (2) In a data link system, the A68AD can be loaded at a master station, localstation, or remote I/O station, but the CPU modules that can be used at master stations and local stations are restricted to those indicated below. (The same restrictions apply for coaxial link and fiber optic link systems).

| Master station | A1CPUP21/R21<br>A2CPUP21/R21<br>A2CPUP21/R21-S1<br>A3CPUP21/R21<br>A3HCPUP21/R21                   | A1NCPUP21/R21<br>A2NCPUP21/R21<br>A2NCPUP21/R21-S1<br>A3NCPUP21/R21 |

|----------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Local station  | A0J2CPUP23/R23<br>A1CPUP21/R21<br>A2CPUP21/R21<br>A2CPUP21/R21-S1<br>A3CPUP21/R21<br>A3HCPUP21/R21 | A1NCPUP21/R21<br>A2NCPUP21/R21<br>A2NCPUP21/R21-S1<br>A3NCPUP21/R21 |

(3) When use with A3CPU(P21/R21), cannot install at the final slot of 7th extension base.

For the processing time (reading/writing) when using the A68AD in a data link system, refer to the Data Link User's Manual.

## 2.3 Precautions when Using One A68AD Module with Multiple Channels

The A68AD isolates the input terminals from the PC power supply by photocoupler, but there is no isolation between channels. When using multiple channels with a single module, pay attention to the following points.

- (1) Since the COM terminals for analog input are connected internally, make the voltage level or current level for the COM terminals the same.

- (2) If the COM terminals do not have the same level, use another A68AD, or isolate the channels externally for analog input.

## 3. SPECIFICATIONS

This chapter describes the general specifications and performance specifications of the A68AD.

#### 3.1 General Specifications

The general specifications of A68AD are indicated in Table 3.1.

| Item                          | Specifications                                                                                                        |              |              |           |                    |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------|--------------|-----------|--------------------|

| Operating ambient temperature | 0 to 5 °C                                                                                                             |              |              |           |                    |

| Storage ambient temperature   | -20 to 75 °C                                                                                                          |              |              |           |                    |

| Operating ambient humidity    | 10 to 90 %RH, no condensation                                                                                         |              |              |           |                    |

| Storage ambient humidity      | 10 to 90 %RH, no condensation                                                                                         |              |              |           |                    |

|                               | Conforms                                                                                                              | Frequency    | Acceleration | Amplitude | Sweep Count        |

| Vibration resistance          | *1 to<br>JIS C0911                                                                                                    | 10 to 50 Hz  | _            | 0.075 mm  | 10 times           |

| roolotarioo                   |                                                                                                                       | 55 to 150 Hz | 1 g          | _         | *(1 octave/minute) |

| Shock resistance              | Conforms to JIS C 0912 (10 g × 3 times in 3 directions)                                                               |              |              |           |                    |

| Noise durability              | By noise simulator 1500 Vpp noise voltage,<br>1 μs noise width and 25 to 60 Hz noise frequency                        |              |              |           |                    |

| Dielectric withstand voltage  | 500 VAC for 1 minute across batch of DC external terminals and ground                                                 |              |              |           |                    |

| Insulation resistance         | $5~\text{M}\Omega$ or larger by 500 VDC insulation resistance tester across batch of AC external terminals and ground |              |              |           |                    |

| Grounding                     | Class 3 grounding                                                                                                     |              |              |           |                    |

| Operating ambience            | To be free from corrosive gases. Dust should be minimal.                                                              |              |              |           |                    |

| Cooling method                |                                                                                                                       |              | Self-cooling | <u> </u>  |                    |

**Table 3.1 General Specifications**

## **REMARK**

One octave marked  $^*$  indicates a change from the initial frequency to double or half frequency. For example, any of the changes from 10 Hz to 20 Hz, from 20 Hz to 40 Hz, from 40 Hz to 20 Hz, and 20 Hz to 10 Hz are referred to as one octave.

<sup>\*1</sup> JIS : Japanese Industrial Standard

## 3.2 Performance Specifications

## 3.2.1 Specifications

| Item                               | Specifications                                                                                                                                                                                                                    |                                                           |  |  |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|

| Analog input                       | Selection depends on input terminals Voltage: -10 to 0 to + 10 VDC (Input resistance : $30 \text{ k}\Omega$ ) Current: + 4 to + 20m ADC (Input resistance : $25 \Omega$ ) *-20 to 0 to + 20 mA ca also be used for current input. |                                                           |  |  |

| Digital output                     | A CPU: 16-bit, signed binary (-204                                                                                                                                                                                                | 8 to +2047)                                               |  |  |

| I/O characteristics                | Analog Input<br>+10 V<br>+5 V or + 20 mA<br>0 V or + 4 mA<br>-5 V or - 12 mA<br>-10 V                                                                                                                                             | Digital Output<br>+2000<br>+1000<br>± 0<br>-1000<br>-2000 |  |  |

| Maximum resolution                 | Voltage: 5 mV (1/2000)<br>Current: 20 μA (1/1000)                                                                                                                                                                                 |                                                           |  |  |

| Overall accuracy                   | Within ± 1 % (Accuracy with respect to the maximum value)                                                                                                                                                                         |                                                           |  |  |

| Maximum conversion speed           | Maximum 2.5 ms/channel                                                                                                                                                                                                            |                                                           |  |  |

| Absolute maximum input             |                                                                                                                                                                                                                                   | Voltage: ± 15 V<br>Current: ± 30 mA                       |  |  |

| Number of analo input points       | 8 channels/module                                                                                                                                                                                                                 |                                                           |  |  |

| Insulation method                  | Photocoupler insulation between output terminals and PC power (Non-insulated between channels)                                                                                                                                    |                                                           |  |  |

| Number of I/O points               | 32 points                                                                                                                                                                                                                         |                                                           |  |  |

| Connection terminal                | 38-point terminal block                                                                                                                                                                                                           |                                                           |  |  |

| Applicable wire size               | 0.75 to 2 mm² (Applicable tightening torque: 7 kg/cm)                                                                                                                                                                             |                                                           |  |  |

| Applicable solderless terminal     | V1.25-3, V1.25-YS3,                                                                                                                                                                                                               | A, V2-S3, V2-YS3A                                         |  |  |

| Internal current consumption (5 V) | 0.9                                                                                                                                                                                                                               | 0.9 A                                                     |  |  |

| Weight                             | 0.6 kg (1.32 lb)                                                                                                                                                                                                                  |                                                           |  |  |

**Table 3.2 Performance Specifications**

## **POINT**

Analog input allowed for maximum resolution and overall accuracy, is from -10 to 0 to +10 V or from -20 to 0 to +20 mA.

#### 3.2.2 I/O conversion characteristics

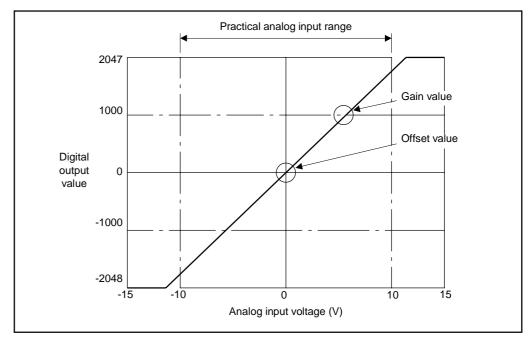

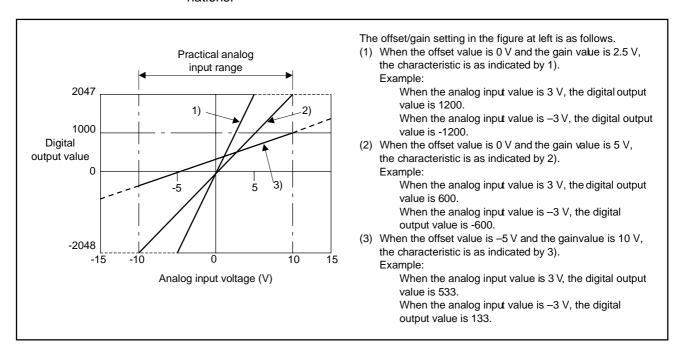

I/O conversion characteristics are dictated by the offset value and gain value set in test mode. Fig. 3.1 shows an example for voltage input.

Fig. 3.1 I/O Conversion Characteristics

## **REMARKS**

- 1. The offset value is the analog input (voltage or current) value at which the digital output value is 0. Set the offset value in test mode.

- 2. The gain value is the analog input (voltage or current) value at which the digital output value is 1000. Set the gain value in test mode.

## (1) Voltage input characteristic

Fig. 3.2 shows the voltage characteristics for three different offset/gain combinations.

Fig. 3.2 Voltage Input Characteristic

#### **POINTS**

- When the input voltage is in the range from -10 to 0 to +10 V, the maximum resolution and overall accuracy are within the quoted range of performance specifications. However, if this range is exceeded, resolution and accuracy will be impaired.

- 2. If an analog input corresponding to a digital output value of more than +2047 or less than -2048 is applied, the digital output value will not exceed +2047 or -2048.

- 3. Do not apply  $\pm 15$  V or more. This will damage the module.

- 4. In offset/gain setting, the offset value should always be less than the gain value. If the offset value is greater than or equal to the gain value, the digital output value will be unpredictable.

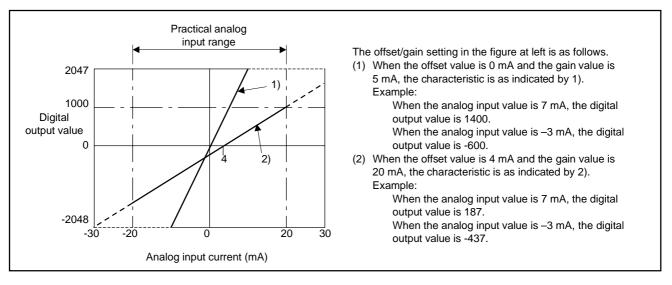

#### (2) Current input characteristic

Fig. 3.3 shows the current characteristics for two different offset/gain combinations.

Fig. 3.3 Current Input Characteristic

#### **POINTS**

- When the input current is in the range from -20 to 0 to +20 mA, the maximum resolution and overall accuracy are within the quoted range of performance specifications. However, if this range is exceeded, resolution and accuracy will be impaired.

- 2. If an analog input, corresponding to a digital output value of more than +2047 or less than -2048 is applied, the digital output value will not exceed +2047 or -2048.

- 3. Do not apply ±30 mA or more. This will damage the module.

- 4. In offset/gain setting, the offset value should always be less than the gain value. If the offset value is greater than or equal to the gain value, the digital output value will be unpredictable.

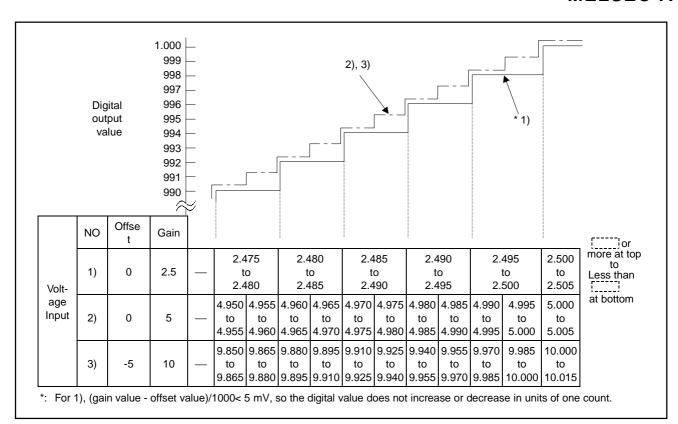

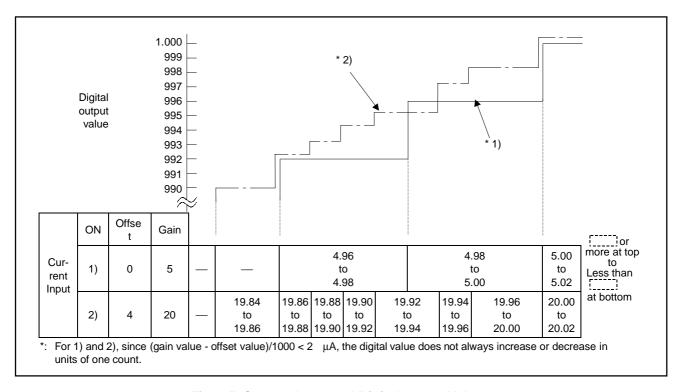

#### (3) Relation between offset/gain setting and digital output value

The maximum resolution of the A68AD is 5 mV in voltage and 20  $\mu$ A in current Maximum resolution may be found using the following expression:

Fig. 3.4 and 3.5 show the relation between the offset/gain setting and the digital output value for the offset/gain settings in Fig. 3.2 and 3.3.

Fig. 3.4 Voltage Input and Digital Output Value

Fig. 3.5 Current Input and Digital OutputValue

#### 3.2.3 Digital I/O system

The digital output value of the A68AD is determined by the following:

(1) I/O conversion characteristics:

Offset value

Gain value

The digital output value depends on the offset value and gain value which have been set in test mode.

(2) A/D conversion system:

| <ul><li>Sampling processing</li></ul> | Averaging processing in terms of count |

|---------------------------------------|----------------------------------------|

|                                       | 1 to 4000 times                        |

| Averaging processing ——               |                                        |

|                                       | Averaging processing in terms of time  |

|                                       | 20 to 10000 ms                         |

#### 1) Sampling processing

The analog input values are converted to digital output values one by one and the digital output values are stored in the buffer memory.

#### 2) Averaging processing

The A68AD makes the A/D conversion for any channels to which averaging processing has been specified from the programmable controller CPU. Using a preset count or a preset period of time, an average is calculated (excluding the maximum value and the minimum value,) and stored to the buffer memory. If the processing count is specified as two or less, sampling processing is applied.

#### **POINT**

The A68AD may sample data in any one of three ways. These sampling methods can be applied separately to any channel. The sampling process is controlled by the A68AD's own CPU, but must be specified from the programmable controller CPU. (This is fully explained in section 3.4.1)

#### Method 1

Sampling Processing: This is the most commonly used sampling procedure. As the A68AD's CPU scans each channel, the value appearing at that instant is written to the buffer memory as a digital value. The timing of this sampling depends on the number of channels used, and may be found from the following expression:

$$\begin{pmatrix} Processing \\ time \end{pmatrix} = \begin{pmatrix} Number of channels \\ used \end{pmatrix} \times 2.5 \text{ (ms/channel)}$$

(Where the maximum conversion speed is taken as 2.5 ms/channel)

Example 1: Number of channels = 5

Processing time =  $5 \times 2.5 \text{ ms} = 12.5 \text{ ms}$

#### Method 2

Averaging processing by specifying time: In this case the CPU takes a number of samples of the data at each channel and than calculates the average value over the specified time period. The number of samples taken depends on the number of channels and the time setting. If is calculated as follows:

(Processing count) =

$$\frac{\text{(Time setting)}}{\text{(Number of channels)} \times 2.5 \text{ ms}} - \text{(I)}$$

Example 2: Time setting = 1000ms, 4 channels

(Processing count) =

$$\frac{1000}{4 \times 2.5}$$

= 100 samples.

(Where maximum conversion speed = 2.5 ms/channel)

#### Method 3

Averaging processing by specifying a number of counts: This is similar to method 2 except that in this case the number of samples for the averaging process is specified. The processing time may be found from the following expression:

$$\begin{pmatrix} Processing \\ time \end{pmatrix} = \begin{pmatrix} Count \\ setting \end{pmatrix} \times \begin{pmatrix} Number of \\ channels \end{pmatrix} \times 2.5 \text{ ms}$$

Example 3: Count setting = 500, 4 channels

(Where maximum conversion speed = 2.5 ms/channel)

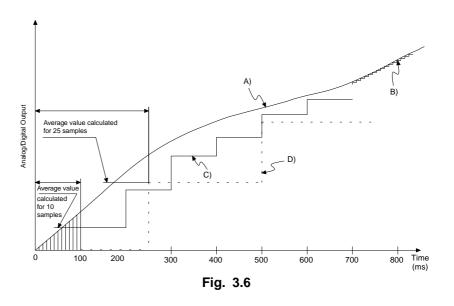

Graph showing variations between output values for different sampling methods.

Refering to the graph in Fig. 3.6

Trace A) represents a steadily rising analog input signal.

Trace B) represents the digital output obtained when method 1, sampling processing, is used. In this case the output value would be susceptible to variations due to any noise present on the analog signal.

Trace C) represents the digital output obtained when time based averaging is used. In this case the number of channels was taken as 4 and the sampling time as 100 ms.

Hence the processing count (from equation I) is:

$$\frac{100}{4 \times 2.5} = 10 \text{ samples}$$

10 samples are therefore taken every 100 ms and an average calculated. This average is then output as a digital value while the CPU takes the next 10 samples.

Note that the allowable time setting range is  $20 \rightarrow 10000$  ms which is equivilant to  $2 \rightarrow 1000$  samples (with 4 channels).

Trace D) represents the digital output obtained when count based averaging is used.

Again, the number of channels was taken as 4, the count setting was 25, the processing time, from equation II is

$$25 \times 4 \times 2.5 = 250 \text{ ms}$$

One sample is therefore taken every 10 ms, and after 25 samples have been taken, the average value is used for the digital output while the next 250 are being sampled.

Note that the allowable count setting range is 1  $\rightarrow$  4000 which is equivilant to 40  $\rightarrow$  40000 ms (with 4 channels).

#### 3.3 I/O List with Respect to Programmable Controller CPU

The I/O signals of the A68AD with respect to a programmable controller CPU are as indicated below. Numbers for X and Y are determined by the slot occupied by the A68AD and the number of points of the other I/O units

The I/O numbers indicated below are used when the A68AD module is loaded into slot No. 0 of the main base unit.

(1) Input signals with respect to programmable controller CPU, 32 points from X0 to 1F.

| Input Signal | Description                                                                                                                                                                                                                                                                                       |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| X0           | Watch dog timer error Turns on if a watch dog timer error occurs in the A68AD.                                                                                                                                                                                                                    |  |  |

| X1           | A/D conversion ready  (1) Turns on when A/D conversion is ready (not in test mode) after the power is turned on or the programmable controller CPU is reset. Turns off in test mode.  (2) Used as an interlock when read or write is performed from the programmable controller CPU to the A68AD. |  |  |

| X2 to X1F    | Not used                                                                                                                                                                                                                                                                                          |  |  |

#### **REMARK**

A/D conversion ready indicates that a digital output value has been stored into the buffer memory after the A/D conversion of all eight channels has been completed.

(2) Output signals with respect to programmable controller CPU, 32 points from Y0 to 1F.

| Output Signal | Description |

|---------------|-------------|

| Y0 to Y1F     | Not used    |

#### **IMPORTANT**

Outputs Y0 to Y1F are reserved, they should not be used in the sequence program.

If these output signals are used (turned ON/OFF) in a sequence program, it will not be possible to guarantee correct functioning of the A68AD.

If the A68AD is used in a remote I/O rack, however, inputs Y0E and Y0F may be set and reset in the sequence program to allow "hand shaking" with the CPU.

For details, refer to the Data Link System User's Manual.

#### 3.4 Buffer Memory

The A68AD is equipped with a buffer memory (which is not battery backed) for the communication of data with a programmable controller CPU. Explanation will be given for the assignment and data configuration of this buffer memory.

For the read and write operation procedures by the sequence program, refer to Chapter 6 (page 6-1).

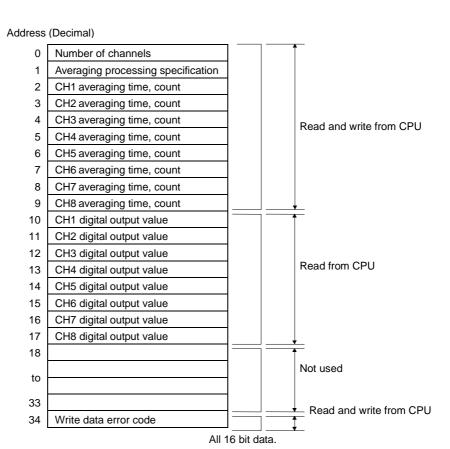

#### 3.4.1 Assignment of buffer memory

#### **POINT**

The addresses 10 to 33 of buffer memory are areas exclusively used for reading from a programmable controller CPU.

Writing to these addresses will cause mis operation.

#### 3.4.2 Contents and data configuration of buffer memory

This section describes the contents and data configuration of buffer memory for each item indicated in Section 3.4.1 (page 3-12).

- (1) Number of channels (Address 0)

- (a) At power-on, the number of channels is set to 8.

- (b) In order to reduce sampling time, the number of channels can be changed by in the sequence program. (For details, refer to Section 6.2.2 on page 6-4)

| Example: | CH1 | Used   |                                                                                  |

|----------|-----|--------|----------------------------------------------------------------------------------|

|          | CH2 | Vacant | By setting the number of channels                                                |

|          | CH3 | Used   | to 4, the sampling time is changed to $2.5 \text{ms} \times 4 = 10 \text{ ms}$ . |

|          | CH4 | Used   |                                                                                  |

|          | CH5 | Vacant |                                                                                  |

|          | CH6 | Vacant |                                                                                  |

|          | CH7 | Vacant |                                                                                  |

|          | CH8 | Vacant |                                                                                  |

#### **POINTS**

- 1. Although the number of channels at power-on is set inside the A68AD, it is not written to address 0 of the buffer memory.

- 2. When 0 is written for the number of channels, the A68AD regards the number of channels as 8 when performing A/D conversion processing.

- 3. When a number of channels other than 0 to 8 is written, setting error occurs and the buffer memory is rewritten. However, the A68AD performs A/D conversion processing for the number of channels set previously.

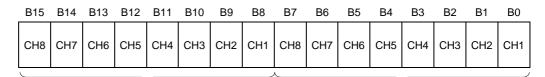

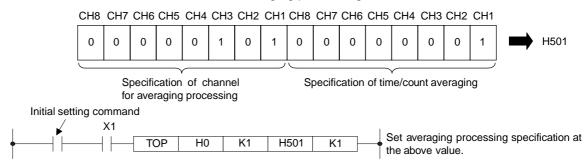

- (2) Averaging processing specification (Address 1)

- (a) When the power is turned on and the A/D conversion ready signal of A68AD is on, all channels are set to sampling processing.

- (b) For selection of sampling processing or averaging processing use address 1 of the buffer memory.

Specification of channel for which averaging processing will be performed

1: Averaging processing

0: Sampling processing

Specification of time/count

1: Time averaging

0: Count averaging

#### **POINT**

When averaging processing is not specified, sampling processing is set without regard to the specification of time/count.

- (3) Averaging time, averaging count (Addresses 2 to 9)

- (a) At power-on, the averaging time and averaging count are set to 0.

- (b) The setting ranges are as indicated below:

Averaging processing in terms of count: 1 to 4000 times Averaging processing in terms of time: 20 to 10000 ms

## **POINT**

If a value outside the above range has been written, setting error occurs and the buffer memory is rewritten. However, the A68AD performs A/D conversion processing at the averaging time or count previously set.

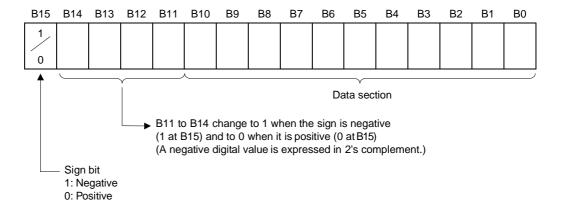

(4) Digital output value (Addresses 10 to 17)

The digital output value is expressed in 16-bit, signed binary within the range from -2048 to +2047.

- (5) Write data error code (Address 34)

- (a) When data is read from the programmable controller CPU, the A68AD makes a data range check for the number of channels used once only. When one of the values is outside the range, the A68AD sets an error code in 16-bit binary. For details of error codes, refer to Section 8.1 (page 8-1).

- (b) To reset an error code, write 0 from the programmable controller CPU.

- (c) When several error codes have occurred, the data error code, witch has been detected by the A68AD first, is stored. The other errors are not stored.

- (d) If an error is reset without remedying the error, the data error code is set to 0 and the RUN LED of A68AD stops flickering (Section 4.2 on page 4-2).

#### 4. HANDLING

This chapter describes the handling instructions, nomenclature, maintenance, and inspection of the A68AD.

#### 4.1 Handling Instructions

- (1) Protect the A68AD and its terminal block from impact.

- (2) Do not touch or remove the printed circuit board from the case.

- (3) When wiring, ensure that no wire offcuts enter the module and remove any that do enter.

- (4) Tighten terminal screws as specified below.

| Screw                                        | TighteningTorque Range<br>(kg⋅cm) |  |  |

|----------------------------------------------|-----------------------------------|--|--|

| I/O terminal block terminal screw (M3 screw) | 5 to 8                            |  |  |

| I/O terminal block mounting screw (M4 screw) | 8 to 14                           |  |  |

(5) To load the module onto the base, press the module against the base so that the hook is securely locked. To unload the module, push the catch on the top of the module, and after the hook is disengaged from the base, pull the module toward you.

#### 4.2 Nomenclature

Switches marked \_\_\_\_ are valid only in test mode. For details, refer to Section 7.1 (page 7-1).

| Terminal No. | S        | ignal Name | Terminal No. | Signal Name |     | Terminal No. | S      | Signal Name |  |

|--------------|----------|------------|--------------|-------------|-----|--------------|--------|-------------|--|

| 1            |          | TEST       | 13           |             | V+  | 25           |        | V+          |  |

| 2            | Not used |            | 14           | С           | I+  | 26           | С      | l+          |  |

| 3            | TEST     |            | 15           | H<br>3      | COM | 27           | H<br>6 | COM         |  |

| 4            |          | Not used   | 16           | ]           | FG  | 28           |        | FG          |  |

| 5            |          | V+         | 17           |             | V+  | 29           |        | V+          |  |

| 6            | С        | l+         | 18           | С           | l+  | 30           | С      | l+          |  |

| 7            | H<br>1   | СОМ        | 19           | H<br>4      | COM | 31           | H<br>7 | COM         |  |

| 8            |          | FG         | 20           | 1           | FG  | 32           |        | FG          |  |

| 9            |          | V+         | 21           |             | V+  | 33           |        | V+          |  |

| 10           | С        | l+         | 22           | С           | l+  | 34           | С      | l+          |  |

| 11           | H<br>2   | СОМ        | 23           | H<br>5      | COM | 35           | Н<br>8 | COM         |  |

| 12           | ] _      | FG         | 24           | ]           | FG  | 36           | ]      | FG          |  |

|              |          |            |              |             |     | 37           |        | Not used    |  |

|              |          |            |              |             |     | 38           |        | Not used    |  |

#### 5. INSTALLATION

#### 5.1 Wiring

#### 5.1.1 Wiring instructions

Protect external wiring against noise with the following precautions:

- (1) Separate AC and DC wiring.

- (2) Separate main circuit and/or high voltage wiring from control and signal wiring.

- (3) Where applicable, ground the shielding of all wires to a common ground point.

#### 5.1.2 Unit connection example

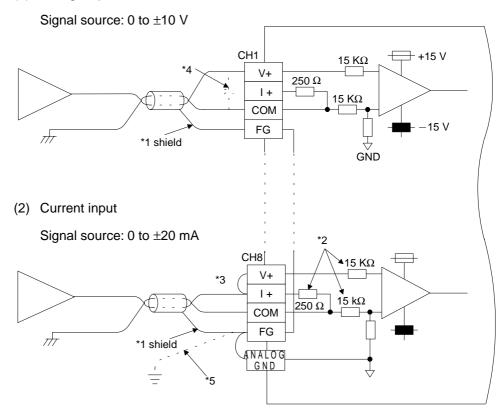

#### (1) Voltage input

- \*1: For the cable, use a two-core twisted shielded wire.

- \*2: Indicates the input resistance of the A68AD.

- \*3: For current input, be sure to connect the terminals (V+) and (I+).

- \*4: If noise or ripple is generated at the external wiring, connect a capacitor of approximately 0.1 to 0.47 μF between terminals V and COM.

- \*5: If there is excessive noise, ground the unit.

#### **POINT**

The FG terminal of the A68AD and the FG terminal of the power supply unit are not connected together internally.

#### 5.1.3 Maintenance and Inspection

The A68AD does not require any specific inspections, but in order to ensure that the system is always used under the optimum conditions, follow the inspection point in the CPU module User's Manual.

#### 6. PROGRAMMING

#### 6.1 Initial Setting

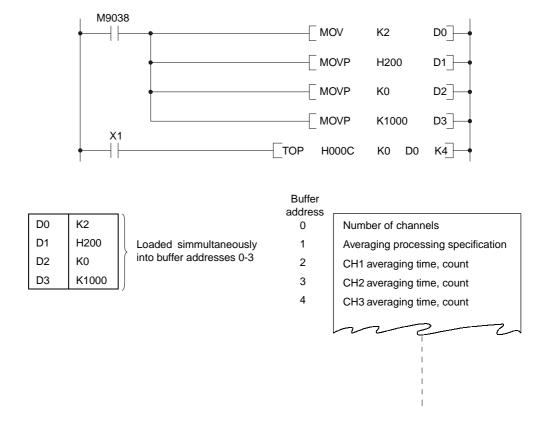

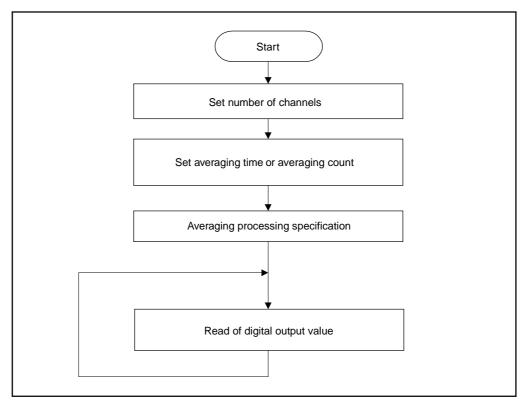

Before analog to digital conversion begins it is necessary to write certain initial data to the buffer memory. This data consists of the number of channels used and specification of the sampling method required (See section 3.4.1)

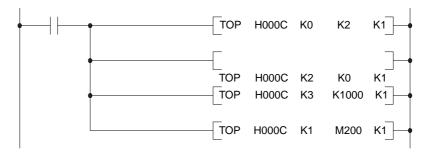

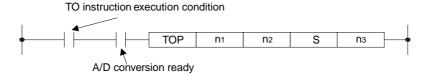

The most convenient way to write this data to the buffer memory is to use a single "TO" type instruction as shown in the example below:

The above example sets the number of channels to 2 (i.e. D0), specifies channel 2 for count averaging (i.e. D1), and sets channel 2 count setting to 1000 (i.e. D3). The A68AD is located in the main base in the slot with head element number X/Y C0.

The initial data may also be written using individual "TO" type instructions for each buffer address, in this case always execute in the following order:

Fig.6.1 Initial Setting Procedure

When this procedure is used, the previous example must be programmed as follows:

i.e. The count setting (K1000) is loaded into buffer address 3 before averaging processing specification, M200, is loaded into address 1. If this order is changed a write in error may occur. This will cause the run LED on the A68AD to flicker. Error status may also be found by monitoring buffer memory address 34.

This error occurs because the A68AD is normally in run mode. If averaging processing specification is made, the A68AD immediatly looks for the relevant averaging data. If this data has not already been written to the unit an error is registered.

#### 6.2 Programming Instructions

This section describes basic programs for read and write operations, setting the number of channels, the specification of averaging processing, read of digital output value and write error code, and application examples.

For details on instructions, refer to the ACPU Programming Manual and the A0J2CPU Programming Manual.

When the module, is used in a remote I/O station, refer to the Data link User's Manual.

#### 6.2.1 Basic programs for read and write

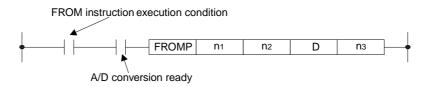

## (1) Read from A68AD: FROM, FROMP, DFRO, DFROP instructions

| Symbol         | Description                                         | Usable Device<br>Number |  |  |

|----------------|-----------------------------------------------------|-------------------------|--|--|

| n1             | Upper 2 digits of head I/O number assigned to A68AD | K, H                    |  |  |

| n <sub>2</sub> | Head address of buffer memory which stores data     | K, H                    |  |  |

| D              | Head number of device which will stored read data   | *T, C, D, W, R          |  |  |

| n3             | Number of words of data to be read                  | K, H                    |  |  |

<sup>\*</sup> With A0J2CPU(P23/R23), only T, C, and D can be used.

Example: To read the 1 word data from address 10 of the buffer memory to D0, with the A68AD assigned to I/O X130 to 14F and Y130 to 14F

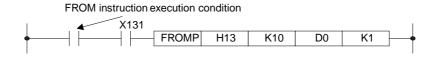

# (2) Write to A68AD: TO, TOP, DTO, DTOP instructions

| Symbol | Description                                                        | Usable Device<br>Number |

|--------|--------------------------------------------------------------------|-------------------------|

| n1     | Upper 2 digits of head I/O number assigned to A68AD                | K, H                    |

| n2     | Head address of buffer memory which will store data                | K, H                    |

| D      | Head device number or constant where data to be written is stored. | *T, C, D, W,<br>R, K, H |

| nз     | Number of words of data to be written                              | K ,H                    |

<sup>\*</sup> With A0J2CPU(P23/R23), only T, C, and D can be used.

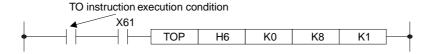

Example: To write 8 to address 0 of the buffermemory, with the A68AD assigned to I/O X60 to 7F and Y60 to 7F

# **POINT**

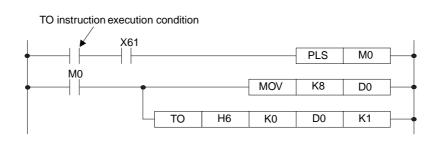

When using A0J2CPU(P23/R23), pay attention to the following points when writing a program.

- (1) There are no FROMP, TOP, DFROP, or DTOP instructions. Use internal relays (M) for pulse conversion.

- (2) Constant (K, H) designations are not possible with TO instructions. Set the data inT, C, and D devices for writing.

#### 6.2.2 Setting the number of channels

- (1) Set the number of channels 1 to 8.

- (2) Even if there is a vacant channel, the number of channels must begin with channel 1. Set the number of the last channel used.

- (3) Program example

To set the number of channels 3

#### 6.2.3 Setting of averaging time or averaging count

- Set the averaging time or averaging count to each channel for which averaging processing will be performed.

- (2) Be sure to set the averaging time or averaging count before specifying the averaging processing.

- (3) Set value

Time: 20 to 10000 ms (Set the time in units of 10 ms.)

Count: 1 to 4000 times

(4) Program example

To set the averaging time of 1000ms to channel 1 and the averaging count of 10 times to channel 3

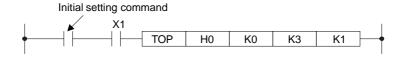

Initial setting command

X1

TOP H0 K2 K1000 K1

Write to channel 1

TOP H0 K4 K10 K1

Write to channel 3

### 6.2.4 Averaging processing specification

- (1) Specify the channels for which averaging processing will be performed, and also specify whether the processing method is count averaging or time averaging.

- (2) Be sure to specify the averaging processing method after setting the averaging time and/or averaging count.

# (3) Program example

To specify time averaging processing at channel 1, sampling processing at channel 2, and count averaging processing at channel 3.

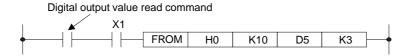

### 6.2.5 Read of digital output value

- (1) The digital output value is read in 16-bit, signed binary.

- (2) Program example

To read the digital output values of channels 1 to 3 to the D5 to 7.

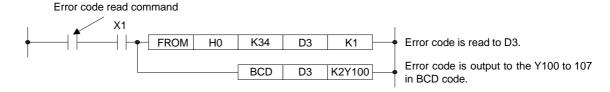

#### 6.2.6 Read and reset of write data error code

- (1) Any error code is set at address 34 of the buffer memory in binary. For details, refer to Section 8.1 (page 8-1).

- (2) Only the first error code to occur, is stored. For details, refer to Section 3.4.2 (page 3-13).

- (3) Reset the error code from the programmable controller CPU.

- (4) Program example

- a) To read the error code to D3 and output it to Y100 to 107 in BCD.

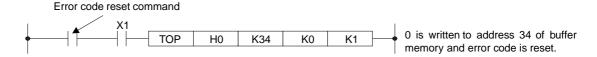

b) To reset the error code

#### 6.2.7 Application circuit examples

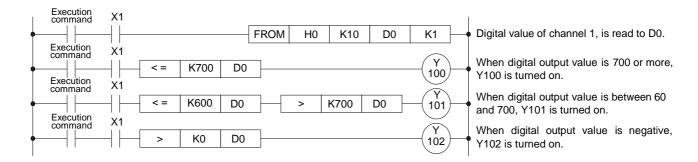

#### (1) Checking the magnitude of the analog signal

Program which turns on Y100 when the digital output value of channel 1 is 700 or more, turns on Y101 when it is between 600 and 700, and turns on Y102 when the value is negative.

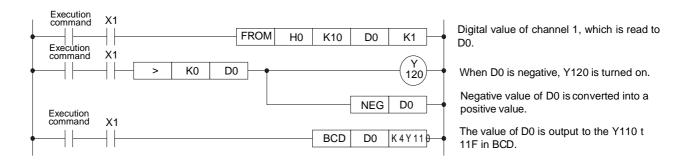

# (2) Digital display of analog signal

Program which outputs the digital output value of channel 1 to Y110 to 11F in BCD and turns on Y120 when that value is negative.

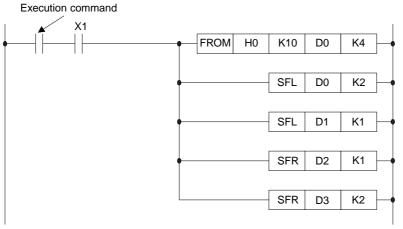

(3) Circuit which changes a gain to 4, 2, 1/2, and 1/4 times by program

The digital output values are changed to the following gains; (all digital value must be > 0)

Channel 1: 4 times

Channel 2: 2 times

Channel 3: 1/2 times

Channel 4: 1/4 times

Digital output values of channels 1 to 4, which have been converted from analog values, are read to the D0 to 3.

The value of D0 is shifted 2 bits leftward and the digital output value of channel 1 is quadrupled.

The value of D1 is shifted 1 bit leftward and the digital output value of channel 2 is doubled.

The value of D2 is shifted 1 bit rightward and the digital output value of channel 3 is halved.

The value of D3 is shifted 2 bits rightwar and the digital output value of channel 4 is quartered.

### 7. TEST OPERATION AND CALIBRATION

This chapter describes offset/gain setting. See also the A CPU User's Manual.

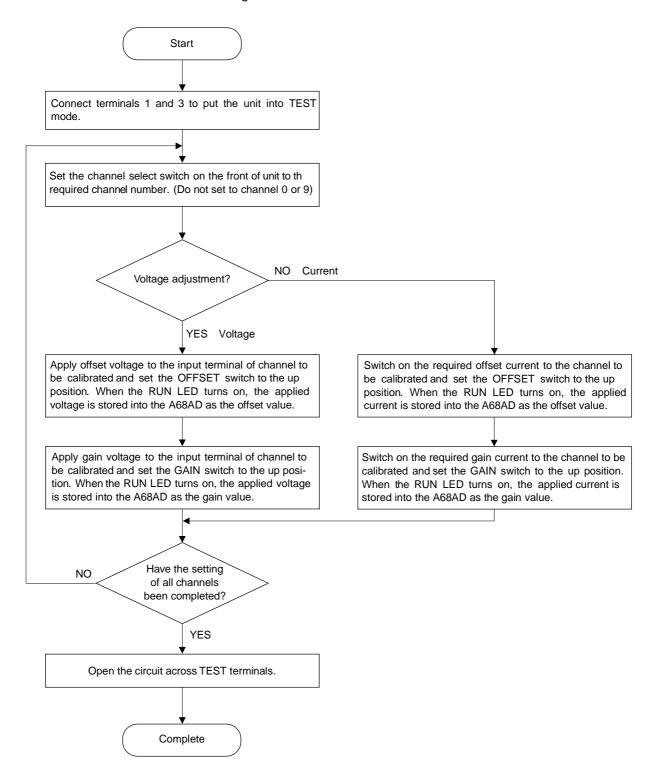

#### 7.1 Offset/Gain Setting

Change the output characteristics as follows. The unit is factory-set to an offset value of 0 V and a gain value of 5 V.

# POINTS

- 1. The offset value and gain value are stored in the A68AD and are not erased if the power is turned off.

- 2. Perform the offset/gain setting with the CPU in stop mode. When the unit is set to test mode, A/D conversion is stopped on all channels. Therefore, use the A/D conversion ready signal as an interlock.

- 3. Perform the offset/gain setting within the range -10 to 0 to +10 VDC or -20 to 0 to +20m ADC. If set outside this range, the maximum resolution and overall accuracy may not be within the ranges specified.

# 7.2 Checks before Staring

| Number | Checking<br>Point      | Description                                                                            | Check |

|--------|------------------------|----------------------------------------------------------------------------------------|-------|

| 1      | Loading of unit        | Is the I/O assignment correct?                                                         |       |

| 2      | Offset/gain<br>setting | Has offset/gain been set for all channels used?                                        |       |

|        |                        | Are set values correct?                                                                |       |

|        |                        | Has the unit been returned to normal mod by opening the circuit across TEST terminals? |       |

| 3      |                        | Are terminal block connections correct?                                                |       |

|        | Connection<br>to A68AD | Are terminal screws of terminal block tightened securely?                              |       |

|        |                        | Is the wire size correct?                                                              |       |

**Table 7.1 Points for Checking**

#### 8. TROUBLESHOOTING

This chapter describes errors, which may occur during the use of the A68AD, and troubleshooting procedures for such errors.

#### 8.1 Write Data Error Code List

The following three errors may occur during the write operation of the number of channels, averaging processing specification, averaging time, and averaging count The numeric value of the error code enclosed in [\_] indicates the channel number for which the error has occurred.

| Description                                                                      | Error Code |

|----------------------------------------------------------------------------------|------------|

| A value other than 0 to 8 has been set as the number of channels.                | 01         |

| A value other than 20 to 10000 ms has been set as an averaging time set value.   | [] 0 to 4  |

| A value other than 1 to 4000 times has been set as an averaging count set value. | [_] 5 to 8 |

**Table 8.1 Types of Write Data Error Codes**

# **POINT**

- 1. [] 0 to 4 and [] 5 to 8 of write data error code are used only to make differentiation between averaging time and averaging count, respectively. The individual numerals do not have any significance.

- 2. When an error has occurred, check the write data error code, reset the error code, and then write the corrected data. (Refer to Section 3.4.2 on page 3-13.)

## Example:

(1) Error code 32 has occurred

Since the averaging time of channel 3 is wrong, change the value to within the range 20 to 10000 ms.

(2) Error code 88 has occurred

Since the averaging count of channel 8 is wrong, change the value to within the range 1 to 4000 times.

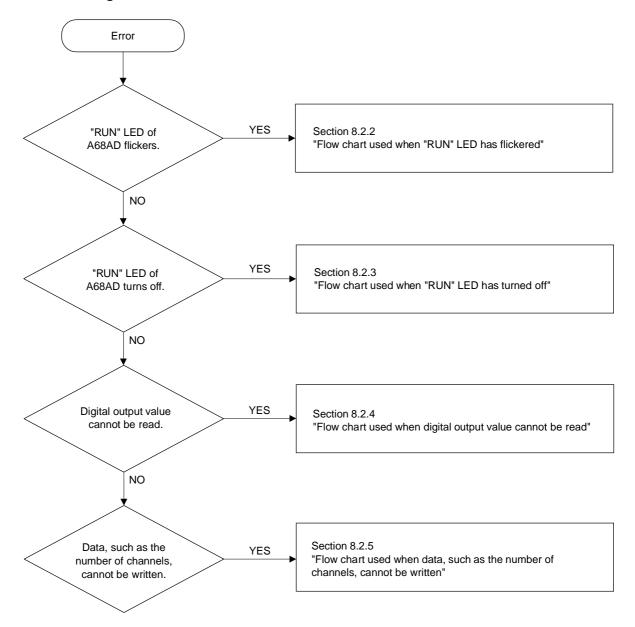

# 8.2 Troubleshooting

This section describes simple troubleshooting procedures for use of the A68AD. For problems relating to the CPU module, refer to the A CPU User's Manual.

### 8.2.1 Troubleshooting flow chart

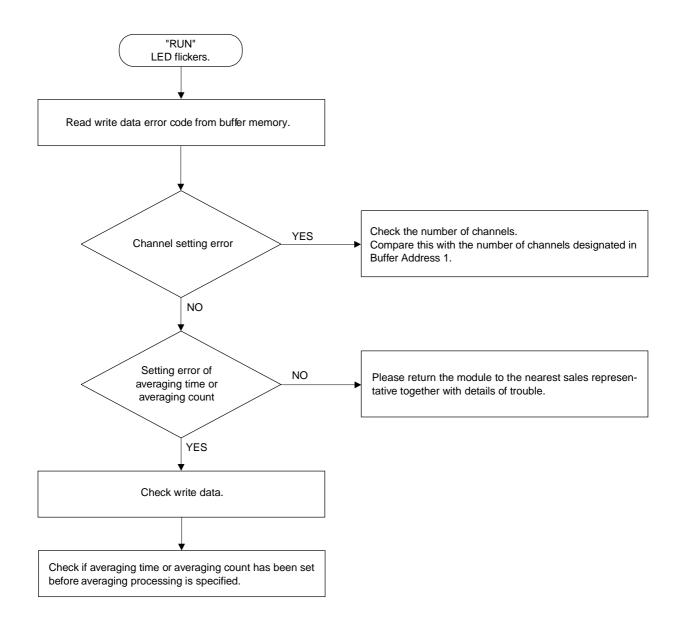

### 8.2.2 Flow chart used when "RUN" LED has flickered

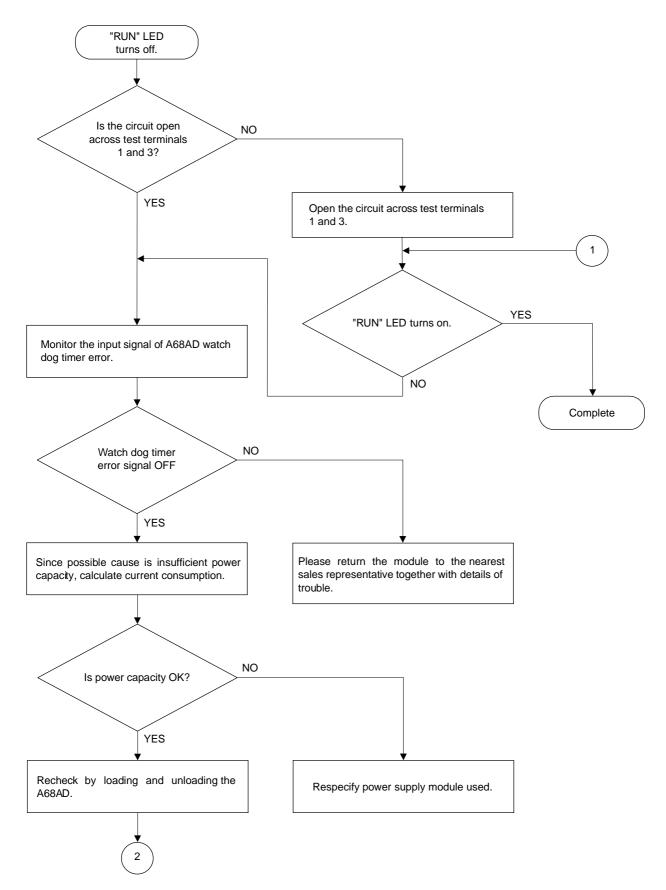

### 8.2.3 Flow chart used when "RUN" LED has turned off

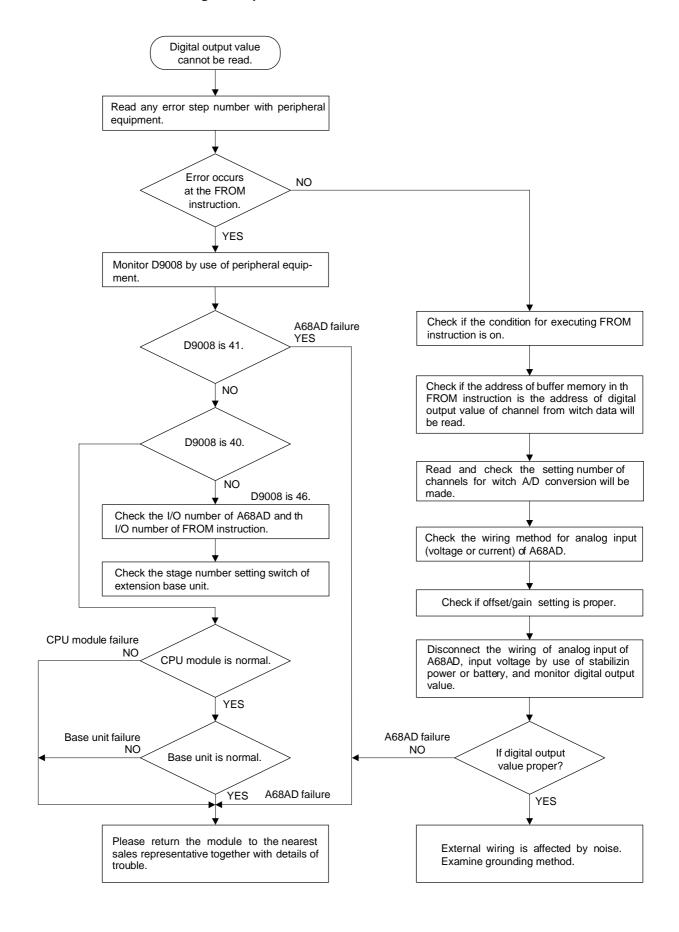

#### 8.2.4 Flow chart used when digital output value cannot be read

# REMARKS

The following contents are written into D9008 when an error has occurred during execution of the FROM or TO instruction to the A68AD.

| Contents<br>(BIN value) of<br>Special Register<br>D9008                  | CPU Status | Error and Cause                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40 Stop                                                                  |            | FROM and TO instructions cannot b executed. Hardware failure of A68AD (special function module), CPU unit, or base unit.                                                                                                                              |

| 41                                                                       | Stop       | When the FROM or TO instruction has been executed, access has been made to the special function module but no answer is returned The accessed A68AD (special function module) has failed.                                                             |

| Stop  Continuous operation can be performed by the setting of parameter. |            | Access has been made (FROM or TO instruction has been executed) to a slot where the A68AD (special function module) is not loaded The content of FROM or TO instruction is incorrect or the stage number setting of extension base unit is incorrect. |

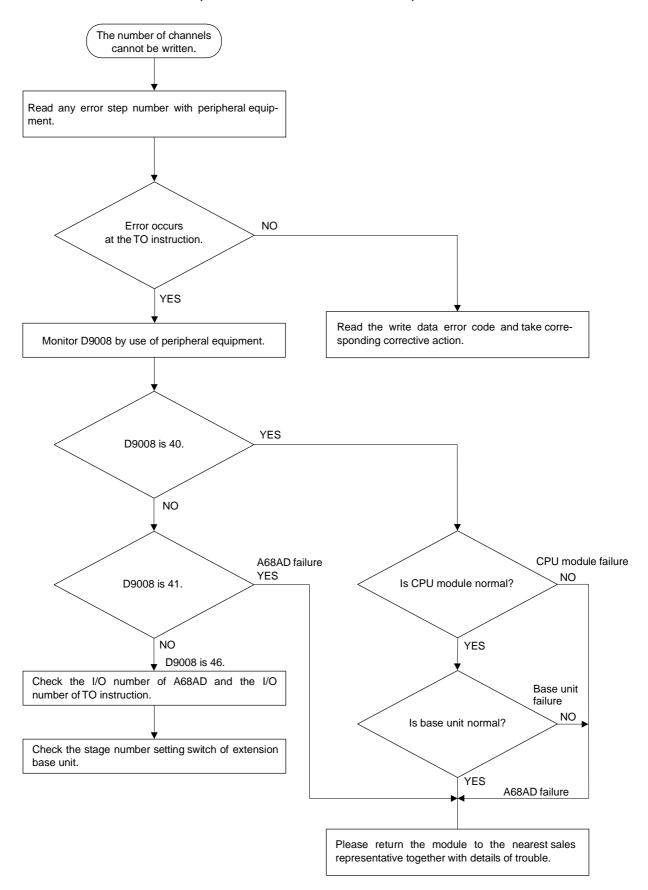

### 8.2.5 Flow chart used when data, such as the number of channels, cannot be written

# **APPENDIX**

### **External View**