Series 9420/9421/9422/9425/9426/9427

**VME Isolated Digital Input Board**

## **USER'S MANUAL**

## ACROMAG INCORPORATED

30765 South Wixom Road P.O. BOX 437 Wixom, MI 48393-7037 U.S.A. Tel: (248) 624-1541 Fax: (248) 624-9234

8500-333-C00M003

## Manual No. 8500-333

The information in this manual is subject to change without notice. Acromag, Inc., makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Further, Acromag, Inc., assumes no responsibility for any errors that may appear in this manual and makes no commitment to update, nor keep current, the information contained in this manual.

No part of this manual may be copied or reproduced in any form, or by any means, without the prior written consent of Acromag, Inc.

# IMPORTANT SAFETY CONSIDERATIONS

It is very important for the user to consider the possible adverse effects of power, wiring, component, sensor or software failures in designing any type of control or monitoring system. This is especially important where economic property loss or human life is involved. It is important that the user employ redundancy and comprehensive failure analysis to insure a safe and satisfactory overall system design. It is agreed between the Buyer and Acromag, that this is the Buyer's responsibility.

Acromag, Inc. 30765 South Wixom Road P.O. Box 437 Wixom, Michigan 48393-7037, USA

Tel: (248) 624-1541 Fax: (248) 624-9234

Copyright 1992 Acromag, Inc. Printed in USA Data and specifications subject to change without notice

## TABLE OF CONTENTS

## CHAPTER

#### PAGE

| 1.0 ( | GENERAL INFORMATION                                    | 1.1                    |

|-------|--------------------------------------------------------|------------------------|

| 1.1 I | NTRODUCTION                                            | 1.1                    |

| 1.2 [ | DIGITAL DC INPUT FEATURES                              | 1.2                    |

| 1.3 \ | VMEbus INTERFACE FEATURES                              | 1.2                    |

| 1.4 F | FIELD COMPATIBILITY                                    | 1.3                    |

|       | .4.1 Digital Inputs                                    |                        |

|       |                                                        |                        |

| 201   | PREPARATION FOR USE                                    | 2 1                    |

|       | UNPACKING AND INSPECTION                               |                        |

|       | CARD CAGE CONSIDERATIONS                               |                        |

|       | BOARD CONFIGURATION                                    |                        |

|       | .3.1 Default Jumper Configuration                      |                        |

| 2     | .3.1.1 Digital DC Input Default Configuration          | 2. <del>-</del><br>2.4 |

| 24    | VMEbus CONFIGURATION                                   | 2. <del>-</del><br>2.4 |

| 2.4   | .4.1 Address Decode Jumper Configuration               | 2. <del>4</del><br>2 / |

| 2     | .4.2 Address Modifier Jumper Configuration             | 2. <del>4</del><br>2.6 |

|       | .4.3 Interrupt Level Select Jumper Configuration       |                        |

|       | .4.4 SYSFAIL* Selection Jumper Configuration           |                        |

| 25    | DIGITAL INPUT CONFIGURATION                            | 2.0                    |

|       | .5.1 Digital DC Input Threshold Detection              |                        |

|       | .5.2 Sensing Contact Closures and Switches             |                        |

|       | .5.3 Debounce Delay Selection                          |                        |

|       | .5.4 Interrupt and Debounce Port Selection             |                        |

| 2     | .5.5 Digital Input Interface to TTL and CMOS Signals   | 2.10                   |

| 26 (  | CONNECTORS                                             | 2 13                   |

|       | .6.1 Digital Input Connector P3 (Port A & Port B)      |                        |

| 2     | .6.2 Digital Input Connector P4 (Port C & Port D)      | 2.10                   |

| 2     | .6.3 Digital Input Connector P2 (Port E & Port F)      | 2 15                   |

|       | .6.4 VMEbus Connections                                |                        |

| 2.7 F | POWER-UP TIMING AND LOADING                            | 2.17                   |

|       | DATA TRANSFER TIMING                                   |                        |

|       | FIELD GROUNDING CONSIDERATIONS                         |                        |

|       |                                                        |                        |

| 3.0   | PROGRAMMING INFORMATION                                | 3.1                    |

|       |                                                        |                        |

|       | .1.1 Board Identification PROM                         |                        |

| 3     | .1.2 Board Status Register                             |                        |

| ~     | 3.1.2.1 Status Bits Usage                              |                        |

|       | .1.3 Interrupt Vector Registers.                       |                        |

|       | .1.4 Digital Input Channel Interrupt Status Register   |                        |

|       | .1.5 Digital Input Channel Interrupt Enable Register   |                        |

| 3     | .1.6 Digital Input Channel Interrupt Polarity Register | 5.1                    |

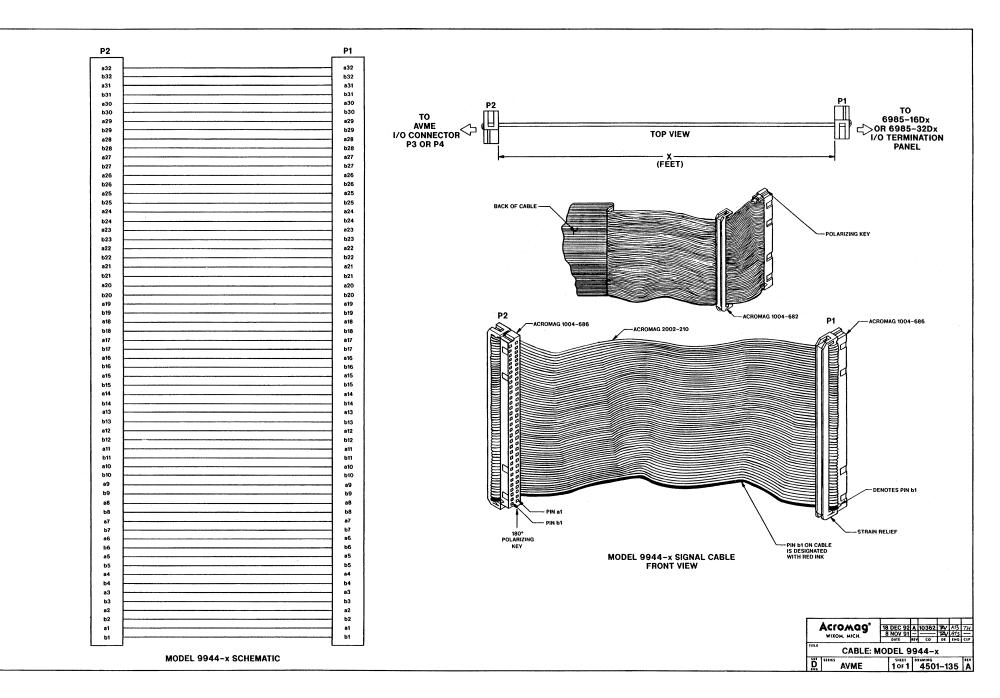

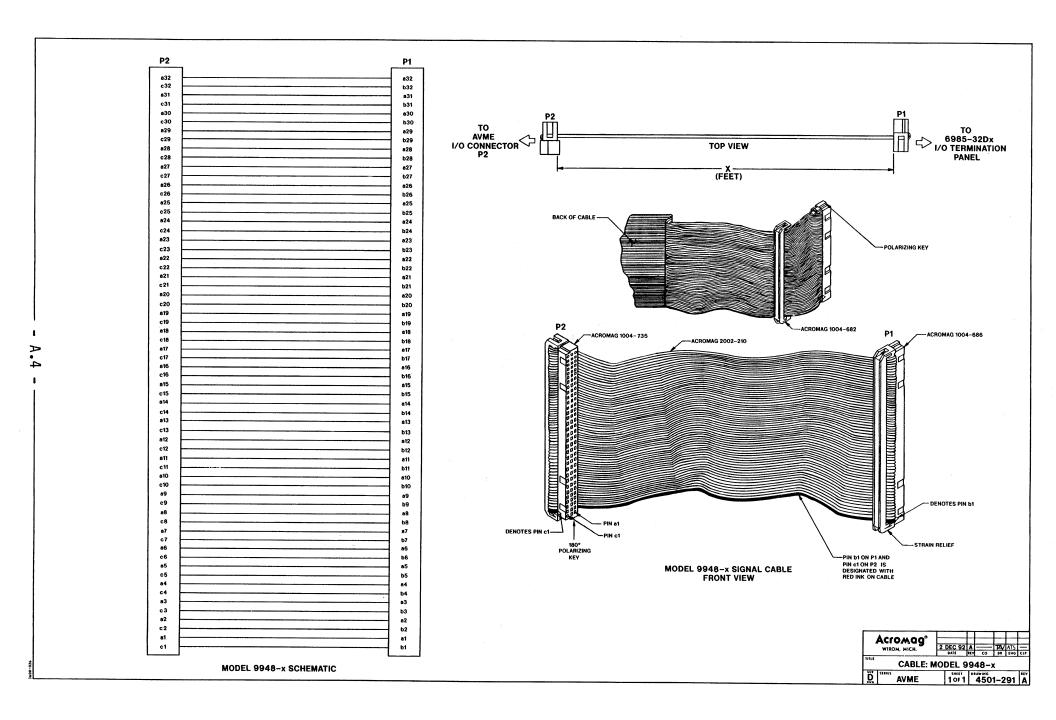

#### **CHAPTER** PAGE 3.1.14 Port F Digital Input Channel Data Register ...... 3.10 **APPENDIX:** A.0 CABLE AND TERMINATION PANELS ...... A.1 A.2 CABLE: MODEL 9948-x..... A.3

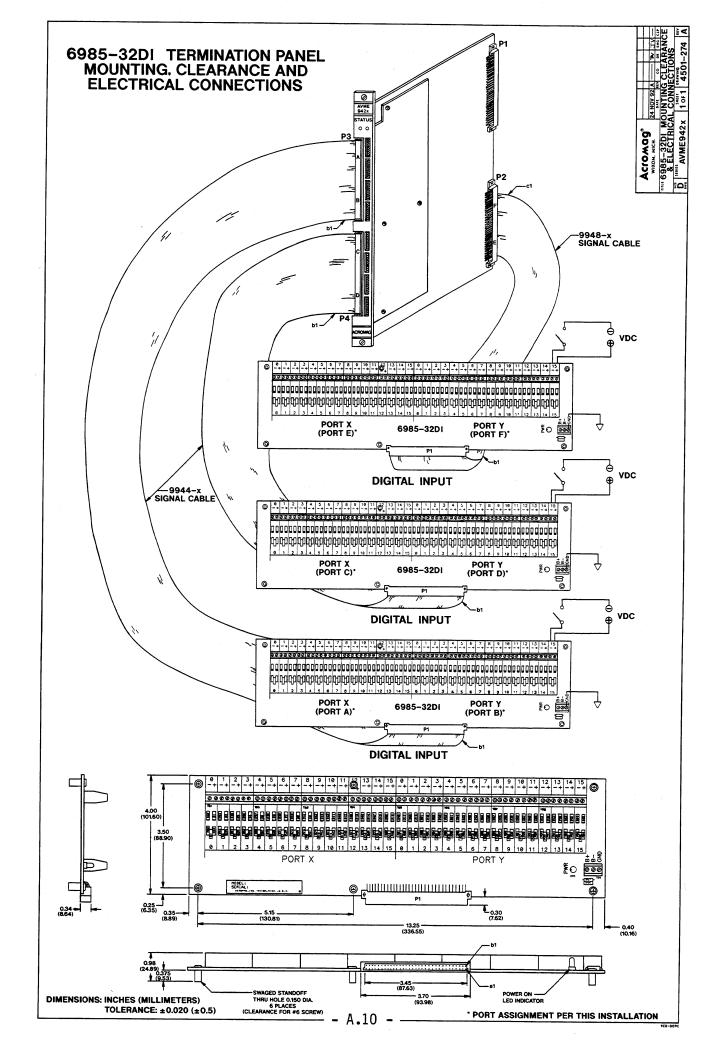

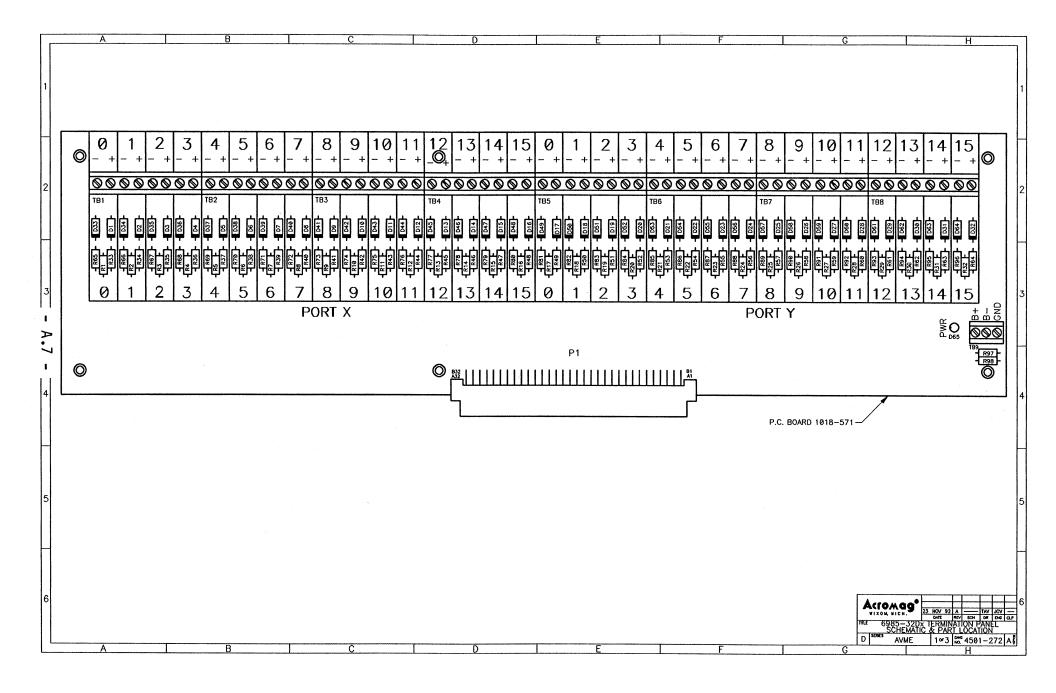

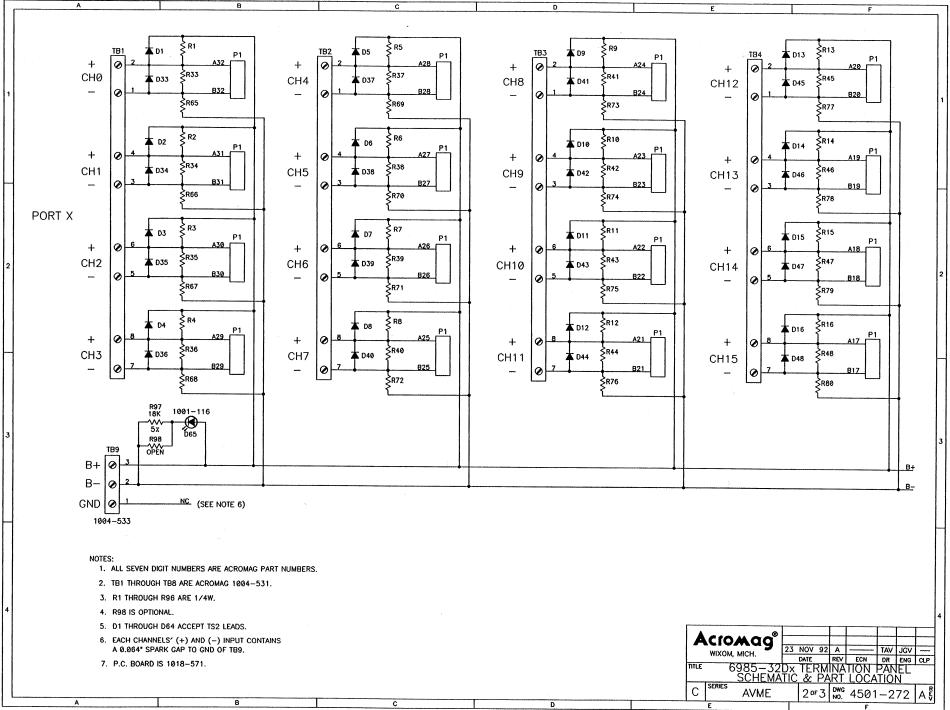

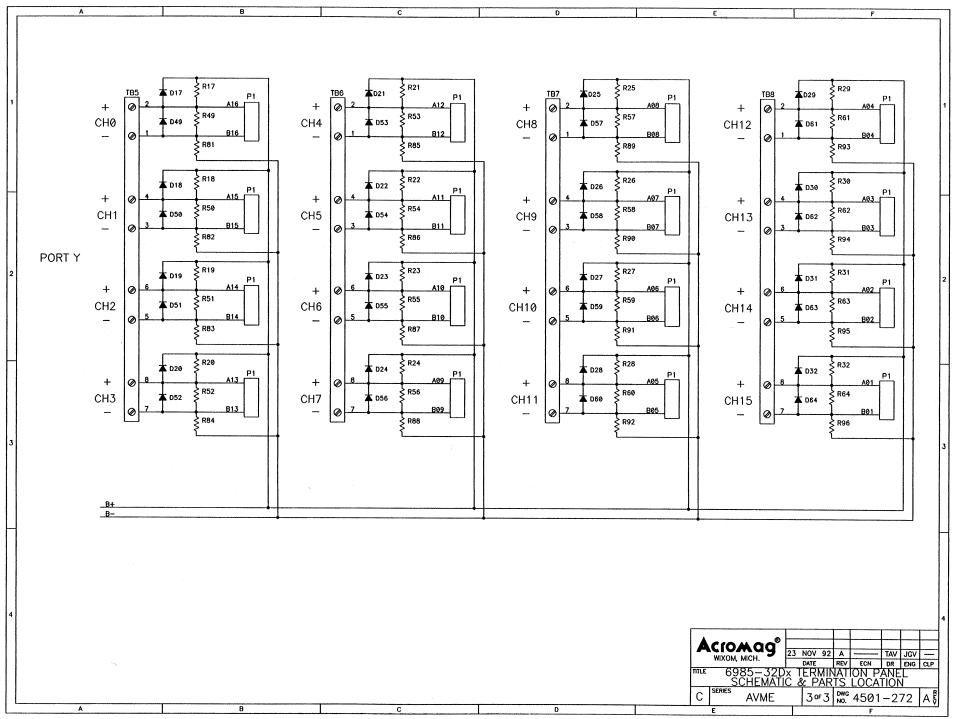

A.3 TERMINATION PANEL: MODEL 6985-32DI ..... A.5

## TABLES:

## PAGE

| 2.2<br>2.3 | P3 CONNECTOR (PORT A & PORT B)<br>P4 CONNECTOR (PORT C & PORT D)<br>P2 CONNECTOR (PORT E & PORT F)                                                                                                                                                               | 2.14<br>2.15 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 5.1        | P1 BUS CONNECTIONS<br>A PARTS LIST FOR MODEL AVME942x-I (MAIN BOARD - PARTS COMMON)<br>B PARTS LIST FOR MODEL AVME9420-I (MAIN BOARD - PARTS UNIQUE)                                                                                                             | 5.2          |

| 5.1<br>5.1 | C PARTS LIST FOR MODEL AVME9421-I (MAIN BOARD - PARTS UNIQUE)<br>D PARTS LIST FOR MODEL AVME9422-I (MAIN BOARD - PARTS UNIQUE)<br>E PARTS LIST FOR MODEL AVME9425-I (MAIN BOARD - PARTS UNIQUE)<br>F PARTS LIST FOR MODEL AVME9426-I (MAIN BOARD - PARTS UNIQUE) | 5.4<br>5.4   |

| 5.1        | G PARTS LIST FOR MODEL AVME9427-I (MAIN BOARD - PARTS UNIQUE)                                                                                                                                                                                                    | 5.5          |

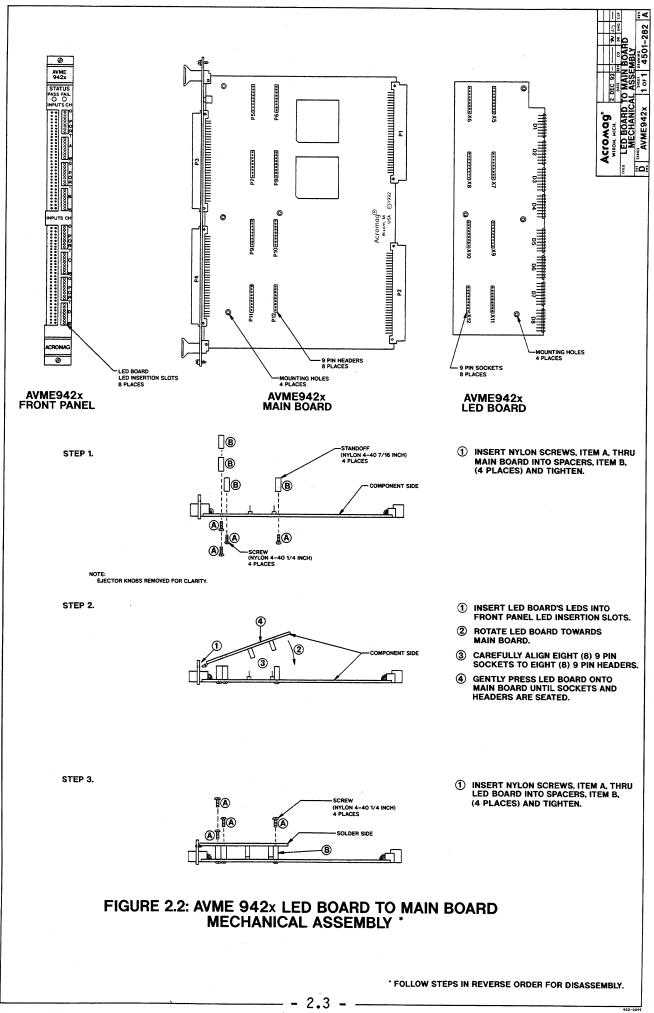

| 2.1        | GURES:<br>AVME942x JUMPER LOCATION DRAWING (4501-281)                                                                                                                                                                                                            |              |

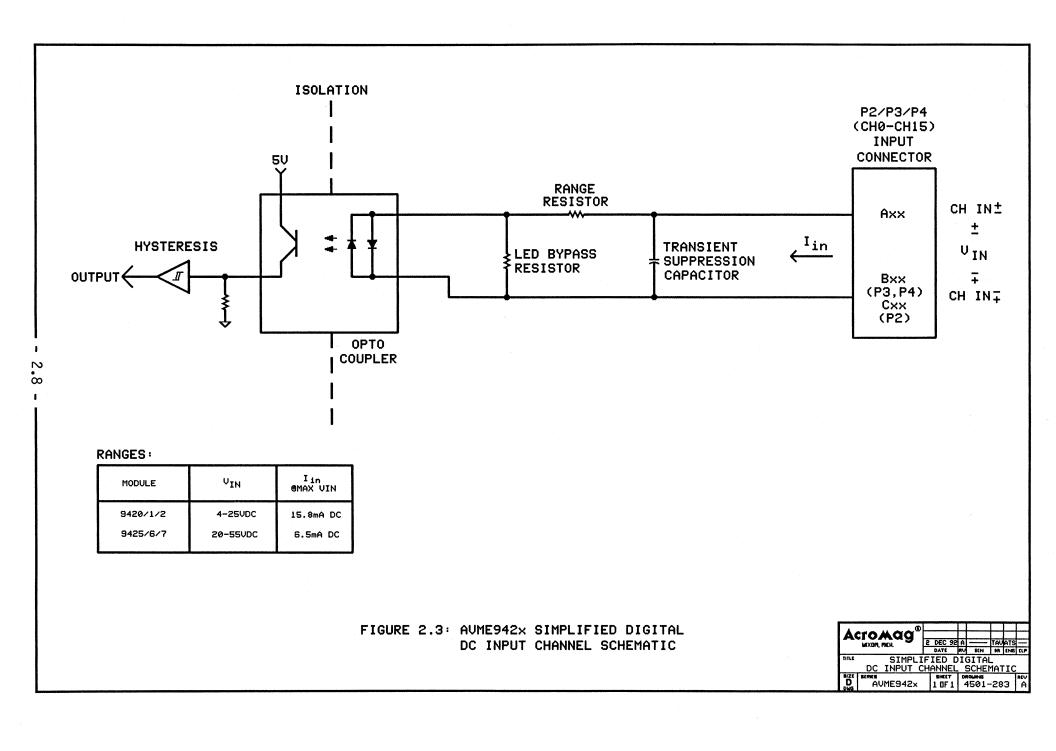

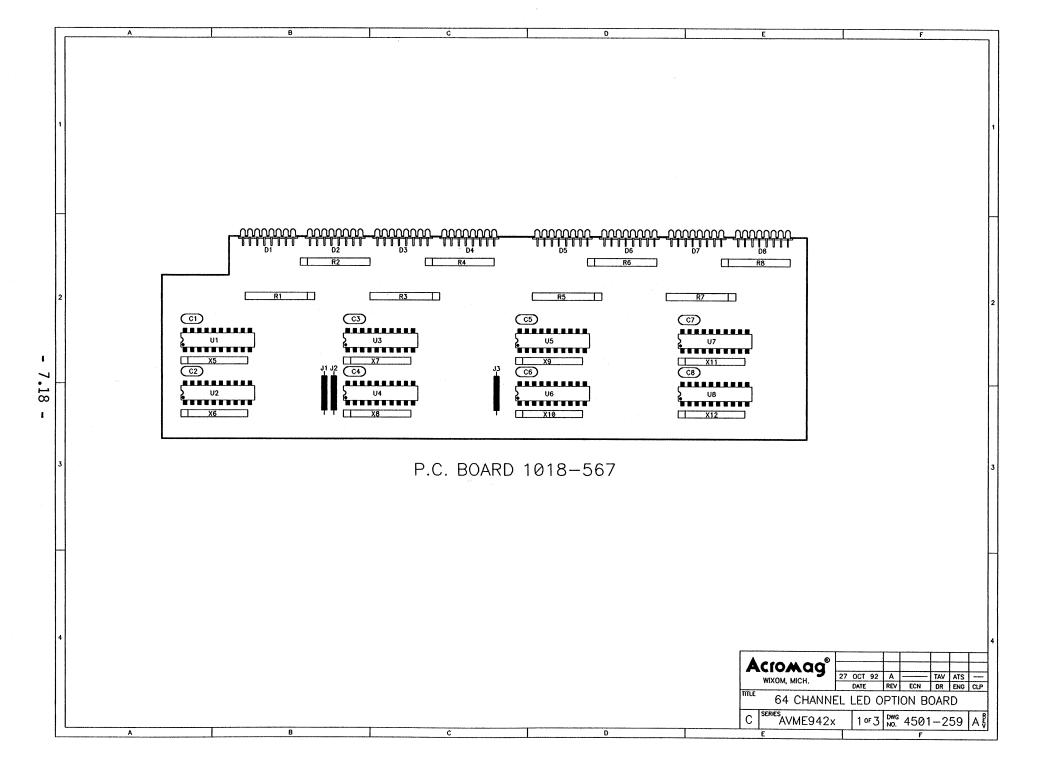

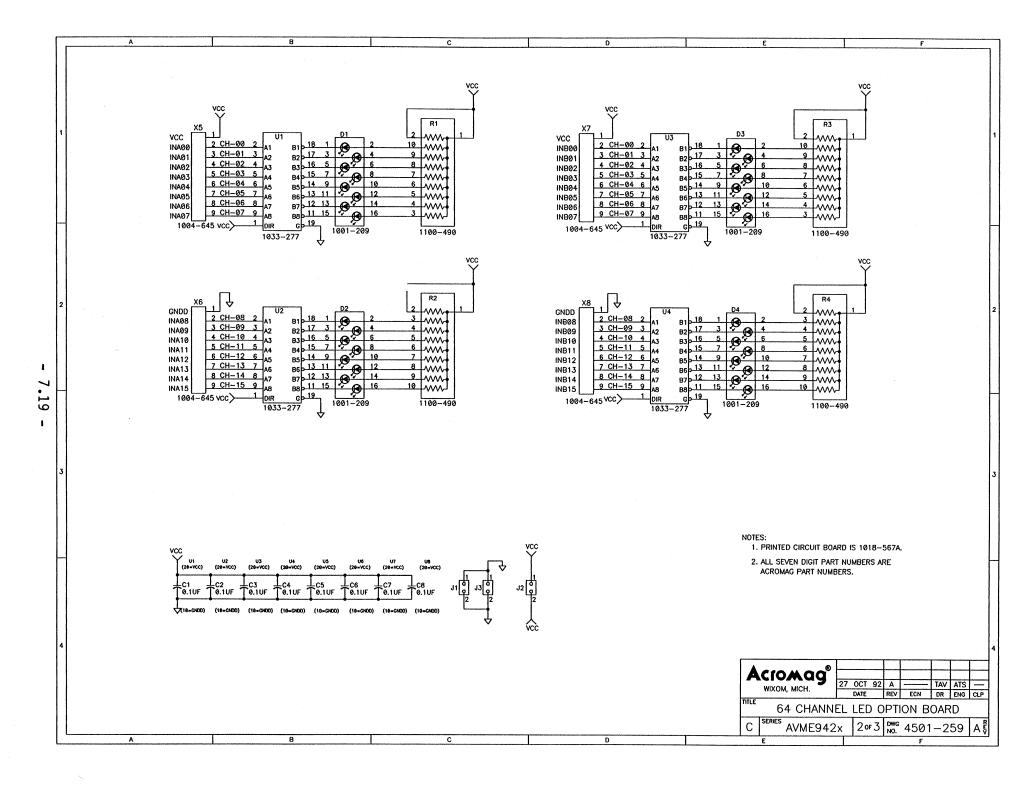

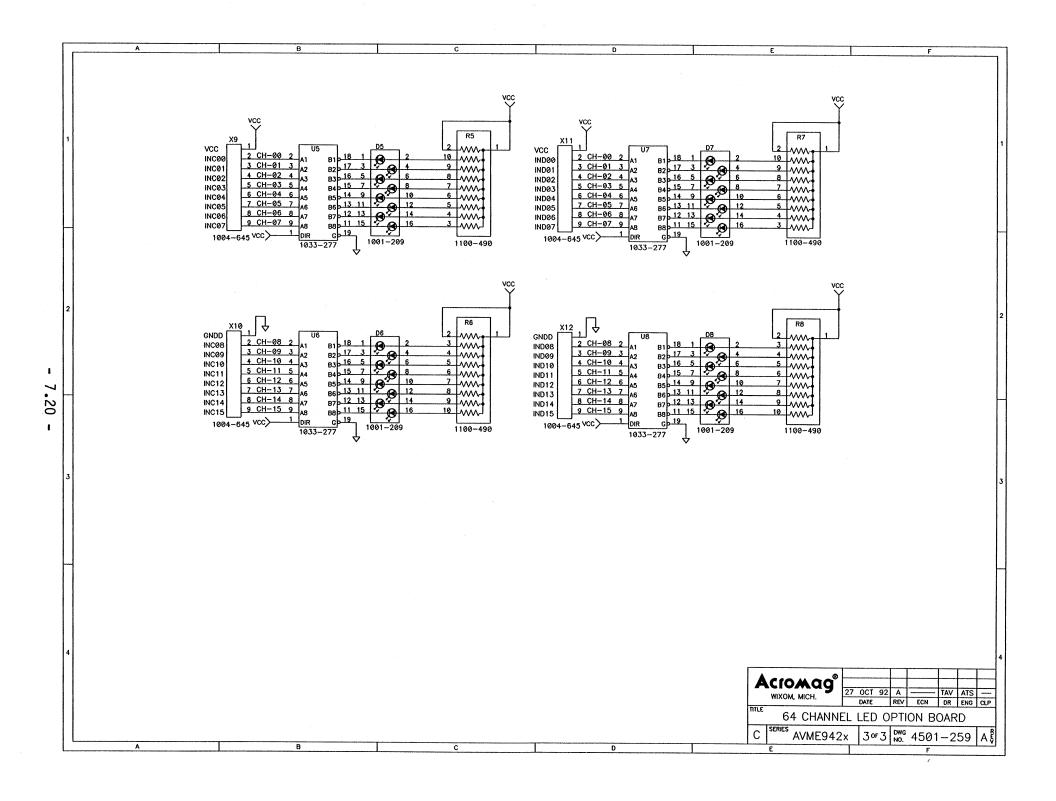

| 2.3<br>2.4 | 2 AVME942x-I-L LED EXPANSION BOARD ASSEMBLY (4501-282)<br>3 AVME942x SIMPLIFIED DIGITAL DC INPUT CHANNEL SCHEMATIC (4501-283)<br>4 AVME942x DIGITAL DC INPUT CHANNEL CONFIGURATIONS (4501-284)<br>5 AVME942x INTERFACE TO TTL AND CMOS SIGNALS (4501-285)        | 2.8<br>2.9   |

| 3.2        | BOARD MEMORY MAP<br>2 AVME9422-I-L BOARD IDENTIFICATION PROM<br>3 AVME942x INPUT RESPONSE AND INTERRUPT TIMING DIAGRAM (4501-286)                                                                                                                                | 3.3          |

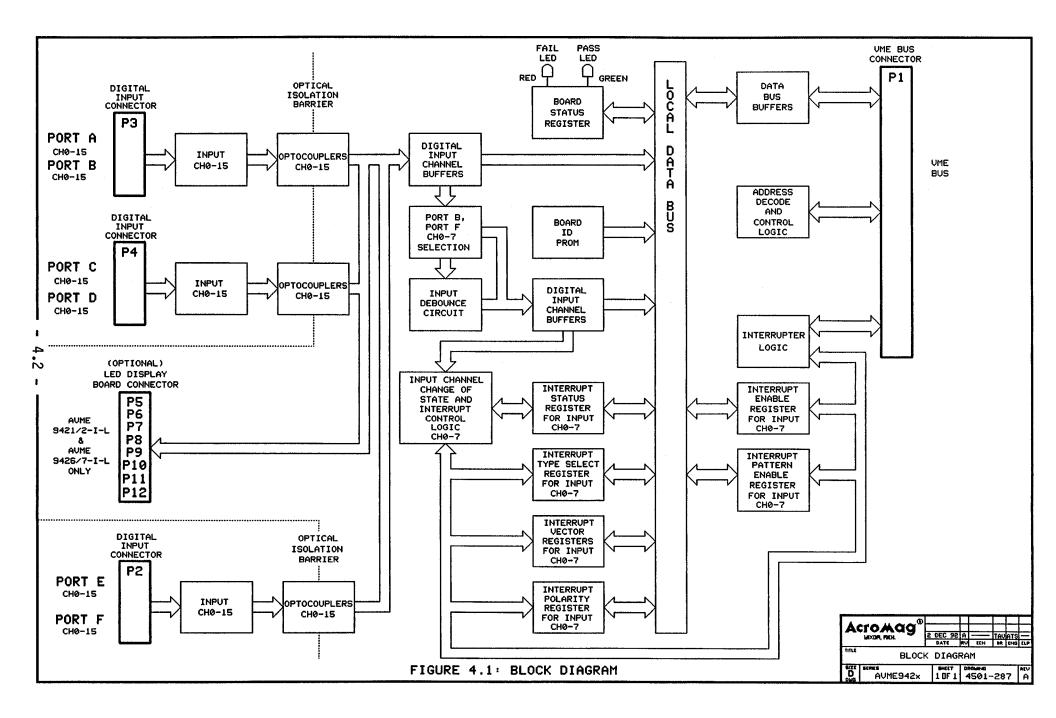

| 4.1        | AVME942x BLOCK DIAGRAM (4501-287)                                                                                                                                                                                                                                | 4.2          |

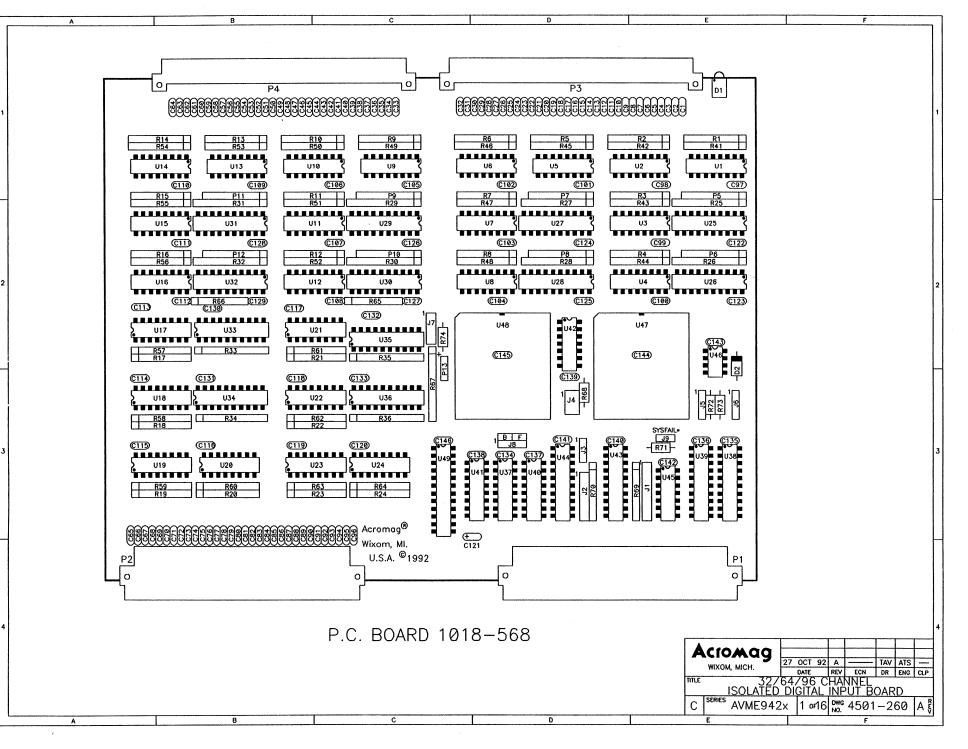

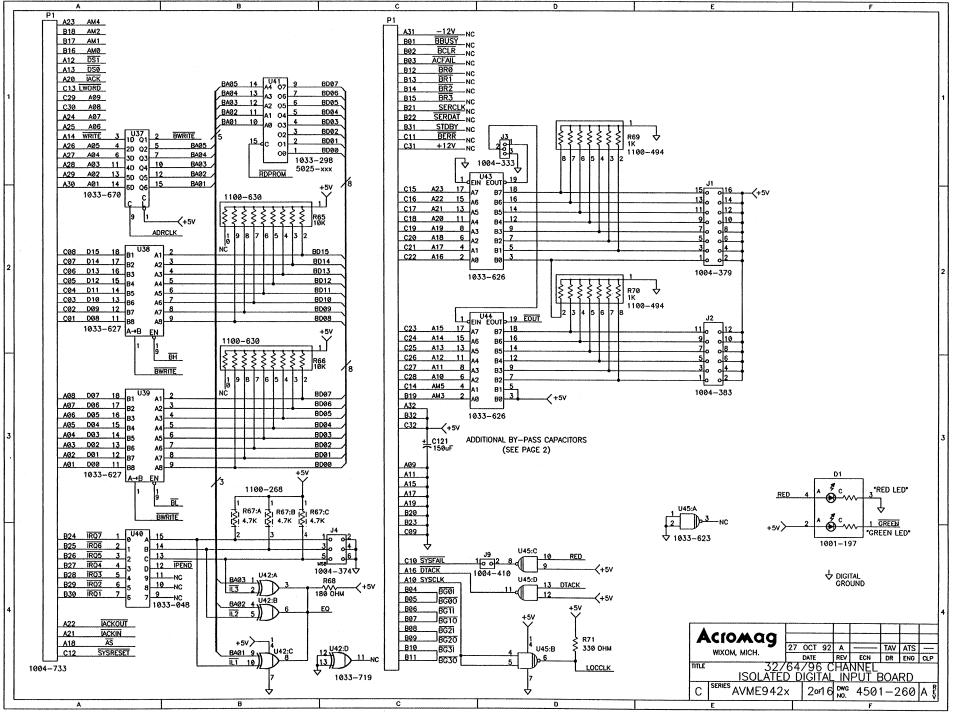

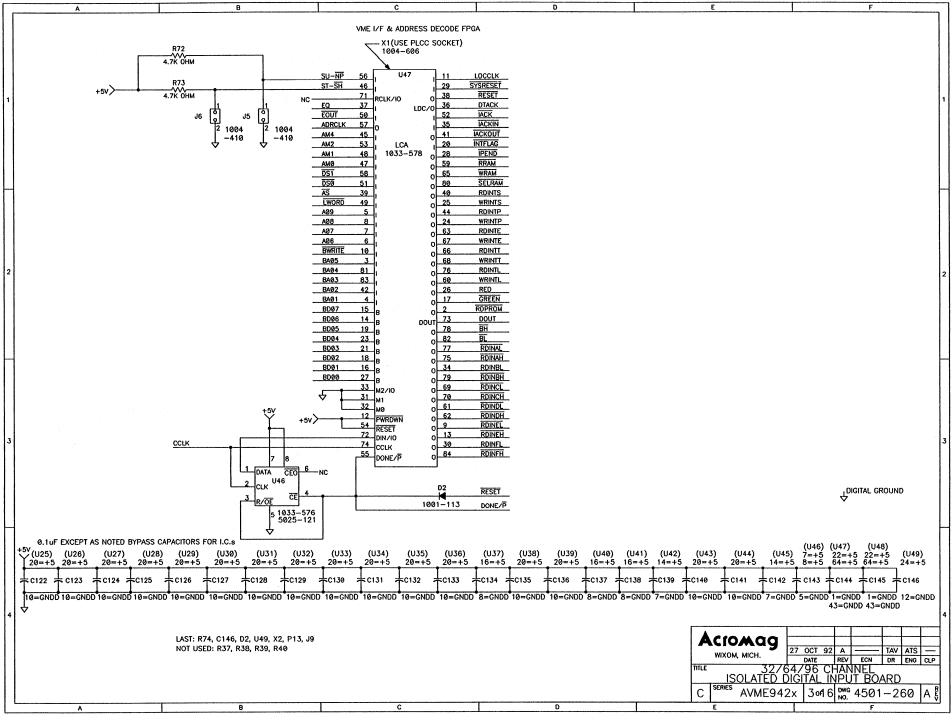

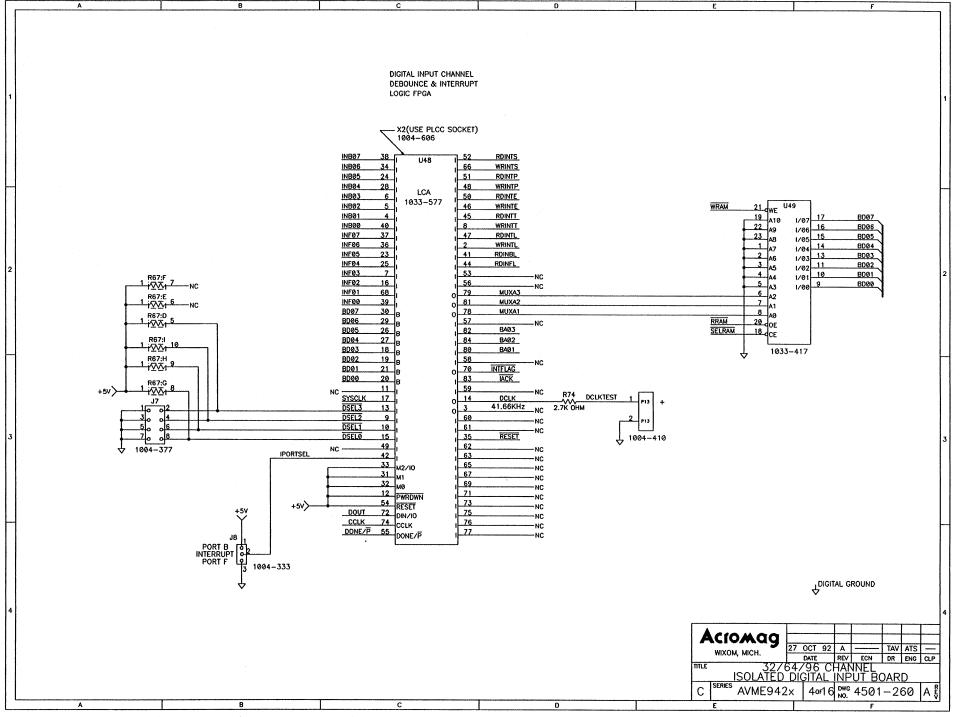

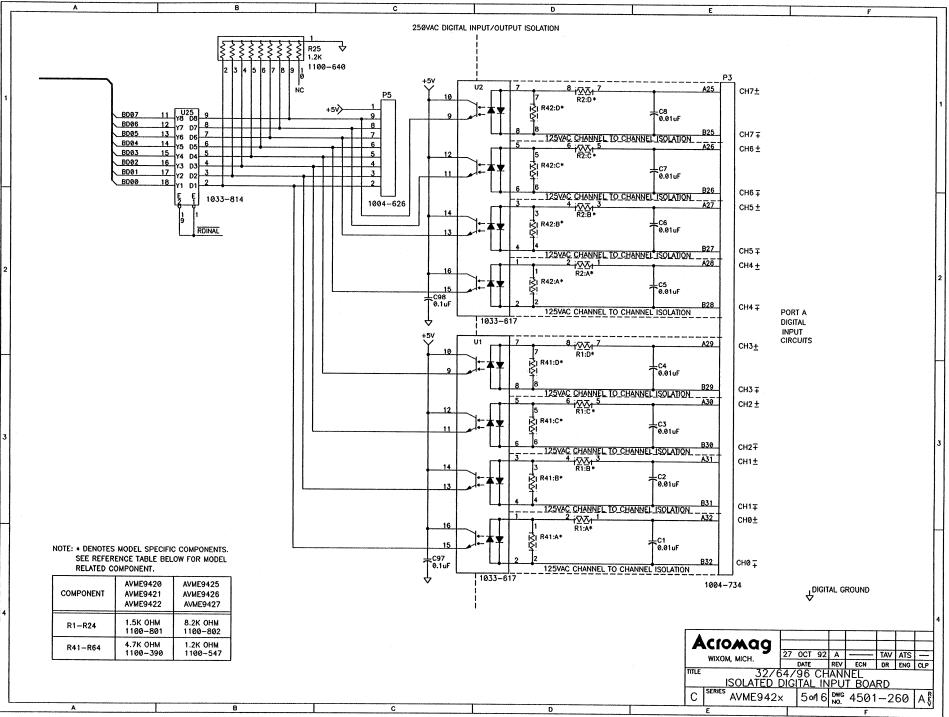

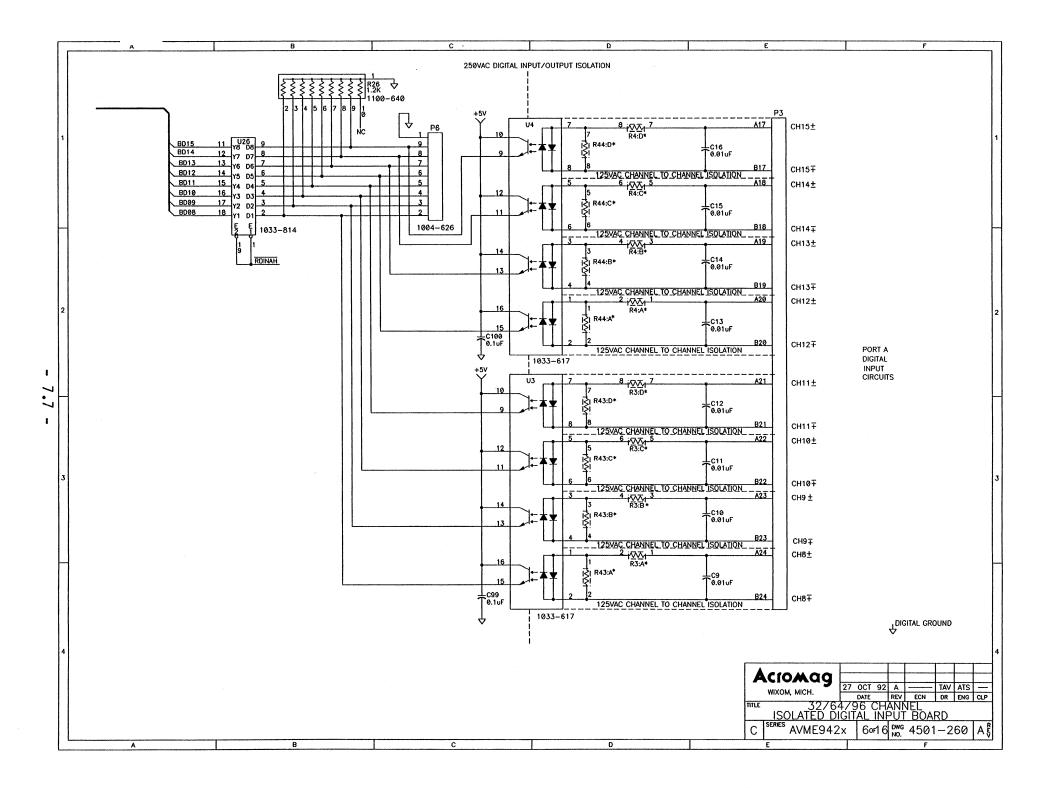

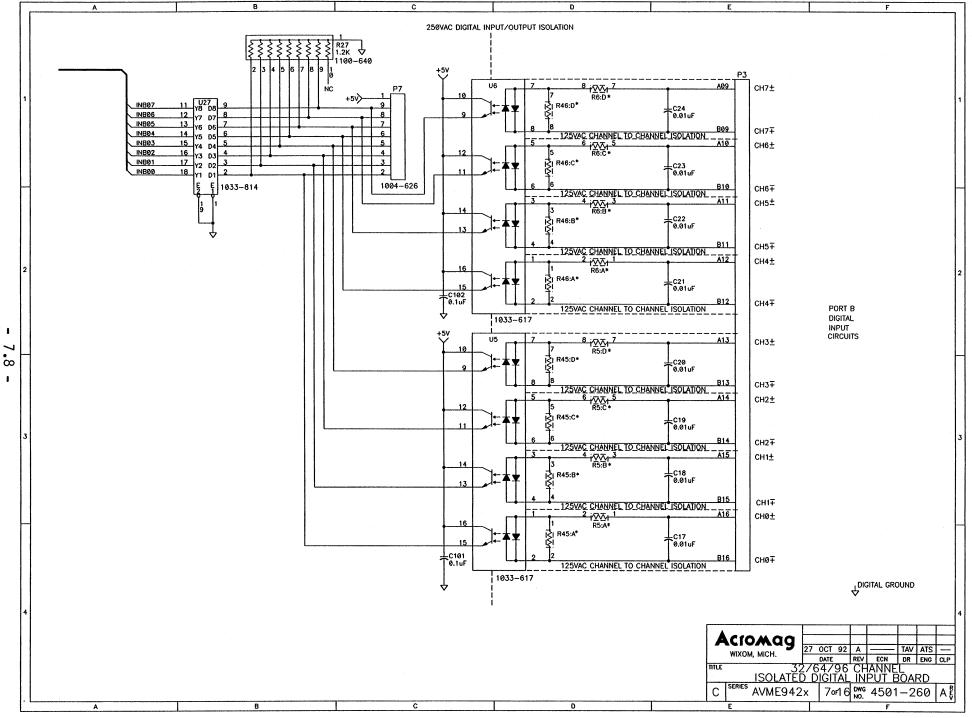

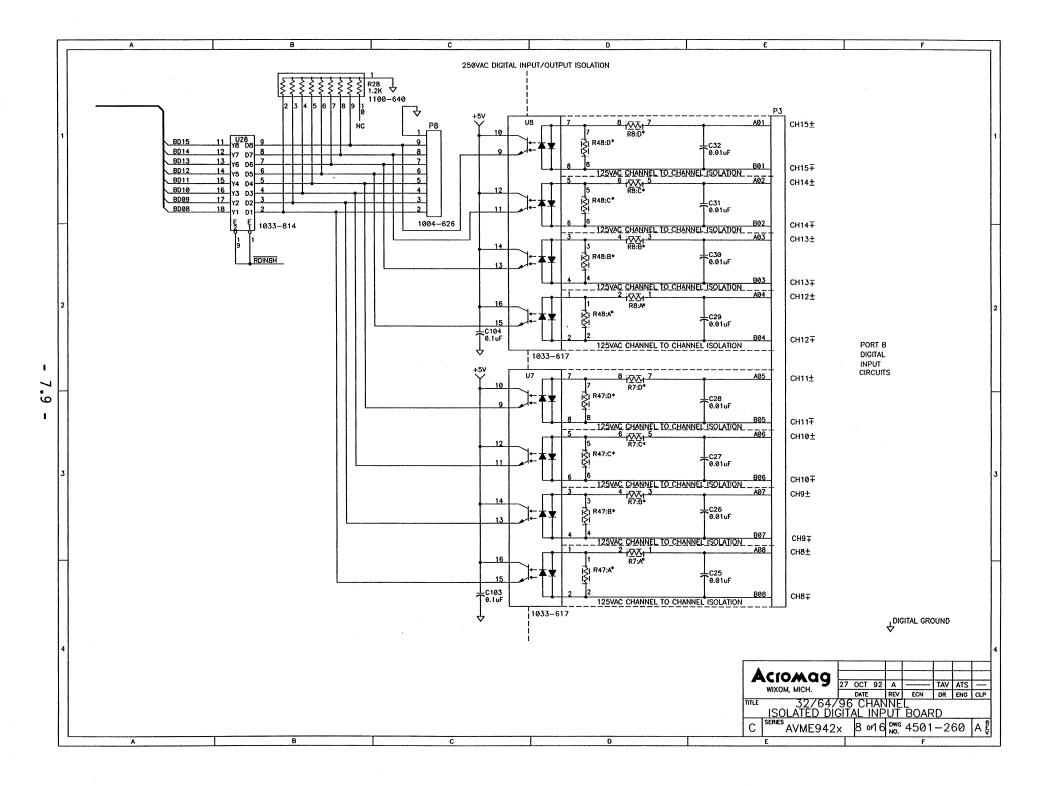

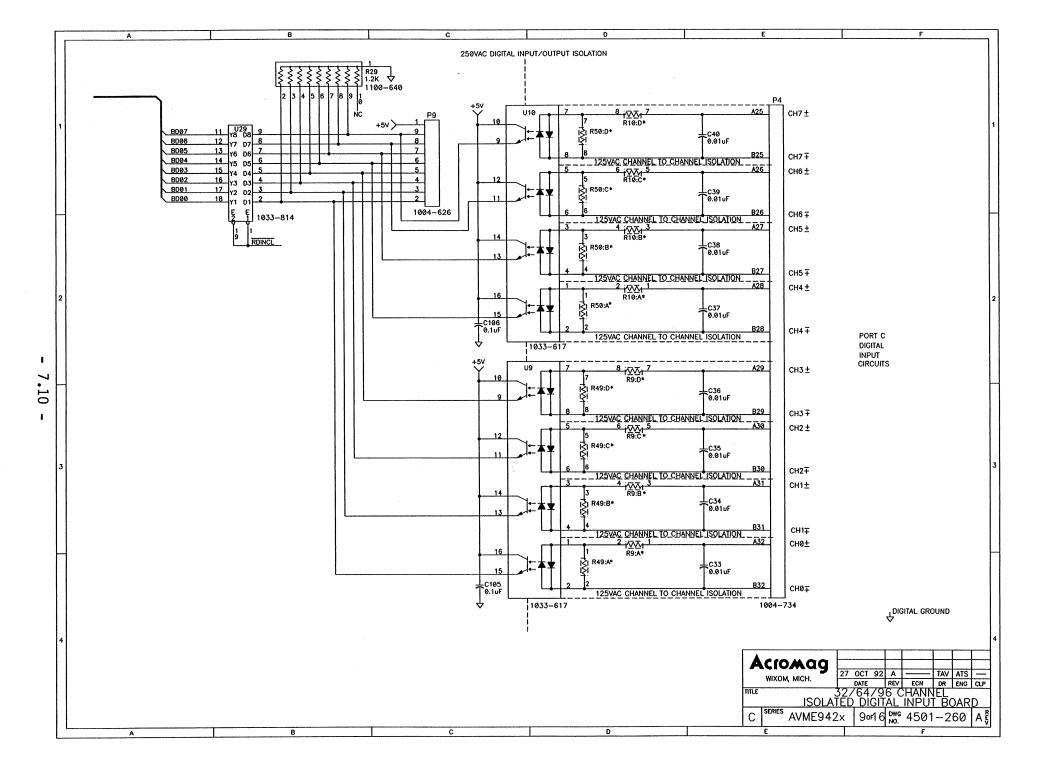

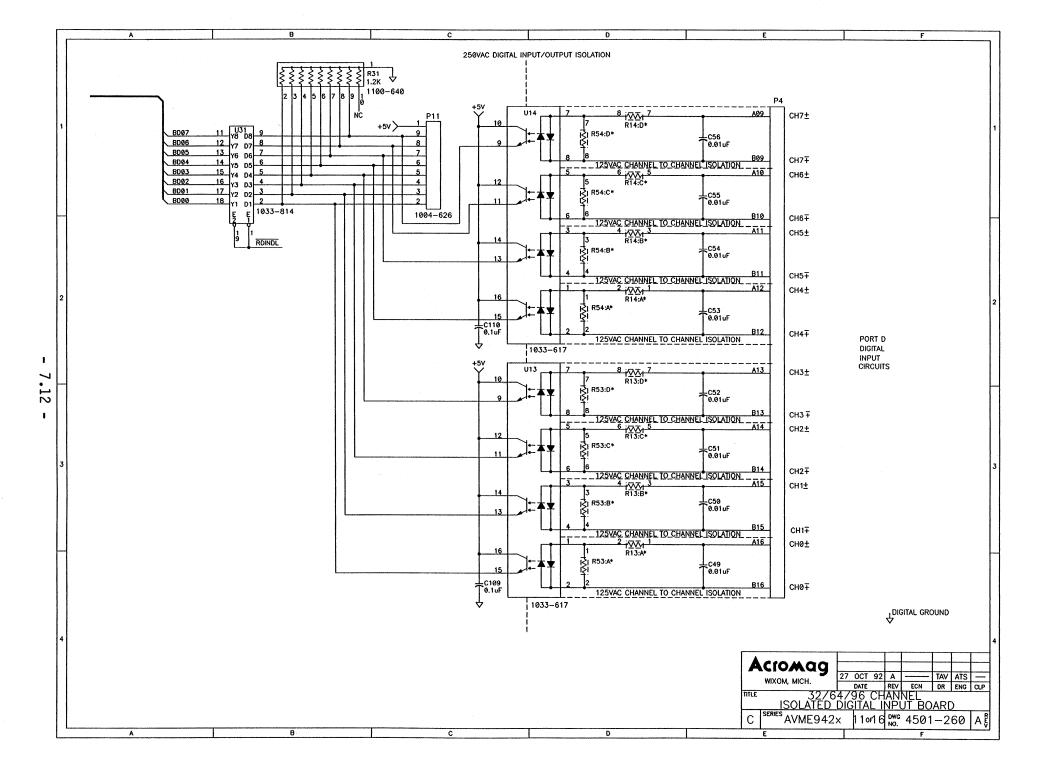

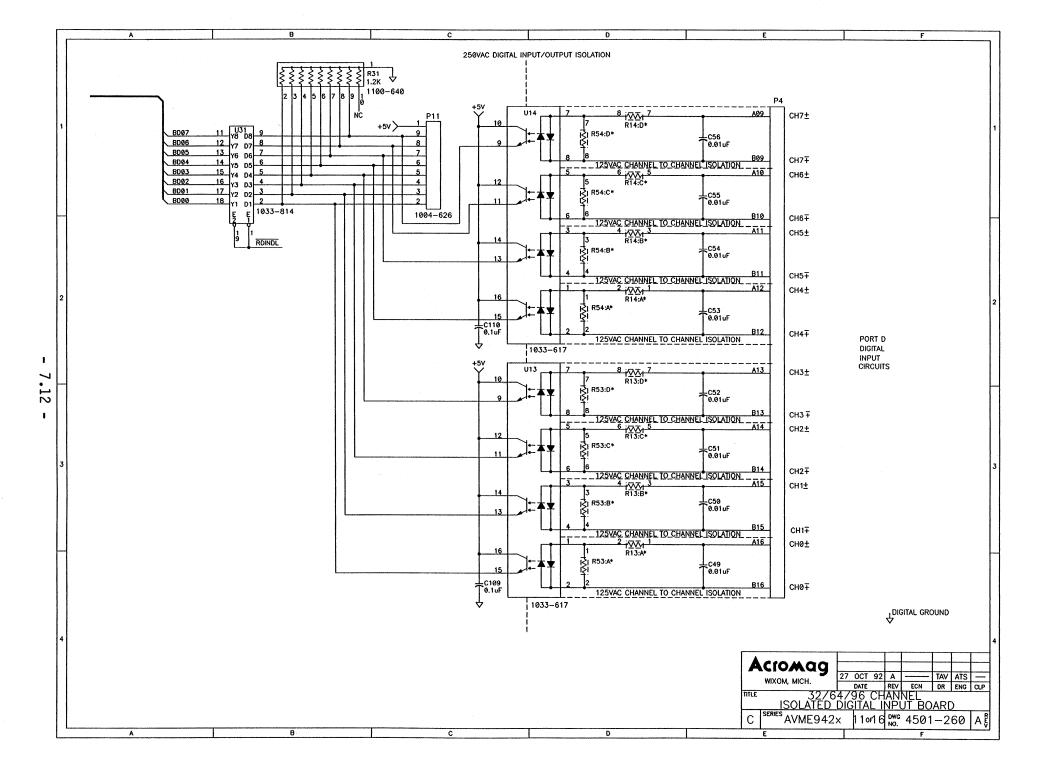

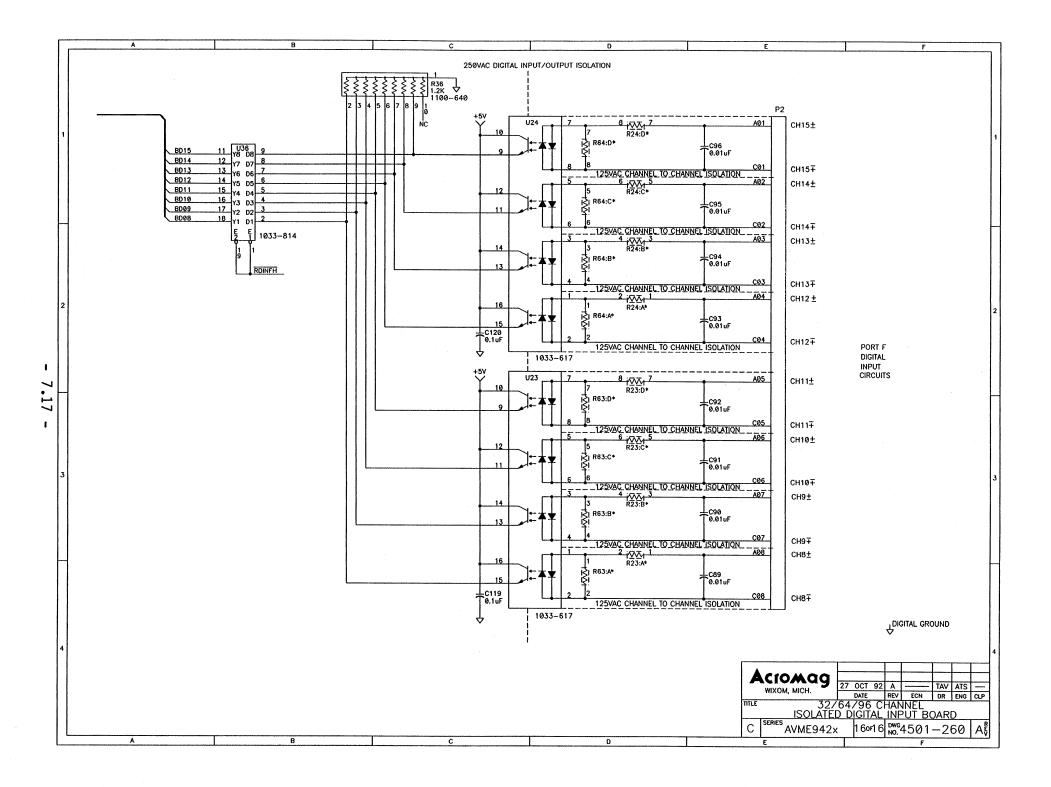

|            | AVME942x SCHEMATIC & PART LOCATION DRAWING (4501-260)<br>AVME942x LED EXP. BOARD SCH. & PART LOC. DRAWING (4501-259)                                                                                                                                             |              |

|            | 9944-X FLAT 64 PIN CABLE (4501-135)<br>9948-X FLAT 64 PIN CABLE (4501-291)<br>6985-32Dx SCHEMATIC & PART LOCATION DRAWING (4501-272)                                                                                                                             | A.4<br>A.7   |

#### **1.0 GENERAL INFORMATION**

#### **1.1 INTRODUCTION**

The AVME9420/9421/9422/9425/9426/9427 Series of VME cards offer a variety of features which make them an ideal choice for many industrial and scientific applications. The AVME9420/9425 contain 32 digital DC voltage input channels, the AVME9421/9426 contain 64 input channels, and the AVME9422/9427 contain 96 input channels. The AVME9420/9421/9422 accept 4-25V DC inputs, while the AVME9425/9426/9427 accept 20-55V DC inputs. In addition, channel status indicators are available on the first 64 channels (P3 and P4) for AVME9421/9426 and AVME9422/9427 models, only.

| Model        | 32 Channel<br>Digital DC<br>Inputs<br>P2 Access | 64 Channel<br>Digital DC<br>Inputs<br>P3, P4 access | 96 Channel<br>Digital DC<br>Inputs P2,<br>P3, P4 access | Channel On<br>LEDs (Green)<br>64 Channels<br>at P3 & P4 |

|--------------|-------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| AVME9420-I   | XX                                              |                                                     |                                                         |                                                         |

| AVME9421-I   |                                                 | XX                                                  |                                                         |                                                         |

| AVME9421-I-L |                                                 | XX                                                  |                                                         | XX                                                      |

| AVME9422-I   |                                                 |                                                     | XX                                                      |                                                         |

| AVME9422-I-L |                                                 |                                                     | XX                                                      | XX                                                      |

| AVME9425-I   | XX                                              |                                                     |                                                         |                                                         |

| AVME9426-I   |                                                 | XX                                                  |                                                         |                                                         |

| AVME9426-I-L |                                                 | XX                                                  |                                                         | XX                                                      |

| AVME9427-I   |                                                 |                                                     | XX                                                      |                                                         |

| AVME9427-I-L |                                                 |                                                     | XX                                                      | XX                                                      |

## **GENERAL FEATURES**

- All Digital DC Inputs are isolated from the VMEbus for up to 250V AC, or 354V DC on a continuous basis (will withstand 1500V AC dielectric strength test for one minute without breakdown).

- All Digital DC Inputs are isolated from each other for up to 125V AC, or 125V DC on a continuous basis (will withstand 1250V AC dielectric strength test for one minute without breakdown).

- PASS/FAIL status indicator LEDs on the front panel.

- Input channel ON indicating green LEDs (with -L option).

- Field connections accessible through connectors P3 and P4 mounted on the front panel (AVME9421/9426 and AVME9422/9427).

- Field connections accessible through connectors mounted on the rear panel (AVME9420/9425 and AVME9422/9427).

- Optional Termination Panel.

## 1.2 DIGITAL DC INPUT FEATURES

- 32 input channels configured as two 16 bit words (AVME9420/9425).

- 64 input channels configured as four 16 bit words (AVME9421/9426).

- 96 input channels configured as six 16 bit words (AVME9422/9427).

- 4 to 25V DC or 20 to 55V DC range boards are available.

- Bidirectional inputs (polarity can be +/- or -/+ at either input of each channel).

- Buffers on all channels contain hysteresis for noise immunity.

- Adjustable debounce circuitry on eight front Port B or eight rear Port F (jumper selectable) channels 0 through 7.

- Generation of interrupts for Port B or Port F (jumper selectable) channels 0 through 7: input Change Of State (COS), input level (polarity) match, or input pattern detection.

- Can be interfaced to TTL & CMOS logic.

- Input channels contain capacitors for transient voltage suppression.

- Input channels contain LED bypass resistors for faster turn-off response.

## **1.3 VMEBUS INTERFACE FEATURES**

- Slave module A24/A16, D16/D08 (EO).

- Short I/O Address Modifiers 29H, 2DH (H = Hex).

- Standard Address Modifiers 39H, 3DH (H = Hex).

- I(1-7) interrupter D08 (O), jumper programmable interrupt level, software programmable interrupt vectors (for Port B or Port F digital input channels 0-7), interrupt release mechanism is Release On Register Access (RORA) type.

- Decode on 1K byte boundaries.

## 1.4 FIELD COMPATIBILITY

See APPENDIX A for more information on compatible products.

#### 1.4.1 DIGITAL INPUTS

Directly compatible with Acromag input termination panel.

Cable:

Model 9944-X: Flat 64 pin cable (female connectors at both ends) for connecting the AVME9421/9422/9426/9427 (P3 or P4 connector) to the 6985-32DI termination panel.

Model 9948-X: Flat 64 pin cable (female connectors at both ends) for connecting the AVME9420/9422/9425/9427 (P2 connector) to the 6985-32DI termination panel.

**Termination Panel:**

Model 6985-32DI: 32 channel input digital termination panel.

## 2.0 PREPARATION FOR USE

This chapter provides information about preparing the Isolated Digital Input Board for system operation.

## 2.1 UNPACKING AND INSPECTION

Inspect the shipping carton immediately upon receipt for evidence of mishandling during transit. If the shipping carton is severely damaged or water stained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is absent when the carton is opened and the contents of the carton are damaged, keep the carton and packing material for the agent's inspection.

For repairs to a product damaged in shipment, refer to the Acromag Service Policy to obtain return instructions. It is suggested that salvageable shipping cartons and packing material be saved for future use in the event the product must be shipped.

The board is physically protected with foam and electrically protected with an antistatic bag during shipment. It is advisable to visually inspect the board for evidence of mishandling prior to applying power.

The board utilizes static sensitive components and should only be handled at a static safe work station.

## 2.2 CARD CAGE CONSIDERATIONS

Refer to the specifications for bus loading and power requirements. Be sure that the system power supplies are able to accommodate the additional requirements within the voltage tolerances specified.

IMPORTANT Adequate air circulation must be provided to prevent a temperature rise above the maximum operating temperature

Adequate air circulation must be provided to prevent a temperature rise above the maximum operating temperature. Large and continuing fluctuations in ambient air temperature should be avoided. If the installation is in an industrial environment and the board is exposed to environmental air, careful consideration should be given to air filtering.

## 2.3 BOARD CONFIGURATION

The board may be configured in a variety of ways for many different applications. Each possible jumper setting will be discussed in the following

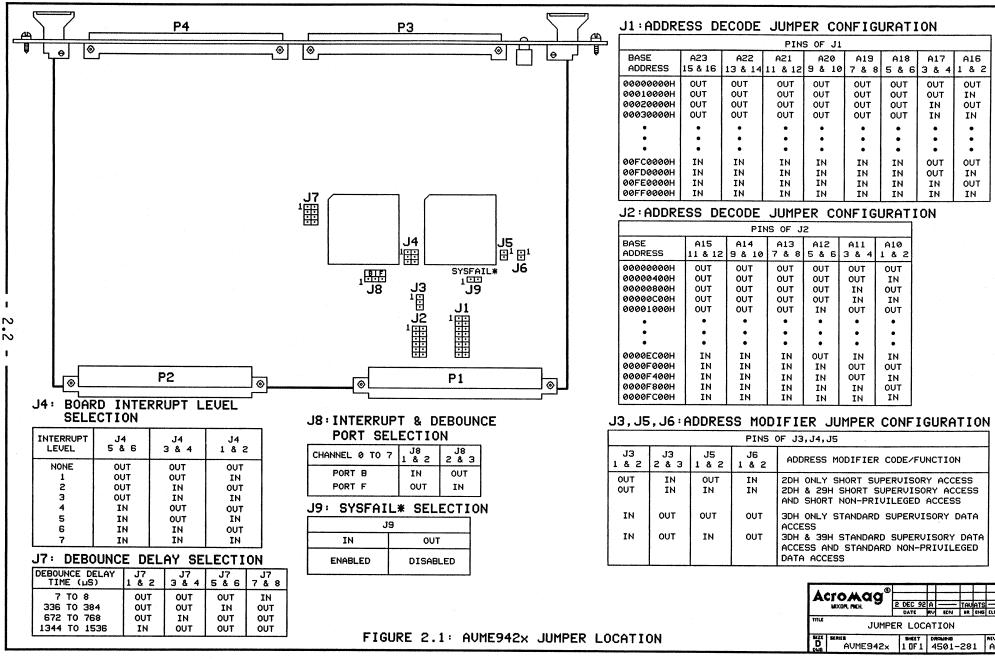

sections. The jumper locations are shown in Figure 2.1.

## 2.3.1 DEFAULT JUMPER CONFIGURATION

#### VMEbus INTERFACE CONFIGURATION

When a board is shipped from the factory, it is configured as follows:

- VMEbus Short I/O Address of 0000H.

- Set to respond to both Address Modifiers 29H and 2DH.

- Sysfail\* enabled to respond to a system failure.

- Interrupt Level: none. Therefore, even if interrupts are enabled, no interrupts will be caused.

#### 2.3.1.1 DIGITAL DC VOLTAGE INPUT DEFAULT CONFIGURATION

- 32, 64 or 96 dedicated digital DC input channels (Port A numbered 0 through 15, Port B numbered 0 through 15, Port C numbered 0 through 15, Port D numbered 0 through 15, Port E numbered 0 through 15 and Port F numbered 0 through 15).

- All channels are board specific for 4-25V DC or 20-55V DC input range.

- Port B channels 0 through 7 are selected for interrupt and debounce on models AVME9421/9422/9426/9427.

- Port F channels 0 through 7 are selected for interrupt and debounce on models AVME9420/9425.

- Minimum input debounce selected.

## 2.4 VMEBUS CONFIGURATION

#### 2.4.1 Address Decode Jumper Configuration

The board interfaces with the VMEbus as a 1K block of address locations in the VMEbus Short I/O Address Space or Standard Address Space. J2 and J1 decode the fourteen most significant address lines A10 through A23 to provide segments of 1K address space. The configuration of the jumpers for different base address locations is shown below. "IN" means that the pins are shorted together with a shorting clip. "OUT" indicates that the clip has been removed. J2 decodes address lines A10 through A15 and J1 decodes Address lines A16 through A23. Therefore, when configured for the Short I/O Address space, only J2 needs to be configured.

## SERIES AVME9420/9421/9422/9425/9426/9427 ISOLATED DIGITAL INPUT BOARDS

|                 | Pins of J2     |               |              |              |              |              |  |  |

|-----------------|----------------|---------------|--------------|--------------|--------------|--------------|--|--|

| Base<br>Address | A15<br>11 & 12 | A14<br>9 & 10 | A13<br>7 & 8 | A12<br>5 & 6 | A11<br>3 & 4 | A10<br>1 & 2 |  |  |

| 0000000H        | OUT            | OUT           | OUT          | OUT          | OUT          | OUT          |  |  |

| 00000400H       | OUT            | OUT           | OUT          | OUT          | OUT          | IN           |  |  |

| 00000800H       | OUT            | OUT           | OUT          | OUT          | IN           | OUT          |  |  |

| 00000C00H       | OUT            | OUT           | OUT          | OUT          | IN           | IN           |  |  |

| 00001000H       | OUT            | OUT           | OUT          | IN           | OUT          | OUT          |  |  |

|                 |                |               |              |              |              |              |  |  |

|                 |                |               |              |              |              |              |  |  |

| 0000EC00H       | IN             | IN            | IN           | OUT          | IN           | IN           |  |  |

| 0000F000H       | IN             | IN            | IN           | IN           | OUT          | OUT          |  |  |

| 0000F400H       | IN             | IN            | IN           | IN           | OUT          | IN           |  |  |

| 0000F800H       | IN             | IN            | IN           | IN           | IN           | OUT          |  |  |

| 0000FC00H       | IN             | IN            | IN           | IN           | IN           | IN           |  |  |

|                 | Pins of J1   |                |                |               |              |              |              |              |  |

|-----------------|--------------|----------------|----------------|---------------|--------------|--------------|--------------|--------------|--|

| Base<br>Address | A23<br>15&16 | A22<br>13 & 14 | A21<br>11 & 12 | A20<br>9 & 10 | A19<br>7 & 8 | A18<br>5 & 6 | A17<br>3 & 4 | A16<br>1 & 2 |  |

| 0000000H        | OUT          | OUT            | OUT            | OUT           | OUT          | OUT          | OUT          | OUT          |  |

| 00010000H       | OUT          | OUT            | OUT            | OUT           | OUT          | OUT          | OUT          | IN           |  |

| 00020000H       | OUT          | OUT            | OUT            | OUT           | OUT          | OUT          | IN           | OUT          |  |

| 00030000H       | OUT          | OUT            | OUT            | OUT           | OUT          | OUT          | IN           | IN           |  |

|                 |              |                |                |               |              |              |              |              |  |

| 00FC0000H       | IN           | IN             | IN             | IN            | IN           | IN           | OUT          | OUT          |  |

| 00FD0000H       | IN           | IN             | IN             | IN            | IN           | IN           | OUT          | IN           |  |

| 00FE0000H       | IN           | IN             | IN             | IN            | IN           | IN           | IN           | OUT          |  |

| 00FF0000H       | IN           | IN             | IN             | IN            | IN           | IN           | IN           | IN           |  |

## 2.4.2 ADDRESS MODIFIER JUMPER CONFIGURATION

The VMEbus Address Modifier jumpers (J3, J5, and J6) permit the board to respond to the various Address Modifier Codes.

|             | Pins of J3, J5, J6 |             |             |                                                                                    |  |  |  |

|-------------|--------------------|-------------|-------------|------------------------------------------------------------------------------------|--|--|--|

| J3<br>1 & 2 | J3<br>2 & 3        | J5<br>1 & 2 | J6<br>1 & 2 | Address Modifier Code/Function                                                     |  |  |  |

| OUT         | IN                 | OUT         | IN          | 2DH Only Short Supervisory Access                                                  |  |  |  |

| OUT         | IN                 | IN          | IN          | 2DH & 29H Short Supervisory Access and<br>Short Non-privileged Access              |  |  |  |

| IN          | OUT                | OUT         | OUT         | 3DH Only Standard Supervisory Data Access                                          |  |  |  |

| IN          | OUT                | IN          | OUT         | 3DH & 39H Standard Supervisory Data Access and Standard Non-privileged Data Access |  |  |  |

#### 2.4.3 INTERRUPT LEVEL SELECT JUMPER CONFIGURATION

The board Interrupt Level is selected by configuring jumper J4 as follows:

| Interrupt<br>level | J4<br>5 & 6 | J4<br>3 & 4 | J4<br>1 & 2 |

|--------------------|-------------|-------------|-------------|

| None               | OUT         | OUT         | OUT         |

| 1                  | OUT         | OUT         | IN          |

| 2                  | OUT         | IN          | OUT         |

| 3                  | OUT         | IN          | IN          |

| 4                  | IN          | OUT         | OUT         |

| 5                  | IN          | OUT         | IN          |

| 6                  | IN          | IN          | OUT         |

| 7                  | IN          | IN          | IN          |

#### 2.4.4 SYSFAIL\* SELECTION JUMPER CONFIGURATION

The AVME942x non-intelligent slave boards assert the SYSFAIL\* signal as described in the VMEbus Specification Rev. C.1, when J9 is installed (the pins are shorted together with a shorting clip). Removing jumper J9 will disconnect the SYSFAIL\* line from the circuitry on the Acromag board.

## 2.5 DIGITAL INPUT CONFIGURATION

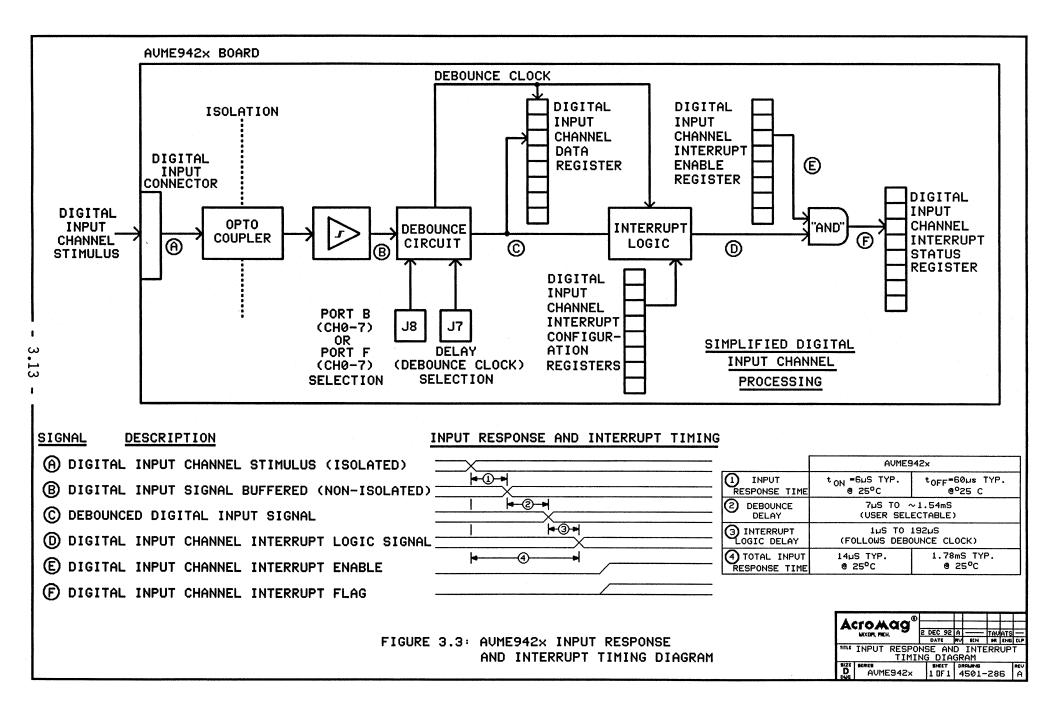

Board specific, low range or high range, input threshold voltages make the digital input channels adaptable to almost any application. The inputs are designed for use with contact closures, switches, alarm trips, and power supply ON/OFF monitoring. Input channels are optically isolated from each other and from the VMEbus. See Figure 2.3 for the simplified schematic of a digital DC input channel for the AVME942x.

Input channel debounce circuitry with selectable delay is provided for Port B or Port F (jumper selectable) channels 0 through 7 to eliminate glitches from the input signals. These glitches are frequently caused by contact bounce in mechanical relays and switches.

Input channel interrupt functions are provided for Port B or Port F (jumper selectable) channels 0 through 7. Each selected channel can be programmed to interrupt for Change Of State (COS), input level (polarity) match, or input pattern match of the input levels.

#### 2.5.1 DIGITAL DC INPUT THRESHOLD SELECTION

Two input threshold voltages are available, 4-25V DC or 20-55V DC, on a per board basis, as shown in the following table:

| Module             | Channel Range | Positive Threshold Voltage<br>(Maximum) |

|--------------------|---------------|-----------------------------------------|

| AVME9420/9421/9422 | 4-25V DC      | 4V DC                                   |

| AVME9425/9426/9427 | 20-55V DC     | 20V DC                                  |

## 2.5.2 SENSING CONTACT CLOSURES AND SWITCHES

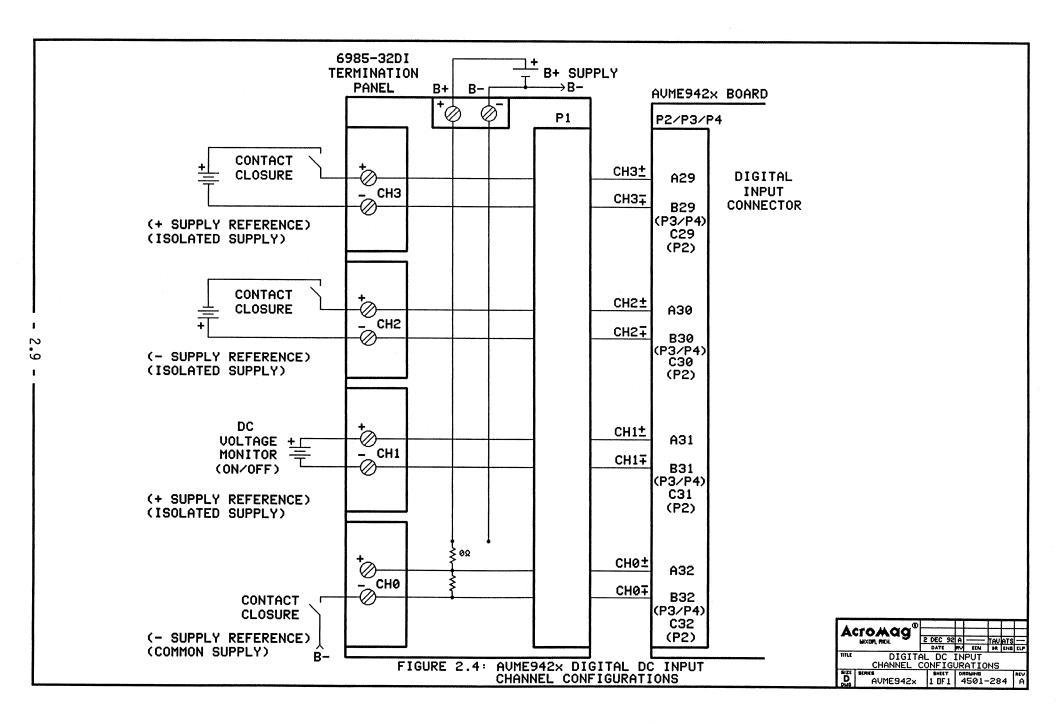

The DC input voltage should be within the range listed in the previous table. See Figure 2.4: Digital DC Input Channel Configurations, for connections for different input types.

## 2.5.3 DEBOUNCE DELAY SELECTION

If mechanical relay contacts (or switches) are used as inputs, then the Port B or Port F channels 0 through 7 should be selected to take advantage of the debounce circuitry on the port. Also, it is strongly recommended that a debounce delay longer than the maximum expected bounce time be used. If the bounce time cannot be determined, then the maximum debounce delay should be selected.

The debounce delay time is jumper programmable (J7) on a global basis for all Port B or Port F input channels 0 through 7 (i.e. all selected input channels will have the same delay), as shown in the following table:

| Debounce<br>Delay Time (uS) | J7<br>1 & 2 | J7<br>3 & 4 | J7<br>5 & 6 | J7<br>7 & 8 |

|-----------------------------|-------------|-------------|-------------|-------------|

| 7 to 8                      | OUT         | OUT         | OUT         | IN          |

| 336 to 384                  | OUT         | OUT         | IN          | OUT         |

| 672 to 768                  | OUT         | IN          | OUT         | OUT         |

| 1344 to 1536                | IN          | OUT         | OUT         | OUT         |

NOTE: One of the debounce delay times must be selected. If none or more than one delay time is selected, the Port B or Port F channels 0 through 7 input signals will not pass through the debounce circuit.

#### 2.5.4 INTERRUPT AND DEBOUNCE PORT SELECTION

The interrupt and debounce port is jumper selectable (J8) on a global basis for all Port B or Port F input channels 0 through 7 (i.e. all port selected input channels will be able to cause interrupts and will have the same delay), as shown in the following table:

| Channels<br>(0-7) | J8<br>1 & 2 | J8<br>2 & 3 |

|-------------------|-------------|-------------|

| Port B            | IN          | OUT         |

| Port F            | OUT         | IN          |

NOTE: One of the interrupt and debounce ports must be selected. If none is selected, the Port B or Port F channels 0 through 7 input signals may not pass through the interrupt and debounce circuit.

## 2.5.5 DIGITAL INPUT INTERFACE TO TTL AND CMOS SIGNALS

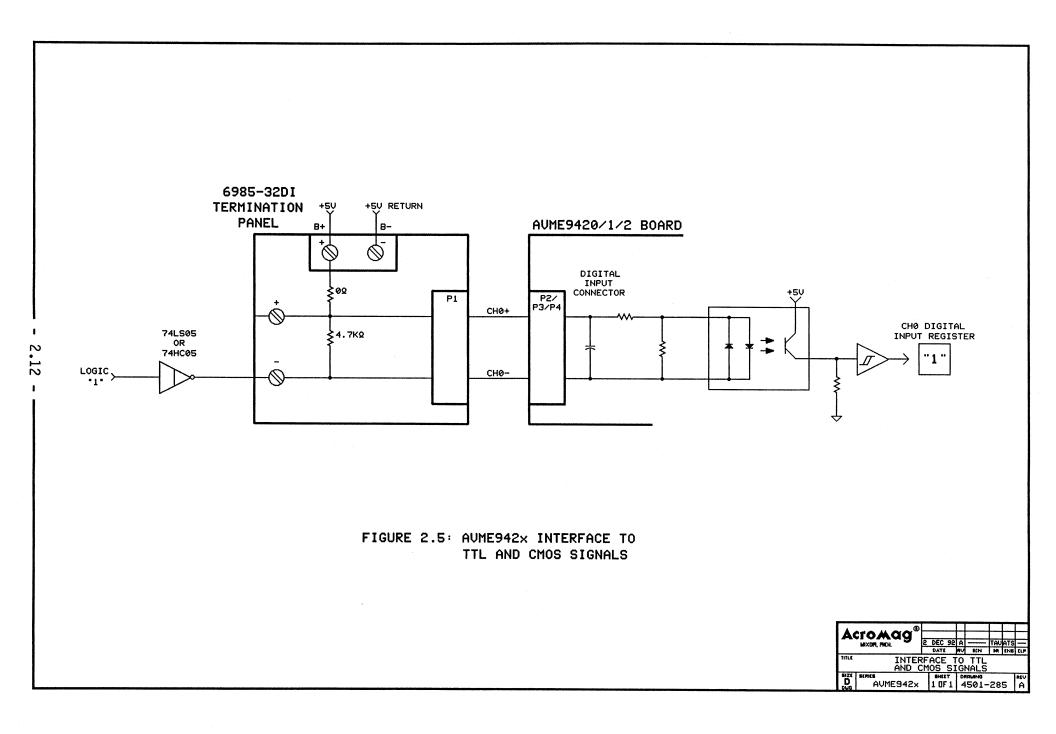

Logic level inputs can be interfaced to the board by the use of common logic elements such as the 74LS05 (or 74HC05) open collector (or drain) inverter gates. See Figure 2.5: AVME942x Interface to TTL and CMOS Signals, for connection information. Applying a logic "1" to the input of the inverter gate sinks the current required to turn the opto-coupler ON (using the lowest input voltage range) and yields a logic "1" for the corresponding input channel register bit position.

## 2.6 CONNECTORS

#### 2.6.1 DIGITAL INPUT CONNECTOR (PORT A & PORT B)

The first group of 32 digital inputs (Port A channels 0 through 15 and Port B channels 0 through 15) are connected to the AVME9421/9422/9426/9427 board via connector P3 (upper connector as viewed from the front). Table 2.1 defines the assignment. These connections are easily accommodated through the use of Acromag termination panels and flat cable assemblies or through the use of a user defined termination panel.

P3: DIN 41612 Type B Level II, 64 Pin Male Connector. Panduit No. 100-064-033B or equiv.

| Port | Pin Number | Mnemonic | Pin Number | Mnemonic |

|------|------------|----------|------------|----------|

|      | 32A        | CH0 +/-  | 32B        | CH0-/+   |

|      | 31A        | CH1+/-   | 31B        | CH1-/+   |

|      | 30A        | CH2+/-   | 30B        | CH2-/+   |

|      | 29A        | CH3+/-   | 29B        | CH3-/+   |

|      | 28A        | CH4+/-   | 28B        | CH4-/+   |

| Р    | 27A        | CH5+/-   | 27B        | CH5-/+   |

| 0    | 26A        | CH6+/-   | 26B        | CH6-/+   |

| R    | 25A        | CH7+/-   | 25B        | CH7-/+   |

| Т    | 24A        | CH8+/-   | 24B        | CH8-/+   |

|      | 23A        | CH9+/-   | 23B        | CH9-/+   |

| А    | 22A        | CH10+/-  | 22B        | CH10-/+  |

|      | 21A        | CH11+/-  | 21B        | CH11-/+  |

|      | 20A        | CH12+/-  | 20B        | CH12-/+  |

|      | 19A        | CH13+/-  | 19B        | CH13-/+  |

|      | 18A        | CH14+/-  | 18B        | CH14-/+  |

|      | 17A        | CH15+/-  | 17B        | CH15-/+  |

|      | 16A        | CH0+/-   | 16B        | CH0-/+   |

|      | 15A        | CH1+/-   | 15B        | CH1-/+   |

|      | 14A        | CH2+/-   | 14B        | CH2-/+   |

|      | 13A        | CH3+/-   | 13B        | CH3-/+   |

|      | 12A        | CH4+/-   | 12B        | CH4-/+   |

| Р    | 11A        | CH5+/-   | 11B        | CH5-/+   |

| 0    | 10A        | CH6+/-   | 10B        | CH6-/+   |

| R    | 9A         | CH7+/-   | 9B         | CH7-/+   |

| Т    | 8A         | CH8+/-   | 8B         | CH8-/+   |

|      | 7A         | CH9+/-   | 7B         | CH9-/+   |

| В    | 6A         | CH10+/-  | 6B         | CH10-/+  |

|      | 5A         | CH11+/-  | 5B         | CH11-/+  |

|      | 4A         | CH12+/-  | 4B         | CH12-/+  |

|      | 3A         | CH13+/-  | 3B         | CH13-/+  |

|      | 2A         | CH14+/-  | 2B         | CH14-/+  |

|      | 1A         | CH15+/-  | 1B         | CH15-/+  |

Table 2.1: P3 CONNECTOR (PORT A & B)

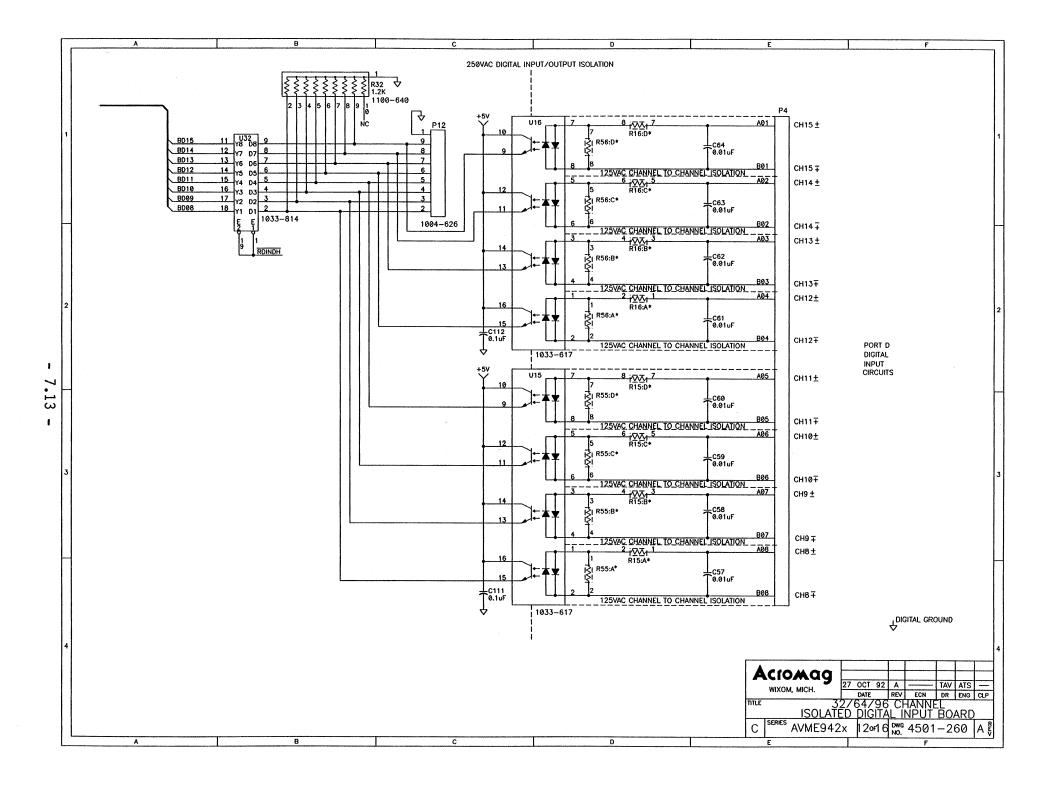

## 2.6.2 DIGITAL INPUT CONNECTOR (PORT C & PORT D)

The second group of 32 digital inputs (Port C channels 0 through 15 and Port D channels 0 through 15) are connected to the AVME9421/9422/9426/9427 board via connector P4 (lower connector as viewed from the front). Table 2.2 defines the assignment. These connections are easily accommodated through the use of Acromag termination panels and flat cable assemblies or through the use of a user defined termination panel.

P4: DIN 41612 Type B Level II, 64 Pin Male Connector. Panduit No. 100-064-033B or equiv.

|      | UNNECTOR   | (PORT C & D) | 1          | · · · · · · · · · · · · · · · · · · · |

|------|------------|--------------|------------|---------------------------------------|

| Port | Pin Number | Mnemonic     | Pin Number | Mnemonic                              |

|      | 32A        | CH0+/-       | 32B        | CH0-/+                                |

|      | 31A        | CH1+/-       | 31B        | CH1-/+                                |

|      | 30A        | CH2+/-       | 30B        | CH2-/+                                |

|      | 29A        | CH3+/-       | 29B        | CH3-/+                                |

|      | 28A        | CH4+/-       | 28B        | CH4-/+                                |

| Р    | 27A        | CH5+/-       | 27B        | CH5-/+                                |

| 0    | 26A        | CH6+/-       | 26B        | CH6-/+                                |

| R    | 25A        | CH7+/-       | 25B        | CH7-/+                                |

| Т    | 24A        | CH8+/-       | 24B        | CH8-/+                                |

|      | 23A        | CH9+/-       | 23B        | CH9-/+                                |

| С    | 22A        | CH10+/-      | 22B        | CH10-/+                               |

|      | 21A        | CH11+/-      | 21B        | CH11-/+                               |

|      | 20A        | CH12+/-      | 20B        | CH12-/+                               |

|      | 19A        | CH13+/-      | 19B        | CH13-/+                               |

|      | 18A        | CH14+/-      | 18B        | CH14-/+                               |

|      | 17A        | CH15+/-      | 17B        | CH15-/+                               |

|      | 16A        | CH0+/-       | 16B        | CH0-/+                                |

|      | 15A        | CH1+/-       | 15B        | CH1-/+                                |

|      | 14A        | CH2+/-       | 14B        | CH2-/+                                |

|      | 13A        | CH3+/-       | 13B        | CH3-/+                                |

|      | 12A        | CH4+/-       | 12B        | CH4-/+                                |

| Р    | 11A        | CH5+/-       | 11B        | CH5-/+                                |

| 0    | 10A        | CH6+/-       | 10B        | CH6-/+                                |

| R    | 9A         | CH7+/-       | 9B         | CH7-/+                                |

| Т    | 8A         | CH8+/-       | 8B         | CH8-/+                                |

|      | 7A         | CH9+/-       | 7B         | CH9-/+                                |

| D    | 6A         | CH10+/-      | 6B         | CH10-/+                               |

|      | 5A         | CH11+/-      | 5B         | CH11-/+                               |

|      | 4A         | CH12+/-      | 4B         | CH12-/+                               |

|      | 3A         | CH13+/-      | 3B         | CH13-/+                               |

|      | 2A         | CH14+/-      | 2B         | CH14-/+                               |

|      | 1A         | CH15+/-      | 1B         | CH15-/+                               |

Table 2.2: P4 CONNECTOR (PORT C & D)

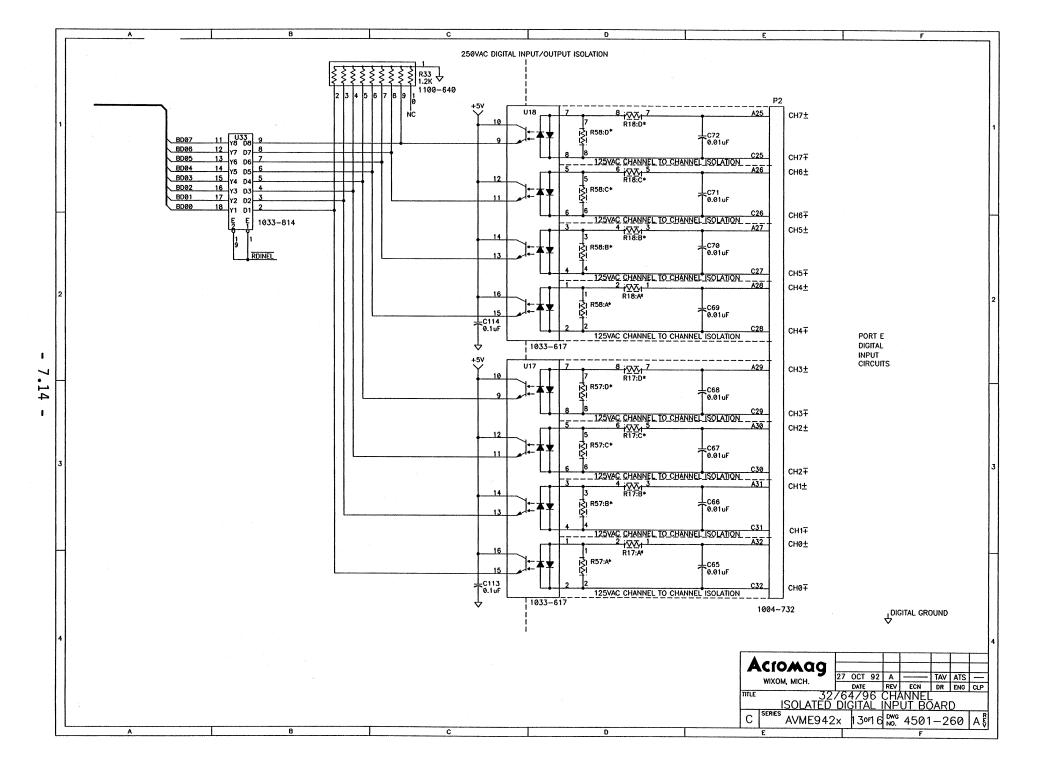

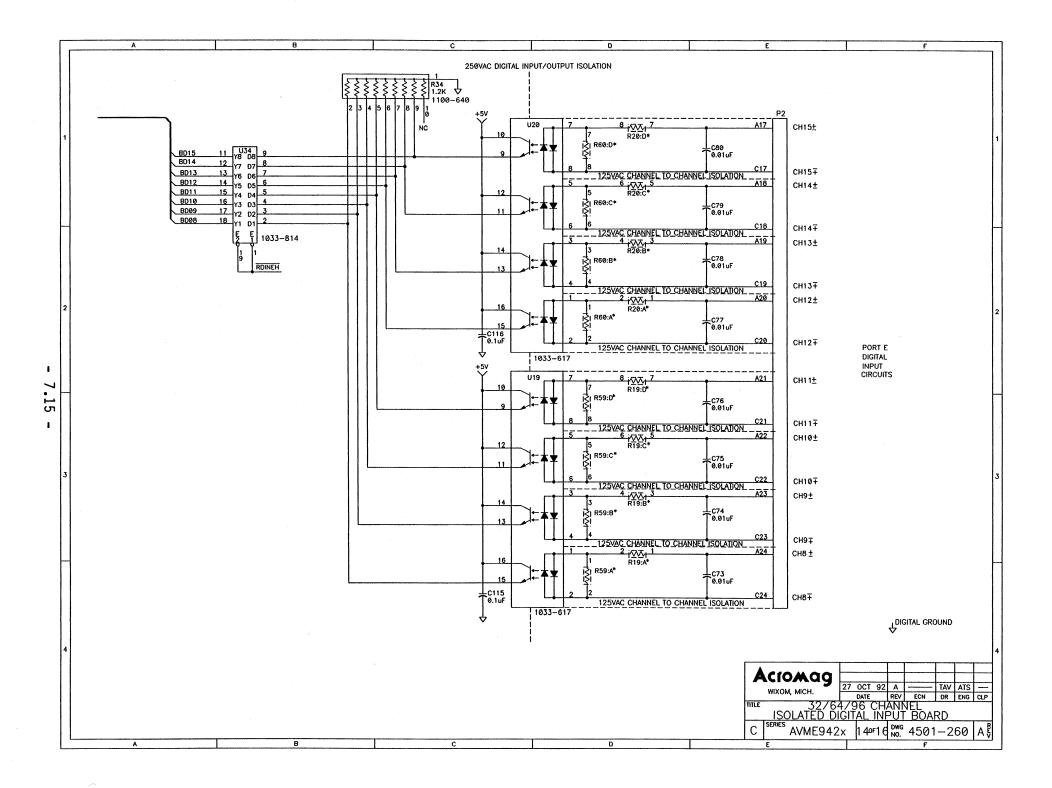

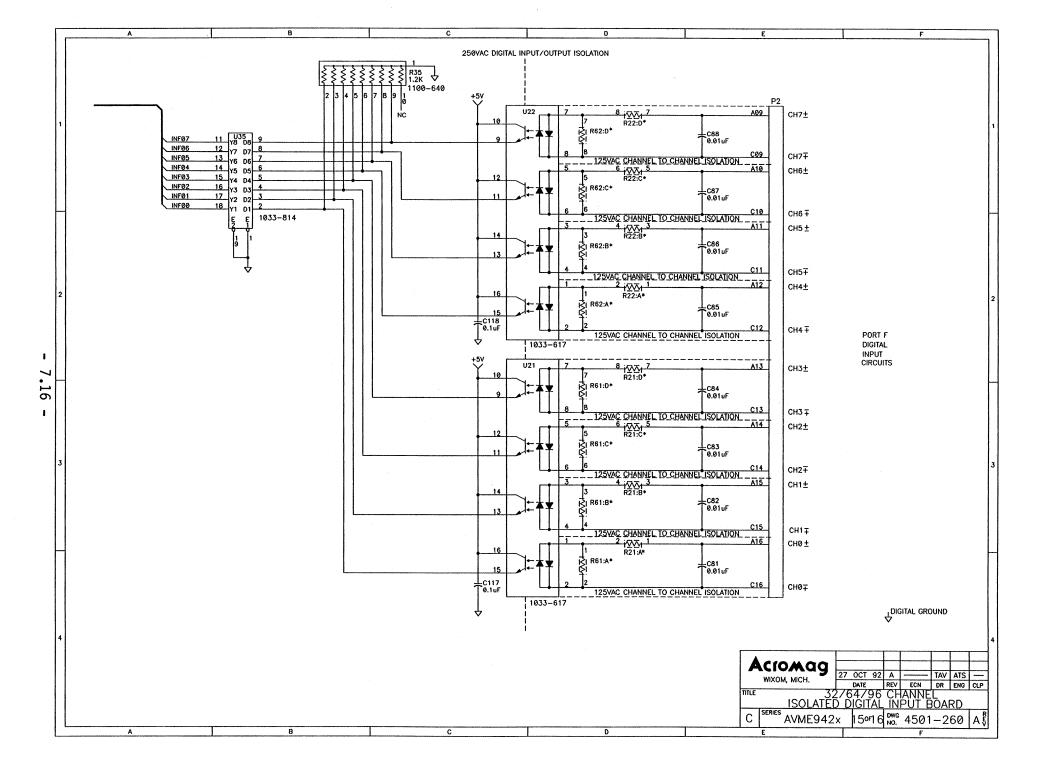

## 2.6.3 DIGITAL INPUT CONNECTOR (PORT E & PORT F)

The third group of digital inputs (Port E channels 0 through 15 and Port F channels 0 through 15) are connected to the AVME9420/9422/9425/9427 board via connector P2 (lower rear connector as viewed from the front). Table 2.3 defines the assignment. These connections are easily accommodated through the use of Acromag termination panels and flat cable assemblies or through the use of a user defined termination panel.

P2: DIN 41612 Type C Level II, 64 Pin Male Connector. Panduit No. 100-964-033B or equiv.

| Port | Pin Number | (PORIE&F)<br>Mnemonic | Pin Number | Mnemonic |

|------|------------|-----------------------|------------|----------|

| FOIL | 32A        | CH0+/-                | 32C        | CH0-/+   |

|      |            |                       | 32C<br>31C |          |

|      | 31A        | CH1+/-                |            | CH1-/+   |

|      | 30A        | CH2+/-                | 30C        | CH2-/+   |

|      | 29A        | CH3+/-                | 29C        | CH3-/+   |

|      | 28A        | CH4+/-                | 28C        | CH4-/+   |

| P    | 27A        | CH5+/-                | 27C        | CH5-/+   |

| 0    | <u>26A</u> | CH6+/-                | 26C        | CH6-/+   |

| R    | 25A        | CH7+/-                | 25C        | CH7-/+   |

| Т    | 24A        | CH8+/-                | 24C        | CH8-/+   |

|      | 23A        | CH9+/-                | 23C        | CH9-/+   |

| E    | 22A        | CH10+/-               | 22C        | CH10-/+  |

|      | 21A        | CH11+/-               | 21C        | CH11-/+  |

|      | 20A        | CH12+/-               | 20C        | CH12-/+  |

|      | 19A        | CH13+/-               | 19C        | CH13-/+  |

|      | 18A        | CH14+/-               | 18C        | CH14-/+  |

|      | 17A        | CH15+/-               | 17C        | CH15-/+  |

|      | 16A        | CH0+/-                | 16C        | CH0-/+   |

|      | 15A        | CH1+/-                | 15C        | CH1-/+   |

|      | 14A        | CH2+/-                | 14C        | CH2-/+   |

|      | 13A        | CH3+/-                | 13C        | CH3-/+   |

|      | 12A        | CH4+/-                | 12C        | CH4-/+   |

| Р    | 11A        | CH5+/-                | 11C        | CH5-/+   |

| 0    | 10A        | CH6+/-                | 10C        | CH6-/+   |

| R    | 9A         | CH7+/-                | 9C         | CH7-/+   |

| Т    | 8A         | CH8+/-                | 8C         | CH8-/+   |

|      | 7A         | CH9+/-                | 7C         | CH9-/+   |

| F    | 6A         | CH10+/-               | 6C         | CH10-/+  |

|      | 5A         | CH11+/-               | 5C         | CH11-/+  |

|      | 4A         | CH12+/-               | 4C         | CH12-/+  |

|      | 3A         | CH13+/-               | 3C         | CH13-/+  |

|      | 2A         | CH14+/-               | 2C         | CH14-/+  |

|      | 1A         | CH15+/-               | 1C         | CH15-/+  |

|      |            |                       | - 2.15 -   | 0.11071  |

Table 2.3: P2 CONNECTOR (PORT E & F)

## 2.6.4 VMEBUS CONNECTIONS

Table 2.4 indicates pin assignments for the VMEbus signals at the P1 connector. The P1 connector is the upper rear connector on the AVME942x board as viewed from the front. The connector consists of 32 rows of three pins labeled A, B, and C. Pin A1 is located at the upper left hand corner of the connector.

| PIN NUMBER | MNEMONIC | PIN NUMBER | MNEMONIC  | PIN NUMBER | MNEMONIC  |

|------------|----------|------------|-----------|------------|-----------|

| 1A         | D00      | 1B         | BBSY*     | 1C         | D08       |

| 2A         | D01      | 2B         | BCLR*     | 2C         | D09       |

| 3A         | D02      | 3B         | ACFAIL*   | 3C         | D10       |

| 4A         | D03      | 4B         | BGOIN*    | 4C         | D11       |

| 5A         | D04      | 5B         | BG0OUT*   | 5C         | D12       |

| 6A         | D05      | 6B         | GB1IN*    | 6C         | D13       |

| 7A         | D06      | 7B         | BG1OUT*   | 7C         | D14       |

| 8A         | D07      | 8B         | BG2IN*    | 8C         | D15       |

| 9A         | GND      | 9B         | BG2OUT*   | 9C         | GND       |

| 10A        | SYSCLK   | 10B        | BG3IN*    | 10C        | SYSFAIL*  |

| 11A        | GND      | 11B        | BG3OUT*   | 11C        | BERR*     |

| 12A        | DS1*     | 12B        | BRO*      | 12C        | SYSRESET* |

| 13A        | DS0*     | 13B        | BR1*      | 13C        | LWORD*    |

| 14A        | WRITE*   | 14B        | BR2*      | 14C        | AM5       |

| 15A        | GND      | 15B        | BR3*      | 15C        | A23       |

| 16A        | DTACK*   | 16B        | AM0       | 16C        | A22       |

| 17A        | GND      | 17B        | AM1       | 17C        | A21       |

| 18A        | AS*      | 18B        | AM2       | 18C        | A20       |

| 19A        | GND      | 19B        | AM3       | 19C        | A19       |

| 20A        | IACK*    | 20B        | GND       | 20C        | A18       |

| 21A        | IACKIN*  | 21B        | SERCLK    | 21C        | A17       |

| 22A        | IACKOUT* | 22B        | SERDAT*   | 22C        | A16       |

| 23A        | AM4      | 23B        | GND       | 23C        | A15       |

| 24A        | A07      | 24B        | IRQ7*     | 24C        | A14       |

| 25A        | A06      | 25B        | IRQ6*     | 25C        | A13       |

| 26A        | A05      | 26B        | IRQ5*     | 26C        | A12       |

| 27A        | A04      | 27B        | IRQ4*     | 27C        | A11       |

| 28A        | A03      | 28B        | IRQ3*     | 28C        | A10       |

| 29A        | A02      | 29B        | IRQ2*     | 29C        | A09       |

| 30A        | A01      | 30B        | IRQ1*     | 30C        | A08       |

| 31A        | -12V     | 31B        | +5V STDBY | 31C        | +12V      |

|            | 1        |            |           |            |           |

#### TABLE 2.4: P1 BUS CONNECTIONS

• Indicates that the signal is active low.

Refer to the VMEbus specification for additional information on the VMEbus signals.

#### 2.7 POWER-UP TIMING AND LOADING

The AVME942x board uses a Logic Cell Array to handle the bus interface and control logic timing. Upon power-up, the Logic Cell Array automatically clocks in configuration vectors from a local PROM to initialize the logic circuitry for normal operation. This time is measured as the first 145 mS (typical) after the +5 Volt supply raises to +2.5 Volts at power-up. If a data transfer is attempted during this time, it will simply be ignored and the board will not respond. This should not be a problem because the VME specification requires that the bus master drive the system reset for the first 200 mS after power-up, thus inhibiting any data transfers from taking place.

Port A, Port B, Port C, Port D, Port E and Port F Digital input channels are reset to the OFF state following a power-up sequence. External input signals above threshold levels can then drive inputs ON.

## 2.8 DATA TRANSFER TIMING

Data transfer time is measured from the falling edge of DSx\* to the falling edge of DTACK\* during a normal data transfer cycle.

| REGISTER      | DATA TRANSFER TIME |

|---------------|--------------------|

| All Registers | 600nS, typical     |

#### 2.9 FIELD GROUNDING CONSIDERATIONS

The board is designed to isolate every input channel from each other as well as from the VMEbus. This is intended to protect each channel and the VMEbus from voltage spikes and transients such as those caused by ground currents and "pick-up". The isolation provides the ability to earth ground the field wiring without the concern of ground currents damaging the card cage electronics.

## 3.0 PROGRAMMING INFORMATION

This chapter provides the specific information necessary to operate the AVME942x Isolated Digital Input Board.

## 3.1 MEMORY MAP

The board is addressable on 1K byte boundaries in the Short I/O Address Space or Standard Address Space. All Acromag VMEbus non-intelligent slaves have a standard interface configuration which consists of a 32 byte board ID PROM and a Board Status register. The rest of the 1K byte address space contains registers or memory specific to the function of the board. The memory map is shown in Figure 3.1 (Addresses in Hex).

| Address<br>Base + | D15 | Even      | D8   | D7                          | Odd                                                | D0      | Address<br>Base + |  |  |  |

|-------------------|-----|-----------|------|-----------------------------|----------------------------------------------------|---------|-------------------|--|--|--|

| 00                | 210 |           | 20   |                             |                                                    |         | 01                |  |  |  |

| 3E                |     | Undefined |      | R –                         | Board ID PR                                        | MC      | 3F                |  |  |  |

| 40                |     | Undefined |      |                             |                                                    |         |                   |  |  |  |

| 7E                |     |           | Ond  |                             |                                                    |         | 7F                |  |  |  |

| 80                |     | Undefined |      | R/W                         | √ – Board Sta                                      | tus     | 81                |  |  |  |

| 82                |     |           |      |                             |                                                    |         | 83                |  |  |  |

| 02                |     |           | Und  | efined                      |                                                    |         | 03                |  |  |  |

| 9E                |     |           |      |                             |                                                    |         | 9F                |  |  |  |

| A0                |     |           |      | R/W –Int                    | Vector Port B                                      | &F CHO  | A1                |  |  |  |

| A2                |     |           |      | R/W –Int                    | R/W –Int Vector Port B&F CH1                       |         |                   |  |  |  |

| A4                |     |           |      | R/W –Int                    | A5                                                 |         |                   |  |  |  |

| A6                |     | Undefined |      | R/W –Int                    | Vector Port E                                      | 8&F CH3 | A7                |  |  |  |

| A8                |     |           |      | R/W –Int                    | Vector Port E                                      | 8&F CH4 | A9                |  |  |  |

| AA                |     |           |      | R/W –Int                    | Vector Port E                                      | 8&F CH5 | AB                |  |  |  |

| AC                |     |           |      | R/W –Int                    | Vector Port E                                      | B&F CH6 | AD                |  |  |  |

| AE                |     |           |      | R/W -Int                    | Vector Port E                                      | B&F CH7 | AF                |  |  |  |

| B0                |     |           | Lind | efined                      |                                                    |         | B1                |  |  |  |

| BE                |     |           | Unu  |                             |                                                    |         | BF                |  |  |  |

| C0                |     | Undefined |      | R/W – I<br>Interru<br>CH7 P | gister                                             | C1      |                   |  |  |  |

| C2                |     | Undefined |      | Interru                     | Digital Input C<br>ipt Enable Re<br>ort B & Port F | gister  | C3                |  |  |  |

#### Figure 3.1: Board Memory Map

Board Memory Map continued on page 3.2

#### Board Memory Map continued

| C4   | Undefined                                                                                        | R/W – Digital Input Channel<br>Interrupt Polarity Register                               | C5  |  |  |  |  |  |  |  |

|------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|--|

|      |                                                                                                  | CH7 Port B & Port F CH0                                                                  |     |  |  |  |  |  |  |  |

| C6   | Undefined                                                                                        | R/W – Digital Input Channel<br>Interrupt Type Select Register<br>CH7 Port B & Port F Ch0 | C7  |  |  |  |  |  |  |  |

| C8   | Undefined R/W – Digital Input Channel<br>Int. Pattern Enable Register<br>CH7 Port B & Port F Ch0 |                                                                                          |     |  |  |  |  |  |  |  |

| CA   | R – Port A Digital Input                                                                         | Channel Data Register                                                                    | СВ  |  |  |  |  |  |  |  |

| C/ T |                                                                                                  | C C                                                                                      | 02  |  |  |  |  |  |  |  |

|      | CH15                                                                                             | CH15 CH0                                                                                 |     |  |  |  |  |  |  |  |

| CC   | R – Port B Digital Input Channel Data Register                                                   |                                                                                          |     |  |  |  |  |  |  |  |

|      | CH15                                                                                             | CH0                                                                                      |     |  |  |  |  |  |  |  |

| CE   | R – Port C Digital Input Channel Data Register                                                   |                                                                                          |     |  |  |  |  |  |  |  |

| UL   | Ŭ I                                                                                              | 3                                                                                        | CF  |  |  |  |  |  |  |  |

|      | CH15                                                                                             | CH0                                                                                      |     |  |  |  |  |  |  |  |

| D0   | R – Port D Digital Input                                                                         | Channel Data Register                                                                    | D1  |  |  |  |  |  |  |  |

|      | CH15 CH0                                                                                         |                                                                                          |     |  |  |  |  |  |  |  |

| D2   | R – Port E Digital Input                                                                         | Channel Data Register                                                                    | D3  |  |  |  |  |  |  |  |

|      | <b>5</b> .                                                                                       | 5                                                                                        | 20  |  |  |  |  |  |  |  |

|      | CH15                                                                                             | CH0                                                                                      |     |  |  |  |  |  |  |  |

| D4   | R – Port F Digital Input                                                                         | Channel Data Register                                                                    | D5  |  |  |  |  |  |  |  |

|      | CH15                                                                                             | CH0                                                                                      |     |  |  |  |  |  |  |  |

| D6   |                                                                                                  |                                                                                          | D7  |  |  |  |  |  |  |  |

| 3EF  | Unde                                                                                             | fined                                                                                    | 3FF |  |  |  |  |  |  |  |

| 366  |                                                                                                  |                                                                                          | SLL |  |  |  |  |  |  |  |

## 3.1.1 BOARD IDENTIFICATION PROM - (READ ONLY) - 01H THROUGH 3FH (ODD)

The board contains an identification section. This section of data describes the board model number, the manufacturer, and the product revision level. The identification section starts at the board's base address plus 1 and is 32 bytes in length. Bytes are addressed using only the odd addresses between 1 and 63. The PROM contents are shown in Figure 3.2 for an AVME9422-I-L (each model has a unique PROM).

| Offset From           | Value           |         |                                               |  |  |  |  |

|-----------------------|-----------------|---------|-----------------------------------------------|--|--|--|--|

| Board Base<br>Address | ASCII Character | Numeric | Descriptions                                  |  |  |  |  |

| 01H                   | V               | 56H     | All Boards have "VMEID"                       |  |  |  |  |

| 03H                   | М               | 4DH     |                                               |  |  |  |  |

| 05H                   | E               | 45H     |                                               |  |  |  |  |

| 07H                   | I               | 49H     |                                               |  |  |  |  |

| 09H                   | D               | 44H     |                                               |  |  |  |  |

| 0BH                   | А               | 41H     | Manufacturer's I.D., "ACR" for Acromag        |  |  |  |  |

| 0DH                   | С               | 43H     |                                               |  |  |  |  |

| 0FH                   | R               | 52H     |                                               |  |  |  |  |

| 11H                   | 9               | 39H     | Board Model Number (6 characters and          |  |  |  |  |

| 13H                   | 4               | 34H     | 1 trailing "blank")                           |  |  |  |  |

| 15H                   | 2               | 32H     |                                               |  |  |  |  |

| 17H                   | 2               | 32H     | (Each model has a unique number)              |  |  |  |  |

| 19H                   | I               | 49H     |                                               |  |  |  |  |

| 1BH                   | L               | 4CH     |                                               |  |  |  |  |

| 1DH                   |                 | 20H     |                                               |  |  |  |  |

| 1FH                   | 1               | 31H     | Number of KILOBYTES of address<br>Space used. |  |  |  |  |

| 21H                   |                 | 20H     |                                               |  |  |  |  |

| 23H                   | Undefined       | 41H     | Reserved                                      |  |  |  |  |

| 25H                   | Undefined       |         |                                               |  |  |  |  |

| 27H                   | Undefined       |         |                                               |  |  |  |  |

| 29H                   | Undefined       |         | Reserved                                      |  |  |  |  |

| 2BH                   | Undefined       |         |                                               |  |  |  |  |

| 2DH                   | Undefined       |         |                                               |  |  |  |  |

| 2FH                   | Undefined       |         |                                               |  |  |  |  |

| 31H                   | Undefined       |         |                                               |  |  |  |  |

| 33H                   | Undefined       |         |                                               |  |  |  |  |

| 35H                   | Undefined       |         |                                               |  |  |  |  |

| 37H                   | Undefined       |         |                                               |  |  |  |  |

| 39H                   | Undefined       |         |                                               |  |  |  |  |

| 3BH                   | Undefined       |         |                                               |  |  |  |  |

| 3DH                   | Undefined       |         |                                               |  |  |  |  |

| 3FH                   | Undefined       |         |                                               |  |  |  |  |

#### Figure 3.2: AVME9422-I-L Board Identification PROM

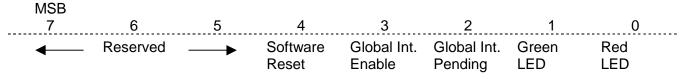

#### 3.1.2 BOARD STATUS REGISTER - (READ/WRITE) - 81H

The Board Status Register reflects and controls functions globally on the board.

Where:

Bits 7,6,5: Reserved for future use - equal "0" if read.

Bit 4: Software Reset (W) - writing a "1" to this bit causes a software reset. Writing "0" or reading the bit has no effect. The effect of a software reset on the various registers is described in the description of each register.

Reset Condition: Set to "0".

Bit 3: Global Interrupt Enable (R/W) - writing a "1" to this bit enables interrupts to be serviced, provided the interrupt level (IRQx\*) is selected. A "0" disables servicing interrupts.

Reset Condition: Set to "0", interrupts disabled.

Bit 2: Global Interrupt Pending (R) - this bit will be a "1" when there is an interrupt pending. This bit will be "0" when there is no interrupt pending. Polling this bit will reflect the board's pending interrupt status, even if the Global Interrupt Enable bit is set to "0".

Reset condition: Set to "0".

Bit 1: Green LED (R/W) - when written, this bit will control the state of the green LED on the front panel. A "1" will turn it on, a "0" will turn it off. Reading it will reflect its current state.

Reset Condition: Set to "0", green LED off.

Bit 0: Red LED (R/W) - when written, this bit will control the state of the red LED on the front panel and the state of the VMEbus SYSFAIL\* signal. A "1" will turn the LED off and set SYSFAIL\* high, a "0" will turn the LED on and set SYSFAIL\* low. Reading it will reflect its current state. (See Section 5.2 for additional information on using SYSFAIL\*.)

Reset Condition: Set to "0", red LED lit, and SYSFAIL\* is set low.

## 3.1.2.1 STATUS BITS USAGE

The status register bits 1 and 0 along with the green and red LEDs provide the user with a means of keeping track of a board's functionality in the system. Since there is no intelligence on the board, the host computer controls these bits. The following paragraphs and summary table describe possible uses of the bits in the status register and the LEDs on the front panel.

On power-up the bits in the status register read low, with the green LED off, the red LED lit, and SYSFAIL\* low. This indicates that the board has failed or that it has not been tested yet.

If the status register bit 1 reads low and Bit 0 reads high, the LEDs will both be off and SYSFAIL\* high. This indicates an inactive board.

If the status register bit 1 reads high and Bit 0 reads low, the LEDs will both be lit and SYSFAIL\* low. This indicates the board is undergoing a diagnostic checkout.

If the status register bits 1 and 0 read high, the green LED will be lit with the red LED off and SYSFAIL\* high. This indicates the board is fully functional.

| Bit 0     | Bit 1       |           |                           |

|-----------|-------------|-----------|---------------------------|

| (Red LED) | (Green LED) | SYSFAIL * | Description               |

| 0, (on)   | 0, (off)    | Low       | Failed or reset condition |

| 1, (off)  | 0, (off)    | High      | Inactive board            |

| 0, (on)   | 1, (on)     | Low       | Diagnostics are running   |

| 1, (off)  | 1, (on)     | High      | Normal operation          |

Status Bits - Possible Usage

## 3.1.3 INTERRUPT VECTOR REGISTERS - (READ/WRITE) - A1H TO AFH (ODD ADDRESSES)

The interrupt vector registers maintain the 8 bit interrupt vector numbers for each of the 8 digital input channel interrupt lines. Note that interrupts can only be generated for Port B or Port F digital input channels 0-7. Also note that Port B and Port F of the same channel would use the same interrupt vector register. The appropriate vector is provided to the VMEbus Interrupt Handler when an interrupt is being serviced. This allows each digital input channel interrupt (Port B ch. 0-7 or Port F ch. 0-7) to be serviced by its own software handler. If desired, a single handler can be used by making all of the vectors the same. In this case, the handler will have to determine the interrupting channel by examining the interrupt status register.

The register content is undefined upon reset.

#### 3.1.4 Digital Input Channel Interrupt Status Register (read/write) - C1H

The digital input channel interrupt status register reflects the status of the 8 input channels (Port B or Port F ch. 0-7). A "1" in a bit position indicates an interrupt is pending for the corresponding channel. Each bit is derived from the logical AND of its associated interrupt input and enable bits. Hence, an input channel that does not have interrupts enabled will never have its interrupt pending bit set to a "1".

An individual channel's interrupt can be cleared by writing a "1" to its bit position in the interrupt status register. However, if the condition which caused the interrupt remains or reappears, a new interrupt will be generated. To permanently disable a channel's interrupt, the corresponding bit in the channel interrupt enable register must be cleared, followed by writing a "1" to the channel's bit position in the channel interrupt status register (to clear the interrupt). This is known as the "Release On Register Access" (RORA) method as defined in the VME system architecture.

Bit 7 of this register has a dual purpose. In addition to indicating an interrupt for channel 7, it is also used to indicate an input channel bit pattern match (see the digital input channel interrupt pattern enable register).

| MSB |     |     |     |     |     |     | LSB |  |

|-----|-----|-----|-----|-----|-----|-----|-----|--|

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

| CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |  |

All interrupts are cleared following a reset.

NOTE: Interrupts are prioritized via hardware within the card. Channel 7 is the highest priority and channel 0 is the lowest. If multiple input channel interrupts become pending simultaneously, the vector corresponding to the highest numbered channel will be delivered first. After the highest channel's interrupt is serviced and cleared, an additional interrupt will be generated for the next highest priority interrupt (pending) channel.

NOTE: Input channel bandwidth should be limited to reduce the possibility of missing channel interrupts. For a specific input channel this could happen if multiple changes occur before the channel's interrupt is serviced.

#### 3.1.5 DIGITAL INPUT CHANNEL INTERRUPT ENABLE REGISTER (READ/WRITE) - C3H

The digital input channel interrupt enable register provides a mask bit for each of the 8 input channels (Port B or Port F ch. 0-7). A "0" in a bit position will prevent the corresponding input channel from causing an external interrupt. A "1" will allow the input channel to cause an interrupt.

| MSB |     |     |     |     |     |     | LSB |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

All input channel interrupts are masked ("0") following a reset.

#### 3.1.6 DIGITAL INPUT CHANNEL INTERRUPT POLARITY REGISTER (READ/WRITE) - C5H

The digital input channel interrupt polarity register determines the level that will cause a channel interrupt for each of the 8 input channels (Port B or Port F ch. 0-7). A "0" in a bit position means an interrupt will occur when the input channel is below threshold (i.e. a "0" in the digital input channel data register). A "1" in a bit position means an interrupt will occur when the input channel is above threshold (i.e. a "1" in the digital input channel data register).

Note that interrupts will not occur unless they are enabled. The interrupt polarity register will have no effect if Change Of State (COS) interrupts are selected (see the digital input channel interrupt type select register).

MSB

LSB

7

6

5

4

3

2

1

0

CH7

CH6

CH5

CH4

CH3

CH2

CH1

CH0

All bits are set to "0" following a reset which means that the inputs will cause interrupts when they are below threshold.

#### 3.1.7 DIGITAL INPUT CHANNEL INTERRUPT TYPE SELECT REGISTER (READ/WRITE) - C7H

The digital input channel interrupt type select register determines the type of input channel behavior that will cause a channel interrupt for each of the 8 input channels (Port B or Port F ch. 0-7). A "0" in a bit position means an interrupt will be generated when the input channel level specified by the digital input channel interrupt polarity register occurs. A "1" in a bit position means an interrupt will occur when a Change Of State (COS) occurs at the input channel (either low to high, or high to low).

Note that interrupts will not occur unless they are enabled.

| MSB |     |     |     |     |     |     | LSB |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

All bits are set to "0" following a reset which means that the inputs will cause interrupts for the input channel levels specified by the digital input channel interrupt polarity register.

#### 3.1.8 DIGITAL INPUT CHANNEL INTERRUPT PATTERN ENABLE REG. (READ/WRITE) - C9H

The digital input channel interrupt pattern enable register provides a mask bit for each of the 8 input channels (Port B or Port F ch. 0-7). A "0" in a bit position will prevent the corresponding input channel from being part of a pattern of channels (bits) which can cause an interrupt. A "1" will allow the input channel to be a component of a pattern which can cause an interrupt. Note that an interrupt will only be generated if all enabled channels (at least 1 and up to 8 channels) forming the pattern meet the level requirements specified in the digital input channel interrupt polarity register. Note that when pattern interrupts are desired, the digital input channel interrupt type select register bits must be set to "0" (interrupt on input level, not on change of state).

Note also that the interrupt generated will result in setting the status bit in the digital input channel interrupt status register which corresponds to channel 7 (i.e. the highest priority channel).

| MSB |     |     |     |     |     |     | LSB |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

All input channel pattern enable bits are masked ("0") following a reset.

#### 3.1.9 PORT A DIGITAL INPUT CHANNEL DATA REGISTER (READ) - CAH & CBH

The Port A digital input channel data register represents the actual state of the 16 Port A digital input channels at the time the register is read (note that the debounce circuit is not available for Port A, and consequently does not introduce any additional delay). A "0" means that the signal across the board's input channel connector is below threshold. A "1" means that the signal is above threshold. Note that the threshold voltage (i.e. range) is not user selectable.

| MSB  |      |      |      |      |      |     |     |     |     |     |     |     |     |     | LSB |

|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 15   | 14   | 13   | 12   | 11   | 10   | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

#### 3.1.10 PORT B DIGITAL INPUT CHANNEL DATA REGISTER (READ) - CCH & CDH

The Port B digital input channel data register represents the actual state of the 16 Port B digital input channels at the time the register is read (note that the debounce circuit will insert a delay, channel 0-7 only, dependent on the degree of debounce selected). A "0" means that the signal across the board's input channel connector is below threshold. A "1" means that the signal is above threshold. Note that the threshold voltage (i.e. range) is not user selectable.

| MSB  |      |      |      |      |      |     |     |     |     |     |     |     |     |     | LSB |

|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 15   | 14   | 13   | 12   | 11   | 10   | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

## 3.1.11 PORT C DIGITAL INPUT CHANNEL DATA REGISTER (READ) - CEH & CFH

The Port C digital input channel data register represents the actual state of the 16 Port C digital input channels at the time the register is read (note that the debounce circuit is not available for Port C, and consequently does not introduce any additional delay). A "0" means that the signal across the board's input channel connector is below threshold. A "1" means that the signal is above threshold. Note that the threshold voltage (i.e. range) is not user selectable.

| MSB  |      |      |      |      |      |     |     |     |     |     |     |     |     |     | LSB |

|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 15   | 14   | 13   | 12   | 11   | 10   | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

#### 3.1.12 PORT D DIGITAL INPUT CHANNEL DATA REGISTER (READ) - D0H & D1H

The Port D digital input channel data register represents the actual state of the 16 Port D digital input channels at the time the register is read (note that the debounce circuit is not available for Port D, and consequently does not introduce any additional delay). A "0" means that the signal across the board's input channel connector is below threshold. A "1" means that the signal is above threshold. Note that the threshold voltage (i.e. range) is not user selectable.

| MSB  |      |      |      |      |      |     |     |     |     |     |     |     |     |     | LSB |

|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 15   | 14   | 13   | 12   | 11   | 10   | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

#### 3.1.13 PORT E DIGITAL INPUT CHANNEL DATA REGISTER (READ) - D2H & D3H

The Port E digital input channel data register represents the actual state of the 16 Port E digital input channels at the time the register is read (note that the debounce circuit is not available for Port E, and consequently does

LSB

not introduce any additional delay). A "0" means that the signal across the board's input channel connector is below threshold. A "1" means that the signal is above threshold. Note that the threshold voltage (i.e. range) is not user selectable.

#### MSB

| 15   | 14   | 13   | 12   | 11   | 10   | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

#### 3.1.14 PORT F DIGITAL INPUT CHANNEL DATA REGISTER (READ) - D4H & D5H

The Port F digital input channel data register represents the actual state of the 16 Port F digital input channels at the time the register is read (note that the debounce circuit will insert a delay, channel 0-7 only, dependent on the degree of debounce selected). A "0" means that the signal across the board's input channel connector is below threshold. A "1" means that the signal is above threshold. Note that the threshold voltage (i.e. range) is not user selectable.

| MSB  |      |      |      |      |      |     |     |     |     |     |     |     |     |     | LSB |

|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 15   | 14   | 13   | 12   | 11   | 10   | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

#### 3.2 GENERAL PROGRAMMING CONSIDERATIONS

#### **3.2.1 BOARD DIAGNOSTICS**

The board is a non-intelligent slave and does not perform self diagnostics. It does, however, provide a standard interface architecture which includes a Board Status Register useful in system diagnostics.

Status bits, control of front panel LEDs, and control of the SYSFAIL\* signal are provided through the Board Status Register. Bits 0 and 1 may be used as follows:

| Board Statu | us Register | Le    | ds  | SYSFAIL* |                                           |

|-------------|-------------|-------|-----|----------|-------------------------------------------|

| Bit 1       | Bit 0       | Green | Red | SIGNAL   | Condition                                 |

| 0           | 0           | Off   | On  | On       | Board failed test or has not been tested. |

| 1           | 0           | On    | On  | On       | Board is being tested.                    |

| 1           | 1           | On    | Off | Off      | Board has passed test.                    |

| 0           | 1           | Off   | Off | Off      | Board is inactive.                        |

At power up, the system diagnostic software can test each non-intelligent Slave, sequencing the status bits to indicate "undergoing test" and then to "passed" or "failed".

After testing each board, the system software records which boards have failed and sets their status to indicate "inactive". By setting the board's status to inactive, the SYSFAIL\* signal is released and may then be useful for an on-line indication of failure by other boards.

Alternatively, the system software could simply set the bits and therefore front panel LEDs, to "passed test" as a visual indication that the presence of the board is recognized.

## 3.3 GENERATING INTERRUPTS

Port B or Port F Digital input channels 0-7 can cause interrupts (for the jumper selected port only) to be generated for a wide variety of conditions. These include interrupts for:

- Change Of State (COS) of selected input channels.

- Input level (polarity) match of selected input channels.

- Input pattern match of the levels of multiple input channels.

The interrupt level (IRQx\*) associated with the card is programmable via a jumper on the board. The interrupt release mechanism is the Release On Register Access (RORA) type. This means that the interrupter will release the interrupt request line (IRQx\*) after the interrupt has been cleared by writing a "1" to the appropriate bit position in the input channel interrupt status register.