# $U2P^{\scriptscriptstyle\mathsf{TM}}$

## UPA to PCI Interface User's Manual

THE NETWORK IS THE COMPUTER"

A Sun Microsystems, Inc. Business 2550 Garcia Avenue Mountain View, CA 94043 USA 1-800-681-8845 www.sun.com/sparc Part No.: 802-7835-01 May 1997 Copyright © 1997 Sun Microsystems, Inc. All Rights Reserved.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS" WITHOUT ANY EXPRESS REPRESENTATIONS OR WARRANTIES. IN ADDITION, SUN MICROSYSTEMS, INC. DISCLAIMS ALL IMPLIED REPRESENTATIONS AND WARRANTIES, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

This document contains proprietary information of Sun Microsystems, Inc. or under license from third parties. No part of this document may be reproduced in any form or by any means or transferred to any third party without the prior written consent of Sun Microsystems, Inc.

Sun, Sun Microsystems, and the Sun logo are trademarks or registered trademarks of Sun Microsystems, Inc. in the United States and other countries. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the United States and other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

The information contained in this document is not designed or intended for use in on-line control of aircraft, air traffic, aircraft navigation or aircraft communications; or in the design, construction, operation or maintenance of any nuclear facility. Sun disclaims any express or implied warranty of fitness for such uses.

Printed in the United States of America.

## Contents

#### 1. Overview 1-1

Introduction 1-1 Product Summary 1-2 Technology 1-2 Package 1-2 Design Size 1-2 Custom Cells 1-2 Maximum Frequency of Operation 1-3 Minimum Frequency of Operation 1-3 Power Consumption 1-3 Performance 1-4 Typical System Partition 1-5 U2P External Interfaces 1-5 U2P Block Diagram 1-7 U2P Block Overviews 1-8 UPA Interface blocks 1-8 PCI Interface blocks 1-8 Interrupt block 1-9 Internal Control 1-9 Clock Ratios 1-10 Miscellaneous 1-10 PCI Address Map Overview 1-10

#### 2. U2P Pin Descriptions 2-1

UPA Interface Signals 2-1 64-bit, 66MHz capable PCI Interface Signals (PCI Bus A) 2-2 64-bit, 33MHz PCI Interface Signals (PCI Bus B) 2-3 Miscellaneous Interfaces 2-4 Power and Ground Pins/Pads 2-5 Total Pin/Pad Count 2-6

#### 3. U2P Functional Description 3-1

Functional Overview 3-1 Top-Level Architectural Philosophy 3-1 **Block Overviews 3-4** PIO Decoder 3-4 DMA Control 3-4 **Bus Control 3-5** UPA Master / Slave 3-5 UPA Reply 3-6 ECC Generate / Check 3-6 DMA Merge Buffer 3-7 PCI Bus Module (PBM) 3-7 **IOMMU 3-10** Streaming Cache 3-10 MDU 3-11 Timer / Counters 3-12 Reset 3-12 Testability 3-13

#### 4. DMA/PIO Transactions Flow 4-1

Block Diagram 4-2 DMA Transaction Flow 4-5 DMA Write Transactions 4-6 64 and 16 Byte DMA Writes to IO Space 4-6 64 Byte DMA Write to Memory 4-8 Less than 64 Byte DMA Write to Memory 4-10 DMA Read Transactions 4-13

iv UPA to PCI Interface (U2P) User's Manual • May 1997

PIO Transaction Flow 4-14 PIO Write 4-15 PIO Read 4-17

#### 5. IOMMU 5-1

Block Diagram 5-2 TLB Entry Format 5-2 TLB CAM Tag 5-3 TLB RAM Data 5-3 DVMA Operation Modes 5-4 Translation Mode 5-4 Bypass Mode 5-5 Pass-through Mode 5-6 Translation Storage Buffer 5-6 Translation Table Entry 5-7 TSB Lookup 5-7 PIO Operations 5-9 Translation Errors 5-9 IOMMU Demap 5-10 TLB Initialization and Diagnostics 5-10

#### 6. PCI Bus Interface 6-1

Introduction 6-1 Supported PCI features: 6-1 Unsupported PCI features: 6-2 PCI Bus Operations 6-2 Bus Master Operation (PIO) 6-2 Target Operation (DMA) 6-4 Transaction Termination Behavior 6-5 Retries 6-5 Disconnects 6-5 Master-aborts 6-5 Target-aborts 6-6 Addressing Modes 6-7 Configuration Cycles 6-7 Special Cycles 6-7 Exclusive Access 6-8 Fast Back-to-Back Cycles 6-8 Functional Topics 6-9 PCI Arbiter 6-9 Bus Parking 6-9 Endianess 6-10 PCI Commands 6-10 Diagnostic Modes 6-11 Clocks 6-11 Reset 6-11

#### 7. Streaming Cache Operation 7-1

Overview 7-1 Streaming Cache Conceptual Overview 7-2 STC Subsections 7-2 Streaming Cache Functional Description 7-3 Streaming Writes 7-3 Byte Holes and Zero Byte Writes 7-4 Streaming Reads 7-4 Entry Flushing 7-5 Streaming Cache Programming Model 7-6 Performance Issues 7-6 Memory Coherency Maintenance 7-7 Error Recovery 7-8

#### 8. Mondo Dispatch Unit 8-1

Overview 8-1

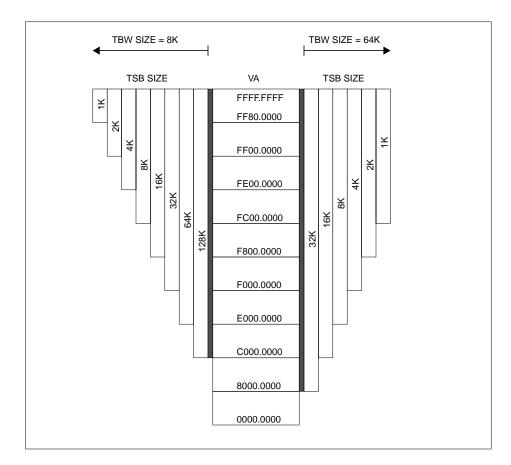

Mondo Dispatch Overview 8-1 Mondo Dispatch Block Diagram 8-3 Mondo Unit Functional Description 8-3 Mondo Vectors 8-4

vi UPA to PCI Interface (U2P) User's Manual • May 1997

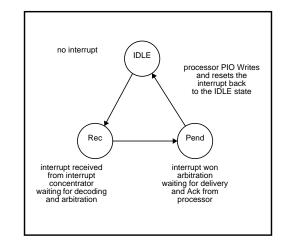

Overview of an Interrupt 8-4 Interrupt Number Register 8-5 Interrupt Types 8-6 Internal/External 8-6 Level/Pulse 8-7 Priority 8-8 Synchronization with DMA writes 8-9 Interrupt Table 8-9 Processing an Interrupt 8-11 Interrupt Receiver 8-12 Interrupt Decoder 8-12 Interrupt Arbiter 8-12 Interrupt Dispatcher 8-12

#### 9. U2P Timer/Counter 9-1

Overview 9-1 Timer Functional Description 9-2

#### 10. Little-endian support 10-1

Big- and Little-endian regions 10-1 Address Space 10-1 Internal blocks 10-2 Byte Twisting 10-2 Specific Cases 10-4 PIOs 10-4 DMA 10-5

#### 11. Error Handling 11-1

Overview 11-1 Fatal Hardware Errors 11-1 UPA Address Parity Error 11-1 Non-fatal Hardware Error 11-2 UPA Datapath Uncorrectable Error 11-2 UPA Timeout 11-3 UPA Read Error 11-3 PCI Data Parity Error 11-3 PCI Target-Abort 11-4 PCI Timeout 11-4 DVMA ECC Error 11-5 IOMMU Translation Error 11-5 PCI Address Parity Error 11-5 PCI System Error 11-6 Summary of Error Reporting 11-6 Unreported Errors 11-9

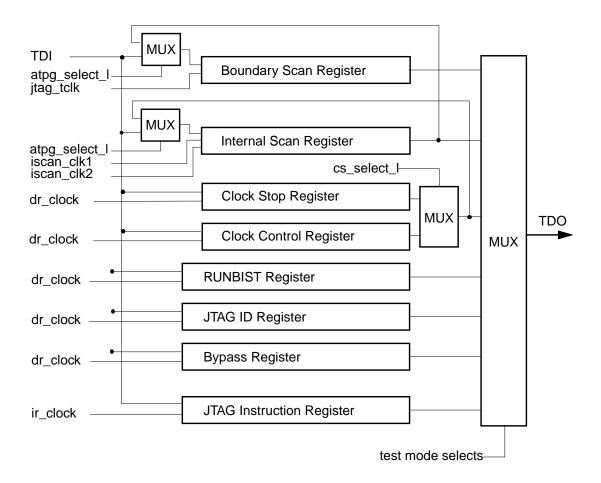

#### 12. JTAG 12-1

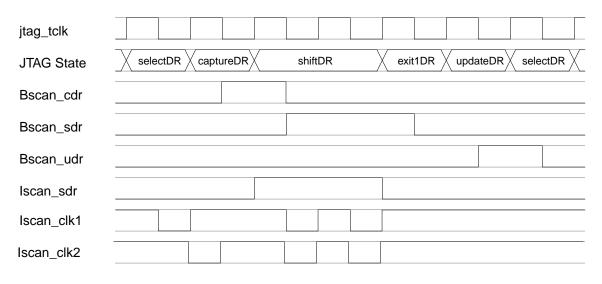

Introduction 12-1 TAP Controller 12-2 Synchronous FSM and Decode 12-5 Instruction Register 12-5 Instruction Decode Logic 12-6 Bypass Register 12-6 Internal Register Clocking Logic 12-7 JTAG ID Register 12-7 Boundary Scan Control Logic 12-7 BIST Control Logic 12-7 **Clock Control Registers** 12-8 Clock Stop Logic 12-8 TDO MUX logic 12-8 Scan Chains 12-9 Boundary Chain 12-9 The Internal Scan Chain 12-9 ATPG Chain 12-10 Special JTAG Instructions 12-10 **INTEST 12-10** The ATPG Instruction 12-10 The RUNBIST Instruction 12-11 Test Coverage Information 12-11 ATPG 12-11 BIST 12-12

#### 13. Programmer's Model 13-1

**Internal Registers 13-1** U2P Control/Status Register 13-2 UPA Registers 13-4 UPA Port ID Register 13-4 UPA Configuration Register 13-5 ECC Registers 13-6 ECC Control Register 13-6 Uncorrectable Error Asynchronous Fault Status/Address Register 13-7 Correctable Error Asynchronous Fault Status/Address Register 13-9 DMA Scoreboard Diagnostic Support 13-10 PCI Bus Module 13-12 PCI Control/Status Register 13-13 PCI Asynchronous Fault Status/Address Registers 13-14 PCI Diagnostic Register 13-17 PBM Configuration Space 13-18 Vendor ID 13-20 Device ID 13-20 Command Register 13-21 Status Register 13-22 **Revision ID Register 13-22** Programming I/F Code Register 13-23 Sub-class Code Register 13-23 Base Class Code Register 13-23 Latency Timer Register 13-23 Header Type Register 13-24 Bus Number 13-24 Subordinate Bus Number 13-24 Unimplemented Registers 13-24 IOMMU Registers 13-25 IOMMU Control Register 13-25 TSB Base Address Register 13-28 Flush Address Register 13-29 TLB TAG Diagnostics Access 13-29

TLB Data RAM Diagnostic Access 13-30 LRU Queue Diagnostic Access 13-31 Virtual Address Diagnostic Register 13-31 TLB Tag Compare Diagnostic Access 13-32 Streaming Buffer Registers 13-33 Streaming Buffer Control Register 13-34 Streaming Buffer Page Invalidate/Flush Register 13-35 Streaming Buffer Flush Synchronization Register 13-35 Streaming Buffer Page Tag Diagnostic Access 13-36 Streaming Buffer Line Tag Diagnostic Access 13-36 Streaming Buffer Data RAM Diagnostic Access 13-37 Streaming Buffer Error Status Diagnostic Access 13-37 Interrupts 13-38 Partial Interrupt Mapping Registers 13-40 Full Interrupt Mapping Registers 13-42 Clear Interrupt Registers 13-43 Interrupt State Diagnostic Registers 13-45 Interrupt Retry Timer Register 13-48 Counter/Timer Registers 13-49 Count Registers 13-49 Limit Registers 13-50 Performance Monitor Registers 13-50 Performance Monitor Control Register 13-51 Performance Counter Register 13-53 PCI Address Spaces 13-53 UPA to PCI 13-53 PCI Configuration Space 13-54 Special Cycles 13-56 PCI I/O Space 13-56 PCI Memory Space 13-56 PCI to UPA 13-57 PCI Configuration Space 13-57 PCI I/O Space 13-57 PCI Memory Space 13-57 Address Map Summary 13-59

x UPA to PCI Interface (U2P) User's Manual • May 1997

## **Figures**

Typical PCI UltraSPARC System Block Diagram 1-5

U2P External Interfaces 1-6

U2P Conceptual Block Diagram 1-7

U2P PIO and DVMA address spaces 1-11

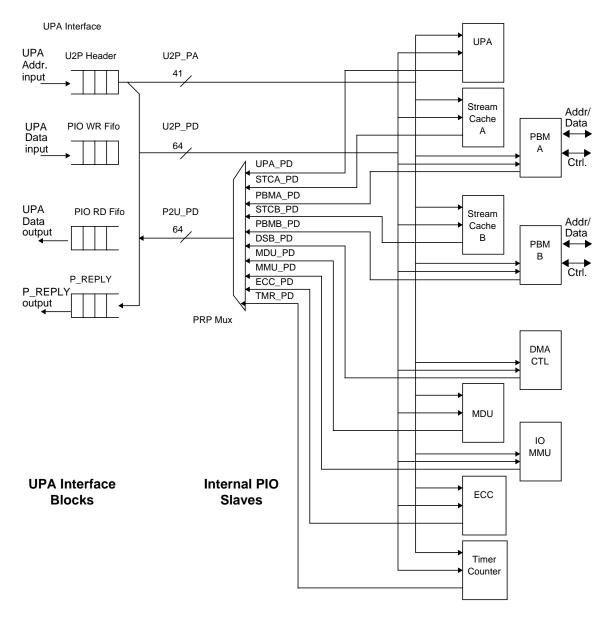

PIO Data & Address Paths 3-2

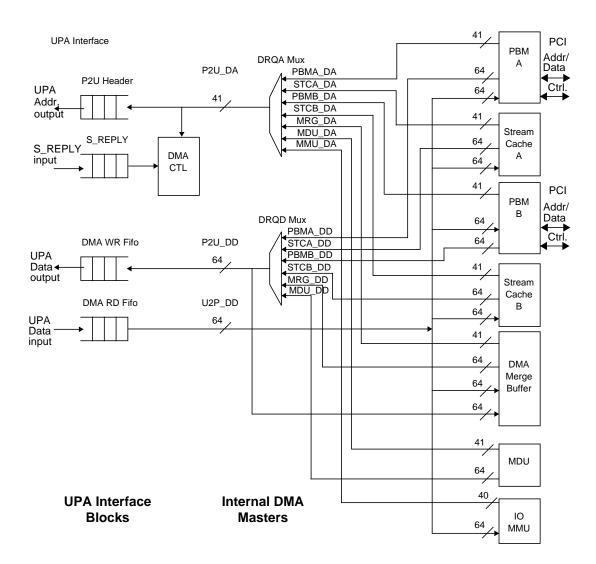

DMA Data & Address Paths 3-3

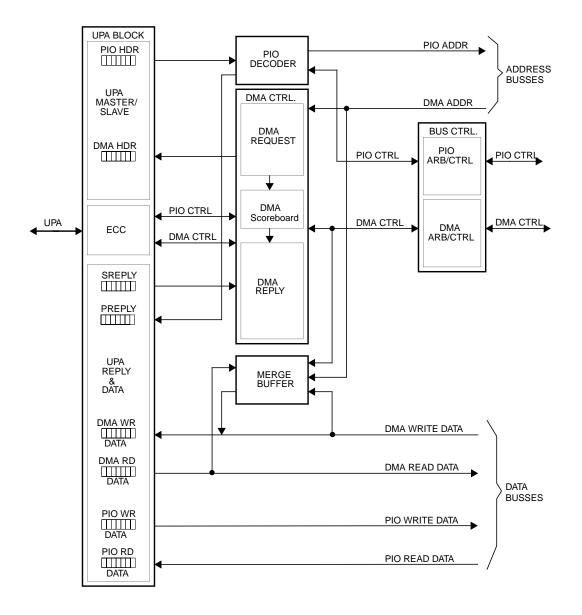

Top level block diagram for DMA and PIO transactions flow/control 4-2

DMA Write to IO space 4-6

64 Bytes DMA Writes to Memory 4-8

Less than 64 Bytes DMA Writes to Memory 4-10

DMA read request to memory or IO space 4-13

PIO Write Transaction Flow 4-15

PIO Read Transaction Flow 4-17

IOMMU top level block diagram 5-2

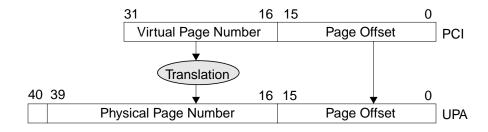

Virtual to physical address translation for 8K page size 5-5

Virtual to physical address translation for 64K page size 5-5

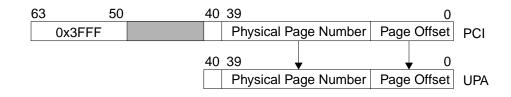

Physical address formation in bypass mode (8K and 64K) 5-5

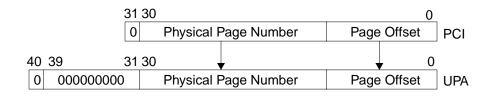

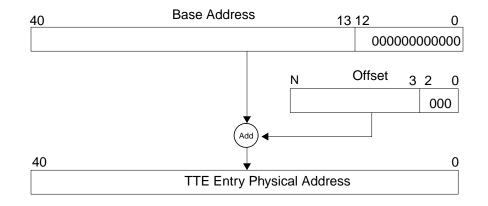

Physical address formation in pass-through mode (8k and 64K) 5-6 Computation of TTE Entry Address 5-8

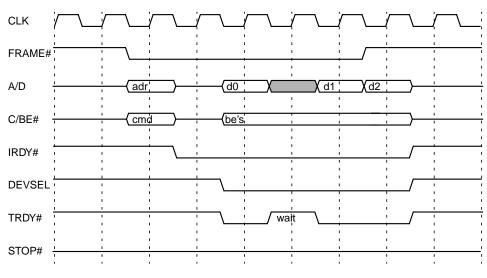

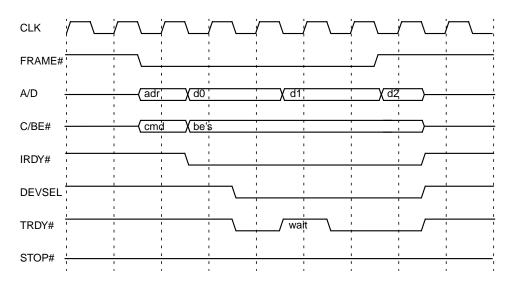

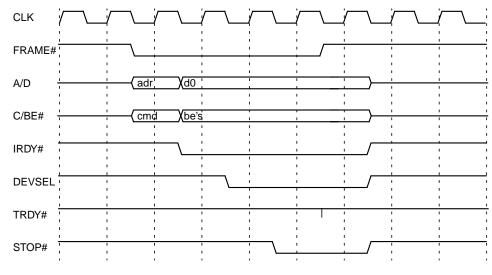

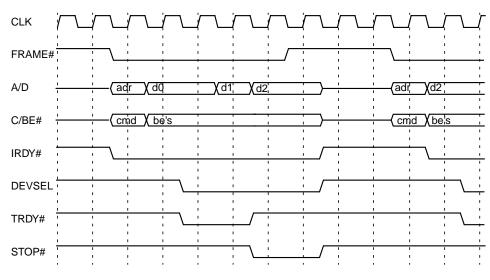

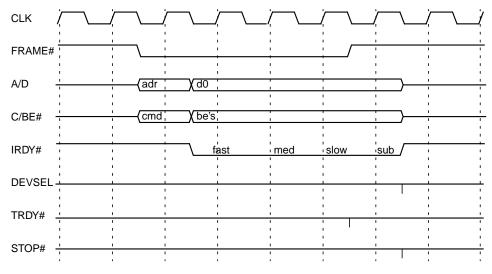

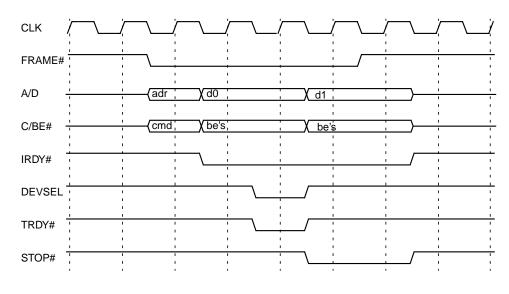

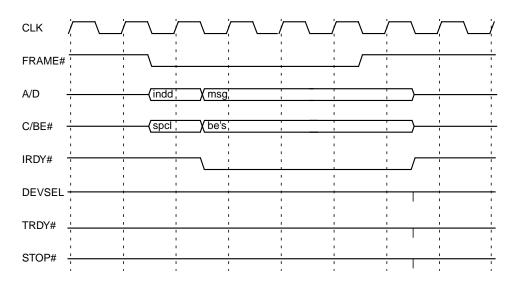

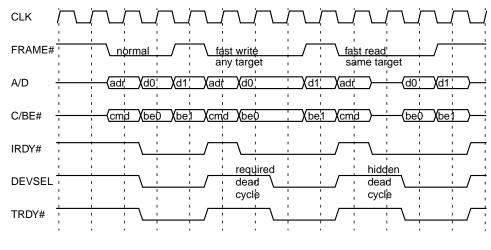

Basic PCI Read Transaction 6-3 Basic PCI Write Transaction 6-3 Retry Cycle 6-5 Disconnect Cycle 6-6 Master-abort Cycle 6-6 Target-abort Cycle 6-7 Special Cycle 6-8 Fast Back-to-Back Cycles 6-9

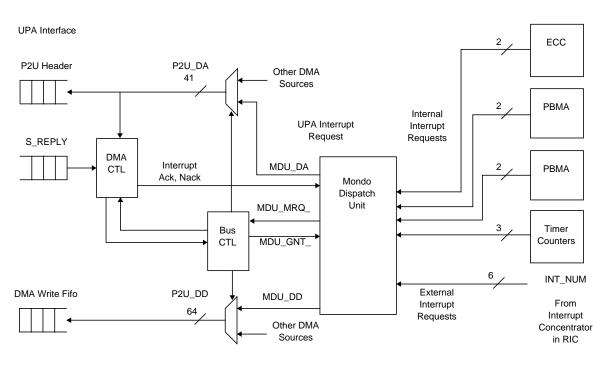

Mondo Dispatch Unit in U2P 8-2

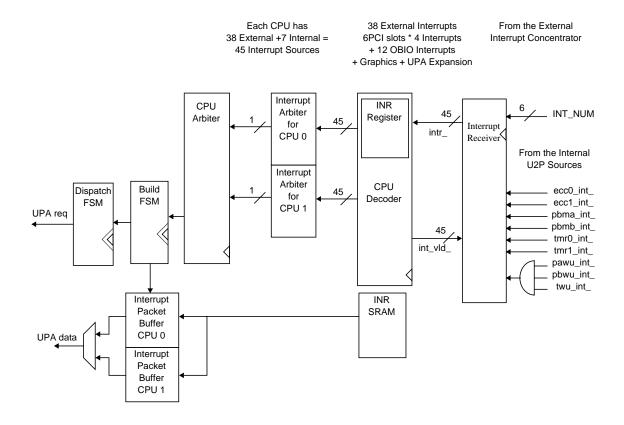

Mondo Dispatch Overview Block Diagram 8-3

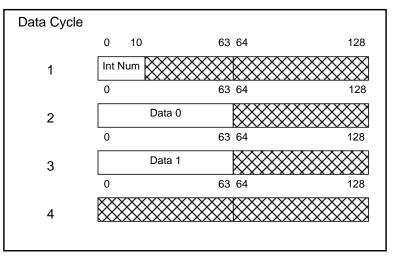

Mondo Vector Format on UPA Data Bus 8-4

Full INR Contents 8-5

Partial INR Contents 8-6

Level Interrupt States 8-8

U2P Byte Twisting 10-3

TAP Controller Block Diagram 12-2 U2P Data registers 12-3 JTAG control signals during ATPG instruction 12-11

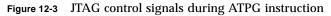

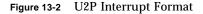

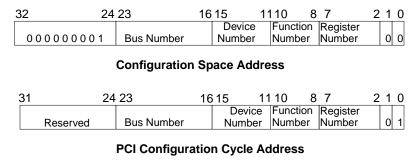

Legal DVMA address configurations 13-27 U2P Interrupt Format 13-38 Type 0 Configuration Address Mapping 13-55 Type 1 Configuration Address Mapping 13-55

xii UPA to PCI Interface (U2P) User's Manual • May 1997

## **Tables**

U2P Absolute Best Case Performance 1-4 UPA Interface Signals 2-1 PCI Bus A signals 2-2 PCI Bus B Signals 2-3 Miscellaneous Signals 2-4 Power and ground pins 2-5 Special power and ground pins 2-5 Total Pin Count 2-6 Type of P\_REQ and S\_REPLY used for DMA write to IO space 4-7 Type of S\_REPLY's U2P receives 4-7 Type of P\_REQ and S\_REPLY used for 64 byte DMA writes to memory 4-9 Type of P\_REQ and S\_REPLY used for less than 64 byte DMA writes 4-11 Type of P\_REQ and S\_REPLY used for DMA reads 4-14 Type of write P\_REQ's U2P receives and type of P\_REPLY it generates 4-16 Type of P\_REPLY's generated by U2P 4-16 Type of read P\_REQ's U2P receives and type of P\_REPLY it generates 4-18

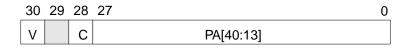

Description of TLB Tag Fields 5-3

TLB Data Format 5-3 PCI DVMA Modes of Operation 5-4 TTE Data Format 5-7 Offset to TSB Table 5-8

#### PCI Command Generation and Response 6-10

Level Interrupt States 8-7 Interrupt Receiver State Register 8-8 Summary of Interrupts 8-10

Summary of Fatal Error Reporting 11-6 Summary of Non-Fatal Error Reporting 11-7

Description of signals in JTAG macro 12-3 Components of the U2P TAP controller 12-4 Instructions supported by U2P JTAG controller 12-5 U2P scan chains 12-9 BIST register files 12-12 Non-BIST register files 12-13

Offset of Control Register 13-2 U2P Control Register 13-2 Offset of UPA Registers 13-4 UPA Port ID Register 13-4 UPA Configuration Register 13-5

Offset of ECC Registers 13-6

ECC Control Register 13-6

ECC Error Reporting 13-7

UE AFSR 13-8

**UE AFAR 13-8** CE AFSR 13-9 **CE AFAR 13-10** Offset of DMA Scoreboard Diagnostic Access 13-10 DMA Scoreboard Diagnostic Access 13-11 Offset of PBM Registers 13-12 PCI Control and Status Register 13-13 PCI AFSR 13-15 PCI AFAR 13-16 PCI Diagnostic Register 13-17 Default offset of PCI Bridge Configuration Spaces 13-18 Configuration Space Header Summary 13-19 Command Register 13-21 Status Register 13-22 Latency Timer Register 13-23 Header Type Register 13-24 Offset of IOMMU Registers 13-25 IOMMU Control Register 13-25 Address space size and base address determination 13-26 TSB Base Address Register 13-28 Flush Address Register 13-29 TLB Tag Diagnostics Access 13-29 TLB Data RAM Diagnostics Access 13-30 LRU Entry Diagnostics Access 13-31 Virtual Address Diagnostic Register 13-31 TLB Tag Comparator Diagnostics Access 13-32 Offset of Streaming Buffer Registers 13-33 Streaming Buffer General Control Register (2 copies) 13-34 Streaming Buffer Page Invalidate/Flush Register (2 copies) 13-35 Streaming Buffer Flush Synchronization Register (2 copies) 13-35 Streaming Buffer Page Tag Format 13-36 Streaming Buffer Line Tag Format 13-36 Streaming Buffer Data RAM Content Format 13-37 Streaming Buffer Data RAM Error Format 13-37 Interrupt Number Offset Assignments 13-39 Offset of Partial Interrupt Mapping Registers 13-40 Format of Partial Interrupt Mapping Registers 13-42 Offset of Full Interrupt Mapping Registers 13-42 Format of Full Interrupt Mapping Registers 13-43 Offset of Clear Interrupt Pseudo Registers 13-43 Clear Interrupt Register 13-45 Offset of Interrupt State Diagnostic Registers 13-45 Level Interrupt State Meaning 13-46 Pulse Interrupt State Meanings 13-46 PCI Int Diag Reg Definition 13-46 OBIO and Misc Int Diag Reg Definition 13-47 Offset of Interrupt Retry Timer Registers 13-48 Interrupt Retry Timer Register 13-48 Offset of Counter/Timer Registers 13-49 Count Register 13-49 Limit Register 13-50 Offset of Performance Monitor Registers 13-50 Performance Monitor Control Register 13-51 Performance Counter Event Sources 13-51 Performance Counter Register 13-53 Offsets for access from UPA space to PCI space 13-53 PCI DVMA Modes of Operation 13-58 Address Map Summary 13-59

xvi UPA to PCI Interface (U2P) User's Manual • May 1997

### CHAPTER 1

### Overview

## 1.1 Introduction

The U2P chip is the primary connection on an UltraSPARC CPU board between the UPA System Bus (including UltraSPARC Processors and Memory) and a PCI based I/O Subsystem. U2P features include:

- Full master and slave port connection to the high-speed UltraSPARC UPA Interconnect. The UPA is a split address/data packet-switched bus which has a potential data throughput rate of over 1 Gbyte/sec. UPA data is ECC protected.

- Two physically separate PCI bus segments, with full master and slave support.

PCI Bus A has the following features:

- 5 volt or 3.3 volt signalling.

- 64-bit data bus.

- Compatible with the PCI Rev 2.1 Specification.

- Compatible with the PCI 66MHz extensions.

- Support for up to four master devices (at 33MHz only).

PCI Bus B has the following features:

- 5 volt signalling.

- 64-bit data bus.

- Compatible with the PCI Rev 2.1 Specification.

- Support for up to six master devices.

- Two separate 16-entry streaming caches, one for each bus segment, for accelerating some kinds of PCI DVMA activity. Single IOMMU with 16-entry TLB for mapping DVMA addresses for both busses.

A "Mondo-Vector" Dispatch Unit, or MDU, for delivering Interrupt requests to UltraSparc CPU modules, including support for PCI interrupts from up to six total slots, as well as interrupts from on board IO devices.

## 1.2 Product Summary

### 1.2.1 Technology

0.35 micron, 3 level metal, 3.3 volt optimized CMOS standard cell library from Lucent Technologies (formerly AT&T).

### 1.2.2 Package

- The U2P die has 352 signal pads (including specialty power/grounds) and 104 VSS/VDD pads for a total pad count of 456.

- The U2P package is a 456 ball PBGA, with 352 signal balls and 104 VSS/VDD balls.

### 1.2.3 Design Size

- 170K gates.

- 29K bits RAM.

- Die size = 404.7 x 435.4 mils (10280 x 11060 microns)

### 1.2.4 Custom Cells

The following non-standard cells are used in the U2P chip design:

- 5V tolerant PCI pads.

- 66MHz capable PCI pads.

- UPA pads (with and without holding amps).

- PLL and PECL receiver for UPA clock.

- PLL for main clock.

### 1.2.5 Maximum Frequency of Operation

- UPA operation (UPACLK) up to 100 MHz (10 ns).

- Main internal clock (PSYCLK) up to 66.7 MHz (15 ns).

- PCI bus A clocks at 1x or 0.5x internal clock (synchronous).

- PCI bus B clocks at 0.5x internal clock (synchronous).

### 1.2.6 Minimum Frequency of Operation

At times it is desirable to run the clocks at less than their intended frequencies. For reliable operation, certain ratios between UPACLK and PSYCLK must be maintained.

- UPACLK > 0.9 \* PSYCLK if Mode bit = 1 (Control/Status Reg bit 0).

- PSYCLK > 0.41 UPACLK

### 1.2.7 Power Consumption

■ Maximum power consumption: 3 Watts.

## **1.3 Performance**

The performance numbers in the table below were extracted from simulations. For PIO and Consistent DMA, 16 back-to-back transactions were simulated, the first 4 were ignored, and the remaining ones were timed. For Streaming DMA, 64 back-to-back transactions were simulated and the first 16 ignored.

| Xfer<br>Size | Bus speed                                       | Bus Width | PIO Wr | PIO Rd <sup>1</sup> | DMA Wr<br>Consistent | DMA Rd<br>Consistent | DMA Wr<br>Streaming | DMA Rd<br>Streaming |  |  |

|--------------|-------------------------------------------------|-----------|--------|---------------------|----------------------|----------------------|---------------------|---------------------|--|--|

| 4            | 33 MHz                                          | 32 bit    | 22.2   | 8.3                 | 10.3                 | 7.7                  | 22.5                | 24.2                |  |  |

| 16           | 33 MHz                                          | 32 bit    | 59.3   | 26.7                | 40.3                 | 27.9                 | 61.0                | 53.3                |  |  |

| 64           | 33 MHz                                          | 32 bit    | 97.0   | 66.7                | 106.7                | 71.1                 | 106.7               | 106.7               |  |  |

| 8            | 33 MHz                                          | 64 bit    |        |                     | 19.5                 | 15.8                 | 45.4                | 44.6                |  |  |

| 16           | 33 MHz                                          | 64 bit    |        |                     | 39.5                 | 29.6                 | 79.0                | 59.3                |  |  |

| 64           | 33 MHz                                          | 64 bit    |        |                     | 177.8                | 94.1                 | 177.8               | 164.1               |  |  |

| 4            | 66 MHz                                          | 32 bit    | 33.3   | 11.1                | 10.1                 | 8.6                  | 33.6                | 33.3                |  |  |

| 16           | 66 MHz                                          | 32 bit    | 106.7  | 38.1                | 40.0                 | 33.3                 | 99.2                | 76.2                |  |  |

| 64           | 66 MHz                                          | 32 bit    | 185.5  | 103.2               | 193.9                | 106.7                | 193.9               | 185.5               |  |  |

| 8            | 66 MHz                                          | 64 bit    |        |                     | 19.6                 | 17.4                 | 67.7                | 59.3                |  |  |

| 16           | 66 MHz                                          | 64 bit    |        |                     | 40.5                 | 34.3                 | 121.9               | 82.1                |  |  |

| 64           | 66 MHz                                          | 64 bit    |        |                     | 304.8                | 125.5                | 304.8               | 222.1               |  |  |

|              | All performance measurements are in MBytes/sec. |           |        |                     |                      |                      |                     |                     |  |  |

Table 1-1

U2P Absolute Best Case Performance

1. The PIO read performance numbers shown here are not absolute best case numbers. Simulations were run with only a single outstanding PIO read allowed. In systems where multiple outstanding PIO reads are supported, somewhat higher PIO read performance numbers are possible.

**Caution** – Except where noted, the table above lists the maximum achievable performance for the U2P chip. These are not minimum or typical performance numbers. Many factors can reduce the above performance numbers, including but not limited to: (1) System clock speed; (2) Contention for memory or UPA bus; (3) Specific SC implementation details; (4) IOMMU tablewalks, or thrashing in the IOMMU or streaming cache; (5) Insertion of wait-states by PCI device (as master or slave); (6) Software overhead.

## 1.4 Typical System Partition

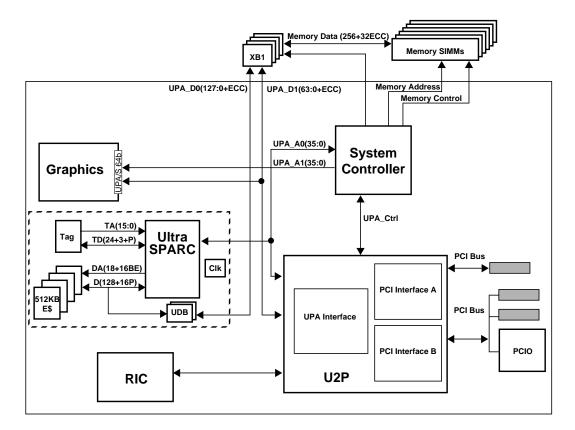

Figure 1-1 shows one possible configuration of U2P in a PCI UltraSPARC system. U2P connects to the system controller chip and other UPA ports via UPA address, control and data busses. The system has both PCI and EPCI slots, as well as an on board PCI device (PCIO). Interrupt information is provided by the RIC chip, and a JTAG port is provided for board test as well as in-circuit test and debug of U2P.

Figure 1-1 Typical PCI UltraSPARC System Block Diagram

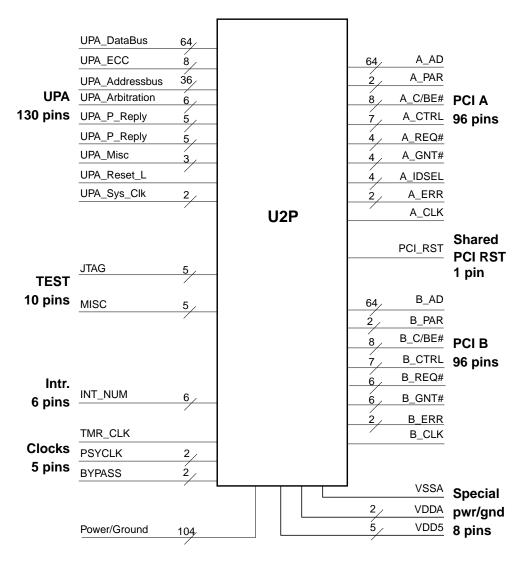

# 1.5 U2P External Interfaces

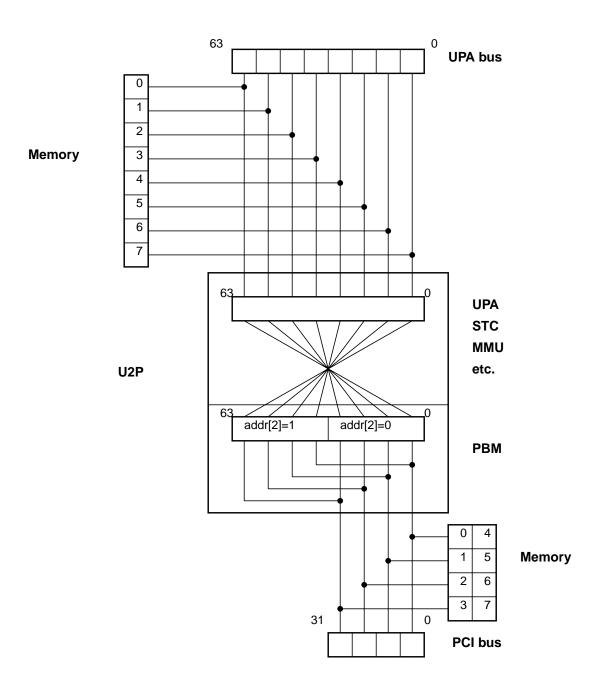

Figure 1-2 summarizes the external interfaces and pins of U2P.

Figure 1-2 U2P External Interfaces

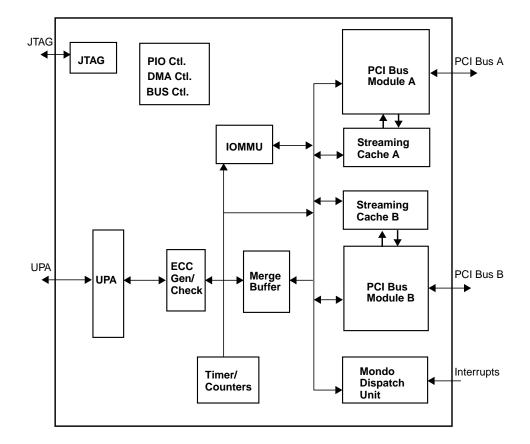

# 1.6 U2P Block Diagram

The diagram below shows a conceptual block diagram of U2P. The actual implementation is somewhat different, for example, there are no internal bidirectional busses. Details of specific implementation of each block can be found in the following chapters.

Figure 1-3 U2P Conceptual Block Diagram

## 1.7 U2P Block Overviews

This section gives a brief description of each top level functional block. A more detailed description of each block can be found in Chapter 3. Each block is also described in its own individual chapter as well. The top level blocks in U2P fall into one of five categories:

- UPA.

- PCI.

- Interrupt.

- Internal Control.

- Miscellaneous.

### 1.7.1 UPA Interface blocks

The UPA is UltraSPARC system's packet switched main system bus. In an UltraSPARC system, the UPA can operate up to 100 MHz. Data and address have independent flow controls. Each type of UPA cycle (PIO read, PIO write, DMA read, etc.) uses its own FIFO-based queueing. There is a synchronization boundary between the UPA interface blocks and other U2P blocks, which run at 66.7 MHz.

- UPA Master/Slave: This block deals exclusively with UPA address control. It listens to UPA\_A when U2P is a slave. It also arbitrates for and drives UPA\_A when U2P is a master.

- UPA\_Reply: This block deals exclusively with UPA data. It generates P\_REPLY to the System Controller (SC) ASIC during PIO and copyback cycles. It also listens to S\_REPLY from the SC and manages the UPA data FIFOs accordingly.

- **ECC Generate:** Generates ECC on the outgoing 64-bit UPA data path.

- **ECC Check:** Checks ECC on the incoming 64-bit UPA data path.

### 1.7.2 PCI Interface blocks

PCI Bus Module (PBM): This is the main portion of the PCI interface. U2P contains two nearly identical copies of this block. One is designed to support a 64-bit PCI bus at 66 MHz or 33 MHz with up to four master devices. The other supports a 64-bit PCI bus at 33MHz with up to six master devices. The PBM adheres to all PCI protocol guidelines as contained in the PCI Revision 2.1

specification. Each PBM controls arbitration, flow control and error handling for its bus segment. Each PBM also handles the big- to little-endian byte twisting required for correct operation of both PIO and DVMA datapaths.

- IOMMU: For the portion of the PCI memory address space which is reserved for DMA to the UPA bus, the IOMMU maps the PCI address into the appropriate UPA physical address. The IOMMU keeps the 16 most recently used translations in a TLB, and automatically performs hardware tablewalks on TLB misses. There is a single IOMMU supporting both PCI busses. Only a single translation can be in progress at a time, and during tablewalks, translations from the other bus segment will be delayed.

- Streaming Cache: The Streaming Cache (STC) is used to accelerate PCI DMA activity. For DMA reads, the STC will speculatively prefetch 64-byte cache lines. For DMA writes, the STC buffers up 64-byte lines before sending to the UPA interface. There are two separate STC blocks in U2P, one associated with each PBM block. Each STC contains storage for 16 virtual address tagged entries and their data, which is stored in 64-byte lines, allocated on a least recently used basis.

### 1.7.3 Interrupt block

Mondo Dispatch Unit (MDU): In the Sun-4U architecture, interrupts to a processor are sent as packets on the UPA bus. The MDU in U2P is a system resource for generating such packets. The MDU accepts interrupt requests from the UPA slave ports, PCI busses and internal U2P sources and dispatches interrupt packets to the UPA.

### 1.7.4 Internal Control

- Merge Buffer: In order to allow sub-line writes into a 64-byte memory line, it is necessary to perform a read-modify-write operation on the UPA. The Merge Buffer is responsible for generating the correct UPA read, merging the partial line, and writing the whole block to the UPA.

- **PIO Control:** Decodes slave requests from the UPA\_A request FIFO, arbitrates for the appropriate resource and dispatches the request.

- Bus Control: This is an internal arbiter shared by the PIO Control and DMA Control blocks. It schedules the use of the main internal data paths.

- **DMA Control:** Arbitrates and decodes requests from internal DMA sources (PBM, STC, IOMMU, MDU), and arbitrates for the appropriate UPA FIFO.

### 1.7.5 Clock Ratios

At times it is desirable to run the clocks at less than their intended frequencies. Such instances might be using the part in a low speed emulation environment, or if on power up the clocks are defaulted to something other than their usual speed.

There are two ratios that must be adhered to:

- UPACLK > 0.9 \* PSYCLK if Mode bit = 1 (Control/Status Reg bit 0). Prevents underrunning the UPA input FIFO which could occur if UPACLK is running too slow in relation to PSYCLK.

- PSYCLK > 0.41 UPACLK.

Prevents underrunning the DMA write data FIFO which could occur if PSYCLK is running too slow in relation to UPACLK.

Note that it is clock ratios which are being specified here and not a minimum operating frequency. U2P has been used in emulation at speeds in the 1KHz range.

### 1.7.6 Miscellaneous

- **Timer/Counter:** Contains two identical 32-bit timer-counters as specified by the Sun-4U architecture. Used for system scheduling and profiling.

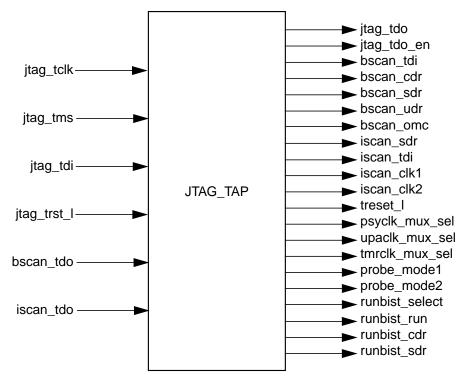

- JTAG Control: Provides the necessary control for the standard IEEE 1149.1 JTAG port, as well as additional scan based features that are useful for debugging purposes.

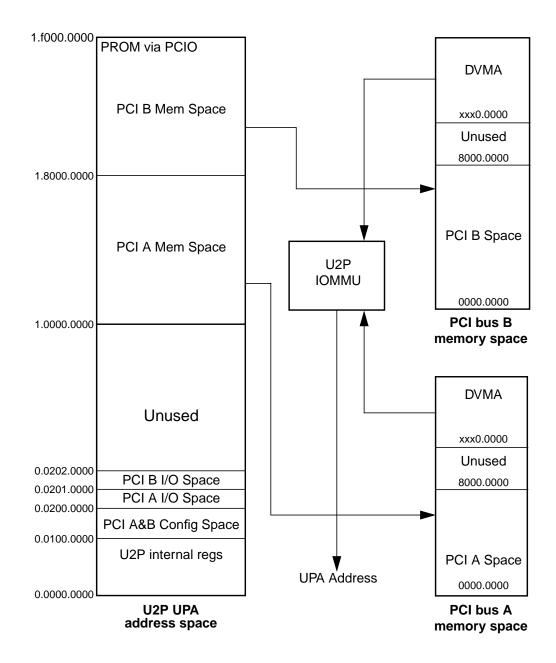

## 1.8 PCI Address Map Overview

Complete information on address maps and other software visible features of U2P can be found in Chapter 13. A simplified diagram showing PIO and normal DVMA address spaces is in Figure 1-4.

Figure 1-4 U2P PIO and DVMA address spaces

1-12 UPA to PCI Interface (U2P) User's Manual • May 1997

### CHAPTER **2**

# **U2P Pin Descriptions**

# 2.1 UPA Interface Signals

These signals connect U2P to the UPA. Maximum frequency of operation is 100 MHz.

| Table 2-1         UPA Interface Signature |

|-------------------------------------------|

|-------------------------------------------|

| Signal Name     | Pin<br>Count | I/O | Description                                     |  |

|-----------------|--------------|-----|-------------------------------------------------|--|

| UPA_DataBus     | 64           | I/O | 64 bit Data Bus                                 |  |

| UPA_ECC         | 8            | I/O | 8 bits for ECC                                  |  |

| UPA_Addressbus  | 36           | I/O | Address/request lines + parity                  |  |

| UPA_Req_in      | 3            | Ι   | Requests from other clients on this address bus |  |

| UPA_Req_out     | 1            | 0   | Request asserted by U2P                         |  |

| UPA_SC_Req_in   | 1            | Ι   | Request from the SC                             |  |

| UPA_Arb_Reset_L | 1            | Ι   | UPA Arbiter reset                               |  |

| UPA_Addr_Valid  | 1            | I/O | Valid address; active high                      |  |

| UPA_ECC_Valid   | 1            | Ι   | ECC Valid                                       |  |

| UPA_Data_Stall  | 1            | I   | Data Stall                                      |  |

| UPA_P_Reply     | 5            | 0   | Port Reply signals                              |  |

| UPA_S_Reply     | 5            | Ι   | System Reply signals                            |  |

Table 2-1

UPA Interface Signals (Continued)

| Signal Name                        | Pin<br>Count | I/O | Description              |

|------------------------------------|--------------|-----|--------------------------|

| UPA_Reset_L                        | 1            | Ι   | Port/System Reset Signal |

| UPA_Sys_Clk_pos<br>UPA_Sys_Clk_neg |              |     | UPA System Clock (PECL)  |

| UPA Total                          | 130          |     |                          |

## 2.2 64-bit, 66MHz capable PCI Interface Signals (PCI Bus A)

These signals connect U2P to the 64-bit,  $66\rm MHz$  capable PCI bus segment. Maximum frequency of operation is  $66.7~\rm MHz.$

| Signal Name  | Pin Count | I/O | Description                                |  |

|--------------|-----------|-----|--------------------------------------------|--|

| A_AD<63:0>   | 64        | I/O | Address/Data Bus                           |  |

| A_PAR        | 1         | I/O | Parity for AD<31:0>                        |  |

| A_PAR64      | 1         | I/O | Parity for AD<63:32>                       |  |

| A_CBE_<7:0>  | 8         | I/O | Command/Byte enable lines                  |  |

| A_FRAME_     | 1         | I/O | Cycle frame                                |  |

| A_REQ64_     | 1         | I/O | Request 64-bit transfer                    |  |

| A_ACK64_     | 1         | I/O | Acknowledge 64-bit transfer                |  |

| A_TRDY_      | 1         | I/O | Target Ready                               |  |

| A_IRDY_      | 1         | I/O | Initiator Ready                            |  |

| A_STOP_      | 1         | I/O | Target initiated STOP                      |  |

| A_DEVSEL_    | 1         | I/O | Target decoded its address                 |  |

| A_IDSEL<3:0> | 4         | 0   | Chip select lines for configuration cycles |  |

| A_PERR_      | 1         | I/O | Parity Error                               |  |

| A_SERR_      | 1         | I/O | System Error                               |  |

| A_CLK        | 1         | Ι   | PCI Clock                                  |  |

Table 2-2

PCI Bus A signals

Table 2-2

PCI Bus A signals (Continued)

| Signal Name     | Pin Count | I/O | Description                   |

|-----------------|-----------|-----|-------------------------------|

| A_REQ_<3:0>     | 4         | Ι   | Bus master request lines      |

| A_GNT_<3:0>     | 4         | 0   | Bus master grant lines        |

| PCI_RST_        | 1         | Ι   | Reset (shared with PCI bus B) |

| PCI Bus A total | 97        |     |                               |

2.3

## 64-bit, 33MHz PCI Interface Signals (PCI Bus B)

These signals connect U2P to the 32-bit PCI bus segment. Maximum frequency of operation is 33.3 MHz.

| Signal Name | Pin Count | I/O | Description                 |

|-------------|-----------|-----|-----------------------------|

| B_AD<63:0>  | 64        | I/0 | Address/Data Bus            |

| B_PAR       | 1         | I/0 | Parity for AD<31:0>         |

| B_PAR64     | 1         | I/0 | Parity for AD<63:32>        |

| B_CBE_<7:0> | 8         | I/0 | Command/Byte enable lines   |

| B_FRAME_    | 1         | I/0 | Cycle frame                 |

| B_REQ64_    | 1         | I/0 | Request 64-bit transfer     |

| B_ACK64_    | 1         | I/0 | Acknowledge 64-bit transfer |

| B_TRDY_     | 1         | I/0 | Target Ready                |

| B_IRDY_     | 1         | I/0 | Initiator Ready             |

| B_STOP_     | 1         | I/0 | Target initiated STOP       |

| B_DEVSEL_   | 1         | I/0 | Target decoded its address  |

| B_PERR_     | 1         | I/0 | Parity Error                |

| B_SERR_     | 1         | I/O | System Error                |

| B_CLK       | 1         | Ι   | PCI Clock                   |

| B_REQ_<5:0> | 6         | Ι   | Bus master request lines    |

Table 2-3 PCI Bus B Signals

Table 2-3

PCI Bus B Signals (Continued)

| Signal Name     | Pin Count | I/O | Description                   |

|-----------------|-----------|-----|-------------------------------|

| B_GNT_<5:0>     | 6         | 0   | Bus master grant lines        |

| PCI_RST_        | 0         | Ι   | Reset (shared with PCI bus A) |

| PCI Bus B total | 96        |     |                               |

# 2.4 Miscellaneous Interfaces

Clocks, interrupts, JTAG interface, and other test pins.

| Signal Name   | Pin Count | I/O | Description                                 |  |

|---------------|-----------|-----|---------------------------------------------|--|

| PSYCHOPS_CLK  | 1         | Ι   | 66 MHz main clock                           |  |

| PSYCHOPS_CLKR | 1         | Ι   | Reference pin for PSYCHOPS_CLK              |  |

| PSY_BYPASS    | 1         | Ι   | Bypass PLL on PSYCHOPS_CLK                  |  |

| UPA_BYPASS    | 1         | Ι   | Bypass PLL on UPA_Sys_Clk                   |  |

| TMR_CLK       | 1         | Ι   | 10 MHz timer/counter clock                  |  |

| INT_NUM       | 6         | Ι   | Encoded interrupt number                    |  |

| BOOT_BUS      | 1         | Ι   | Select PCI bus A or B for system boot path  |  |

| EXT_EVENT     | 1         | Ι   | External event trigger                      |  |

| INT_EVENT     | 1         | 0   | Internal event trigger                      |  |

| B_CPU_REQ     | 1         | 0   | Test signal - copy of PBMB internal request |  |

| B_CPU_GNT     | 1         | 0   | Test signal - copy of PBMB internal grant   |  |

| JTAG          | 5         | I/O | JTAG test port                              |  |

| Misc. total   | 21        |     |                                             |  |

Table 2-4

Miscellaneous Signals

## 2.5 Power and Ground Pins/Pads

Each signal pin (or ball) is directly connected to a pad on the U2P die. Power and ground pins are connected to power and ground planes on the package substrate. Power and ground pads on the die are connected to these planes as well, but there is no 1-1 correspondence between power/ground pads and pins.

Table 2-5Power and ground pins

| Signal Name     | Pad<br>Count | Pin<br>Count | Description       |  |

|-----------------|--------------|--------------|-------------------|--|

| VDD             | 52           | 32           | 3.3V power supply |  |

| VSS             | 52           | 72           | Digital ground    |  |

| Power total 104 |              | 104          |                   |  |

In addition to the main power and ground pins, U2P has some special purpose power and ground pins. These are treated as signal pads/balls, and there is no special handling on the package substrate.

| Signal Name Pad Pin<br>Count Count |   |   | Description          |  |

|------------------------------------|---|---|----------------------|--|

| VDD5                               | 5 | 5 | 5V reference voltage |  |

| VDDA                               | 2 | 2 | 3.3V analog supply   |  |

| VSSA                               | 1 | 1 | Analog ground        |  |

| Special total                      | 8 | 8 |                      |  |

Table 2-6Special power and ground pins

# 2.6 Total Pin/Pad Count

| Interface            | Pad Count | Pin Count |

|----------------------|-----------|-----------|

| UPA                  | 130       | 130       |

| PCI Bus A            | 97        | 97        |

| PCI Bus B            | 96        | 96        |

| Miscellaneous        | 21        | 21        |

| Special Power/Ground | 8         | 8         |

| Subtotal             | 352       | 352       |

| Power/Ground         | 104       | 104       |

| Total Count          | 456       | 456       |

#### Table 2-7 Total Pin Count

### CHAPTER 3

## **U2P** Functional Description

## 3.1 Functional Overview

This chapter contains the functional description of the U2P chip at the top level. Overall chip design is discussed and the address data/flow is presented. This chapter has 2 major sections:

- Block diagrams of the address and data paths.

- A description of each of the major design blocks within U2P.

# 3.2 Top-Level Architectural Philosophy

When reviewing the U2P internal bus structure, it is important to keep in mind the architectural philosophy of the chip:

- U2P has a UPA bus.

- U2P has two PCI busses.

- The design connects them together so that data goes as fast as possible without making the chip too complicated.

- Where practical, the UPA to SBus (U2S) chip design has been leveraged.

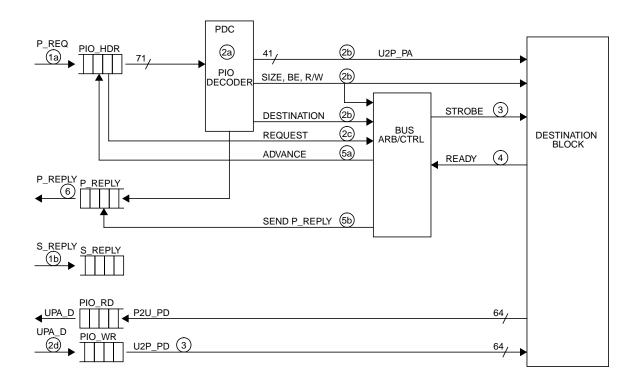

Figure 3-1 PIO Data & Address Paths

Figure 3-2 DMA Data & Address Paths

## 3.3 Block Overviews

### 3.3.1 PIO Decoder

This block decodes requests from the U2P header request FIFO. The target of the PIO cycle may be either PCI bus or one of the internal U2P units. For PCI, the corresponding PBM will determine the transaction timing based on the response of the PCI device. For internal units, the PIO Decoder and Bus Controller block control the timing. All PIO requests are serviced strictly in order and one at a time.

For PIO accesses to PCI configuration space, the PIO Decoder does not have enough information to determine which PBM receives the transaction. With the help of the Bus Controller block, the PIO Decoder will forward the request to both PBM modules. Based on the values programmed into the Bus Number and Subordinate Bus Number registers in each PBM, one or none of the PBM's will accept the PIO, and the Bus Control unit will correctly handle the situation.

The PIO decoder allows the following transaction types:

- P\_NCBRD\_REQ, P\_NCBWR\_REQ Only to PCI memory space portion of address space, not to U2P internal address space or PCI config or PCI I/O space.

- P\_NCRD\_REQ With byte masks representing 1, 2, 4, or 8-byte aligned accesses to any U2P internal register.

- P\_NCRD\_REQ With byte masks representing 1, 2, or 4-byte aligned accesses to PCI I/O or PCI Configuration space.

- P\_NCRD\_REQ 1, 2, 4, 8, or 16-byte accesses are allowed to PCI memory space.

- P\_NCWR\_REQ 8-byte accesses are allowed to U2P internal registers (less than 8byte access is allowed, but treated as 8 bytes).

- P\_NCWR\_REQ 4-byte or less accesses are allowed to PCI I/O or PCI Configuration Space.

- P\_NCWR\_REQ Any arbitrary byte mask is allowed to PCI memory space.

## 3.3.2 DMA Control

This block decodes and builds the UPA packet for requests from PCI bus A or B, streaming cache A or B, the IOMMU, the Mondo Dispatch Unit or the Merge Buffer. This block also keeps a FIFO of the requests. All DMA transactions are issued on the UPA with the class bit set to 0, so the UPA will service U2P DMA requests in order. U2P is capable of generating the following transaction types:

- P\_NCBRD\_REQ, P\_NCBWR\_REQ From PBM blocks only.

- P\_NCWR\_REQ From PBM block only, may have arbitrary byte mask.

- P\_RDO\_REQ, P\_WRB\_REQ From merge buffer for partial line DMA writes.

- P\_RDD\_REQ From PBM, STC or IOMMU.

- P\_WRI\_REQ From PBM or STC.

- P\_INT\_REQ From Mondo Dispatch Unit.

## 3.3.3 Bus Control

This is an internal arbiter shared between the DMA Control and PIO Control units. The bus control unit handles timing of internal U2P resources based on the number of clocks required for each kind of transaction. The bus control unit correctly handles "ambiguous" PIO destinations (i.e. PIO's to PCI configuration space, in which either or none of the PBM blocks may respond).

There are separate busses for each of the following operations: PIO read, PIO write, DMA read and DMA write. The PIO read and write busses are considered a single resource by the bus controller, so only one PIO operation is in progress at a time. The remaining busses are independent, however, so the bus controller allows a PIO operation, a DMA read, and a DMA write all to be in progress at the same time.

The bus controller also handles allocation of the merge buffer. A DMA write that requires the merge buffer is held off until it is available. Once the merge buffer is allocated, the bus controller will not allow any other DMA operation to be initiated until the merged data is written back to the UPA.

### 3.3.4 UPA Master / Slave

The UPA Master / Slave (UMS) block is U2P's interface to the UPA\_A request bus. When U2P is addressed as a UPA slave (PIO requests), the UMS always writes the request into the U2P Header FIFO.

When U2P is performing a DMA request, the UMS arbitrates for use of the UPA\_A bus and drives the request out from the P2U Header FIFO.

As with the UPA Reply block, the UMS runs at the UPA clock frequency, up to 100 Mhz. Signals from other internal U2P blocks are 2-clock synchronized by the UMS before being used. Likewise, status and control which is an output of the UMS block is 2-clock synchronized with the U2P main clock (66.7 Mhz) before being used.

## 3.3.5 UPA Reply

The UPA Reply unit manages replies to the system controller. P\_REPLY requests are received from the PIO Control Unit and forwarded to the UPA bus. For PIO reads, P\_REPLY indicates that U2P has read data ready in the PIO\_RD FIFO. For PIO writes, P\_REPLY indicates that U2P has removed write data from the PIO\_WR FIFO. P\_REPLY is not used for DMA.

S\_REPLY is used for both PIO and DMA cycles. For PIO reads, S\_REPLY indicates that the system controller is ready to read data out of the PIO\_RD FIFO. For PIO writes, S\_REPLY indicates that data is being written into the PIO\_WR FIFO. For DMA reads, S\_REPLY indicates that data is being delivered into the DMA\_RD FIFO, and for DMA writes, S\_REPLY indicates that the system controller is ready to read data out of the DMA\_WR FIFO.

The UPA Reply unit is responsible for reading and writing the appropriate data FIFO's and enabling the UPA Data outputs if necessary. In addition, the UPA Reply unit must control the ECC check logic. When data is arriving at U2P (related to a PIO write or DMA read), the data is ECC checked. The UPA Reply unit must accumulate the ECC results for the entire packet, which may be between 1 and 64 bytes in length. The UPA Reply unit manages a separate packet status FIFO which signals the PIO and DMA CTL units of error conditions.

## 3.3.6 ECC Generate / Check

The ECC unit is split into separate generate and check functions. ECC is always calculated on 64 bits of data. The ECC generate logic is positioned on the "internal" side of all of the data FIFO's. (There is not enough time between receiving S\_REPLY and providing data to generate the ECC if the logic is on the UPA side of the FIFO.) This also allows more flexibility in the circuit timing since the UPA clock is faster than the internal U2P clock. In some situations, it is necessary for U2P to generate intentionally bad ECC with the data. When this is needed, bits [1:0] of the outgoing ECC are inverted to provide a guaranteed Uncorrectable Error.

The ECC check logic will detect Correctable and Uncorrectable ECC errors. (CE and UE errors.) Refer to the ECC chapter for the rules for detecting and correcting errors. For a correctable error, the data will be repaired before being sent to the internal destination block. None of the internal U2P units will be aware of CE errors. For both UE and CE errors, the ECC unit will signal the Mondo Dispatch Unit to generate a Mondo Vector (interrupt) if enabled.

### 3.3.7 DMA Merge Buffer

The DMA Merge Buffer block is used for servicing cacheable DMA Writes of less than 64 bytes (partial writes). This is required in a UPA based system because there is no way to write cacheable memory in sub-line increments. (There are at least 2 problems that force this; the SIMMS do not have individual byte controls and ECC is generated on 8-byte boundaries.). In order to perform a sub-line write, U2P performs a UPA Read-to-Own (P\_RDO\_REQ) transaction to gain control of the line, merge the new data into the line and then flush the line to memory with a UPA Writeback (P\_WRB\_REQ) transaction. Once the Merge Buffer's request for a Read-to-Own transaction is granted internally, no other DMA requests will be serviced until the writeback completes.

The only blocks capable of partial writes are the two PBM's and the two streaming caches. The Merge Buffer contains a 64-byte buffer for storing the partial line while waiting for data from the P\_RDO\_REQ transaction. There are valid bits for each byte in the buffer, so it is able to handle completely arbitrary byte enables on a consistent write from a PCI device. Although the merge buffer could also handle arbitrary byte enables on a streaming access, U2P does not support this because the streaming cache only stores a begin and end pointer for valid data, and not individual byte enables.

To avoid the complexity of having to participate in system coherence during a merge, the external system controller is responsible for blocking all requests to the line for which U2P has issued a Read-to-Own until the data merge is completed and U2P has issued a Writeback of the line to memory. U2P will not issue any other transactions between the Read-to-Own and the Writeback.

The DMA Merge Buffer is not intended to be a high performance solution for subline DMA writes from a PCI bus; rather its purpose is to provide correct functionality given the UPA bus constraints. The streaming cache (STC) can be used to improve PCI performance by buffering data into 64-byte lines before flushing to memory. STC line flushes that contain a complete 64 bytes will be able to bypass the Merge Buffer by doing a Write Invalidate (P\_WRI\_REQ) on the UPA.

## 3.3.8 PCI Bus Module (PBM)

Each PCI Bus Module block implements a complete PCI Master and Slave interface. Each PBM implements all of the required host bridge functions for PCI, and also acts as the central resource for: arbitration, reset, and system error (SERR#) monitoring.

The PBM handles the timing of PIO requests to the PCI bus. These are handled one at a time. The PBM handles target disconnects, retries and various error conditions during the PIO. If necessary, multiple PCI transactions will be generated for each PIO (up to 16 transactions in the case of 64-byte block reads or writes). While the multiple transactions of a single PIO are occurring on the PCI bus, DMA requests from other devices on that bus can be still be serviced.

Only 1, 2, 4, 8, 16 or 64-byte aligned PIO read accesses are allowed to the PCI bus Memory Space. Writes to the PCI bus Memory Space may be of any size supported on the UPA. For most PIO's, the command used on the PCI bus will be Memory Read or Memory Write. 64-byte PIO reads will use the Memory Read Line command. Other command types can be generated by PIO's to special regions in the PCI address space. These include the Configuration Read, Configuration Write, I/O Read, I/O Write, and Special Cycle commands. With these command types, only 4byte or smaller PIO's are supported.

The PBM also responds as a target to other PCI masters. The PBM will respond to any PCI Memory Space transaction for which address bit 31 is on. Typically, the transaction address is treated as a virtual address, and translated to a physical address by the IOMMU. These transactions are referred to as DVMA transactions. The PBM communicates with the IOMMU and STC blocks as needed to complete DVMA cycles to/from the PCI bus. (An IOMMU bypass mode is also available, which can directly access the entire UPA physical address space using PCI Dual-Address Cycles.) DVMA data can be moved from the PCI bus to either the associated STC or directly to the UPA. Peer-to-peer DMA is also allowed between two devices on the same PCI bus segment, but due to the way PCI addressing is defined, U2P is not involved in these transfers (except as the central arbiter for bus request and grant signals).

The PBM will only respond, as a target, to PCI memory space commands (Memory Read, Memory Read Line, Memory Read Line Multiple, Memory Write, and Memory Write & Invalidate). All other PCI command types are ignored.

All PCI transactions targeting U2P will be disconnected by the PBM if the master attempts to cross a 64-byte boundary. Under certain conditions, the PBM will issue a retry for an incoming PCI transaction. These conditions include:

- PBM requests the IOMMU to do a tablewalk to get mapping for this transaction.

- STC indicates that it is initiating a request to get the desired read data.

- Due to congestion, resources (buffers) are currently lacking to accept a transaction.

For DVMA transactions to cacheable memory, based on the IOMMU mapping information for the virtual address, the PBM will treat the DVMA cycle as a **consistent** or **streaming** access (accesses made in IOMMU bypass mode are always treated as consistent). Consistent accesses are sent directly to the UPA and have strict ordering constraints; The performance of consistent accesses can be worse than streaming accesses (particularly for reads or sub-line writes), and DVMA pages should only be marked consistent-mode when necessary. DVMA accesses to noncacheable memory is always treated in consistent mode. For consistent DVMA reads, the PBM treats all three PCI memory read commands identically. For streaming reads, the PBM passes the information on which command was used to the streaming cache so that a decision can be made on prefetching data. For all DVMA write transactions, both PCI memory write commands are treated the same.

For DVMA reads, the DVMA master may drive arbitrary byte enables on the PCI bus, which will be ignored. DVMA reads always generate 64-byte requests on the UPA bus, and correct data is returned for all byte lanes on the PCI bus, regardless of the byte enables.

For consistent DVMA writes, arbitrary byte enables are also allowed. The byte enables for the transaction are stored along with the data, and are passed on to the Merge Buffer for partial line writes to cacheable space. For non-cacheable partial writes, the byte enables are passed on to the Bus Controller/DMA Controller, which uses them for the Bytemask field of the outgoing P\_NCWR\_REQ packet(s).

For streaming DVMA writes, arbitrary byte enables are not allowed. Within a single PCI transaction, all data must be contiguous bytes. If any byte holes are detected, the PBM will set a status bit, and an interrupt will be generated if enabled. Meanwhile, the transaction continues as if the byte hole were not there, and the appropriate byte enables were on. This will cause incorrect data to be eventually be written to memory for these bytes. This only applies to a single continuous PCI transaction - gaps between the end address of one transaction and the start address of the next are allowed, and correctly handled by the streaming cache (although they may cause performance degradation).

The PBM also helps to enforce certain ordering constraints between consistent DVMA writes (cacheable or non-cacheable) and the following synchronization events:

- PIO reads of PCI registers.

- Interrupts.

- Other consistent DVMA writes (e.g. a descriptor update).

For PIO reads (to PCI space, not internal registers), the PBM for the targeted bus communicates with the DMA Controller to ensure that all of its previous consistent DVMA writes have completed before allowing the PIO to complete.

For PCI related interrupts, the MDU notifies the appropriate PBM when an interrupt is received. The PBM then notifies the MDU when all of its outstanding consistent DVMA writes have been flushed. The MDU will not generate the interrupt packet until the PBM has flushed data.

Descriptor updates are correctly handled by the strict ordering of all consistent DVMA accesses.

The only PCI bus function that is not handled by the PBM is the interrupt logic. This is contained in the MDU block.

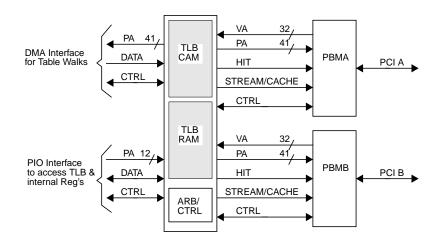

## 3.3.9 IOMMU

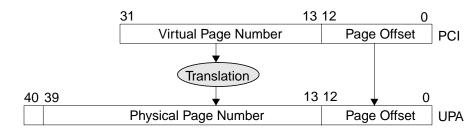

This block is used for PCI DVMA cycles. It maps 32-bit PCI Virtual Addresses to 41bit UPA Physical Addresses for both PBM blocks. There is a single 16-entry Translation Look-aside Buffer (TLB) to cache recently used translations. The TLB entries are replaced on an LRU basis, without regard to the bus of origin. The IOMMU can provide 2 levels of service when a PBM presents a virtual address for translation:

- First, the IOMMU examines the TLB to see if a translation for the virtual address is already available.

- If there is a miss in the TLB, the IOMMU block will perform a HW table-walk to get the translation if requested by the PBM (since the PBM also checks the streaming cache for a translation, this may not be necessary). The IOMMU does this by reading from the TSB table by issuing a DMA read to main memory. This is only a single-level table search, unlike previous Sun MMU models.

The IOMMU allows only a single translation to be in progress at a time. This includes the tablewalk portion of a translation, so if one PBM has requested a tablewalk, translation requests from the other PBM are held off until the tablewalk completes.

In the case of simultaneous translation requests by both PBM's, priority is given to PBM A.

## 3.3.10 Streaming Cache

Each Streaming Cache (STC, but sometimes referred to as a Streaming Buffer) is used to accelerate DVMA traffic to/from its associated PCI bus. It contains a pool of 16 64-byte entries. These entries are tagged by virtual page number, and are managed as a fully-associative cache. Only one entry will be valid for any given virtual page. Entries are assigned as needed by the STC logic. An LRU algorithm is used to assign new pages to entries when all of the entries are valid. All 16 entries are available for either read or write streams, although at a given time, each entry is only valid for a single direction.

For DVMA writes, the STC will buffer up data in an entry until a 64 byte has been reached. The STC will then flush the completed line into a flush buffer. As soon as the internal busses are available, data in the flush buffer is sent to the UPA block. The flush is guaranteed to occur if the last word of the line has been written - there is no possibility of a completed dirty line being left in the streaming cache for an indeterminate amount of time. For DVMA reads, the STC will often be able to prefetch a new 64 byte line into a prefetch buffer, and then copy it into the correct streaming cache entry before it is needed by the requesting device. This prefetch is initiated whenever the Memory Read Line or Memory Read Line Multiple commands are used on the PCI bus, as signalled to the STC by the PBM, and there is

not already an outstanding prefetch request waiting for data. A prefetch is also initiated if it has not already been issued and the last word of a line is read. Prefetches are never issued when a page boundary is reached.

The STC expects that the DVMA device is accessing data in sequential and increasing order, without any byte holes. If the actual device access pattern is different, the STC, in concert with the PBM, will maintain data correctness but the performance gains will not be as high. One exception to data correctness is if a device generates byte-holes within a single write transaction. When this happens, the byte enables in the byte hole are treated as if they were on (thus possibly causing data corruption), and a Streaming Byte Hole Interrupt is signalled (if enabled).

Data which is stored in the STC does **not** participate in the UPA cache coherence protocol. The STC implements a flush command to allow system software to explicitly remove virtual pages from the STC when a DVMA transfer is done or when an IOMMU demap operation occurs. In order to ensure that the STC flush data has reached UPA memory, a special synchronization register is provided.

The two streaming caches in U2P do not communicate with each other. There is no snooping done to determine if the same virtual page is in use in both caches. It is up to software to ensure that either no devices from separate busses access the same virtual page in streaming mode, or, if they do, that they do not access the same 64-byte lines within the page. (Note that the same warning applies to having multiple virtual addresses in either or both streaming caches map to the same physical address.)

#### 3.3.11 MDU

The Mondo Dispatch Unit is U2P's vehicle for dispatching Interrupt packets to an Interrupt Handler on the UPA bus (primarily a CPU). The MDU will generate a special type of UPA packet (a Mondo Vector, P\_INT\_REQ). The MDU block accepts external interrupt requests from PCI or UPA devices (encoded onto a 6-bit INT\_NUM bus) as well as internal U2P interrupt sources and dispatches Interrupt packets to the UPA. The contents and target of the interrupt packet are controlled through the Interrupt Number Registers (INR) within the MDU. Each INR is 16 bits, with 5 of these bits indicating the MID of the target CPU. For simplicity, no data other than the interrupt number (INO) is sent in the 64-byte interrupt packet from U2P (unused bits are all sent as 0s).

There are 38 external interrupt sources that can have their requests serviced through the MDU. In order to conserve pins on U2P, these are handled by an external interrupt concentrator (e.g. the RIC chip). The interrupt concentrator sends interrupt requests to the U2P by encoding them onto a 6 bit interface. Once an interrupt is received from the external concentrator, it is put into one of 2 groups, based on the least significant bit of the target MID programmed into the corresponding INR (U2P is optimized for a system with 2 CPU's, but can be used in systems with up to 4 CPU's). Within each of these groups, the MDU performs a priority arbitration to determine which interrupt to send.

Before any PCI related interrupt packet is sent to the UPA, the MDU checks with the appropriate PBM block to see if it has any posted consistent DMA write data. If so, the MDU waits until the PBM indicates that the write data has been sent to the UPA block.

The Mondo Interrupt packet is then sent to the target CPU using the same UPA queue that is used for DMA writes. The Mondo packet can be either ACKed or NACKed by the UPA. If the packet is NACKed (rejected), the CPU is already busy servicing another Mondo. In this case, the MDU will resubmit the packet at a later time based on a free-running retry interval counter. (This retry interval is programmable.) In the meantime, Mondo packets can still be sent to other CPU's (as long as they differ in the LSB of the MID). To simplify the design, U2P can only have one Mondo vector outstanding (i.e. waiting for ACK or NACK) at any time.

### 3.3.12 Timer / Counters

There are two identical, independent 29-bit timer/counters in U2P. Each can provide either periodic interrupts or single-event interrupts to a selected processor. The interrupt is delivered to the target CPU using a Mondo vector, and each counter can target a different CPU. The counters are driven by the TMR\_CLK input, which is nominally at 10MHz. This clock is scaled down by a factor of 10 first, so the counters will typically increment once a microsecond, which allows periodic interrupt intervals of up to 536 seconds.

Each counter has an associated Limit Register, and a Periodic enable bit. When a counter reaches its limit value, an interrupt is generated (if enabled). If the Periodic bit is set, the count is reset to 0, otherwise it is left alone (the count is also reset to 0 whenever the Limit Register is written). To obtain a periodic interrupt every 'N' microseconds, the limit value should be set to 'N-1'.

#### 3.3.13 Reset

A synchronous reset is implemented in U2P. UPA\_RST\_L is the source of this reset and it is distributed to 3 internal clock domains and to the PCI bus.

To the UPA domain UPA\_RST\_L is registered on input and distributed to the various modules within the domain. Each of those modules further registers the reset before distribution to the destination flops. This gives a 3 cycle delay between the external reset pin and the time the internal logic is reset.

In the PSYCLK domain UPA\_RST\_L will occur at the destination flops either 1 or 2 clocks from the time of it's assertion. This is due to the fact that UPA\_RST\_L is based in the UPACLK time domain and is thus asynchronous to the PSYCLK domain. The de-assertion of UPA\_CLK\_L will occur at the destination flops a maximum of 3 PSYCLK cycles later. This is accomplished by sending UPA\_RST\_L through a dual rank synchronizer which feeds an AND function, and at the same time by-passing the synchronizer with UPA\_RST\_L to feed the other term of the AND function.

To the PCI bus, UPA\_RST\_L is asserted asynchronously and de-asserted synchronously. This is accomplished using the dual rank synchronizer and AND function described in the previous paragraph. The PCI signal PCI\_RST\_ will be asserted in the same cycle as UPA\_RST\_L and will be de-asserted 2 PSYCLK cycles after UPA\_RST\_L.

### 3.3.14 Testability

U2P has a JTAG (IEEE 1149.1) compliant TAP controller and boundary scan. In addition, all internal functional flip-flops are scannable. Several other scan based test and debug features are implemented as well, including Built-In Self-Test (BIST) circuitry for internal memories that are not directly accessible via PIO accesses. The Design-for-Testability (DFT) features of U2P are further documented in Chapter 12.

3-14 UPA to PCI Interface (U2P) User's Manual • May 1997

#### CHAPTER **4**

## **DMA/PIO Transactions Flow**

This chapter describes the flow of DMA and PIO transactions through U2P's UPA (Unified/UltraSPARC Port Architecture) bus interface. The major generic blocks involved in any DMA transaction are the Bus Controller, DMA controller, and UPA bus interface (and the Merge Buffer for coherent DMA writes of less than 64 Bytes). The major blocks involved in any PIO transaction are the Bus Controller, PIO Decoder, and the UPA bus interface.

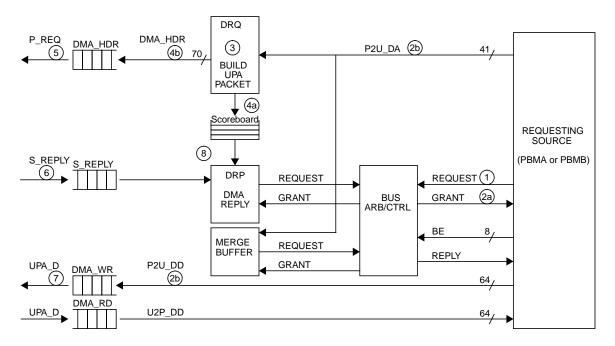

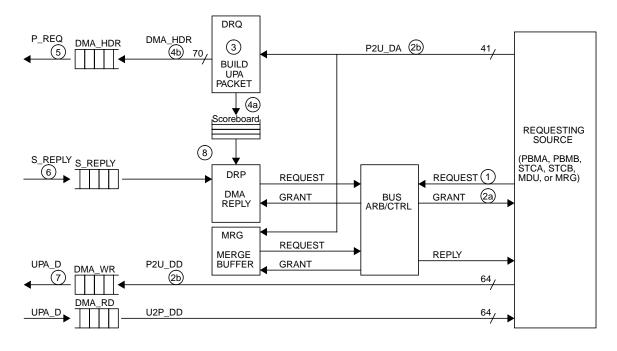

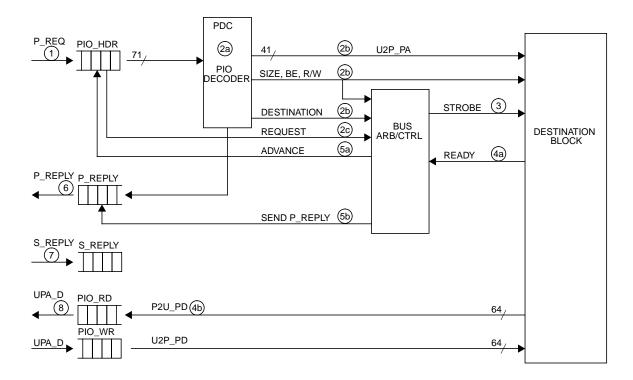

Figure 4-1 shows a top level block diagram of the interconnection between the blocks responsible for DMA and PIO transactions control.

**Note** – This chapter assumes that the reader is familiar with the basics of the UPA (Unified/UltraSPARC Port Architecture) Interconnect. Please refer to "UPA Interconnect Architecture" Release 2.0, Document Part Number 960-1156-01.

# 4.1 Block Diagram

<sup>4-2</sup> UPA to PCI Interface (U2P) User's Manual • May 1997

- UPA Block: This block is U2P's interface to the UPA bus. It is composed of three major sub-blocks:

- a. UPA Master/Slave: This block is so called because it simultaneously operates in two different modes, Master and Slave. In Master mode, it arbitrates for the UPA bus and puts a UPA request on the UPA address bus after it wins arbitration. In slave mode, it listens to the UPA address bus waiting for a transaction.

- b. UPA Reply/Data: This block contains all data FIFO's needed to buffer DMA and PIO data. It also handles P\_REPLY and S\_REPLY packets.

- c. ECC: This block generates ECC on data sent from U2P to the UPA bus, and checks ECC on data received from the UPA bus.

- DMA Controller: This block is responsible for building DMA transaction packets sent to the UPA bus and for keeping track of them. It is composed of three major sub-blocks:

- a. DMA Request: DMA requests from U2P's internal blocks are sent to this block under control from the Bus Controller. The DMA Request block then builds the appropriate UPA transaction and inserts it in the DMA header FIFO in UPA Master/Slave. At the same time it sends all information related to the DMA transaction to the Scoreboard to be stored until the DMA transaction is completely serviced (i.e., DMA read data has been received, or DMA write data has been taken).

- b. DMA Reply: The UPA Reply/Data block forwards all DMA related S\_REPLY's to this block to be decoded. If the S\_REPLY is related to an outstanding DMA read, the DMA reply arbitrates for U2P's internal busses to deliver the DMA read data and removes the DMA request from the scoreboard. If the S\_REPLY is related to an outstanding DMA write, the DMA Reply just removes the DMA write request from the scoreboard. This block also drives the appropriate Ack and Nack signals to U2P's internal blocks based on the S\_REPLY type.

- c. Scoreboard: The scoreboard keeps a record of all outstanding DMA transactions to the UPA. It stores the following DMA related information:

- i. Transaction direction (Read/Write).

- ii. Cacheable bit to indicates transaction destination (memory vs. IO).

- iii. 16-bit Byte Mask.

- iv. ID of the block that initiated the DMA transaction.

- v. Special field (4 bits) that can be used by the block which initiated the DMA to store any type of information. The Streaming Cache, for example, stores an index number to its 16 buffers. This index number is returned to the streaming cache along with the DMA read data.

- vi. DMA address (used for DMA read error recording).

- PIO Decoder: The UPA Master/Slave passes UPA transactions to this block to be decoded. The PIO Decoder extracts from the UPA transaction the PIO address, destination, direction (read or write), byte mask, and transfer size. Outputs of this block are used by the Bus Controller to initiate the PIO access internally.

- Bus Controller: This block is in charge of concurrently coordinating DMA and PIO transactions inside U2P. It is composed of three major sub-blocks. The first one controls PIO transactions to all internal blocks. The second one is responsible for arbitration between internal blocks and for passing DMA requests to the DMA Controller. The third block communicates with the DMA Reply to deliver DMA read data to the requesting block.

- Merge Buffer: The merge buffer concept was introduced to eliminate the need for U2P to participate in the UPA cache coherence protocol. Its main function is to handle coherent DMA writes to main memory which are less than 64 Bytes. When the Bus Controller detects that the size of the write transaction is less than 64 Bytes it informs the merge buffer. The merge buffer fetches the addressed data block (64 Bytes) from the memory and merges the new data, then it writes the data block back into the memory.

U2P's internal blocks that issue DMA transactions destined for the UPA are called in this chapter *Requesting Sources or Blocks*. These sources include the PBM Modules (A & B), the Streaming Caches (A & B), the Merge Buffer, the Mondo Dispatch Unit (Interrupts are treated as DMA Writes), and the IOMMU. Blocks that can be accessed in slave mode (PIO) are called *Destination Blocks*. These blocks include, in addition to all requesting blocks, the UPA interface, the ECC block, the Timer block, the Scoreboard, and the Performance registers.

The acronyms below are used in the following sections:

- **DMA\_HDR**: A 70 bit DMA header which is basically the two cycles of a UPA transaction (side by side) without the parity bits.

- DMA\_HDR FIFO: DMA Header FIFO used to buffer UPA transactions until U2P wins the UPA bus arbitration.

- **DMA\_WR FIFO**: DMA Write Data FIFO.

- **DMA\_RD FIFO**: DMA Read Data FIFO.

- **P2U\_DD: PCI-**to-**UPA DMA Data** (DMA Write Data).

- U2P\_DD: UPA-to-PCI DMA Data (DMA Read Data).

- P2U\_DA: PCI-to-UPA DMA Address.

- PIO\_HDR: A 71 bit PIO header which is basically the two cycles of a UPA transaction received from the UPA bus (side by side) without the parity bits. Bit 71 is set if a parity error is detected in either of the two cycles.

- **PIO\_HDR FIFO**: PIO Header FIFO used to buffer UPA transactions forwarded to U2P from the SC.

- **PIO\_WR FIFO**: PIO Write Data FIFO.

- **PIO\_RD FIFO**: PIO Read Data FIFO.

- **U2P\_PD**: UPA-to-**PCI PIO D**ata (PIO Write Data).

- **P2U\_PD: PCI**-to-UPA **P**IO **D**ata (PIO Read Data).

- **U2P\_PA:** UPA-to-**PCI PIO A**ddress.

## 4.2 DMA Transaction Flow

This section describes the flow of a DMA request and reply through the DMA Controller. Refer to the figures provided below for each step described in the transaction flow (a step number is shown on the corresponding figure in a circle). The delta between the numbers in circles does not necessarily represent the actual number of clock cycles between steps.

The following discussion uses a simplified signal handshake protocol between the requesting DMA source and the Bus Controller. See Chapter 3 for more details.

Note – U2P uses class 0 only for all UPA transactions. Class 1 is not used.

## 4.2.1 DMA Write Transactions

#### 4.2.1.1 64 and 16 Byte DMA Writes to IO Space

Figure 4-2 DMA Write to IO space

Note – PBMA and PBMB are the only blocks which access IO space

PBMA is used as an example of a requesting block.

- 1. PBMA raises a request for a transfer. It indicates a write with the C bit clear (non-Cacheable). It also indicates the size which can be either 64 bytes or any arbitrary number of bytes less than or equal to 16. The Bus Controller begins arbitration.

- 2. Two things happen:

- a. PBMA wins arbitration.

- b. PBMA drives address and data busses. Data is entered into DMA\_WR FIFO.

- 3. The DMA header (DMA\_HDR) is formed in the DMA request block (DRQ). If the size is less than or equal to 16 bytes, the value on the Byte Enable (BE) lines from PBMA is used to determine the Bytemask field in the UPA transaction.

- 4. Two things happen:

- a. The Request is entered in the DMA Scoreboard.

- b. The Request is entered in the DMA header (DMA\_HDR) FIFO in the UPA interface.

- 5. P\_REQ packet is issued on the UPA bus. Table 4-1 shows the type of P\_REQ packets issued and the type of possible S\_REPLY.

| Source | Size (byte) | P_REQ       | S_REPLY |

|--------|-------------|-------------|---------|

| PBMA,  | 1 - 16      | P_NCWR_REQ  | S_WAS   |

| PBMB   | 64          | P_NCBWR_REQ | S_WAB   |

Table 4-1 Type of P\_REQ and S\_REPLY used for DMA write to IO space

6. S\_REPLY received from SC (System Controller). Table 4-2 briefly describes the action taken by U2P based on the type of S\_REPLY it receives.

| S_REPLY | Description                                                          |

|---------|----------------------------------------------------------------------|

| S_WAS   | Write Ack Single. U2P sources 16B of data from DMA_WR FIFO.          |

| S_WAB   | Write Ack Block. U2P sources 64B of data from DMA_WR FIFO.           |

| S_INAK  | Interrupt NACK. No data is transferred. U2P retries sometime later.  |

| S_RBU   | Read Block Ack. Unshared. U2P receives 64B of data into DMA_RD FIFO. |

| S_RBS   | Read Block Ack. Shared. U2P receives 64B of data into DMA_RD FIFO.   |

| S_SWB   | Write Block Ack. U2P receives 64B data into PIO_WR FIFO.             |

| S_SWS   | Write Single Ack. U2P receives 16B data into PIO_WR FIFO.            |

| S_SRB   | Read Block Ack. U2P sources 64B data from PIO_RD FIFO.               |

| S_SRS   | Read Single Ack. U2P sources 16B data from PIO_RD FIFO.              |

| S_ERR   | Error. No data is transferred.                                       |

| S_RTO   | Read Time Out. No data is transferred.                               |

Table 4-2

Type of S\_REPLY's U2P receives

- 7. U2P sources write data from DMA\_WR data FIFO to UPA data bus.

- 8. The DMA Reply Controller is informed of the reply. It removes the transaction from the scoreboard. U2P considers the DMA write transaction complete.

#### 4.2.1.2 64 Byte DMA Write to Memory

Figure 4-3 64 Bytes DMA Writes to Memory

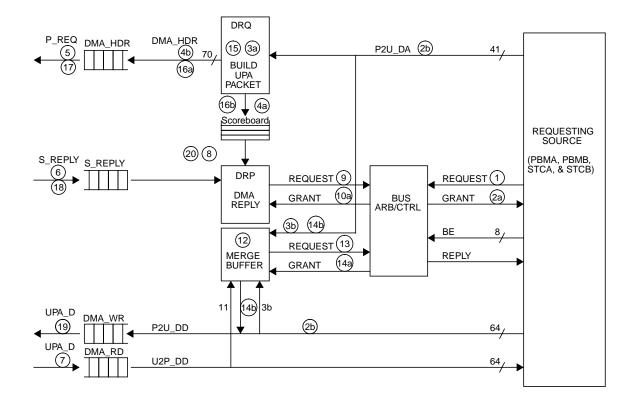

**Note** – PBMA, PBMB, STCA, STCB, and Merge Buffer (MRG) do 64 bytes DMA writes to memory. Interrupt transactions from MDU have identical flow.

PBMA is used as an example of a requesting block.

- 1. PBMA raises a request for a transfer. It indicates a 64B write with the C bit set (Cacheable). The Bus Controller begins arbitration.

- 2. Two things happen:

- a. PBMA wins arbitration.

- b. PBM drives address and data busses. Data is entered into DMA\_WR FIFO.

- 3. The UPA header is formed in the DRQ. 64 Byte writes bypass the merge buffer.

- 4. Two things happen:

- a. The Request is entered in the DMA Scoreboard.

- b. The Request is entered in the DMA\_HDR FIFO in the UPA interface.

- 5. P\_REQ packet is issued on the UPA bus. Table 4-3 shows the type of P\_REQ packets issued and the type of possible S\_REPLY.

Table 4-3 Type of P\_REQ and S\_REPLY used for 64 byte DMA writes to memory

| Source     | Size (byte) | P_REQ                  | S_REPLY        |

|------------|-------------|------------------------|----------------|

| PBMA, PBMB | 64          | P_WRI_REQ              | S_WAB          |

| STCA, STCB | 64          | P_WRI_REQ              | S_WAB          |

| MRG        | 64          | P_WRB_REQ              | S_WAB          |

| MDU        | 64          | P_INT_REQ <sup>1</sup> | S_WAB   S_INAK |

1. The flow of interrupt transaction is similar to 64 byte DMA write transactions, therefore it is shown here.

- 6. S\_REPLY received from SC (System Controller). See Table 4-2 for brief description of the action taken by U2P based on the type of S\_REPLY it receives. It is assumed here that U2P receives S\_WAB.

- 7. U2P sources write data from DMA\_WR data FIFO to UPA data bus.

- 8. The DMA Reply Controller is informed of the reply. It removes the transaction from the scoreboard. U2P considers the DMA write transaction complete.

#### 4.2.1.3 Less than 64 Byte DMA Write to Memory

Figure 4-4 Less than 64 Bytes DMA Writes to Memory

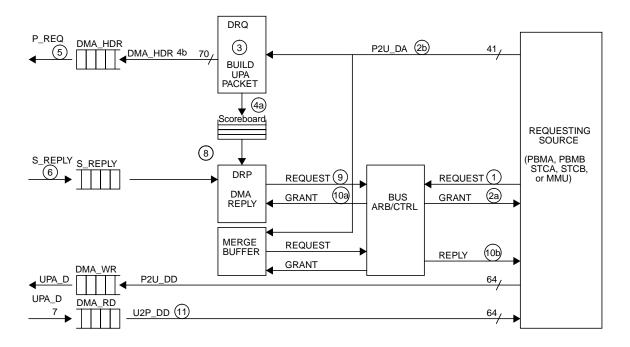

Note - Only PBMA, PBMB, STCA, & STCB issue less than 64 Bytes DMA write.

PBMA is used as an example of a requesting block.

- 1. PBMA raises a request for a transfer. It indicates a write with the C bit set (Cacheable). It also indicates that the size is less than 64 bytes. The size can be any arbitrary number of bytes less than or equal 63 bytes. The Bus Controller begins arbitration.

- 2. Two things happen:

- a. PBMA wins arbitration. DMA Requests from all other blocks are blocked.

- b. PBMA drives address and data busses (and byte enable lines).

- 3. Two things happen:

- a. The DMA header is formed in the DMA request block (DRQ). The DRQ recognizes that it is less than 64 Byte write to memory, so it forms a Read-To-Own transaction to read the whole block (64B) that contains the addressed data and forwards it to the merge buffer upon return.

Note - Read-To-Own (P\_RDO\_REQ) transaction is issued with DVP bit set.

- b. Write address and data are sent to the merge buffer along with the value on the Byte Enable (BE) lines.

- 4. Two things happen:

- a. The Request is entered in the DMA Scoreboard. The requestor ID is changed from PBMA to Merge buffer (MRG) before the transaction is entered in the scoreboard.

- b. The Request is entered in the DMA\_HDR FIFO in the UPA interface.

- 5. P\_REQ packet is issued on the UPA bus. Table 4-4 shows the type of P\_REQ packets issued and the type of possible S\_REPLY.

| Source     | Size (byte) | P_REQ     | S_REPLY               |

|------------|-------------|-----------|-----------------------|

| PBMA, PBMB | 1-63        | P_RDO_REQ | S_RBU   S_ERR  S_RTO  |

| STCA, STCB | 1-63        | P_RDO_REQ | S_RBU   S_ERR   S_RTO |

| MRG        | 64          | P_WRB_REQ | S_WAB                 |

Table 4-4 Type of P\_REQ and S\_REPLY used for less than 64 byte DMA writes

- 6. S\_REPLY received from SC (System Controller). See Table 4-2 for brief description of the action taken by U2P based on the type of S\_REPLY it receives. It is assumed here that U2P receives S\_RBU for P\_RDO\_REQ and S\_WAB for P\_WRB\_REQ.

- 7. U2P latches read data into DMA\_RD data FIFO.

- 8. The DMA Reply Controller is informed of the reply. It removes the transaction from the scoreboard.

- 9. The DMA Reply raises a request to return the data to the merge buffer (DMA Reply gets the requestor ID from the scoreboard). The bus controller begins arbitration.

- 10. Two things happen:

- a. The DMA Reply wins arbitration.

- b. Bus controller informs the Merge Buffer to receive the read data by asserting signal Reply (not shown).

- 11. Data is sourced from DMA\_RD data FIFO to merge buffer.

- 12. Data is merged inside the merge buffer (the byte enable value received earlier is used during the merge).