# DAQ

## NI PCI-1200 User Manual

Multifunctional I/O Device for PCI Bus Computers

#### **Worldwide Technical Support and Product Information**

ni.com

#### **National Instruments Corporate Headquarters**

11500 North Mopac Expressway Austin, Texas 78759-3504 USA Tel: 512 683 0100

#### **Worldwide Offices**

Australia 03 9879 5166, Austria 0662 45 79 90 0, Belgium 02 757 00 20, Brazil 011 3262 3599, Canada (Calgary) 403 274 9391, Canada (Montreal) 514 288 5722, Canada (Ottawa) 613 233 5949, Canada (Québec) 514 694 8521, Canada (Toronto) 905 785 0085, China (Shanghai) 021 6555 7838, China (ShenZhen) 0755 3904939, Czech Republic 02 2423 5774, Denmark 45 76 26 00, Finland 09 725 725 11, France 01 48 14 24 24, Germany 089 741 31 30, Greece 30 1 42 96 427, Hong Kong 2645 3186, India 91 80 4190000, Israel 03 6393737, Italy 02 413091, Japan 03 5472 2970, Korea 02 3451 3400, Malaysia 603 9596711, Mexico 001 800 010 0793, Netherlands 0348 433466, New Zealand 09 914 0488, Norway 32 27 73 00, Poland 0 22 3390 150, Portugal 351 210 311 210, Russia 095 238 7139, Singapore 6 2265886, Slovenia 386 3 425 4200, South Africa 11 805 8197, Spain 91 640 0085, Sweden 08 587 895 00, Switzerland 056 200 51 51, Taiwan 02 2528 7227, United Kingdom 01635 523545

For further support information, see the *Technical Support and Professional Services* appendix. To comment on the documentation, send email to techpubs@ni.com.

© 1996–2002 National Instruments Corporation. All rights reserved.

## **Important Information**

#### Warranty

The NI PCI-1200 is warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this document is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

Except as specified herein, National Instruments makes no warranties, express or implied, and specifically disclaims any warranty of merchantability or fitness for a particular purpose. Customer's right to recover damages caused by fault or negligence on the part of National Instruments shall be limited to the amount therefore paid by the customer. National Instruments will not be liable for Damages resulting from loss of data, profits, use of products, or incidental or consequential damages, even if advised of the possibility thereof. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

#### **Trademarks**

$CVI^{\text{IM}}$ ,  $DAQCard^{\text{IM}}$ ,  $LabVIEW^{\text{IM}}$ ,  $Measurement Studio^{\text{IM}}$ ,  $MITE^{\text{IM}}$ ,  $National Instruments^{\text{IM}}$ ,  $NI^{\text{IM}}$ ,  $ni.com^{\text{IM}}$ ,  $NI-DAQ^{\text{IM}}$ , and  $SCXI^{\text{IM}}$  are trademarks of National Instruments Corporation.

Product and company names mentioned herein are trademarks or trade names of their respective companies.

#### **Patents**

For patents covering National Instruments products, refer to the appropriate location: **Help»Patents** in your software, the patents.txt file on your CD, or ni.com/patents.

#### WARNING REGARDING USE OF NATIONAL INSTRUMENTS PRODUCTS

(1) NATIONAL INSTRUMENTS PRODUCTS ARE NOT DESIGNED WITH COMPONENTS AND TESTING FOR A LEVEL OF RELIABILITY SUITABLE FOR USE IN OR IN CONNECTION WITH SURGICAL IMPLANTS OR AS CRITICAL COMPONENTS IN ANY LIFE SUPPORT SYSTEMS WHOSE FAILURE TO PERFORM CAN REASONABLY BE EXPECTED TO CAUSE SIGNIFICANT INJURY TO A HUMAN.

(2) IN ANY APPLICATION, INCLUDING THE ABOVE, RELIABILITY OF OPERATION OF THE SOFTWARE PRODUCTS CAN BE IMPAIRED BY ADVERSE FACTORS, INCLUDING BUT NOT LIMITED TO FLUCTUATIONS IN ELECTRICAL POWER SUPPLY, COMPUTER HARDWARE MALFUNCTIONS, COMPUTER OPERATING SYSTEM SOFTWARE FITNESS, FITNESS OF COMPILERS AND DEVELOPMENT SOFTWARE USED TO DEVELOP AN APPLICATION, INSTALLATION ERRORS, SOFTWARE AND HARDWARE COMPATIBILITY PROBLEMS, MALFUNCTIONS OR FAILURES OF ELECTRONIC MONITORING OR CONTROL DEVICES, TRANSIENT FAILURES OF ELECTRONIC SYSTEMS (HARDWARE AND/OR SOFTWARE), UNANTICIPATED USES OR MISUSES, OR ERRORS ON THE PART OF THE USER OR APPLICATIONS DESIGNER (ADVERSE FACTORS SUCH AS THESE ARE HEREAFTER COLLECTIVELY TERMED "SYSTEM FAILURES"). ANY APPLICATION WHERE A SYSTEM FAILURE WOULD CREATE A RISK OF HARM TO PROPERTY OR PERSONS (INCLUDING THE RISK OF BODILY INJURY AND DEATH) SHOULD NOT BE RELIANT SOLELY UPON ONE FORM OF ELECTRONIC SYSTEM DUE TO THE RISK OF SYSTEM FAILURE. TO AVOID DAMAGE, INJURY, OR DEATH, THE USER OR APPLICATION DESIGNER MUST TAKE REASONABLY PRUDENT STEPS TO PROTECT AGAINST SYSTEM FAILURES, INCLUDING BUT NOT LIMITED TO BACK-UP OR SHUT DOWN MECHANISMS. BECAUSE EACH END-USER SYSTEM IS CUSTOMIZED AND DIFFERS FROM NATIONAL INSTRUMENTS' TESTING PLATFORMS AND BECAUSE A USER OR APPLICATION DESIGNER MAY USE NATIONAL INSTRUMENTS PRODUCTS IN COMBINATION WITH OTHER PRODUCTS IN A MANNER NOT EVALUATED OR CONTEMPLATED BY NATIONAL INSTRUMENTS, THE USER OR APPLICATION DESIGNER IS ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATING THE SUITABILITY OF NATIONAL INSTRUMENTS PRODUCTS WHENEVER NATIONAL INSTRUMENTS PRODUCTS ARE INCORPORATED IN A SYSTEM OR APPLICATION, INCLUDING, WITHOUT LIMITATION, THE APPROPRIATE DESIGN, PROCESS AND SAFETY LEVEL OF SUCH SYSTEM OR APPLICATION.

# **Contents**

| About  | This Manual                                      |     |

|--------|--------------------------------------------------|-----|

|        | Conventions Used in This Manual                  | ix  |

|        | National Instruments Documentation               |     |

|        | Related Documentation                            | xi  |

| Chapt  | er 1                                             |     |

| Introd | uction                                           |     |

|        | About the NI PCI-1200                            | 1-1 |

|        | What You Need to Get Started                     | 1-1 |

|        | Software Programming Choices                     | 1-2 |

|        | NI-DAQ                                           |     |

|        | National Instruments ADE Software                |     |

|        | Optional Equipment                               | 1-3 |

|        | Custom Cabling                                   |     |

|        | Unpacking                                        | 1-4 |

|        | Safety Information                               | 1-5 |

| Chapt  | er 2                                             |     |

| •      | ling and Configuring the NI PCI-1200             |     |

| motar  | Installing the Software                          | 2.1 |

|        | Installing the Hardware                          |     |

|        | Configuring the Device                           |     |

|        | Analog I/O Configuration                         |     |

|        | Analog Output Polarity                           |     |

|        | Analog Input Polarity                            |     |

|        | Analog Input Mode                                |     |

|        | RSE Input Mode (Eight Channels, Reset Condition) |     |

|        | NRSE Input Mode (Eight Channels)                 |     |

|        | DIFF Input Mode (Four Channels)                  |     |

# Chapter 3 Signal Connections

| I/O Connector                                        | 3-1   |

|------------------------------------------------------|-------|

| Signal Connection Descriptions                       |       |

| Analog Input Signal Connections                      |       |

| Types of Signal Sources                              |       |

| Floating Signal Sources                              |       |

| Ground-Referenced Signal Sources                     | 3-7   |

| Input Configurations                                 | 3-7   |

| Differential Connection Considerations               |       |

| (DIFF Configuration)                                 | 3-9   |

| Differential Connections for Grounded Signal Sources | 3-10  |

| Differential Connections for Floating Signal Sources |       |

| Single-Ended Connection Considerations               | 3-12  |

| Single-Ended Connections for Floating Signal Sources |       |

| (RSE Configuration)                                  | 3-13  |

| Single-Ended Connections for Grounded                |       |

| Signal Sources (NRSE Configuration)                  |       |

| Common-Mode Signal Rejection Considerations          |       |

| Analog Output Signal Connections                     |       |

| Digital I/O Signal Connections                       |       |

| Logical Inputs and Outputs                           |       |

| Port C Pin Connections                               |       |

| Power Connections                                    |       |

| DAQ and General Purpose Timing Signal Connections    |       |

| DAQ Timing Connections                               |       |

| General Purpose Timing Signal Connections            |       |

| Timing Specifications                                |       |

| Mode 1 Input Timing                                  |       |

| Mode 1 Output Timing                                 |       |

| Mode 2 Bidirectional Timing                          | 3-30  |

|                                                      |       |

| Chapter 4                                            |       |

| Theory of Operation                                  |       |

| Functional Overview                                  | 4 1   |

| PCI Interface Circuitry                              |       |

| Timing                                               |       |

|                                                      |       |

| Analog Input                                         |       |

| DAQ Operations                                       |       |

| Controlled Acquisition Mode                          |       |

| Freerun Acquisition Mode                             |       |

| Produit Acquistion Word                              | . 4-0 |

| Interval Scanning Acquisition Mode    | 4-8 |

|---------------------------------------|-----|

| Single-Channel Data Acquisition       | 4-9 |

| Multichannel Scanned Data Acquisition | 4-9 |

| DAQ Rates                             |     |

| Analog Output                         |     |

| Analog Output Circuitry               |     |

| DAC Timing                            |     |

| Digital I/O                           |     |

| Chapter 5                             |     |

| Calibration                           |     |

| Calibration at Higher Gains           | 5-2 |

| Calibration Equipment Requirements    | 5-2 |

| Using the Calibration Function        |     |

| -                                     |     |

|                                       |     |

# Appendix A Specifications

# Appendix B Technical Support and Professional Services

Glossary

Index

## **About This Manual**

This manual describes the electrical and mechanical aspects of the National Instruments PCI-1200 data acquisition (DAQ) device and contains information concerning its operation and programming.

The NI PCI-1200 is a low-cost multifunction analog, digital, and timing device. The NI PCI-1200 is a member of the National Instruments PCI Series of expansion devices for PCI bus computers. These devices are designed for high-performance data acquisition and control for applications in laboratory testing, production testing, and industrial process monitoring and control.

## **Conventions Used in This Manual**

The following conventions appear in this manual

Angle brackets that contain numbers separated by an ellipsis represent a

range of values associated with a bit or signal name—for example,

DBIO<3..0>.

This icon denotes a note, which alerts you to important information.

This icon denotes a caution, which advises you of precautions to take to avoid injury, data loss, or a system crash. When this symbol is marked on a product, see the *Safety Information* section of Chapter 1, *Introduction*, for

precautions to take.

**bold** Bold text denotes items that you must select or click on in the software,

such as menu items and dialog box options. Bold text also denotes

parameter names.

italic Italic text denotes variables, emphasis, a cross reference, or an introduction

to a key concept. This font also denotes text that is a placeholder for a word

or value that you must supply.

Macintosh Macintosh refers to all Macintosh computers with PCI bus, unless

otherwise noted.

monospace Text in this font denotes text or characters that you should enter from the

keyboard, sections of code, programming examples, and syntax examples.

This font is also used for the proper names of disk drives, paths, directories,

<>

programs, subprograms, subroutines, device names, functions, operations, variables, filenames and extensions, and code excerpts.

NI-DAQ

NI-DAQ is used in this manual to refer to the NI-DAQ software for PC or Macintosh computers, unless otherwise noted.

**SCXI**

SCXI stands for Signal Conditioning eXtensions for Instrumentation and is a National Instruments product line designed to perform front-end signal conditioning for National Instruments plug-in DAQ devices.

## **National Instruments Documentation**

The *PCI-1200 User Manual* is one piece of the documentation set for your DAQ system. You could have any of several types of manuals, depending on the hardware and software in your system. Use the manuals you have as follows:

- Getting Started with SCXI—If you are using SCXI, this is the first

manual you should read. It gives an overview of the SCXI system and

contains the most commonly needed information for the modules,

chassis, and software.

- SCXI Chassis Manual—If you are using SCXI, read this manual for maintenance information on the chassis and installation instructions.

- SCXI hardware user manuals—If you are using SCXI, read these

manuals next for detailed information about signal connections and

module configuration. They also explain in greater detail how the

module works and contain application hints.

- DAQ hardware user manuals—These manuals have detailed information about the DAQ hardware that plugs into or is connected to the computer. Use these manuals for hardware installation and configuration instructions, specification information about the DAQ hardware, and application hints.

- Software documentation—Examples of software documentation you may have are the LabVIEW or LabWindows/CVI documentation sets and the NI-DAQ documentation. After you set up the hardware system, use either the application software (LabVIEW or LabWindows/CVI) or the NI-DAQ documentation to help you write your application. If you have a large and complicated system, it is worthwhile to look through the software documentation before you configure the hardware.

- Accessory installation guides or manuals—If you are using accessory products, read the terminal block and cable assembly installation

guides and accessory user manuals. They explain how to physically connect the relevant pieces of the system. Consult these guides when making connections.

## **Related Documentation**

The following documents contain information that you may find helpful:

- NI Developer Zone tutorial, Field Wiring and Noise Considerations for Analog Signals, located at ni.com/zone

- PCI Local Bus Specification, Revision 2.2, available at pcisig.com

- The technical reference manual for the computer

Introduction

1

This chapter describes the NI PCI-1200, lists what you need to get started, software programming choices, and optional equipment, and explains how to build custom cables and unpack the NI PCI-1200.

## **About the NI PCI-1200**

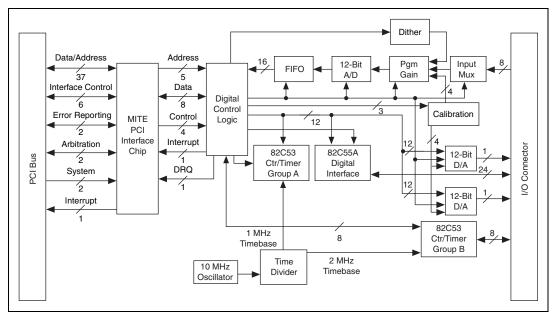

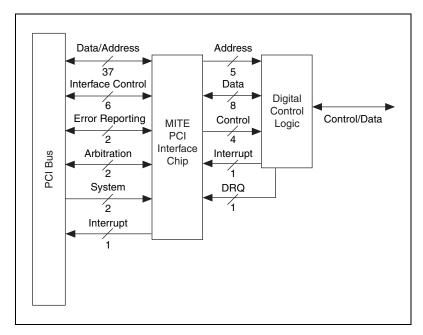

Thank you for purchasing the NI PCI-1200, a low-cost, high-performance multifunction analog, digital, and timing device for PCI bus computers. The NI PCI-1200 has eight analog input (AI) channels that you can configure as eight single-ended or four differential inputs, a 12-bit successive-approximation A/D converter (ADC), two 12-bit D/A converters (DACs) with voltage outputs, 24 lines of TTL-compatible digital I/O (DIO), and three 16-bit counter/timers for timing I/O (TIO).

Detailed NI PCI-1200 specifications are in Appendix A, Specifications.

## What You Need to Get Started

| То | et up and use your NI PCI-1200, you need the following items: |  |  |  |  |

|----|---------------------------------------------------------------|--|--|--|--|

|    | A computer                                                    |  |  |  |  |

|    | NI PCI-1200 device                                            |  |  |  |  |

|    | NI PCI-1200 User Manual                                       |  |  |  |  |

|    | One of the following software packages and documentation:     |  |  |  |  |

|    | <ul> <li>LabVIEW for Macintosh or Windows</li> </ul>          |  |  |  |  |

|    | <ul> <li>Measurement Studio for Windows</li> </ul>            |  |  |  |  |

|    | <ul> <li>NI-DAQ for Macintosh or Windows</li> </ul>           |  |  |  |  |

## **Software Programming Choices**

When programming National Instruments DAQ hardware, you can use an NI application development environment (ADE) or other ADEs. In either case, you use NI-DAQ.

#### NI-DAQ

NI-DAQ, which ships with the NI PCI-1200, has an extensive library of functions that you can call from the ADE. These functions allow you to use all the features of the NI PCI-1200.

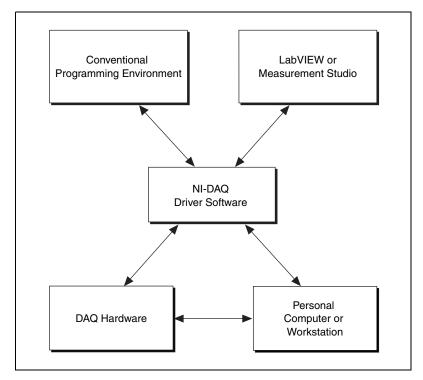

NI-DAQ carries out many of the complex interactions, such as programming interrupts, between the computer and the DAQ hardware. NI-DAQ maintains a consistent software interface among its different versions so that you can change platforms with minimal modifications to the code. Whether you are using LabVIEW, Measurement Studio, or other ADEs, your application uses NI-DAQ, as illustrated in Figure 1-1.

Figure 1-1. The Relationship Between the Programming Environment, NI-DAQ, and the Hardware

To download a free copy of the most recent version of NI-DAQ, click **Download Software** at ni.com.

#### **National Instruments ADE Software**

LabVIEW features interactive graphics, a state-of-the-art interface, and a powerful graphical programming language. The LabVIEW Data Acquisition VI Library, a series of virtual instruments for using LabVIEW with National Instruments DAQ hardware, is included with LabVIEW.

Measurement Studio, which includes LabWindows/CVI, tools for Visual C++, and tools for Visual Basic, is a development suite that allows you to use ANSI C, Visual C++, and Visual Basic to design the test and measurement software. For C developers, Measurement Studio includes LabWindows/CVI, a fully integrated ANSI C application development environment that features interactive graphics and the LabWindows/CVI Data Acquisition and Easy I/O libraries. For Visual Basic developers, Measurement Studio features a set of ActiveX controls for using National Instruments DAQ hardware. These ActiveX controls provide a high-level programming interface for building virtual instruments. For Visual C++ developers, Measurement Studio offers a set of Visual C++ classes and tools to integrate those classes into Visual C++ applications. The libraries, ActiveX controls, and classes are available with Measurement Studio and NI-DAQ.

Using LabVIEW or Measurement Studio greatly reduces the development time for your data acquisition and control application.

## **Optional Equipment**

NI offers a variety of products to use with the NI PCI-1200 device, including cables, connector blocks, and other accessories, as follows:

- Shielded cables and cable assemblies

- Connector blocks, RTSI bus cables, 50-shielded and 68-pin screw terminals

- SCXI modules and accessories for isolating, amplifying, exciting, and multiplexing signals for relays and analog output. With SCXI you can condition and acquire up to 3,072 channels. To use the NI PCI-1200 with SCXI you need the SCXI-1341 adapter.

- Low-channel-count signal conditioning modules, devices, and accessories, including conditioning for strain gauges and resistance

temperature detectors (RTDs), simultaneous sample and hold, and relays

For more information about optional equipment available from NI, refer to ni.com/catalog.

## **Custom Cabling**

NI offers cables and accessories for you to prototype your application or to use if you frequently change device interconnections.

If you want to develop your own cable, however, the following guidelines may be useful:

- For the AI signals, shielded twisted-pair wires for each AI pair yield the best results, assuming that you use differential inputs. Tie the shield for each signal pair to the ground reference at the source.

- You should route the analog lines separately from the digital lines.

- When using a cable shield, use separate shields for the analog and digital halves of the cable. Failure to do so results in noise coupling into the analog signals from transient digital signals.

The mating connector for the NI PCI-1200 is a 50-position, polarized, ribbon socket connector with strain relief. NI uses a polarized (keyed) connector to prevent inadvertent upside-down connection to the NI PCI-1200.

## **Unpacking**

The NI PCI-1200 is shipped in an antistatic package to prevent electrostatic damage to the device. Electrostatic discharge (ESD) can damage several components on the device. To avoid such damage in handling the device, take the following precautions:

**Caution** Never touch the exposed pins of connectors.

- Ground yourself using a grounding strap or by holding a grounded object.

- Touch the antistatic package to a metal part of your computer chassis before removing the device from the package.

Remove the device from the package and inspect the device for loose components or any other sign of damage. Notify NI if the device appears damaged in any way. Do *not* install a damaged device into your computer.

Store the NI PCI-1200 in the antistatic envelope when not in use.

## **Safety Information**

The following section contains important safety information that you *must* follow during installation and use of the product.

Do *not* operate the product in a manner not specified in this document. Misuse of the product can result in a hazard. You can compromise the safety protection built into the product if the product is damaged in any way. If the product is damaged, return it to NI for repair.

If the product is rated for use with hazardous voltages (>30  $V_{rms}$ , 42.4  $V_{pk}$ , or 60  $V_{dc}$ ), you may need to connect a safety earth-ground wire according to the installation instructions. Refer to Appendix A, *Specifications*, for maximum voltage ratings.

Do *not* substitute parts or modify the product. Use the product only with the chassis, modules, accessories, and cables specified in the installation instructions. You *must* have all covers and filler panels installed during operation of the product.

Do *not* operate the product in an explosive atmosphere or where there may be flammable gases or fumes. Operate the product only at or below the pollution degree stated in Appendix A, *Specifications*. Pollution is foreign matter in a solid, liquid, or gaseous state that can produce a reduction of dielectric strength or surface resistivity. The following is a description of pollution degrees:

- Pollution degree 1 means no pollution or only dry, non conductive pollution occurs. The pollution has no influence.

- Pollution degree 2 means that only non conductive pollution occurs in most cases. Occasionally, however, a temporary conductivity caused by condensation must be expected.

- Pollution degree 3 means that conductive pollution occurs, or dry, non conductive pollution occurs, which becomes conductive due to condensation.

Clean the product with a soft nonmetallic brush. The product *must* be completely dry and free from contaminants before returning it to service.

You *must* insulate signal connections for the maximum voltage for which the product is rated. Do *not* exceed the maximum ratings for the product. Remove power from signal lines before connection to or disconnection from the product.

Operate this product only at or below the installation category stated in Appendix A, *Specifications*.

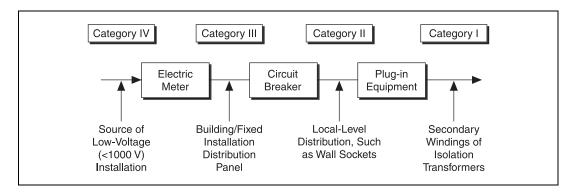

The following is a description of installation categories:

Installation Category I is for measurements performed on circuits not directly connected to MAINS<sup>1</sup>. This category is a signal level such as voltages on a printed wire device (PWB) on the secondary of an isolation transformer.

Examples of Installation Category I are measurements on circuits not derived from MAINS and specially protected (internal) MAINS-derived circuits.

Installation Category II is for measurements performed on circuits directly connected to the low-voltage installation. This category refers to local-level distribution such as that provided by a standard wall outlet.

Examples of Installation Category II are measurements on household appliances, portable tools, and similar equipment.

- Installation Category III is for measurements performed in the building installation. This category is a distribution level referring to hardwired equipment that does not rely on standard building insulation.

- Examples of Installation Category III include measurements on distribution circuits and circuit breakers. Other examples of Installation Category III are wiring including cables, bus-bars, junction boxes, switches, socket outlets in the building/fixed installation, and equipment for industrial use, such as stationary motors with a permanent connection to the building/fixed installation.

- Installation Category IV is for measurements performed at the source of the low-voltage (<1,000 V) installation.

- Examples of Installation Category IV are electric meters, and measurements on primary overcurrent protection devices and ripple-control units.

<sup>&</sup>lt;sup>1</sup> MAINS is defined as the electricity supply system to which the equipment concerned is designed to be connected either for powering the equipment or for measurement purposes.

#### Below is a diagram of a sample installation.

# Installing and Configuring the NI PCI-1200

This chapter describes how to install and configure the NI PCI-1200.

## Installing the Software

If you are using NI-DAQ or NI application software, refer to the installation instructions in your software documentation to install and configure your software.

Complete the following steps to install the software before installing the NI PCI-1200.

- Install the application development environment (ADE), such as LabVIEW or Measurement Studio, according to the instructions on the CD and the release notes.

- 2. Install NI-DAQ according to the instructions on the CD and the *DAQ Quick Start Guide* included with the NI PCI-1200.

**Note** It is important to install NI-DAQ before installing the NI PCI-1200 to ensure that the NI PCI-1200 is properly detected.

## Installing the Hardware

The following are general installation instructions. Consult the computer or chassis user manual or technical reference manual for specific instructions and warnings about new devices.

- 1. Power off and unplug your computer.

- 2. Remove the top cover or access port to the I/O channel.

- 3. Remove the expansion slot cover on the back panel of the computer.

- 4. Ground yourself using a grounding strap or by holding a grounded object. Follow the ESD protection precautions described in the *Unpacking* section of Chapter 1, *Introduction*.

- 5. Insert the NI PCI-1200 in an unused PCI system slot. The fit may be tight, but do *not* force the device into place.

- Screw the NI PCI-1200 mounting bracket to the back panel rail of the computer or use the slot side tabs, if available, to secure the NI PCI-1200 in place.

- 7. Replace the top cover on the computer. Visually verify the installation. Make sure the device is not touching other devices or components and is fully inserted into the slot.

- 8. Plug in and power on the computer.

The NI PCI-1200 device is installed.

## **Configuring the Device**

The NI PCI-1200 is completely software configurable. The NI PCI-1200 is fully compliant with the *PCI Local Bus Specification*, *Revision 2.2*. Therefore, all device resources are automatically allocated by the system. For the NI PCI-1200, this allocation includes the base memory address and interrupt level. You do not need to perform any configuration steps after the system powers up.

## **Analog I/O Configuration**

Upon power-up or after a software reset, the NI PCI-1200 is set to the following configuration:

- Referenced single-ended input mode

- ±5 V AI range (bipolar)

- ±5 V analog output (AO) range (bipolar)

Table 2-1 lists all the available analog I/O configurations for the NI PCI-1200 and shows the configuration in reset condition.

| Parameter                  | Configuration                                        |

|----------------------------|------------------------------------------------------|

| Analog Output CH0 Polarity | Bipolar—±5 V (reset condition)<br>Unipolar—0 to 10 V |

| Analog Output CH1 Polarity | Bipolar—±5 V (reset condition)<br>Unipolar—0 to 10 V |

Table 2-1. Analog I/O Settings

Chapter 2

ParameterConfigurationAnalog Input PolarityBipolar—±5 V (reset condition)<br/>Unipolar—0 to 10 VAnalog Input ModeReferenced single-ended (RSE) (reset condition)<br/>Nonreferenced single-ended (NRSE)<br/>Differential (DIFF)

**Table 2-1.** Analog I/O Settings (Continued)

Both the AI and AO circuitries are software configurable. Refer to the software documentation for more information on changing these settings.

## **Analog Output Polarity**

The NI PCI-1200 has two channels of AO voltage at the I/O connector. You can configure each AO output channel for either unipolar or bipolar output. A unipolar configuration has a range of 0 to 10 V at the analog output. A bipolar configuration has a range of –5 to +5 V at the analog output. In addition, you can select the coding scheme for each DAC as either two's complement or straight binary.

If you select a bipolar range for a DAC, the two's complement coding is recommended. In this mode, data values written to the AO channel range from F800 hex (–2,048 decimal) to 7FF hex (2,047 decimal). If you select a unipolar range for a DAC, the straight binary coding is recommended. In this mode, data values written to the AO channel range from 0 to FFF hex (4,095 decimal).

## **Analog Input Polarity**

You can select the analog input on the NI PCI-1200 for either a unipolar range (0 to 10 V) or a bipolar range (–5 to +5 V). In addition, you can select the coding scheme for analog input as either two's complement or straight binary. If you select a bipolar range, the two's complement coding is recommended. In this mode, –5 V input corresponds to F800 hex (–2,048 decimal) and +5 V corresponds to 7FF hex (2,047 decimal). If you select a unipolar mode, the straight binary coding is recommended. In this mode, 0 V input corresponds to 0 hex, and +10 V corresponds to FFF hex (4,095 decimal).

## **Analog Input Mode**

The NI PCI-1200 has three input modes—referenced single-ended (RSE) input mode, non-referenced single-ended (NRSE) input mode, and differential (DIFF) input mode. The single-ended input configurations use eight channels. The DIFF input configuration uses four channels. Table 2-2 describes these configurations.

| Analog Input<br>Modes | Description                                                                                                                                                                                                                                                             |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSE                   | RSE mode provides eight single-ended inputs with the negative input of the instrumentation amplifier referenced to analog ground (reset condition).                                                                                                                     |

| NRSE                  | NRSE mode provides eight single-ended inputs with the negative input of the instrumentation amplifier tied to AISENSE/AIGND and not connected to ground.                                                                                                                |

| DIFF                  | DIFF mode provides four differential inputs with the positive input of the instrumentation amplifier tied to channels 0, 2, 4, or 6 and the negative input tied to channels 1, 3, 5, or 7, respectively, thus choosing channel pairs (0, 1), (2, 3), (4, 5), or (6, 7). |

Table 2-2. Analog Input Modes for the NI PCI-1200

While reading the following sections, you may find it helpful to refer to the *Analog Input Signal Connections* section of Chapter 3, *Signal Connections*, which contains diagrams showing the signal paths for the three configurations.

#### **RSE Input Mode (Eight Channels, Reset Condition)**

RSE input means that all input signals are referenced to a common ground point that is also tied to the NI PCI-1200 AI ground. The differential amplifier negative input is tied to analog ground. RSE mode is useful for measuring floating signal sources. With this input configuration, the NI PCI-1200 can monitor eight AI channels.

Considerations for using RSE mode are discussed in Chapter 3, *Signal Connections*. Notice that in this mode, the signal return path is analog ground at the connector through the AISENSE/AIGND pin.

#### **NRSE Input Mode (Eight Channels)**

NRSE input means that all input signals are referenced to the same common-mode voltage, which floats with respect to the NI PCI-1200 analog ground. This common-mode voltage is subsequently subtracted by the input instrumentation amplifier. NRSE mode is useful for measuring ground-referenced signal sources.

Considerations for using NRSE mode are discussed in Chapter 3, *Signal Connections*. Notice that in this mode, the signal return path is through the negative terminal of the amplifier at the connector through the AISENSE/AIGND pin.

#### **DIFF Input Mode (Four Channels)**

DIFF input means that each input signal has its own reference, and the difference between each signal and its reference is measured. The signal and its reference are each assigned an input channel. With this input configuration, the NI PCI-1200 can monitor four differential AI signals.

Considerations for using DIFF mode are discussed in Chapter 3, *Signal Connections*. Notice that the signal return path is through the negative terminal of the amplifier and through channel 1, 3, 5, or 7, depending on which channel pair you select.

# **Signal Connections**

This chapter describes how to make input and output signal connections to the NI PCI-1200 through the device I/O connector and details the I/O timing specifications.

The I/O connector for the NI PCI-1200 has 50 pins that you can connect to 50-pin accessories.

## I/O Connector

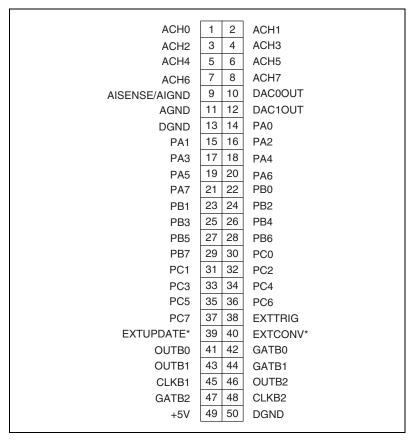

Figure 3-1 shows the pin assignments for the NI PCI-1200 I/O connector.

**Caution** You should not externally drive DIO lines while the computer is powered off; doing so can damage the computer. NI is *not* liable for any damage resulting from signal connections that exceed these maximum ratings. Connections, including connecting power signals to ground and vice versa, that exceed any of the maximum ratings of input or output signals on the NI PCI-1200 may damage the NI PCI-1200 and the computer.

Figure 3-1. NI PCI-1200 I/O Connector Pin Assignments

## **Signal Connection Descriptions**

The following table describes the connector pins on the NI PCI-1200 I/O connector by pin number and gives the signal name and description of each signal connector pin.

Table 3-1. Signal Descriptions for NI PCI-1200 I/O Connector Pins

| Pin | Signal Name   | Direction | Reference | Description                                                                                        |

|-----|---------------|-----------|-----------|----------------------------------------------------------------------------------------------------|

| 1–8 | ACH<70>       | AI        | AGND      | Analog Channel 7 through 0—AI channels 0 through 7.                                                |

| 9   | AISENSE/AIGND | I/O       | AGND      | Analog Input Sense/Analog Input<br>Ground—Connected to AGND in RSE<br>mode, AI sense in NRSE mode. |

Table 3-1. Signal Descriptions for NI PCI-1200 I/O Connector Pins (Continued)

| Pin    | Signal Name | Direction | Reference | Description                                                                                                                                |

|--------|-------------|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 10     | DAC0OUT     | AO        | AGND      | Digital-to-Analog Converter 0 Output—Voltage output signal for AO channel 0.                                                               |

| 11     | AGND        | N/A       | N/A       | Analog Ground—AO ground reference for AO voltages. Bias current return point for differential measurements.                                |

| 12     | DAC1OUT     | AO        | AGND      | Digital-to-Analog Converter 1 Output—Voltage output signal for AO channel 1.                                                               |

| 13, 50 | DGND        | N/A       | N/A       | Digital Ground—Voltage ground reference for the digital signals and the +5 V supply.                                                       |

| 14–21  | PA<70>      | DIO       | DGND      | Port A 7 through 0—Bidirectional data lines for port A. PA7 is the most significant bit (MSB), and PA0 is the least significant bit (LSB). |

| 22–29  | PB<70>      | DIO       | DGND      | Port B 7 through 0—Bidirectional data lines for port B. PB7 is the MSB, and PB0 is the LSB.                                                |

| 30–37  | PC<70>      | DIO       | DGND      | Port C 7 through 0—Bidirectional data lines for port C. PC7 is the MSB, and PC0 is the LSB.                                                |

| 38     | EXTTRIG     | DI        | DGND      | External Trigger—External control signal to trigger a DAQ operation.                                                                       |

| 39     | EXTUPDATE*  | DI        | DGND      | External Update—External control signal to update DAC outputs.                                                                             |

| 40     | EXTCONV*    | DIO       | DGND      | External Convert—External control signal to time A/D conversions (DI) and drive SCANCLK when you use SCXI (DO).                            |

| 41     | OUTB0       | DO        | DGND      | Output B0—Digital output signal of counter B0.                                                                                             |

| 42     | GATB0       | DI        | DGND      | Gate B0—External control signal for gating counter B0.                                                                                     |

| Pin                                        | Signal Name                                                     | Direction | Reference | Description                                                                                                  |  |

|--------------------------------------------|-----------------------------------------------------------------|-----------|-----------|--------------------------------------------------------------------------------------------------------------|--|

| 43                                         | OUTB1                                                           | DIO       | DGND      | Output B1—Digital output signal of counter B1 (DO). External control signal for timing a scan interval (DI). |  |

| 44                                         | GATB1                                                           | DI        | DGND      | Gate B1—External control signal for gating counter B1.                                                       |  |

| 45                                         | CLKB1                                                           | DI        | DGND      | Clock B1—External control clock signal for counter B1.                                                       |  |

| 46                                         | OUTB2                                                           | DO        | DGND      | Counter B2—Digital output signal of counter B2.                                                              |  |

| 47                                         | GATB2                                                           | DI        | DGND      | Gate B2—External control signal for gating counter B2.                                                       |  |

| 48                                         | CLKB2                                                           | DI        | DGND      | Clock B2—External control clock signal for counter B2.                                                       |  |

| 49                                         | +5V                                                             | DO        | DGND      | +5 Volts—This pin is fused for up to 1 A of +4.65 to +5.25 V.                                                |  |

| * Indicates that the signal is active low. |                                                                 |           |           |                                                                                                              |  |

| DI = Digi                                  | DI = Digital Input $DO = Digital Output$ $N/A = Not Applicable$ |           |           |                                                                                                              |  |

**Table 3-1.** Signal Descriptions for NI PCI-1200 I/O Connector Pins (Continued)

The connector pins are grouped into AI signal pins, AO signal pins, DIO signal pins, TIO signal pins, and power connections. The following sections describe the signal connection guidelines for each of these groups.

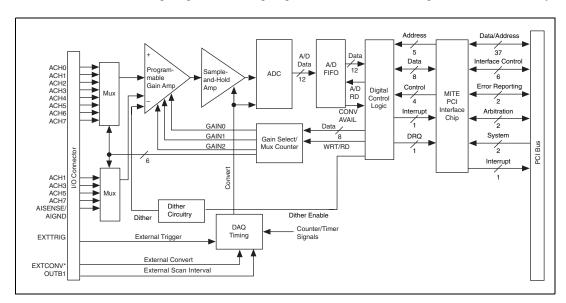

## **Analog Input Signal Connections**

Pins 1 through 8 are AI signal pins for the 12-bit ADC. Pin 9, AISENSE/AIGND, is an analog common signal. You can use this pin for a general analog power ground tie to the NI PCI-1200 in RSE mode or as a return path in NRSE mode. Pin 11, AGND, is the bias current return point for differential measurements. Pins 1 through 8 are tied to the eight single-ended AI channels of the input multiplexer through 4.7 k $\Omega$  series resistors. Pins 2, 4, 6, and 8 and also tied to an input multiplexer for DIFF mode.

The signal ranges for inputs ACH<7..0> at all possible gains are shown in Tables 3-2 and 3-3. Exceeding the input signal range will not damage the input circuitry as long as the maximum powered-on input voltage rating

of  $\pm 35$  V or powered off voltage rating of  $\pm 25$  V is not exceeded. The NI PCI-1200 is guaranteed to withstand inputs up to the maximum input voltage rating.

**Caution** Exceeding the input signal range distorts input signals. Exceeding the maximum input voltage rating may damage the NI PCI-1200 device and the computer. NI is *not* liable for any damage resulting from such signal connections.

Table 3-2. Bipolar Analog Input Signal Range Versus Gain

| Gain Setting | Input Signal Range |

|--------------|--------------------|

| 1            | -5.0 to 4.99756 V  |

| 2            | -2.5 to 2.49878 V  |

| 5            | -1.0 to 0.99951 V  |

| 10           | -500 to 499.756 mV |

| 20           | –250 to 249.877 mV |

| 50           | -100 to 99.951 mV  |

| 100          | −50 to 49.975 mV   |

**Table 3-3.** Unipolar Analog Input Signal Range Versus Gain

| Gain Setting | Input Signal Range |

|--------------|--------------------|

| 1            | 0 to 9.99756 V     |

| 2            | 0 to 4.99878 V     |

| 5            | 0 to 1.99951 V     |

| 10           | 0 to 999.756 mV    |

| 20           | 0 to 499.877 mV    |

| 50           | 0 to 199.951 mV    |

| 20           | 0 to 99.975 mV     |

How you connect AI signals to the NI PCI-1200 depends on how you configure the NI PCI-1200 AI circuitry and the type of input signal source. With different NI PCI-1200 configurations, you can use the NI PCI-1200

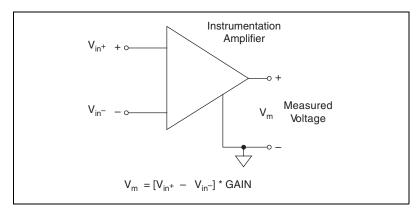

instrumentation amplifier in different ways. Figure 3-2 shows a diagram of the NI PCI-1200 instrumentation amplifier.

Figure 3-2. NI PCI-1200 Instrumentation Amplifier

The NI PCI-1200 instrumentation amplifier applies gain, common-mode voltage rejection, and high-input impedance to the AI signals connected to the NI PCI-1200. Signals are routed to the positive and negative inputs of the instrumentation amplifier through input multiplexers on the device. The instrumentation amplifier converts two input signals to a signal that is the difference between the two input signals multiplied by the gain setting of the amplifier. The amplifier output voltage is referenced to the NI PCI-1200 ground. The NI PCI-1200 ADC measures this output voltage when it performs A/D conversions.

All signals must be referenced to ground, either at the source device or at the NI PCI-1200. If you have a floating source, you must use a ground-referenced input connection at the NI PCI-1200. If you have a grounded source, use a nonreferenced input connection at the NI PCI-1200.

## Types of Signal Sources

When configuring the input mode of the NI PCI-1200 and making signal connections, first determine whether the signal source is floating or ground referenced. These two signal types are described in the following sections.

### Floating Signal Sources

A floating signal source is not connected in any way to the building ground system but has an isolated ground-reference point. Some examples of floating signal sources are outputs of transformers, thermocouples, battery-powered devices, optical isolator outputs, and isolation amplifiers.

Tie the ground reference of a floating signal to the NI PCI-1200 AI ground to establish a local or onboard reference for the signal. Otherwise, the measured input signal varies or appears to float. An instrument or device that supplies an isolated output falls into the floating signal source category.

#### **Ground-Referenced Signal Sources**

A ground-referenced signal source is connected in some way to the building system ground and is, therefore, already connected to a common ground point with respect to the NI PCI-1200, assuming that the computer is plugged into the same power system. Nonisolated outputs of instruments and devices that plug into the building power system fall into this category.

The difference in ground potential between two instruments connected to the same building power system is typically between 1 and 100 mV but can be much higher if power distribution circuits are improperly connected. The connection instructions that follow for grounded signal sources eliminate this ground potential difference from the measured signal.

**Note** If you power both the NI PCI-1200 and the computer with a floating power source (such as a battery), the system may float with respect to earth ground. In this case, treat all of the signal sources as floating sources.

## **Input Configurations**

You can configure the NI PCI-1200 for RSE, NRSE, or DIFF input mode. The following sections discuss the use of single-ended and differential measurements, and considerations for measuring both floating and ground-referenced signal sources. Table 3-4 summarizes the recommended input configurations for both types of signal sources.

Table 3-4. Summary of Analog Input Connections

|                                                 | Signal Source Type                                                                                   |                                                                    |  |  |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|

|                                                 | Floating Signal Source<br>(Not Connected to Building Ground)                                         | Grounded Signal Source                                             |  |  |

| Input                                           | Examples  • Ungrounded Thermocouples  • Signal Conditioning with Isolated Outputs  • Battery Devices | Examples • Plug-in Instruments with Nonisolated Outputs            |  |  |

| Differential<br>(DIFF)                          | ACH(+)  + V <sub>1</sub> ACH(-)  R AIGND  See text for information on bias resistors.                | ACH(+) + V <sub>1</sub> ACH(-) AIGND                               |  |  |

|                                                 |                                                                                                      | NOT RECOMMENDED                                                    |  |  |

| Single-Ended —<br>Ground<br>Referenced<br>(RSE) | ACH + V1 AIGND &                                                                                     | ACH  + V <sub>1</sub> AIGND  AIGND                                 |  |  |

|                                                 |                                                                                                      | Ground-loop losses, V <sub>g</sub> , are added to measured signal. |  |  |

| Single-Ended —<br>Nonreferenced<br>(NRSE)       | ACH  AISENSE  R  AIGND  See text for information on bias resistors.                                  | ACH + V1 AISENSE AIGND                                             |  |  |

#### **Differential Connection Considerations (DIFF Configuration)**

Differential connections are those in which each NI PCI-1200 AI signal has its own reference signal or signal return path. These connections are available when you configure the NI PCI-1200 in the DIFF mode. Each input signal is tied to the positive input of the instrumentation amplifier, and its reference signal, or return, is tied to the negative input of the instrumentation amplifier.

When configuring the NI PCI-1200 for DIFF input, each signal uses two of the multiplexer inputs—one for the signal and one for its reference signal. Therefore, only four AI channels are available when using DIFF mode. Use DIFF input mode when any of the following conditions is present:

- Input signals are low level (less than 1 V).

- Leads connecting the signals to the NI PCI-1200 are greater than 10 ft.

- Any of the input signals require a separate ground-reference point or return signal.

- The signal leads travel through noisy environments.

Differential signal connections reduce noise pickup and increase common-mode signal and noise rejection. With these connections, input signals can float within the common-mode limits of the input instrumentation amplifier.

#### **Differential Connections for Grounded Signal Sources**

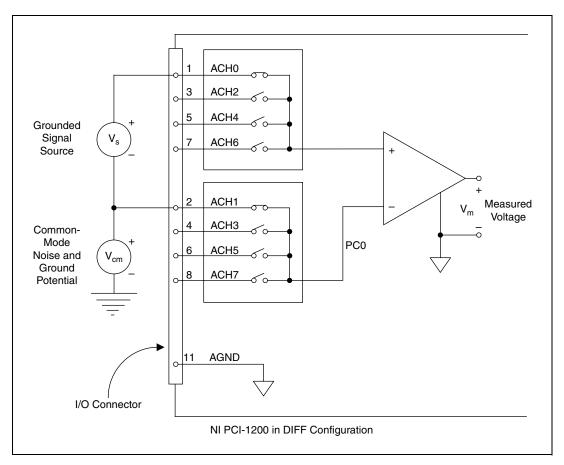

Figure 3-3 shows how to connect a ground-referenced signal source to a NI PCI-1200 configured for DIFF input mode. Configuration instructions are in the *Analog I/O Configuration* section of Chapter 2, *Installing and Configuring the NI PCI-1200*.

**Figure 3-3.** Differential Input Connections for Grounded Signal Sources

With this connection type, the instrumentation amplifier rejects both the common-mode noise in the signal and the ground-potential difference between the signal source and the NI PCI-1200 ground (shown as  $V_{cm}$  in Figure 3-3).

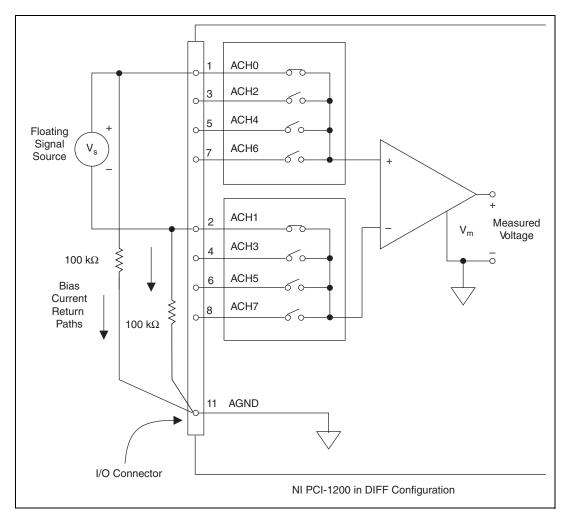

#### **Differential Connections for Floating Signal Sources**

Figure 3-4 shows how to connect a floating signal source to a NI PCI-1200 configured for DIFF input mode. Configuration instructions are in the *Analog I/O Configuration* section of Chapter 2, *Installing and Configuring the NI PCI-1200*.

Figure 3-4. Differential Input Connections for Floating Sources

The  $100~k\Omega$  resistors shown in Figure 3-4 create a return path to ground for the bias currents of the instrumentation amplifier. If there is no return path, the instrumentation amplifier bias currents charge stray capacitances, resulting in uncontrollable drift and possible saturation in the amplifier. Typically, values from  $10~to~100~k\Omega$  are used.

A resistor from each input to ground, as shown in Figure 3-4, provides bias current return paths for an AC-coupled input signal.

If the input signal is DC-coupled, you need only the resistor that connects the negative signal input to ground. This connection does not lower the input impedance of the AI channel.

#### **Single-Ended Connection Considerations**

Single-ended connections are those in which all NI PCI-1200 AI signals are referenced to one common ground. The input signals are tied to the positive input of the instrumentation amplifier, and the common ground point is tied to the negative input of the instrumentation amplifier.

When the NI PCI-1200 is configured for a single-ended input mode (NRSE or RSE), eight AI channels are available. Use single-ended input connections when the following conditions are met by all input signals:

- Input signals are high level (greater than 1 V).

- Leads connecting the signals to the NI PCI-1200 are less than 10 ft.

- All input signals share a common reference signal (at the source).

If any of the preceding criteria is not met, use the DIFF input configuration.

You can software configure the NI PCI-1200 for two types of single-ended connections, RSE configuration and NRSE configuration. Use the RSE configuration for floating signal sources; in this case, the NI PCI-1200 provides the reference ground point for the external signal. Use the NRSE configuration for ground-referenced signal sources; in this case, the external signal supplies its own reference ground point and the NI PCI-1200 should not supply one.

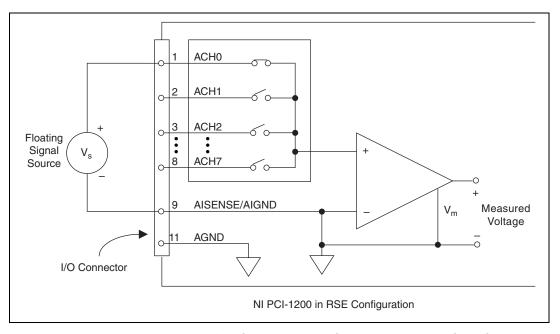

# Single-Ended Connections for Floating Signal Sources (RSE Configuration)

Figure 3-5 shows how to connect a floating signal source to an NI PCI-1200 configured for RSE mode. Configure the NI PCI-1200 AI circuitry for RSE input to make these types of connections. Configuration instructions are in the *Analog I/O Configuration* section of Chapter 2, *Installing and Configuring the NI PCI-1200*.

Figure 3-5. Single-Ended Input Connections for Floating Signal Sources

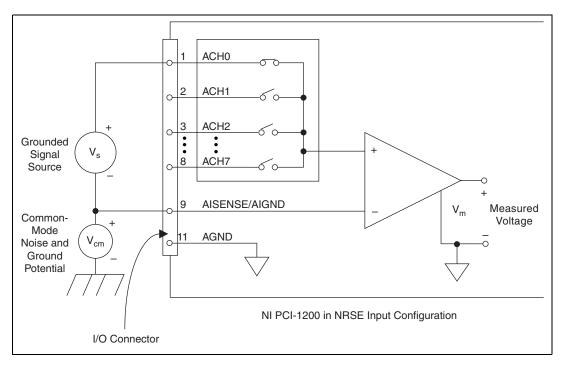

# Single-Ended Connections for Grounded Signal Sources (NRSE Configuration)

If you measure a grounded signal source with a single-ended configuration, configure the NI PCI-1200 in the NRSE input configuration. The signal is connected to the positive input of the NI PCI-1200 instrumentation amplifier and the signal local ground reference is connected to the negative input of the NI PCI-1200 instrumentation amplifier. Therefore, connect the ground point of the signal to the AISENSE pin. Any potential difference between the NI PCI-1200 ground and the signal ground appears as a common-mode signal at both the positive and negative inputs of the instrumentation amplifier and is therefore rejected by the amplifier. On the other hand, if the input circuitry of the NI PCI-1200 is referenced to ground,

such as in the RSE configuration, this difference in ground potentials appears as an error in the measured voltage.

Figure 3-6 shows how to connect a grounded signal source to an NI PCI-1200 configured in NRSE input mode. Configuration instructions are included in the *Analog I/O Configuration* section of Chapter 2, *Installing and Configuring the NI PCI-1200*.

**Figure 3-6.** Single-Ended Input Connections for Grounded Signal Sources

### **Common-Mode Signal Rejection Considerations**

Figures 3-4 and 3-6 show connections for signal sources that are already referenced to some ground point with respect to the NI PCI-1200. In these cases, the instrumentation amplifier can reject any voltage caused by ground-potential differences between the signal source and the NI PCI-1200. In addition, with differential input connections, the instrumentation amplifier can reject common-mode noise pickup in the leads connecting the signal sources to the NI PCI-1200.

The common-mode input range of the NI PCI-1200 instrumentation amplifier is the magnitude of the greatest common-mode signal that can be rejected.

The common-mode input range for the NI PCI-1200 depends on the size of the differential input signal,  $V_{diff} = (V_{in}+) - (V_{in}-)$ , and the gain setting of the instrumentation amplifier. In unipolar mode, the differential input range is 0 to 10 V. In bipolar mode, the differential input range is –5 to +5 V. Inputs should remain within a range of –5 to 10 V in both bipolar and unipolar modes.

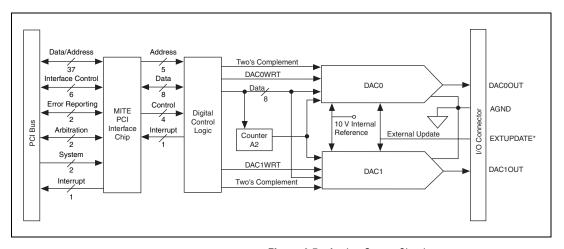

## **Analog Output Signal Connections**

Pins 10 through 12 on the I/O connector are AO signal pins.

Pins 10 and 12 are the DAC0OUT and DAC1OUT signal pins. DAC0OUT is the voltage output signal for AO channel 0. DAC1OUT is the voltage output signal for AO channel 1.

Pin 11, AGND, is the ground-reference point for the AO and AI channels.

The following output ranges are available:

- Bipolar output: ±5 V<sup>1</sup>

- Unipolar output: 0 to 10 V<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> Maximum load current: ±2 mA for 12-bit linearity

Load VOUT 0

Load VOUT 1

Load VOUT 1

Load VOUT 1

Load VOUT 1

AGND

12

DAC1OUT Channel 1

Analog Output Channels

NI PCI-1200

Figure 3-7 shows how to make AO signal connections.

Figure 3-7. Analog Output Signal Connections

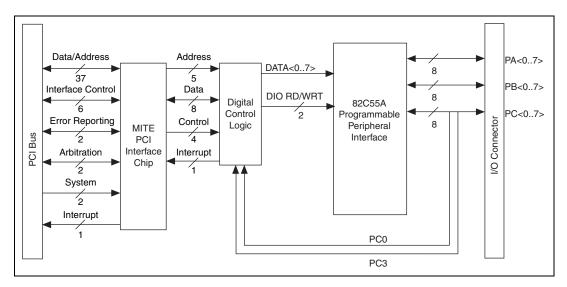

### **Digital I/O Signal Connections**

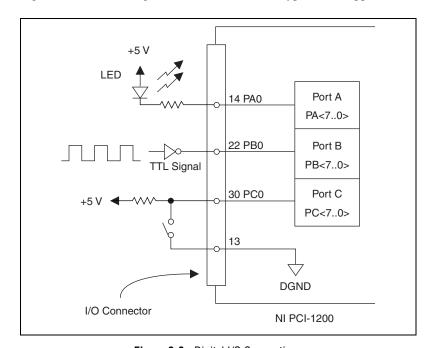

Pins 13 through 37 of the I/O connector are DIO signal pins. DIO on the NI PCI-1200 uses the 82C55A integrated circuit. The 82C55A is a general-purpose peripheral interface containing 24 programmable I/O pins. These pins represent the three 8-bit ports (PA, PB, and PC) of the 82C55A.

Pins 14 through 21 are connected to the digital lines PA<7..0> for DIO port A. Pins 22 through 29 are connected to the digital lines PB<7..0> for DIO port B. Pins 30 through 37 are connected to the digital lines PC<7..0> for DIO port C. Pin 13, DGND, is the digital ground pin for all three DIO ports. Refer to Appendix A, *Specifications*, for signal voltage and current specifications.

The following specifications and ratings apply to the DIO lines. All voltages are with respect to DGND.

### **Logical Inputs and Outputs**

| • | Abs | solute max voltage rating                                          | -0.5 to $+5.5$ V |           |

|---|-----|--------------------------------------------------------------------|------------------|-----------|

| • | DIC | ) lines:                                                           |                  |           |

|   | _   | Input logic low voltage                                            | -0.3 V min       | 0.8 V max |

|   | _   | Input logic high voltage                                           | 2.2 V min        | 5.3 V max |

|   | -   | Output logic low voltage (at output current = 2.5 mA)              | _                | 0.4 V max |

|   | -   | Output logic high voltage (at output current = $-2.5 \text{ mA}$ ) | 3.7 V min        | _         |

|   | -   | Input leakage current $(0 < V_{in} < 5 V)$                         | −1 µA min        | 1 μA max  |

Figure 3-8 illustrates signal connections for three typical DIO applications.

Figure 3-8. Digital I/O Connections

In Figure 3-8, port A is configured for digital output, and ports B and C are configured for digital input. Digital input applications include receiving

TTL signals and sensing external device states, such as the state of the switch in Figure 3-8. Digital output applications include sending TTL signals and driving external devices, such as the LED in Figure 3-8.

#### **Port C Pin Connections**

The signals assigned to port C depend on the mode in which the 82C55A is programmed. In mode 0, port C is considered to be two 4-bit I/O ports. In modes 1 and 2, port C is used for status and handshaking signals with two or three I/O bits mixed in. Table 3-5 summarizes the signal assignments of port C for each programmable mode.

| Programmable                               |                    |                    | Group A |                    |                   | Group B            |                    |                   |

|--------------------------------------------|--------------------|--------------------|---------|--------------------|-------------------|--------------------|--------------------|-------------------|

| Mode                                       | PC7                | PC6                | PC5     | PC4                | PC3               | PC2                | PC1                | PC0               |

| Mode 0                                     | I/O                | I/O                | I/O     | I/O                | I/O               | I/O                | I/O                | I/O               |

| Mode 1 Input                               | I/O                | I/O                | $IBF_A$ | STB <sub>A</sub> * | INTR <sub>A</sub> | STB <sub>B</sub> * | IBFB <sub>B</sub>  | INTR <sub>B</sub> |

| Mode 1 Output                              | OBF <sub>A</sub> * | ACK <sub>A</sub> * | I/O     | I/O                | INTR <sub>A</sub> | ACK <sub>B</sub> * | OBF <sub>B</sub> * | INTR <sub>B</sub> |

| Mode 2                                     | OBF <sub>A</sub> * | ACK <sub>A</sub> * | $IBF_A$ | STB <sub>A</sub> * | INTR <sub>A</sub> | I/O                | I/O                | I/O               |

| * Indicates that the signal is active low. |                    |                    |         |                    |                   |                    |                    |                   |

Table 3-5. Port C Signal Assignments

#### **Power Connections**

Pin 49 of the I/O connector supplies +5 V from the computer power supply through a self-resetting fuse. The fuse resets automatically within a few seconds after the overcurrent condition is removed. Pin 49 is referenced to DGND, and you can use the +5 V to power external digital circuitry.

• Power rating: 1 A at +4.65 to +5.25 V

**Caution** Do not directly connect this +5 V power pin to analog or digital ground or to any other voltage source on the NI PCI-1200 or any other device. Doing so can damage the NI PCI-1200 or the computer. NI is *not* liable for any damage due to incorrect power connections.

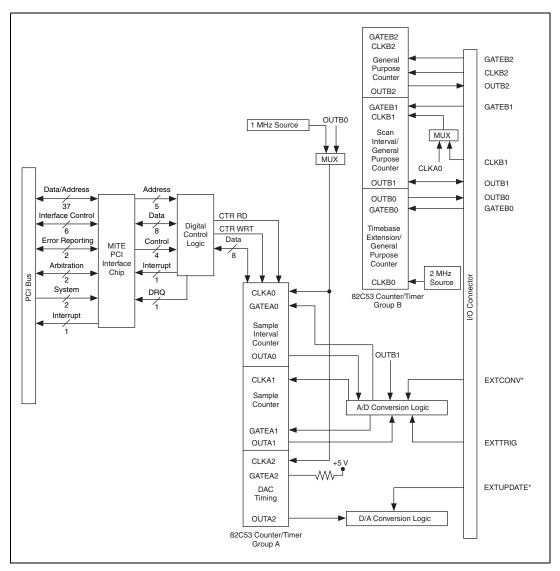

### **DAQ and General Purpose Timing Signal Connections**

Pins 38 through 48 of the I/O connector are connections for TIO signals. The NI PCI-1200 timing I/O uses two 82C53 counter/timer integrated circuits. One circuit, designated 82C53(A), is used exclusively for DAQ timing, and the other, 82C53(B), is available for general use. Use pins 38

through 40 and pin 43 to carry external signals for DAQ timing. These signals are explained in the *DAQ Timing Connections* section. Pins 41 through 48 carry general purpose timing signals from 82C53(B). These signals are explained in the *General Purpose Timing Signal Connections* section.

### **DAQ Timing Connections**

Each 82C53 counter/timer circuit contains three counters. Counter 0 on the 82C53(A) counter/timer, referred to as A0, is a sample-interval counter in timed A/D conversions. Counter 1 on the 82C53(A) counter/timer, referred to as A1, is a sample counter in controlled A/D conversions. Therefore, counter A1 stops data acquisition after a predefined number of samples. These counters are unavailable for general use.

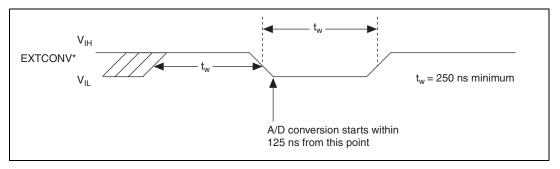

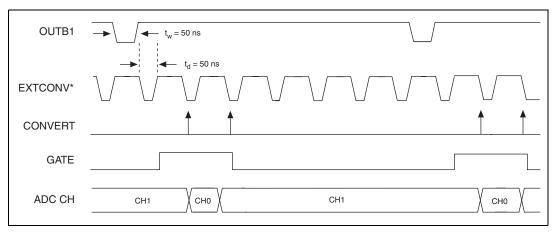

Instead of counter A0, you can use EXTCONV\* to externally time conversions. Figure 3-9 shows the timing requirements for the EXTCONV\* input. An A/D conversion is initiated by a falling edge on the EXTCONV\*.

Figure 3-9. EXTCONV\* Signal Timing

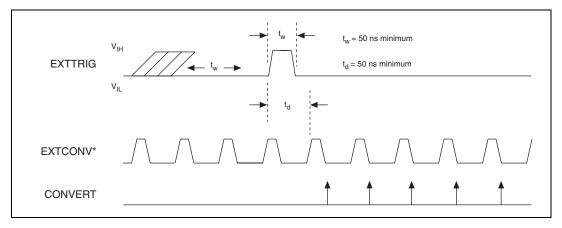

The external control signal EXTTRIG can either start a DAQ sequence or terminate an ongoing DAQ sequence depending on the mode—posttrigger (POSTTRIG) or pretrigger (PRETRIG). These modes are software-selectable.

In the POSTTRIG mode, EXTTRIG serves as an external trigger that initiates a DAQ sequence. When you use counter A0 to time sample intervals, a rising edge on EXTTRIG starts counter A0 and the DAQ sequence. When you use EXTCONV\* to time sample intervals, data acquisition is enabled on a rising edge of EXTTRIG followed by a rising edge on EXTCONV\*. The first conversion occurs on the next falling edge of EXTCONV\*. Further transitions on the EXTTRIG line have no effect until a new DAQ sequence is established.

Figure 3-10 shows a possible controlled DAQ sequence using EXTCONV\* and EXTTRIG. The rising edge of EXTCONV\* that enables external conversions must occur a minimum of 50 ns after the rising edge of EXTTRIG. The first conversion occurs on the next falling edge of EXTCONV\*.

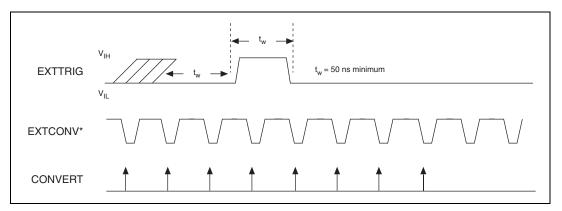

Figure 3-10. Posttrigger DAQ Timing

In the PRETRIG mode, EXTTRIG serves as a pretrigger signal. Data is acquired both before and after the EXTTRIG signal occurs. A/D conversions are software enabled, which initiates the DAQ operation. However, the sample counter is not started until the EXTTRIG input senses a rising edge. Conversions remain enabled until the sample counter counts to zero. You can acquire up to 65,535 samples after the stop trigger. The number of samples acquired before the trigger is limited only by the size of the memory buffer available for data acquisition.

Figure 3-11 shows a pretrigger DAQ timing sequence using EXTTRIG and EXTCONV\*. The DAQ operation has been initiated through software.

ni.com

**Note** The sample counter has been programmed to allow five conversions after the rising edge on the EXTTRIG signal. Additional transitions on the EXTTRIG line have no effect until you initiate a new DAQ sequence.

Figure 3-11. Pretrigger DAQ Timing

For interval scanning data acquisition, counter B1 determines the scan interval. Instead of using counter B1, you can externally time the scan interval through OUTB1. If you externally time the sample interval, you should also externally time the scan interval.

Figure 3-12 shows an example of an interval-scanning DAQ operation. The scan interval and the sample interval are being timed externally through OUTB1 and EXTCONV\*. Channels 1 and 0 of the input multiplexers are scanned once during each scan interval. The first rising edge of EXTCONV\* must occur a minimum of 50 ns after the rising edge on OUTB1. The first rising edge of EXTCONV\* after the rising edge of OUTB1 enables an internal GATE signal that allows conversions to occur. The first conversion then occurs on the following falling edge of EXTCONV\*. The GATE signal disables conversions for the rest of the scan interval after the desired channels have been scanned. Refer to the *Interval Scanning Acquisition Mode* section of Chapter 4, *Theory of Operation*, for more information on interval scanning.

Figure 3-12. Interval-Scanning Signal Timing

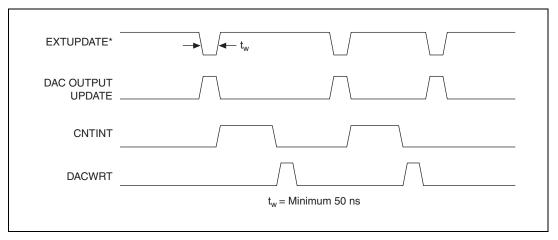

Use the final external control signal, EXTUPDATE\*, to externally control updating the output voltage of the 12-bit DACs and/or to generate an externally timed interrupt. There are two update modes, immediate update and delayed update. In immediate update mode, the analog output is updated as soon as a value is written to the DAC. If you select the delayed update mode, a value is written to the DAC; however, the corresponding DAC voltage is not updated until a low level on the EXTUPDATE\* signal is sensed. Furthermore, if you enable interrupt generation, an interrupt is generated whenever a rising edge is detected on the EXTUPDATE\* bit. Therefore, you can perform externally timed, interrupt-driven waveform generation on the NI PCI-1200. The EXTUPDATE\* line is susceptible to noise caused by switching lines and could generate false interrupts. You should make the width of the EXTUPDATE\* pulse as short as possible, but greater than 50 ns.

Figure 3-13 illustrates a waveform generation timing sequence using the EXTUPDATE\* signal and the delayed-update mode. The DACs are updated by a high level on the DAC OUTPUT UPDATE signal, which in this case is triggered by a low level on the EXTUPDATE\* line. CNTINT is the signal that interrupts the computer. This interrupt is generated on the rising edge of EXTUPDATE\*. DACWRT is the signal that writes a new value to the DAC.

Figure 3-13. EXTUPDATE\* Signal Timing for Updating DAC Output

The absolute max voltage input rating for the EXTCONV\*, EXTTRIG, OUTB1, and EXTUPDATE\* signals is -0.5 to 5.5 V with respect to DGND.

For more information concerning the various modes of data acquisition and analog output, refer to Chapter 4, *Theory of Operation*, or to the NI-DAQ documentation.

### **General Purpose Timing Signal Connections**

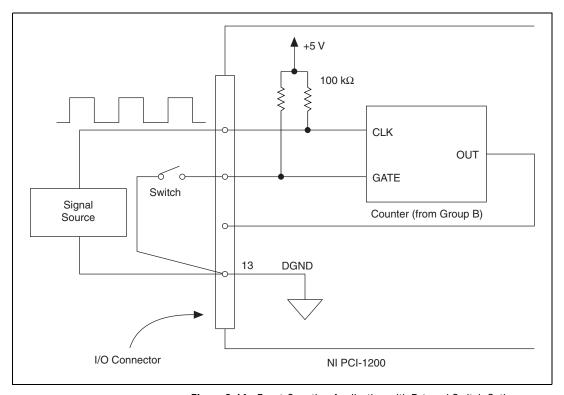

The general purpose timing signals include the GATE, CLK, and OUT signals for the three 82C53(B) counters. The 82C53 counter/timers can be used for general-purpose applications such as pulse and square wave generation, event counting, and pulse-width, time-lapse, and frequency measurement. For these applications, the CLK and GATE signals at the I/O connector control the counters. The single exception is counter B0, which has an internal 2 MHz clock.

To perform pulse and square wave generation, program a counter to generate a timing signal at its OUT output pin. To perform event counting, program a counter to count rising or falling edges applied to any of the 82C53 CLK inputs, then read the counter value to determine the number of edges that have occurred. You can enable or disable the counting operation by controlling the gate input. Figure 3-14 shows connections for a typical event-counting operation in which a switch is used to gate the counter on and off.

Figure 3-14. Event-Counting Application with External Switch Gating

Pulse-width measurement is performed by level gating. The pulse you want to measure is applied to the counter GATE input. The counter is loaded with the known count and is programmed to count down while the signal at the GATE input is high. The pulse width equals the counter difference (loaded value minus read value) multiplied by the CLK period.

Perform time-lapse measurement by programming a counter to be edge gated. An edge is applied to the counter GATE input to start the counter. Program the counter to start counting after receiving a low-to-high edge. The time lapse since receiving the edge equals the counter value difference (loaded value minus read value) multiplied by the CLK period.

To perform frequency measurement, program a counter to be level gated and count the number of falling edges in a signal applied to a CLK input. The gate signal applied to the counter GATE input is of known duration. In this case, program the counter to count falling edges at the CLK input while the gate is applied. The frequency of the input signal then equals the count value divided by the gate period. Figure 3-15 shows the connections for a

frequency measurement application. You can also use a second counter to generate the gate signal in this application. If you use a second counter, you must externally invert the signal.

Figure 3-15. Frequency Measurement Application

The GATE, CLK, and OUT signals for counters B1 and B2 are available at the I/O connector. The GATE and CLK pins are internally pulled up to +5 V through a  $100 \text{ k}\Omega$  resistor. Refer to Appendix A, *Specifications*, for signal voltage and current specifications.

The following specifications and ratings apply to the 82C53 I/O signals:

- Absolute max voltage input rating -0.5 to +5.5 V, with respect to DGND

- 82C53 digital input specifications (referenced to DGND):

- V<sub>ih</sub> input logic high voltage

V<sub>il</sub> input logic low voltage

Input load current

V<sub>ih</sub> input logic low voltage

V min

0.8 V max

Hout load current

μA min

μA max

• 82C53 digital output specifications (referenced to DGND):

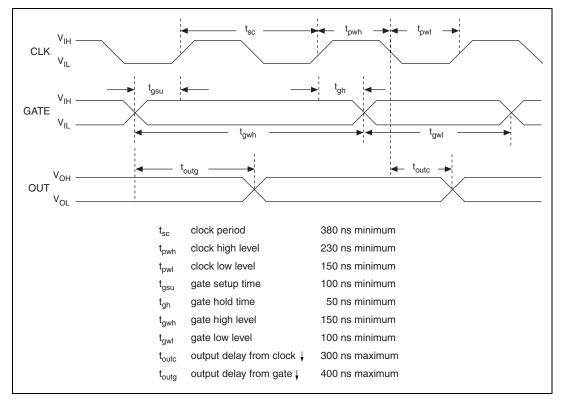

Figure 3-16 shows the timing requirements for the GATE and CLK input signals and the timing specifications for the 82C53 OUT output signals.

Figure 3-16. General Purpose Timing Signals

The GATE and OUT signals in Figure 3-16 are referenced to the rising edge of the CLK signal.

### **Timing Specifications**

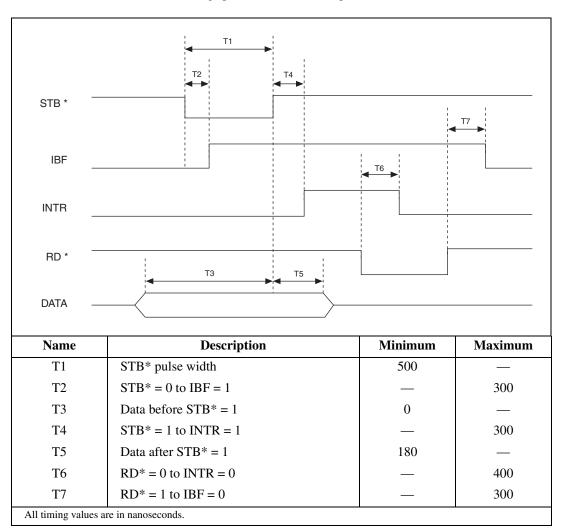

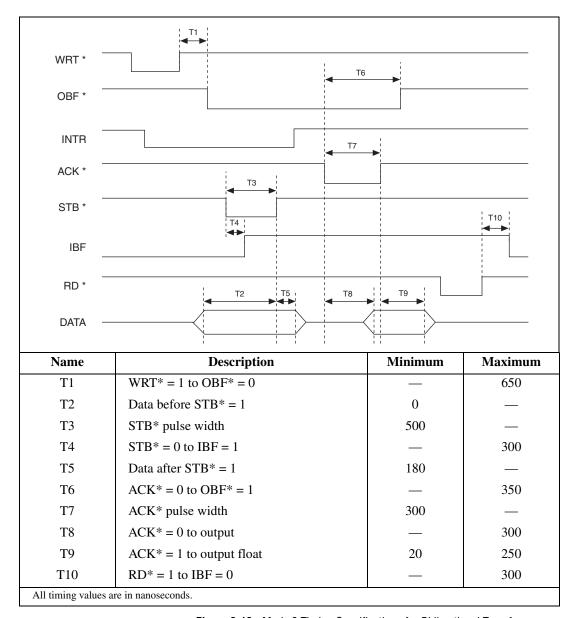

Use the handshaking lines STB\* and IBF to synchronize input transfers. Use the handshaking lines OBF\* and ACK\* to synchronize output transfers.

The following signals are used in the mode timing diagrams.

**Table 3-6.** Signal Names Used in Timing Diagrams

| Name | Туре          | Description                                                                                                                                                                                                                                  |

|------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STB* | Input         | Strobe Input—A low signal on this handshaking line loads data into the input latch.                                                                                                                                                          |

| IBF  | Output        | Input Buffer Full—A high signal on this handshaking line indicates that data has been loaded into the input latch. IBF is primarily an input acknowledge signal.                                                                             |

| ACK* | Input         | Acknowledge Input—A low signal on this handshaking line indicates that the data written from the specified port has been accepted. ACK* is primarily a response from the external device that it has received the data from the NI PCI-1200. |

| OBF* | Output        | Output Buffer Full—A low signal on this handshaking line indicates that data has been written from the specified port.                                                                                                                       |

| INTR | Output        | Interrupt Request—This signal becomes high when the 82C55A is requesting service during a data transfer. Set the appropriate interrupt enable signals to generate this signal.                                                               |