## **User's Manual**

## **FoCs**

Formal Checkers - a Productivity Tool

Version 0.59

Formal Methods and Technologies Group IBM Research Labs in Haifa February 2003

## **Notices**

FoCs User's Manual Date modified February 2003

For information regarding FoCs, contact: Gil Shapir (shapir@il.ibm.com)

Tel: +972-4-8296258

International Business Machines Corporation provides this publication "as is" without warranty of any kind, either express or implied. Some states do not allow disclaimer of express or implied warranties in certain transactions; therefore this statement may not apply to you.

This publication may contain technical inaccuracies or typographical errors. While every precaution has been taken in the preparation of this document, the publisher and author assume no responsibility for errors or omissions. Nor is any liability assumed for damages resulting from the use of the information contained herein. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/ or changes in the product(s) and/or the program(s) described in this publication at any time.

It is possible that this publication may contain references to, or information about, IBM products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that IBM intends to announce such IBM products, programming, or services in your country.

All trademarks and service marks are trademarks of their respective owners.

$\ensuremath{\odot}$  Copyright IBM Research Lab in Haifa 2000-2003. All rights reserved.

## **Table of Contents**

| CHAPTER 1 | Introduction                            | 5  |

|-----------|-----------------------------------------|----|

| 1.1       | Overview                                | 5  |

| 1.2       | About This Manual                       | 6  |

|           |                                         |    |

| CHAPTER 2 | Installation and Setup                  | 8  |

| 2.1       | Installation                            | 8  |

| 2.2       | Running FoCs                            | 9  |

| CHAPTER 3 | Linking Checkers with your Design       | 11 |

| 3.1       | Introduction                            | 11 |

| 3.2       | Signal Mapping                          | 12 |

| 3.3       | Linkage                                 | 17 |

| CHAPTER 4 | Tutorial                                | 21 |

| 4.1       | Introduction                            | 21 |

| 4.2       | Design Description                      | 21 |

|           | The Rules File                          |    |

| 4.4       | Initial Setup for a Working Environment | 25 |

| 4.5       | Generating Checkers                     | 26 |

| CHAPTER 5 | The Sugar Specification Language        | 30 |

| 5.1       | Introduction                            | 30 |

|           | Getting Started with Sugar              |    |

| 5.3       | The Building Blocks of a Sugar Formula  | 38 |

| 5.4       | Writing a Rules File                    | 43 |

| 5.5       | State Machines                          | 49 |

| CHAPTER 6 | Customizing FoCs Settings               | 61 |

| 6.1       | Overview                                | 61 |

| 6.2       | Main Tab                                | 61 |

| 6.3       | Clock and Reset Tab                     | 62 |

| 6.4       | Checker Generation Style Tab            | 64 |

| 6.5       | Reporting Tab                           | 66 |

| 6.6       | Signal Manning Tab                      | 81 |

| CHAPTER 7  | Using FoCs for Functional Coverage Analysis  | 83  |

|------------|----------------------------------------------|-----|

| 7.1        | Functional Coverage                          | 83  |

| CHAPTER 8  | Defining Bugspray Events                     | 85  |

| 8.1        | Introduction                                 | 85  |

| 8.2        | Syntax                                       | 85  |

| 8.3        | Events                                       | 86  |

| CHAPTER 9  | FoCs for RuleBase Users                      | 91  |

| 9.1        | Tips for Users of RuleBase                   | 91  |

| CHAPTER 10 | Appendix A                                   | 93  |

| 10.        | Examples of Checker Code in Verilog and VHDL | 93  |

| 10.2       | 2 Checker Code in Verilog                    | 93  |

| 10.3       | 3 Checker Code in VHDL                       | 95  |

| CHAPTER 11 | Appendix B                                   | 103 |

| 11.1       | Common FoCs Error Messages                   | 103 |

## CHAPTER 1 Introduction

#### 1.1 Overview

FoCs (short for Formal Checkers, pronounced "fox") is a productivity tool that greatly aids design and verification engineers in the complex, costly task of developing simulation test benches.

FoCs automatically generates simulation checkers, also known as monitors, from properties specified in the language Sugar<sup>†</sup>. These properties, also called "rules" or "assertions", describe the legal behaviors of the design under test. Typically, the user of FoCs derives properties from the design specification documents where they are written informally in English and writes them as Sugar formulas. Using FoCs, these properties are translated into checker code in the desired target language—Verilog or VHDL<sup>‡</sup>. The checker code is then connected to the simulation environment. During simulation, the checkers track and report violations of the properties.

As an example of the power of FoCs, consider an arbiter which must abide by the following property: upon the completion of five consecutive cycles where the request

<sup>†. &</sup>quot;Sugar" is an industry-standard language for assertion-based verification. It was selected as a basis for an IEEE standard by Accellera on April 22, 2002.

<sup>‡.</sup> In the future, FoCs will also generate checkers in C/C++.

signal is asserted and the acknowledge signal not asserted, the busy signal should be asserted.

The Sugar formulation for this property is:

• {[\*], {request & ! acknowledge}[5]}-> {busy\_flag}

Once this property is fed into FoCs, the tool produces a corresponding VHDL or Verilog checker that can be integrated into a simulation environment and monitor the design behavior on a cycle-by-cycle basis for violation of the property. It is often the case that a 1-line or 2-line Sugar property is automatically translated by FoCs to a checker which spans hundreds of lines of HDL code<sup>†</sup>. The benefit—in terms of programmer time that would have otherwise been spent in manually coding the checker—is evident. There are other benefits to using FoCs—such as reduced debugging time, portability, and reuse of properties. The checking code produced by FoCs is synthesizable, so this code can be used in emulation as well. By virtue of these advantages, FoCs increases engineering productivity in a very notable manner.

A complimentary application of FoCs is the generation of coverage monitors for coverage analysis. When FoCs is used for this purpose, the user specifies combinations and/or sequences of events which he or she wants covered in simulation. FoCs then automatically generates a checker to track the occurrence of these events during simulation.

For further information on FoCs, see the FoCs website at

www.haifa.il.ibm.com/projects/verification/focs/index.html

#### 1.2 About This Manual

This manual is intended to serve as a guide for using FoCs (including the definition of design properties using Sugar). The manual is organized as follows:

- Chapter 1 Introduction introduces the FoCs tool.

- Chapter 2 Installation and Setup explains how to install and set up the FoCs tool.

<sup>†.</sup> The checker produced by FoCs for the above Sugar property is included, for reference, in Appendix A.

#### Introduction

- Chapter 3 Linking the Checkers with your Design explains how to link the checkers with the design you are testing.

- **Chapter 4 Tutorial** guides you through a short example, where you can get hands-on experience in creating checkers using FoCs.

- Chapter 5 Sugar provides details on how to start using the Sugar and EDL specification languages to specify the design properties, including the structure of the rules file, creating formulas, expressions, and satellites. This chapter also presents examples of real-life formulas that can be used with FoCs.

- Chapter 6 Customizing FoCs Settings describes the settings and tabs that can be customized for your use.

- Chapter 7 Using FoCs for Functional Coverage explains how to enhance the quality of tests by providing a means for measuring test coverage.

- Chapter 8 Defining Bugspray Events for users who want to use FoCs with Bugspray instrumentation. Explains how to define Bugspray events in the FoCs rules file.

- Chapter 9 FoCs for RuleBase Users explains the methodology of working with FoCs with properties used for Formal Verification.

- **Appendix A** Shows examples of checker code in VHDL and Verilog.

- **Appendix B** Documents and explains common error messages.

## CHAPTER 2 Installation and Setup

#### 2.1 Installation

This section explains how to install the FoCs tool and get it up and running.

If FoCs is not already installed on your computer or network, proceed as follows:

- 1. Create a new directory and copy the installation file focs.tar.gz into the directory.

- 2. Type the command gzip -d focs.tar and press Enter.

- 3. Type the command tar xvf focs.tar and press Enter.

- 4. Type the command rm focs.tar and press Enter.

This will unzip the tar file and copy the installation files into their appropriate location.

#### 2.1.1 Personal Setup

To customize FoCs for your individual environment, you need to set an environment variable and create an alias for FoCs.

The environment variable FOCS\_DIR should point to the FoCs installation directory.

```

In csh: setenv FOCS_DIR the_installation_directory

In ksh: export FOCS DIR=the installation directory

```

#### **Installation and Setup**

Create an alias "focs" for \$FOCS\_DIR/focs as follows:

```

In csh: alias focs '$FOCS_DIR/focs' or add $FOCS DIR to your search path.

```

## 2.2 Running FoCs

The following sections provide tips on how to begin working with FoCs.

#### 2.2.1 Checker Generation

Before you begin, you should create a working directory from which you run FoCs.To begin using the FoCs tool:

- 1. Type the command: focs

- 2. If this is your first FoCs session in this directory, you have to set up FoCs for your project. Click **Settings** to open the Settings dialog.

- 3. Select the target language (VHDL or Verilog), the target simulator (only for VHDL), the clock signal name, and the reset signal name (unless you ask FoCs to generate an internal reset).

- 4. Select the rules file—the file in which you write your rules. The language in which you specify rules (Sugar) is described in Chapter 4 of this guide.

- 5. You can browse through the other Settings tabs and fields if you want to have more control over the generation process. Use the tool-tips to see short field descriptions.

- 6. When you are done, close the Settings dialog and return to the main window.

- 7. Select a rule to be translated into a checker and click **Generate**. Errors are reported in the Messages window below. If generation is successful, the checker filename will appear in the Messages window.

- 8. If you wish to translate several rules into one checker file, select these rules (using control/mouse-button or shift/mouse-button or the All button) and press Generate. You will be asked to provide a name for the checker file, and for the entity name if the generated checker is in VHDL.

#### 2.2.2 Batch Mode

Checkers can also be generated by the command line without invoking the GUI. To generate a checker for a specific rule, you must type in the command line: **focs** - **batch** <**rule name>**. To generate a checker for all rules in the rules file, you must type in the command line: **focs** -**batch** all. To generate several rules, you must type in the command line: **focs** -**batch** <**rules names>**. In this case, the settings for the generated checker are those defined in the file focs.setup. The best way to update this file is by defining the settings through the GUI. When exiting FoCs, the settings are saved to this file. You can also use the following flags in the batch mode:

focs -batch <rule name or rules names or all> -rule file> -o <output\_file\_name> -s <setup\_file\_name>.

| Flag | Explanation                                                                                                                             |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|

| -r   | This flag reads the rule file from the command line instead of reading the rule file from the setup file                                |

| -0   | This flag gives a specific name for the output file (checker name).                                                                     |

| -S   | This flag reads the setup file from the command line instead of reading the default setup file focs.setup (from the current directory). |

# CHAPTER 3 Linking Checkers with your Design

#### 3.1 Introduction

In order to monitor design behavior during simulation, the generated checkers must become part of the simulated model. This occurs through the following three steps:

#### 1. Linkage

The checker module (in Verilog) or entity/architecture (in VHDL) must be compiled and linked to the design under test. The actual commands are specific to the compilation/simulation environment, and are not within the scope of this document.

#### 2. Instantiation

A call to the module (in Verilog) or instantiation of the entity (in VHDL) must (usually) be included in the design. FoCs assists in this step by generating the calling statements.

#### 3. Signal Connection

The checker signals must be connected to the real design signals. The solution depends on the language and on the simulation environment. FoCs provides a standard language solution for port mapping, and specific signal-connection solutions for several simulations.

In the following sections, we describe the mapping method and linkage.

## 3.2 Signal Mapping

To keep your formulas simple and readable, you can use short and meaningful signal names. You can then map these simple names to the real signal names. FoCs will map those signals to real ports if an instantiation statement was created, when a mapping for MTI is defined, or when Bugspray is used.

For example, use the name request rather than BXX\_ARB\_REQ. You can create a mapping file in your working directory and let FoCs map the aliases to the real names. The basic format of the mapping file is a list of pairs of signal names, one pair in each line.

```

alias1 realname1 alias2 realname2

```

#### For example:

```

request BXX_ARB_REQ

signal1 /MY DESIGN/BLOCK1/BLOCK11/SIGNAL1

```

You should define the deliminators according to your mapping option, for example, dots for port mapping or slashes for MTI Signal Spy.

The mapping file should be pointed to by Settings/SignalMapping/MappingFile.

#### 3.2.0.1 Nested Design Signals

If design signals are nested and all signals are declared in the same entity, it is possible to define the Design Signals Prefix parameter in the settings options, under Signal Mapping. The value of this field is added to every design signal that appears in the mapping file. In case of Automatic Mapping, where the port name is considered to be the corresponding design signal name, the Design Signals Prefix is added to all port names that appear in the checkers entity (see Section 3.2.0.2 on page 14).

For example:

Design Signals Prefix is defined to: design.buf

#### Linking Checkers with your Design

#### content of file mapping.dat:

```

clk clock

rec receive

trans transmit

```

#### Is equivalent to:

```

clk design.buf.clock;

rec design.buf.receive;

trans design.buf.transmit;

```

To map ports to signals that appear in different parts of the design (the signals are nested, but the path is different from signal to signal), the following syntax exists in the file mapping.dat:

```

#path < path for the signal >

```

All of the signals that appear after this line, and until the next line with the same syntax, will receive the string in arrow brackets (<>) as a subpath, in addition to the global path defined by a environment variable. It is possible to use this syntax without defining a global path.

#### Example 1:

Design Signals Prefix is defined to: design

content of file mapping.dat:

```

#path buf_1

clk clock

rec receive

#path buf_2

trans transmit

```

#### Is equivalent to:

```

clk design.buf_1.clock;

rec design.buf_1.receive;

```

```

trans design.buf_2.transmit;

Example 2:

Design signals Prefix is undefined.

content of file mapping.dat:

#path design.buf_1

clk clock

rec receive

```

#### Is equivalent to:

```

clk design.buf_1.clock;

rec design.buf_1.receive;

trans design.buf_2.transmit;

```

#### 3.2.0.2 Automatic Signal Mapping

#path design.buf\_2

trans transmit

There is one more possibility to map a port signal. If the port signals have the same names as the signals in the design and are not nested or have the common path, they can be mapped by defining Warn Incomplete Mapping to No (in the Settings options, under Signal Mapping), and defining Design Signals Prefix to the path needed.

In this case, every port name in the checker that does not appear in the mapping file (or if a mapping file does not exist at all) will be mapped to the signal with the same name and with the path defined by Design Signals Prefix. A mapping that is defined in a mapping file, overrides the Automatic Mapping. As before, defining the path is optional.

#### Example 1:

```

Warn Incomplete Mapping No

Design Signals Prefix design

content of mapping.dat

#path buf

clk clock

```

#### **Linking Checkers with your Design**

```

checker ports : clk, rec, trans

Is equivalent to:

clk design.buf.clock;

rec design.rec;

trans design.trans;

```

#### Example 2:

Warn Incomplete Mapping No Design signals Prefix is undefined file mapping.dat doesn't exist checker ports: clk, rec, trans

#### Is equivalent to:

```

clk clk;

rec rec;

trans trans;

```

#### Example 3:

File mapping.dat doesn't exist

Warn Incomplete Mapping No

Design signals Prefix design

Is equivalent to:

```

clk design.clk;

rec design.rec;

trans design.trans;

```

#### 3.2.0.3 Using Hierarchical Signal Names

It is possible to use hierarchical signal names when writing Sugar formulas. For such signals, FoCs will automatically create a unique, non hierarchal signal name, and map it to the hierarchical name.

For example, it is possible to write the formula:

```

formula

{

always(u1.u2.aa)

}

```

In this case, FoCs will generate a checker signal named **focs\_u1\_u2\_aa**, and a mapping between it and u1.u2.aa.

If a design signal prefix is defined, it will be added to the signals mapping. In the previous example, if we had design signal prefix set to main we would get the mapping:

```

focs u1 u2 aa => main..u1.u2.aa

```

For this kind of mapping, "Automatic Mapping" should be chosen, i.e., "Warn Incomplete Mapping" should be set to "No".

It is possible to override the default mapping that is created by defining a different mapping for the signal name that was created in the mapping.dat file.

In the above example, it is possible to define in the file mapping.dat the following mapping:

```

focs u1 u2 aa "design.my block.aa"

```

#### 3.2.0.4 Mapping Vectors

When a checker port is a vector, the signal that will be mapped to it should also be a vector. In the file mapping.dat, the syntax for vector is:

```

vector name(index1..index2)

```

#### Linking Checkers with your Design

This is a syntax only for design signals because the range of a checker port is known (the size of design vector has to correspond to the appropriate checker port).

#### Example:

content of file mapping.dat:

```

#path buf_1

clk clock

rec "receive"

#path buf_2

trans transmit

bus "vector(10..41)"

```

Where "bus" is the port in the checker which is vector 0..31, the above is equivalent to:

```

clk buf_1.clock;

rec buf_1.receive;

trans buf_2.transmit;

bus buf_2.vector(10..41);

```

If the range of the vector is not defined, the range of the checker port will be used. All the options that were discussed in the previous subsections are relevant for both vectors and signals.

## 3.3 Linkage

The following sections discuss linkage, which describes how to link the generated checkers with the design for several simulation environments.

#### 3.3.1 Verilog

By default, two files are generated—the checker module and a file that contains a call to this module. You should embed the call statement in the design. The actual parameters in the call statement are the design signal names mentioned in the

formulas. If a name is mapped, as described in the Signal Mapping section above, the post-mapping name will be used as an actual parameter in the call statement.

You can choose to generate a bare Verilog by using Settings/GenerationStyle/GenerateModule=NO. In this case, the checker will not be encapsulated in a module and you will have to embed its body in the design.

#### 3.3.2 Pure VHDL

By default, three files are generated—the checker entity+architecture, a file that contains a component statement, and a file that contains an instantiation statement. You should embed the latter two statements in the design (automatically, if possible). The actual parameters in the port map of the instantiation statement are the design signal names mentioned in the formulas. If a name is mapped, as described in the Signal Mapping section above, the post-mapping name will be used in the instantiation.

#### 3.3.3 Bugspray (IBM only)

The generated checker contains instrumentation directives that help Bugspray link the checker to the design and connect the checker signals to the design signals. The component and instantiation statements are not required and are not generated. Settings/GenerationStyle/DesignEntityName must specify the design entity to which the checkers refer. Port mapping names are used in Bugspray "--!! inputs" section.

#### 3.3.4 Model Sim®

Three files are generated—the checker entity+architecture, a file that contains a component statement and a file that contains an instantiation statement. You should embed the latter two statements in the design.

There are three possible signal mapping methods, controlled by Settings/ SignalMapping/MappingMethod. If you choose None, the generated checker will be regarded as a Pure VHDL checker and linked to the design as such (see above). We recommend that you choose None. If force freeze or signal spy is used, appropriate mapping directives will be added to the generated checker. In the case of force-freeze, the directives are written to a separate file, with the extension "mon" (shortcut for monitor). When using signal spy, every design signal name must be double quoted

#### **Linking Checkers with your Design**

except for generic ports, described in the next section. This is because signal spy mapping deals with strings.

#### 3.3.4.1 Signal Spy Mapping Using Generic Ports

It is possible to define a mapping from signals to generic ports.

To map a signal to a generic port, simply write the name of the generic port, in the mapping file, without double quotes. It is also possible to use a concatenation of strings, using generic ports (exactly as you do when applying signal spy on your VHDL).

#### For example:

```

aa, bb, cc are checker ports.

/main/u1/aa, main/u2/bb, main/u2/cc are design-under-test signals

to which we want to map checker ports (correspondingly).

```

Two examples of possible mappings FoCs can generate:

init\_signal\_spy("aa", "/main/u1/aa");

a. without generic ports:

It is the user's responsibility to set x to be "1" and y to be "2" in checker instantiation.

\* Note: two mappings are give the same result under condition  $\mathbf{x} = "1"$  and  $\mathbf{y} = "2"$ .

Mapping file for (a) - without generic ports:

```

aa "/main/u1/aa"

bb "/main/u2/bb"

cc "/main/u2/cc"

```

Mapping file for (b) - with generic ports:

```

aa "/main/u" & x & "/aa"

bb "/main/u" & y & "/bb"

cc "/main/u" & y & "/cc"

```

\* Note: x and y appear in mapping file without double quotes so that they are interpreted by FoCs as generic ports.

For more information about force freeze and signal spy, see the MTI documentation. The directives are derived from the mapping mechanisms described in the Signal Mapping section above. This means that you have to provide a mapping file and/or use the Design Signal Prefix option.

If the mapping method is something other than None, the generated entity, component, and instantiation have an almost empty port map because the actual signal hooking is done through the special directives. Only the clock and reset signals are explicitly referenced.

## Tutorial

#### 4.1 Introduction

This chapter guides you through an example of a simple design and how FoCs can be used to enhance its verification productivity. The tutorial presents a small design named BUF and a list of rules which the design must abide by, and shows you how to generate checkers from these rules.

## 4.2 Design Description

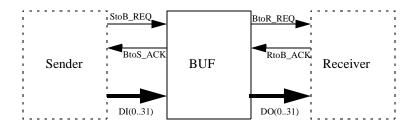

BUF is a design block that buffers a word of data (32 bits) sent by a sender to a receiver. It has two control inputs, two control outputs, and a data bus on each side, as shown in the block diagram below:

Communication (on both sides) takes place by means of a four-phase handshaking as follows:

When the sender has data to send to the receiver, it initiates a transfer by putting the data on the data bus and asserting Stob\_REQ (server to buffer request). If BUF is free, it reads the data and asserts BtoS\_ACK (buffer to server acknowledge). Otherwise, the sender waits. After seeing BtoS\_ACK, the sender may release the data bus and deassert Stob\_REQ. To conclude the transaction, BUF deasserts BtoS\_ACK.

When BUF has data, it initiates a transfer to the receiver by putting the data on the data bus and asserting BtoR\_REQ (buffer to receiver request). If the receiver is ready, it reads the data and asserts RtoB\_ACK (receiver to buffer acknowledge). Otherwise, BUF waits. After seeing RtoB\_ACK, BUF may release the data bus and deassert BtoR\_REO. To conclude the transaction, the receiver deasserts RtoB\_ACK.

#### 4.3 The Rules File

For the tutorial, a rules file with some rules regarding the BUF design has already been created, and can be found at: \$FOCS\_DIR/tutorial/rules.

The rules are written in Sugar. See CHAPTER 5: The Sugar Specification Language for more details.

The rules file contains the following rules:

```

rule ack_interleaving {

btor_reqstob_reqbtos_ackbtos_ack formula

```

```

"No overflow: rtob_ack is asserted between any two btos_ack

assertions "

{ [*] , !RST & rose(btos ackbtos ack) , true }(

rose(rtob ack) before rose(btos ack) )

formula

"No underflow: btos_ack is asserted between any two rtob_ack

assertions"

{ [*] , !RST & rose(rtob_ack) , true } ( rose(btos_ack) before

rose(rtob_ack) )

rule four_phase_handshake_left{

formula

"A request can not be raised when ack is high "

{ [*] , !stob req & btos ack , stob req }(false)

formula

"A request can not be lowered when ack is low"

{ [*] , stob_req & !btos_ack , !stob_req }(false)

formula

"An acknowledge can not be raised when reg is low"

```

```

{

{ [*] , !btos ack & !stob req , btos ack }(false)

formula

"An acknowledge can not be lowered when reg is high"

{ [*] , btos_ack & stob_req , !btos_ack }(false)

rule four_phase_handshake_right{

formula

"A request can not be raised when ack is high"

{ [*] , !btor_req & rtob_ack , btor_req }(false)

formula

"A request can not be lowered when ack is low"

{ [*] , btor_req & !rtob_ack , !btor_req }(false)

formula

"An acknowledge can not be raised when req is low"

{ [*] , !rtob_ack & !btor_req , rtob_ack }(false)

formula

```

```

"An acknowledge can not be lowered when req is high"

{ [*] , rtob ack & btor req , !rtob ack }(false)

VAR tmp(0..31):boolean;

ASSIGN init(tmp(0..31)) := 0;

ASSIGN next(tmp(0..31)) :=

IF rose(btos_ack) THEN DI(0..31)

ELSE tmp(0..31)

ENDIF;

rule checking_data{

"The data sent to the receiver is the same data received from the

sender in the last write"

formula {

{ [*], !RST \& rose(rtob_ack) } ( DO(0..31) = tmp(0..31) )

```

### 4.4 Initial Setup for a Working Environment

If you are running FoCs for the first time:

1. Add the following setting to your .cshrc file (or the shell with which you are working):

```

setenv FOCS_DIR location_of_focs_executable

```

alias focs \$FOCS\_DIR/focs

- 2. Create a directory called focs\_tutorial.

- 3. Copy \$FOCS\_DIR/tutorial/rules into your focs\_tutorial directory. The rules file includes four rules about BUF.

- 4. Invoke the FoCs GUI by typing **focs**.

## 4.5 Generating Checkers

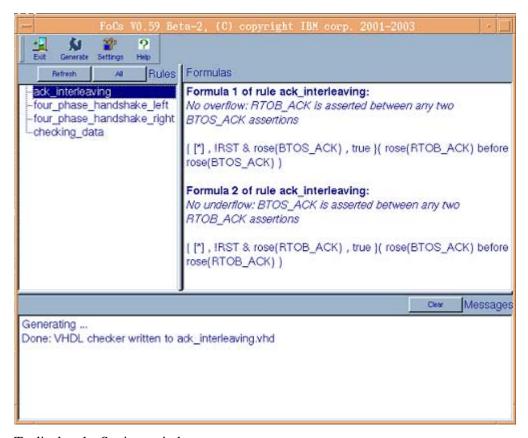

The FoCS GUI has three different windows:

- **Rules window** displays a list of rule names from the rule file (select rule file from the settings window).

- **Formulas window** displays all formulas from the selected rules in the rules window.

- Messages window displays all relevant messages from FoCs.

The following is a screenshot from the tutorial.

To display the Settings window:

- 1. Click **Settings**.

- 2. Update the **Clock Name and Reset Name** in the Clock/Reset Tab. You can browse through the other Settings tabs and fields if you want to have more control over the generation process. Use the tool-tips to see short field descriptions.

- 3. Choose the target language: VHDL/Verilog When you open FoCS for the first time, all settings are set to their default values.

- 4. Click **OK.** This saves your settings and closes the Settings window.

To generate a checker from one rule:

#### 1. Select rule ack\_interleaving

The Formulas window displays two formulas.

#### 2. Click Generate.

One of the following messages (according to the target language) appears in the Message window:

Generating ...

Done: VHDL checker written to ../ack interleaving.vhd

or

Done: Verilog checker written to ../ack\_interleaving.v

You can open the file (ack\_interleaving.vhd or ack\_interleaving.v) created in your current directory, and see the checker that was generated.

#### To generate a checker **from several rules**:

- 1. Select rule ack\_interleaving.

- 2. Press the Ctrl button and select rule **checking data**. The Formulas window displays all of the formulas for these two rules.

- 3. Click **Generate**.

The **Choose an output filename** window will open.

4. Enter the name of the desired checker (**checker.vhd or checker.v**) and click **OK**. The following message appears in the Messages window:

Generating ...

Done: VHDL checker written to ../checker.vhd

or

Done: Verilog checker written to ../checker.v

#### To generate a checker **from all rules**:

Click All from the Rules window.

This selects all rules in this window.

2. Click Generate.

The **Choose an output filename** window opens.

#### **Tutorial**

3. Enter the name of the desired checker (all.vhd or all.v) and click **OK**. The following message appears in the Messages window:

Generating ...

Done: VHDL checker written to ../checker.vhd

or

Done: Verilog checker written to ../checker.v

# The Sugar Specification Language

#### 5.1 Introduction

Sugar is the specification language used by FoCs. It is used to describe properties that are required to hold in the design under test (DUT). FoCs can very easily create powerful checkers from Sugar properties using only a small number of Sugar constructs.

In this document, the term 'property' refers to a specification, described in informal English, that must hold true for the design under simulation. The term 'formula' refers to the coded representation of properties in Sugar. This chapter introduces Sugar in a way that allows FoCs users to start describing properties in Sugar and generating checkers from those properties simply.

The chapter is organized as follows:

Section 5.2: Getting Started with Sugar – introduces the basic Sugar constructs. This is an informal description of these constructs, designed to give you the notion of how to describe the required design behaviors using Sugar.

Section 5.3: The Building Blocks of a Sugar Formula – this is a more precise description of the Sugar properties building blocks.

Section 5.4: Writing a Rules File – describes the notion and structure of the Rules File,

#### The Sugar Specification Language

from which FoCs reads Sugar properties to create checkers.

Section 5.5: State Machines – this section describes how to use a larger subset of the Sugar language and gain further expressive power, for defining complex properties.

## 5.2 Getting Started with Sugar

The Sugar specification language lets you describe properties to which the design under simulation must adhere. Many properties can be easily described using the following constructs.

#### 5.2.1 Always (p)

This Sugar construct enables you to assert that some property p is true on every cycle of the simulation. P can be any boolean expression composed of signal names, constants, and operators.

For example, you may want to check that signals grant1 and grant2 are not asserted together. This property can be expressed in Sugar by the following formula:

```

always (!(grant1 & grant2))

```

which states that at every cycle of a simulation, it is never the case that both grant1 and grant2 are asserted.

The following are more examples of properties that can be expressed using **always**(p):

• The property "Whenever ack is asserted, req was asserted in the previous cycle," can be expressed as

```

always (ack->prev(rew))

```

prev(x) is a built-in function, which is true if x was true in the previous cycle. A list of built-in functions you can use appears in Section 5.3.3 on page 43.

• "Variables state1 and state2 never have the same value."

```

always (state1 != state2)

```

"!=" denotes inequality. A list of relational operators appears in Table 2.

• "If busy is true then working is also true"

```

always (busy -> working)

```

"->" denotes "implies".

"At most one of the signals x, y, or z is 1 (mutual exclusion)."

```

always (x+y+z <=1)

```

A list of mathematical operators appears in Section 5.3.1 on page 38.

"If the head pointer of a queue is equal to the tail pointer, queue\_empty must be true":

```

always((head(0..3)=tail(0..3)-> queue\_empty))

```

Both head and tail are 4-bit arrays and the expression head(0..3)=tail(0..3) denotes equality of arrays. The symbol ".." denotes a range of array bits. head(0..3) denotes bits 0 through 3 in the array head. You can refer either to a range of entries of an array head (0..3) or to one entry of an array (e.g., head(2)). A reference to a whole vector should explicitly include its range (vec1(0..16) rather than vec1).

• "The bitwise and of vectors vec(0..7) and mask(0..7) has at least one bit set": always((vec(0..7) & mask(0..7))) != 00000000b)

We need the parentheses around vec(0..7) & mask(0..7) because "!=" has a higher precedence than "&". Table 1 shows the operators precedence.

#### 5.2.2 Sugar Extended Regular Expression – SERE

The construct **always(p)** can refer only to an expression that spans one cycle. Sometimes we want to check events that span over a period of time, and not just one cycle.

To this end, we can express properties of multi-cycle traces using Sugar Extended Regular Expressions—SEREs. SEREs can be used to describe sequences of boolean expressions over time.

For example, a SERE describing any occurrence of start, ready, ready can be written as: {[\*], start, ready, ready}.

The [\*] at the start of the sequence is an event that denotes "skip any number of cycles"; start between two commas (,start,) means a cycle in which start is asserted; and in the following two cycles, ready is asserted. So this sequence represents many possible traces. For example:

• traces in which start is asserted at the beginning and then followed by two ready: start, ready, ready,...

#### The Sugar Specification Language

• traces in which start happens at the second step and then followed by two ready: true, start, ready, ready (true represents "skip one cycle"), etc.

If we omit [\*], the sequence would describe only traces that start with start, ready, ready. It is important to write [\*] at the beginning of the sequence because we usually want to refer to any occurence of start, ready, ready in the trace, and not just at the beginning of the execution.

Writing SEREs is an extension to writing regular expressions. Regular expressions are simple to write but still very expressive. Defining a regular expression is very intuitive, when keeping the desired timing diagram in mind.

#### 5.2.2.1 The constructs {SERE} -> {SERE} and {SERE} =>{SERE}

SERE's can be used to described properties that span several cycles. For example, the property "whenever the sequence start, ready, ready appears, the second ready after start is accompanied by result = ok and followed by done" can be written as

```

{[*], start, ready, ready} ->{result=ok, done}

```

The meaning of this construct is as follows: if the sequence on the left side is encountered during simulation, then the right side should be true, starting at the last cycle of this sequence.

It is possible to use two kinds of implication operators. Using -> between the two sequences means that the right hand sequence must begin at the last cycle of the left hand side. Using => means that the right hand side sequence must begin one cycle after the left hand side.

The following are examples of properties that can be expressed using SEREs implication:

- {[\*],start, busy[\*], end}->{success, done} states that if signal start is asserted, at the next cycle or later in the future, signal end is asserted, and in the interim signal busy holds, then success is asserted with end, and at the next cycle done is asserted.

- {[\*],request}=>{request[\*], grant} states that if there is a request, than it must remain active until grant.

• All properties in the form of {SERE} -> {SERE} and {SERE} => {SERE}, can be described in English as "If the right side occurs, then the left side must occur." For example, the property "If during get tag=1, then in the next get tag=2 and in the next get tag=3," is expressed by:

```

{ [*] , get&tag=1 }=>{ !get[*], get&tag=2, !get[*] , get&tag=3 } And the property "If during get tag=1 \underline{and} in the next get tag=2 \underline{then} in the next get tag=3," is expressed by:

```

```

{ [*], get&tag=1, !get[*], get&tag=2}=>{ !get[*], get&tag=3 }

```

- When we want to express that a signal p is asserted at least once, we can use the event p[+].

For example, {[\*], start, busy[+], end}->{success, done} states that if signal start is asserted, signal busy is asserted for one or more cycles, and finally signal end is asserted, then success is asserted with end, and followed by done.

- Instead of writing true[+], you can write [+].

{[\*], start, [+], end}->{success}

states that if signal start is asserted, and two or more cycles later signal end is asserted, then success is asserted with end, followed by done.

- There is a special way to describe an exact number of consecutive repetitions. For example, writing ready[8] expresses eight consecutive cycles in which ready is asserted.

```

{[*], start, ready[8]}->{result=ok}

```

states that if start is followed by eight consecutive cycles in which ready is asserted, then at the eighth ready result=ok.

To say that ready is asserted at most eight consecutive cycles we write ready[..8].

- {[\*], start, ready[..8], !ready}->{ok} states that if start was asserted, and starting the next cycle, ready was asserted for at most eight cycles until ready was false, then ok is asserted with !ready. The other types of consecutive repetitions are listed in Table 2.

- Assume we want to write "the second ready after start should be accompanied with success". Here we want to check also executions in which the start and the ready signals are not necessarily consecutive. This can be expressed by

```

{[*], start, !ready[*], ready, !ready[*], ready}

->{success}

```

#### The Sugar Specification Language

The expression !ready[\*] means zero or more consecutive steps in which ready is false.

• There is a special shorthand for non-consecutive repetition. For example, the property "Whenever we see eight non-consecutive data transfers between start\_trans and end\_trans, the signal error is not asserted with end\_trans" can be described by:

```

{[*],start_trans,data[=8],end_trans}->{!error}

```

The event data[=8] represents eight non-consecutive repetitions of data.

#### 5.2.2.2 Subsequences

A sequence may contain a subsequence in curly braces.

- For example, the sequence

- {[\*], {start, [\*], end}[\*]} describes a trace in which there are zero or more occurrences of the scenario in which start is asserted and in the next cycle or later end is asserted.

- The other consecutive repetitions can also be applied to subsequences. For example:

- $\{[*], \{start, [*], end\}[+]\}$  describes a trace in which the subsequence  $\{start, [*], end\}$  occurs at least once.

- {[\*], {start, [\*], end}[8]} describes a trace in which the subsequence {start, [\*], end} occurs exactly eight times.

- {[\*], {start, [\*], end}[..8]} describes a trace in which the subsequence {start, [\*], end} occurs at most eight times.

The following are examples that use subsequences:

After start, if we see 8 gets (not necessarily consecutive) and there is no abort during this period, then one cycle after the last get must begin 8 puts (not necessarily consecutive before done (done may not come at all)

```

{ [*], start, {!get&!abort[*], get&!abort}[8] }=>{ {!put&!done[*],

put&!done}[8] }

```

- If req1 is active, it will be granted (gnt1) within no more than 7 gnts { [\*], req1 }->{ {!qnt[\*], qnt&!qnt1}[0..6], !qnt[\*], qnt&qnt1 }

- p is true in cycle 0 and every fifth cycle

```

{ true, {true[4]}[*] }=>{ p }

```

For details on all subsequence options, see Section 5.3.2.2 on page 41.

#### 5.2.2.3 The || and && operators

It is possible to define an AND and OR relation between subsequences, using the  $\parallel$  and &&, respectively.

• For example, to express the property:

"If there is a request that is followed either by read and no cancel\_read or write and no cancel\_write until done, then ok is asserted with done"

it is possible to write:

```

{[*], request, {read, !cancel_read, !done[*]}||{write,

!cancel_write, !done[*]}, done} -> {ok}

```

Writing an or between two subsequences means that only one of them must happen for the sequence to hold. The subsequences may be of different length.

• To express the property:

"If there is no abort during {start, a, b, c[\*], d, end}, success will be asserted with end"

```

it is possible to write:

{[*], {start, a, b, c[*], d, end}&&{!abort[*]}}->{success}

```

The subsequences that have a && operator between them occur simultaneously. This means that they begin and end together, and must have a non-contradicting length.

The && operator cannot appear in the right side sequence.

#### 5.2.2.4 Applying Never to SERE's

We can use a sequence to check that a bad trace never happens. This is done by applying the **never** operator to the forbidden sequence.

#### Examples:

• If request is asserted it will remain active until (inclusive) grant.

```

never{[*], request& !grant, !grant[*], !request}

```

• If request is asserted, it will remain active until (not inclusive) grant: never{[\*], request, !grant[\*], !request & !grant}

• If grant is active, and there is no retry in the next cycle, busy must become active two cycles after grant:

```

never {[*], grant, !retry, !busy}

```

#### 5.2.2.5 Counting Boolean events

It is possible to count boolean events that are not necessarily consecutive. This is particularly useful when combined with &&.

#### Examples:

- Request will be serviced within the 5 coming acknowledges never{[\*], req, ack[=5]&&serv[=0]}

- It is forbidden to have 15 writes during which there are less then 2 reads. never{[\*], write[=15]&&read[<2]}

### 5.2.3 Suffix Implication (SERE)()

It is possible to combine SEREs with temporal properties. This form of writing means that starting from the last cycle of the sequence, the temporal property must hold.

### 5.2.3.1 {SERE}(p until q)

Using this construct, it is possible to check that some signal holds until another signal is asserted. For example: "Between a request and its acknowledge the busy signal must remain asserted" can be described by

```

{[*], req, true}(busy until ack)

```

{SERE} ( a until b) means a should be true on the last cycle of the sequence and continue to be true until (but not including when) b is true. a and b are boolean expressions, and b may never happen.

{SERE} (a until\_b) means a should be true on the last cycle of the sequence, and continue to be true until (and including when) b is true. a and b are boolean expressions, and b may never happen.

For example:

• {[\*], req, !retry, !retry} (busy until end) states that for every request (assertion of signal req) that is not retried (signal retry is not retried in the next two cycles), signal busy must be asserted until signal end is asserted.

### 5.2.3.2The Construct {SERE} (p before q)

If we want to describe that a specific signal must be asserted before another signal, we can use the **before** operator. For example: "Always if req then ack will happen **before** the next req".

```

{ [*], req, true}(ack before req)

{SERE} ( a before b)

```

expresses the requirement that on the last cycle of all traces that match SERE, the first occurrence of a must happen before or together with the first occurrence of b. There is no requirement that b eventually happen.

```

{SERE} ( a before_ b)

```

expresses the requirement that on the last cycle of all traces that match SERE, the first occurrence of a must happen strictly before or the first occurrence of b. There is no requirement that b eventually happen.

#### For example:

• If start is activated, it must not be active again before stop is activated.

```

{ [*], start, true }( stop before start)

```

The true at the end of the sequence skips one cycle because we want to check the property on the cycle after start.

# 5.3 The Building Blocks of a Sugar Formula

### 5.3.1 Boolean Expressions

The basic building blocks of a Sugar formula are Boolean expressions. A Boolean expression consists of signal names of the design under verification, numbers, constants, and operators.

#### 5.3.1.1 Signal Names

For integers i and j, the following are the signal names:

- a simple name: signal\_name

- A bit of a vector: signal\_name(i) (bit i of signal signal\_name)

- signal\_name(i..j) (bits i through j of signal signal\_name)

- signal\_name(b: i..j) (bit b of signal signal\_name, where the range is given by i and j. b must be an integer, and the relevant signal must be defined in the rules file)

#### 5.3.1.2 Numbers

- A decimal number has only decimal digits and no suffix (e.g., 1276)

- A binary number consists of binary digits and ends with 'B' (e.g., 1011B)

- A hexadecimal number begins with a decimal digit, has hexadecimal digits less than 8, and ends with 'H' (e.g., 7FFFH, 0FFH)

A reference to a whole vector should explicitly include its range (vec1(0..16) rather than vec1).

### 5.3.1.3 Operators

The operators appearing in boolean expressions in decreasing precedence are described below.

### **TABLE 1. Operators**

```

() parentheses

! not

* / multiplication and division

+ - addition and subtraction

=!=><>= relational operators

& Boolean and

| Boolean or

xor Boolean xor

-> Boolean implication

<< >> vector shift; the right operand should be an integer

```

### Examples:

- request is a boolean expression asserting that the environment signal request is set.

- op=READ | op=WRITE is a boolean expression asserting that the design signal op currently has either the value READ or the value WRITE.

- (counter>32) <-> queue\_is\_full is a boolean expression asserting that the user-defined signal counter has a value greater than 32, if and only if the design-signal queue\_is\_full is asserted.

## **5.3.2 Temporal Properties**

### **5.3.2.1 Temporal Constructs**

The temporal constructs of Sugar used by FoCs are summarized below. These

constructs provide for the definition of temporal behavior across multiple cycles.

- always (p) p is true on every cycle

- {SERE} -> {SERE} if the left side sequence occurs, the right side sequence must hold, starting from its last cycle.

- {SERE} => {SERE} if the left hand side sequence occurs, the right hand side sequence must hold, starting from the following cycle.

- **never**{**SERE**} The sequence may never occur.

- {SERE} (p until q) Starting at the last cycle of the sequence, p must hold until q occurs, not including the cycle q is asserted. The formula does not require that q must eventually occur (in that case, p must be true forever).

- {SERE} (p until\_q) Starting at the last cycle of the sequence, p must hold until q occurs, including the cycle q is asserted. The formula does not require that q must eventually occur (in that case, p must be true forever)

- **{SERE}** (p **before**\_q) Starting at the last cycle of the sequence, p must happen before the first q. The formula does not require that q eventually happen.

- **{SERE}** (p **before** q) Starting at the last cycle of the sequence, p must happen before or together with the first q. The formula does not require that q eventually happen.

The above formulas are enough for expressing most desired properties. For a description of all Sugar formulas, see the Sugar v1.4 document.

### **5.3.2.2 Sequence Operators**

The building blocks of sequences are boolean expressions and operations on them. The following tables summarize the possible operators.

Using b to represent a boolean expression, Table 2 lists legal operators and their meaning.

**TABLE 2. Simple Operators**

| b[*]                                                                   | b occurs in 0 or more consecutive cycles                                |

|------------------------------------------------------------------------|-------------------------------------------------------------------------|

| b[+]                                                                   | b occurs in one or more consecutive cycles                              |

| b[i]                                                                   | b occurs in exactly i consecutive cycles                                |

| b[ij]                                                                  | b occurs in at least i consecutive cycles, but in no more than j cycles |

| b[i]                                                                   | b occurs in i or more consecutive cycles                                |

| b[i]                                                                   | b occurs in no more than i consecutive cycles                           |

| [*]                                                                    | Zero or more cycles are skipped                                         |

| [+]                                                                    | One or more cycles are skipped                                          |

| [i]                                                                    | i cycles are skipped                                                    |

| [ij]                                                                   | at least i cycles, but no more than j cycles, are skipped               |

| [i]                                                                    | At least i cycles are skipped                                           |

| [i]                                                                    | At most i cycles are skipped                                            |

| b[=i]                                                                  | A sub-sequence in which b occurs the number of times indicated          |

| b[>i]<br>b[ <k]< td=""><td>(not necessarily consecutively).</td></k]<> | (not necessarily consecutively).                                        |

| b[>=i]                                                                 |                                                                         |

| b[<=i]                                                                 |                                                                         |

| b[>i, <j]< td=""><td></td></j]<>                                       |                                                                         |

| b[>=i, <j]< td=""><td></td></j]<>                                      |                                                                         |

| b[>i,<=j]<br>b[>=i,<=j]                                                |                                                                         |

| ひ[/-エ,<-]]                                                             |                                                                         |

**TABLE 3. Subsequence Operators**

If Q represents a sequence, then the following are possible operators:

| Operator | Name                | Description                 |

|----------|---------------------|-----------------------------|

| Q[*]     | Any repetition      | Q occurs 0 or more times.   |

| Q[+]     | Positive repetition | Q occurs one or more times. |

| Q[i]     | Exact repetition    | Q occurs exactly i times.   |

| Operator | Name                | Description                                           |

|----------|---------------------|-------------------------------------------------------|

| Q[ij]    | Range repetition    | Q occurs at least i times, but not more than j times. |

| Q[i]     | At least repetition | Q occurs i or more times.                             |

| Q[i]     | At most repetition  | Q occurs no more than i times.                        |

#### 5.3.3 Built-in Functions

Sugar has several built-in functions, which are described below:

**fell**(expr) is true if expr is 0, and was 1 on the previous cycle.

rose(expr) is true if expr is 1, and was 0 on the previous cycle.

$\mathbf{prev}(\mathbf{x})$  is true if  $\mathbf{x}$  was true in the previous cycle.

**next** (x) is true if x is true in the next formula. This construct can not be used in rules, since rules shouldn't relate to the future. It can be used when defining auxiliary variables and behaviors, as will be explained in section 4.7.

# 5.4 Writing a Rules File

FoCs is rule-oriented. A rule is the basic component for which FoCs can generate a checker. A rule defines a group of related properties, represented as Sugar formulas, which are translated into one checker. (It is possible to translate multiple rules into one checker). It is also possible to define auxiliary variables and state machines by defining Finite State Machines (FSMs), as explained in section 5.5, and to include macro definitions, as explained in Section 5.4.3.

### 5.4.1 The Structure of the Rules File

Before beginning, you should plan the hierarchical structure of the rules files and how it will best represent the design properties.

A rules file consists of a set of rules, where each rule may include one or more formulas (at least one formula), macros, and FSM statements. A formula describes a property of the design at hand. Macros and FSM statements can be used to define auxiliary variables and state machines that ease expressing properties.

The structure of the rules file is:

The rule names are any meaningful names that begin with a letter and consist of letters, digits, or underscores. The textual description is text delimited within double quotes that describes the property in informal English. The formal description is a Sugar expression. The syntax of the Sugar language, FSM statements, and macros are defined in the following sections of this chapter.

The rule syntax is as follows:

```

rule name {

<Macro definitions (#define,%if,%for)> (optional)

<FSM statements (var, assign, define, module, instance)>

(optional)

formula "textual description" { Sugar-formula }

formula "textual description" { Sugar-formula }

...

```

}

A rule must contain at least one formula. All the other parts are optional. The order of statements in a rule is unimportant, and each type of a statement may appear several times. It is important to fill in the textual description of formulas. It is possible to have this description displayed when the checker generated from this formula detects an error during simulation.

### 5.4.2 A Methodology for Writing Rules Files

When designing a rules file, you should consider both readability and efficiency issues.

- Go over the block outputs, one by one, and write (in English) all the things you can check on that signal—its shape, its valid values, its relations with other signals, etc.

- From a methodological standpoint, it is useful to divide rules into 3 levels: Level 1: Every signal to itself (e.g., pulse, constant zero...).

- Level 2: Relations between signals at the same interface (e.g., request, ack).

- Level 3: Cross-design signals or very complex rules.

- Write an English explanation for every rule, specifying exactly what you are checking. If you have an English documentation of the rules—use the same description for both, and write the rule names in the relevant places in the documentation as well.

- Keep your rules file as readable and simple as possible—you'll return to them when you don't expect it! Using advanced mechanisms such as "module" and "% for" is not always the most readable approach.

- Write your rules short as well—A long/complex rule can be easily fragmented. It's good for generic reasons and also for readability.

- Partitioning your rules into several files will make it easier to work with when you have dozens of them.

- Use special naming conventions for auxiliary variables defined by FSM statements to distinguish them from signals of the design.

### 5.4.3 Comments, Macros, and Preprocessing Directing

There are two types of comments in environment description files:

- 1) Text beginning with "--" and ending at the end of line.

- 2) Text beginning with "/\*" and ending with "\*/".

Comment text is ignored by FoCs A comment can be inserted anywhere a space is legal (except in text strings).

Before processing the environment description files, FoCs calls a standard preprocessor, cpp, to filter these files. The mechanisms provided by cpp can be used to facilitate the development of environment models. The most useful mechanisms are macros, conditional compilation (#ifdef, #if, #endif, etc.) and #include. See "man cpp" on your unix system for more details.

FoCs provides additional preprocessing abilities in addition to cpp. These are the **%for** and **%if** constructs described below.

#### %for

The **%for** construct replicates a piece of text a number of times, with the possibility of each replication receiving a parameter. The syntax of the **%for** construct is as follows:

```

%for <var> in <exprl> ... <expr2> do

...

%end

or:

%for <var> in <exprl> ... <expr2> step <expr3> do

...

%end

-- step can be negative

or:

%for <var> in { <item> , <item> , ... , <item> } do

...

%end

```

where <item> is either a number, an identifier, or a string in double-quotes. When the value of an item is substituted into the loop body (see below), the double quotes will stripped.

Be aware that **%for** generates a formula for each iteration of the **%for** loop.

In the first case, the text inside the **%for-%end** pairs will be replicated expr2-expr1+1 times (assuming that expr2>=expr1). In the second case, the text will be replicated (|expr2-expr1|+1)/expr3 times (if both |expr2-expr1| and expr3 are positive, or both are negative). In the third case, the text will be replicated according to the number of items in the list.

During each replication of the text, the loop variable value can be substituted into the text as follows. Suppose the loop variable is called "ii". Then, the current value of the loop variable can be accessed from the loop body using the following three methods:

The current value of the loop variable can be accessed using simply "ii" if "ii" is a separate token in the text. For instance:

```

define aa(ii) := ii > 2;

%end

is equivalent to:

define aa(0) := 0 > 2;

define aa(1) := 1 > 2;

define aa(2) := 2 > 2;

define aa(3) := 3 > 2;

If "ii" is part of an identifier, it can be accessed using %{ii} as follows:

%for ii in 0..3 do

define aa%{ii} := ii > 2;

%end

is equivalent to:

define aa0 := 0 > 2;

define aal := 1 > 2;

define aa2 := 2 > 2;

define aa3 := 3 > 2;

If "ii" needs to be used as part of an expression, it can be accessed using %{<expr>}

as follows:

```

%for ii in 1..4 do

%for ii in 0..3 do

```

define aa%{ii-1} := %{ii-1} > 2;

%end

is equivalent to:

define aa0 := 0 > 2;

define aa1 := 1 > 2;

define aa2 := 2 > 2;

define aa3 := 3 > 2;

```

The following operators can be used in pre-processor expressions:

```

= != < > <= >= - + * / %

```

In the current version, operators work only on numeric values (i.e., it's OK to write the following):

```

%for i in 0..3 do

i %if i != 3 %then + %end

%end

```

But it is not possible to write

The **%if** construct is similar to the #if construct of the cpp preprocessor. However, **%if** must be used when <expr> refers to variables defined in an encapsulating **%for**. The syntax of the **%if** construct is as follows:

```

%if <expr> %then

...

%end

or:

%if <expr> %then

...

```

```

%else

...

%end

```

### 5.5 State Machines

Although Sugar increases expressiveness capabilities, there are still properties that cannot be expressed, and others that are too complicated to formulate. **State machines** may provide solutions in many of these cases. The state machine records events that occur in the design under verification. Formulas can then refer to these events by accessing the state machine's internal state. State machines do not affect the design because information flows only from the design to the state machine. In this section, we describe the special statements for writing state machines.

For example, assume that a queue of depth k reads data on one side and writes it on the other side. Assume that we want to prove that the queue never contains more than k data items. Formulation of this property in Sugar is difficult, but it becomes easy with a satellite. An up/down counter is defined, with a range of 0 to k, and which is incremented on reads and decremented on writes.

It is now necessary only to verify that the counter never exceeds k.We can use the same counter to check for an underflow; its value should never be less than 0.

Some properties might have become easier if one could talk about past events. Assume we want to state that "if p occurs, then at that time q should be active since the last occurrence of r." We can define a state-machine inside the rule that will help us express this property as follows:

```

rule if_p_then_q_since_r{

var state:boolean; -- defining a boolean variable state

assign init(state):= 0 -- initialising the variable

assign next(state):= -- assigning a value to state in the next

case -- cycle

!q:0; -- if q is false then next(state) is false

q & r:1; -- if q and r are true then next(state) is true

```

### 5.5.1 Additional Expressions Used in State Machines

State machines may include boolean expressions, if-then-else expressions, and case expressions.

#### 5.5.1.1 if and case Expressions

There are two constructs which express a choice between two or more expressions. They are the **case** and **if** expressions, described below.

The **case** expression has the following format:

```

case

condition1 : expr1 ;

condition2 : expr2 ;

...

else : exprn ;

esac

```

A **case** expression is evaluated as follows: condition1 is evaluated first. If it is true, expr1 is returned. Otherwise, condition2 is evaluated. If it is true, expr2 is returned, and so forth. The **else** part is essential FoCs—in order to define the behavior as deterministic, it is advisable to the behavior as the default entry if you are not certain that the other conditions cover all the cases. Falling through the end of a case statement may have unpredictable results. Notice that from the description of the case expression above, it follows that an earlier condition takes precedence over a later

one. That is, if two conditions are true, the first takes precedence.

The **if** expression is shorthand for a case with two entries, and it has the following format:

```

if condition then exprA else exprB endif

```

In the above **if** expression, *exprA* is returned if *condition* is true, and *exprB* is returned if *condition* is false.

#### 5.5.2 Statements for State Machines – FSM Statements

The following statements are required for defining auxiliary variables writing state machines:

var

define

assign next, assign init

#### module, instance

The order of the statements is unimportant. We now describe each of these statements in detail.

#### 5.5.2.1 The var Statement

A **var** statement declares auxiliary variables required for the state-machine and the formulas in a rule, and has the following format:

```

var name, name, ...: type; name, name, ...: type; ...

The type can be one of the following:

boolean

{ enum1, enum2, ... }

number1 .. number2 (range between integers)

For instance, the following are legal var statements:

var request, acknowledge: boolean;

var state: {idle, reading, writing, hold};

```

var counter: {0, 1, 2, 3};

```

var length: 3 .. 15;

```

The first statement declares two variables, "request" and "acknowledge", to be of type boolean. The second statement declares a variable called "state" which can take on one of four enumerated values: "idle", "reading", "writing", or "hold". The third statement declares a variable called "counter" which can take on the values 0, 1, 2, or 3. The fourth statement declares a variable called "length" which can take on any of the values between 3 and 15, inclusive.

We can also define arrays using the var statement:

An array of state variables is defined as follows:

```

var name ( index1 .. index2 ) : type ;

```

It actually defines (|index2-index1|+1) state variables named name(index1), ..., name(index2), where index1 can be either greater or less than index2.

#### Examples:

```

var

addr(0..7) : boolean; -- 8 boolean variables, addr(0), addr(1), ... ,

```

A **var** statement only declares auxiliary variables. The **assign** and **define** statements, described below, define the behavior of these variables. FoCs does not allow non-determinism—the value of a variable at each cycle should be explicitly defined using the assign and define statements.

### 5.5.2.2 The Assign Statement

An **assign** statement assigns a value to a state variable declared with a **var** statement. It has one of the following formats:

```

assign init(name) := expression;

assign next(name) := expression;

assign name := expression;

```

The first statement assigns an initial value to an auxiliary variable. The second statement defines the value of an auxiliary variable in the next cycle. The third statement assigns a value to a variable in the current cycle.

The following are examples of legal **assign** statements:

```

assign init(state) := idle;

assign next(state) :=

case

reset : idle1;

state=idle & !start : idle;

state=idle & start : busy;

state=busy & done : { idle };

else : state;

esac

```

The keyword **assign** may be omitted for the second and following consecutive **assign** statements. Thus, the following:

#### 5.5.2.3 The Define Statement

A **define** statement is used to give a name to a frequently-used expression, much like a macro in other programming or hardware description languages. The **define** statement has the following format:

```

define name := expression;

```

For instance, the following are legal **define** statements:

```

define adef := (q | r) & (t | v);

define bb(0) := q & t; cc := 3;

```

As with the **assign** statement, the keyword **define** may be omitted in second and

following consecutive **define** statements.

assign must refer to a variable defined with var.

**define** must NOT refer to a variable defined with var.

#### 5.5.2.4 The Module and Instance Statements

A **module** statement is used to group together the statements of a state machine. Instead of writing them directly inside the rule, this module can be instantiated inside the rule using the **instance** statement.

For instance, the following is a legal **module** statement:

```

module since(e1,e2)(e1_since_e2)

{

var state:boolean;

assign next(state):=

case

!e1 :0;

e1 &e2 :1;

else :state;

esac;

define e1_since_e2 :=(e1 &e2)|(e1 &state);

}

```

This module can be defined in the rules file (outside a rule) and instantiated and used in a rule as follows:

```

rule if_p_then_q_since_r{

instance il :since(q,r)(q_since_r);

formula

"If p occurs, then at that time q should be active since the last occurrence of r"

{always (p ->q_since_r)}

}

```

A module statement is used to define a module which can be instantiated a number of times, as in hardware description languages. It has the following format:

```

module module_name ( inputs ) ( outputs )

{

statement;

statement;

...

}

```

where *inputs* is a list of formal parameters passed to the module, *outputs* is a list of formal parameters produced by the module, and *statements* is any sequence of **var**, **assign**, **define** and **instance** statements. The input/output parameters can be thought of as input/output signals. Input parameters are produced elsewhere, and they drive the module, while output parameters are produced by the module itself and can be used elsewhere. A signal that appears as an output parameter of a module must be defined and assigned a value in that module (**var** or **define** or **instance** output). If a signal that appears as an input parameter of a module is not used in that module, FoCs will issue a warning.

Modules cannot be declared inside rules or other modules but they can be used (instantiated) by rules and other modules.

A **module** statement is only a definition—it has no effect until it is instantiated (called). The **instance** statement instantiates a module using the following format:

```

instance instance_name : module_name ( inputs ) ( outputs );

```

#### where:

instance\_name is the name of the specific instance (one module can be multiply instantiated)

module\_name is the name of the module being instantiated inputs is a list of expressions passed as inputs to this instance outputs is a list of output parameters, actually connecting the instance outputs to real signals of the design. An instance name is optional.

### 5.5.2.5 Advanced Operations on Arrays

It is often convenient to apply operations to entire arrays or to ranges of indices. Boolean arrays are the only arrays supported by FoCs. These arrays are commonly used for buses and bundles.

#### 5.5.2.6 Defining Arrays

An array of state variables is defined as follows:

```

var name ( index1 .. index2 ) : boolean ;

An array can also be defined with a define statement:

define name( index1 .. index2 ) := <expr>;

For example:

define masked sig(0..3) := sig(0..3) & mask(0..3);

```

### 5.5.2.7 Operations on Arrays

#### Reference:

The simplest operation on an array is a reference to a bit or a bit range. One bit of an array is referenced as  $array\_name(N)$  where N is a constant. A range of bits is referenced as  $array\_name(M..N)$ . It is always necessary to specify the bit range when referencing an array.

Other operations that can be used with arrays are:

```

:= != if case & | ^{1}! -> <->

Example: aa(0..7) := if bb(0..2)=cc(0..2) then dd(0..7) else ee(1..8) endif;

```

In boolean operands, both operands must be of the same width (unless one of them is constant). The result will have the same width as the vector operands.

```

Example: v(0..7) := x(0..7) \& y(0..7) | !z(0..7);

```

```

Relational: < > <= >=

```

Both operands must be of the same width (unless one of them is constant). The result will be a scalar boolean value.

```

Examples: c := v(0..7) > x(0..7); d := v(0..7) <= 16;

Arithmetic (unsigned): + - *

```

Both operands must be of the same width (unless one of them is constant). The result will have the same width as the vector operands.

#### Examples:

```

define cc1(0..7) := aa(0..7) + bb(0..7);

cc2(0..7) := aa(0..7) + 1;

cc3(0..7) := 10 * aa(0..7);

```

In order not to lose the most significant bits of the result, pad the operands with zeroes on the left. For example:

```

define aa(0..7) := zeroes(4) ++ bb(0..3) * zeroes(4) ++ cc(0..3);

co++sum(0..7) := 0++a(0..7) + 0++b(0..7);

```

(++ is the concatenation operator, described below. zeroes(4) is a vector of four zeroes)

```

Shift: >> <<

```

The first operand must be a boolean vector and the second operand must be an integer constant or variable. The result is a boolean vector of the same width as the first operand. These operations perform the logical shift (i.e., vacated bit positions are filled with zeroes).

#### Examples:

### Conversion of Bit Vectors to Integers and Vice Versa

The following are built-in functions for converting bit vectors to integers and vice versa.

#### Bit vector to integer:

```

bvtoi( a_vector )

Integer to bit vector:

itobv( an_integer )

Example:

always ( Addr(0..31) = itobv(256) -> bvtoi(data(0..3)) = 9 )

```

Note that constant integers are converted to bit vectors implicitly. There is no need to apply itobv.

#### **Construction of Bit Vectors from Bits or Sub-vectors**

The concatenation operator (++) is used to make bit vectors out of bits or smaller vectors:

```

expr ++ expr