How to Get the Most Out Of Your Embedded Hardware While Keeping Development Time to a Minimum

A Comparison of Two architectures and Two IDEs for Atmel AVR 8-bit Microcontrollers

**NICLAS ARNDT**

# How to Get the Most out of Your Embedded Hardware while Keeping Development Time to a Minimum

A Comparison of Two Architectures and Two IDEs for Atmel AVR 8-bit Microcontrollers

# Niclas Arndt

Bachelor Thesis, Information Technology

## **Abstract**

This thesis aims to answer a number of basic questions about microcontroller development:

- What's the potential for writing more efficient program code and is it worth the effort? How could it be done?

Could the presumed trade-off between code space and development time be overcome?

- Which microcontroller hardware architecture should you choose?

- Which IDE (development ecosystem) should you choose?

This is an investigation of the above, using separate sets of incremental code changes (improvements) to a simple serial port communication test program. Two generations of Atmel 8-bit AVR microcontrollers (ATmega and ATxmega) and two conceptually different IDEs (BASCOM-AVR and Atmel Studio 6.1) are chosen for the comparison.

The benefits of producing smaller and/or faster code is the ability to use smaller (cheaper) devices and reduce power consumption. A number of techniques for manual program optimization are used and presented, showing that it's the developer skills and the IDE driver library concept and quality that mainly affect code quality and development time, rather than high code quality and low development time being mutually exclusive.

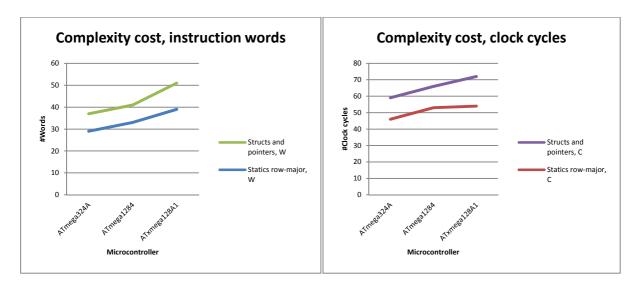

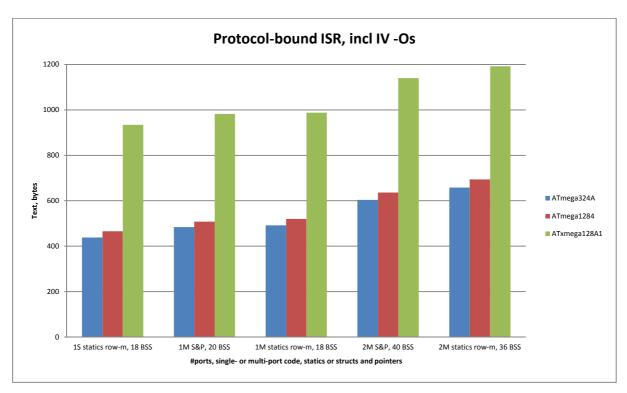

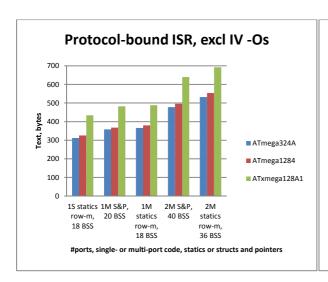

The investigation shows that the complexity costs incurred by using memory-wise bigger and more powerful devices with more features and peripheral module instances are surprisingly big. This is mostly seen in the IV table space (many and advanced peripherals), ISR prologue and epilogue (memory size above 64k words), and program code size (configuration and initialization of peripherals).

The 8-bit AVR limitation of having only three memory pointers is found to have consequences for the programming model, making it important to avoid keeping several concurrent memory pointers, so that the compiler doesn't have to move register data around. This means that the ATxmega probably can't reap the full benefit of its uniform peripheral module memory layout and the ensuing struct-based addressing model.

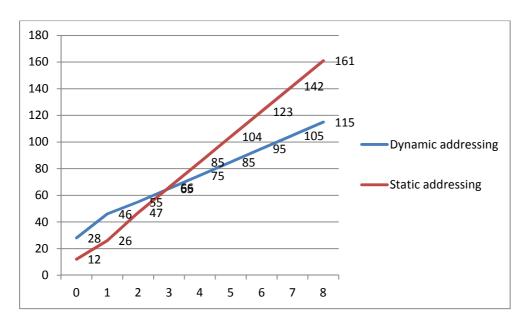

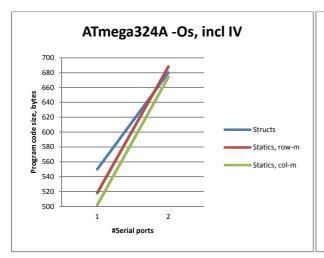

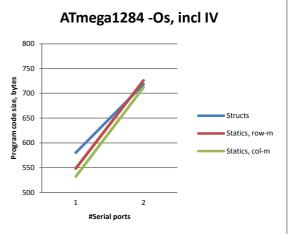

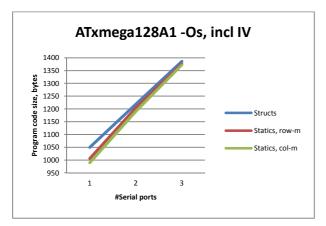

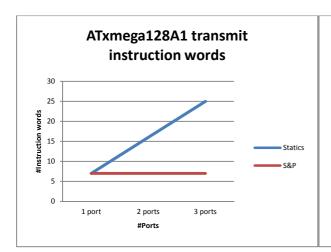

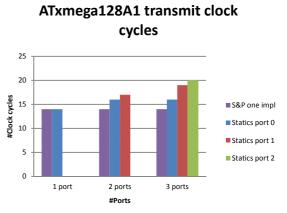

The test results show that a mixed addressing model should be used for 8-bit AVR ATxmega, in which "static" (absolute) addressing is better at one (serial port) instance, at three or more the "structs and pointers" addressing is preferable, and at two it's a draw. This fact is not dependent on the three pointer limitation, but is likely to be strengthened by it.

As a mixed addressing model is necessary for efficient programming, it is clear that the driver library must reflect this, either via alternative implementations or by specifying "interfaces" that the (custom) driver must implement if abstraction to higher-level application code is desired. A GUI-based tool for driver code generation based on developer input is therefore suggested.

The translation from peripheral instance number to base address so far used by BASCOM-AVR for ATxmega is expensive, which resulted in a suggestion for a HW-based look-up table that would generally reduce both code size and clock cycle count and possibly enable a common accessing model for ATmega, ATxmega, and ARM.

In the IDE evaluation, both alternatives were very appreciated. BASCOM-AVR is found to be a fine productivity-enhancement tool due to its large number of built-in commands for the most commonly used peripherals. Atmel Studio 6.1 suffers greatly in this area from its ill-favored ASF driver library. For developers familiar with the AVRs, the powerful avrgcc optimizing compiler and integrated debugger still make it worthwhile adapting application note code and datasheet information, at a significant development time penalty compared to BASCOM-AVR.

Regarding ATmega vs. ATxmega, it was decided that both have its place, due to differences in feature sets and number of peripheral instances. ATxmega seems more competitively priced compared to ATmega, but incurs a complexity cost in terms of code size and clock cycles. When it's a draw, ATmega should be chosen.

# **Table of contents**

| 1 | Intro | oduction                                          | 1  |

|---|-------|---------------------------------------------------|----|

|   | 1.1   | Outline                                           | 1  |

|   | 1.2   | General background                                | 2  |

|   | 1.3   | Commercial background                             | 3  |

|   | 1.4   | Problem description                               | 3  |

|   | 1.5   | Purpose and goal                                  | 5  |

|   | 1.6   | Delimitations                                     | 5  |

|   | 1.7   | Terminology                                       | 6  |

|   | 1.8   | References                                        | 6  |

|   | 1.9   | Other considerations                              | 7  |

| 2 | Met   | hod                                               | 8  |

|   | 2.1   | Method description                                | 8  |

|   | 2.2   | Test equipment and setup                          | 8  |

| 3 | The   | Atmel AVR 8-bit microcontrollers                  | 11 |

|   | 3.1   | Introduction                                      | 11 |

|   | 3.2   | Architecture details                              | 12 |

|   | 3.3   | HW design and programming considerations          | 15 |

|   | 3.4   | (Other) differences between ATmega and ATxmega    | 16 |

| 4 | Pres  | entation of the IDEs                              | 19 |

|   | 4.1   | BASCOM-AVR                                        | 19 |

|   | 4.2   | Atmel Studio 6                                    | 21 |

| 5 | BAS   | COM-AVR analysis                                  | 25 |

|   | 5.1   | Serial communication analysis test log            | 25 |

|   | 5.2   | BASCOM-AVR summary #1                             | 32 |

|   | 5.3   | Why is the ATxmega code so much bigger?           | 34 |

|   | 5.4   | Generalization                                    | 40 |

| 6 | Atm   | el Studio 6.1 2562 using ASF3.13.1 code analysis  | 42 |

|   | 6.1   | Optimization primer                               | 42 |

|   | 6.2   | ATmega324A analysis                               | 42 |

|   | 6.3   | ATxmega128A1 analysis                             | 50 |

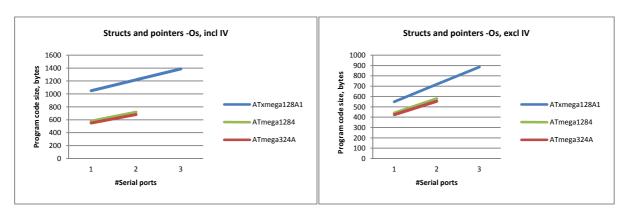

|   | 6.4   | Scaling ATmega 324A, ATmega1284, and ATxmega128A1 | 63 |

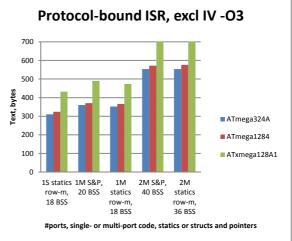

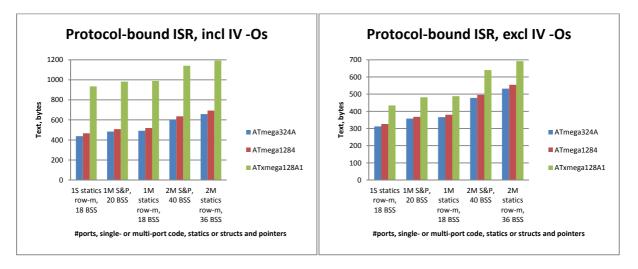

|   | 6.5   | Protocol-bound ISR scaling (AS3j & AS3k)          | 73 |

|    | 6.6 | ATmega324A structs and pointers two-port USART ISR placed in IV   | 75  |

|----|-----|-------------------------------------------------------------------|-----|

| 7  | Con | npilation and discussion of the test results                      | 76  |

|    | 7.1 | Static vs. dynamic addressing (BASCOM-AVR) or S&P (AVR-GCC C)     | 76  |

|    | 7.2 | Hardware-related complexity costs                                 | 78  |

|    | 7.3 | Software-related costs                                            | 80  |

|    | 7.4 | Programmer skills                                                 | 83  |

|    | 7.5 | ATmega or ATxmega or both?                                        | 84  |

|    | 7.6 | IDE comparison                                                    | 86  |

|    | 7.7 | Suggestions for future work                                       | 88  |

| 8  | Sun | nmary                                                             | 89  |

|    | 8.1 | IDE choice                                                        | 89  |

|    | 8.2 | HW selection                                                      | 89  |

|    | 8.3 | The programming test results and the conclusions I draw from them | 90  |

|    | 8.4 | On efficient programming                                          | 90  |

| 9  | Ref | erences                                                           | 93  |

| 10 | ) Δ | ppendix A                                                         | 102 |

|    | A.1 | Response from the IDE companies                                   | 102 |

|    | A.2 | Additional sources                                                | 104 |

|    | A.3 | How to disassemble                                                | 107 |

|    | A.4 | Atmel application notes on efficient programming                  | 108 |

|    | A.5 | IDE-specific additional information                               | 112 |

|    | A.6 | BASCOM incremental code pieces                                    | 117 |

|    | A.7 | Atmel studio 6.1 and ASF screen dumps                             | 128 |

|    | A.8 | Atmel Studio #ports scaling                                       | 132 |

|    | A.9 | ATmega324A structs and pointers two-port USART ISR placed in IV   | 139 |

# 1 Introduction

## 1.1 Outline

This is a long thesis that covers a wide area. The reader might want to choose the parts of most interest and here I briefly describe the contents and provide reading advice.

If you want to digest this work as quickly as possible, it is recommended that you browse chapter 1, read section 3.4.1 and then read chapters 7 and 8. Chapters 3, 5, and 6 can in this case be consulted for details about particular tests and their results.

- Chapter 1 is the introduction.

- Chapter 2 describes the method and the test setup. It briefly explains and illustrates how the

tests were performed. An experienced microcontroller programmer could probably skip this

part.

- Chapter 3 presents the AVR 8-bit microcontroller architecture, differences between ATmega and ATxmega, and programming-related properties relevant to this thesis. It is very detailed with regards to register design, I/O and peripheral device registers, internal memories, and Atmel's advice on efficient programming. The alternative peripheral module register layout that is very important to this paper is explained in 3.4.1. I recommend every reader to read this last piece, but if you are seriously interested in efficient AVR programming you must get a solid understanding of this entire chapter.

- Chapter 4 is an overview of the two IDEs, describing their most important features and qualities. If you are mostly interested in their consequences you can find this in chapter 7.

- Chapters 5 and 6 each contain one separate IDE-specific analysis and discussion of the findings. Written as log books that document my progress, they are very detailed and include personal remarks indicating my reactions to the results. These chapters provide the empirical groundwork that also explains or "proves" my findings. You can read it as a whole or read the parts that lead up to the results you found interesting in chapter 7.

- Chapter 7 compiles and discusses the results, which leads up to a number of conclusions. All aspects considered relevant are treated here. A must-read for this paper.

- Chapter 8 is a summary of the conclusions. This is where the different lines of investigation end in IDE choice, HW selection, results from the programming tests, and conclusions on efficient programming.

- Chapter 9 holds the table of references.

- Various additional information, sources, and incremental pieces of code have been put in appendix A.

- The source code and disassemblies reside in the external appendix B due to their size. Please contact the author for a copy.

# 1.2 General background

For many years, I have been doing microcontroller (a.k.a. embedded systems) prototyping as a hobby. I have now reached the level at which I consider turning my hobby into a business and one of many questions is which platform I should choose in terms of

- hardware (HW) architecture and

- Integrated Development Environment (IDE).

I also want to get a deeper understanding of (microcontroller) programming; a feeling for how much computer programs can be improved in terms of performance and compiled code size and how further studies in this area could be designed:

- Should I use a generic programming style or are there differences in IDE and HW architecture that motivate different approaches?

- How good are the predefined software (SW) libraries and IDE commands with respect to compiled code size, performance, and development time?

- Should I use high-level language only or combine it with inline assembly or custom assembly functions?

On a similar note, as the great yearly increase in computer HW performance that we had grown accustomed to seems to have been slowed down, I believe that there is reason to rekindle our interest in SW performance:

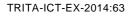

Figure 1: The general computer HW performance trend (relative performance vs. year)

This illustrative graph is representative of a number of real charts in "The Future of Computing Performance: Game Over or Next Level?" (1) <sup>1</sup>. In many of the most important HW metrics, the increase in performance has slowed down:

- Integer and floating-point performance

- Power dissipation and clock frequency

<sup>&</sup>lt;sup>1</sup> Free download at http://www.nap.edu/catalog.php?record\_id=12980

So, what ways are there to further increase performance?

"The claimed benefits of high-level languages are now widely accepted. In fact, as computers got faster, modern programming languages added more and more abstractions. For example, modern languages - such as Java, C#, Ruby, Python, F#, PHP, and Javascript - provide such features as automatic memory management, object orientation, static typing, dynamic typing, and referential transparency, all of which ease the programming task. They do that often at a performance cost, but companies chose these languages to improve the correctness and functionality of their software, which they valued more than performance mainly because the progress of Moore's law hid the costs of abstraction." (1) <sup>1</sup> p107

"Future growth in computing performance will have to come from software parallelism that can exploit hardware parallelism. Programs will need to be expressed by dividing work into multiple computations that execute on separate processors and that communicate infrequently or, better yet, not at all."  $(1)^{1}$  p105

I too see parallelism as a very important area in software development, but I also see great potential in more efficient programming. 8-bit microcontrollers are simple and enable high-level development from which the machine code consequences can be analyzed directly. I'm hoping that such an analysis will give insights that are also applicable to PC- and server-class programming.

# 1.3 Commercial background

I am currently developing a series of (uninterruptible) power supply products. They have quite modest requirements in terms of performance and program memory size, but I still want to make an informed platform decision and lay a solid code foundation for what will be common functionality:

- I believe that writing good code once is cheaper in the long run.

- If the code size reduction is substantial, it will enable me to use smaller (and cheaper) devices.

- According to Johnny Burlin at IAR Systems (one of the world-leading compiler makers for embedded processors) (2), the best way to reduce power consumption is to speed-optimize the code so that the microcontroller gets the job done as quickly as possible and then goes into sleep mode. In this paper I won't go into power efficiency, but it is relevant for batterypowered devices.

# 1.4 Problem description

My previous designs are based on Atmel's AVR 8-bit microcontrollers, more specifically the ATmega architecture (3)  $^2$ , with the BASCOM-AVR IDE (4)  $^3$ . Its syntax is close to Visual Basic 6, here called VB.

I have now started to use the more powerful ATxmega series (5) <sup>4</sup> and I am considering a switch to Atmel's IDE, Atmel Studio 6 (6) <sup>5</sup>. The main reason for this would be the optimizing compiler, integrated debugger, and being able to use the industry-standard C or C++ that are more easily portable to other HW. It also has support for Atmel's ARM-based products and a claimed easy transition from ATxmega to ARM due to the common Atmel Software Foundation (ASF) (7) <sup>6</sup> driver library.

<sup>&</sup>lt;sup>2</sup> http://www.atmel.com/products/microcontrollers/avr/megaavr.aspx

http://www.mcselec.com/

http://www.atmel.com/products/microcontrollers/avr/avr\_xmega.aspx

<sup>&</sup>lt;sup>5</sup> http://www.atmel.se/microsite/atmel\_studio6/

<sup>&</sup>lt;sup>6</sup> http://www.atmel.com/tools/avrsoftwareframework.aspx?tab=overview

I decided that a simple feature comparison wouldn't answer all my questions. Instead, I will implement the same basic test program (a serial port communication routine) for each of the HW/IDE combinations below, with a number of incremental code modifications in order to find the optimum programming style in each situation.

I will try to see how much I can improve the generic high-level code (mostly in terms of compiled code size, but in some cases also clock cycle count and RAM usage) and then how much further I can reduce it by replacing parts with inline assembly. As a last step, I will see how much can be saved by swapping the protocol-unbound design for a protocol-bound implementation.

| BASCOM AVR VB-only                                              |

|-----------------------------------------------------------------|

| BASCOM AVR VB + inline assembly                                 |

| BASCOM AVR VB + inline assembly, protocol-bound implementation  |

| Atmel Studio C-only                                             |

| Atmel Studio C + inline assembly                                |

| Atmel Studio C + inline assembly, protocol-bound implementation |

Table 1: Test overview, for ATmega and ATxmega respectively

Below are the main questions that will guide my work. As the investigation is open-ended and the further direction of the analysis is decided during its execution, the summary and conclusions will be shaped by the actual findings, not necessarily following this structure.

#### Software-related:

- How much can you improve your code? Is it worth the time and effort?

- High-level language only

- With inline assembly (or custom assembly functions)

- How do the two IDEs (BASCOM-AVR 2.0.7.6 and Atmel Studio 6.1) compare?

- Ease of use

- o Productivity-enhancement tools (software libraries / built-in commands)

- Efficiency / optimization of compiled code

- Simulation and debugging possibilities

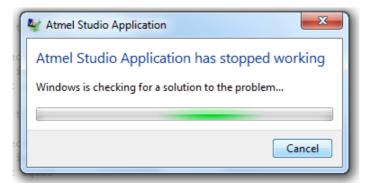

- SW stability

- Code reusability and portability to other device types or brands

- Coverage

- HW architectures (including easy transition between different HW)

- SW longevity (have the version changes been smooth?)

- User forum usefulness

- What are the differences between developing in BASCOM VB and AVR GCC C code (using their respective IDE)?

## Hardware-related:

- Should you strive to migrate to the newer and more feature-rich ATxmega?

- Features

- Complexity

- Maturity

- o New programming model and its effect on code size and clock cycle count

## 1.5 Purpose and goal

This thesis has the following purpose:

- Evaluate two microcontroller IDEs and two HW architectures for a decision about the platform for my future commercial products.

- Investigate the area of efficient microcontroller programming:

- Learn how big is the potential for writing smaller or faster computer programs.

- o Could the presumed code space / development time trade-off be overcome?

- O Understand to what extent the programming style should be adapted to IDE and HW, how to balance the development time savings to the cost of the abstractions added by generic libraries / commands, and how much inline assembly should be used.

- Get an initial picture of how further studies in this area could be designed.

In other words: To search for a way to get the most out of my embedded hardware while keeping development time to a minimum.

#### 1.6 Delimitations

The thesis title is chosen for two reasons: it captures the essence of the thesis and it is believed to catch the reader's interest. It is however too big a topic to be properly addressed by a bachelor thesis. In this respect, this work aims to give a fundamental understanding of what drives (microcontroller) program size and runtime.

It seems that many companies replace their old architecture with 32-bit ARM. Maybe this is what I too will choose in the end. However, I decided that a comparison between BASCOM-AVR on 8-bit Atmel AVR ATmega and IDE *ABC* on brand *XYZ* 32-bit ARM wouldn't be meaningful, as so many things would be different that not many generalizations could be made. By choosing AVR ATxmega and Atmel Studio IDE as the alternatives, real comparisons are possible.

Development time and execution time might be difficult to actually measure. For this reason, development time might have to be a subjective "feeling" of the effort required and execution time might have to be measured by counting microcontroller clock cycles for the instructions in a disassembly of the compiled code. I chose to focus on compiled program size.

With the invention of smart phones, surf pads, and so on, it could be argued that many embedded systems are now so complex and versatile that developing them requires an operating system, high-level languages, generic drivers, and lots of abstraction. I don't oppose to this view on a part of the embedded market, but my designs (like many other microcontroller systems) are fairly simple one-task devices, so I will only consider such designs in this thesis.

# 1.7 Terminology

I use "IDE" (Integrated Development Environment) in the sense of development ecosystem - not only the GUI or front end.

Some of the terms I use in this thesis are partly my own:

- "Static" or "absolute" addressing: The address (typically to a peripheral IO register) is hardcoded. This should not be confused with the C language attribute "static".

- "Dynamic" addressing: I came to use this expression when analyzing the BASCOM-AVR ATxmega code that translates a port number 0-7 to the corresponding peripheral module base address. This address is then (inside the built-in commands) used in a call to a "structs and pointers" driver routine.

- "Structs and pointers" (S&P): This refers to the new way of addressing peripherals that Atmel introduced with the ATxmega uniform register layout. For each type of peripheral, a struct with all the registers is defined. Its fields implicitly denote an offset or a displacement from the start of the struct (= the base address). The driver is written so that it only exists in one generic version. In the driver function call you include a pointer to the peripheral module's (register group's) base address. The base address is typically placed in the Z pointer and the sub-registers are accessed via LD (load) or LDD (load with displacement) instructions (and ST/STD for storing). The difference between "dynamic" and S&P is that the former takes a port number and the latter an address.

I use the terms "UART" and "USART" in the same sense. (USART = Universal Synchronous and Asynchronous serial Receiver and Transmitter, while UART is only asynchronous.)

After the tests I renamed them, so that there would be a clear structure. This means that in some places (e.g. code comments, paths names, and examples) the old name are still used, but I decided that it doesn't cause any significant confusion.

There are two ways of numbering the "cells" in an array; row-major and column-major. The usual definition can be found here: (8) <sup>7</sup> When you think of an array like this:

the row-major representation in memory is

and the column-major is 0 A 1 B 2 C 3 D

This is a fixed part of the language you are developing in, but in a row-major language like C, you can achieve column-major behavior by swapping row and column in your declaration: When I use the term "column-major", this is what I actually mean.

## 1.8 References

In this thesis I am using Zotero, Vancouver citation style. For the reader's convenience, I generally both provide the reference and a footnote with a URL (web hyperlink) to the document so that it isn't necessary to jump back and forth when reading.

<sup>&</sup>lt;sup>7</sup> http://en.wikipedia.org/wiki/Row-major order

# 1.9 Other considerations

## 1.9.1 IDE company participation and previous connections

Both MCS Electronics (4) <sup>8</sup> (the company behind the BASCOM-AVR IDE) and Atmel (9) <sup>9</sup> were invited to participate and/or comment on this thesis. I leave it to the reader to decide whether I am biased.

The owner of MCS, Mark Alberts, made two comments that can be found in appendix A.1. Prior to this thesis, I already had a friendly professional relationship with Mark Alberts, having shared library code with an application note for an SD memory card driver and moderating its user forum thread at MCS' web site.

Atmel sponsored "my" team in a robot project course last spring and very generously gave all members an ARM development board and debugger afterwards. However, we had severe difficulties with the initial delivery and nearly had to abandon Atmel. We were afterwards asked to provide feedback on the software and shared a strong opinion on the usefulness of their driver library.

At the start of my thesis work, Atmel declined my request for a contact for this thesis (appendix A.1). In February 2014 when my work was almost complete, I contacted Atmel again with an invitation to read and comment on my work, but I did not receive a reply.

## 1.9.2 Environmental aspects / sustainable development

On a large scale, even small improvements in clock cycle count should amount to a significant difference in total power consumption.

# 1.9.3 Gender, ethnic, or religious aspects

Not applicable. The areas of programming types and HW / IDE selection are orthogonal to questions of discrimination based on gender, ethnic belonging, and religious beliefs.

\_

<sup>8</sup> http://www.mcselec.com/

<sup>9</sup> http://www.atmel.com/

# 2 Method

What's the best way to compare two IDEs or HW architectures? I fear that a feature table with summation of weighted scores wouldn't capture the real qualities that in my experience become clear only after a period of actual use.

Considering that I also want to compare programming styles, I decided that the center of this thesis should be the incremental code changes on each platform. By focusing on a specific test program and going as deep into this topic as possible, I believe that I will implicitly also get a reasonably good picture of the IDEs' ease of use, qualities, and (part of) the two HW architectures.

I decided that the best place to start is the main program loop, which in this application is quite strongly tied to the (serial port) communication with the PC. It controls the program flow, is relatively application-dependent, well delimited, and also involves a specific hardware module (i.e. driver development).

The BASCOM-AVR part is completed before the start of the Atmel Studio 6 part.

# 2.1 Method description

The method used in this thesis is a fairly controlled (dual) set of iterative and incremental experiments. The area (main loop with serial port communication routines) is fixed, but the direction for the incremental changes is determined during the actual testing. When- or wherever I find something of interest, I investigate its cause and consequences, directly influencing the direction of the rest of the testing. The two analysis chapters are separate logs of what I do and find.

This work could be seen as an initial scientific investigation, with a complete set of source code and incremental analyses so that others could repeat and question the actual findings. Perhaps the results could be used as a starting point when formulating a series of tests of all ATmega and ATxmega peripherals or a bigger programming model analysis, but that's for others to consider.

# 2.2 Test equipment and setup

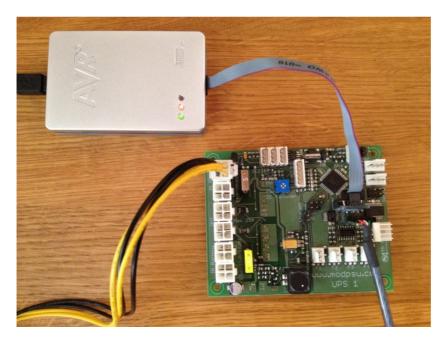

The PC application sends a serial port sequence of binary bytes, starting with 254 followed by message type byte, the actual data byte(s), and terminated by 255. The AVR responds to this with a message of the same kind. The PC will always wait for the response before sending the next message. The AVR will only initiate a conversation to send an error message (which is not part of this work).

The test application implements two messages:

- The PC sends [254, 243, 255] and receives [254, 242, 1, 2, 3, 255]

- The PC sends [254, !=243, ..., 255] and receives [254, 251, 255]

The AVR code should be written for an ATmega324A and an ATxmega128A1 with conditional compilation. The first high-level-only versions are based on a circular buffer that gets its data from the RX interrupt routine for USART. The main program loop calls a sub-routine that polls this buffer and extracts any received data and puts it into a separate array. When the entire message is received, the appropriate response is sent. At the end, a protocol-bound implementation is developed. It might have to be based on inline assembly.

## 2.2.1 Test beds

I used the following microcontroller types:

- ATmegaXX4 (164/A/P/PA, 324/A/P/PA, 644/A/P/PA, and 1284/P)

- o This family supports JTAG debugging.

- ATxmegaA1(U) (64A1/A1U and 128A1/A1U), where "U" indicates that it is a later (bug-fixed) revision that includes a USB module. This USB module is not covered by this thesis.

- o This family supports JTAG and PDI debugging.

Within each type, the main difference lies in the size of the various memories, where the number states the program memory size (324 == 32 kB and 128 == 128 kB program flash EEPROM).

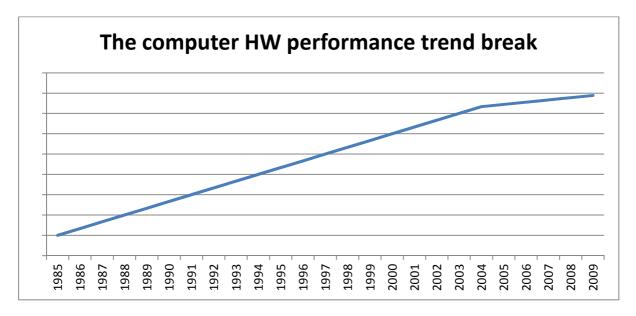

Figure 2: ATmega324A-based board, with two USARTs

Figure 3: ATxmega128A1-based board, with eight USARTs, of which two are used in the tests

## 2.2.1.1 PC application

The PC application is developed in MS Visual Studio 2010 C#.Net, using the SerialPort class. Just getting this to work with static COM port number assignment is very simple. However, nowadays people mostly use USB<->serial bridges. They tend to acquire a new port number each time you plug them in to a different port. For this reason, I added the FTDI .dll and wrapper class for USB bridge identification and found a nice generic COM port listing class on the internet. With them the application automatically connects to the right COM port number.

Figure 4: The two supported messages with response

(Enter the message in the upper textbox, click "Test" and the response is shown in the lower one.)

# 2.2.1.2 How to disassemble

Please see appendix A.3 for information about how to disassemble.

# 3 The Atmel AVR 8-bit microcontrollers

## 3.1 Introduction

The AVR microcontroller is an 8-bit modified Harvard load/store RISC architecture with a 2-stage 1-wide pipeline, which means:

- RISC, Reduced Instruction Set Computing: By using instructions that each does a very small

and specialized task, the clock speed can be increased. This boils down to higher over-all

performance. The other (and older) philosophy is CISC, Complex ISC, which has instructions

that often do very intricate (series of) operations requiring several clock cycles. RISC also

often uses the "load/store architecture" that only operates on memory using specific

instructions, rather than as part of the aforementioned complex instructions. (10) 10

- Harvard architecture: It uses separate buses for program and data memory. (11) <sup>11</sup>

- Modified: It is possible to access the program memory area as read-only data memory (11) (and also update the program memory using a so called boot-loader program).

- 8-bit: It uses data registers 8 data bits wide (but the program memory uses 16 bit or sometimes 2\*16 bit wide instructions).

- 2-stage pipeline: The first stage fetches the next instruction and the second stage executes the current instruction. (12) 12

- 1-wide: It does one operation at a time. (12)

- Microcontroller: A processor with most of the peripherals and memories on the chip.

- AVR: Believed to stand for "Alf-Egil and Vegard's RISC" processor.

AVR originates in the 1992 graduation thesis written by the two Norwegian students Alf-Egil Bogen and Vegard Wollan. In 1997 the AT90S1200 was launched as a microcontroller product by Atmel Corporation. It was one of the first in the industry to use internal flash program memory. (13) <sup>13</sup>

The AT90S series evolved into two product lines with self-explanatory names, ATtiny and ATmega, which a few years later were accompanied by the ATxmega, a major revision or even redesign. They all use the same instruction set (although each model might not support every instruction). A 32-bit AVR was launched in 2006 (14) <sup>14</sup> and starting in 2008, Atmel is now licensing much of the 32-bit ARM-based microcontrollers and microprocessors. (15) <sup>15</sup> This thesis only treats the AVR 8-bit Atmega and ATxmega, henceforth referred to as AVR, ATmega, or ATxmega.

The "AVR and AVR32 - Quick Reference Guide" (16) <sup>16</sup> is slightly outdated (especially as it doesn't contain Atmel's ARM offering), but it still provides a good overview of the AVR products. I could also point to "Microprocessor (MPU) or Microcontroller (MCU)?" (17),<sup>17</sup> which is a marketing presentation that gives a good background to what was considered important in 2013.

<sup>&</sup>lt;sup>10</sup> http://en.wikipedia.org/w/index.php?title=Reduced instruction set computing&oldid=594087688

<sup>11</sup> http://en.wikipedia.org/w/index.php?title=Harvard architecture&oldid=585324105

http://www.atmel.se/Images/Atmel-8331-8-and-16-bit-AVR-Microcontroller-XMEGA-AU\_Manual.pdf

<sup>13</sup> http://www.youtube.com/watch?v=HrydNwAxbcY

http://en.wikipedia.org/w/index.php?title=AVR32&oldid=587706001

<sup>15</sup> http://en.wikipedia.org/w/index.php?title=AT91SAM&oldid=584613739

http://www.atmel.se/Images/doc4064.pdf

<sup>&</sup>lt;sup>17</sup> http://www.atmel.se/Images/MCU vs MPU Article.pdf

## 3.2 Architecture details

## 3.2.1 Registers

AVR has 32 general-purpose eight-bit working registers. The last six can be used as three pairs of 16-bit registers, called X, Y, and Z, e.g. when addressing memory locations. All of these can do pre- or post-incementation, while Y and Z also support positive 6-bit displacement, which is practical when accessing arrays, SW stack, or sub-registers that control a peripheral. Z can be used to read or write flash program and special device settings. The register with the higher number is the most significant.

16 bits equates to a 64 k bytes data memory or a 64 k words program memory addressable space. (AVR program memory is made up of 16-bit instruction words, so 128 kB of program memory can be addressed with 16 bits.) When accessing a location above this, you must use an additional register for the >16 bits:

- RAMPX, RAMPY, or RAMPZ: for the X, Y, or Z register pairs >64k byte (kB) data memory.

- RAMPD: when the instruction includes a 16-bit constant to access >64kB data memory.

- EIND: to do jumps or calls to >64k word program memory.

The SP (Stack Pointer) is a special register pair that resets to the highest internal SRAM address and automatically updates when you execute PUSH or POP instructions. It is also the place where the return address for the CALL instructions is stored.

The R0+R1 register pair is also the destination for the MULxx multiplication instructions.

The SREG (Status REGister) contains bit-wise results from or input to arithmetic and logic operations and the global interrupt on/off setting.

Some instructions only operate on the top half of the registers (R16-R31), typically the "immediate" ones taking a constant, and yet some others only work with R16-R23.

The 16-bit ADIW and SBIW instructions add or subtract a constant to/from the register pairs R24+R25, X, Y, and Z. As you will typically want to reserve X, Y, and Z for stack operations and use as memory pointers, R24+R25 is left for other 16-bit purposes, for example a counter.

This sub-section is largely based on (12) <sup>18</sup> and (18) <sup>19</sup>.

I present the conventions for register use and calling in appendix A.5.

<sup>&</sup>lt;sup>18</sup> http://www.atmel.se/Images/Atmel-8331-8-and-16-bit-AVR-Microcontroller-XMEGA-AU Manual.pdf

## 3.2.2 ATmega324 data memory

| 32 Registers              | 0x0000 - 0x001F            |

|---------------------------|----------------------------|

| 64 I/O Registers          | 0x0020 - 0x005F            |

| 160 Ext I/I Reg.          | 0x0060 - 0x00FF            |

| Internal SRAM             | 0x0100 -                   |

| 1024/2048/4096/16384 x 8) | 0x04FF/0x08FF/0x10FF/040FF |

Table 2: Data Memory Map for ATmega164A/324A/644A/1284 et al

(The table above is based on ATmega164A/PA/324A/PA/644A/PA/1284/P Complete (19) 20, p21)

The data memory is actually a collection of different types of memory that often have two different addressing modes:

- The 32 general-purpose working registers. Apart from their register number (by which they are directly accessible by most instructions), they are also mapped into the data memory space at 0x0000 0x001F, accessible via instructions LD/LDS/LDD and ST/STS/STD.

- The 64 lowest I/O registers. They can be accessed with the "short" instructions IN and OUT on I/O address space 0x00 0x3F. They are also mapped into the data memory space at 0x0020 0x005F, in which area they can be accessed by instructions LD/LDS/LDD and ST/STS/STD. This is the reason why these particular I/O registers are referred to with the double notation 0x00 (0x0020).

The lower 32 of these 64 I/O registers can also be bit-accessed on I/O address space 0x00 – 0x1F using instructions SBI (Set Bit in I/O register) or CBI (Clear Bit in I/O register) and the "mini-branch instructions" SBIS (Skip if Bit in I/O Register is Set) or SBIC (Skip if Bit in I/O Register is Cleared).

In the ATmega324's family, these 32 addresses are most importantly home to the physical ports A – D, which makes it possible to do bit manipulations on all the ports. The device also has three GPIO (General-purpose I/O) registers that are particularly useful for status flags or global variables. GPIOR0 is in I/O address space at 0x1E, while GPIOR1 and GPIOR2 are outside of the bit-operable area.

- The 160 extended I/O registers only reside in the data memory space at addresses 0x0060 0x00FF, accessible by instructions LD/LDS/LDD and ST/STS/STD.

- The internal SRAM starts at data memory space address 0x0100 and ends at a device-specific address that is also the end of the data memory. It can only be used with LD/LDS/LDD and ST/STS/STD instructions.

In ATmega1284, 32/100 of the peripheral registers can be accessed via IN/OUT, plus the digital IO pin registers. For more information, please see the datasheet, pp 554-557 (19)

\_

http://www.atmel.se/Images/Atmel-8272-8-bit-AVR-microcontroller-ATmega164A PA-324A PA-644A PA-1284 P datasheet.pdf

## 3.2.3 ATxmegaAU data memory

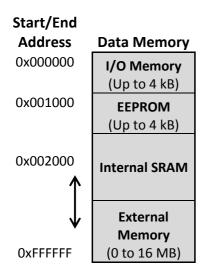

Table 3: ATxmegaAU data memory map

(The table above is based on Atmel AVR XMEGA AU Manual rev F (12) 21, p23)

Currently, there are five ATxmega series, A through E, with certain differences in functionality and intended area of use. The A series is divided into one or a few "sub"-series, e.g. A1, A3, and A4, each implementing a subset of the full A series functionality, peripheral modules, and ports (and thereby pin count). Finally, e.g. A1 exists in two memory sizes, 64kB and 128kB. The "U" states that it has built-in HW support for USB.

In the ATxmega, the 32 working registers are not mapped into the data memory space. Instead, it starts with (up to 4 kB of) I/O memory with only one address numbering. The first 64 locations can be accessed with the IN and OUT instructions and the first 32 of these can be bit-manipulated:

- At 0x0000 0x000F there are 16 GPIO registers that should typically be used for global variables and flags.

- At 0x0010 0x001F there are four sets of virtual ports. Each port can be mapped to one of the 11 physical ports A R (whichever are available in the specific device). A port set consists of the sub-registers DIR (direction), OUT, IN, and INTFLAGS (interrupt settings), so they can be used for easy interaction bit- or byte-wise with the outside world. (Not for communicating with the built-in peripherals.)

After the 32 bit-operable registers, there are 32 more IN/OUT-operable registers for CPU, CLK, SLEEP, and OSCillator. In ATxmegaA1U, 4 out of the 61 peripheral register groups can be accessed via IN/OUT, excluding the digital IO pin registers. 4 out of the 11 IO ports can be mapped to virtual ports that are covered by IN/OUT.

Then follow the rest of the I/O registers that are accessible by instructions LD/LDS/LDD and ST/STS/STD.

21

<sup>&</sup>lt;sup>21</sup> http://www.atmel.se/Images/Atmel-8331-8-and-16-bit-AVR-Microcontroller-XMEGA-AU Manual.pdf

In ATxmega, the on-chip EEPROM can be accessed either in its own EEPROM address space or mapped into the data memory space starting at 0x1000 and ending no later than 0x1FFFF (depending on device-specific EEPROM size). In the data memory space, the EEPROM is only accessible by instructions LD/LDS/LDD and ST/STS/STD.

At 0x2000 the internal SRAM (of device-specific size) starts, immediately followed by (optional) external SRAM, both only accessible by instructions LD/LDS/LDD and ST/STS/STD.

# 3.3 HW design and programming considerations

Due to the AVR design based on the load/store architecture with 32 general-purpose working registers, a great fraction of the instructions require only one clock cycle. In internet user forums I remember seeing claims that the effective average CPI (Clock cycles Per Instruction) is about 1.5, but I haven't been able to find the source. However, the clock cycle counts in this thesis' analyses roughly confirm a CPI of this magnitude.

Another distinguishing feature of the AVR is its non-banked memory, which means that the entire data memory space is linear and continuous (even though the RAMPx and EIND registers can be seen as a way to achieve 64k banks). This makes memory pointer displacement easy and efficient.

These two things have programming, compilation, and performance consequences that I will soon delve into. I have found one Atmel document that looks to architectural choices and two that describe how they affect the optimum programming style:

- "The AVR Microcontroller and C Compiler Co-Design" (20) 22

- "AVR035: Efficient C Coding for 8-bit AVR microcontrollers" (21) <sup>23</sup>

- "AVR4027: Tips and Tricks to Optimize Your C Code for 8-bit AVR Microcontrollers" (22) 24 25

Here I will summarize the first of these documents. The last two partly contain programming conventions that I am actually treating in a separate section, but I include them in appendix A.4 as the C code recommendations so heavily depend on the underlying hardware.

Please also see the "AVR Instruction Set" (23) <sup>26</sup> document.

# 3.3.1 The AVR Microcontroller and C Compiler Co-Design

"The AVR microcontroller was developed with the C language in mind in order to make it possible to construct a code efficient C compiler for AVR." This was done in cooperation with compiler company IAR Systems <sup>27</sup>:

- By not using paged memory, the memory pointers can reach 64 displacement locations instead of just 16.

- The original two 16-bit pointers were too few to support both SW stack and efficiently copying from one memory location to another, so a third one, X, was added.

http://www.atmel.com/dyn/resources/prod\_documents/COMPILER.pdf

http://www.atmel.se/Images/doc1497.pdf

<sup>24</sup> www.atmel.se/Images/doc8453.pdf

www.atmel.se/Images/AVR4027.zip

http://www.atmel.com/Images/doc0856.pdf

<sup>&</sup>lt;sup>27</sup> http://www.iar.com

- It was decided that the AVR would benefit from both indirect addressing (separately loading the address into e.g. XL and XH and then loading the content of this location into a working register) and direct addressing (one instruction loads the content of a specified memory location into a working register). Direct addressing results in fewer instruction words for 1-byte variables, while indirect addressing is more efficient when loading a 4-byte long integer.

- Atmel also decided to propagate both carry and zero flags in certain instructions so that 16or 32-bit operations would be easier.

- Due to space constraints, there is no ADDI (16-bit constant addition without carry) but instead a SUBI (16-bit constant subtraction without carry) and an SBCI (16-bit constant subtraction with carry). Addition is accomplished as a subtraction by a negation of the actual value.

- They also made room for a non-destructive CPI (ComParison with Immediate) and nondestructive CPC (Compare with Carry). (20)

# 3.4 (Other) differences between ATmega and ATxmega

So far I have mostly discussed (some of) the common properties of the AVR family: CPU, working register, instruction set, and data memory space (well...). This is because I expect that they will have the greatest effect on the optimum programming style (for my test application). Please see the device and family datasheets for more information:

"ATmega164A/PA/324A/PA/644A/PA/1284/P Complete" (19) 28

"Atmel AVR XMEGA AU Manual" (12) 29

"ATxmega64A1U/128A1U Complete" (24) 30

(And the Atmel documentation web site is a good place to find e.g. application notes. (25) 31)

There are also (great) differences between ATmega and ATxmega. In short: from a feature perspective, ATxmega is vastly superior to the ATmega with the following additions:

- DMA controller

- Event system

- AES and DES crypto engine

- High-speed DAC and ADC with higher resolution

- Lower power consumption

- 1.6V operation

- 32MHz maximum clock frequency (compared to 16 or 20MHz for ATmega)

- More advanced clock system and sleep modes

- More advanced physical ports

- Virtual port mapping of physical ports to the bit-operable I/O address area

\_

<sup>&</sup>lt;sup>28</sup> http://www.atmel.se/Images/Atmel-8272-8-bit-AVR-microcontroller-ATmega164A\_PA-324A\_PA-644A\_PA-1284\_P\_datasheet.pdf

http://www.atmel.se/Images/Atmel-8331-8-and-16-bit-AVR-Microcontroller-XMEGA-AU\_Manual.pdf http://www.atmel.com/Images/Atmel-8385-8-and-16-bit-AVR-Microcontroller-ATxmega64A1U-

ATxmega128A1U datasheet.pdf

http://atmel.no/webdoc/atmel.docs/atmel.docs.3.application.note.html

- More GPIO registers in the bit-operable I/O address area

- Multilevel interrupt controller

- EBI, External Bus Interface, for external SRAM or SDRAM

- Often "more of everything" compared to ATmega peripherals

The above and more information can be found in these documents:

"AVR XMEGA" (26) 32

"Introducing a New Breed of Microcontrollers for 8/16-bit Applications" (27) 33

"AVR1005: Getting started with XMEGA" (28) 34

There's also a new (alternative) addressing scheme with uniform placement of peripheral registers, so that one common driver can be used with module base pointer and sub-register displacement. This is such an important change, that it gets its own sub-section:

## 3.4.1 Alternative struct-based addressing mode

As the ATmega series grew with more families and the families were extended with additional devices, the I/O register layout(s) became more and more cluttered. This meant that static addressing was more or less necessary, which meant that sometimes the same code had to exist in as many copies as the used number of each peripheral type. It also required more work from Atmel to write and maintain the datasheets. Something had to be done.

Atmel's solution to this was to create a limited number of series (named A - E) for their new ATxmega AVR. All devices within a series share a common set of properties and features and thus part of the datasheets could be maintained as one per series. The device-specific data remains in one datasheet per device type, which is why ATmega has one datasheet and ATxmega two.

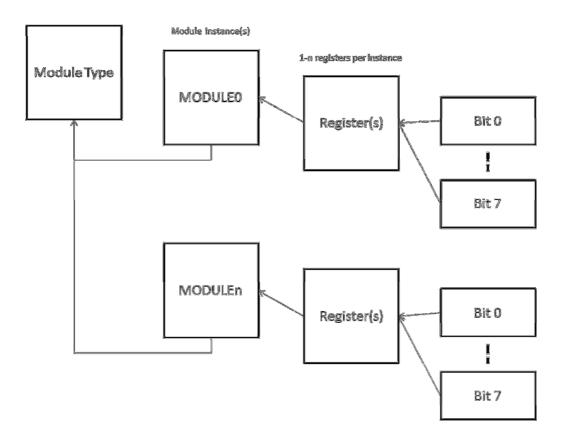

Atmel also took the opportunity to bring order to the I/O register layout. Central to ATxmega is the "module". I have failed to find an exact definition, but (29) <sup>35</sup> seems to call every separate function of the device a module. I pragmatic view is that whatever needs to be controlled resides in an adjoined set of registers that together constitute a module, exactly defined by a module type. Some functions exist in more than one instance and each one is internally exactly like the other modules of the same type. The instances are often(?) (always?) placed at an equal distance from the previous one. This means that you can access a particular I/O register by:

- 1. Finding the base address of the first instance

- 2. Adding (a multiple of) the inter-module offset to find the base address of the instance

- 3. Based on the module type definition (struct), find the memory pointer displacement

http://www.atmel.com/Images/doc8169.pdf

<sup>32</sup> http://www.atmel.com/Images/doc7925.pdf

http://www.atmel.com/Images/doc7926.pdf

Available from: http://www.atmel.com/Images/doc8075.pd

Figure 5: Module types, instances, registers, and bits

(The figure above is based on "AVR1000: Getting Started Writing C-code for XMEGA" (29), p2)

# 4 Presentation of the IDEs

## 4.1 BASCOM-AVR

BASCOM-AVR is an IDE developed by a small Dutch company called MCS Electronics. It is designed for procedural programming in a Basic dialect similar to Visual Basic 6, henceforth referred to as VB. You can also use inline assembly intermixed with your high-level code or you can define your own assembly subroutines and functions. (A Basic subroutine is the same as a C void function.)

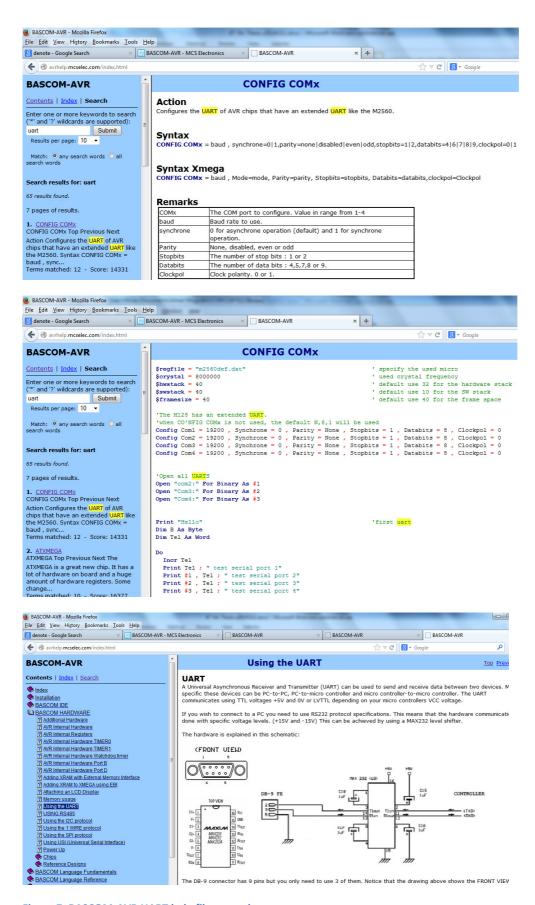

Figure 6: BASCOM-AVR developer view with a configuration code example

The concept of built-in commands is fundamental. They are hand-written assembly routines with the necessary auxiliary code for handling parameters and return values. There are commands both for configuration (like in the above screen dump) and subs/functions. The complete program is a stichwork of these hand-optimized commands and the non-optimized VB application code that "uses" and inter-connects them.

The company focused on functionality and ease of use, rather than ultimate performance (appendix A.1.1), which means that it doesn't have an optimizing compiler. There is support for most common microcontroller peripheral types out of the box. In the following screen dumps from the online help (30) <sup>36</sup> you get a glimpse of extended UART configuration command options, some code samples, and additional information. There's currently around 220 entries in the language reference, which gives a rough estimate of the number of built-in commands.

BASCOM-AVR has a simulator but no debugger. It outputs files that can easily be used for debugging with Visual Studio 6.

I end this very short presentation with a reference to the "Products" web page for BASCOM-AVR. Please look here for more details: (31) <sup>37</sup>

<sup>36</sup> http://avrhelp.mcselec.com/index.html

http://www.mcselec.com/index.php?option=com\_content&task=view&id=14&Itemid=41

Figure 7: BASCOM-AVR UART help file examples

### 4.1.1 User forum

The BASCOM-AVR user forum is located at the company's web site <u>www.mcselec.com</u>. (32) <sup>38</sup> It is active and a good place to get in touch with both employees and independent developers. Apart from posting in the forum, users can also share working code and publish application notes that typically present a complete design or a major piece of code.

#### **4.1.2** Price

There is a free version (usually lagging some releases) that supports almost all features up to 4 kB of compiled code. The full commercial version costs €89 at the company's web site.

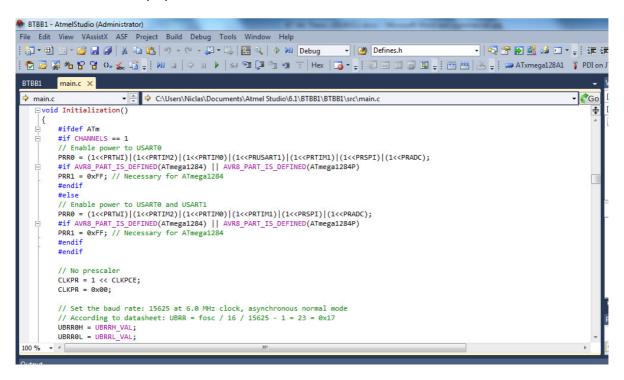

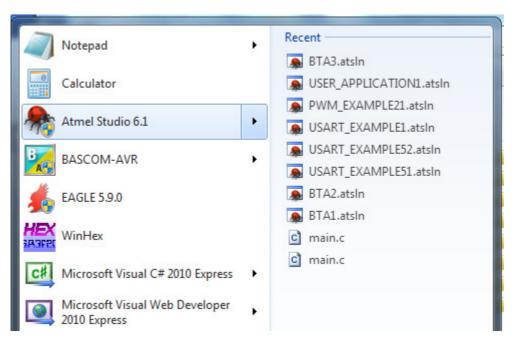

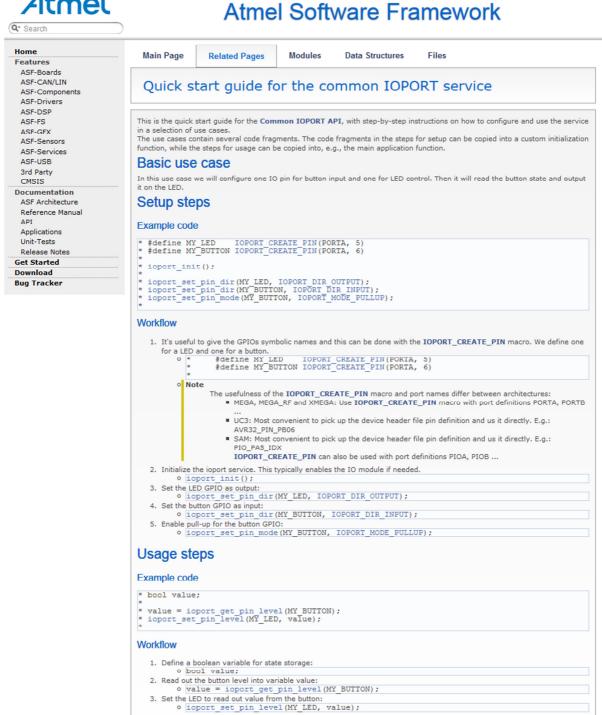

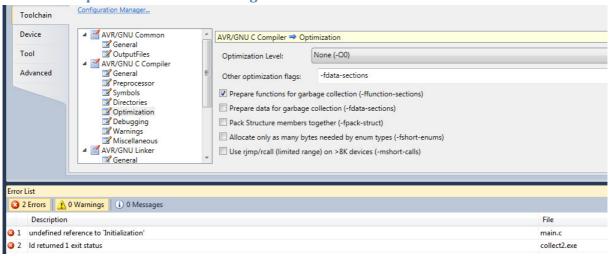

## 4.2 Atmel Studio 6

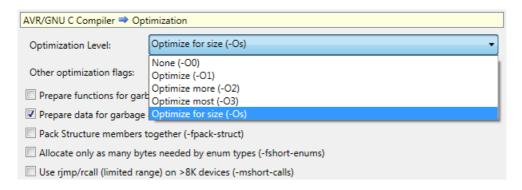

Atmel Studio 6.x is the company's second release based on Microsoft Visual Studio. It has support not only for all 8-bit AVRs, but also for AVR32 and Atmel's ARM devices. At its heart is AVR-GCC (Gnu Compiler Collection), which has a powerful optimizing compiler. I won't go into AVR-GCC, but you can find detailed information about it here: (33) <sup>39</sup> (34) <sup>40</sup>

Two other useful documents are:

The GCC (GNU Compiler Collection) manual on optimization options (35)  $^{41}$  The AVR-Libc manual (36)  $^{42}$

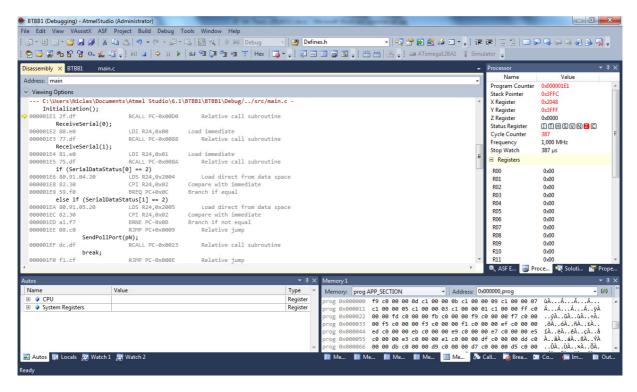

Figure 8: Atmel Studio 6.1 developer view

In Atmel Studio you can develop in Assembly, C, and C++. For detailed information, please see the Atmel Studio 6 web site:  $(6)^{43}$

21

<sup>38</sup> http://www.mcselec.com/index2.php?option=com\_forum&Itemid=59

http://gcc.gnu.org/wiki/avr-gcc

http://www.avrfreaks.net/wiki/index.php/Documentation:AVR GCC/AVR GCC Tool Collection

<sup>41</sup> http://gcc.gnu.org/onlinedocs/gcc/Optimize-Options.html#Optimize-Options

<sup>42</sup> http://www.nongnu.org/avr-libc/user-manual/

You can simulate your program in either high-level or disassembly mode and you can also attach a debugger to your development board / custom PCB and verify real program behavior:

Figure 9: Atmel Studio 6.1 debugging

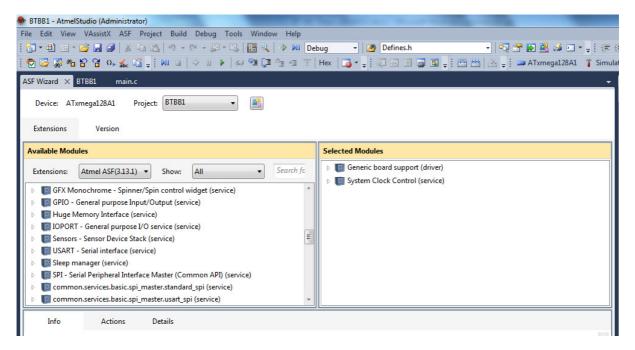

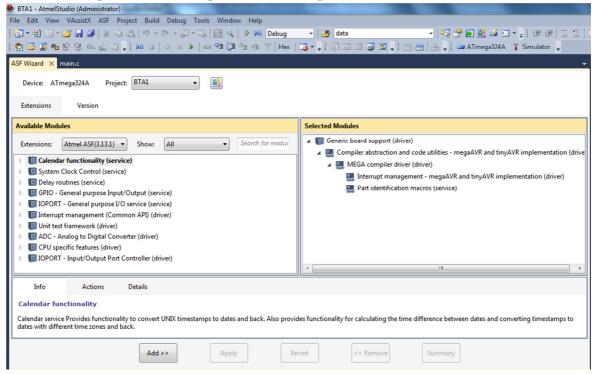

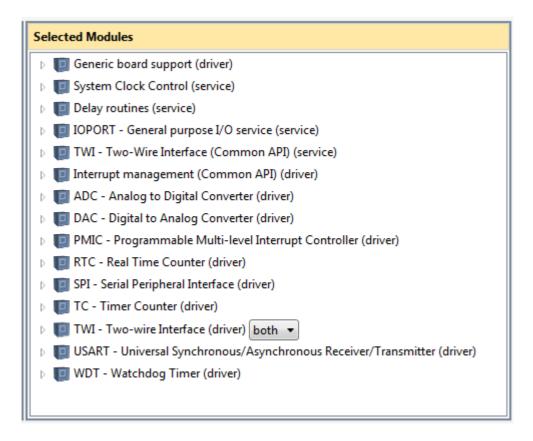

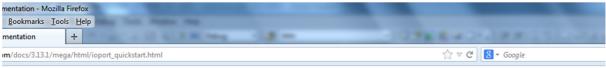

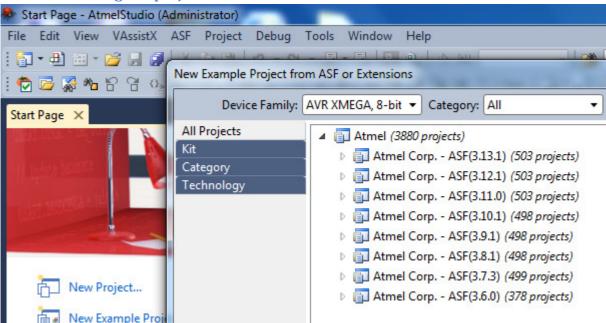

ASF (Atmel Software Foundation, formerly AVR SF) is a repository for standardized drivers and example projects that demonstrate some Atmel Evaluation kit feature.

Figure 10: ASF Wizard in Atmel Studio 6.1

<sup>43</sup> http://www.atmel.se/microsite/atmel\_studio6/

# **Atmel Software Framework**

Main Page Related Pages Modules Namespaces Data Structures Files

# Quickstart guide for Common service TWI

This is the quickstart guide for the Common service TWI, with step-by-step instructions on how to configure and use the driver in a selection of use cases.

The use cases contain several code fragments. The code fragments in the steps for setup can be copied into a custom initialization function, while the steps for usage can be copied into, e.g., the main application function.

#### Basic use case

In the most basic use case, the TWI module is configured for

- · Master operation

- addressing one slave device of the bus at address 0x50

- . TWI clock of 50kHz

- · polled read/write handling

# Setup steps

## Example code

```

Add to your application C-file:

* void twi_init(void)

* {

twi_master_options_t opt = {

.speed = 50000,

.chip = 0x50

* };

* twi_master_setup(&TWIMO, &opt);

* }

*

```

### Workflow

- 1. Ensure that board\_init() has configured selected I/Os for TWI function.

- 2. Ensure that conf\_twim.h is present for the driver.

o Note

This file is only for the driver and should not be included by the user.

3. Define and initialize config structs for TWI module in your TWI initialization function:

- o field speed sets the baudrate of the TWI bus

o field chip sets the address of the slave device you want to communicate with

- Call twi\_master\_setup and optionally check its return code

Note

The config structs can be reused for other T

The config structs can be reused for other TWI modules after this step. Simply reconfigure and write to others modules.

# Usage steps

## Example code: Writing to a slave device

Figure 11: ASF online documentation example (quickstart guide)

For more information, please see the following two documents:

"AVR4029: Atmel Software Framework - Getting Started" (37) 44

"AVR4030: AVR Software Framework - Reference Manual" (38) 45

## 4.2.1 History: AVR Studio 4 & 5, WinAVR, and Eclipse

Please see appendix A.5.3 for information about Atmel Studio 6's history that might shed some light on its current state.

### 4.2.2 User forum

Atmel's main user forum for their AVR offering is <u>www.avrfreaks.net</u>. (39) <sup>46</sup> It is active and a mix of independent developers and a number of more or less official employees. Users can also create "projects" that typically contain a working application or a driver.

### **4.2.3** Price

AVR Studio 4 & 5 and Atmel Studio 6 are free for registered users.

## 4.2.4 (Inline) assembly documentation

I'm just including these documents here for future reference:

- "AVR Assembler User Guide" (40) 47

- "Atmel AT1886: Mixing Assembly and C with AVRGCC" (41) 48 49

- "AVR000: Register and Bit-Name Definitions for the 8-bit AVR Microcontroller" (42)

- "AVR001: Conditional Assembly and portability macros" (43) 51

47 www.atmel.com/images/doc1022.pdf

<sup>&</sup>lt;sup>44</sup> http://www.atmel.com/Images/Atmel-8431-8-and32-bit-Microcontrollers-AVR4029-Atmel-Software-Framework-User-Guide Application-Note.pdf

<sup>45</sup> http://www.atmel.com/Images/doc8432.pdf

http://www.avrfreaks.net/

http://www.atmel.se/Images/doc42055.pdf

<sup>49</sup> http://www.atmel.se/Images/AT1886.zip

http://www.atmel.com/Images/doc0931.pdf

<sup>51</sup> http://www.atmel.com/Images/doc2550.pdf

# **5** BASCOM-AVR analysis

I started with a previously developed piece of BASCOM-AVR VB code used for serial communication between a PC monitoring application and an AVR microcontroller. I first did most of the development on the ATmega and then added the ATxmega with conditional compilation.

# 5.1 Serial communication analysis test log

# **5.1.1** VB high-level code implementations

Please note: The original disassemblies were made on versions with "Config Com1 = 15625..." and without "Config Portd.0" = "Input and Config Portd.1 = Output". The comments are on ATmega324A. In this section, all code sizes are in bytes.

|      | Atmega | ATxmega |                                               |                                                |

|------|--------|---------|-----------------------------------------------|------------------------------------------------|

| Step | 324A   | 128A1   | Action                                        | Comment                                        |

|      |        |         | Local variable Uartsendbyte in Sendpollport   |                                                |

|      |        |         | sub and Senderror sub.                        |                                                |

|      |        |         | Printbin command used for each USART          |                                                |

| BA1a | 1006   | 1720    | sending                                       |                                                |

|      |        |         |                                               | Simply by using a global variable instead of a |

|      |        |         |                                               | local one, we save 50 bytes of compiled code   |

|      |        |         |                                               | (5%). See disassembly                          |

|      |        |         |                                               | BA2_324_disdump_b.txt, ReceiveSerial sub,      |

|      |        |         |                                               | for the operations concerning creating three   |

|      |        |         |                                               | local variables on the frame and pointers to   |

|      |        |         | Global variable Uartsendbyte.                 | them on the software stack. (And, at the end   |

|      |        |         | Printbin command used for each USART          | of the sub, the frame and software stack       |

| BA1b | 956    | 1670    | sending                                       | pointers must be restored.)                    |

|      |        |         | Changed                                       |                                                |

|      |        |         | Config Com1 = 15625 , Synchrone = 0 ,         |                                                |

|      |        |         | Parity = None , Stopbits = 1 , Databits = 8 , |                                                |

|      |        |         | Clockpol = 0                                  |                                                |

|      |        |         | to                                            |                                                |

|      |        |         | Config Com1 = Dummy , Synchrone = 0 ,         |                                                |

|      |        |         | Parity = None , Stopbits = 1 , Databits = 8 , |                                                |

|      |        |         | Clockpol = 0.                                 | Assumingly this change removes the duplicate   |

| BA1c | 938    | 1670    | Global variable Uartsendbyte.                 | mentioned further down in BA2.                 |

|      |        |         | ,                                             |                                                |

|      |        |         |                                               | Moving the Printbin commands used for each     |

|      |        |         | Created gosub Prbin for Printbin command.     | byte to a gosub with a common Printbin         |

| BA2  | 896    | 1596    | Global variable Uartsendbyte.                 | command saves us another 42 bytes.             |

Figure 12: BASCOM-AVR iterations 1-2

Before we continue, let's take a look at the BA2 ATmega 324A disassembly:

- The actual program starts at 0x7C (after the interrupt vector). By default, an initialization phase is run:

- It sets the stack pointer to the end of RAM.

- Register Y (pair R28 & R29) is used as the software stack pointer.

- Pair R4 & R5 is used as the frame pointer.

- Register MCUSR (reset flags) is cleared except for WDRF (watchdog refresh).

- Watchdog is disabled.

- The entire internal SRAM is cleared (zeroed). This means that all global variables are automatically initialized to 0, so my current sub Initialization is unnecessary.

This initialization can be omitted by using \$NOINIT at the beginning of the .bas file.

Then follow the setup of USARTO, clearing of special register R6, and enabling of RX0 interrupt. For some reason the USARTO setup is done twice. According to the datasheet (p180) (19) <sup>52</sup>, this shouldn't be necessary. (This turned out to be a programmer mistake, partly due to incomplete documentation. See comment on BA1c above.)

Apart from the clearing of the global variables in sub Initialization, I was surprised to see that the compiler clears R24 for each and every variable. The same can be seen at the beginning of the Receiveserial sub. A similar case is 0x17C & 0x17E vs. 0x182 & 0x184.

Another peculiarity is that the compiler doesn't check if the jump destination is another jump (e.g. in nested if statements). See the main program loop and the Receiveserial sub.

The routines at 0x30A to 0x30E and 0x31C to 0x324 are not used. They are probably part of frequently used code that's included in one standardized package for simplicity. I'll come back to them at the end of the BASCOM-AVR analysis and subtract their size from the final comparison.

It is worth noticing that turning optimization on produces no code size difference in the BA2 code. It's still 896 bytes. I didn't disassemble to see if there are code changes.

Let's try using array-based sending instead of byte-wise sending:

|      | Atmega | ATXmega |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step | 324A   | 128A1   | Action                                                                                                                                                                                                                                                                               | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |        |         | Changed from global Uartsendbyte to global Serialoutdata(20) array and Serialoutcount. Subs Sendpollport and Senderror fill this array, update the counter, and finally make one call to Prbin.  Now the Prbin gosub contains the following command:  Printbin #1, Serialoutdata(1), | At first I couldn't get this to work, neither using Serialoutcount nor a fixed value (6). I often got the correct response, but sometimes several bytes with the value 0. The correct syntax according to documentation is with "; Serialcount", but that would sometimes send additional bytes. As the saving with this version would be only 6 bytes (a total of 890) with a 20 + 1 byte increase in RAM, I didn't look closer into this until later:  By changing to ", Serialoutcount" it seems to |

| BA3  | 880    | 1580    | Serialoutcount                                                                                                                                                                                                                                                                       | work properly and the size becomes 880.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Figure 13: BASCOM-AVR iteration 3

As mentioned in the comment, I didn't continue building on this branch as the RAM increase surpasses the program code saving.

http://www.atmel.se/Images/Atmel-8272-8-bit-AVR-microcontroller-ATmega164A PA-324A PA-644A PA-1284 P datasheet.pdf

I next investigated different uses of global and local variables and (byref) parameters:

|      | Atmega | ATXmega |                                                |                                                   |

|------|--------|---------|------------------------------------------------|---------------------------------------------------|

| Step | 324A   | 128A1   | Action                                         | Comment                                           |

|      |        |         | BA2 is used as the basis for BA4.              |                                                   |

|      |        |         | Comment out the initialization of global       |                                                   |

| BA4a | 878    |         | variables to 0.                                |                                                   |

|      |        |         |                                                | (10 bytes saved by "If Ischarwaiting(#1) = 1      |

|      |        |         | In sub Receiveserial, omit local Serialwaiting | Then". 6 bytes saved by removing local byte       |

| BA4b | 862    |         | and use "If Ischarwaiting(#1) = 1 Then".       | Serialwaiting.)                                   |

|      |        |         | In sub Receiveserial, break out                |                                                   |

|      |        |         | "Serialdata(receivecounter) = Serialbyte"      |                                                   |

|      |        |         | and place it in new sub with byref             |                                                   |

| BA4c | 868    |         | parameter.                                     |                                                   |

|      |        |         | Convert sub Receiveserial's local Serialbyte   |                                                   |

|      |        |         | to global Serialbyte and remove the byref      |                                                   |

| BA4d | 836    |         | parameter.                                     |                                                   |

|      |        |         |                                                | No change as a parameterless sub is in fact a     |

| BA4e | 836    |         | Convert sub Insertserialdata to a gosub.       | gosub.                                            |

|      |        |         | Convert sub Receiveserial's local Continue     |                                                   |

| BA4f | 792    | 1492    | to global Continue.                            | This is the final BA4 version.                    |

|      |        |         |                                                | We just saw that a local byte requires 6 bytes    |

|      |        |         |                                                | of program code, so the "fixed cost" of using     |

|      |        |         |                                                | the first local byte is 830 - 792 - 6 = 32 bytes. |

|      |        |         |                                                | As we'll see from the disassembly of BA5, 22      |

|      |        |         |                                                | of these saved bytes come from the two            |

|      |        |         |                                                | sections that make room on the frame for          |

|      |        |         | Added a local Test byte to sub Receiveserial.  | local variables, of which 10 refer to unused      |

| BA4g | 830    |         | This variable isn't used.                      | code.                                             |

Figure 14: BASCOM-AVR iteration 4

We now have a figure for the cost of using local variables, both in terms of an offset and a variable "fee" for each one. If you want to optimize your BASCOM-AVR development, you should only use parameters and locals when there is a good reason to do so. This is quite contrary to the general "rule" of using no global variables at all unless absolutely necessary. I'll return to this later in this section.

To proceed, we need to look at improving the structure of the program itself:

|      | Atmega | ATXmega |                                             |         |

|------|--------|---------|---------------------------------------------|---------|

| Step | 324A   | 128A1   | Action                                      | Comment |

|      |        |         | Changed all subs to gosubs.                 |         |

|      |        |         | Revised the main loop and gosub             |         |

|      |        |         | Receiveserial.                              |         |

|      |        |         | No longer keep the program looping inside   |         |

|      |        |         | gosub Receiveserial after start token until |         |

| BA5a | 754    |         | end token.                                  |         |

|      |        |         | Removed global Continue.                    |         |

|      |        |         | Removed global Receivedata.                 |         |

|      |        |         | Renamed global Serialdataready to           |         |

|      |        |         | Serialdatastatus (value 1).                 |         |

|      |        |         | Removed global Serialcommandfound. Its      |         |

|      |        |         | meaning incorporated in Serialdatastatus    |         |

| BA5b | 748    | 1444    | (value 2).                                  |         |

Figure 15: BASCOM-AVR iteration 5

At this point, I assumed that BA5b 748 is the furthest I could improve this code without resorting to even more exotic programming. (It turned out I was very wrong.)

So far I had "only" replaced a while loop with a goto and used global variable aliasing to mimic local

variable use at global variable cost. As we saw earlier, the assembly implementation of nested if clauses end with jumps to the outer if clause's ending jump and so on. This doesn't lead to an increase in compiled code, but you lose a few clock cycles. This should be taken care of by the compiler, but it is possible to replace the if-else-end if and Select case-case else-end select with gotos to labels, but I won't do it in VB code for fear of cluttering up the code completely.

## Let's sum up:

The interrupt vector takes 124 bytes compiled code. For simplicity's sake, let's say that the default initialization (except USART setup) takes another 58 bytes. In other words, the application-specific code starts at 0xB6 (182 dec). The initial (worst) design required 1006 bytes, netting at 824 bytes application code. BA5b 748 has a net application size of 566 bytes. This is a reduction of (824 - 566) / 824 = 31%.

Now I'll see how much more I can improve this on the assembler level.

## 5.1.2 Looking for inline assembly improvements to standard BASCOM-AVR funtionality

## 5.1.2.1 Receiveserial gosub

As mentioned before, nested if clauses result in jump to jump to destination rather than jump to destination. Three jumps could be modified so they go directly to destination, but this is hardly worth the conversion into inline assembler. The only real reason to do this would be if it would enable us to realize a potential saving in Insertserial gosub.

## 5.1.2.2 Insertserialdata gosub

Change to non-autoincrementing (AC 90). This enables removal of the next operation.

0000019C AD 90 ld r10, X+ R10 = global Receivecounter, X post-increment

Remove this: 000001A2 B1 E0 ldi r27, 0x01 ; 1 ...

So long as the entire array SERIALDATA resides within the same RAM address LSB (Least Significant Byte), this RAM address MSB operation is unnecessary.

```

000001A6 BB 1D adc r27, r11 ...

```

Total potential saving: two 1-word operations = 4 bytes. Is it possible to realize this by using inline assembler? Yes, if we can be sure that R24, X, R10, and R11 can be used freely without pushing and popping them on the stack.

The Bascom register convention <sup>53</sup> doesn't mention any of these, so we should be safe. (Please see appendix A.5.1):

Just looking at the compiled code, it seems like Bascom is generally only using / tying up the "other registers" inside Bascom commands.

-

<sup>&</sup>lt;sup>53</sup> Look up "Mixing ASM and BASIC" at <a href="http://avrhelp.mcselec.com/index.html">http://avrhelp.mcselec.com/index.html</a>

## Two examples from the BA2 disassembly's Receiveserial:

| 144:   | 81 e0       | ldi  | r24, 0x01 | ; 1     | Local Serialbyte on frame                             |

|--------|-------------|------|-----------|---------|-------------------------------------------------------|

| 146:   | 0e 94 93 01 | call | 0x326     | ; 0x326 |                                                       |

| ??14a: | 81 e0       | ldi  | r24, 0x01 | ; 1     | Local Serialwaiting on frame                          |

| 14c:   | 0e 94 93 01 | call | 0x326     | ; 0x326 |                                                       |

| ??150: | 81 e0       | ldi  | r24, 0x01 | ; 1     | Local Continue on frame                               |

| 152:   | 0e 94 93 01 | call | 0x326     | ; 0x326 |                                                       |