# FOR A DUAL OPERATIONAL AMPLIFIER IN CHIP SCALE PACKAGE

by

#### SERGIO HIDALGO BOUCHEZ, B.S.E.E.

A THESIS

IN

# **ELECTRICAL ENGINEERING**

Submitted to the Graduate Faculty of Texas Tech University in Partial Fulfillment of the Requirements for the Degree of

MASTER OF SCIENCE

IN

**ELECTRICAL ENGINEERING**

Approved

# **ACKNOWLEDGEMENTS**

An ideal is only reached when it is kept in mind every day until its completion. God's grace, smiles making life enjoyable, slaps on the back expressing support, incentive words, technical ideas and corrections, trust and love fed this daily work. It would not have been possible to complete this project without all those elements together. I want to thank all you who participate in giving me all of that. I will try to learn from you by imitating the example you taught to me.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                              | ii |

|---------------------------------------------------------------|----|

| ABSTRACT                                                      |    |

| LIST OF TABLES                                                |    |

| LIST OF FIGURES                                               | ix |

| CHAPTER                                                       |    |

| 1. INTRODUCTION                                               |    |

| 1.1 Definition of the problem                                 |    |

| 1.2 Solution of the problem                                   |    |

| 1.3 Previous work                                             |    |

| 1.4 Chapters summary                                          |    |

| 2. BACKGROUND                                                 |    |

| 2.1 What is a dc automated bench solution?                    |    |

| 2.3 Development of the operational amplifier                  |    |

| 2.4 Definition of the operational amplifier                   |    |

| 2.4.1 Real operational amplifier                              |    |

| 2.4.2 Ideal operational amplifier                             |    |

|                                                               |    |

| 2.5 Device under test (DUT)                                   |    |

| 2.5.1 Product data sheet only with DC parameters to be tested | 9  |

| 2.5.2 Package of the DUT                                      | 10 |

| 2.5.3 Applications                                            | 14 |

| 2.6 Testing DC parameters                                     | 14 |

| 2.6.1 Test circuit                                            | 14 |

| 2.6.2 Verification routine                                    | 16 |

| 2.6.3 Quiescent current test (I <sub>Q</sub> )                | 16 |

| 2.6.4 Positive input bias current (I <sub>B+</sub> )          | 17 |

| 2.6.5 Negative input bias current (I <sub>B</sub> -)          | 18 |

| 2.6.6 Input offset current (I <sub>OS</sub> )                 | 19 |

| 2.6.7 False summing junction test circuit                     | 19 |

| 2.6.8 Input offset voltage (Vos)                              | 21 |

| 2.6.9 Power supply rejection ratio (PSRR)                     | 21 |

| 2.6.10 Common-mode rejection ratio half scale (CMRRh)         | 22 |

| 2.6.11 Common-mode rejection ratio full scale (CMRRf)         | 22 |

|    | 2.6.12 Open loop voltage gain (A <sub>OL</sub> )                                                                                                                                                                                                                                               | 23                                           |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|    | 2.6.13 Voltage output swing from rail (SW <sub>out±</sub> )                                                                                                                                                                                                                                    | 24                                           |

| 3. | TEST HARDWARE                                                                                                                                                                                                                                                                                  | 25                                           |

|    | 3.1 Socketing the DUT                                                                                                                                                                                                                                                                          |                                              |

|    | 3.2 Printed circuit board design                                                                                                                                                                                                                                                               |                                              |

|    | 3.2.1 Protel                                                                                                                                                                                                                                                                                   |                                              |

|    | 3.2.2 Adapter boards                                                                                                                                                                                                                                                                           | 26                                           |

|    | 3.2.3 Device interface board                                                                                                                                                                                                                                                                   | 28                                           |

|    | 3.3 PXI system                                                                                                                                                                                                                                                                                 |                                              |

|    | 3.3.1 Introduction                                                                                                                                                                                                                                                                             | 32                                           |

|    | 3.3.2 Controller                                                                                                                                                                                                                                                                               | 33                                           |

|    | 3.3.3 18-slot PXI chassis (PXI-1006 chassis)                                                                                                                                                                                                                                                   | 33                                           |

|    | 3.3.4 General purpose relay switch card (NI PXI-2565)                                                                                                                                                                                                                                          | 33                                           |

|    | 3.3.5 Electromechanical relay multiplexer card (NI PXI-2503)                                                                                                                                                                                                                                   | 34                                           |

|    | 3.3.6 GPIB module with Ethernet port (NI PXI-8212)                                                                                                                                                                                                                                             | 36                                           |

|    | 3.3.7 PXI-MXI-3 copper link (NI PXI-PCI8330)                                                                                                                                                                                                                                                   | 36                                           |

|    | 3.3.8 6½ digital multimeter (NI PXI-4070)                                                                                                                                                                                                                                                      | 36                                           |

|    | (1/2 / 1/2 / 0 / 0 / 0 / 0 / 0 / 0 / 0 / 0 / 0 /                                                                                                                                                                                                                                               | 50                                           |

|    | 3.3.9 Analog output (NI PXI-6704)                                                                                                                                                                                                                                                              |                                              |

|    |                                                                                                                                                                                                                                                                                                | 37                                           |

|    | 3.3.9 Analog output (NI PXI-6704)                                                                                                                                                                                                                                                              | 37<br>38                                     |

|    | 3.3.9 Analog output (NI PXI-6704)                                                                                                                                                                                                                                                              | 37<br>38<br>41                               |

| 4. | 3.3.9 Analog output (NI PXI-6704)  3.4 Hardware interconnection  3.4.1 HP DMMs  TEST SOFTWARE  4.1 Test program based on LabVIEW                                                                                                                                                               | 37<br>38<br>41<br>42<br>42                   |

| 4. | 3.3.9 Analog output (NI PXI-6704)  3.4 Hardware interconnection 3.4.1 HP DMMs  TEST SOFTWARE  4.1 Test program based on LabVIEW  4.2 Test program subVIs                                                                                                                                       | 37<br>38<br>41<br>42<br>42<br>43             |

| 4. | 3.3.9 Analog output (NI PXI-6704)  3.4 Hardware interconnection 3.4.1 HP DMMs  TEST SOFTWARE 4.1 Test program based on LabVIEW 4.2 Test program subVIs 4.2.1 Delay (mS) subVI                                                                                                                  | 37 38 41 42 42 43 43                         |

| 4. | 3.3.9 Analog output (NI PXI-6704)  3.4 Hardware interconnection 3.4.1 HP DMMs  TEST SOFTWARE  4.1 Test program based on LabVIEW  4.2 Test program subVIs  4.2.1 Delay (mS) subVI                                                                                                               | 37<br>38<br>41<br>42<br>43<br>43             |

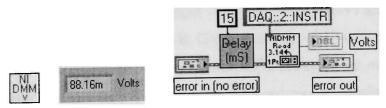

| 4. | 3.3.9 Analog output (NI PXI-6704)  3.4 Hardware interconnection 3.4.1 HP DMMs  TEST SOFTWARE  4.1 Test program based on LabVIEW  4.2 Test program subVIs 4.2.1 Delay (mS) subVI  4.2.2 NI AO subVI  4.2.3 NI DMM I subVI                                                                       | 37<br>41<br>42<br>43<br>43<br>43             |

| 4. | 3.3.9 Analog output (NI PXI-6704)  3.4 Hardware interconnection 3.4.1 HP DMMs  TEST SOFTWARE  4.1 Test program based on LabVIEW  4.2 Test program subVIs  4.2.1 Delay (mS) subVI                                                                                                               | 37<br>41<br>42<br>43<br>43<br>43             |

| 4. | 3.3.9 Analog output (NI PXI-6704)  3.4 Hardware interconnection 3.4.1 HP DMMs  TEST SOFTWARE.  4.1 Test program based on LabVIEW 4.2 Test program subVIs 4.2.1 Delay (mS) subVI.  4.2.2 NI AO subVI.  4.2.3 NI DMM I subVI.  4.2.4 NI DMM V subVI.  4.2.5 HP DMM V subVI.                      | 37<br>48<br>42<br>43<br>43<br>43<br>44<br>44 |

| 4. | 3.3.9 Analog output (NI PXI-6704)  3.4 Hardware interconnection 3.4.1 HP DMMs  TEST SOFTWARE 4.1 Test program based on LabVIEW 4.2 Test program subVIs 4.2.1 Delay (mS) subVI 4.2.2 NI AO subVI 4.2.3 NI DMM I subVI 4.2.4 NI DMM V subVI                                                      | 37<br>48<br>42<br>43<br>43<br>43<br>44<br>44 |

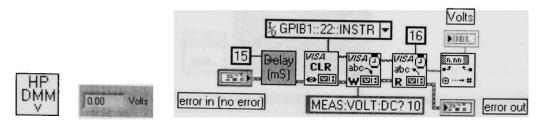

| 4. | 3.3.9 Analog output (NI PXI-6704)  3.4 Hardware interconnection 3.4.1 HP DMMs  TEST SOFTWARE.  4.1 Test program based on LabVIEW 4.2 Test program subVIs 4.2.1 Delay (mS) subVI.  4.2.2 NI AO subVI.  4.2.3 NI DMM I subVI.  4.2.4 NI DMM V subVI.  4.2.5 HP DMM V subVI.                      | 37 38 41 42 43 43 44 44 45                   |

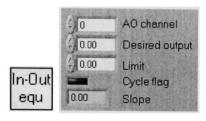

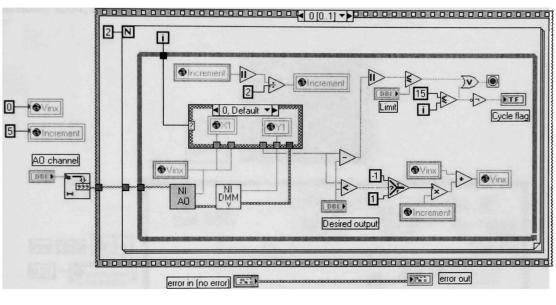

| 4. | 3.3.9 Analog output (NI PXI-6704)  3.4 Hardware interconnection 3.4.1 HP DMMs  TEST SOFTWARE.  4.1 Test program based on LabVIEW  4.2 Test program subVIs 4.2.1 Delay (mS) subVI  4.2.2 NI AO subVI  4.2.3 NI DMM I subVI  4.2.4 NI DMM V subVI  4.2.5 HP DMM V subVI  4.2.6 In-out equ subVI. | 37 41 42 43 43 44 44 45 47                   |

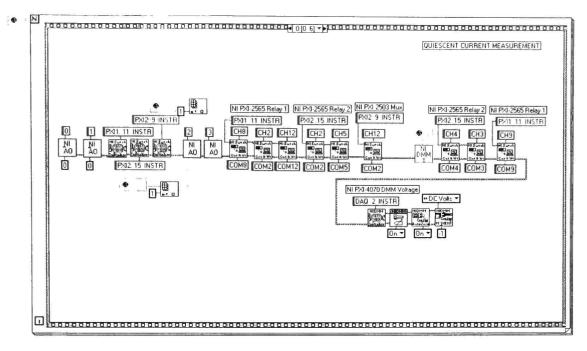

| 4.3.1 I <sub>Q</sub> measurement Test Seq subVI CD 00 00            | 49 |

|---------------------------------------------------------------------|----|

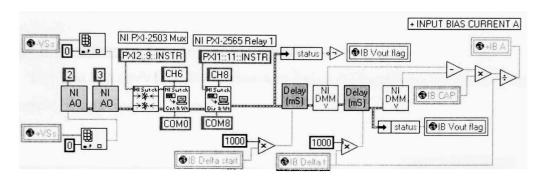

| 4.3.2 I <sub>B+</sub> A measurement Test Seq subVI CD 01 00         | 50 |

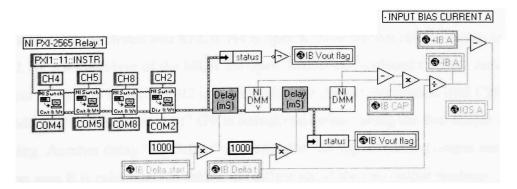

| 4.3.3 I <sub>B</sub> . A measurement Test Seq subVI CD 01 01        | 51 |

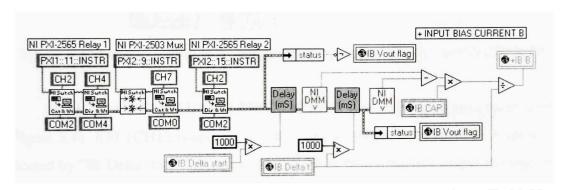

| 4.3.4 I <sub>B+</sub> B measurement Test Seq subVI CD 01 02         | 52 |

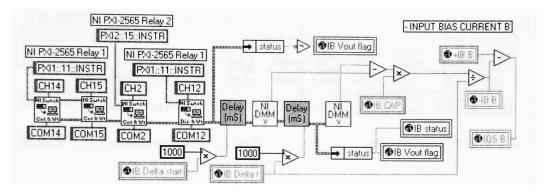

| 4.3.5 I <sub>B</sub> . B measurement Test Seq subVI CD 01 03        | 53 |

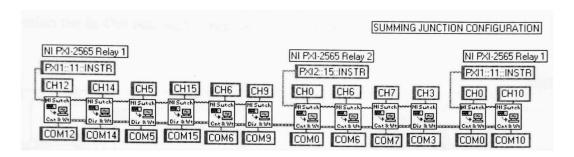

| 4.3.6 Summing junction configuration set up Test Seq subVI CD 02 00 | 54 |

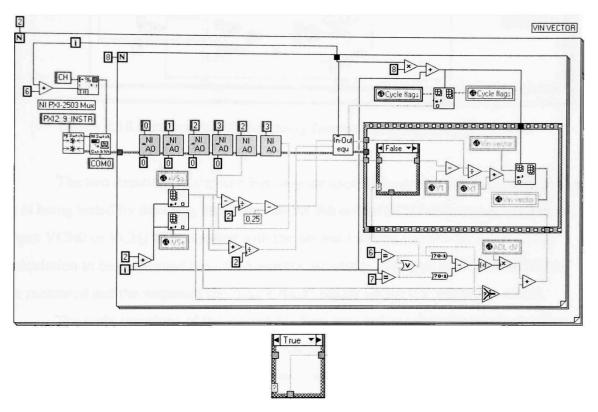

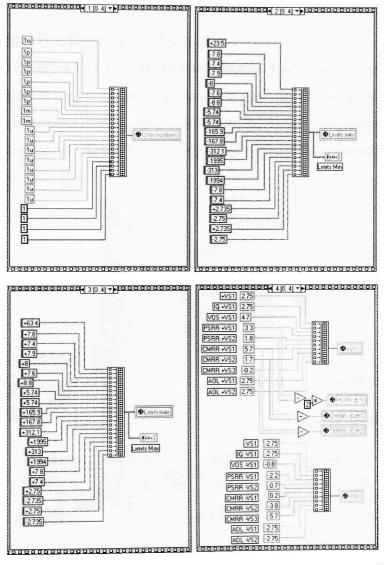

| 4.3.7 Vin vector Test Seq subVI CD 03 0x                            | 54 |

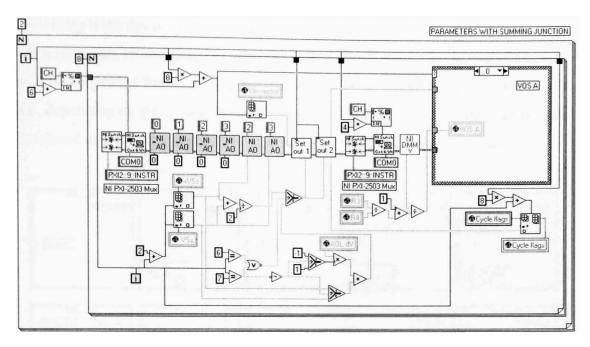

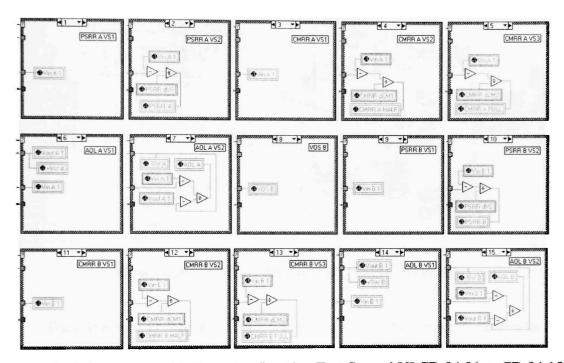

| 4.3.8 Parameters with Summing Junction Test Seq subVI CD 04 0x      | 55 |

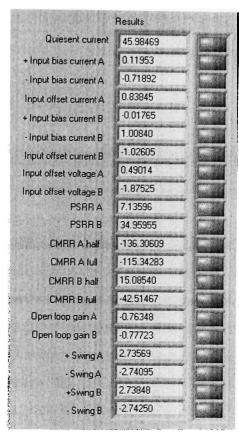

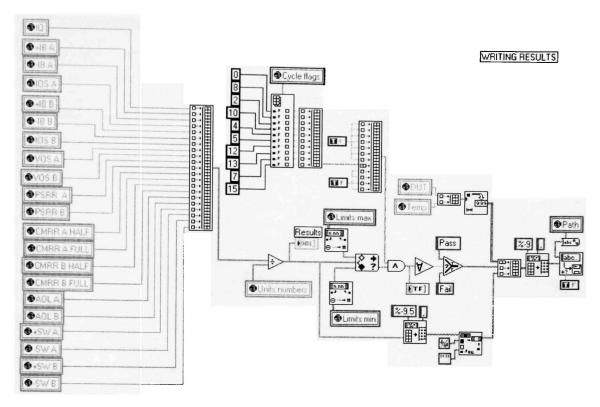

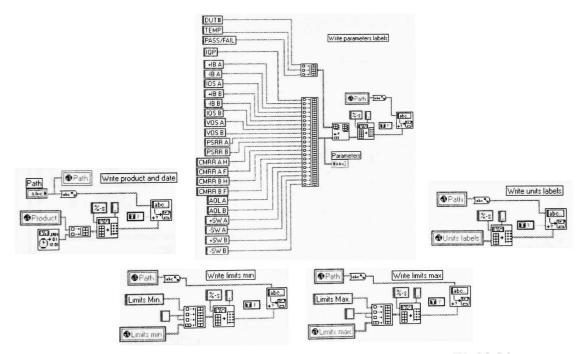

| 4.3.9 Writing results Test Seq subVI CD 05 00                       | 57 |

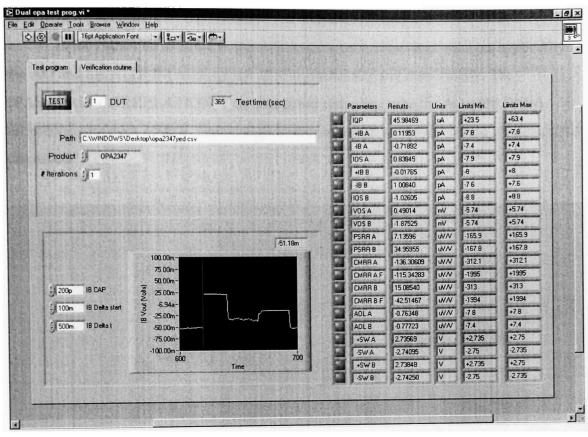

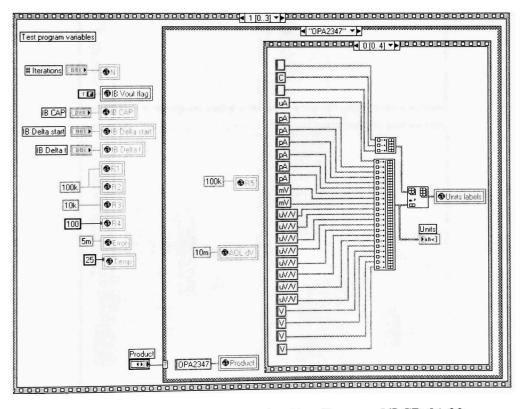

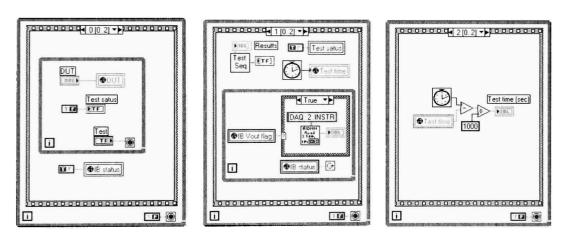

| 4.4 Test Program VI                                                 |    |

| 4.4.2 Variables initialization Test Program VI CD 01 0x             | 62 |

| 4.4.3 Writing labels Test Program VI CD 02 0x                       | 64 |

| 4.4.4 Test Program VI CD 03 0x                                      | 65 |

| 5. DATA ANALYSIS FOR REPEATABILITY AND CORRELATION                  |    |

| 5.1.2 I <sub>B</sub> data analysis                                  | 69 |

| 5.1.3 SW <sub>OUT</sub> from rail data analysis                     | 71 |

| 5.1.4 V <sub>OS</sub> data analysis                                 | 71 |

| 5.1.5 PSRR data analysis                                            | 72 |

| 5.1.6 CMRR data analysis                                            | 73 |

| 5.1.7 A <sub>OL</sub> data analysis                                 | 74 |

| 5.1.8 Test time                                                     | 75 |

| 6. CONCLUSIONSREFERENCES                                            |    |

#### **ABSTRACT**

The development of a direct current (DC) automated bench solution for a dual operational amplifier in Chip Scale Package (CSP) is the purpose of this thesis. Packaging and electrical properties of the device under test (DUT) are described. The design and implementation of the test hardware is covered. A detail explanation of the test program developed in LabVIEW is also included. Finally a statistical analysis is used to verify the system is repeatable and accurate in relationship with an automated test equipment (ATE).

# LIST OF TABLES

| 2.1 Some CSP characteristics                                            | 6  |

|-------------------------------------------------------------------------|----|

| 2.2 Product data sheet DC parameters of the OPA2347                     | 9  |

| 2.3 Electrical performance of LM2904uSMD and OPA2347YED                 | 14 |

| 3.1 Adapter board characteristics                                       | 28 |

| 3.2 Device interface board characteristics                              | 31 |

| 3.3 NI PXI-2503 front connector pin assignments for two-wire mode       | 35 |

| 3.4 NI PXI-2503 pin assignments for two-wire mode using the NI TB-2505  | 36 |

| 3.5 NI PXI-6704 front connector pin assignments                         | 37 |

| 3.6 NI PXI-6704 pin assignments using the NI SCB-68                     | 38 |

| 3.7 Interconnection between NI PXI-4070 DMM and NI PXI-2503 Multiplexer | 39 |

| 3.8 Interconnection between NI PXI-2565 REL 1 and bench board           | 39 |

| 3.9 Interconnection between NI PXI-2565 Relay 2 and bench board         | 39 |

| 3.10 Interconnection between NI PXI-2503 Multiplexer and bench board    | 40 |

| 3.11 Interconnection between NI PXI-6704 Analog output and bench board  | 41 |

| 3.12 Interconnection between NI PXI-4070 DMM and HP-34401A DMM          | 41 |

| 5.1 I <sub>Q</sub> statistical data                                     | 69 |

| 5.2 I <sub>Q</sub> repeatability results                                | 69 |

| 5.3 I <sub>Q</sub> correlation results                                  | 69 |

| 5.4 I <sub>B</sub> statistical data                                     | 70 |

| 5.5 I <sub>B</sub> repeatability results                                | 70 |

| 5.6 I <sub>B</sub> correlation results                                  | 70 |

| 5.7 V <sub>OS</sub> statistical data                                    | 71 |

| 5.8 V <sub>OS</sub> repeatability results                               | 71 |

| 5.9 V <sub>OS</sub> correlation results                                 | 72 |

| 5.10 PSRR statistical data                                              | 72 |

| 5.11 PSRR repeatability results                                         | 72 |

| 5.12 PSRR correlation results                                           | 73 |

| 5.13 CMRR statistical data                 | 73 |

|--------------------------------------------|----|

| 5.14 CMRR repeatability results            | 73 |

| 5.15 CMRR correlation results              | 74 |

| 5.16 A <sub>OL</sub> statistical data      | 74 |

| 5.17 A <sub>OL</sub> repeatability results | 74 |

| 5.18 A <sub>OL</sub> correlation results   | 75 |

# LIST OF FIGURES

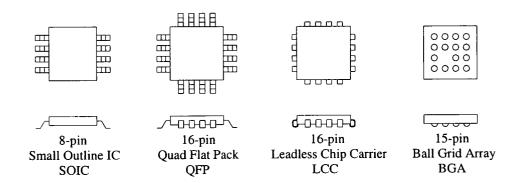

| 2.1 Modern integrated circuit (IC) packages                            | 4  |

|------------------------------------------------------------------------|----|

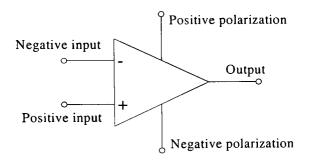

| 2.2 Symbol of the operational amplifier                                | 7  |

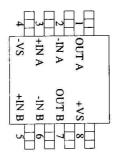

| 2.3 Typical top-view configuration of a dual op amp                    | 9  |

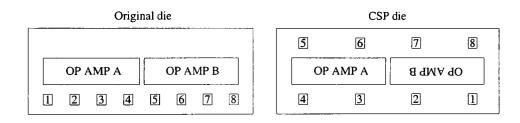

| 2.4 Original and CSP OPA2347 die layout                                | 10 |

| 2.5 Cross-section illustrations for BOP and RDL                        | 12 |

| 2.6 OPA2347YED outline                                                 | 13 |

| 2.7 LM2904 uSMD outline                                                | 13 |

| 2.8 General test circuit                                               | 15 |

| 2.9 Quiescent current (I <sub>Q</sub> ) test circuit                   | 17 |

| 2.10 Positive input bias current (I <sub>B+</sub> ) test circuit       | 18 |

| 2.11 Negative input bias current (I <sub>B</sub> -) test circuit       | 19 |

| 2.12 False summing junction test circuit                               | 20 |

| 3.1 Schematic for adapter boards                                       | 26 |

| 3.2 Top and bottom layer layout for DIP adapter board PR791            | 27 |

| 3.3 Top and bottom layer layout for edge connector adapter board PR792 | 28 |

| 3.4 Schematic for device interface board PR825                         | 29 |

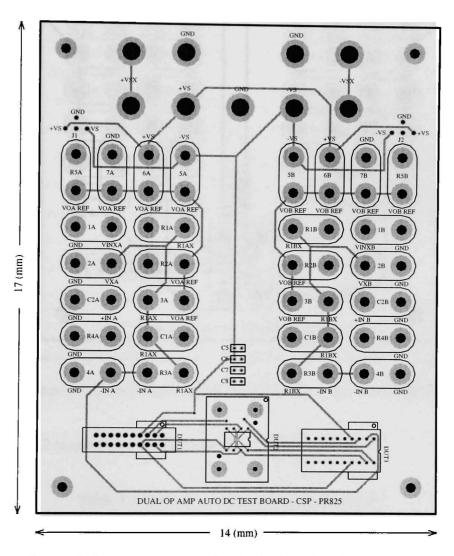

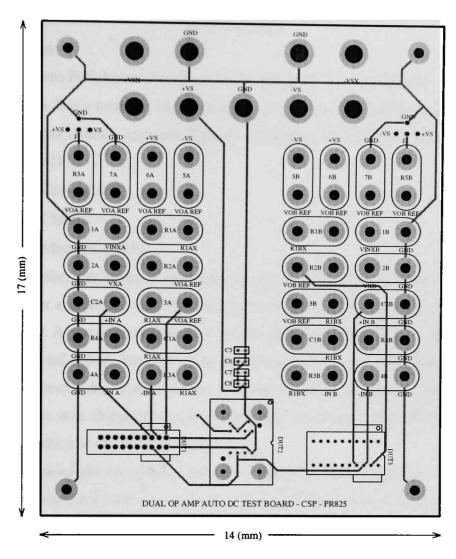

| 3.5 Top layer layout for device interface board PR825                  | 30 |

| 3.6 Bottom layer layout for device interface board PR825               | 31 |

| 3.7 NI PXI-2503 Switch architecture                                    | 34 |

| 3.8 NI PXI-2503 2-wire 12*1 12*1 switch architecture                   | 34 |

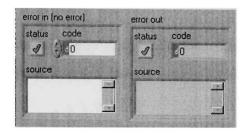

| 4.1 Error in control and error out indicator                           | 43 |

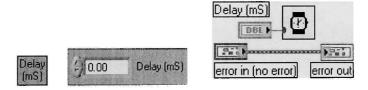

| 4.2 Delay subVI icon, FP and CD                                        | 43 |

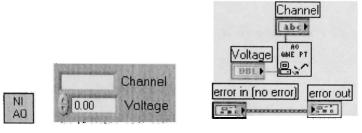

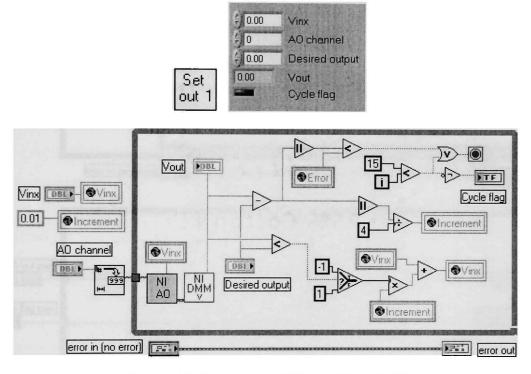

| 4.3 NI AO subVI icon, FP and CD                                        | 44 |

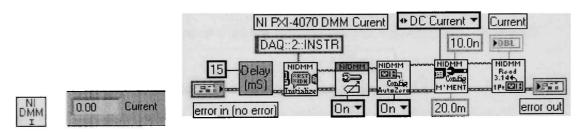

| 4.4 NI DMM I subVI icon, FP and CD                                     | 44 |

| 4.5 NI DMM V subVI icon, FP and CD                                     |    |

| 4.6 HP DMM V subVI icon, FP and CD                                     | 45 |

| 4.7 In-out equ subVI icon, FP and CD 00 00, CD 00 01 and CD 01 00      | 46 |

| 4.8 Set out 1 subVI icon, FP and CD                                       | 47 |

|---------------------------------------------------------------------------|----|

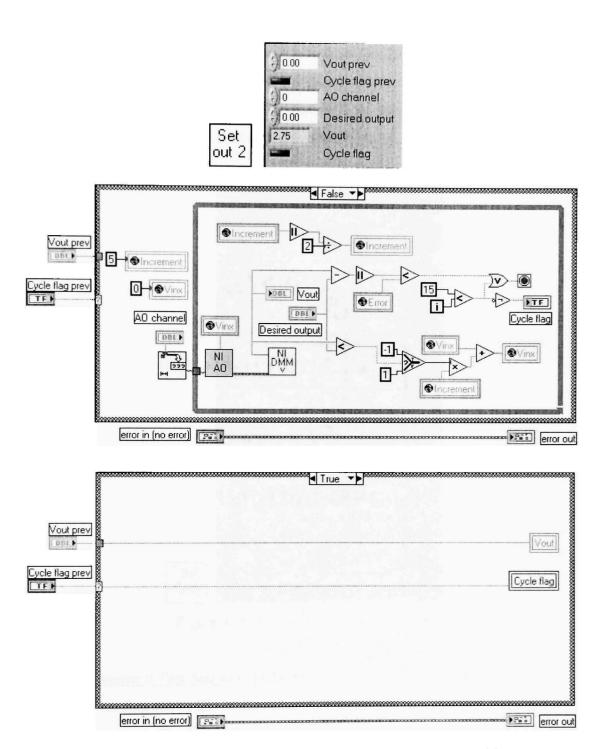

| 4.9 Set out 2 subVI icon, FP, CD 00 00 and CD 01 00                       | 48 |

| 4.10 Test Seq subVI icon and FP                                           | 49 |

| 4.11 Quiescent current measurement Test Seq subVI CD 00 00                | 50 |

| 4.12 Positive input bias current measurement A Test Seq subVI CD 01 00    | 51 |

| 4.13 Negative input bias current measurement A Test Seq subVI CD 01 01    | 51 |

| 4.14 Positive input bias current measurement B Test Seq subVI CD 01 02    | 52 |

| 4.15 Negative input bias current measurement B Test Seq subVI CD 01 03    | 53 |

| 4.16 Summing junction configuration set up Test Seq subVI CD 02 00        | 54 |

| 4.17 Vin vector Test Seq subVI CD 04 00 and CD 03 01                      | 55 |

| 4.18 Parameters with Summing Junction Test Seq subVI CD 04 00             | 56 |

| 4.19 Parameters with Summing Junction Test Seq subVI CD 04 01 to CD 04 15 | 57 |

| 4.20 Writing results Test Seq subVI CD 05 00                              | 58 |

| 4.21 Test Program CP 00 00                                                | 59 |

| 4.22 Test Program CP 00 01                                                | 60 |

| 4.23 Verification routine Test Program VI CD 00 00                        | 61 |

| 4.24 Variables initialization Test Program VI CD 01 00                    | 62 |

| 4.25 Variables initialization Test Program VI CD 01 01 to CD 01 04        | 63 |

| 4.26 Writing labels Test Program VI CD 02 00 to CD 02 04                  | 64 |

| 4.27 Test Program VI CD 03 00 to CD 03 02                                 | 65 |

# CHAPTER 1 INTRODUCTION

### 1.1 Definition of the problem

A new packaging technology called Chip Scale Package (CSP) will be utilized on the dual operational amplifier OPA2347 in Texas Instruments. Reduction of footprint, price and test time is the cause for implementing this technology. This CSP is developed with a wafer level packaging technology, which means that the device is already packaged after sawing the individual die from the wafer; therefore the cost of packaging is saved.

Normally, a device is tested twice before being sent to the costumer, first at probe and then at final test. Final test must be eliminated for this product because there is no automated handler to support production of the device since this is the first CSP product in the company. The problem is to have another way to test the device for correlation with the automated test equipment (ATE).

#### 1.2 Solution of the problem

An automated bench solution must be developed to support results from the existing ATE. Selecting adequate instruments and socket for the device, designing test boards, adapter boards and test software are all part of this solution. The final system has to be much cheaper than ATE and easily hardware and software configurable.

#### 1.3 Previous work

There is an automated bench solution in Texas Instruments for a dual op amp in other than a CSP package without the implementation of all the DC parameters tested at the ATE. The input bias current (I<sub>B</sub>) and output swing (SW<sub>OUT</sub>) tests are not included in this solution. Neither the hardware nor the software of this existing system are documented.

# 1.4 Chapters summary

Chapter 2 covers the background of the thesis. This is defining the purpose of having an automated bench solution, an introduction to chip scale packaging, an explanation of the op amp, the packaging and electrical characteristics of the device under test (DUT), and the circuitry used to test every DC parameter of the DUT.

Chapter 3 explains the hardware utilized as well as the way to interconnect all. The hardware consists of a modular, computer-based instrumentation platform called PCI eXtensions for instrumentation (PXI) and the design of 2 Adapter Boards and a Device Interface Board (DIB). A Chassis is the core of the system, where different modules are inserted: Digital Multimeter, Analog Output, Multiplexer, Relay Switch, GPIB (General purpose interface bus) and MXI-3. Another MXI-3 card plugged in the PCI slot of a computer is required to interface the software and hardware. The first adapter board has 8 pins in a dual in line package (DIP) format to make the conversion from CSP to DIP. The second one contains gold fingers to make contact with a female edge connector socket. Test circuitry implemented on the DIB is software configurable. The Summing Junction configuration is used test all DC parameters except for Quiescent Current (I<sub>Q</sub>) and Bias Current (I<sub>B</sub>). The bench board has three socketing options: CSP, PDIP and edge connector.

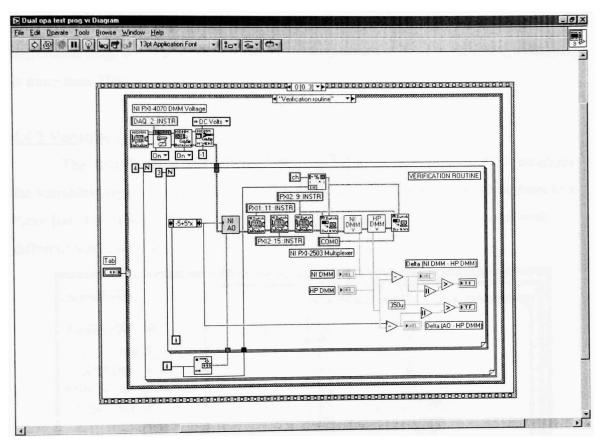

Chapter 4 examines the test software. The program developed in LabVIEW (Laboratory Virtual Instrument Engineering Workbench) is in charge of controlling the test by applying inputs and measure outputs with the PXI system. A verification routine is first executed and then the DC test.

Chapter 5 performs an statistical analysis to support the conclusion that the automated bench solution is repeatable and accurate in relationship with an automated test equipment (ATE) system.

Chapter 6 gives the conclusion of the thesis by providing the difficulties found and their solutions, the ways to improve the test hardware and software, the limitations of the system and how extra features, like test at temperature and multiple test by multiplexing, can be added.

# CHAPTER 2 BACKGROUND

# 2.1 What is a dc automated bench solution?

A dc automated bench solution is actually a low cost set of automated test equipment controlled by software that is easily hardware configurable and transportable. Transportability plays an important role because test at temperature requires the equipment to be moved to the dedicated ovens. A list of the basic elements needed to build a dc automated bench system is given below.

- Software

- Controller (computer)

- Hardware-software interconnection

- Chassis

- Relay board

- Power supply

- Digital multimeter

- Device interface board

Designing any automated bench system is a fascinating challenge for a test engineer. It involves creativity, knowledge, research, programming skills and patience to deal with all problems involved.

First, the engineer must analyze the expected measurements to know the required resolution, power characteristics and other capabilities of test instruments. Then, the device interface board (DIB) must be developed in accordance with socket specifications and design rules for preventing parasitic resistance, inductance and capacitance that could cause incorrect readings. Finally, after verifying all instruments are properly calibrated the real task starts with putting all the pieces together and making it test with accuracy, repeatability and reproducibility.

A detailed explanation of how the dc automated bench solution for the OPA2347 works is explained in Chapter 3 and Chapter 4. Chapter 3 explains the hardware of the system and Chapter 4 the software.

### 2.2 Packaging

When the first transistor was developed by Bell Laboratories in 1947, another problem emerged immediately. The device had to be protected from the outside environment to be commercially viable. Packaging the device was needed to provide physical protection and electrical contact. The problem was not solved until 1954, when the manufacturing processes were perfected [1].

Since then, there have been many types of packages. Some of them have leads to make electrical contact while others have solder bumps or plated flat lands. These interconnects are located in different ways depending on customer needs. Some modern integrated circuit (IC) packages are shown in Figure 2.1 [2].

Figure 2.1 Modern integrated circuit (IC) packages

Having an existing product in a Chip Scale Package (CSP) was the starting point of this thesis. According to IPC (Association Connecting Electronics Industries), the package area of a CSP is less than 1.2 times its die area. When the package-to-die size ratio is more than 1.2 and only solder balls are the board-level interconnect, the device is called a BGA (Ball Grid Array) instead of a CSP. This is not always true because pitch

can also be used to classify a product as CSP. For example, Fujitsu's MicroBGA is a CSP because of its fine pitch of 0.8mm even though its package-to-chip size ratio is more than 1.2. Hitachi Cable's Micro Stud Array Package (MSA) does not fit the CSP definition, but it is also considered CSP because of its fine pitch stud array of 0.5mm. Therefore for a device to be classified as CSP most have either one or both of the characteristics listed below [3].

- Package-to-chip size ratio less than 1.2

- Pitch of less than 1mm

CSPs are then classified into four groups as follows [3].

- Customized-lead-frame-based-CSP or Lead On Chip (LOC)

- CSP with flexible substrate or Chip On Flex (COF)

- CSP with rigid substrate

- Wafer-level redistribution CSP

LOC's purpose is to increase the die-to-package size ratio for lead-frame-based packages. CSP with a flexible or rigid substrate utilizes an interposer to redistribute the original die level pitch to a standard CSP pitch (0.5, 0.65, 0.75, 0.8 or 1 mm) singularly (after dicing the wafer). Wafer-level redistribution CSP uses a metal layer instead of a substrate for pitch redistribution on the wafer [3].

CSPs have different characteristics from each other. Some of them can be seen in Table 2.1. The highlighted terms in Table 2.1 indicate particular characteristics of the Device Under Test (DUT) OPA2347 in CSP. The suffix YED is added to OPA2347 to specify that the product is in CSP. A more complete description of the physical and electrical characteristics of the DUT is explained later.

Table 2.1 Some CSP characteristics

| Package-to-chip size ratio             | <1.2mm           | >1.2mm only if pitch ≤1mm                 |                              |                               | <del></del>                       |

|----------------------------------------|------------------|-------------------------------------------|------------------------------|-------------------------------|-----------------------------------|

| Pitch (mm)                             | 0.5              | 0.65                                      | 0.75                         | 0.8                           | 1                                 |

| CSP group                              | LOC              | Flexible Substrate                        | Rigid substrate              | Wafer-level<br>redistribution |                                   |

| 1 <sup>st</sup> -level<br>interconnect | Wire<br>bonds    | Metallization (Sputtering/Electroplating) | Inner Lead<br>Bonding (ILB)  | Solder<br>bumps               |                                   |

|                                        | C4 solder joints | Stud bumps                                | Ribbonlike<br>flexible leads | Thin film deposition          |                                   |

| Board-level interconnect               | C-lead           | Plated flat lands                         | Solder bumps                 | Solder<br>studs               | Solid<br>core<br>metal<br>spheres |

|                                        | Plated<br>bumps  | Solder pads                               | Solder balls                 | Cu bumps                      |                                   |

| Terminals location                     | Тор              | Bottom                                    | Sides                        |                               |                                   |

| Terminals<br>distribution              | Array            | Frame                                     | Mirror                       |                               |                                   |

| Chip orientation                       | Face up          | Face down                                 |                              |                               |                                   |

| Packaging level                        | Wafer            | Singulated                                |                              |                               |                                   |

### 2.3 Development of the operational amplifier

The main purpose of an Operational Amplifier (Op Amp) is to achieve mathematical functions. The Op Amp can be used to add, subtract, take the derivative and integrate depending on the configuration of elements connected to it. Its design is based on a three terminal active semiconductor device called a transistor. Bell Laboratories invented the transistor in 1947. This invention replaced the use of vacuum tubes, which was the only technology, at that time, capable of amplifying and detecting electric signals since 1907. In the early days of electronics the electrical system used to do mathematical operations was called an analog computer. Today's fabrication is based on silicon, which is the most popular material used in the production of integrated circuits (IC). An integrated circuit is defined as a combination of circuit elements interconnected on a semiconductor material [1].

Texas Instruments (TI) was one of the first companies to manufacture transistors. TI developed a small radio in 1954. Around 100,000 radios were sold during 1955 for \$49.99 each. It was the first radio based on transistors in the market [1].

# 2.4 Definition of the operational amplifier

The operational amplifier is a high gain active element that can be configured with other elements to perform a specific function. Op amps have two differential inputs, one output and two power supply inputs. Since the op amp can amplify AC signals; the op amp is characterized as an active element. Passive elements, such as resistors, capacitors and inductors, only absorb energy. An active element can provide AC energy by converting the DC energy of its power supplies. Figure 2.2 shows the symbol for the Op Amp.

Figure 2.2 Symbol of the operational amplifier.

# 2.4.1 Real operational amplifier

To understand the real behavior of the Op Amp it is necessary to know some properties of its terminals.

The output voltage  $(V_{out})$  of the Op Amp cannot be more than its polarization voltages  $(V_+$  and  $V_-)$ . Another important relationship for  $V_{out}$  is established in Equation 2.1.

$$Vout = -A(V_1 - V_2)$$

Equation 2.1

The high gain, A, has a typical value of  $10^6$ .  $V_1$  is the negative input and  $V_2$  is the positive input.  $V_1$  and  $V_2$  have a high impedance input of  $10^{13}\Omega$ . The potential difference between the two inputs  $(V_1-V_2=V_e)$  is in the range of  $10^{-6}$  to  $10^{-3}$  volts.

Current flowing into the input terminals has a magnitude of  $10^{-12}$  amperes. It is called bias current ( $I_B$ ).

These characteristics have values that are either too small or too large in relationship to the other parameters in the circuit. This makes it possible to model the Op Amp as an ideal operational amplifier. As a consequence, circuit analysis becomes easier.

An explanation of the properties of the ideal operational amplifier is given in the next section.

## 2.4.2 Ideal operational amplifier

The ideal operational amplifier has the following characteristics [1].

- $I_{B+} = I_{B-} \rightarrow 0$

- A → ∞

- $(V_1 \ V_2) \rightarrow 0$  (Condition only satisfied with negative feedback)

Due to  $I_B$  for both inputs  $\to 0$ , the input impedance  $\to \infty$ . If there is negative feedback in the network, the infinite gain causes the inputs to be consider as virtually connected with zero resistance. In this case, if the positive input is grounded, the negative input is virtually grounded. With this principle, many useful circuit configurations can be developed. Even though the gain is considered to  $A \to \infty$ , the output value is limited by the supply voltages.

# 2.5 Device under test (DUT)

The device under test (DUT) OPA2347YED is a dual CMOS (Complementary Metal Oxide Semiconductor) operational amplifier in a chip scale package (CSP). The suffix YED indicates that the device is CSP. Its main DC electrical characteristics are low power consumption with a quiescent current ( $I_Q$ ) of  $20\mu A$  per amplifier, a single or split supply from 2.3V to 5.5V and rail-to-rail inputs and outputs [4].

# 2.5.1 Product data sheet only with DC parameters to be tested

Table 2.2 contains the DC parameters to be tested with their abbreviated names. The condition column establishes test requirements for every test to ensure results within maximum (max) and minimum (min) limits. These limits, if present, are guaranteed values. Typical values are not guaranteed. They were calculated by design to give a reference.

Table 2.2 Product data sheet DC parameters of the OPA2347

| Parameter                                        | Condition                                                                                                    | Min | Тур  | Max | Units |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| Input offset voltage V <sub>OS</sub>             | $V_S = 5.5V$<br>$V_{CM} = (V-) + 0.8V$                                                                       |     | 2    | 6   | mV    |

| Power-Supply Rejection Ratio PSRR                | $V_S$ =2.5V to 5.5V $V_{CM}$ <(V+)-1.7V                                                                      |     | 60   | 175 | μV/V  |

| Common-Mode Rejection Ratio CMRR                 | V <sub>S</sub> =5.5V<br>(V-)-0.2V <v<sub>CM&lt;(V+)-1.7V<br/>(V-)-0.2V<v<sub>CM&lt;(V+)+0.2V</v<sub></v<sub> | 70  | 80   |     | dB    |

| Input Bias Current I <sub>B</sub>                |                                                                                                              |     | ±0.5 | ±10 | pA    |

| Input Offset Current I <sub>OS</sub>             |                                                                                                              |     | ±0.5 | ±10 | pA    |

| Open-Loop Voltage Gain A <sub>OL</sub>           | $V_S$ =5.5V<br>$R_L$ =100k $\Omega$<br>0.015< $V_O$ <5.485V                                                  | 100 | 115  |     | dB    |

| Voltage Output Swing from Rail                   | $R_L=100k\Omega$<br>$A_{OL}>100dB$                                                                           |     | 5    | 15  | mV    |

| Quiescent Current (per amplifier) I <sub>Q</sub> | $I_{O}=0$                                                                                                    |     | 20   | 34  | μΑ    |

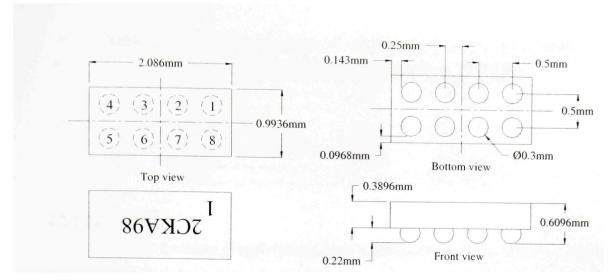

Figure 2.3 represents the top view of the typical input/output (I/O) pin configuration for this dual operational amplifier. All previous packages of the OPA2347 have leads to perform board level interconnections. The number and name of every terminal are shown in Figure 2.3.

Figure 2.3 Typical top-view configuration of a dual op amp

## 2.5.2 Package of the DUT

Because the OPA2347YED has a package-to-chip size ratio less than 1.2 and its pitch is less than 1mm, it is categorized as CSP. Wafer level packaging technology is applied to this product. This means that after sawing the wafer the device is already packaged.

This location of the bond pads on the original integrated circuit (IC) layout had to be reconfigured in order to meet bump on pad CSP technology. The original pads were located in line on one side of the die to facilitate wire bonding for packaging. IC redistribution was required to extend interconnections between active circuitry and bond pads for this new package in order to have a final pitch of 0.5mm. In other words, the original IC layout had to be reconfigured without modifying any circuitry. The original circuitry did not suffer any functional modifications. To facilitate metal trace extension to the corresponding bond pad, it was necessary to rotate operational amplifier B 180 degrees as shown in Figure 2.4.

Figure 2.4 Original and CSP OPA2347 die layout

The area of the original die is 358.8µm \*1731.2µm. On a 6'' wafer approximately 14,000 die can be built. On the other hand, CSP die had to be increased to 888.85µm \*1981.2µm to accommodate solder bumps on pads with a pitch of 0.5mm. As a result, the number of die per wafer was decreased to 7,500. It appears that the cost per die increases for this package, but the original die has to be packaged after sawing and the CSP die does not. This makes wafer level chip scale packaging (WL-CSP) cheaper than other

conventional packaging techniques. It is important to note that the pitch and solder bump size determine the minimum die area for a CSP product.

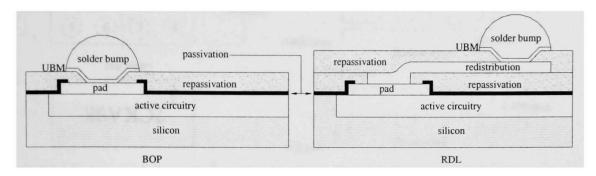

Wafer-level redistribution is the CSP group to which the OPA2347YED belongs. This group defines the way to interconnect solder bumps to existing I/O pads at the wafer level. Redistribution layer (RDL) and Bump On Pad (BOP) are two approaches used.

RDL and BOP require a passivation layer on top of the active circuitry. Then a Benzocyclobutene (BCB) repassivation layer is required. This BCB polymer layer provides [5]:

- Reconfiguration of perimeter I/O pads,

- Planarization of a severe surface topology,

- Size reduction of perimeter I/O pad openings,

- Stress buffer or scratch protection,

- Lower coupling between redistribution lines and active circuitry.

RDL is a metal layer deposition and patterning technique utilized to interconnect existing I/O pads to a solder-bump array. IC layout reconfiguration is not required. Solder bumps are placed on top of this redistribution layer. RDL was not an option for the OPA2347YED. BOP was used instead because die reconfiguration was possible without affecting the circuitry's functionality [5].

BOP requires IC layout reconfiguration to meet CSP specifications. This is the case of the OPA2347YED. An Under Bump Metallurgy (UBM) is placed on top of the pad before solder bump deposition. UBM's diameter for the OPA2347YED is  $247\mu m$ . UBM provides [5]:

- A solder wettable terminal,

- Size and area of the solder connection,

- Adhesion between solder and chip,

- Diffusion barrier between solder and chip,

- Electrical contact to the chip I/O.

Solder bump placement is the last procedure to complete. Composition of 63% Sn and 37% Pb is used in this case. Cross section illustrations for both RDL and BOP are presented in Figure 2.5 [6] to help understand the previous explanations.

Figure 2.5 Cross-section illustrations for BOP and RDL

Since this is the first time TI-Tucson has introduced an operational amplifier in CSP, a comparison with its first competitor will be discussed. National Semiconductor produces the LM2904 in a micro Solder Mask Defined (uSMD) package. Although National Semiconductor is in the head of CSP technology, the electrical and mechanical performance of the LM2904uSMD does not surpass the OPA2347YED [4] [7].

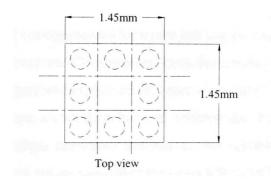

Starting with the I/O array of 2\*4 bumps, the OPA2347YED resembles the conventional pin out for a dual op amp. This is an advantage to the customer since they will be dealing with an identical pin out configuration previously used with the same product in a different package. On the other hand, the LM2904uSMD has an I/O array of 3\*3 bumps without a center bump. Figure 2.6 and Figure 2.7 identify the outlines of these products [7].

Figure 2.6 OPA2347YED outline

Bump diameters of 0.3 mm against 0.16-0.18mm is another advantage for the OPA2347YED because the larger the bump size makes for easier assemble and visual inspection. Even though both have a pitch of 0.5 mm, the LM2904uSMD occupies more area because of its center bump [7].

Figure 2.7 LM2904 uSMD outline

Power consumption is a key factor for a product because the larger the quiescent current ( $I_q$ ) the more expensive to keep the device working. The OPA2347YED consumes 25 times less power than the LM2904uSMD. The electrical performance for both components is illustrated in the following table [4, 7].

Table 2.3 Electrical performance of LM2904uSMD and OPA2347YED

| Parameter                    | LM2904uSMD | OPA2347YED |

|------------------------------|------------|------------|

| Quiescent current            | 500 μΑ     | 20 μΑ      |

| Input bias current           | 40 nA      | ±0.5 pA    |

| Input offset voltage         | 2 mV       | 2 mV       |

| Power supply rejection ratio | 100 dB     | 85 dB      |

| Common mode rejection ratio  | 70 dB      | 80 dB      |

| Bandwidth                    | 1 MHz      | 350 MHz    |

| Slew rate                    | 0.5 V/μs   | 0.17 V/μs  |

# 2.5.3 Applications

There are a variety of applications for this product including portable equipment, battery-powered equipment, two-wire transmitters, smoke detectors and CO detectors [4].

# 2.6 Testing DC parameters

#### 2.6.1 Test circuit

Testing DC parameters of a dual operational amplifier is not an easy task.

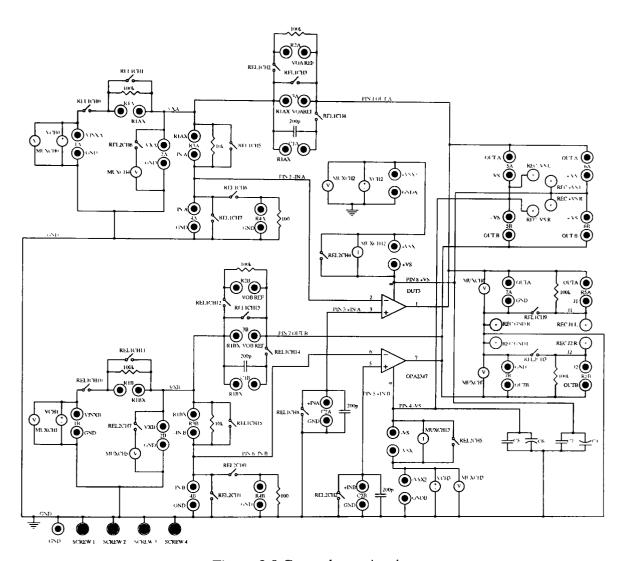

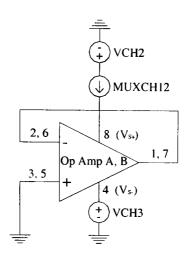

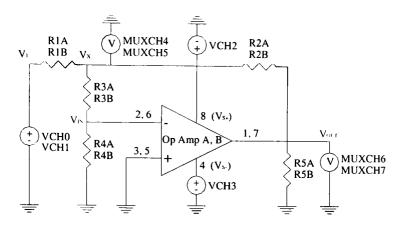

Different circuit configurations and conditions can be applied per parameter. As a result, a general test circuit shown in Figure 2.8 will be used to meet configuration requirements for every test.

Particular circuit configurations for every test can be obtained by closing specific relays of the general test circuit. Consequently only the circuit needed to test each parameter will be displayed and explained. In order to occupy less figure area, two labels separated by a coma or one above the other will differentiate the elements and pins of op amps A and B. Closed relays, parameter definitions, test conditions, with an explanation and special considerations are also included based on OPA2347YED data sheet specifications.

The false summing junction configuration, consisting of five resistors and negative feedback, is used to set the output of an op amp to a desired level by adjusting the input of the circuit [8]. Predominance is granted to this circuit shown in Figure 2.12 because it will help to test the majority of the parameters.

Capacitors are connected as close as possible to each power supply pin of the DUT to ground in order to maintain the voltage applied to each terminal stable. These are called decoupling capacitors.

Figure 2.8 General test circuit

MUXCHxx represent the places where voltage and current measurements must be taken. MUXCH0 to MUXCH7 are for voltage. MUXCH12 to MUXCH13 are for current. VCHx indicates the points where voltages are applied. Since this circuit is implemented on a printed circuit board, circle symbols point out the terminals where resistors,

capacitors, relays (RELxCHxx), multiplexer relays (MUXCHxx) and instruments must be connected. The test temperature is 25°C.

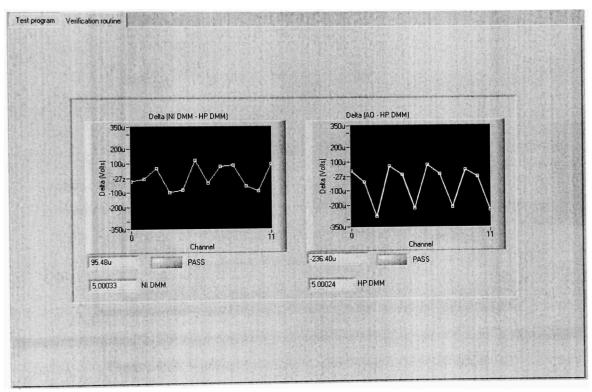

### 2.6.2 Verification routine

Definition: The verification routine verifies if the power supply (AO) and digital multimeter (DMM) are setting and measuring voltages without exceeding an error of  $100\mu V$  (DMM) and  $350\mu V$  (AO) with respect to a well known calibrated DMM.

Closed relays: None

Test circuit configuration: None

Test conditions: Connect DMM 1 and DMM 2 in parallel.

Steps: Apply 3 voltage levels (-5, 0 and 5 V) per each voltage channel VCH0. VCH1, VCH2 and VCH3 while measuring them with both DMM 1 and DMM 2 through MUX0, MUX3, MUX6 and MUX7. Having DMM 2 as a reference, readings taken from DMM 1 and the desired voltage level cannot differ by more than  $100\mu V$  and  $350\mu V$ .

Special considerations: Make sure all instruments have the same ground reference.

# 2.6.3 Quiescent current test (I<sub>O</sub>)

Definition: Power supply current of the op amp when its output current is zero [8].

Relays in use: REL1CH3, REL1CH5, REL1CH8, REL1CH13, REL1CH15, REL2CH2 and REL2CH5.

Test circuit configuration: Voltage follower shown in Figure 2.9.

Test conditions: No load

Expected value: 40µA (20µA per amplifier).

Steps: Apply  $V_{S+}=2.75 \text{ V}$ ,  $V_{S-}=-2.75 \text{ V}$ , close all relays in use and then measure MUXCH12 current. Divide this reading by 2 to obtain I<sub>O</sub> per amplifier.

Special considerations: Verify if the op amp is oscillating with the use of an oscilloscope connected to the output. If the op amp oscillates due to parasitic elements on the DIB, a pole-zero analysis previously done by the designer of the DUT must be studied to correct this problem.

Figure 2.9 Quiescent current (I<sub>O</sub>) test circuit

# 2.6.4 Positive input bias current (I<sub>B+</sub>)

Definition: The current flowing into the positive input of the op amp [8].

Test configuration: Stop watch integration shown in Figure 2.10.

Relays in use: REL1CH3, REL1CH5, REL1CH8, REL1CH9, REL1CH13, REL1CH15, REL2CH2, REL2CH3, REL2CH4 and REL2CH5.

Test conditions:  $R_L=R5=100k\Omega$  and C2=200pF.

Expected value: ±0.5pA.

Steps: Apply  $V_{S+}$ =2.75 V,  $V_{S-}$ =-2.75V, close all the relays, open the relay REL1CH8/REL2CH2, wait for signal settling  $\Delta_{START}$ >10ms before taking  $V_{OUT1}$ , wait  $\Delta_{T}$ >500ms, measure  $V_{OUT2}$  and then compute  $I_{B+}$ =-C2\*( $V_{OUT1}$ - $V_{OUT2}$ )/( $\Delta_{T}$ ). The negative sign corrects polarity of the input bias current.

Explanation: Since the current to be measured is in the order of pA and a DMM capable of measuring it is very expensive, a capacitor is used to integrate this current over a period of time ( $\Delta_T$ ) to obtain the corresponding voltage change ( $V_{OUT1}$ - $V_{OUT2}$ ). The relationship of the voltage and current through a capacitor is  $V_C$ = $C^*$   $I_C^*$ dt. C2=200pF

was calculated by using the typical value for  $I_{B+}$ =0.5pA, and choosing  $\Delta_T$ =1sec and  $(V_{OUT1}-V_{OUT2})$ =2.5mV.

Special considerations: Connect an oscilloscope at the output to verify the circuit is integrating properly without leaking, saturation or oscillation. Leaking increases the voltage rate of change at the output resulting in a higher measurement. Saturation produces a zero measurement because the output would reach either of the supplies in less than 100ms once the relay is open. Oscillation generates a sine wave at the output of the op amp. Accuracy can be improved by incrementing Δt or decrementing C2. Both ways minimize noise by allowing a larger (V<sub>OUT1</sub>-V<sub>OUT2</sub>). Capacitance reduction is a concern when on-board parasitics of the same value are present. When measuring pA a glass capacitor is preferred due to its better performance with respect to any other type.

Figure 2.10 Positive input bias current (I<sub>B+</sub>) test circuit

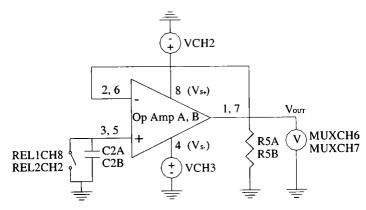

# 2.6.5 Negative input bias current (I<sub>B</sub>-)

Definition: The current flowing into the negative input of the op amp [8].

Test configuration: Stop watch integration shown in Figure 2.11.

Relays in use: REL1CH3, REL1CH4, REL1CH5, REL1CH8, REL1CH9, REL1CH13, REL1CH14, REL1CH15, REL2CH2, REL2CH3, REL2CH4 and REL2CH5.

Test conditions:  $R_L$ =R5= $100k\Omega$  and C1=200pF.

Expected value: ±0.5pA.

Steps: Apply  $V_{S+}$ =2.75 V,  $V_{S-}$ =-2.75 V, close all the relays, open the relay REL1CH3/REL2CH13, wait for signal settling  $\Delta_{START}$ >10ms before taking  $V_{OUT1}$ , measure  $V_{OUT2}$  after waiting  $\Delta_{T}$ >500ms and then compute  $I_{B-}$ =C1\*( $V_{OUT1}$ - $V_{OUT2}$ )/( $\Delta_{T}$ ).

Explanation: Although the capacitor for this test is connected from the output to the negative input of the op amp, the same principle used to obtain  $I_{B+}$  is applied for  $I_{B-}$ .

Special considerations: Nearby circuitry other than the one in use can be a source of noise. Although glass capacitors are very expensive they provide the best performance for this test.

Figure 2.11 Negative input bias current (I<sub>B</sub>-) test circuit

#### 2.6.6 Input offset current (I<sub>OS</sub>)

Definition: The difference between  $I_{B+}$  and  $I_{B-}$  [8].

Expected value: Less than  $\pm 0.5 pA$  due to the expected values for  $I_{B+}$  and  $I_{B-}$  are in the same range.

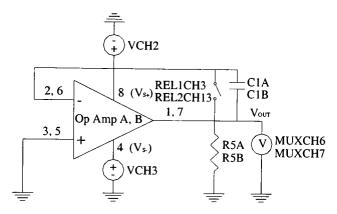

#### 2.6.7 False summing junction test circuit

The false summing junction configuration will be used to test the rest of the DC parameters. Five resistors and negative feedback form the basic idea of this circuit illustrated in Figure 2.12. Both VCH2 and VCH3 can be positive or negative depending on the test conditions [8].

Values for all resistors are shown below:

•

$$R_1 = R_2 = 100k\Omega$$

- $R_3 = 10k\Omega$

- $R_4 = 100\Omega$

- R<sub>5</sub> = disconnected

Figure 2.12 False summing junction test circuit

The load resistance  $R_L$  specified in the product data sheet (PDS) is  $100k\Omega$ . It is not the one connected between the output and ground  $(R_5)$  but the parallel combination of  $R_2$  and  $R_5$  ( $R_L=R_5$ |  $R_2=100k\Omega$ ). Therefore if choosing  $R_2=100k\Omega$ , then  $R_5$  must be disconnected. With these resistor values and considering the ideal behavior of the op amp ( $I_B=0$ ), the voltage between the two inputs  $V_{IN}$  is amplified  $(1+R_3/R_4)$  times at  $V_X$ .

$$V_{IN} = V_X / (1 + R_3 / R_4)$$

Equation 2.2

This circuit is used to set  $V_{OUT}$  at a desired voltage by adjusting the input of the circuit  $(V_1)$ . The relationship between  $V_{OUT}$  and  $V_{IN}$  is essential for calculating the remaining DC parameters. Even though the positive input is grounded, the common mode voltage  $(V_{CM})$  is not always 0V as for split supplies but the difference between 0V and the output being at the middle point of the supplies. This means that the  $V_{CM}$  applied is with respect to the middle point of the supplies. The supplies used for each test are

specified in the PDS with respect to an initial  $V_{CM}$ . Since the positive input for the SJC is grounded, this initial  $V_{CM}$  is 0V. Substitute  $V_{CM}$ =0V to obtain the supplies per test.  $V_S$  is the difference between the positive  $(V_{S+})$  and the negative  $(V_{S-})$  supply.

Relays closed for this circuit are REL1CH0, REL2CH6, REL1CH6, REL1CH2, REL1CH8, REL1CH10, REL2CH7, REL2CH0, REL1CH12, REL2CH2, REL2CH4 and REL2CH5.

# 2.6.8 Input offset voltage (Vos)

Definition: V<sub>IN</sub> when V<sub>OUT</sub> is at the middle point of the two supplies [8].

Test conditions:  $V_S=5.5V$ ,  $V_{CM}=(V_-)+0.8V$

Expected value: 2mV

Steps: Apply  $V_{S+}$ =4.7V,  $V_{S-}$ =-0.8V, adjust the input to set the output at 1.95V, measure  $V_X$  to calculate  $V_{IN}$ = $V_{OS}$ .

Explanation: Measuring the input offset voltage is the easiest test but it varies with the common mode voltage ( $V_{CM}$ ) applied to the positive and negative input. By setting the output at the middle point of the supplies when adjusting the input as specified in the test conditions, a  $V_{CM}$  of -1.95V is obtained.

# 2.6.9 Power supply rejection ratio (PSRR)

Definition: The change of  $V_{IN}$  with  $V_S$  [8].

Test conditions:  $V_S=2.5V$  to 5.5V,  $V_{CM}<(V+)-1.7$

Expected value:  $60\mu V/V$ .

Steps: Apply  $V_{S+}=3.3V=V_{S1+}$ ,  $V_{S-}=-2.2V=V_{S1-}$ , adjust the input to have  $V_{OUT}$  at 0.55V, measure  $V_X$  to calculate  $V_{IN}=V_{IN1}$ . Set  $V_{S+}=1.8V=V_{S2+}$ ,  $V_{S-}=-0.7V=V_{S2-}$ , adjust the input to have  $V_{OUT}$  at 0.55V, measure  $V_X$  to calculate  $V_{IN}=V_{IN2}$ , compute PSRR as shown in Equation 2.3.

$$PSRR = (V_{IN1} - V_{IN2}) / 2(V_{S1+} V_{S2+})$$

Equation 2.3

Explanation: PSRR is used to measure the ability of the op amp to reject a symmetrical change in  $V_S$  reflected at  $V_{IN}$ . The  $V_{CM}$  remains at the same level  $(V_{CM1}=V_{CM2}=-0.55V)$  when changing  $V_S$  to eliminate the  $V_{CM}$  contribution in the PSRR calculation. This is obtained by changing the supplies symmetrically.

Special considerations: Make sure decoupling capacitors are connected as close as possible from  $V_{S+}$  and  $V_{S-}$  to ground.

# 2.6.10 Common-mode rejection ratio half scale (CMRRh)

Definition: The change of  $V_{IN}$  with  $V_{CM}$  at half scale [8].

Test conditions:  $V_S=5.5V$ ,  $(V-)-0.2V < V_{CM} < (V+)-1.7$

Expected value: 100µV/V (80dB).

Steps: Apply  $V_{S+}=5.7V=V_{S1+}$ ,  $V_{S-}=0.2V=V_{S1-}$ , adjust the input to have  $V_{OUT}$  at  $2.95V=-V_{CM1}$ , measure  $V_X$  to calculate  $V_{IN}=V_{IN1}$ . Set  $V_{S+}=1.7V=V_{S2+}$ ,  $V_{S-}=-3.8V=V_{S2-}$ , adjust the input to have  $V_{OUT}$  at  $-1.05V=-V_{CM2}$ , measure  $V_X$  to calculate  $V_{IN2}$ , compute CMRRh as shown in Equation 2.4.

$$CMRRh = (V_{IN1} - V_{IN2}) / (V_{CM1} - V_{CM2})$$

Equation 2.4

Explanation: CMRR is used to measure the ability of the op amp to reject a change in the  $V_{CM}$  reflected at  $V_{IN}$ . The  $V_{CM}$  is not kept at the same level when changing the supplies. The supplies are moved asymmetrically keeping  $V_S$  fixed to eliminate the supplies contribution in the CMRR calculation. The  $V_{CM}$  change of 4V serves to classify this CMRR measurement as half scale.

# 2.6.11 Common-mode rejection ratio full scale (CMRRf)

Definition: The change of  $V_{\text{IN}}$  with  $V_{\text{CM}}$  at full scale [8].

Test conditions:  $V_S=5.5V$ ,  $(V-)-0.2V < V_{CM} < (V+)+0.2$

Expected value: 316.227µV/V (70dB).

Steps: Apply  $V_{S+}=5.7V=V_{S1+}$ ,  $V_{S-}=0.2V=V_{S1-}$ , adjust the input to have  $V_{OUT}$  at  $2.95V=-V_{CM1}$ , measure  $V_X$  to calculate  $V_{IN}=V_{IN1}$ . Set  $V_{S+}=-0.2V=V_{S2+}$ ,  $V_{S-}=-5.7V=V_{S2-}$ , adjust the input to have  $V_{OUT}$  at  $-2.95V=-V_{CM2}$ , measure  $V_X$  to calculate  $V_{IN}=V_{IN2}$ , compute CMRRf as shown in Equation 2.5.

$$CMRRf = (V_{IN1} - V_{IN2}) / (V_{CM1} - V_{CM2})$$

Equation 2.5

Explanation: The  $V_{\text{CM}}$  change of 5.9V serves to classify this CMRR measurement as full scale.

# 2.6.12 Open loop voltage gain (A<sub>OL</sub>)

Definition: The change of  $V_{OUT}$  with  $V_{IN}$  [8].

Test conditions:  $V_S=5.5V$ ,  $(V_-)+0.005V < V_{OUT} < (V_+)-0.005V$

Expected value: 1.778µV/V (115dB)

Steps: Apply  $V_{S+}$ =2.75V,  $V_{S-}$ =-2.75V, adjust the input to have  $V_{OUT}$ =2.74V= $V_{OUT1}$ , measure  $V_X$  to calculate  $V_{IN}$ = $V_{IN1}$ , adjust the input to obtain  $V_{OUT}$ =-2.74V= $V_{OUT2}$ , measure  $V_X$  to calculate  $V_{IN}$ = $V_{IN2}$ , compute  $A_{OL}$  as shown in Equation 2.6.

$$A_{OL} = | (V_{OUT1} \quad V_{OUT2}) / (V_{IN1} \quad V_{IN2}) |$$

Equation 2.6

Explanation: The name of this measurement infers that the op amp must be in open loop in order to measure a change in  $V_{OUT}$  with  $V_{IN}$ . This circuit configuration is not possible because if applying a  $V_{IN}$  of  $\pm 1 \text{mV}$ , which is the typical accuracy of a DMM, the output would be limited by either of the supplies instead of being amplified 562429.69 times. Therefore a fix voltage change in the output divided by the corresponding change

in  $V_{IN}$  is used for the  $A_{OL}$  calculation. Notice that the swing condition for this test (more than 5mV from the rail) is not the same specified in the PDS (more than 15mV from the rail). This is because the op amp can actually swing to 5mV, based on data collected, maintaining a linear relationship between the output and the  $V_{OS}$ .

# 2.6.13 Voltage output swing from rail (SW<sub>out+</sub>)

Definition: The maximum voltage the output of the op amp can swing from each rail maintaining a linear relationship with respect to  $V_{OS}$ .

Test circuit configuration: Summing junction configuration when the open loop gain is performed.

Test conditions:  $R_L=R5=100k\Omega$ ,  $A_{OL}>100dB$

Expected value: 5mV (15mV maximum)

Steps: Obtain a plot of VOUT versus VOS by adjusting the input. Determine the values for VOUT in which the plot becomes not linear. These values are the positive and negative voltage output swing from rail. Since this technique is time consuming, one can only do a pass/fail test by setting the output of the op amp at least 15mV from the rail by adjusting the input and verify if the output can be set in that range, otherwise the device fails for this parameter.

Explanation: Since the output set in the  $A_{OL}$  test is in the expected range for this parameter, the positive and negative voltage outputs of the op amp used to calculate  $A_{OL}$  can be used to verify if the output can swing at least 15mV from each rail.

# CHAPTER 3 TEST HARDWARE

# 3.1 Socketing the DUT

Socketing and surface mounting a device to adapter boards serve to make electrical contact to the I/O. One is as important as the other. Although the customer is going to solder the component to a printed circuit board (PCB), it is cheaper to use a CSP socket for testing. Assembling only 20 units on adapter boards equals the price of a CSP socket. The OPA2347YED is tested on adapter boards and also with a clam shell type CSP socket having springs to provide the board level interconnection. Thus the CSP socket is not soldered to the device interface board (DIB) but mechanically attached with four nuts. This feature protects the DIB from socket replacement because unsoldering usually causes damage. Edge connector and dual in line package (DIP) are the socketing versions for the adapter boards.

## 3.2 Printed circuit board design

#### 3.2.1 Protel

Protel is the software utilized to design the printed circuit boards. The purpose of this section is not to explain how to use the software, but to provide the key steps to generate a PCB layout from a circuit schematic.

One project database file stores as many schematic, layout, schematic library or layout library type files as wanted. A schematic file contains any kind of circuit diagram. It is built with symbols created and stored in schematic libraries. A layout file is a bylayer physical representation of a circuit diagram. Schematic and layout can be either independent or mutually synchronized so that any change performed in one is updated in the other. It is always easier to draw the schematic first and then Protel generates the layout. For doing this, the user must type on every symbol placed on the schematic file its layout symbol reference. Nodes are also synchronized [9].

Once every symbol of the layout, also called the footprint, has been oriented and located, the trace width has to be set. All interconnection nodes are automatically traced, based on layout rules, when the autoroute command is activated. Then, traces are manually corrected and revised with the error checklist command. Finally, the following files along with board characteristics have to be zipped and sent to the manufacturer [9].

- Gerber files

- NC drill files

#### 3.2.2 Adapter boards

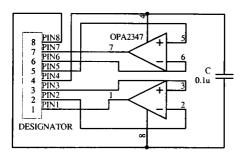

As previously mentioned, two adapter boards are used to attach the OPA2347YED and make electrical contact to the I/O. The circuit schematic created for both is shown in Figure 3.1. Three symbols appear on that circuit. "C" represents the capacitor footprint of the layout. "DESIGNATOR" represents either the 2\*4 hole array for the DIP version or the two-sided 4 pad array for the edge connector type. "OPA2347" represents the footprint of the OPA2347YED.

Figure 3.1 Schematic for adapter boards

Then PIN1 to PIN8 labels next to every interconnection wire serves for node identification. This is necessary when performing layout generation based on this circuit schematic.

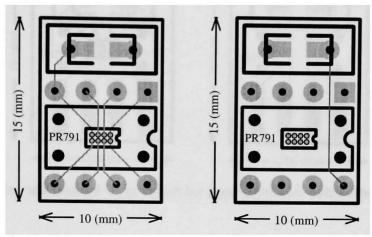

Top and bottom layer drawings for both adapter boards are shown in Figure 3.2 and Figure 3.3. The capacitor footprint allows either surface mounted or lead based

technologies. Plated holes are indicated as solid black circles with gray contour. Holes are simply solid black holes. CSP pads are solid gray circles with black contour. The 2\*4 DIP plated hole array for board PR791 is where pins are inserted and solder to make electrical and mechanical contact to a DIP socket.

Figure 3.2 Top and bottom layer layout for DIP adapter board PR791

The black contour around CSP pads specifies that the solder mask opening has to be larger than the pad size. It is called non-solder mask defined (NSMD). NSMD prevents solder bridging among solder balls when reflowing is performed. Reflow is the process used to solder the CSP to the board. It consists of applying solder paste on pads, placing the CSP on top of them and generating air hot flux to solder every ball to its respective pad. The amount of solder paste as well as the pad size are based on ball size. The pad size diameter in this case is 0.275mm and solder mask opening is 0.375mm [10].

It is important to know how much down pressure the assembly house will apply when handling the CSPs. Cracks on silicon may be caused if the pick and place piece of equipment is not set up properly. The OPA2347YED handles a pick and place down force of 80 grams (10grams/ball).

Board PR792 (edge connector) is not a common way to adapt a device but a more economical solution. Buying and assembling pins is eliminated with this version.

Fabrication cost may be more expensive in comparison with board PR791 (DIP) but the

final cost, including assembly, is less. Four plated holes called vias connect the top and bottom layers. Characteristics for boards PR791 and PR792 is in Table 3.1.

Figure 3.3 Top and bottom layer layout for edge connector adapter board PR792

| Characteristic      | Value                          |

|---------------------|--------------------------------|

| Board material      | Polyimide                      |

| Board thickness     | 1.5748mm (62mil)               |

| Trace material      | Immersion gold                 |

| Trace thickness (T) | 25.4µm (1mil)                  |

| Trace width (W)     | 0.1524mm (4mil)                |

| Mask type           | LPI-GREEN 2-Sides              |

| CSP pad diameter    | 0.275mm                        |

| Land pattern        | Non-solder mask defined (NSMD) |

0.375mm

Table 3.1 Adapter board characteristics

#### 3.2.3 Device interface board

NSMD diameter

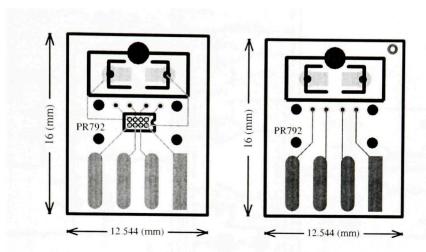

As previously stated, the test circuit is implemented on a printed circuit board named bench board or device interface board (DIB). Three socketing options are included on this board: edge connector, DIP and CSP. Symbols for the circuit schematic shown in Figure 3.4 were first created, placed, PCB layout related, and then interconnected including node identifiers.

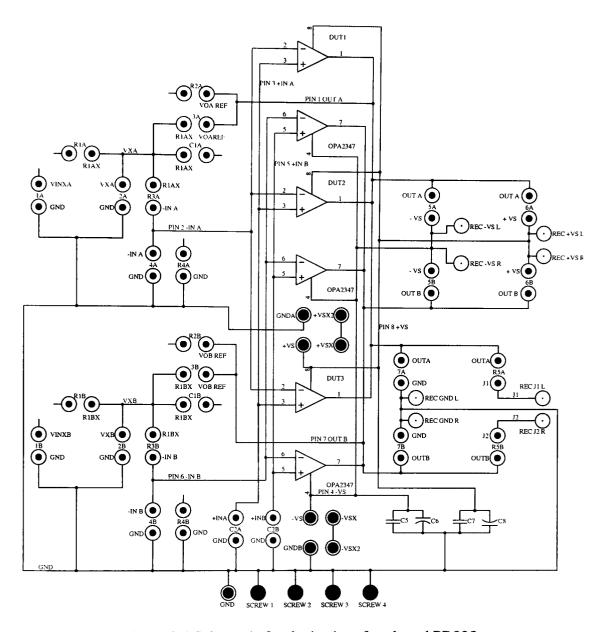

Figure 3.4 Schematic for device interface board PR825

The schematic-to-layout symbol representations are listed below.

- DUT1 → Edge connector socket footprint

- DUT2 → CSP socket footprint

- DUT3  $\rightarrow$  DIP socket footprint

- Solid circle → Hole for screwing stand off

- Large solid circle → Banana receptacle footprint

- Medium solid circle → Mini banana receptacle footprint

- Small solid circle → Resistor receptacle footprint

- Capacitor → Standard capacitor footprint

All footprints and interconnections are found in Figure 3.5 and Figure 3.6.

Figure 3.5 Top layer layout for device interface board PR825

Figure 3.6 Bottom layer layout for device interface board PR825

Table 3.2 summarizes the characteristics of the board PR825.

Table 3.2 Device interface board characteristics

| Characteristic                | Value             |

|-------------------------------|-------------------|

| Board material                | FR4               |

| Board thickness               | 1.574mm (62mil)   |

| Trace material                | Hard body gold    |

| Trace thickness (T)           | 25μm (1mil)       |

| Trace width (W)               | 0.307mm (12mil)   |

| Trace width on DUT2 area (W2) | 12 mil (307μm)    |

| Mask type                     | LPI-GREEN 2-Sides |

#### 3.3 PXI system

#### 3.3.1 Introduction

PXI means Peripheral component interconnect (PCI) eXtensions for Instrumentation. It is a modular, computer-based instrumentation platform based on the PCI bus. PCI is an industry-standard, high-speed databus. The elements of a PXI system are listed below [11].

- Controller

- Chassis

- Modules (cards)

A controller can be either a personal computer or an embedded Pentium class or higher computer and peripherals. The main disadvantage between these two options is price and speed. A personal computer can be four times less expensive, but also slower than the embedded option. The embedded option can perform real time applications because the system is dedicated to interact with the modules and nothing else [11].

A chassis is in charge of providing mechanical protection, ventilation, power supply and interface to the modules inserted in it.

PXI modules are classified as multifunction boards and instruments. A multifunction board can be of any type, like a general purpose relay switch, relay multiplexer, analog-to-digital, digital-to-analog, image acquisition, motion control, etc. Instruments can vary from digital multimeters, oscilloscopes, power supplies, spectrum analyzers, and many others [11].

One way to interface a desktop computer with PXI modules is through a link called MXI-3 consisting of a MXI-3 module, cable and PCI card [11].

External instruments like the high resolution 8½ digit DMM HP-3458A or the 6½ digit DMM HP-34401A can communicate with the PXI chassis through a PXI general purpose interface bus (GPIB) card. The instrument receives and sends GPIB commands from and to the controller to perform a specific function [11, 12, 13].

The controller and modules from National Instruments (NI) utilized to test the OPA2347YED with a NI PXI chassis are explained in this section and listed below.

- 1 MXI-3 link

- 1 18-module PXI chassis

- 1 GPIB module with Ethernet port (NI PXI-8212)

- 2 General purpose relay switch card (NI PXI-2565)

- 1 Electromechanical relay multiplexer card (NI PXI-2503)

- 1 6½ Digital multimeter (NI PXI-4070)

- 1 Analog output (NI PXI-6704)

The interconnection among modules and DIB is also covered.

#### 3.3.2 Controller

A personal computer (PC) is the controller for the automated bench system. A Pentium I running at 100MHz with 96Mb of RAM is good enough for the tester. The PC communicates with the PXI modules through a MXI-3 link.

#### 3.3.3 18-slot PXI chassis (PXI-1006 chassis)

In order to have extra slots for future modules, an 18-slot PXI chassis was chosen. The current system comes with PXI and CompactPCI module capability and only occupies 9 slots. Modules are easily plugged into the system, like drawers into a desk. Before connecting the chassis with the MXI-3 cable to the computer, all drivers must be installed on the PC. The PC is turn on after the PXI system, so that all inserted modules are recognized [14].

#### 3.3.4 General purpose relay switch card (NI PXI-2565)

The NI PXI-2565 is a 16-channel general purpose electromechanical relay switch card. The relays can switch 30V DC at 5A DC with a resistive load. They have a contact resistance of  $30m\Omega$  and operate (open or close) in no more than 10ms. Figure 3.7 shows the NI PXI-2565 switch architecture [15].

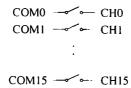

Figure 3.7 NI PXI-2503 Switch architecture

#### 3.3.5 Electromechanical relay multiplexer card (NI PXI-2503)

A multiplexer is a set of electromechanical or semiconductor switches with a common output that can select one of a number of input signals.

The NI PXI-2503 is an electromechanical relay multiplexer card in a PXI/Compact PCI format with 24\*1 two-wire multiplexer. It also operates with 4 banks of 6 two-wire channels (2-wire quad 6\*1), each bank having its own common two-wire output. The board is software-configurable as shown below [16].

- 1-wire MUX

- 2-wire 12\*1 12\*1

- 2-wire MUX

- 2-wire quad 6\*1

- 4-wire MUX

- 6\*4 matrix

The relays have a contact resistance of  $100m\Omega$ , operate (open or close) in no more than 5ms and can switch 30V DC at 1A DC with a resistive load. Figure 3.8 shows the NI PXI-2503 switch architecture [16].

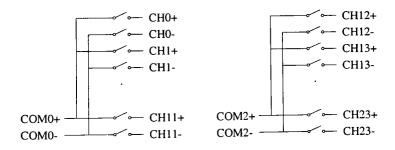

Figure 3.8 NI PXI-2503 2-wire 12\*1 12\*1 switch architecture

The NI PXI-2503 has a front panel 68-pin female connector. Table 3.3 shows the pin assignments. The NI TB-2505 is a front panel mounting screw terminal block that is plugged into the female connector in order to electrically access the channels, common terminals and other pins of the NI PXI-2503. The pin assignments for the two-wire mode using the NI TB-2505 are shown in Table 3.4 [16].

Table 3.3 NI PXI-2503 front connector pin assignments for two-wire mode

| Pin name      | Pin# | Pin# | Pin name    |

|---------------|------|------|-------------|

| CJS0-         | 34   | 68   | CJS0+       |

| CH0-          | 33   | 67   | CH0+        |

| CH1-          | 32   | 66   | CH1+        |

| CH2-          | 31   | 65   | CH2+        |

| CH3-          | 30   | 64   | CH3+        |

| CH4-          | 29   | 63   | CH4+        |

| CH5-          | 28   | 62   | CH5+        |

| COM0-         | 27   | 61   | COM0+       |

| COM1-         | 26   | 60   | COM1+       |

| CH6-          | 25   | 59   | CH6+        |

| CH7-          | 24   | 58   | CH7+        |

| CH8-          | 23   | 57   | CH8+        |

| 1_WIRE_LO_REF | 22   | 56   | GND         |

| CH9-          | 21   | 55   | CH9+        |

| CH10-         | 20   | 54   | CH10+       |

| CH11-         | 19   | 53   | CH11+       |

| AB0-          | 18   | 52   | AB0+        |

| AB1-          | 17   | 51   | AB1+        |

| CH12-         | 16   | 50   | CH12+       |

| CH13-         | 15   | 49   | CH13+       |

| CH14-         | 14   | 48   | CH14+       |

| CH15-         | 13   | 47   | CH15+       |

| CH16-         | 12   | 46   | CH16+       |

| CH17-         | 11   | 45   | CH17+       |

| COM2-         | 10   | 44   | COM2+       |

| COM3-         | 9    | 43   | COM3+       |

| +5 V          | 8    | 42   | SCAN_ADV    |

| GND           | 7    | 41   | EXT_TRIG_IN |

| CH18-         | 6    | 40   | CH18+       |

| CH19-         | 5    | 39   | CH19+       |

| CH20-         | 4    | 38   | CH20+       |

| CH21-         | 3    | 37   | CH21+       |

| CH22-         | 2    | 36   | CH22+       |

| CH23-         | 1    | 35   | CH23+       |

Table 3.4 NI PXI-2503 pin assignments for two-wire mode using the NI TB-2505

| Pin #      | Pin name | Pin # | Pin name | Pin # | Pin name | Pin # | Pin name |

|------------|----------|-------|----------|-------|----------|-------|----------|

| 10         | COM2-    |       |          | 09    | COM3-    |       |          |

| 44         | COM2+    |       |          | 43    | COM3+    |       |          |

| 13         | CH15-    | 05    | CH19-    | 01    | CH23-    |       |          |

| <b>4</b> 7 | CH15+    | 39    | CH19+    | 35    | CH23+    | 41    | TRIG IN  |

| 14         | CH14-    | 06    | CH18-    | 02    | CH22-    | 42    | SCANADV  |

| 48         | CH14+    | 40    | CH18+    | 36    | CH22+    |       |          |

| 15         | CH13-    | 11    | CH17-    | 03    | CH21-    |       |          |

| 49         | CH13+    | 45    | CH17+    | 37    | CH21+    |       |          |

| 16         | CH12-    | 12    | CH16-    | 04    | CH20-    | "     |          |