# EMERALD-P CPU MODULE SK-86R12-CPU01

# **USERGUIDE**

# **Revision History**

| Date        | Issue                                       |

|-------------|---------------------------------------------|

| 30 Nov 2011 | V1.0 Herbert Hönig First release            |

| 07 Dec 2011 | V1.01 Herbert Hoenig Corrected typo         |

| 12 Jan 2012 | V1.1 Herbert Hönig Added PSMODE information |

|             |                                             |

This document contains 11 pages.

### Warranty and Disclaimer

To the maximum extent permitted by applicable law, Fujitsu Semiconductor Europe GmbH restricts its warranties and its liability for **all products delivered free of charge** (eg. software include or header files, application examples, target boards, evaluation boards, engineering samples of IC's etc.), its performance and any consequential damages, on the use of the Product in accordance with (i) the terms of the License Agreement and the Sale and Purchase Agreement under which agreements the Product has been delivered, (ii) the technical descriptions and (iii) all accompanying written materials. In addition, to the maximum extent permitted by applicable law, Fujitsu Semiconductor Europe GmbH disclaims all warranties and liabilities for the performance of the Product and any consequential damages in cases of unauthorised decompiling and/or reverse engineering and/or disassembling. **Note, all these products are intended and must only be used in an evaluation laboratory environment**.

- 1. Fujitsu Semiconductor Europe GmbH warrants that the Product will perform substantially in accordance with the accompanying written materials for a period of 90 days form the date of receipt by the customer. Concerning the hardware components of the Product, Fujitsu Semiconductor Europe GmbH warrants that the Product will be free from defects in material and workmanship under use and service as specified in the accompanying written materials for a duration of 1 year from the date of receipt by the customer.

- 2. Should a Product turn out to be defect, Fujitsu Semiconductor Europe GmbH's entire liability and the customer's exclusive remedy shall be, at Fujitsu Semiconductor Europe GmbH's sole discretion, either return of the purchase price and the license fee, or replacement of the Product or parts thereof, if the Product is returned to Fujitsu Semiconductor Europe GmbH in original packing and without further defects resulting from the customer's use or the transport. However, this warranty is excluded if the defect has resulted from an accident not attributable to Fujitsu Semiconductor Europe GmbH, or abuse or misapplication attributable to the customer or any other third party not relating to Fujitsu Semiconductor Europe GmbH.

- To the maximum extent permitted by applicable law Fujitsu Semiconductor Europe GmbH disclaims all other warranties, whether expressed or implied, in particular, but not limited to, warranties of merchantability and fitness for a particular purpose for which the Product is not designated.

- 4. To the maximum extent permitted by applicable law, Fujitsu Semiconductor Europe GmbH's and its suppliers' liability is restricted to intention and gross negligence.

#### NO LIABILITY FOR CONSEQUENTIAL DAMAGES

To the maximum extent permitted by applicable law, in no event shall Fujitsu Semiconductor Europe GmbH and its suppliers be liable for any damages whatsoever (including but without limitation, consequential and/or indirect damages for personal injury, assets of substantial value, loss of profits, interruption of business operation, loss of information, or any other monetary or pecuniary loss) arising from the use of the Product.

Should one of the above stipulations be or become invalid and/or unenforceable, the remaining stipulations shall stay in full effect

## Contents

| Revisi | sion History            | 2  |

|--------|-------------------------|----|

| Warra  | anty and Disclaimer     | 3  |

|        | ents                    |    |

| 0 In   | Introduction / Features |    |

|        | System Overview         |    |

|        | Startup CPU Module      |    |

|        |                         |    |

| 3.1    | <u> </u>                |    |

| 3.2    | DIP Switches            | 8  |

| 3.3    | Power presets           | 10 |

| 3.4    | USB HOST                | 10 |

| 3.5    | LEDs                    | 10 |

| 4 A    | Appendix                | 11 |

| 4.1    | Used literature         | 11 |

| 4.2    | Figures                 | 11 |

#### 0 Introduction / Features

Here you will find a short summary and overview of the features that the SK-86R12-CPU01 Module offers.

#### It provides

- 3x APIX2 Video Outputs, 1x APIX2 Video Input

- 1x USB Host

- JTAG/Trace Debug Connectors (20 Pin + Mictor Connector)

- NOR Flash 1GBit

- DDR3 2x 2GBit (= 512MByte)

- NOR Flash usage with 16 oder 32 Bit access

- Base Connectors for use with Emerald European Base Board SK-86R11-BASE and Japanese Baseboard MB86R11EVB-BASE01

#### Mechanical dimensions:

- PCB: 117 x 127 mm

For details about interfaces refer to the Emerald-P Hardware Manual (see appendix).

## 1 System Overview

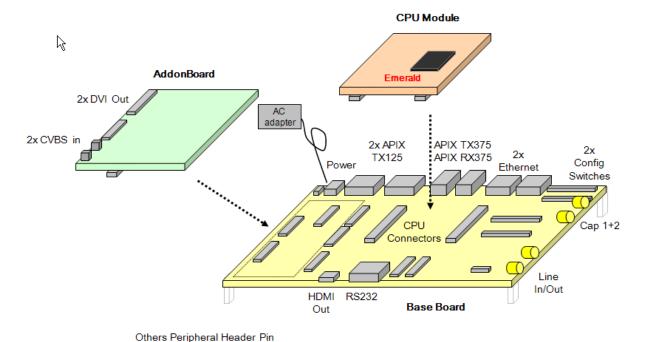

The Emerald-P system consists of three modules:

- CPU module (Emerald-P chip, USB connector): SK-86R12-CPU01

- Base board (supplies interfaces and power): SK-86R11-BASE

- Additional Addon board (from Jade-L system), provides 2x DVI output and 2x CVBS input: SK-86R03-VIDEO

Figure 1-1: System Overview

## 2 Startup CPU Module

- Connect the CPU Module to the baseboard

- Connect appropriate cables (HDMI, RS232, Power etc) to baseboard (Please refer here to the Baseboard Manual – see appendix)

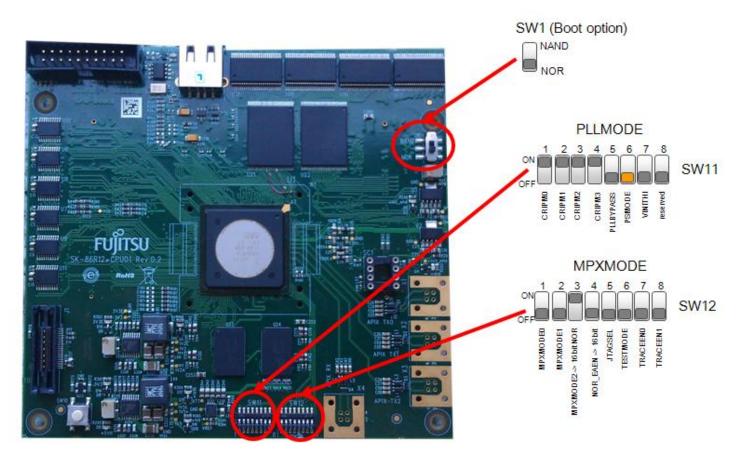

- Set switches SW1, SW11 and SW12 according to your needs (please refer here to the Hardware Manual see appendix)

- Power on baseboard

- Demo starts up on HDMI output

#### **Default settings for the CPU Module:**

- Clock PLL set to 533MHZ

- NOR Flash boot activated

- Bootloader and Linux system flashed in NOR and NAND Flash

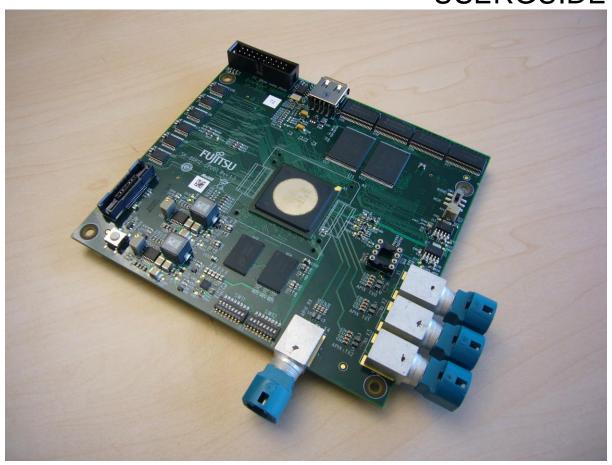

Figure 2-1: Board Layout

## 3 Detailed Settings

#### 3.1 NAND / NOR Boot Option

For NAND/NOR Boot Option SW1 is used

NAND SELFL = HIGH Boot from NAND

NOR SEFLL = LOW Boot from onboard NOR (default)

#### 3.2 DIP Switches

#### SW11 - PLL Mode

| SW11 | Signal    | Description                                                                                 | Default |

|------|-----------|---------------------------------------------------------------------------------------------|---------|

| 1    | CRIPM0    | ON = 0, OFF = 1                                                                             | ON      |

| 2    | CRIPM1    | ON = 0, OFF = 1                                                                             | ON      |

| 3    | CRIPM2    | ON = 0, OFF = 1                                                                             | ON      |

| 4    | CRIPM3    | ON = 0, OFF = 1                                                                             | ON      |

| 5    | PLLBYPASS | ON = PLL Clock is bypassed  OFF = PLL Clock is not bypassed                                 | OFF     |

| 6    | PSMODE    | OFF = PLL clock frequency divider ratio = 0  ON = PLL clock frequency divider ratio = 1     | OFF     |

| 7    | VINITHI   | ON = Exception Vectors located at 0xFFFF0000  OFF = Exception Vectors located at 0x00000000 | OFF     |

| 8    | -         | Unused                                                                                      | OFF     |

Notes:

CRIPM[0:3] default settings results in 533 MHz clock frequency

#### SW12 - MPX Mode

| SW12 | Signal   | Description                | Default |

|------|----------|----------------------------|---------|

| 1    | MPXMODE0 | ON = 1, OFF = 0            | OFF     |

| 2    | MPXMODE1 | ON = 1, OFF = 0            | OFF     |

| 3    | MPXMODE2 | ON = 1, OFF = 0            | OFF     |

| 4    | NOREAN   | NOR Flash Bus Width Select | ON      |

|      |          | ON = 32 Bit = 0 (Default)  |         |

|      |          | OFF = 16 Bit = 1           |         |

| 5    | JTAGSEL  | JTAG Select                | OFF     |

|      |          | ON = DFT                   |         |

|      |          | OFF = Normal (Default)     |         |

| 6    | TESTMODE | Test Mode Select           | OFF     |

|      |          | ON= Test Mode              |         |

|      |          | OFF = Normal (Default)     |         |

| 7    | TRACEEN0 | Pin Group B ETM            | OFF     |

|      |          | ON = use                   |         |

|      |          | OFF = not in use (Default) |         |

| 8    | TRACEEN1 | Pin Group H ETM            | OFF     |

|      |          | ON = use                   |         |

|      |          | OFF = not in use (Default) |         |

#### Notes:

MPX Mode Settings also available on Main Connector A

Attention: Do not set SW12-7 and SW12-8 to ON at the same time!

#### 3.3 Power presets

| R24  | 1.2V APIX Power Supply Adjustment | Set to 1.2V at Test Point TP8  |

|------|-----------------------------------|--------------------------------|

| R269 | 1.2V Power Supply Adjustment      | Set to 1.2V at Test Point TP4  |

| R275 | 1.5V Power Supply Adjustment      | Set to 1.5V at Test Point TP13 |

3.3V APIX Power Supply : Dedicated LDO: R19 = OPEN, R20 = 0R 1.2V APIX Power Supply: Dedicated LDO: R21 = DNI, R22 = 0R

#### 3.4 USB HOST

Settings:

Chip Select : used MEM\_nCS2 -> R205 = 0R, R204 = OPEN

Interrupt: IRQ = INT\_A0 -> R206 = OR, R209 = OPEN

#### 3.5 LEDs

| D8  | Global 5V Supply from base board connector   |

|-----|----------------------------------------------|

| D9  | 1.2V supply to MB86R12 (APIX)                |

| D10 | 3.3V supply to MB86R12 (APIX)                |

| D12 | 1.2V supply to MB86R12 (general)             |

| D13 | 5V Supply to USB bus                         |

| D14 | Global 3.3V Supply from base board connector |

| D15 | 3.3V supply to MB86R12 (general)             |

| D16 | 1.5V supply to DDR3 memory                   |

| D15 | 3.3V supply to MB86R12 (general)             |

|     |                                              |

## 4 Appendix

#### 4.1 Used literature

- Emerald-P Hardware Manual:

<a href="http://www.fujitsu.com/emea/services/microelectronics/gdc/gdcdevices/mb86r12-emerald-p.html">http://www.fujitsu.com/emea/services/microelectronics/gdc/gdcdevices/mb86r12-emerald-p.html</a>

- Emerald-P CPU Module Schematics:

<a href="http://www.fujitsu.com/emea/services/microelectronics/gdc/evalbds/emerald-p-starterkit.html">http://www.fujitsu.com/emea/services/microelectronics/gdc/evalbds/emerald-p-starterkit.html</a>

- Emerald-L Base Board Schematics:

<a href="http://www.fujitsu.com/emea/services/microelectronics/gdc/evalbds/emerald-p-starterkit.html">http://www.fujitsu.com/emea/services/microelectronics/gdc/evalbds/emerald-p-starterkit.html</a>

- Software Update: Please check Website regularly for updates of the used Linux system <a href="http://www.fujitsu.com/emea/services/microelectronics/gdc/swtools/gdc-software-index.html">http://www.fujitsu.com/emea/services/microelectronics/gdc/swtools/gdc-software-index.html</a>

#### 4.2 Figures

| Figure 1-1: System Overview | . 6 |

|-----------------------------|-----|

| Figure 2-1: Board Layout    | . 7 |