# User's Manual MIDAS-100/200 series

## PMC I/O Subsystem for VMEbus and RACEway

Rev. 1.0b - Valid for 'MIDAS PCB-B'

The information in this document is subject to change without notice and should not be construed as a commitment by VMETRO. While reasonable precautions have been taken, VMETRO assumes no responsibility for any errors that may appear in this document.

© Copyright VMETRO 2000.

This document may not be furnished or disclosed to any third party and may not be copied or reproduced in any form, electronic, mechanical, or otherwise, in whole or in part, without prior written consent of VMETRO Inc. (Houston, TX, USA) or VMETRO A/S (Oslo, Norway).

**VMETRO**

MIDAS USER'S MANUAL

#### Warranty

VMETRO products are warranted against defective materials and workmanship within the warranty period of 1 (one) year from date of invoice. Within the warranty period, VMETRO will, free of charge, repair or replace any defective unit covered by this warranty, shipping prepaid. A Return Authorization Code should be obtained from VMETRO prior to return of any defective product. With any returned product, a written description of the nature of malfunction should be enclosed. The product must be shipped in its original shipping container or similar packaging with sufficient mechanical and electrical protection in order to maintain warranty.

This warranty assumes normal use. Products subjected to unreasonably rough handling, negligence, abnormal voltages, abrasion, unauthorized parts replacement and repairs, or theft are not covered by this warranty and will if possible be repaired for time and material charges in effect at the time of repair.

VMETRO's warranty is limited to the repair or replacement policy described above and neither VMETRO nor its agent shall be responsible for consequential or special damages related to the use of their products.

#### **Limited Liability**

VMETRO does not assume any liability arising out of the application or use of any product described herein; neither does it convey any license under its patent rights nor the rights of others. VMETRO products are not designed, intended, or authorized for use as components in systems intended to support or sustain life, or for any application in which failure of the VMETRO product could create a situation where personal injury or death may occur. Should Buyer purchase or use VMETRO products for any such unintended or unauthorized application, Buyer shall indemnify and hold VMETRO and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that VMETRO was negligent regarding the design or manufacture of the part.

USA: VMETRO. Inc.

1880 Dairy Ashford, Suite 535 Houston, TX 77077, USA

Tel.: (281) 584-0728 Fax: (281) 584-9034 Email: info@vmetro.com

Europe, Asia: VMETRO asa

Brynsveien 5

N-0667 OSLO, Norway Tel.: +47 2210 6090 Fax: +47 2210 6202 Email: info@vmetro.no

http://www.vmetro.com/

iv • Contents MIDAS USER's MANUAL

## **Contents**

| Gene  | ral Information                               | 1  |

|-------|-----------------------------------------------|----|

|       | This document                                 | 1  |

|       | Conventions used in this document             |    |

|       | Related Documents                             |    |

| Prod  | uct Overview                                  | 3  |

|       | MIDAS Family                                  | 3  |

|       | The MIDAS-200 Series                          | 3  |

|       | Twin i960RD I/O processors                    | 3  |

|       | The MIDAS-100 Series                          | 4  |

|       | i960RD I/O processor                          | 4  |

|       | Main Components                               | 5  |

|       | i960®RD I/O Processor                         | 5  |

|       | Universe II PCI-VMEbus Bridge                 | 6  |

|       | PXB PCI-RACEway Bridge                        | 7  |

| Insta | llation                                       | 7  |

|       | Board Precautions                             | 7  |

|       | Unpacking                                     |    |

|       | Board Layout                                  |    |

|       | Installation of PMC Modules                   |    |

|       | Assembly Procedure for MIDAS-x50              |    |

|       | Installation in VMEbus System                 |    |

|       | Slot selection                                |    |

|       | Power consumption                             |    |

|       | Configuration Switch & Jumpers                |    |

| Func  | tional Description                            | 14 |

|       | i960®RD and its Surroundings                  | 14 |

|       | i960 <sup>®</sup> RD Address Map              |    |

|       | i960 <sup>®</sup> RD Power-Up Options         |    |

|       | FLASH Memory                                  |    |

|       | RS232 Interface                               |    |

|       | Connecting two i960 <sup>®</sup> RDs          |    |

|       | VMEbus Interface (Universe II VME-PCI Bridge) |    |

|       | 'Universe II' Power-Up Options                |    |

|       | Auto-Slot ID                                  |    |

|       | Configuration ROM                             |    |

|       | Switch & Jumper Descriptions                  |    |

|       | Reset Button                                  |    |

|       | RACEway Interface (PXB RACEway-PCI Bridge)    |    |

|       | Jumper Descriptions                           | 24 |

|       | PCI Bus Details                               |    |

|       | Arbitration                                   | 25 |

|       | 'IDSEL' Generation                            | 27 |

|       | Subtractive Decoding Agent                    |    |

|       | Interrupt Routing                             | 29 |

|       | Interrupt Mode Selection                      | 29 |

|       | Interrupt Jumpers                             | 30 |

|       | Interrupt Routing Tables                      | 30 |

| Interrupt Mode 0:                              | 31   |

|------------------------------------------------|------|

| Interrupt Mode 1:                              |      |

| Interrupt Mode 2:                              |      |

| Appendix I: PMC I/O Routing                    | 35   |

| PMC I/O Routing Scheme                         | 35   |

| Appendix II: Universe II Configuration Example | s 36 |

| General Information                            | 36   |

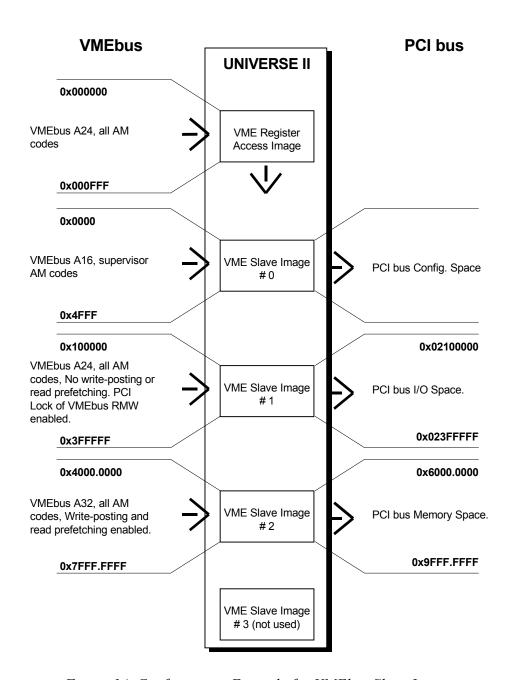

| VMEbus Slave Images                            | 36   |

| PCI Master Enable                              | 36   |

| VMEbus Register Access Image                   | 37   |

| VMEbus Slave Image 0                           | 38   |

| VMEbus Slave Image 1                           |      |

| VMEbus Slave Image 2                           | 39   |

| Initialization Sequence                        | 39   |

| PCI Slave Images                               | 40   |

| PCI Target Enable - Memory & I/O Space         | 40   |

| PCI Slave Image 0                              |      |

| PCI Slave Image 1                              | 42   |

| PCI Slave Image 2                              |      |

| Initialization Sequence                        | 43   |

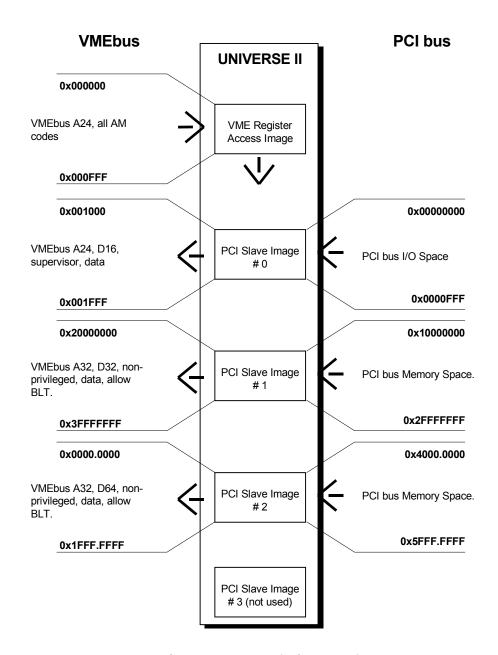

| Appendix III: PXB Information                  | 44   |

| PXB Register Descriptions                      | 44   |

| P-Side Register Descriptions                   |      |

| X-Side Register Descriptions                   |      |

| Miscellaneous PXB Information                  | 52   |

| Configuration Serial EEPROM                    | 52   |

| PCI-to-RACEway Addressing                      |      |

| RACEway-to-PCI Addressing                      | 55   |

| PCI-to-PCI Bridge Operation                    | 56   |

| PXB Initialization Example                     | 57   |

| Appendix IV:                                   | 61   |

| List of Tables                                 | 61   |

| List of Figures                                | 62   |

## **General Information**

#### This document

This document has been prepared to help the customer integrate MIDAS in their VMEbus system. The following models are covered by this document:

**MIDAS-120:** Intelligent I/O Subsystem with single i960<sup>®</sup>RD and memory, and two PMC positions.

**MIDAS-150:** Intelligent I/O Subsystem with single i960<sup>®</sup>RD and memory, and five PMC positions. Occupies two VMEbus slots.

MIDAS-220: Intelligent I/O Subsystem containing dual i960®RD with

independent memories, and two PMC positions.

**MIDAS-250:** Intelligent I/O Subsystem containing dual i960<sup>®</sup>RD with

independent memories, and five PMC positions. Occupies two

VMEbus slots.

The following options are described:

**-R** RACEway option. Interface to 160 MB/s RACEway crossbar.

-S Symmetrical configuration. Configuration option with one PMC position on each PCI bus. Applies to MIDAS-120 and MIDAS-220 only.

#### Conventions used in this document

The following section describes conventions used in this document.

Symbols Meaning:

The STOP symbol indicates a section of critical importance. Overlooking this information may cause damage to the MIDAS and/or other equipment.

Indicates important, but not crucial, information. Still, you should take notice if you want to use all capabilities built into your MIDAS.

#### **Related Documents**

This document does <u>not</u> include detailed information about the following main board components:

- i960<sup>®</sup>RD Intelligent I/O Processor.

- 'Universe II' VME-to-PCI bridge chip.

- 'PXB' RACEway-to-PCI bridge chip.

Since a majority of the control registers, and a large part of the complexity of the MIDAS is implemented in these chips, their documentation contains information, which is essential to the understanding of the product.

VMEbus-PCI (Tundra): UNIVERSE II™ USER MANUAL

i960®RD (Intel Corp.): i960®Rx I/O Microprocessor Developer's Manual

i960®RD - DATA SHEET

RACEway-PCI PXB OVERVIEW

PXB BRIDGE SPECIFICATION

Documentation can be obtained from VMETRO by ordering a MIDAS Documentation Package.

The vendors of some of the major components used on MIDAS publish device data via Internet. Some components may contain design defects or errors known as errata, which may cause the component to deviate from published specifications. The respective vendors, on their web pages document current characterized errata.

| Vendor                      |  | Component                    | Available documentation |

|-----------------------------|--|------------------------------|-------------------------|

| Tundra (formerly Newbridge) |  | Universe II (VME-PCI Bridge) | User Manual             |

|                             |  |                              | Device Errata           |

|                             |  |                              | Application Notes       |

| http://www.tundra.c         |  | om/                          |                         |

| Intel Corporation           |  | 80960RD (I/O Processor)      | User Manual             |

|                             |  | Not used on MIDAS-20/50      | Device Errata           |

|                             |  |                              | Application Notes       |

|                             |  |                              | and more                |

| http://www.intel.com        |  | m/design/i960/               |                         |

## **Product Overview**

## **MIDAS Family**

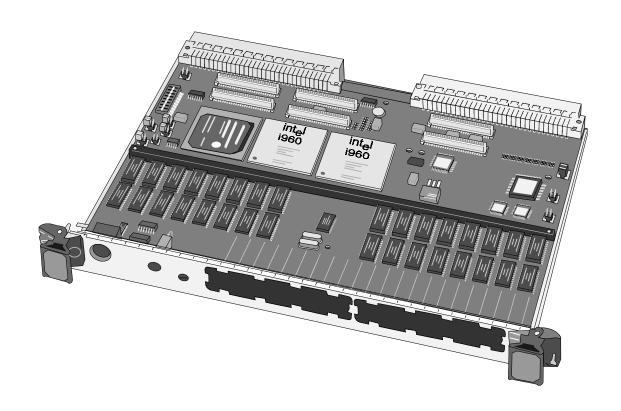

The MIDAS family provides complete PMC I/O Sub-systems for VMEbus and/or RACEway. The boards may carry two or five PMC - PCI Mezzanine Cards, and are designed for effective integration of high-performance PCI I/O functions into VME systems. The family ranges from a very simple 2x PMC Carrier (MIDAS-20), to a powerful Twin i960 & Memory 5x PMC Carrier (MIDAS-250), in which, twin memories and processing power from two CPUs are available.

#### The MIDAS-200 Series

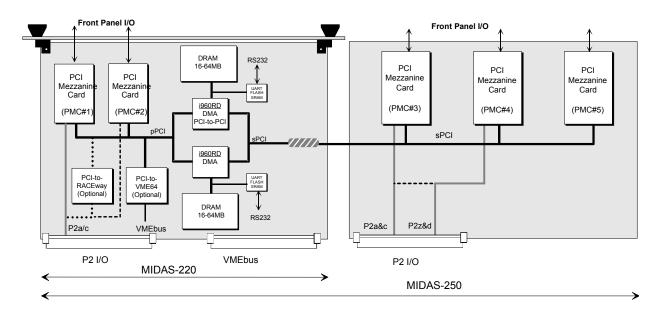

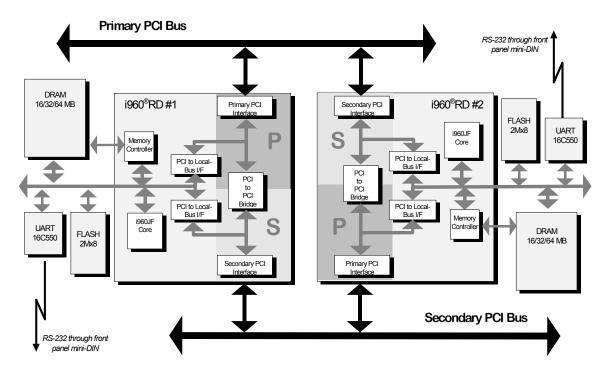

Figure 1. MIDAS-220/250 Block Diagram

The MIDAS-220 series utilize unique, independent, dual i960 processor and Memory arrays, each coupled to a PMC I/O Sub-System, for maximum data through-put to both VMEbus and/or RACEway. The boards carry two or five PMC - PCI Mezzanine Cards, and are designed for effective integration of high-performance PCI I/O functions into the VME or RACEway systems, where twin memories and/or processing power from two CPUs is required. The MIDAS-220 series is particularly well suited for applications such as Imaging, Data Acquisition, and Signal Processing.

## Twin i960RD I/O processors

A central element of the MIDAS-220 series is the *twin* Intel i960RD processor architecture. The highly integrated i960RD features a powerful RISC I/O

processor, a PCI-to-PCI bridge, a memory controller and a flexible DMA-controller with linked-list capability.

Each of the two i960RDs has direct access to its own FLASH PROM, a RS232 UART, all of the PCI resources on the board, and of course, its associated DRAM bank. This allows it to offload the host CPU by running dedicated I/O drivers for the PMC modules mounted on the board.

For applications that do not need the processing power of the i960RD, but only twin DRAM memories and/or DMA, the processors may rest idle during normal operation.

#### The MIDAS-100 Series

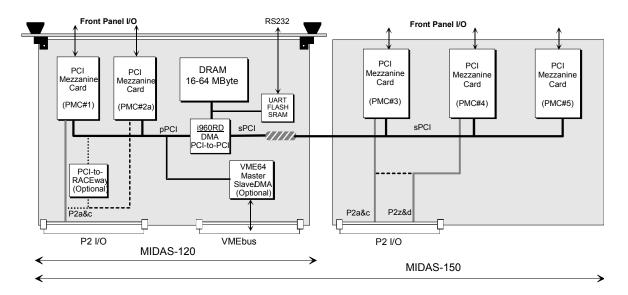

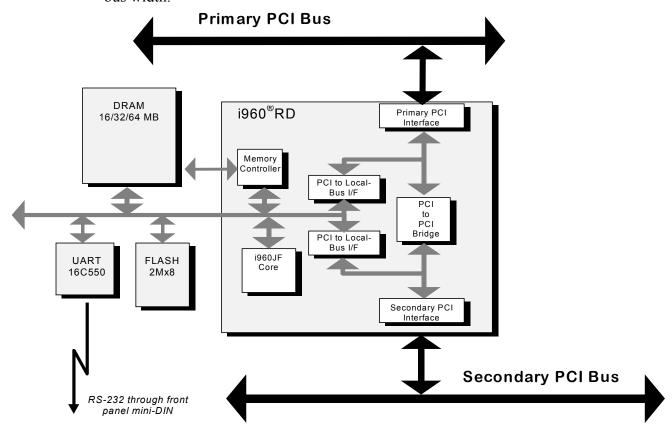

Figure 2. MIDAS-120/150 Block Diagram

The MIDAS-100 series are versatile PMC I/O Sub-System & Memory modules for VMEbus and/or RACEway, holding two or five PMC - PCI Mezzanine Cards. The boards are designed for cost-effective integration of PCI I/O functions into the VME or RACEway systems, where local memory and/or processing power is required.

## i960RD I/O processor

A central element of the MIDAS-100 series is the Intel i960RD processor. The highly integrated i960RD features a powerful RISC I/O processor, a PCI-to-PCI bridge, a memory controller and a flexible DMA-controller with linked-list capability.

The i960RD has direct access to FLASH PROM, a RS232 UART, all of the PCI resources on the board, and of course, the DRAM. This allows it to offload the

4 ◆ Product Overview MIDAS USER's MANUAL

host CPU by running dedicated I/O drivers for the PMC modules mounted on the board.

## **Main Components**

## i960<sup>®</sup>RD I/O Processor

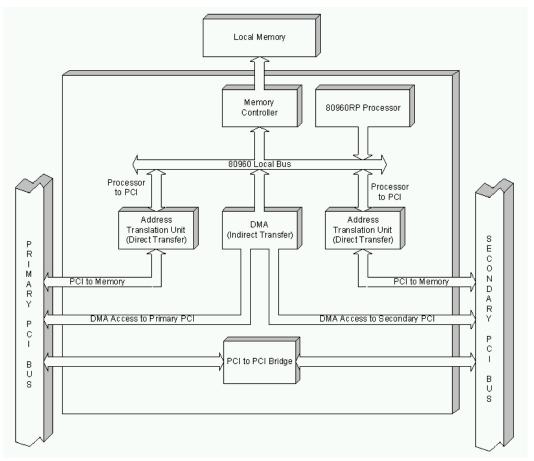

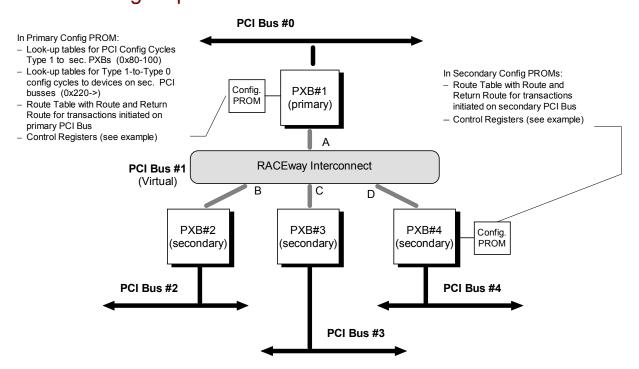

The i960 RD processor integrates a high-performance 80960 "core" into a Peripheral Components Interconnect (PCI) functionality. This integrated processor addresses the needs of intelligent I/O applications. The primary functional units include an i960 core processor, PCI to PCI bus bridge, PCI-to-80960 Address Translation Unit, Messaging Unit, Direct Memory Access (DMA) Controller, Memory Controller, and Secondary PCI bus Arbitration Unit.

The PCI Bus is an industry standard, high performance, low latency system bus, which operates up to 132 Mbytes/sec. The PCI-to-PCI bridge provides a connection path between two independent 32-bit PCI buses and provides the ability to overcome PCI electrical loading limits. The addition of the i960 core processor brings intelligence to the PCI bus bridge.

Figure 3. i960®RD Data Flow

The i960 RD processor is a multi-function PCI device: Function 0 is the PCI-to-PCI bridge, Function 1 is the Address Translation Unit. The i960 RD processor contains PCI configuration space, which is accessible through the primary PCI bus. This multi-function PCI device is fully compliant with the PCI Local Bus Specification Revision 2.1.

#### Universe II PCI-VMEbus Bridge

The Universe II is a second-generation high performance VMEbus to PCI bridge manufactured by Tundra Semiconductor. It features:

- Fully compliant 33 MHz PCI local bus interface.

- Fully compliant, high performance 64-bit VMEbus interface.

- Integral FIFOs for write posting to maximize bandwidth utilization.

- Programmable DMA controller with linked list support.

- VMEbus transfer rates of 60-70 Mbytes/sec.

- Complete suite of VMEbus address and data transfer modes:

- A32/A24/A16 master and slave

- D64 (MBLT)/D32/D16/D08 master and slave

- BLT, ADOH, RMW, LOCK

- Flexible register set, programmable from both the PCI bus and VMEbus ports.

- Full VMEbus system controller functionality.

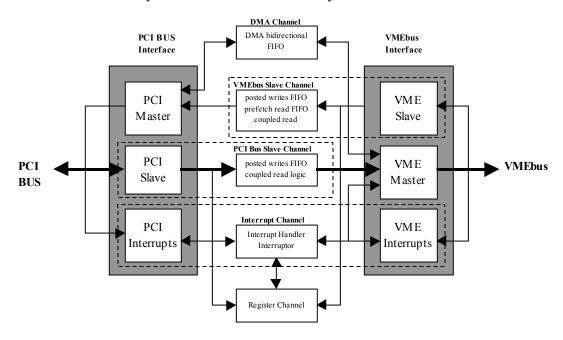

Figure 4 PCI-VME bridge functional diagram

#### PXB PCI-RACEway Bridge

The PXB is a high performance RACEway to PCI bridge developed by Mercury Computer Systems. It features:

- Bridges a 32 bit, 33MHz PCI bus with a 32 bit, 40MHz RACEway switching fabric.

- Compliant to Rev 2.1 PCI local bus specification, including delayed operations.

- Compliant to Rev 1.0 PCI to PCI Bridge specification.

- Bridges up to sixteen 32 bit, 33MHz PCI busses

- Able to sustain up to 125MB/sec with large memory write transfers, and 100MB/sec with large memory read transfers.

- Integral FIFOs for write posting to maximize bandwidth utilization.

## Installation

#### **Board Precautions**

The MIDAS circuit board is sensitive to static electricity and can be damaged by a static discharge. Always wear a grounded anti-static wrist strap and use grounded, static protected work surfaces when touching the circuit board and its components.

When the board is not installed, always keep in the static-protective envelope.

## Unpacking

All precautions described above must be taken when unpacking the MIDAS from its shipping container. Verify that no damage has occurred in the shipment. Refer to packing list and verify that all items are present.

MIDAS USER's MANUAL Installation • 7

## **Board Layout**

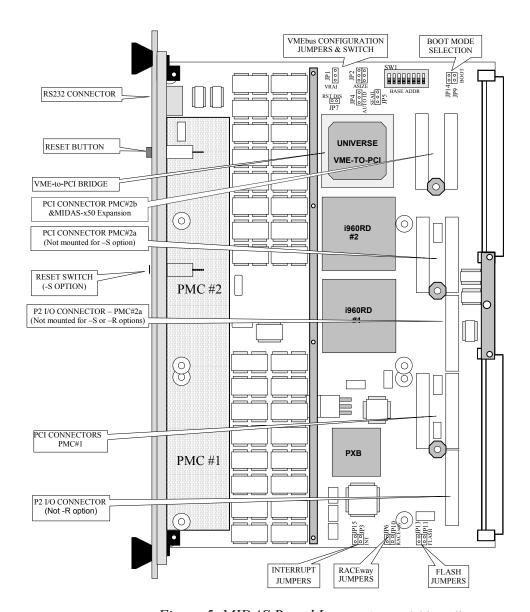

Figure 5. MIDAS Board Layout (No model has all parts mounted.)

## **Installation of PMC Modules**

The MIDAS is shipped with two PMC filler panels mounted in the front panel. They act as EMC shielding in unused PMC positions. Before installing a PMC module, the filler panel(s) must be removed. This is done by pushing them out from the backside of the front panel.

Four screws must be used to secure each PMC on the MIDAS board.

8 • Installation MIDAS USER's MANUAL

Note: Be extremely careful when inserting screws to secure PMC modules. Touching component leads, or the printed circuit board itself, with a screwdriver may cause permanent damage to the board

## **Assembly Procedure for MIDAS-x50**

The MIDAS-x50 is a dual slot VMEbus board that mates the back-plane connectors in two neighbor slots. The MIDAS-x50 module can handle the insertion and extraction forces applied when installing or removing it from the backplane. However, this requires that the assembly procedure described in this section be followed.

WARNING: The MIDAS-x50 boards may be destroyed during insertion or extraction from a VMEbus system if this procedure is not followed.

#### STEP#1: Dismount MEZZ-x50 board from MIDAS-x20 board.

- Place the MIDAS-x50 board on a smooth static protected work surface with the bottom side of the MIDAS-x20 board facing up.

- From the bottom side of the MIDAS-x20 PCB, remove the 5 screws holding the metal spacers between the MEZZ-x50 and MIDAS-x20. (these screws are located close to the edge of the board in each corner, and between the VMEbus connectors). **Note:** Do not throw away the screws. They are needed later in this procedure.

- Pull the boards carefully apart. Use hand force only, applied to the two upper VMEbus connectors for both boards.

- If the small SPACER-x50 PCB is attached to the MIDAS-x20 PCB after the separation, remove it and mount it on the bottom side of the MEZZ-x50 board instead.

#### STEP#2: Mount PMC modules 1 and 2 on the MIDAS-x20 board.

- Place the MIDAS-x20 board on a smooth static protected work surface.

- Install PMC module #1 in the lower PMC position

- Install PMC module #2 in the upper PMC position

- Secure PMC modules with screws on the bottom side of the MIDAS-x20 board.

Installation • 9

MIDAS USER'S MANUAL

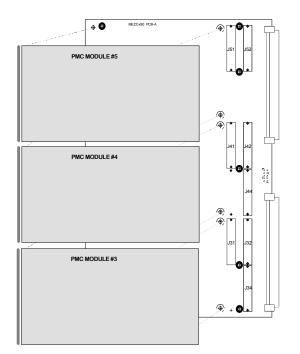

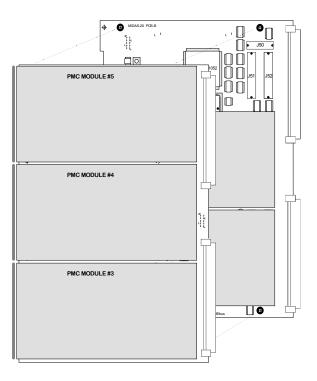

#### STEP#3: Mount PMC modules 3, 4 and 5 on the MEZZ-x50 board.

- Place the MEZZ-x50 board on a smooth static protected work surface.

- Install PMC module #3 in the lower PMC position.

- Install PMC module #4 in the middle PMC position.

- Install PMC module #5 in the upper PMC position.

- Secure the PMC modules with screws on the bottom side of the MEZZ-x50 board.

Figure 6. Steps 2&3: Mount PMC modules on the MEZZ-x50 and MIDAS-x20 boards.

**Note:** Before proceeding, make sure the switch and jumper settings of the MIDAS-x20 board are set according to the needs of your application.

10 • Installation MIDAS USER's MANUAL

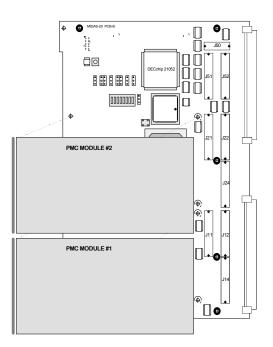

#### STEP#4: Mount MEZZ-x50 with PMC modules on the MIDAS-x20 board.

- If the SPACER-x50 board and the five metal spacers are not already mounted on the bottom side of the MEZZ-x50 board, do it now.

- Place the MIDAS-x20 board on a smooth, static protected work surface.

- Carefully position the MEZZ-x50 board over the MIDAS-x20, so that the three connectors on the bottom side of the spacer, are aligned with the connectors J50, J51 and J52, on the MIDAS-x20. Make sure that none of the five metal spacers mounted on the MEZZ-x50 board touch components or component leads, on the MIDAS-x20, in the process.

- Push the MEZZ-x50 board down, so that all connectors mate completely.

Figure 7. Step 4: Mount the MEZZ-x50 with PMC modules on the MIDAS-x20 board.

## STEP#5: Mount and fasten screws to all metal spacers on the back of the MIDAS-x20 board.

- Take the 5 screws removed in step#1 of this procedure, and mount them on the back side of the MIDAS-x20 board, through the holes which mate the 5 metal spacers on the MEZZ-x50.

- Fasten all five screws with a suitable screwdriver.

- Verify that the screws attaching the metal spacers to the MEZZ-x50 are also fastened.

- All screws holding the five metal spacers on both boards, must be firmly fastened in order to make the MIDAS-x50 mechanically stable.

MIDAS USER's MANUAL Installation • 11

## Installation in VMEbus System

#### Slot selection

The MIDAS can be installed in any slot in a 6U VMEbus chassis, as long as the daisy-chains for the bus grant and interrupt acknowledge signals are continuous from slot#1 to the slot in which the MIDAS is installed.

Installation into slot#1 of a VMEbus system is automatically detected, as specified in the VME64 specification. System controller functions are also enabled as a consequence.

WARNING: Do not install the board in a powered system!

## **Power consumption**

WARNING: Due to its power consumption, the MIDAS board requires forced air cooling for reliable operation. Operation on extender boards is not recommended.

| Model         | Memory Size | Operating Mode                                                                                                       | Power Consumption<br>typ. @ +5V |

|---------------|-------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------|

| MIDAS-220Y/M  | 32MB        | Both processors are in the idle state.                                                                               | 14.5W                           |

| MIDAS-220 Y/M | 32MB        | One processor transferring data across VME and Raceway, the other processor idle                                     | 14.7W                           |

| MIDAS-220 Y/M | 32MB        | One processor transferring data<br>across VME and Raceway, the<br>other processor performing an<br>extended selftest | 15.2W                           |

| MIDAS-220 SR  | 128MB       | Both processors are in the idle state.                                                                               | 15.0W                           |

| MIDAS-220 SR  | 128MB       | One processor transferring data across VME and Raceway, the other processor idle                                     | 15.7W                           |

| MIDAS-220 SR  | 128MB       | One processor transferring data<br>across VME and Raceway, the<br>other processor performing an<br>extended selftest | 17.0W                           |

| MIDAS-120     | 32MB        | Processor Idle                                                                                                       | 10.5W                           |

| MIDAS-120     | 32MB        | Processor running selftest                                                                                           | 11.5W                           |

| MIDAS-120     | 32MB        | Processor transferring data over VME                                                                                 | 11.5W                           |

Table 1. Power Consumption

12 • Installation MIDAS USER's MANUAL

## **Configuration Switch & Jumpers**

The MIDAS has a large number of configuration registers, which need to be initialized before the board is operational. Most registers are normally initialized by an i960<sup>®</sup>RD, but in some applications, an external host processor can perform this initialization, or parts of it, over VMEbus or RACEway. To allow this, power up options in some MIDAS components are loaded from jumpers or a DIPswitch.

A detailed description of each jumper is included in the relevant part of the "Functional Description" section.

MIDAS USER's MANUAL Installation • 13

## **Functional Description**

## i960®RD and its Surroundings

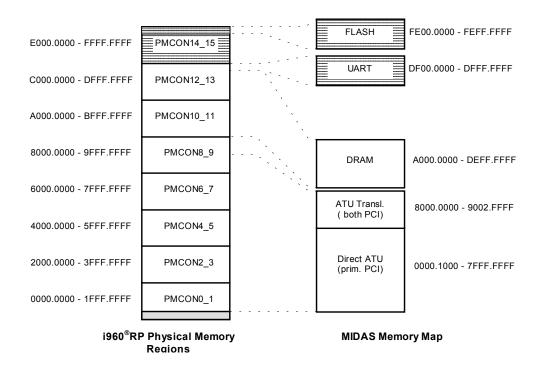

As indicated in Figure 8, each i960<sup>®</sup>RD on MIDAS has its own private FLASH memory and RS-232 interface, in addition to its own block of DRAM.

Note that the UART and FLASH must be located in memory regions, with an 8-bit bus width.

Figure 8. i960®RD with External Devices

## i960®RD Address Map

Figure 9. Local Memory Address Space

## i960®RD Power-Up Options

The i960®RD monitors a number of pins during reset to define its mode of operation. The most important are:

#### Secondary PCI Arbiter Enable/Disable:

For both i960®RDs, the secondary PCI arbiter is always enabled.

#### i960<sup>®</sup>RD Boot Modes

Two of the power-up options control the boot process of the i960<sup>®</sup>RD. These two options can be controlled through two jumpers (JP9 & JP14) located in the top right corner of the board.

|  | Jumpers: i960 <sup>®</sup> RD #1 |                          | i960 <sup>®</sup> RD #2        |

|--|----------------------------------|--------------------------|--------------------------------|

|  | JP14                             | Processor: Boot directly | Processor: Boot directly       |

|  | F                                | PCI: Retry until CSR set | PCI: Retry until CSR set       |

|  | JP14                             | Processor: Boot directly | Processor: Sleep until CSR set |

|  |                                  | PCI: Retry until CSR set | PCI: Accept config. cycles     |

| 4000 | Processor: Sleep until CSR     | Processor: Boot directly              |

|------|--------------------------------|---------------------------------------|

|      | set <sup>1</sup>               | PCI: Retry until CSR set <sup>2</sup> |

|      | PCI: Accept config. cycles     | j                                     |

| 400  | Processor: Sleep until CSR set | Processor: Sleep until CSR set        |

|      | PCI: Accept config. cycles     | PCI: Accept config. cycles            |

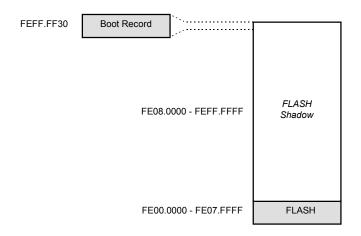

#### **FLASH Memory**

Each i960<sup>®</sup>RD on the MIDAS-220 has a private 16Mbit FLASH device. A 95ns 2Mx8 flash-file device is used.

| Jumpers: | Function:                                                                                                                                                                                    |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | JP13 - Removed / JP11 - Inserted:                                                                                                                                                            |

|          | * Locked FLASH blocks are write/erase protected. With some restrictions, blocks can be locked. Ref. i28F016SC/S5 datasheet. ('RD#' pin is at V <sub>IH</sub> level with this jumper setting) |

|          | JP13 & JP11 – Removed:                                                                                                                                                                       |

|          | Entire FLASH is write protected.                                                                                                                                                             |

Avoid the following jumper settings

|      | JP13 & JP11 - Inserted:                                                         |

|------|---------------------------------------------------------------------------------|

|      | ** No Protection. Entire FLASH can be erased/written. Lock bits can be altered. |

|      | JP13 - Inserted / JP11 - Removed:                                               |

| JP13 | Indeterminate state - Memory contents is <b>not</b> protected                   |

<sup>\*</sup> Normal Operation Unlocked flash blocks may be erased and re-programmed.

\*\* This setting should only be used DURING flash updates of locked flash blocks (Normally only the MIDAS  $\circledR$  Monitor).

<sup>&</sup>lt;sup>1</sup> If U44 (a PLD mounted on the backside of the i960<sup>®</sup>RD#1, on the opposite side of the board) is labeled "1002-A", i960<sup>®</sup>RD#1 will boot directly.

<sup>&</sup>lt;sup>2</sup> If U44 is labeled "1002-A", the PCI bus will accept config. cycles.

Figure 10. FLASH Boot Address

#### RS232 Interface

Each i960®RD on the MIDAS-220 has a private UART for serial port communication. The 'TL16C550' is used for this purpose.

Both RS-232 interfaces share a mini-DIN connector for connection through the front panel.

The UART is located at a fixed address in the i960 address space. The base address is 0xDF00.0000. The eight most significant address bits are used for the address decoding, which means that a 16MB window is occupied.

#### RS232 Cables

MIDAS-100 and MIDAS-200 series boards are shipped with a short converter cable to allow standard D-SUB cables to connect to the non-standard, Mini-DIN MIDAS connector.

The cable for the MIDAS-200 board is a split cable, with one 9 pin D-sub connector for each processor. The shorter cable connects to the UART of i960®RD#1, while the longer cable connects to processor number two.

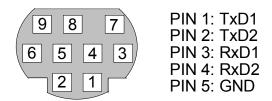

Figure 11. Pin definition for the RS232 female connector mounted on the front panel

## Connecting two i960®RDs

To maximize the utilization of the i960<sup>®</sup>RD's resources, the two processors are connected as shown in Figure 12.

The primary PCI bus interface on i960<sup>®</sup>RD#1 is connected to the secondary interface on i960<sup>®</sup>RD#2, and vice versa. The primary PCI bus in MIDAS terms connects to the primary side of i960<sup>®</sup>RD#1.

Figure 12. Connection of two i960®RDs on MIDAS-220

Note that for any connection of two i960<sup>®</sup>RDs in parallel between two PCI busses, like on the MIDAS-220, introduces restrictions on the programming of the address translation units, as well as on the P2P bridge.

The P2P bridge in i960<sup>®</sup>RD#2 should **not** be enabled, in order to simplify the generation of a valid address map.

## VMEbus Interface (Universe II VME-PCI Bridge)

The VME-PCI bridge on MIDAS has a number of configuration registers, which need to be initialized before the bridge is fully operational. One i960®RD processor or a host processor residing on VMEbus does this initialization.

#### 'Universe II' Power-Up Options

The 'Universe II' loads a number of power-up options after power-up or system reset. A detailed description of these options is found in the UNIVERSE II™ USER MANUAL. Table 2 shows how they are controlled on the MIDAS.

| Option:                         | Enabled<br>by | Register  | Field     | MIDAS           |

|---------------------------------|---------------|-----------|-----------|-----------------|

| VME Register Access Slave Image | PWR/SYS       | VRAI_CTL  | EN        | Jumper - JP1    |

|                                 |               |           | VAS       | Jumpers - JP2-3 |

|                                 |               | VRAI_BS   | BS        | Switch - SW1    |

| VME CR/CSR Slave Image          | PWR/SYS       | VCSR_CTL  | LAS       | I/O Space       |

|                                 |               | VCSR_TO   | ТО        | '0x00'          |

|                                 |               | PCI_CSR   | MAST_EN   | Enabled         |

| PCI Slave Image                 | PWR/SYS       | LSI0_CTL  | EN        | Disabled        |

|                                 |               |           | LAS       | Mem. space      |

|                                 |               |           | VAS       | A16             |

|                                 |               | LSI0_BS   | BS        | 0x0             |

|                                 |               | LSI0      | BD        | 0x0             |

| PCI Register Access             | PWR/SYS       | PCI_BS    | SPACE     | I/O Space       |

| PCI Bus Size                    | RST#          | MISC_STAT | LCLSIZE   | 32-bit          |

| Auto-ID                         | PWR/SYS       | MISC_STAT | DY4AUTO   | Disabled        |

|                                 |               |           | VME64AUTO | Jumper - JP4    |

| BI-Mode                         | PWR/SYS       | MISC_CTL  | BI        | Disabled        |

| SYSFAIL* Assertion              | PWR/SYS       | VCSR_SET  | SYSFAIL   | Jumper - JP5    |

|                                 |               | VCSR_CLR  | SYSFAIL   |                 |

| Auto-Syscon Detect              | SYS           | MISC_CTL  | SYSCON    | Enabled         |

Table 2. 'Universe II' Power-Up Options

#### Auto-Slot ID

Plug&Play

The MIDAS supports the Auto-Slot ID mechanism as defined by the VME64 specification. By use of the daisy-chained IACK signal, CR/CSR space accesses are enabled for one VME slot at a time. Thus, the "Monarch" (host for initialization) is able to recognize installed modules and initialize them to achieve Plug&Play VMEbus systems.

Enabling of the Auto-Slot ID feature causes IRQ2\* to be asserted, this may cause problems in systems containing VMEbus boards which do not support the Auto-Slot ID feature. In such cases, the Auto-Slot ID feature must be disabled.

#### **Configuration ROM**

To support the Auto-slot ID protocol, the MIDAS board implements a configuration ROM. This ROM is implemented as a PCI bus slave-only device, which responds in PCI I/O space using subtractive decoding.

Note that parity is not generated when reading the MIDAS configuration ROM. Parity errors should therefor be disregarded when reading these locations. In the power-up state of the Universe II VME-PCI bridge, parity errors are disregarded.

The configuration ROM is disabled by any write, in PCI Configuration Space, with address bit 30 set to 1. This way boot software may "remove" the CROM from PCI I/O space to allow another subtractive decoding agent, or to avoid parity errors on reads from "non present devices".

#### MIDAS-x20 Configuration ROM

CROM Offset: 03 (VME CR/CSR Space)

| Offset | ROM<br>Value | Description                                                            |  |

|--------|--------------|------------------------------------------------------------------------|--|

| 03     |              | Checksum. Eight bit 2s complement binary checksum (CR bytes 03-7F).    |  |

| 07     | 00           | Length of ROM to be checksummed. (MSB)                                 |  |

| 0B     | 00           | Length of ROM to be checksummed. (NMSB)                                |  |

| 0F     | 1F           | Length of ROM to be checksummed. (LSB)                                 |  |

| 13     | 81           | CR Data access width $(0x81 = D08(EO), every forth byte)$              |  |

| 17     | 81           | CSR Data access width $(0x81 = D08(EO), every forth byte)$             |  |

| 1B     | 01           | CR/CSR Space Specification ID (0x01 = VME64 - 1994 version)            |  |

| 1F     | 43           | 'C'. Used to identify valid CR.                                        |  |

| 23     | 52           | 'R'. Used to identify valid CR.                                        |  |

| 27     | 00           | 24 bit IEEE Assigned Manufacturers ID.                                 |  |

| 2B     | 60           | 0x006046 = VMETRO                                                      |  |

| 2F     | 46           |                                                                        |  |

| 33     | 00           | Board ID (VMETRO Assigned)                                             |  |

| 37     | 00           | 0x00020020 = MIDAS-20R/50R                                             |  |

| 3B     | 02           | 0x00000120 = MIDAS-120xx/150xx                                         |  |

| 3F     | 20           | 0x00000220 = MIDAS-220xx/250xx                                         |  |

| 43     | 00           | Revision ID (VMETRO Assigned)                                          |  |

| 47     | 00           | Example 0x0000B001 = PCB Rev: B, ECO-level:1                           |  |

| 4B     | В0           | 1                                                                      |  |

| 4F     | 01           |                                                                        |  |

| 53     | 00           | Pointer to null terminated ASCII string. Revision ID (VMETRO Assigned) |  |

| 57     | 00           | 0x0000000 = No string                                                  |  |

| 5B     | 00           |                                                                        |  |

| 5F-7B  | 00           | Reserved for future use                                                |  |

| 7F     | 01           | Program ID Code. $0x01 = No \text{ program}$ , ID ROM only.            |  |

Table 3. MIDAS Configuration ROM

#### Switch & Jumper Descriptions

MIDAS has a DIPswitch and a number of jumpers for board configuration. For easy identification, their functions are indicated with silk-screen text on the printed circuit board.

#### VME Register Access Image - ENABLE/DISABLE

The *VME Register Access Image (VRAI)* permits accesses from VMEbus to the VME-PCI bridge internal registers at power-up. Unless the Auto-Slot ID protocol (which uses its own slave image) is used, this slave image must be enabled to allow initialization from VMEbus.

| Jumpers: |         | Function:   |                                            |

|----------|---------|-------------|--------------------------------------------|

| VRAI     | JP2<br> | JP1 - DOWN: | VME Register Access Image <u>DISABLED.</u> |

| VRAI     | JP2     | JP1 - UP:   | VME Register Access Image <u>ENABLED.</u>  |

#### VME Register Access Image - ADDRESS SIZE

The *VME Register Access Image* can accept A16, A24 or A32 AM codes, depending on the positioning of the 'A SIZE' jumpers (JP2 & JP3). At power-up, this slave image accepts AM codes for: Supervisor, User, Data and Code.

| Jumpers: |         | Function:        |                                       |

|----------|---------|------------------|---------------------------------------|

| VRAI     | JP2<br> | JP2 - UP/UP:     | VME Register Access Image A24.        |

| VRAI     | JP2     | JP2 - DOWN/DOWN: | VME Register Access Image <u>A32.</u> |

| VRAI     | JP2     | JP2 - UP/DOWN:   | VME Register Access Image <u>A16.</u> |

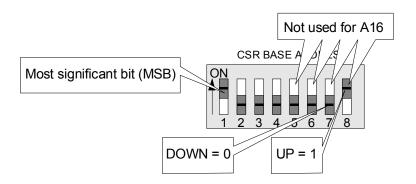

#### VME Register Access - BASE ADDRESS

The DIPswitch is used to define the base address for the *VME Register Access Image*. The size of this image is fixed to 4KB.

|                 |             | BASE ADDRESS |                     |

|-----------------|-------------|--------------|---------------------|

| VRAI Addr. Size | BS[31:24]   | BS[23:16]    | BS[15:12]           |

| A16             | N.A.        | N.A.         | From switch (4 MSB) |

| A24             | N.A.        | From switch  | 0x00                |

| A32             | From switch | 0x00         | 0x00                |

Table 4. VRAI Base Address Definition

Figure 13. DIP Switch Details. (Shown switch value: 0x81)

#### VME64 Auto-Slot ID - ENABLE/DISABLE

By using new address space for CR/CSR accesses, the VME64 specification defines a method for implementing Plug&Play on the VMEbus, called Auto-Slot ID. 'JP6' controls the enabling of the VME64 Auto-Slot ID mechanism.

| Jumpers:                          | Function:   |                                     |

|-----------------------------------|-------------|-------------------------------------|

| AUTO ID  O O O  JP5  O O O  SFAIL | JP4 - UP:   | VME64 AUTO-SLOT ID <u>ENABLED.</u>  |

| AUTO ID JP4 JP5 SFAIL             | JP4 - DOWN: | VME64 AUTO-SLOT ID <u>DISABLED.</u> |

#### SYSFAIL Assertion - ENABLE/DISABLE

The VMEbus interface provides the option to assert the VMEbus signal, SYSFAIL, during power up. When this feature is enabled, the MIDAS board will assert SYSFAIL on the VMEbus until the boot/initialization software has completed the power-up selftest and configuration routines. SYSFAIL is then deasserted to signal to the VMEbus system that the board is ready to operate. 'JP5' controls the enabling of this mechanism.

| Jumpers:                          | Function:   |                            |

|-----------------------------------|-------------|----------------------------|

| AUTO ID  O O O  JP4  JP5  SFAIL   | JP5 - UP:   | SYSFAIL ASSERTION DISABLED |

| AUTO ID O O © JP4 JP5 O O © SFAIL | JP5 - DOWN: | SYSFAIL ASSERTION ENABLED  |

#### SYSRST\* Assertion - ENABLE/DISABLE

If this jumper is removed, pushing of the reset button will perform both a local and a global reset. In order to perform only a local reset (without assertion of the SYSRST\* signal on the VMEbus), the jumper should be inserted.

| Jumpers | Function:       |                            |

|---------|-----------------|----------------------------|

| RST DIS | JP7 - INSERTED: | SYSRST* ASSERTION DISABLED |

| RST DIS | JP7 - REMOVED:  | SYSRST* ASSERTION ENABLED  |

When disabling SYSRST\* assertion, the Universe II chip is <u>partly</u> reset by the front panel reset button. This may have undesired side effects. The RST DIS jumper is included to support reset isolation in certain development systems.

#### Reset Button

Pushing the reset button will perform both a local and a global reset.

In order to perform only a local reset (without assertion of the SYSRST\* signal on the VMEbus), the soft reset mechanism must be utilized. This can be done from the host, by setting the bit 23 of the Universe II MISC\_CTL register (offset 404).

## RACEway Interface (PXB RACEway-PCI Bridge)

Some MIDAS models (with -R option) incorporate the PXB chip, a PCI-RACEway bridge developed by Mercury Computer Systems.

#### **Jumper Descriptions**

MIDAS has two jumpers for configuration of the RACEway interface. They are located close to the bottom edge of the board, indicated with silk-screen text: RACEway. As explained in the description below, both RACEway jumpers are removed during normal operation.

#### No EEPROM

When the *No EEPROM* jumper is removed, the PCI-RACEway bridge chip loads its internal registers from a serial EEPROM. This setting should always be used, except for cases where the PROM is blank or corrupted.

If the PROM is corrupted, and this jumper is removed, the PCI-RACEway bridge may reset to a state which causes the MIDAS board (in worst case the entire system) to hang.

If the *No EEPROM* jumper is inserted, the PCI-RACEway bridge reset state is independent of PROM contents. This setting is normally used for the initial programming of the PROM or if the board is plugged into a non-RACEway slot. Note that before programming the PROM, the PXB must be set in *bridge mode* (ref. PXB description).

| Jumpers:           | Function:       |                                       |

|--------------------|-----------------|---------------------------------------|

| O JP6              | JP6 - Inserted: | PXB registers not loaded from EEPROM. |

| ○ ● JP6<br>MACEway | JP6 - Removed:  | PXB registers loaded from EEPROM.     |

#### Reset from X

When the *Reset from X* jumper is removed, the PCI-RACEway bridge receives reset from PCI bus (i.e. MIDAS reset circuitry), and drives reset to the RACEway interlink. This setting should always be used.

Inserting this jumper may be destructive for the MIDAS board, and is likely to cause system malfunction.

| Jumpers:       | Function:       |                                     |

|----------------|-----------------|-------------------------------------|

| O DP10 RACEway | JP10 - Removed: | This setting should always be used. |

#### **PCI Bus Details**

#### **Arbitration**

#### Secondary PCI bus.

The PCI bus arbitration unit in the i960<sup>®</sup>RD # 1 is responsible for arbitration on the secondary PCI bus, for all MIDAS models.

The secondary bus arbiter of the i960®RD supports up to six secondary bus masters, plus its own secondary bus interface. Each request can be disabled or programmed to one of three priority levels. A memory mapped control register, programmed by the application software, sets the priorities for each of the bus masters. Each priority level is handled in a round-robin fashion. The three levels define a low, medium and high priority. Using the round-robin mechanism ensures there is a winner for each priority level. To enforce the concept of fairness, a slot is reserved for the winner of each priority level (except the highest) in the next highest priority. When the winner of a priority level is not granted the bus, during that particular arbitration sequence, it is promoted to the next highest level of priority. Once its bus ownership is removed, the device is reset to its initially programmed priority and may start arbitration once again.

For more information on the arbitration scheme, and on the programming of the arbiter, please refer to the i960<sup>®</sup>RD User's Manual.

Assignments to Arbiter (RD#1) Device Numbers

| PCI DEVICE               | DEVICE NUMBER |  |

|--------------------------|---------------|--|

| PMC # 2b                 | Device 0      |  |

| PMC # 3                  | Device 2      |  |

| PMC # 4                  | Device 4      |  |

| PMC # 5                  | Device 0      |  |

| i960 <sup>®</sup> RD # 2 | Device 1      |  |

Table 5. Secondary PCI Bus

#### Primary PCI bus

The arbitration of the primary PCI bus is handled in three different ways depending on MIDAS model.

#### MIDAS-200 Series

The PCI bus arbitration unit in the i960<sup>®</sup>RD # 2 is responsible for arbitration on the primary PCI bus for all MIDAS-200 series models. For more information, refer to the brief description *Secondary PCI Bus* (page 25) or the i960 User's manual.

Assignments to Arbiter (RD#2) Device Numbers

| realignments to rubiter (result) Beries realisers |               |  |  |  |

|---------------------------------------------------|---------------|--|--|--|

| PCI DEVICE                                        | DEVICE NUMBER |  |  |  |

| PMC # 1                                           | Device 1      |  |  |  |

| PMC # 2                                           | Device 2      |  |  |  |

| i960 <sup>®</sup> RD # 1                          | Device 0      |  |  |  |

| PXB (PCI-RACEway)                                 | Device 4      |  |  |  |

| VME-PCI BRIDGE                                    | Device 3      |  |  |  |

Table 6. Primary PCI Bus - Arbiter: RD#1

#### MIDAS-100 Series with RACEway Interface

For MIDAS models with RACEway interface, and with only one or none i960<sup>®</sup>RDs, the PCI bus arbitration unit in the PXB is responsible for arbitration on the primary PCI bus. This arbiter is programmable, and uses a round-robin arbitration scheme with two priority levels.

Assignments to Arbiter (PXB) Req/Gnt Pairs

| PCI DEVICE               | Req/Gnt Pairs |  |

|--------------------------|---------------|--|

| PMC # 1                  | Req1/Gnt1     |  |

| PMC # 2                  | Req2/Gnt2     |  |

| i960 <sup>®</sup> RD # 1 | Req4/Gnt4     |  |

| VME-PCI BRIDGE           | Req3/Gnt3     |  |

Table 7. Primary PCI Bus - Arbiter: PXB

#### Other MIDAS-1x0 Models

For MIDAS-120 and -150 models without RACEway interface, the arbiter for the primary PCI bus is implemented in a PLD. This arbiter uses a single level roundrobin arbitration scheme.

#### 'IDSEL' Generation

PCI bus uses a separate address space for initialization called *Configuration Space*. This address space uses a geographic addressing signal, IDSEL, to select target for all transactions. The standard way of assigning IDSEL to PCI devices & boards is to connect the IDSEL pin of each device/board to a unique AD[ ] bit.

This is also how IDSEL is generated on MIDAS. Table 8 & Table 9 shows IDSEL assignments.

| PCI DEVICE/BOARD         | IDSEL   | PCI ADDRESS FOR<br>CONFIG. CYCLE | VME BASE ADDRESS<br>FOR PCI CONFIG. CYCLE |

|--------------------------|---------|----------------------------------|-------------------------------------------|

| PMC # 1                  | pAD[16] | 0x00010XXX                       | 0xYYZZ2800                                |

| PMC # 2                  | pAD[17] | 0x00020XXX                       | 0xYYZZ3000                                |

| i960 <sup>®</sup> RD # 1 | pAD[18] | 0x00040XXX                       | 0xYYZZ3800                                |

| PXB (PCI-RACEway)        | pAD[19] | 0x00080XXX                       | 0xYYZZ4000                                |

| i960 <sup>®</sup> RD # 2 | pAD[20] | 0x00100XXX                       | 0xYYZZ4800                                |

| VME-PCI BRIDGE           | pAD[31] | 0x80000XXX                       |                                           |

'ZZ' = PCI Bus Number (as defined in Universe II MAST CTL register)

'YY' = VME base address for slave image

Table 8. IDSEL Assignments for Primary PCI Bus

| PCI DEVICE/BOARD         | IDSEL   | PCI ADDRESS FOR CONFIG. CYCLE | VME BASE ADDRESS<br>FOR PCI CONFIG. CYCLE |

|--------------------------|---------|-------------------------------|-------------------------------------------|

| PMC # 3                  | sAD[16] | 0x00010XXX                    | 0xYYWW0000                                |

| PMC # 4                  | sAD[17] | 0x00020XXX                    | 0xYYWW0800                                |

| PMC # 5                  | sAD[18] | 0x00040XXX                    | 0xYYWW1000                                |

| PMC # 2b                 | sAD[19] | 0x00080XXX                    | 0xYYWW1800                                |

| i960 <sup>®</sup> RD # 1 | sAD[21] | 0x00200XXX                    | 0xYYWW2800                                |

| i960 <sup>®</sup> RD # 2 | sAD[20] | 0x00100XXX                    | 0xYYWW2000                                |

'WW' = PCI Bus Number for secondary bus (as defined in i960 $^{\circ}$ RD)

Table 9. IDSEL Assignments for Secondary PCI Bus

## **Subtractive Decoding Agent**

The CR/CSR PLD utilizes subtractive decoding in the PCI bus *I/O Space*. No other PCI devices are allowed to do the same. Subtractive decoding in *Memory Space* may be used.

For further information, please refer to description of Configuration ROM.

<sup>&#</sup>x27;YY' = VME base address for slave image

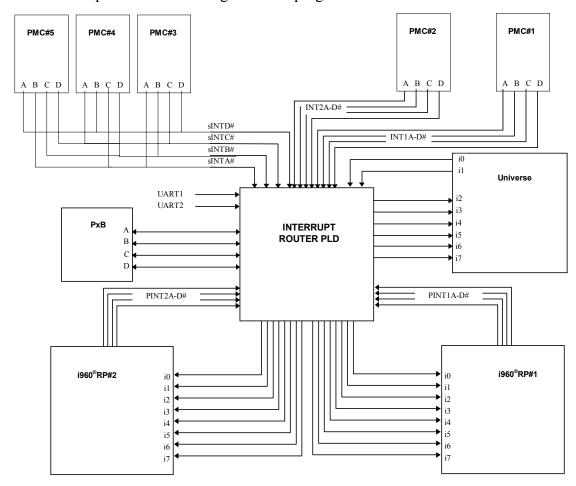

## **Interrupt Routing**

The MIDAS board has a number of interrupt sources and destinations. In order to provide a flexible interrupt routing scheme, which also allows customization, all interrupts are routed through a JTAG programmable PLD.

## **Interrupt Mode Selection**

Interrupt mode is selected by i960<sup>®</sup>RD #1 through two register bits in its UART.

| Register Name: MCR | Size: 8 bits | Address: 0xDF00.0004 |

|--------------------|--------------|----------------------|

|--------------------|--------------|----------------------|

| Bit | S | Function |   |     |      |          |     |     |  |  |

|-----|---|----------|---|-----|------|----------|-----|-----|--|--|

| 7:0 | ) | 0        | 0 | AFE | Loop | INT_MODE | RTS | DTR |  |  |

#### **MCR Description**

| Name     | Type Reset<br>State |    | Function        |                       |  |

|----------|---------------------|----|-----------------|-----------------------|--|

| INT_MODE | R/W                 | 00 | Interrupt Mode: | 00 = Interrupt Mode 0 |  |

|          |                     |    |                 | 01 = Interrupt Mode 1 |  |

|          |                     |    |                 | 10 = Interrupt Mode 2 |  |

Table 10. Interrupt Mode Selection

#### **Interrupt Jumpers**

Currently these jumpers are only used for MIDAS-xxxR boards to control whether the PCI-RACEway bridge should be treated as an interrupt source or a destination.

| Jumpers:        | Function:                                              |  |  |  |  |  |

|-----------------|--------------------------------------------------------|--|--|--|--|--|

| O O JP3         | JP15/3 - IN/OUT: PXB Treated as interrupt destination. |  |  |  |  |  |

| 0 0 JP15 NT INT | Other combinations: PXB Treated as interrupt source.   |  |  |  |  |  |

This jumper setting must be used if a MIDAS board with RACEway (-R) option is plugged into a non-RACEway slot.

#### **Interrupt Routing Tables**

The tables below show how the interrupts are routed for the three defined interrupt modes. All interrupt sources and destinations are present for a MIDAS-250R only. For other models, the routing scheme is the same, but sources (and destinations) not present should be ignored.

# Interrupt Mode 0:

|                      |         |         |                  | INTERRUP | T PIN - SOUR | CE         |      |         |         |

|----------------------|---------|---------|------------------|----------|--------------|------------|------|---------|---------|

| i960 <sup>®</sup> RD | PMC#1   | PMC#2   | PMC#3/<br>PMC#2b | PMC#4    | PMC#5        | Universe I | UART | PXB     | 1960RD  |

| #1&2                 |         |         | PIVIC#20         |          |              |            |      |         | (other) |

| Interrupt pin        | A B C D | A B C D | A B C D          | A B C D  | A B C D      | 0 1        |      | A B C D | A B C D |

| XINT0#               |         |         | Α                | С        | В            |            |      | D       | С       |

| XINT1#               |         |         | В                | D        | С            |            |      | Α       | D       |

| XINT2#               |         |         | С                | Α        | D            |            |      | В       | Α       |

| XINT3#               |         |         | D                | В        | Α            |            |      | С       | В       |

| XINT4#               | A C     | B D     |                  |          |              |            |      |         |         |

| XINT5#               | B D     | A C     |                  |          |              |            |      |         |         |

| XINT6#               |         |         |                  |          |              | 0          |      |         |         |

| XINT7#               |         |         |                  |          |              | 1          | Х    |         |         |

|               |    |      |   |   |      |   |   |   |              |   | ı | NTE | RR  | RUP1 | PI | N · | - Sc | DUR | CE |     |     |            |    |     |     |                |   |   |    |   |

|---------------|----|------|---|---|------|---|---|---|--------------|---|---|-----|-----|------|----|-----|------|-----|----|-----|-----|------------|----|-----|-----|----------------|---|---|----|---|

| UNIVERSE II   | PM | IC#1 |   | F | PMC# | 2 |   |   | C#3/<br>C#2b |   | F | PM( | C#4 | 4    | F  | PN  | 1C#  | 5   | 19 | 60F | RD# | <b>‡</b> 1 | 19 | 60F | RD# | <del>‡</del> 2 |   | P | XB |   |

| Interrupt pin | АВ | С    | D | Α | ВС   | D | Α | В | С            | D | Α | В   | С   | D    | Α  | В   | С    | D   | Α  | В   | С   | D          | Α  | В   | С   | D              | Α | В | С  | D |

| LINT2#        | Α  |      |   |   |      | D |   |   |              |   |   |     |     |      |    |     |      |     |    |     |     |            |    |     |     |                |   |   |    |   |

| LINT3#        |    |      | D | Α |      |   |   |   |              |   |   |     |     |      |    |     |      |     |    |     |     |            |    |     |     |                |   |   |    |   |

| LINT4#        |    | С    |   |   |      |   | Α |   |              |   |   |     | С   |      |    | В   |      |     | Α  |     |     |            |    |     | С   |                |   |   | С  |   |

| LINT5#        |    |      |   |   | С    |   |   | В |              |   |   |     |     | D    |    |     | С    |     |    | В   |     |            |    |     |     | D              | Α |   |    |   |

| LINT6#        | В  |      |   |   |      |   |   |   | С            |   | Α |     |     |      |    |     |      | D   |    |     | С   |            | Α  |     |     |                |   |   |    | D |

| LINT7#        |    | В    |   |   |      |   |   | D |              | В |   |     | Α   |      |    |     |      |     |    | D   |     | В          |    |     |     | В              |   | · |    |   |

|               |   |    |     |   |   |    |     |   |   |   |              |   | ı | NTE | ERR | RUP1 | Pı | N - | So  | UR | CE |     |     |            |    |     |     |    |   |      |       |   |

|---------------|---|----|-----|---|---|----|-----|---|---|---|--------------|---|---|-----|-----|------|----|-----|-----|----|----|-----|-----|------------|----|-----|-----|----|---|------|-------|---|

| PXB           | F | PM | C#1 | 1 | ı | PM | C#2 | 2 | ı |   | C#3/<br>C#2b |   | F | PM  | C#4 | 1    | F  | PM¢ | C#5 | 5  | 19 | 60F | RD# | <b>‡</b> 1 | 19 | 60F | RD: | #2 | U | NIVE | RSE I | 1 |

| Interrupt pin | Α | В  | С   | D | Α | В  | С   | D | Α | В | С            | D | Α | В   | С   | D    | Α  | В   | С   | D  | Α  | В   | С   | D          | Α  | В   | С   | D  |   | 0    | 1     |   |

| INTA#         |   |    | С   |   |   |    |     | D | Α |   |              |   |   |     | С   |      |    | В   |     |    | Α  |     |     |            |    |     | С   |    |   | 0    |       |   |

| INTB#         | Α |    |     |   |   |    | С   |   |   | В |              |   |   |     |     | D    |    |     | С   |    |    | В   |     |            |    |     |     | D  |   |      |       |   |

| INTC#         |   | В  |     |   | Α |    |     |   |   |   | С            |   | Α |     |     |      |    |     |     | D  |    |     | С   |            | Α  |     |     |    |   |      |       |   |

| INTD#         |   |    |     | D |   | В  |     |   |   |   |              | D |   | В   |     |      | Α  |     |     |    |    |     |     | D          |    | В   |     |    |   |      | 1     |   |

# Interrupt Mode 1:

|                        |    |                                              |   |   |     |    |   |   |              |   | Int | ERF | RUP | т Рі | N - | Sou | JR | CE    |        |      |   |   |    |   |   |    |    |   |

|------------------------|----|----------------------------------------------|---|---|-----|----|---|---|--------------|---|-----|-----|-----|------|-----|-----|----|-------|--------|------|---|---|----|---|---|----|----|---|

| i960 <sup>®</sup> RD#1 | PM | C#1                                          | 1 | F | PMC | #2 |   |   | C#3/<br>C#2b |   | PM  | C#4 | 1   | F    | PMC | #5  |    | UNIVE | RSE II | UART |   | P | ΧB |   |   | RD | #2 |   |

| Interrupt pin          | АВ | С                                            | D | Α | В   | D  | Α | В | C D          | Α | В   | С   | D   | Α    | В   | С   | D  | 0     | 1      |      | Α | В | С  | D | Α | В  | С  | D |

| XINT0#                 | Α  | С                                            |   |   |     |    |   |   |              |   |     |     |     |      |     |     |    |       |        |      |   |   |    |   |   |    |    |   |

| XINT1#                 |    |                                              |   | Α | (   |    |   |   |              |   |     |     |     |      |     |     |    |       |        |      |   |   |    |   |   |    |    |   |

| XINT2#                 | В  |                                              | D |   |     |    | Α |   |              |   |     | С   |     |      | В   |     |    |       |        |      | Α |   |    |   |   |    |    |   |

| XINT3#                 |    |                                              |   |   | В   | D  |   |   | С            | Α |     |     |     |      |     | [   | D  |       |        |      |   | В |    |   |   |    |    |   |

| XINT4#                 |    |                                              |   |   |     |    |   |   | D            |   | В   |     |     | Α    |     |     |    |       |        | Х    |   |   |    |   |   |    |    |   |

| XINT5#                 |    |                                              |   |   |     |    |   | В |              |   |     |     | D   |      |     | С   |    | 0     |        |      |   |   |    |   |   |    |    |   |

| XINT6#                 |    | Reserved i960 <sup>®</sup> RD DMA Controller |   |   |     |    |   |   |              |   |     |     |     |      |     |     |    |       |        |      |   |   |    |   |   |    |    |   |

| XINT7#                 |    | Reserved i960 <sup>®</sup> RD Message Unit   |   |   |     |    |   |   |              |   |     |     |     |      |     |     |    |       |        |      |   |   |    |   |   |    |    |   |

|                        |    |                                            |                                              |   |     |    |   |   |             |   |   | Int | ERF | RUP | т Рі | N - | Sc  | UR | CE    |        |      |   |   |    |   |   |     |            |

|------------------------|----|--------------------------------------------|----------------------------------------------|---|-----|----|---|---|-------------|---|---|-----|-----|-----|------|-----|-----|----|-------|--------|------|---|---|----|---|---|-----|------------|

| i960 <sup>®</sup> RD#2 | PΝ | /IC#                                       | 1                                            | ı | PMC | #2 |   |   | C#3<br>C#2I |   | ı | РМ  | C#4 | 1   | F    | РМ  | C#5 | 5  | UNIVE | RSE II | UART |   | P | ΚB |   | ı | ₹Dŧ | <b>#</b> 1 |

| Interrupt pin          | АВ | С                                          | D                                            | Α | В   | СС | Α | В | С           | D | Α | В   | С   | D   | Α    | В   | С   | D  | 0     | 1      |      | Α | В | С  | D | Α | В   | C D        |

| XINT0#                 |    |                                            |                                              | Α |     | С  |   |   |             |   |   |     |     |     |      |     |     |    |       |        |      |   |   |    |   |   |     |            |

| XINT1#                 | Α  | С                                          |                                              |   |     |    |   |   |             |   |   |     |     |     |      |     |     |    |       |        |      |   |   |    |   |   |     |            |

| XINT2#                 |    |                                            |                                              |   | В   | С  | ) |   | С           |   | Α |     |     |     |      |     |     | D  |       |        |      |   |   | С  |   |   |     |            |

| XINT3#                 | В  | }                                          | D                                            |   |     |    | Α |   |             |   |   |     | С   |     |      | В   |     |    |       |        |      |   |   |    | D |   |     |            |

| XINT4#                 |    |                                            |                                              |   |     |    |   |   |             | D |   | В   |     |     | Α    |     |     |    |       |        | Х    |   |   |    |   |   |     |            |

| XINT5#                 |    |                                            |                                              |   |     |    |   | В |             |   |   |     |     | D   |      |     | С   |    |       | 1      |      |   |   |    |   |   |     |            |

| XINT6#                 |    |                                            | Reserved i960 <sup>®</sup> RD DMA Controller |   |     |    |   |   |             |   |   |     |     |     |      |     |     |    |       |        |      |   |   |    |   |   |     |            |

| XINT7#                 |    | Reserved i960 <sup>®</sup> RD Message Unit |                                              |   |     |    |   |   |             |   |   |     |     |     |      |     |     |    |       |        |      |   |   |    |   |   |     |            |

|               |    |     |   |   |     |    |     |   |            |   |   | INT | ERR | RUP | г Рі | N  | - S | OUR        | CE |     |     |            |    |     |     |    |   |   |    |   |

|---------------|----|-----|---|---|-----|----|-----|---|------------|---|---|-----|-----|-----|------|----|-----|------------|----|-----|-----|------------|----|-----|-----|----|---|---|----|---|

| Universe II   | PM | C#1 |   | F | PMC | #2 |     |   | C#3<br>C#2 |   | ı | PM  | C#4 | 4   | ı    | PΝ | 1C# | <b>#</b> 5 | 19 | 60F | RD# | <b>‡</b> 1 | 19 | 60F | RDi | #2 |   | P | ΧB |   |

| Interrupt pin | АВ | С   | D | Α | В   | C  | ) A | В | С          | D | Α | В   | С   | D   | Α    | В  | C   | D          | Α  | В   | С   | D          | Α  | В   | С   | D  | Α | В | С  | D |

| LINT2#        |    |     |   |   |     |    |     |   |            |   |   |     |     |     |      |    |     |            |    |     |     |            |    |     |     |    | Α |   |    |   |

| LINT3#        |    |     |   |   |     |    |     |   |            |   |   |     |     |     |      |    |     |            |    |     |     |            |    |     |     |    |   | В |    |   |

| LINT4#        |    |     |   |   |     |    |     |   |            |   |   |     |     |     |      |    |     |            | Α  |     |     |            |    |     | С   |    |   |   |    |   |

| LINT5#        |    |     |   |   |     |    |     |   |            |   |   |     |     |     |      |    |     |            |    | В   |     |            |    |     |     | D  |   |   |    |   |

| LINT6#        |    |     |   |   |     | •  |     | • |            |   |   |     |     |     |      |    |     |            |    | •   | С   |            | Α  |     |     |    |   | • | •  |   |

| LINT7#        |    |     |   |   |     |    |     |   |            |   |   |     |     |     |      |    |     |            |    |     |     | D          |    | В   |     |    |   |   |    |   |

|               |         |         |                  | INTERRUP | TPIN - SOUR | CE       |          |             |

|---------------|---------|---------|------------------|----------|-------------|----------|----------|-------------|

| PXB           | PMC#1   | PMC#2   | PMC#3/<br>PMC#2b | PMC#4    | PMC#5       | 1960RD#1 | 1960RD#2 | Universe II |

| Interrupt pin | A B C D | A B C D | A B C D          | A B C D  | A B C D     | A B C D  | A B C D  | 0 1         |

| INTA#         |         |         |                  |          |             | А        | С        |             |

| INTB#         |         |         |                  |          |             | В        | D        |             |

| INTC#         |         |         |                  |          |             | С        | Α        |             |

| INTD#         |         |         |                  |          |             | D        | В        |             |

# Interrupt Mode 2:

|                        |       |    |   |     |                |   |   |              |   | ı | INTE | RF  | UP. | гΡι | N - | Sc  | DUF | RCE   |        |      |   |   |    |   |    |     |          |

|------------------------|-------|----|---|-----|----------------|---|---|--------------|---|---|------|-----|-----|-----|-----|-----|-----|-------|--------|------|---|---|----|---|----|-----|----------|

| i960 <sup>®</sup> RD#1 | PMC#  | ‡1 | - | PMC | <del>‡</del> 2 |   |   | C#3/<br>C#2b |   | F | PMC  | C#4 | _   | F   | PMC | C#5 | 5   | UNIVE | RSE II | UART |   | P | ΚB |   | R  | D#2 | <u>?</u> |

| Interrupt pin          | A B C | D  | Α | В   | D              | Α | В | С            | ) | Α | В    | С   | D   | Α   | В   | С   | D   | 0     | 1      |      | Α | В | С  | D | AE | 3 C | D        |

| XINT0#                 |       |    |   |     |                | Α |   |              |   |   |      | С   |     |     | В   |     |     |       |        |      |   |   |    | D |    | С   |          |

| XINT1#                 |       |    |   |     |                |   | В |              |   |   |      |     | D   |     |     | С   |     |       |        |      | Α |   |    |   |    |     | D        |

| XINT2#                 |       |    |   |     |                |   |   | С            |   | Α |      |     |     |     |     |     | D   |       |        |      |   | В |    |   | Α  |     |          |

| XINT3#                 |       |    |   |     |                |   |   | [            | ) |   | В    |     |     | Α   |     |     |     |       |        |      |   |   | С  |   | E  | 3   |          |

| XINT4#                 |       |    |   |     |                |   |   |              |   |   |      |     |     |     |     |     |     | 0     |        |      |   |   |    |   |    |     |          |

| XINT5#                 |       |    |   |     |                |   |   |              |   |   |      |     |     |     |     |     |     |       | 1      |      |   |   |    |   |    |     |          |

| XINT6#                 | A C   | ;  |   |     |                |   |   |              |   |   |      |     |     |     |     |     |     |       |        |      |   |   |    |   |    |     |          |

| XINT7#                 | В     | D  |   |     |                |   |   | ·            |   |   |      |     |     |     |     |     |     |       |        | Х    |   |   |    |   |    |     |          |

|                        |         |         |                  | INTERRUP | T PIN - SOUF | RCE         |      |         |         |

|------------------------|---------|---------|------------------|----------|--------------|-------------|------|---------|---------|

| i960 <sup>®</sup> RD#2 | PMC#1   | PMC#2   | PMC#3/<br>PMC#2b | PMC#4    | PMC#5        | Universe II | UART | PXB     | RD#1    |

| Interrupt pin          | A B C D | A B C D | A B C D          | A B C D  | A B C D      | 0 1         |      | A B C D | A B C D |

| XINT0#                 |         |         | Α                | С        | В            |             |      | D       | С       |

| XINT1#                 |         |         | В                | D        | С            |             |      | Α       | D       |

| XINT2#                 |         |         | С                | Α        | D            |             |      | В       | Α       |

| XINT3#                 |         |         | D                | В        | Α            |             |      | С       | В       |

| XINT4#                 |         |         |                  |          |              | 1           |      |         |         |

| XINT5#                 |         |         |                  |          |              | 0           |      |         |         |

| XINT6#                 |         | A C     |                  |          |              |             |      |         |         |

| XINT7#                 |         | B D     |                  |          |              |             | Х    |         |         |

|               |         |         |                  | INTERRUP <sup>-</sup> | r Pin - Sour | CE       |          |         |

|---------------|---------|---------|------------------|-----------------------|--------------|----------|----------|---------|

| UNIVERSE II   | PMC#1   | PMC#2   | PMC#3/<br>PMC#2b | PMC#4                 | PMC#5        | 1960RD#1 | 1960RD#2 | РХВ     |

| Interrupt pin | A B C D | A B C D | A B C D          | A B C D               | A B C D      | A B C D  | A B C D  | A B C D |

| LINT2#        | А       | D       |                  |                       |              |          |          |         |

| LINT3#        | D       | Α       |                  |                       |              |          |          |         |

| LINT4#        | С       |         | Α                | С                     | В            | Α        | С        | С       |

| LINT5#        |         | С       | В                | D                     | С            | В        | D        | Α       |

| LINT6#        | В       |         | С                | Α                     | D            | С        | Α        | D       |

| LINT7#        |         | В       | D                | В                     | Α            | D        | В        | В       |

|               |   |     |     |   |   |     |     |   |     |             |   |   | INTE | RRI | UPT | PIN - | Sc  | URO | CE  |     |     |          |    |     |     |                |    |      |        |  |

|---------------|---|-----|-----|---|---|-----|-----|---|-----|-------------|---|---|------|-----|-----|-------|-----|-----|-----|-----|-----|----------|----|-----|-----|----------------|----|------|--------|--|

| PXB           | F | PMO | C#1 | l | F | PMO | C#2 | 2 |     | 1C#3<br>C#2 |   | ı | PMC  | C#4 |     | PM    | C#! | 0   | 196 | 30F | RD# | <u>1</u> | 19 | 60F | RD# | <del>‡</del> 2 | Uı | NIVE | RSE II |  |

| Interrupt pin | Α | В   | С   | D | Α | В   | С   | D | A E | С           | D | Α | В    | С   | D   | АВ    | С   | D   | Α   | В   | С   | D        | Α  | В   | С   | D              |    | 0    | 1      |  |

| INTA#         |   |     |     |   |   |     |     |   | Α   |             |   |   |      | С   |     | В     |     |     |     |     |     |          |    |     |     |                |    |      |        |  |

| INTB#         |   |     |     |   |   |     |     |   | Е   | }           |   |   |      |     | D   |       | С   |     |     |     |     |          |    |     |     |                |    |      |        |  |

| INTC#         |   |     |     |   |   |     |     |   |     | С           |   | Α | •    |     |     |       | •   | D   |     |     |     |          |    | •   |     |                |    |      |        |  |

| INTD#         |   |     |     |   |   |     |     |   |     |             | D |   | В    |     |     | Α     |     |     |     |     |     |          |    |     |     |                |    |      |        |  |

# **Appendix I: PMC I/O Routing**

# **PMC I/O Routing Scheme**

| DMG0 T4 | DVG1 T4 | D0 3     |

|---------|---------|----------|

| PMC2 J4 | PMC1 J4 | P2 row A |

| 34      | 2       | 1        |

| 36      | 4       | 2        |

| 38      | 6       | 3        |

| 40      | 8       | 4        |

| 42      | 10      | 5        |

| 44      | 12      | 6        |

| 46      | 14      | 7        |

| 48      | 16      | 8        |

| 50      | 18      | 9        |

| 52      | 20      | 10       |

| 54      | 22      | 11       |

| 56      | 24      | 12       |

| 58      | 26      | 13       |

| 60      | 28      | 14       |

| 62      | 30      | 15       |

| 64      | 32      | 16       |

|         | 34      | 17       |

|         | 36      | 18       |

|         | 38      | 19       |

|         | 40      | 20       |

|         | 42      | 21       |

|         | 44      | 22       |

|         | 46      | 23       |