Date: Jan. 15, 2013

# RENESAS TECHNICAL UPDATE

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                                                          |          | Document<br>No.         | TN-RX*-A048A/E                             | Rev. | 1.00 |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------|--------------------------------------------|------|------|

| Title                 | I <sup>2</sup> C bus interface (RIIC) Precautions for using timeout detection function and stop condition issuance timing when receiving master. |          | Information<br>Category | Technical Notification                     |      |      |

|                       |                                                                                                                                                  | Lot No.  |                         |                                            |      |      |

| Applicable<br>Product | RX630 group                                                                                                                                      |          | Reference<br>Document   | RX630 group                                |      |      |

|                       | RX63N, RX631 group                                                                                                                               | All lots |                         | RX63N, RX631 group<br>User's Manual, Hardw |      | on   |

This is to let you know that we have revised the Technical Update which had been already issued (Issue number:

TN-RX\*-A012A/E Rev.1.00, TN-RX\*-A013A/E Rev.1.00). The revised portions are indicated in red letters (in flow chart, indicated in red and blue letters).

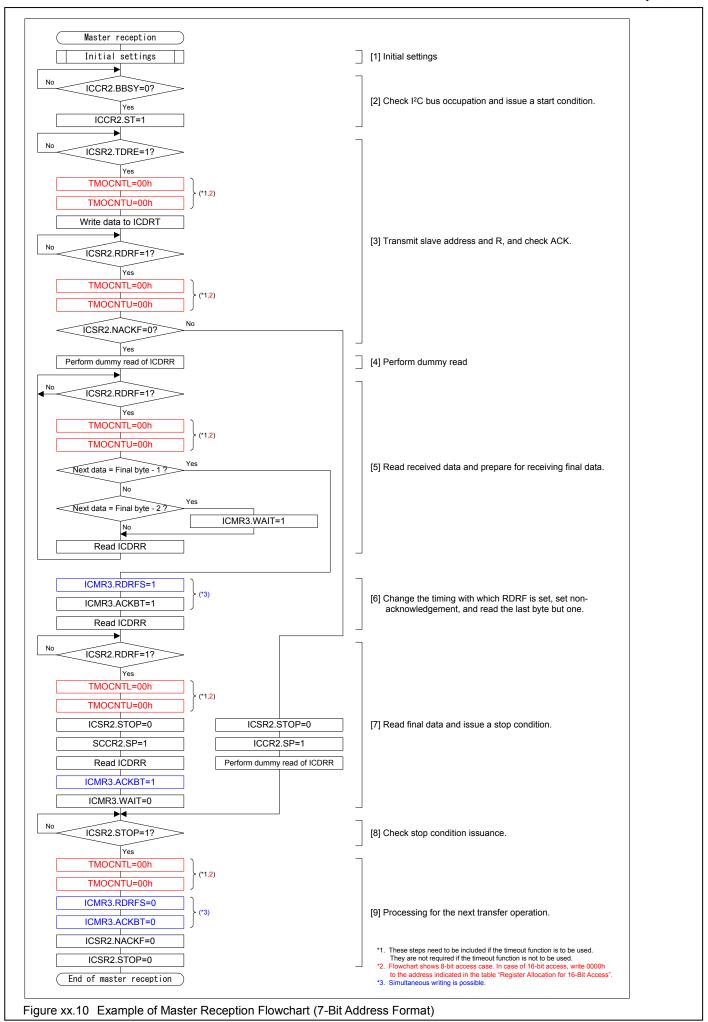

1. Precautions for stop condition issuance timing when receiving master

With I<sup>2</sup>C bus interface (RIIC), one clock cycle may be inserted between the ninth clock cycle of master reception and stop condition issuance.

When this clock affects the communication, follow the avoidance flow "Figure xx.10 Example of Master Reception Flowchart (7-Bit Address Format)" indicated on the Page.6 of this Technical Update.

## (1) Conditions

- •While holding at low at the falling edge of the ninth clock cycle, writing SP=1 and reading data from ICDRR are performed in a row.

- •When data is read from ICDRR after the falling edge of the ninth clock of master reception and writing SP=1 are detected at the same time in the RIIC.

- •After SP=1 is written, when the falling edge of the ninth clock cycle of master reception and data reading from ICDRR are detected at the same time in the RIIC.

#### (2) Phenomenon

One clock cycle is inserted between the ninth clock cycle of master reception and stop condition issuance.

## 2. Precautions when using timeout detection function

While timeout detection function of  $I^2C$  bus interface (RIIC) is set to CMR1.CKS [2:0]  $\neq$  000b, timeout is detected even when communications are proceeding correctly. To avoid this, use registered disclosed in this document and follow the avoidance flow. In this avoidance flow, every time data is accessed, write 00h to the timeout internal counter and clear counter.

Thus, it is applicable only to data transfer using CPU or one using DTC. When you use DMAC for data transfer of RIIC, you need to set ICMR1.CKS [2:0] = 000b or change it to transfer using CPU or one using DTC.

Date: January 15, 2013

(1) Condition

When using timeout detection function of  $I^2C$  bus interface (RIIC) under the setting of CMR1.CKS [2:0]  $\neq$  000.

(2) Phenomenon

Even when communications are proceeding correctly, timeout is detected from a set of ICFER.TMOE bit after a certain period of time for detection has elapsed.

## (3) Disclosed register

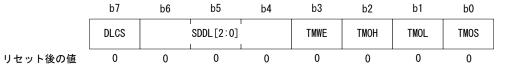

① ICMR2.TMWE bit (b3) of I2C bus mode register (ICMR2) will be disclosed.

| Bit | Symbol | Bit name                                  | Description                                                                                                                  | R/W |

|-----|--------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|

| b3  | TMWE   | Timeout internal counter write enable bit | 0: Writing to internal counter of timeout detection function is disabled                                                     | R/W |

|     |        |                                           | 1: Writing to internal counter of timeout detection function is enabled                                                      |     |

|     |        |                                           | When this bit is set to "1", the address of timeout internal counter (TMOCNTL/U) is allocated to the address of SARL0/SARU0. |     |

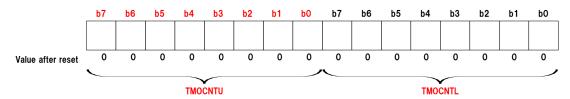

② Disclose the timeout internal counter register (TMOCNT).

Timeout internal counter (TMOCNT)

Address RIIC0.TMOCNTL 0008 830Ah\*, RIIC0.TMOCNTU 0008 832Ah\*

RIIC1.TMOCNTL 0008 830Bh\*, RIIC1.TMOCNTU 0008 832Bh\*

\*Same addresses with ones of the slave address registers, SARL0, SARU0. Care should be taken.

# ·TMOS=0 (Long mode)

## ·TMOS=1 (Short mode)

| Date: January 15, 2 |

|---------------------|

|---------------------|

| Bit  | Symbol  | Bit name                 | Description                        | R/W  |

|------|---------|--------------------------|------------------------------------|------|

| b7-0 | TMOCNTL | Timeout internal counter | Timeout internal counter low-order | W *1 |

<sup>\*1 :</sup> Value in timeout internal counter cannot be read. When value is read, the read value is FFh.

| Bit  | Symbol  | Bit name                 | Description                            | R/W  |

|------|---------|--------------------------|----------------------------------------|------|

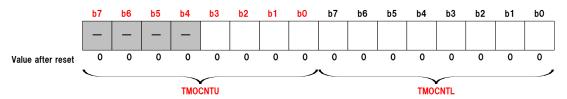

| b7-0 | TMOCNTU | Timeout internal counter | Timeout internal counter high-order *1 | W *2 |

<sup>\*1 :</sup> With TMOS=1 (Short mode), b7-b4 are reserved bits. They are writable, however value written is disabled.

Timeout internal counter (TMOCNTL/TMOCNTU) is initialized (00h) after a reset, while ICCR1.IICRST=1 or ICFER.TMOE=1 and PCLK/1 is selected with ICMR1.CKS[2:0]=000b setting, and when counter clear conditions specified by TMOH/TMOL of ICMR2 (SCL rising edge/falling edge detection) are satisfied.

TMOCNTL register and TMOCNTU register comprise a single 16-bit register so they can be accessed together by 16-bit transfer instruction. In case of 16-bit access, please access to the address indicated in the table "Register Allocation for 16-Bit Access" below.

Table. Register Allocation for 16-Bit Access

| Address    | Upper 8 Bits  | Lower 8 Bits  |

|------------|---------------|---------------|

| 0008 830Ah | RIIC0.TMOCNTU | RIIC0.TMOCNTL |

| 0008 832Ah | RIIC1.TMOCNTU | RIIC1.TMOCNTL |

<sup>\*2 :</sup> Value in timeout internal counter cannot be read. When value is read, the read value is FFh.

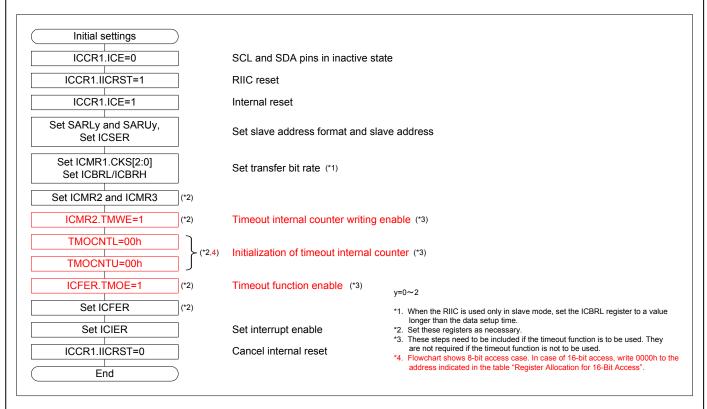

#### 3. Avoidance Flow

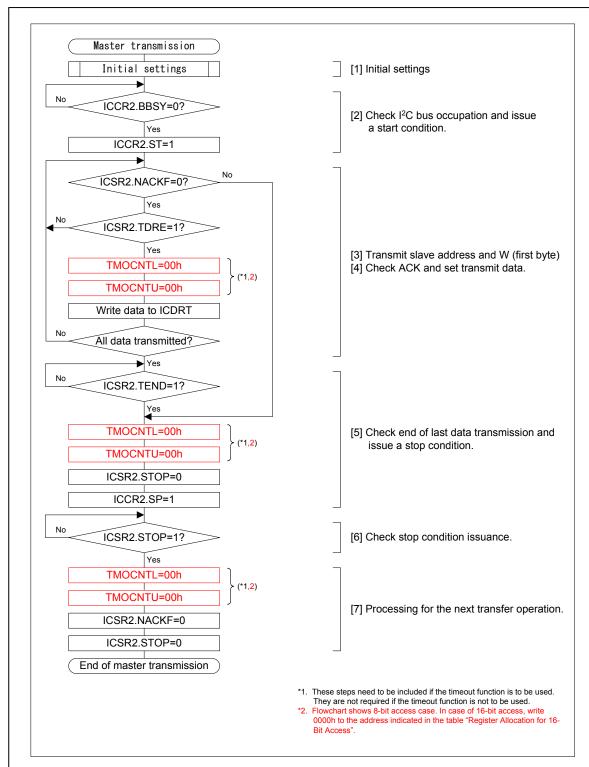

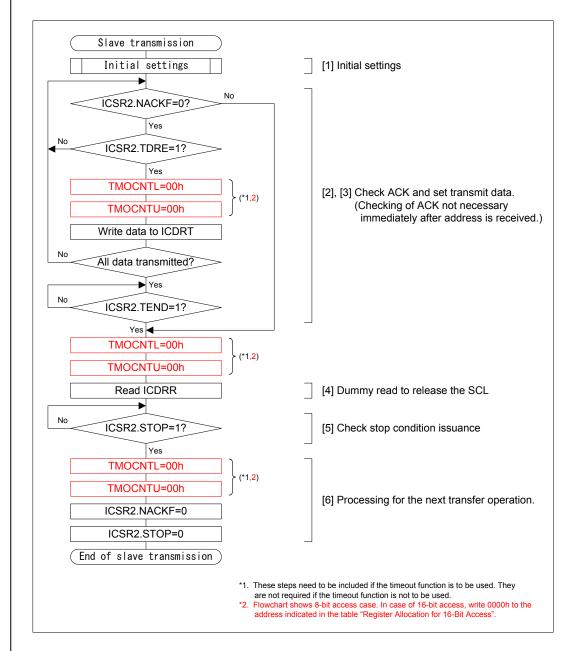

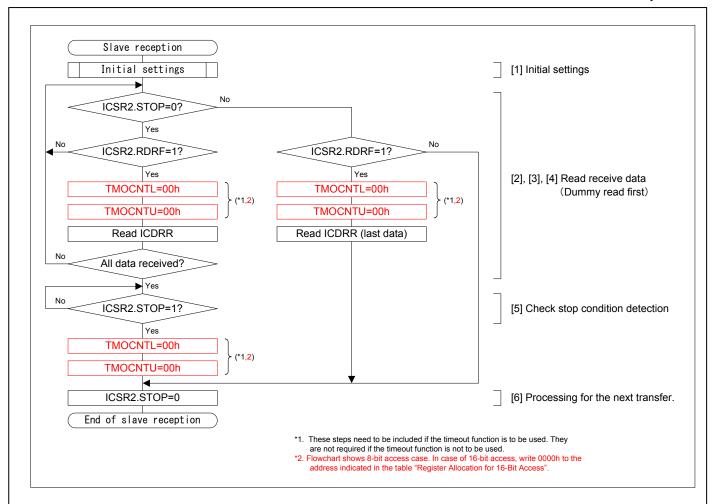

To avoid "1. Precautions for stop condition issuance timing when receiving master" and "2. Precautions for timeout detection function", add the procedures to the flowchart in the user's manual.

Additional procedures for "1. Precautions for stop condition issuance timing when receiving master" are marked in blue, and those for "2. Precautions for using timeout detection function" are marked in red.

"xx" as in Figure xx.5 indicates the chapter of I<sup>2</sup>C of the user's manual respectively. Please refer to the "Target products and Reference" for details.

Figure xx.5 Example of RIIC Initialization Flow

Date: January 15, 2013

Figure xx.6 Example of Master Transmission Flowchart

Figure xx.14 Example of Slave Transmission Flowchart

Figure xx.17 Example of Slave Reception Flowchart

#### Date: January 15, 2013

#### 4. Avoidance when using DTC

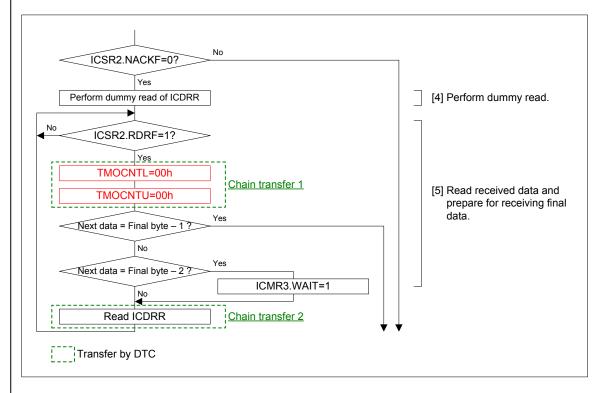

When writing transmit data to ICDRT or reading receive data from ICDRR by the DTC during master transmission/reception, use the following flow to avoid the phenomenon. Set the DTC to chain transfer, and clear internal counter every time transmit data or receive data is transferred.

Master reception flowchart is indicated below.

This flowchart shows only flow involved with DTC transfer. For the rest of the flow, refer to the flowcharts indicated on page 4 to 8.

(1) Initial settings flow: What is indicated on page 4 + DTC setting

The DTC needs to be set to enable the following operation.

Set the DTC to chain transfer.

- •First chain transfer (Chain transfer 1): Write 00h to TMOCNTL and TMOCNTU.

- ·Subsequent chain transfer (Chain transfer 2): Transfer specified by user (Read ICDRR, etc)

- (2) Example of flowchart during N-2 times transfer by DTC (excerpt comments from the flowchart on page 6)

# Date: January 15, 2013

# ■Target Products and Reference

| Group                       | Title                                            | Rev.     | Document No.    | Chapter of I <sup>2</sup> C |

|-----------------------------|--------------------------------------------------|----------|-----------------|-----------------------------|

| RX630 group                 | RX630 Group User's Manual: Hardware              | Rev.1.50 | R01UH0040EJ0150 | 33                          |

| RX63N group,<br>RX631 group | RX63N Group, RX631 Group User's Manual: Hardware | Rev.1.50 | R01UH0041EJ0150 | 36                          |