# **MCDS User's Guide**

### **TRACE32 Online Help**

**TRACE32 Directory**

**TRACE32 Index**

| TRACE32 Documents                      |    |

|----------------------------------------|----|

| ICD In-Circuit Debugger                |    |

| Processor Architecture Manuals         |    |

| TriCore                                |    |

| MCDS User's Guide                      | 1  |

| Introduction                           | 5  |

| Intended Audience                      | 5  |

| How to read this Document              | 5  |

| Related Documents                      | 6  |

| Background Information                 | 7  |

| Trace Source                           | 7  |

| Program Trace                          | 7  |

| Trace Sink                             | 8  |

| Trace Filter and Trigger               | 8  |

| The Emulation Device Concept           | 9  |

| TRACE32 Support for Emulation Devices  | 11 |

| Feature Overview                       | 11 |

| Target Interface                       | 11 |

| MCDS Licensing                         | 12 |

| MCDS Basic Features                    | 14 |

| MCDS Concept                           | 14 |

| MCDS of XC2000ED and C166              | 14 |

| MCDS of TriCore                        | 15 |

| MCDS Configuration                     | 16 |

| General Settings                       | 17 |

| Timestamp Setup                        | 17 |

| Trace Buffer Configuration             | 18 |

| AGBT Off-chip Trace Configuration      | 18 |

| Trace Sources                          | 18 |

| Example: Core Trace on TriCore AURIX   | 19 |

| Example: Bus Trace on TriCore AUDO-MAX | 20 |

| Trace Control                          | 21 |

| Trace States                           | 21 |

|                                        |    |

| Trace Buffer Size and Usage                  | 22 |

|----------------------------------------------|----|

| Trace Modes                                  | 22 |

| Trace Trigger Configuration                  | 22 |

| Other Trace Configuration Commands           | 23 |

| Basic Trace Usage                            | 23 |

| Trigger and Filter via Break.Set command     | 24 |

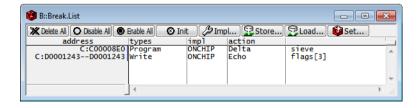

| MCDS Breakpoints                             | 25 |

| Trace Filter                                 | 35 |

| Examples                                     | 35 |

| Watchpoints                                  | 39 |

| Example                                      | 40 |

| Trace Decoding                               | 41 |

| Bus Trace Information                        | 43 |

| Searching the Trace                          | 44 |

| Specific Cycles                              | 44 |

| Special Events                               | 45 |

| Exception Decoding                           | 45 |

| Exception Decoding Using Tables              | 46 |

| Exception Decoding Using DCU Messages        | 46 |

| Trace Limitations and Restrictions           | 47 |

| MCDS Unlocking                               | 48 |

| MCDS Special Features                        | 49 |

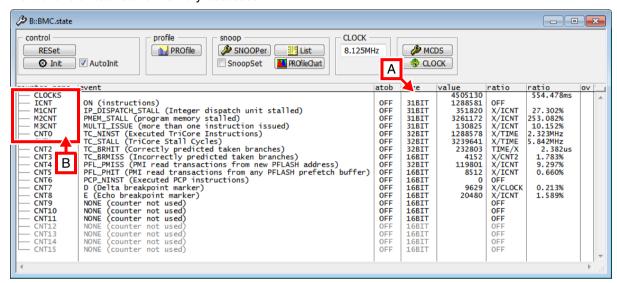

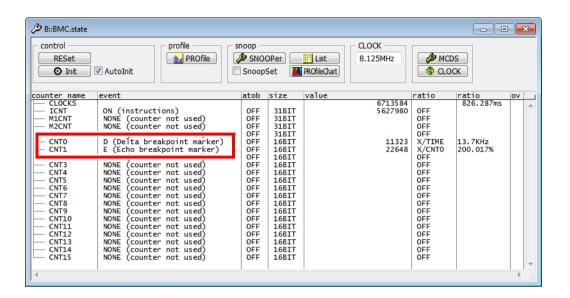

| Benchmark Counters                           | 49 |

| Counting Chip-internal Signals               | 50 |

| Example                                      | 50 |

| Counting User-defined Events                 | 50 |

| Example                                      | 50 |

| Trace Through Resets and Power Cycles        | 51 |

| Soft Resets                                  | 51 |

| Hard Resets                                  | 52 |

| Power Cycles                                 | 52 |

| Reset Marker                                 | 52 |

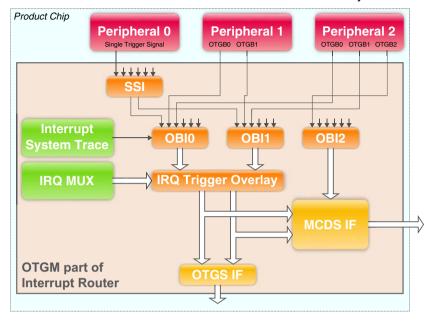

| Special Trace Sources via OTGM               | 53 |

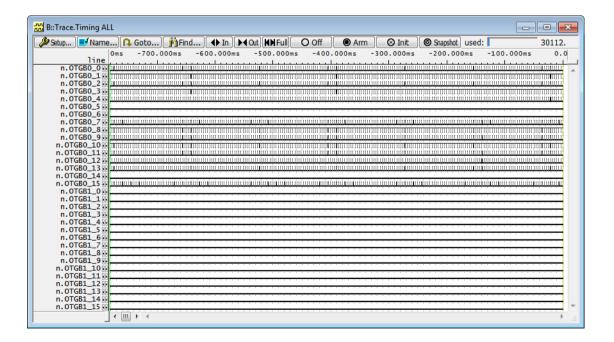

| Peripheral Trace                             | 55 |

| Example: Peripheral Trace for DMA of TC277TE | 56 |

| Trace Evaluation                             | 57 |

| Signal Options                               | 59 |

| Tracing the GTM                              | 60 |

| Example: GTM trace of TC265DE                | 61 |

| miniMCDS                                     | 67 |

| Known Issues and Recommendations             | 68 |

| OCTL Complex Trigger Programming             | 69 |

| OCTL Features                                | 69 |

| OCTL Example: Bus Trigger                       |  |

|-------------------------------------------------|--|

| Clock System                                    |  |

| EEC Clock System                                |  |

| Maximum Clock Frequency                         |  |

| Allowed Clock Ratios                            |  |

| Verifying the Clock Setup                       |  |

| Device Specific Details                         |  |

| XC2000ED and C166                               |  |

| TriCore AUDO-NG (TC v1.3)                       |  |

| TriCore AUDO-F, AUDO-S and AUDO-MAX (TC v1.3.1) |  |

| TriCore AUDO-MAX (TC v1.6)                      |  |

| TriCore AURIX (TC v1.6.1)                       |  |

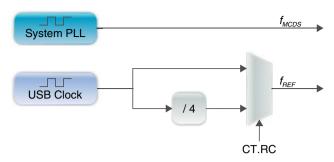

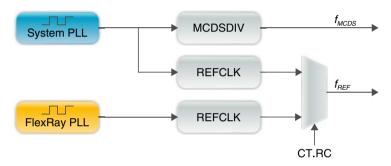

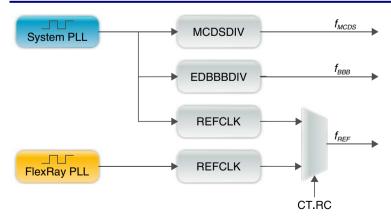

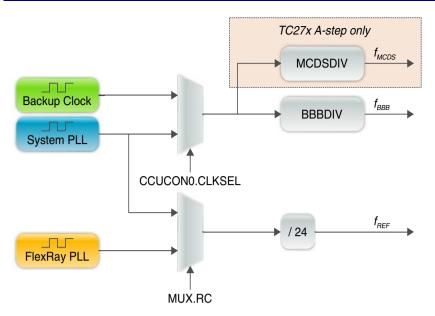

| MCDS Clock System                               |  |

| MCDS Sampling                                   |  |

| MCDS Timestamps                                 |  |

| Clock Counters                                  |  |

| Timestamp Configuration                         |  |

| Timestamp Decoding                              |  |

| Periodic Trigger                                |  |

| MCDS Clock Configuration                        |  |

| Automatic Configuration with the CLOCK Commands |  |

| Manual Configuration                            |  |

| Deprecated Configuration                        |  |

| Emulation Memory                                |  |

| Background Information                          |  |

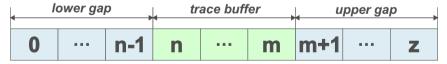

| EMEM Partitioning                               |  |

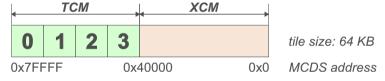

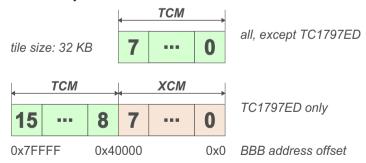

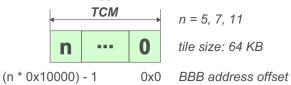

| Memory Arrays and Tiles                         |  |

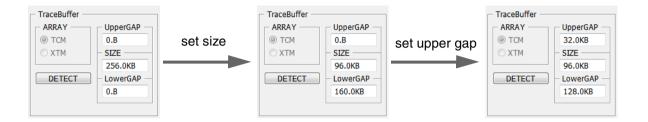

| Trace Buffer Configuration                      |  |

| GUI Integration                                 |  |

| PRACTICE Functions                              |  |

| Co-operation with Third-party Usage             |  |

| Configuration Example                           |  |

| Device Specific Details                         |  |

| TriCore AUDO-NG                                 |  |

| TriCore AUDO-F                                  |  |

| TriCore AUDO-S and AUDO-MAX                     |  |

| TriCore AURIX                                   |  |

| AGBT High-speed Serial Trace                    |  |

| Background Information                          |  |

| Xilinx Aurora                                   |  |

| Requirements                                    |  |

| TriCore Chip Requirements                       |  |

| Target Board Requirements                                     | 91  |

|---------------------------------------------------------------|-----|

| TRACE32 Requirements                                          | 92  |

| AGBT Configuration                                            | 93  |

| Trace Streaming                                               | 94  |

| Limitations and Restrictions                                  | 95  |

| Advanced Emulation Device Access                              | 96  |

| EEC Access                                                    | 96  |

| EEC EMEM Access                                               | 97  |

| EEC Register Access                                           | 97  |

| Impact of Direct EEC Access                                   | 98  |

| Guarded MCDS Programming                                      | 98  |

| Timestamp Usage                                               | 99  |

| Trigger Program Example                                       | 99  |

| Example Scripts                                               | 101 |

| Known Issues and Application Hints                            | 102 |

| Missing Instructions                                          | 102 |

| Invalid Program Trace at the Beginning of the Trace Recording | 102 |

| No Trace Content Displayed                                    | 102 |

| FIFOFULL error                                                | 103 |

| Concurrent Usage of OCDS-L2 Off-chip Trace and On-chip Trace  | 103 |

| PCP Channel ID                                                | 104 |

| Workaround for the TASKING PCP C/C++ Compiler                 | 104 |

| Glossary                                                      | 105 |

| Infineon Glossary                                             | 105 |

| Lauterbach Glossary                                           | 106 |

# **MCDS User's Guide**

## Version 06-Nov-2015

| 08-Sep-14 | New manual.                                                                                                                                                                                                                                                                                         |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09-Jul-15 | Added chapter MCDS Special Features: Moved BMC here. Added description of Trace Through Reset and Power Cycle. Added description of peripheral trace, including DMA and GTM. Added chapter on miniMCDS. Added many screenshots to other sections. Reworked and updated chapter AGBT Off-chip Trace. |

| 26-Aug-15 | Reworked and updated chapter Clock System                                                                                                                                                                                                                                                           |

## Introduction

The MCDS (Multi-Core Debug Solution) is an on-chip trigger and trace solution from Infineon, available for the Infineon TriCore and C166/ XC2000 devices. It is used during the development stage of an embedded system for debugging, tracing, profiling, and verification.

Using TRACE32, the user can set up the MCDS for performing on- and off-chip trace. Based on the generated trace recording, the user can analyze, profile, and verify the behavior of his application. Additionally, it is possible to program triggers for stopping program execution, redirecting them to device pins or to influence the trace recording, e.g. for recording only the trace data of interest.

The on-chip memory used for storing the trace data can also be used for calibration, a technique that allows the dynamic overlay of code and data memory with alternate code or parameters. Calibration is not supported by Lauterbach tools. TRACE32 can be configured to cooperate with third-party tools to share resources, e.g. the on-chip memory.

For using these features, a special version of the chip is required, the Emulation Device. But also some of the Product Devices include the MCDS or at least a reduced variant of the MCDS, the so-called Mini-MCDS. For related information, refer to the documentation of your device.

This MCDS User's Guide is intended to guide the TRACE32 user through the configuration of the on-chip trace, trigger and filter setup. Additionally it provides background knowledge. This User's Guide is not intended to replace the available training manuals or the TRACE32 command references.

### **Intended Audience**

The reader of this document is assumed to have basic knowledge in using TRACE32 and has gathered experience using it. Additionally specific knowledge of the architecture and the device is mandatory, see the Infineon documentation. The MCDS User's Guide is not a replacement for the Infineon documentation of the Emulation Devices.

## How to read this Document

It is recommended to completely read the chapters **Background Information** and **MCDS Basic Features** before reading the other ones. Developers responsible for the PLL setup are expected to read the **EEC Cock System** chapter to understand why the application should program the EEC clocks.

It is not necessary to read this documentation completely for using the MCDS. This User's Guide is separated into independent chapters handling different topics. These chapters can be read independently and in arbitrary order. Reading the first paragraph of a chapter gives the reader all the information to decide whether it is important for his use case or not.

Some of the TRACE32 features require a deeper understanding of the MCDS and the Emulation Device implementation. The related parts and chapters of this User's Guide are indicated to be for MCDS Expert Users only.

The MCDS on TriCore chips does not only support the TriCore cores, it also supports the PCP and the GTM. When referring to TriCore in general, the entire TriCore device is addressed. This includes the TriCore cores as well as the PCP or GTM cores.

From the user's point of view the MCDS implementation for C166 and XC2000 devices is identical. Within this document there is no differentiation between C166 and XC2000.

#### **Related Documents**

Before using the MCDS it is mandatory to know the architecture under debug. The most important information about the device can be found in the Infineon Documentation:

- User's Manual and/or Target Specification

- Emulation Device Target Specification (for MCDS Expert Users)

- Data-, Delta- and Errata Sheets

Please contact Infineon for this documentation.

This document assumes that the reader already knows how to use the TRACE32 debugger for the corresponding device. The related information can be found in the Processor Architecture Manuals:

- "TriCore Debugger and Trace" (debugger\_tricore.pdf)

- "PCP Debugger Reference" (debugger\_pcp.pdf)

- "GTM Debugger and Trace" (debugger gtm.pdf)

- "XC2000/XC16x/C166CBC Debugger" (debugger\_166cbc.pdf)

For TriCore AURIX there is a trace training manual:

"AURIX Trace Training" (training aurix trace.pdf)

Detailed information about the commands can be found in the General Commands Reference Guides. For information about the MCDS commands, refer to the MCDS command group:

"General Commands Reference Guide M" (general\_ref\_m.pdf)

## **Background Information**

This chapter gives an overview of the related terms and definitions. To provide the necessary background information it explains the Emulation Device concept and introduces the MCDS and its components.

It is highly recommended that every MCDS user reads this chapter prior to any other.

The **Glossary** at the end of this User's Guide provides a description of the most important terms and abbreviations.

### **Trace Source**

A trace source is a chip component that generates one or more types of trace data. For example, a core provides information about the executed instructions (*program trace*) or data accesses (*data trace*). A bus provides information about the bus transactions (*data trace*). Other information may be the ownership, a channel ID or status information.

Each trace type within a trace source can be enabled separately. So it is possible to record only the data accesses to a variable without the corresponding program flow.

### **Program Trace**

Program trace can be recorded using different strategies, depending on the use case:

Flow Trace

A flow trace records the entire program flow, including all instructions. A trace message is only generated in case the sequential execution of instructions is broken, e.g. in case of a jump or branch instruction, a call or return or an exception. This reduces trace buffer consumption.

Sync Trace

A sync trace generates a trace message on every MCDS clock cycle. Depending on  $f_{CPU}$ :  $f_{MCDS}$  and the architecture (super-scalar or not) not all instructions will generate a dedicated trace message. This consumes much more trace buffer, but higher accuracy is achieved for timestamps and event assignment.

Compact Function Trace (CFT)

The Compact Function Trace only generates trace messages on call and return instructions. All intermediate jump instructions are omitted. In case the compiler uses regular jump instructions for function entry and exit (jump-linked functions) these function calls and exits are also not recorded. Additionally very small functions can be omitted from recording.

As timestamp information is only generated for a trace message, not all instructions have their own timestamp information. The most accurate timing information is possible for the sync trace.

The trace data generated by the trace sources are recorded by a trace sink. Depending on where this information is stored, the technology for recording the data is called on-chip trace or off-chip trace.

Off-chip Trace

Microcontroller chips implementing an off-chip trace provide the trace data continuously via port pins. An external tool, e.g. the PowerTrace II, constantly records this information in a huge trace memory where it can be accessed for display and analysis purposes.

The off-chip trace is controlled using the **Analyzer** command group.

On-chip Trace

Microcontroller devices implementing an on-chip trace store the trace data in a memory located on the SoC instead of transferring it directly to an external tool. The trace buffer is later read by the tool. An on-chip trace buffer is usually much smaller than the trace buffer of an off-chip trace solution. A common size is 4 KB, TriCore devices have up to 1 MB of on-chip trace buffer.

The on-chip trace is controlled using the **Onchip** command group.

The other trace sinks supported by TRACE32 are not related to MCDS. For more information refer to <a href="http://www.lauterbach.com/tracesinks.html">http://www.lauterbach.com/tracesinks.html</a> and the Trace. METHOD command.

The **Trace**. **METHOD** command allows to use the **Trace** commands as an alias either for **Analyzer** or **Onchip**. For MCDS the default trace method is **Analyzer**. If this is not available the default is **Onchip**.

## **Trace Filter and Trigger**

While off-chip traces usually have enough memory for a long time recording, on-chip traces do not. Consequently for on-chip traces, it is important to limit the recording to the information of interest. This can be achieved by programming triggers and filters.

• A *trace trigger* is an event that results in a termination of the trace recording. The termination can optionally be delayed.

For example, a trace trigger can be configured on an error condition to make sure that information is recorded on how this error occurred. The optional delay between the event ant the termination can be used to record how the application reacted on the error event.

A trace filter only generates trace data for defined events.

Defining trace filters reduces the trace buffer consumption.

The configuration of a trace filter or trigger has an impact on the recorded data:

- In case no trace filter is programmed (unconditional trace) all enabled trace sources will generate trace data.

- In case at least one trace filter is programmed *(conditional trace)*, all enabled trace sources will generate trace data as long as the condition for the trace recording is true.

For cost and power saving reasons, the trace and trigger features are only implemented in special SoC versions, the Emulation Devices. The normal Product Devices for the mass-market do not contain them.

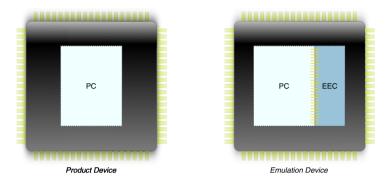

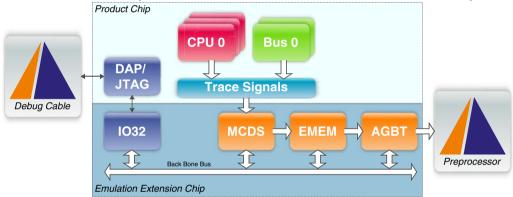

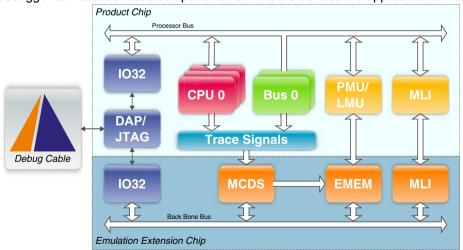

- The *Product Device (PD)* is for the mass production but also for development. It consists of a single die, the *Product Chip (PC)*, including all application and debug functionality.

- The *Emulation Device (ED)* is for development and field tests. It contains two dies, the unmodified *Product Chip (PC)* and the *Emulation Extension Chip (EEC)* offering the additional trace, trigger, and calibration features. Both dies are connected by bond wires.

The packages of Product and Emulation Devices almost have the same pinout. A single debug port is used to access the PC and the EEC.

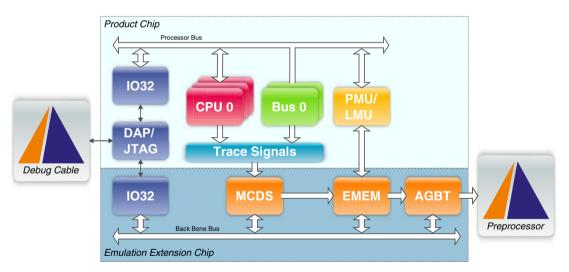

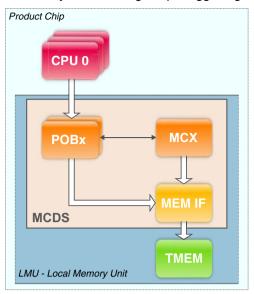

The EEC consists of the following main components:

MCDS (Multi-core Debug Solution) for trace, trigger and filter

The MCDS is the basic module of the EEC, it collects status information from the various chip components. Based on the status information, the MCDS generates debug events and trace data.

For an overview, see chapter MCDS Concept.

EMEM (Emulation Memory) for trace data storage and calibration

The Emulation Memory is a dual-ported memory used for storing the generated on- and off-chip trace data as well as calibration information. On some devices, the EMEM can be used as additional application RAM via the LMU.

The EMEM is discussed in chapter **Emulation Memory**.

#### AGBT (Aurora GigaBit Trace) for serial high-speed off-chip trace

The Aurora GigaBit Trace module uses the Aurora serial protocol to transfer the generated trace data to the TRACE32 preprocessor. AGBT uses a part of the EMEM as FIFO.

The AGBT off-chip trace is discussed in chapter AGBT High-speed Serial Trace.

#### BBB (Back Bone Bus) for connecting the EEC modules

The BBB is an FPI bus independent from the Product Chip for connecting all EEC components, memories, and registers. It can be accessed by the debugger via the debug port.

On TriCore the application can also access the BBB using the MLI bridge (TriCore AUDO) or the LMU (TriCore AURIX). On XC2000 Emulation Devices the application cannot access the EEC components.

#### Cerberus IO Client (IO32)

The Cerberus IO Client (IO32) on the EEC enables the TRACE32 debugger to configure the Emulation Device and to read out the EMEM via the debug port of the Product Device.

### Other peripherals

Depending on the device, the EEC may provide additional peripheral components. They are mainly used for a specific purpose only, e.g. USB over Emulation Device or the Camera Interface (CIF), and are not covered by this document.

Older TriCore devices up to AUDO-NG feature an OCDS-L2 off-chip trace port (parallel trace) to provide information about the program flow via a dedicated protocol. This obsolete trace protocol was part of the Product Chip and is not related to the Emulation Device or MCDS.

## **TRACE32 Support for Emulation Devices**

This chapter describes how TRACE32 supports the various Emulation Device features, the required licenses, and the physical device connection. All MCDS users are advised to read this chapter.

The MCDS command group is used for configuring the MCDS, the AGBT, and the Emulation Memory.

### **Feature Overview**

When trace is available, TRACE32 provides an out-of-the box trace configuration: the program flow trace for the first core of the architecture is selected by default. As soon as program execution starts, recording is started, too.

**NOTE:** The MCDS of TriCore devices is restricted to generate trace and trigger information only for up to two cores, even if the devices have more cores.

If the device supports off-chip trace and a suitable trace preprocessor is connected, off-chip trace is used is used automatically (**Trace.METHOD Analyzer**). Otherwise on-chip trace is configured automatically (**Trace.METHOD Onchip**).

The most important and most frequently-used features can easily be selected and configured with the following commands:

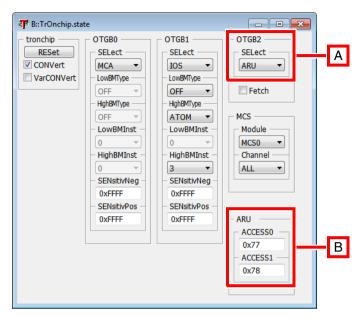

| MCDS.state | Opens the <b>MCDS.state</b> window, where you can quickly enable and disable the different trace sources.                                                                 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Break.Set  | Allows you to easily configure commonly used trace triggers and filters, including OS-aware tracing (option /TraceData).                                                  |

| CTS        | CTS (Context Tracking System) allows debugging an application based on its program trace recording.                                                                       |

| ВМС        | <b>Benchmark Counters</b> are used to count important events, e.g. cache hits and misses, the number of calls to a function or exceptions.                                |

| OCTL       | Specific trigger and filter setups can be programmed using OCTL. MCDS Expert users can get low level access to the MCDS as explained in chapter Guarded MCDS Programming. |

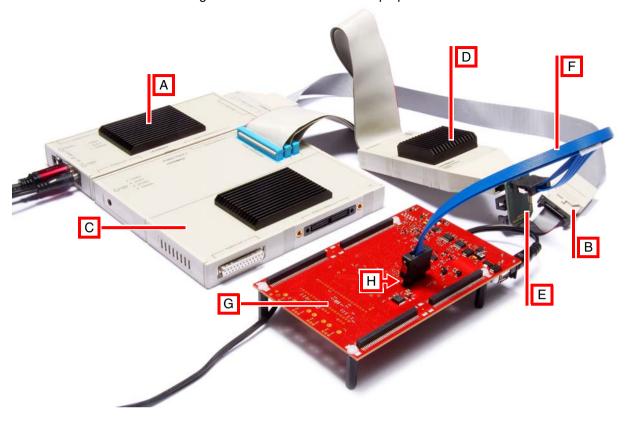

## **Target Interface**

No extra debug port is required for accessing and configuring the EEC. Only one debug cable is required for debug and on-chip trace.

The debug port connector, the debug cables and available adapters and converters are described in the following application notes:

- "Application Note Debug Cable TriCore" (tricore\_app\_ocds.pdf)

- "Application Note Debug Cable C166" (c166 app ocds.pdf)

For the AGBT off-chip trace, the 22-pin ERF-8 trace connector is required. The trace connector also includes the debug signals, so the debug cable and the trace preprocessor can be connected to the target via one connector. For the pinout and the signals, refer to:

- http://www.lauterbach.com/ad3829.html

- "ERF8 22-pin Power.org Connector" (debugger\_tricore.pdf)

- Infineon Application Note AP32186 "Aurora Connector & Cable"

Lauterbach uses the Infineon TriBoards for development and verification. Their documentation contains schematics and additional information about the debug and trace interfaces. Lauterbach recommends that you use this information as reference for proprietary hardware.

In addition to the break pins at the debug port, most TriCore Emulation Devices have further package pins to provide an external trigger signal. These pins are often also available via the GPIO ports. For more information, see the Infineon User's Manual and Data Sheet of your device.

## **MCDS Licensing**

The use of the MCDS trigger features and the EEC access is covered by the architecture's debug license.

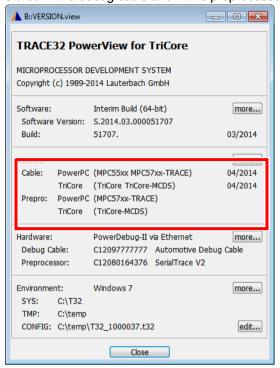

Decoding the MCDS trace data requires an extra license:

- TriCore-MCDS for TriCore, including PCP and GTM.

- C166-MCDS for XC2000ED and C166.

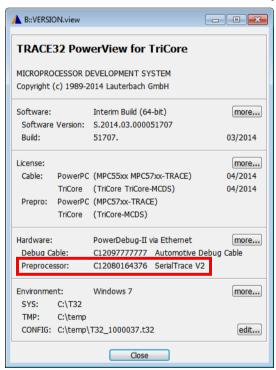

The trace license is either stored in the debug cable or in the trace preprocessor and can be used for on- and off-chip trace. For example, the **TriCore-MCDS** license stored in the preprocessor connected to the trace module can be used for TriCore MCDS on-chip trace.

### NOTE:

- The Serial Trace preprocessor is architecture independent. In case originally purchased for PowerPC or ARM it does not contain an MCDS license.

- The obsolete OCDS-L2 preprocessor (parallel trace) is not recognized as an MCDS trace license as the trace protocols are completely different.

The licenses available for your current setup are displayed in the **VERSION.view** window. A more detailed list is displayed in the **LICENSE.List** window. The example below shows that the TriCore-MCDS license is stored in the debug cable and in the preprocessor.

**NOTE:** For order information and prices, please contact your local **Lauterbach**

representative.

### **MCDS Basic Features**

This chapter introduces the basic features of the TRACE32 support for MCDS, especially the trigger and filter configuration via the **Break.Set** command. All MCDS users using trace and trigger are strongly advised to read this chapter.

## **MCDS Concept**

The MCDS is the main module of the EEC, it collects status information of the various chip components. Based on the collected status information, the MCDS generates debug and trace events as well as trace data. Understanding the MCDS concept helps understanding its behavior.

The MCDS consists of one or more independent *Observation Blocks* receiving status and run-time information from a core or bus. This information can be written to the trace buffer or used to generate debug and trace signals:

- Debug signals are used to generate signals to the SoC, e.g. to stop a core or to toggle a pin.

- Trace signals together with optional trace filters are used to enable or disable trace data generation, to generate a watchpoint message, or to count events.

- For information about watchpoint messages, see chapter Watchpoints.

- For information about event counters, see chapter Benchmark Counters.

The basic MCDS setup is identical for on- and off-chip trace.

#### MCDS of XC2000ED and C166

XC2000 and C166 Emulation Devices only have one observation block. Only the core can be observed.

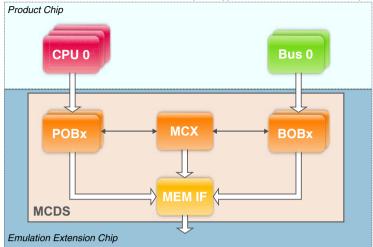

TriCore has up to two *Processor Observation Blocks (POB)* to observe the cores (TriCore, PCP and GTM) and two *Bus Observation Blocks (BOB)*) to observe the buses (LMB, SRI, SPB or RPB).

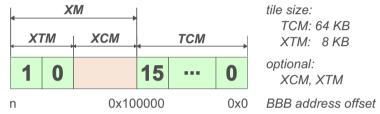

The trace data generated by the Observation Blocks is forwarded to the *Memory Interface (MEM IF)* where all messages are sorted according their temporal order and then written to the Emulation Memory.

The POBs observe the program execution as well as the data accesses of the core (program- and data trace). The BOBs observe the data transactions on the buses (data trace), also containing meta information about the transaction, e.g. bus master, channel and priority.

NOTE:

Restrictions for TriCore AUDO-NG:

LMB cannot be traced.

Restrictions for TriCore AURIX:

- Only two out of four cores can be selected for trace and trigger.

- HSM cannot be traced, all related bus traffic is removed on SoC level.

- SCR cannot be traced, all related bus accesses available.

The *Multi-core Cross-connect (MCX)* does not observe anything. It is used for generating the timestamp messages and contains counters.

- The counters can be used to count internal evens (see chapter Benchmark Counters).

Alternatively counters can be used to implement state machines. This allows to implement trace filters, e.g. record all bus transactions while a specific function is active.

- MCDS does not attach timestamp information to each trace message. Instead, the timestamps

are dedicated messages. So several messages generated at the same time share one

timestamp message to reduce trace buffer consumption.

- Timestamps can be enabled continuously or on demand to tag dedicated events only. The Observation Blocks can signal the MCX to generate a timestamp in case an event happened.

NOTE:

For TriCore AUDO this signal from the Observation Block to the MCX is delayed, so the timestamp messages are generated asynchronously, resulting in incorrect timestamp information. To avoid this, TRACE32 only allows continuous timestamp generation for TriCore AUDO. For TriCore AURIX this issue is fixed. See chapter No Trace Content Displayed for more information.

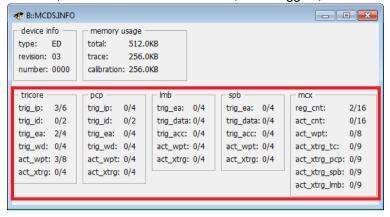

## **MCDS Configuration**

The **MCDS** command group is used to configure the MCDS. For a complete description of all MCDS commands, see chapter "MCDS" in General Commands Reference Guide M, page 57 (general\_ref\_m.pdf).

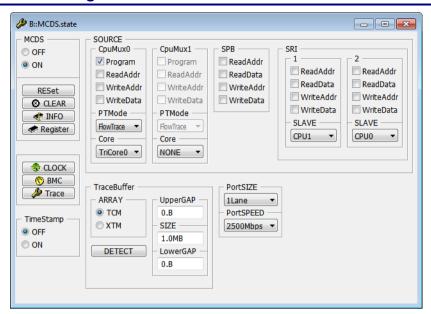

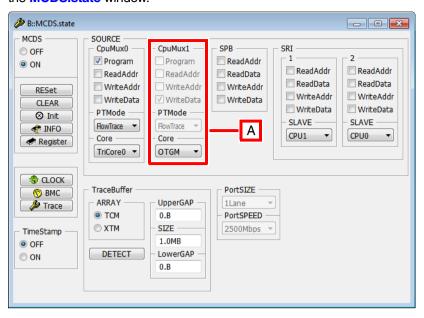

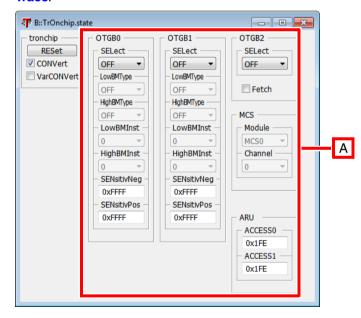

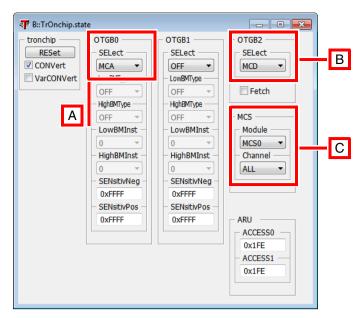

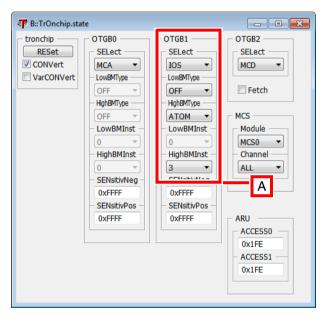

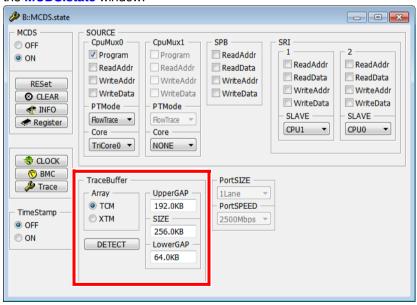

The MCDS.state window shows the most important configuration options available for the selected device. The following sections give an overview and introduction only, please refer to the corresponding chapters of this User's Guide to get more information.

#### General MCDS configuration:

The TRACE32 MCDS implementation has two states: ON and OFF.

The default is MCDS.ON. It is required for tracing and programming any triggers and filters. If switched off (MCDS.OFF), TRACE32 does not access any MCDS register. This can be used to avoid interference with third-party tools or applications.

- MCDS.RESet resets all MCDS configuration to the default.

- MCDS.CLEAR deletes all configuration made by the MCDS.Set command group. See chapter Guarded MCDS Programming for details.

- MCDS.INFO provides information about the availability of hardware resources.

- MCDS.Register opens a peripheral access to all MCDS registers.

#### Buttons as shortcuts to MCDS related features:

- CLOCK: SoC clock configuration, required for using timestamps.

- BMC: Count MCDS generated events using the Benchmark Counters.

- Trace: Configure the currently selected Trace method.

## **Timestamp Setup**

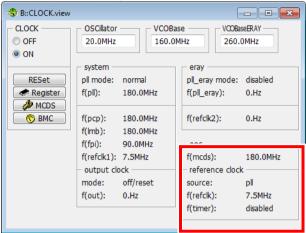

Enabling and using the MCDS-generated on-chip timestamps requires two steps:

- Enable the MCDS timestamp generation: MCDS.TimeStamp ON.

- Use the CLOCK commands to inform TRACE32 about the chip's base clocks. CLOCK.ON tells TRACE32 to use these clocks for calculating the timestamps.

#### Example:

```

SYStem.CPU TC275TE

CLOCK.OSCillator 20.0MHz ; frequency of on-board oscillator

SYStem.Mode Up

Data.LOAD.Elf myapplication.elf /NoCODE

Go PLL_ConfigDone

CLOCK.view ; manually verify clock setup

MCDS.TimeStamp ON ; enable timestamp generation

```

**NOTE:** A correct programming of the on-chip clocks is mandatory for a correct operation of

the MCDS hardware and timestamp generation. See chapter **EEC Clock System**

for details.

Timestamp decoding requires the entire trace buffer to be processed. For huge trace buffers, e.g. off-chip trace, this may take up to several minutes.

## **Trace Buffer Configuration**

TRACE32 can be configured to share the EMEM with third-party tools or applications using the MCDS.TraceBuffer commands. See chapter Emulation Memory for details.

As long as no sharing of the EMEM is required TRACE32 automatically chooses the most suitable EMEM configuration.

NOTE: XC2000 Emulation Devices do not allow configuring the EMEM.

## **AGBT Off-chip Trace Configuration**

The commands MCDS.PortSIZE and MCDS.PortSPEED are used to configure the *Aurora GigaBit Trace* (*AGBT*). See chapter AGBT High-speed Serial Trace for more information.

#### Trace Sources

Selecting a trace source enables the generation of the corresponding trace data. On TriCore, the trace sources of the different cores and buses can be enabled independently. On XC2000 only the core can be traced.

For the program trace different variants exist: program trace, sync trace, and CFT. For details please refer to chapter **Trace Sources**.

TriCore AURIX is limited to tracing only two cores at the same time. Multiplexers are implemented to select the cores to be traced. Use the command MCDS.SOURCE.Set CpuMux[0 | 1].Core to configure them.

The TriCore SRI is not a bus, it is a fabric that can perform more than one transaction per clock cycle. The MCDS hardware is limited to tracing only two transactions in parallel. The command MCDS.SOURCE.Set SRI.[1 | 2].SLAVE is used to select the corresponding bus slave. All transactions to selected slaves are recorded. The masters that initiated these transactions are available from the recorded trace data.

The GTM peripheral module is implemented as a peripheral trace. So in addition to the executed instructions and data accesses internal signals can be recorded, too. These signals can be displayed as a timing diagram, implementing the feature of an on-chip logic analyzer. See "GTM Debugger and Trace" (debugger\_gtm.pdf) and the TriCore-related GTM demos in demo/gtm/hardware/ for more information.

**NOTE:** OCTL and MCDS.Set have their own methods for selecting the trace sources.

#### **Example: Core Trace on TriCore AURIX**

1. On TriCore TC277TE, the program flow of core 0 and core 1 are to be traced. Additionally all read accesses of core 0 and all write accesses of core 1 are to be recorded:

```

MCDS.SOURCE.RESet

; configure trace for core 0

MCDS.SOURCE.CpuMux0.Core TriCore0

MCDS.SOURCE.CpuMux0.Program ON

MCDS.SOURCE.CpuMux0.PTMode FlowTrace

MCDS.SOURCE.CpuMux0.ReadAddr ON

; read data trace not implemented by MCDS

; configure trace for core 1

MCDS.SOURCE.CpuMux1.Core TriCore1

MCDS.SOURCE.CpuMux1.Program ON

MCDS.SOURCE.CpuMux1.PTMode FlowTrace

MCDS.SOURCE.CpuMux1.WriteAddr ON

MCDS.SOURCE.CpuMux1.WriteData ON

```

On TriCore TC277TE, the program flow of core 1 and the performed read and write accesses are to be traced. The sync trace is to be used to show the correct temporal order of the executed instructions and performed accesses:

```

MCDS.SOURCE.RESet

; configure trace for core 0

MCDS.SOURCE.CpuMux0.Core TriCore1

MCDS.SOURCE.CpuMux0.Program ON

MCDS.SOURCE.CpuMux0.PTMode SyncTrace

MCDS.SOURCE.CpuMux0.ReadAddr ON

MCDS.SOURCE.CpuMux0.WriteAddr ON

MCDS.SOURCE.CpuMux0.WriteData ON

```

On TriCore TC1798ED, all read accesses to PMU0 (internal Flash) and all write accesses to the EBU area to be traced:

```

MCDS.SOURCE.RESet

MCDS.SOURCE.NONE; disable all trace sources

; trace all read accesses to PMU0

MCDS.SOURCE.SRI.1.SLAVE PMU0

MCDS.SOURCE.SRI.1.ReadAddr ON

MCDS.SOURCE.SRI.1.ReadData ON

; trace all write accesses to the EBU

MCDS.SOURCE.SRI.2.SLAVE EBU

MCDS.SOURCE.SRI.2.WriteAddr ON

MCDS.SOURCE.SRI.2.WriteData ON

```

2. On TriCore TC1798ED, all accessed peripherals are to be traced:

```

MCDS.SOURCE.RESet

MCDS.SOURCE.NONE; disable all trace sources

; trace all accessed peripherals

MCDS.SOURCE.SPB.ReadAddr ON

MCDS.SOURCE.SPB.WriteAddr ON

```

TRACE32 provides two different methods for controlling the MCDS trace:

- The Analyzer commands are used to control the off-chip trace [A].

- The Onchip commands are used to control the on-chip trace [B].

MCDS allows only one of these trace methods to be active at the same time. Unless stated otherwise the commands described here can be applied to **Analyzer** as well as to **Onchip**.

#### In this chapter:

- Trace state and mode

- Trace buffer size and usage

- TraceTrigger configuration

Here, only the most important commands are described. For more information about these commands as well as those not mentioned here, please refer to the command group **Trace**.

#### **Trace States**

The **DISable** state prevents tracing at all. The EMEM is not configured so it can be used exclusively for another purpose, e.g. calibration. Refer to chapter **Emulation Memory** for more information. Using the MCDS for triggering is possible in this state, any trace data generated by the chip will be ignored.

The default trace state is **OFF**, which means that TRACE32 configures the necessary parts of the EMEM for tracing. Note that in the **OFF** state no trace data is recorded.

The EMEM is ready to capture trace data in the **Arm** state. Any generated trace data will be recorded.

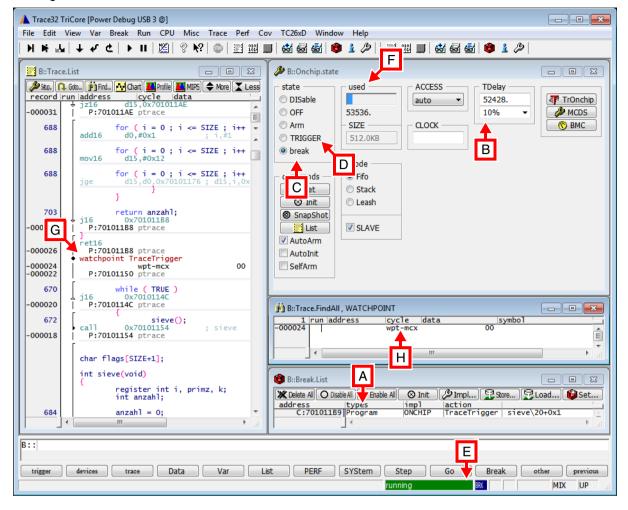

The **TRIGGER** and **break** states are related to the **TraceTrigger** option. TRIGGER means that the configured event has occurred but the trace is still recording (transition from Arm to TRIGGER). When recording has stopped, the trace switches to the break state to indicate that recording has stopped due to the occurrence of the configured trigger. The delay between TRIGGER and break can be configured with **Trace.TDelay**.

NOTE: Trace.TDelay is only available for Onchip.

### Trace Buffer Size and Usage

The **SIZE** box shows how many bytes of the trace memory are used as trace buffer:

Trace method Analyzer

Trace buffer size of the Power Trace module.

Trace method Onchip

Size of the EMEM used for tracing. Refer to chapter **Emulation Memory** for more information and for changing the EMEM usage for trace and calibration.

The progress bar under **used** indicates the fill state of the trace buffer. The fill rate depends on the amount of generated trace data and the configured clocks.

The trace buffer will normally not be filled completely with trace data. The reason is that the decompression information is located at the beginning of a paragraph (usually 1 or 4 KB). Refer to chapter **EMEM Partitioning** for details on the trace buffer organization.

#### **Trace Modes**

The trace memory can be operated in different modes, see **Trace.Mode** for details.

- In *Fifo mode* the trace recording is endless. Use this mode when you are interested in the data up to the point where trace recording is stopped.

- In Stack mode recording is stopped when the trace buffer is full while program execution continues. This mode is useful when the information of interest is assumed close to the start of the recording and program execution must not be stopped.

- The Leash mode is similar to the Stack mode with the difference that program execution is stopped when the trace buffer is full. This mode can be used to generate a seamless trace by joining smaller trace recordings to a large one. For more information, see the Trace.JOINFILE command. Leash mode is not supported by all Emulation Devices.

## **Trace Trigger Configuration**

A TraceTrigger can be used to capture run-time information of what happened before and after an event. This means that program execution must not be stopped, instead trace recording continues for some time after the event. Using the **TraceTrigger** option in TRACE32 you can trigger on the event of interest, and with the **Trace.TDelay** feature you can define which amount of the trace buffer is reserved for the trace data generated after the event.

Programming the TraceTrigger event is performed via the TraceTrigger action of **Break.Set**, see chapter **Trace Trigger** for an example.

NOTE:

The TraceTrigger feature normally only makes sense in Fifo mode. It is not available in Stack mode, configuration is silently ignored.

### **Other Trace Configuration Commands**

- Trace.RESet resets all settings of the Trace command group to the defaults, the trace buffer is initialized. Only the selected trace method is reset.

- Trace.Init initializes the trace buffer by discarding all recorded data.

NOTE:

The on-chip trace buffer is always cleared when a new trace recording is started. It is not possible to attach a new recording to the previous one. Instead, save the recording to a file, and attach the recording to the contents of the file using **Trace.JOINFILE**.

- Trace.AutoArm will start and stop the trace recording simultaneously with the program

execution. Resuming program execution will automatically start trace recording (Arm state), a

break terminates trace recording (OFF state).

- Trace.AutoInit will initialize the trace buffer and discard all recorded data when resuming program execution.

## **Basic Trace Usage**

The default MCDS setup allows the user to perform unconditional tracing without additional configuration:

- The first core of the device is configured to generate trace data for the program flow. Data trace, bus trace and timestamps are disabled.

- Trace recording automatically starts when the core starts execution and stops when the core breaks. See command Trace.AutoArm for details.

- The EMEM is configured automatically depending on the device and the trace method. For onchip trace the maximum possible size is selected. Refer to chapter Emulation Memory if a different configuration is required.

- Endless recording is configured so the program flow up to the break can be inspected. For details, see command Trace.Mode Fifo.

For examples on the basic trace usage of TriCore AURIX devices, please refer to "AURIX Trace Training" (training\_aurix\_trace.pdf).

NOTE: Using OCTL and MCDS.Set disables unconditional tracing.

### Trigger and Filter via Break.Set command

TRACE32 uses the MCDS to implement the following features:

- Breakpoint: stop program execution (break).

- Trace Filter: conditionally generate trace messages.

- Trace Trigger: terminate the generation of trace messages with an optional delay.

- **Watchpoint**: make an internal event visible without affecting the real-time behavior, e.g. generate a special trace message or an external signal (pin event).

- **Marker**: use a certain event for a pre-defined, special action, e.g. for incrementing a counter. See chapter **Benchmark Counter** for more information.

These features are implemented as trigger and filter via the **Break.Set** command with the corresponding Break Action. The number of configurable Break Actions depends on the device and the MCDS resources already used by other MCDS features, e.g. the **Benchmark Counters** or **OCTL**.

MCDS triggers and filters via the **Break.Set** command only have an effect in case the related core either executes at the specified address (program breakpoint) or accesses the specified address (data address and/or data value breakpoint). It depends on the device and the core or bus which kind of data access can be triggered on.

The Break Actions define events which enable or disable the trace recording. The type of recorded information is defined with the **MCDS.SOURCE** command group.

#### **Available Break Actions:**

| stop         | Breakpoint                                                                                                                            |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Delta, Echo  | Marker                                                                                                                                |

| WATCH        | Watchpoint                                                                                                                            |

| TraceEnable  | Sample only the specified event.                                                                                                      |

| TraceData    | OS-aware trace: sample the complete program flow and the specified data event.                                                        |

| TraceON      | Switch the sampling to the trace buffer on after the specified event occurred.                                                        |

| TraceOFF     | Switch the sampling to the trace buffer off after the specified event occurred.                                                       |

| TraceTrigger | Terminate the sampling to the trace buffer at the specified event. A delay between the trigger event and the termination is possible. |

Break Action **TraceData** is required for performing an OS-aware trace: the entire program flow is recorded. Additionally all write accesses to the variable holding the task ID are traced. So all context switches can be reconstructed by the trace decoder and a OS-aware performance analysis is possible. Trace Data automatically enables the recording of the program flow and the data address and value.

On TriCore, PCP and GTM **TraceON** and **TraceOFF** will trigger with a delay of up to two core clock cycles (up to six core instructions).

### **MCDS Breakpoints**

MCDS can be programmed to stop the program execution if specified conditions become true (MCDS trigger). TRACE32 PowerView is using this MCDS capability to extend the breakpoint capabilities provided by the debug logic.

The MCDS resources can be used:

- To allow complex breakpoints that cannot be implemented by the debug logic.

- To allow complex breakpoints that are otherwise implemented as intrusive breakpoints.

- To extend the number of on-chip breakpoints.

MCDS-based breakpoints have the following disadvantages:

- Due to the complex logic of MCDS, the program execution is not stopped exactly at the breakpoint, but several cycles later (approximately 20 assembler instructions).

- It is possible to identify which MCDS breakpoint caused the MCDS trigger by inspecting the trace recording.

- If several MCDS breakpoints are set, it is not possible to indicate which MCDS breakpoint caused the program execution to stop.

- A Read breakpoint together with a data value cannot be implemented on some MCDS devices, especially not for the TriCore architecture (MCDS restriction). The following error message is displayed, if you try to set this type of breakpoint:

- data not allowed for this on-chip breakpoint.

If you want to use MCDS-based breakpoints, you have to enable the following MCDS resources:

| MCDS.Option ProgramBreak ON                       | Allow TRACE32 PowerView to use MCDS to set Program breakpoints.                                                                                                                                                             |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCDS.Option AddrBreak ON                          | Allow TRACE32 PowerView to use MCDS to set Read/Write/ReadWrite breakpoints.                                                                                                                                                |

| MCDS.Option AddrBreak ON MCDS.Option DataBreak ON | <b>TriCore:</b> Allow TRACE32 PowerView to use MCDS to set Write breakpoints when specified data values are written.                                                                                                        |

|                                                   | Others: Allow TRACE32 PowerView to use MCDS to set Read/Write/ReadWrite breakpoints when specified data values are written respectively to set Read breakpoints when specified data values are read. (if supported by MCDS) |

### **Complex Breakpoints**

TRACE32 PowerView allows to configure a breakpoint that stops the program execution if an instruction of a specified instruction range accesses a specified data range.

**Example 1 (single-core):** Stop the program execution if an instruction of the function sieve() writes 0x0 to the variable flags[3].

```

DO ~~\demo\tricore\hardware\triboard-tc2x5\tc275tf\tc275tf demo.cmm

; configure MCDS to generate trace information for the instruction

; execution sequence and all write accesses

MCDS.state

MCDS.SOURCE.Set CpuMux0.Program ON

MCDS.SOURCE.Set CpuMux0.WriteAddr ON

MCDS.SOURCE.Set CpuMux0.WriteData ON

; enable MCDS breakpoints on program addresses, data addresses

; and data values

MCDS.Option ProgramBreak ON

MCDS.Option AddrBreak ON

MCDS.Option DataBreak ON

Var.Break.Set sieve /VarWrite flags[3] /DATA.Byte 0x0

; start program execution and wait until it stops at the breakpoint

Go

WAIT !STATE.RUN()

; find the MCDS trigger event in the trace recording

Trace.Find Address Var.RANGE(flags[3]) Data.B 0x0 CYcle Write /Back

IF FOUND()

Trace.List TRACK.RECORD()

```

**Example 2 (single-core):** Stop the program execution if an instruction outside of the function func10() writes 0x0 to the variable flags[3].

```

DO ~~\demo\tricore\hardware\triboard-tc2x5\tc275tf\tc275tf demo.cmm

; configure MCDS to generate trace information for the instruction

; execution sequence and all write accesses

MCDS.state

MCDS.SOURCE.Set CpuMux0.Program ON

MCDS.SOURCE.Set CpuMux0.WriteAddr ON

MCDS.SOURCE.Set CpuMux0.WriteData ON

; enable MCDS breakpoints on program addresses, data addresses

; and data values

MCDS.Option ProgramBreak ON

MCDS.Option AddrBreak ON

MCDS.Option DataBreak ON

Var.Break.Set func10 /VarWrite flags[3] /DATA.Byte 0x0 /EXclude

; start program execution and wait until it stops at the breakpoint

WAIT !STATE.RUN()

; find the MCDS trigger event in the trace recording

Trace.Find Address Var.RANGE(flags[3]) Data.B 0x0 CYcle Write /Back

IF FOUND()

Trace.List TRACK.RECORD()

```

**Example 3 (SMP system consisting of three TriCore cores):** Stop the program execution if an instruction of the function sieve() writes 0x0 to the variable flags[3].

Please be aware that MCDS-based breakpoints can only be programmed to cores that are connected to the trace multiplexer.

```

DO ~~\demo\tricore\hardware\triboard-tc2x5\tc275tf\tc275tf_smp_demo_multisieve.cmm

; connect TriCore0 and TriCore1 to the trace multiplexer

; configure MCDS to generate trace information for the instruction

; execution sequence and all write accesses

MCDS.state

MCDS.SOURCE.Set CpuMux0.Core TriCore0

MCDS.SOURCE.Set CpuMux0.Program ON

MCDS.SOURCE.Set CpuMux0.WriteAddr ON

MCDS.SOURCE.Set CpuMux0.WriteData ON

MCDS.SOURCE.Set CpuMux1.Core TriCore1

MCDS.SOURCE.Set CpuMux1.Program ON

MCDS.SOURCE.Set CpuMux1.WriteAddr ON

MCDS.SOURCE.Set CpuMux1.WriteData ON

; enable MCDS breakpoints on program addresses, data addresses

: and data values

MCDS.Option ProgramBreak ON

MCDS.Option AddrBreak ON

MCDS.Option DataBreak ON

Var.Break.Set sieve /VarWrite flags[3] /DATA.Byte 0x0

; start program execution and wait until it stops at the breakpoint

Go

WAIT !STATE.RUN()

; Find the MCDS trigger event in the trace recording

Trace.Find Address Var.RANGE(flags[3]) Data.B 0x0 CYcle Write /Back

IF FOUND()

Trace.List TRACK.RECORD()

```

#### Real-time MCDS Breakpoints Instead of Intrusive Breakpoints

The debug-logic of the TriCore does not provide data value breakpoints. The following breakpoint is implemented as an **intrusive breakpoint** by default.

```

Var.Break.Set flags[12] /Write /DATA.Byte 0x0

```

The following commands allow TRACE32 PowerView to implement this type of breakpoint as a real-time MCDS breakpoint. Please be aware that this is only possible for Write breakpoints.

MCDS.Option AddrBreak ON MCDS.Option DataBreak ON

Allow TRACE32 PowerView to use MCDS to set Write breakpoints when specified data values are written. (TriCore)

```

DO ~~\demo\tricore\hardware\triboard-tc2x5\tc275tf\tc275tf demo.cmm

; configure MCDS to generate trace information for the instruction

; execution sequence and all write accesses

MCDS.state

MCDS.SOURCE.Set CpuMux0.Program ON

MCDS.SOURCE.Set CpuMux0.WriteAddr ON

MCDS.SOURCE.Set CpuMux0.WriteData ON

; enable MCDS breakpoints on data addresses and data values

; (write access only)

MCDS.Option AddrBreak ON

MCDS.Option DataBreak ON

Var.Break.Set flags[12] /Write /DATA.Byte 0x0

; start program execution and wait until it stops at the breakpoint

WAIT !STATE.RUN()

; find the MCDS trigger event in the trace recording

Trace.Find Address Var.RANGE(flags[12]) Data.B 0x0 CYcle Write /Back

IF FOUND()

Trace.List TRACK.RECORD()

```

**Example 2 (single-core):** Stop the program execution if a data value other than 0x0 is written as a byte to the variable flags[12].

```

DO ~~\demo\tricore\hardware\triboard-tc2x5\tc275tf\tc275tf_demo.cmm

; configure MCDS to generate trace information for the instruction

; execution sequence and all write accesses

MCDS.state

MCDS.SOURCE.Set CpuMux0.Program ON

MCDS.SOURCE.Set CpuMux0.WriteAddr ON

MCDS.SOURCE.Set CpuMux0.WriteData ON

; enable MCDS breakpoints on data addresses and data values

; (write access only)

MCDS.Option AddrBreak ON

MCDS.Option DataBreak ON

Var.Break.Set flags[12] /Write /DATA.Byte !0x0

; start program execution and wait until it stops at the breakpoint

Go

WAIT !STATE.RUN()

; find the MCDS trigger event is the trace recording

Trace.Find Address Var.RANGE(flags[12]) Data.B !0x0 CYcle Write /Back

IF FOUND()

Trace.List TRACK.RECORD()

```

**Example 3 (SMP system consisting of three TriCore cores):** Stop the program execution if 0x0 is written as a byte to the variable flags[12].

Please be aware that a MCDS trigger can only be activated by a core that is connected to the trace multiplexer.

```

DO ~~\demo\tricore\hardware\triboard-tc2x5\tc275tf\tc275tf_smp_demo_multisieve.cmm

; connect TriCoreO and TriCoreI to the trace multiplexer

; configure MCDS to generate trace information for the instruction

; execution sequence and all write accesses

MCDS.state

MCDS.SOURCE.Set CpuMux0.Core TriCore0

MCDS.SOURCE.Set CpuMux0.Program ON

MCDS.SOURCE.Set CpuMux0.WriteAddr ON

MCDS.SOURCE.Set CpuMux0.WriteData ON

MCDS.SOURCE.Set CpuMux1.Core TriCore1

MCDS.SOURCE.Set CpuMux1.Program ON

MCDS.SOURCE.Set CpuMux1.WriteAddr ON

MCDS.SOURCE.Set CpuMux1.WriteData ON

; enable MCDS breakpoints on data addresses and data values

; (write access only)

MCDS.Option AddrBreak ON

MCDS.Option DataBreak ON

Var.Break.Set flags[12] /Write /DATA.Byte 0x0

; start program execution and wait until it stops at the breakpoint

Go

WAIT !STATE.RUN()

; find the MCDS trigger event is the trace recording

Trace.Find Address Var.RANGE(flags[12]) Data.B 0x0 CYcle Write /Back

IF FOUND()

Trace.List TRACK.RECORD()

```

**Example 4 (SMP system consisting of three TriCore cores):** Stop the program execution if a data value between 0x10--0x20 is written as a long (32-bit) to the variable nAbsSmall.

Please be aware that a MCDS trigger can only be activated by a core that is connected to the trace multiplexer.

```

DO ~~\demo\tricore\hardware\triboard-tc2x5\tc275tf\tc275tf_smp_demo_waveform.cmm

; connect TriCore0 and TriCore1 to the trace multiplexer

; configure MCDS to generate trace information for the instruction

; execution sequence and all write accesses

MCDS.state

MCDS.SOURCE.Set CpuMux0.Core TriCore0

MCDS.SOURCE.Set CpuMux0.Program ON

MCDS.SOURCE.Set CpuMux0.WriteAddr ON

MCDS.SOURCE.Set CpuMux0.WriteData ON

MCDS.SOURCE.Set CpuMux1.Core TriCore1

MCDS.SOURCE.Set CpuMux1.Program O

MCDS.SOURCE.Set CpuMux1.WriteAddr ON

MCDS.SOURCE.Set CpuMux1.WriteData ON

; enable MCDS breakpoints on data addresses and data values

; (write access only)

MCDS.Option AddrBreak ON

MCDS.Option DataBreak ON

Var.Break.Set nAbsSmall /Write /DATA.Long 0x10..0x20

; find the MCDS trigger event is the trace recording

Trace.Find Address nAbsSmall Data.L 0x10--0x20 CYcle Write /Back

IF FOUND()

Trace.List TRACK.RECORD()

```

**Example 5 (SMP system consisting of three TriCore cores):** Stop the program execution if a data value between less than 0x10 or greater than 0x20 is written as a long (32-bit) to the variable nAbsSmall.

Please be aware that a MCDS trigger can only be activated by a core that is connected to the trace multiplexer.

```

DO ~~\demo\tricore\hardware\triboard-tc2x5\tc275tf\tc275tf_smp_demo_waveform.cmm

; connect TriCore0 and TriCore1 to the trace multiplexer

; configure MCDS to generate trace information for the instruction

; execution sequence and all write accesses

MCDS.state

MCDS.SOURCE.Set CpuMux0.Core TriCore0

MCDS.SOURCE.Set CpuMux0.Program ON

MCDS.SOURCE.Set CpuMux0.WriteAddr ON

MCDS.SOURCE.Set CpuMux0.WriteData ON

MCDS.SOURCE.Set CpuMux1.Core TriCore1

MCDS.SOURCE.Set CpuMux1.Program ON

MCDS.SOURCE.Set CpuMux1.WriteAddr ON

MCDS.SOURCE.Set CpuMux1.WriteData ON

; enable MCDS breakpoints on data addresses and data values

; (write access only)

MCDS.Option AddrBreak ON

MCDS.Option DataBreak ON

Var.Break.Set nAbsSmall /Write /DATA.Long !0x10..0x20

; find the MCDS trigger event is the trace recording

Trace.Find Address nAbsSmall Data.L 0x0--0x0f OR Data.L 0x21--0xfffffffff

CYcle Write /Back

IF FOUND()

Trace.List TRACK.RECORD()

```

#### More On-chip (MCDS) Breakpoints

The number of Onchip Breakpoints provided by the debug logic is limited.

For details refer to chapter "On-chip Breakpoints" in TriCore Debugger and Trace, page 21 (debugger\_tricore.pdf).

If more than the available number of Onchip breakpoints is set, the following error message is displayed: no on-chip breakpoint of this type possible.

The following commands can be used to extend the number of Onchip breakpoints:

| MCDS.Option ProgramBreak ON | Allow TRACE32 PowerView to use MCDS to set Program breakpoints.              |

|-----------------------------|------------------------------------------------------------------------------|

| MCDS.Option AddrBreak ON    | Allow TRACE32 PowerView to use MCDS to set Read/Write/ReadWrite breakpoints. |

TRACE32 PowerView applies the following rule: Onchip breakpoints are sorted by their addresses. Breakpoints are implemented by their sorting order. Lower address breakpoints are programmed via the debug logic. After all available resources are used, the higher address breakpoints are programmed into MCDS.

#### **Example:**

```

DO ~~\demo\tricore\hardware\triboard-tc2x5\tc275tf\tc275tf demo.cmm

MCDS.Option ProgramBreak ON

; OCDS breakpoints

Break.Set func1 / Program / Onchip ; func1 at address 0x70100A10

Break.Set func20 /Program /Onchip

; func20 at address 0x70100C86

Break.Set func26 /Program /Onchip

Break.Set func27 /Program /Onchip

; func26 at address 0x70100CA0

; func27 at address 0x70100CA8

Break.Set func2a /Program /Onchip

; func2a at address 0x70100CD4

Break.Set func47 / Program / Onchip

; func47 at address 0x70100D90

Break.Set func7 /Program /Onchip

Break.Set func9 /Program /Onchip

; func7 at address 0x70100E20

; func9 at address 0x701010CC

; MCDS breakpoint

Break.Set sieve /Program /Onchip

; sieve at address 0x701012E8

```

#### Trace Filter

When programming trace filters, remember to enable the trace data generation for the trace sources you are interested in. By default, only program trace for the first core is enabled. If you configure a trace filter on a variable, manually enabling WriteAddr and WriteData is required for recording the data accesses.

#### **Examples**

Enable the trace as long as code within an address range is executed

Trace sieve() function without recording sub-functions:

```

MCDS.SOURCE TriCore Program ON

Break.Set Var.RANGE(sieve) /Program /Onchip /TraceEnable

```

Trace function sieve() including all sub-functions and exceptions.

Configure a TraceON action on the first assembler instruction of function sieve() and a TraceOFF action on the last one:

```

MCDS.SOURCE TriCore Program ON

Break.Set sieve /Program /Onchip /TraceON

Break.Set Var.END(sieve) /Program /Onchip /TraceOFF

```

Delayed stop of the trace recording when a certain address is executed.

Reserve 10 % of the trace buffer for recording the program trace after function sieve() has been exited the first time. Stop trace recording, but continue program execution:

```

MCDS.SOURCE TriCore Program ON

Break.Set Var.END(sieve) /Program /Onchip /TraceTrigger

Onchip.TDelay 10%

```

After the function sieve() is exited for the first time not more than the defined 10 % of the trace buffer will be used for recording. There is no possibility to cancel or restart this process. See the **Onchip.TDelay** command for details.

**NOTE:** The AGBT off-chip trace does not support the Trace Trigger feature.

TraceTrigger only makes sense in Fifo mode:

- In Stack mode, the trace will stop recording only when the trace buffer is full for the first time. The Trace Trigger watchpoint is generated.

- In Leash mode recording is disabled in any case when the trace buffer is full for the first time. The Trace Trigger watchpoint is generated.

When programming Onchip.TDelay 0%, recording will be disabled, but the watchpoint message will be missing in the trace.

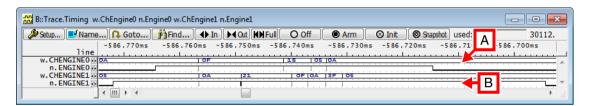

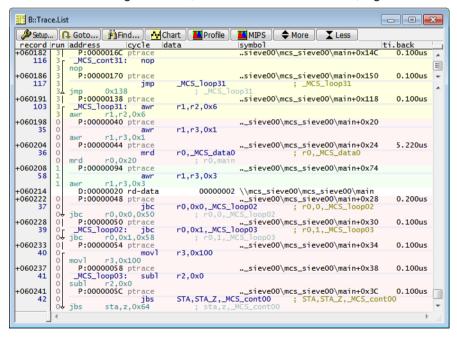

- A Breakpoint with action /TraceTrigger defines the trigger event.

- **B** TDelay defines to continue recording after the trigger has occurred, using 10% of the total trace buffer capacity for post-trigger recording.

- C TRIGGER state indicates that the trigger has occurred and post-trigger recording is in progress.

- D break state indicates that the trigger has occurred and post-trigger recording has completed.

- E Status bar indicates that CPU is still executing (running), but post-trigger recording has completed.

- F Size of data in trace buffer.

- **G** A watchpoint TraceTrigger in the **Trace.List** window indicates the occurrence of the trigger.

- **H** The watchpoint can be searched for using **Trace.Find** or **Trace.FindAll**. It is not possible to distinguish the TraceTrigger watchpoint from any other watchpoint. See chapter **Watchpoints** for details.

- Trace all write accesses to a certain data address.

All writes to the flags[3] variable are traced (data address and value):

```

MCDS.SOURCE.Set TriCore.Program OFF

MCDS.SOURCE.Set TriCore.WriteAddr ON

MCDS.SOURCE.Set TriCore.WriteData ON

Var.Break.Set flags[3] /Write /Onchip /TraceEnable

```

Trace all write accesses of a defined value to a data address.

Trace when 0x01 is written to the flags[3] variable. The code that triggered the access is also traced:

```

MCDS.SOURCE.Set TriCore Program ON ; enable Program Flow Trace

MCDS.SOURCE.Set TriCore.WriteAddr ON

MCDS.SOURCE.Set TriCore.WriteData ON

Var.Break.Set flags[3] /Write /Data.Byte 0x01 /Onchip /TraceEnable

```

Note that the exact opcode triggering the data access may not be included in the trace, but the recorded address specifies the location where to look for.

Trace all write accesses of a defined value to a data address triggered from a certain address range.

In case the CPU executes within the function sieve(), all occurrences are traced where 0x01 is written to the flags[3] variable. The code that triggered the access is also traced:

```

MCDS.SOURCE.Set TriCore.Program ON

MCDS.SOURCE.Set TriCore.WriteAddr ON

MCDS.SOURCE.Set TriCore.WriteData ON

Break.Set Var.RANGE(sieve) /MemoryWrite flags+0x0C \

/Data.Byte 0x01 /Onchip /TraceEnable

```

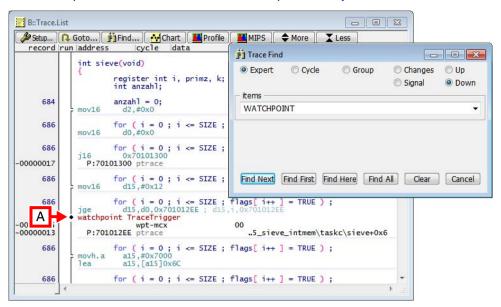

The TraceTrigger is marked in the trace as a special watchpoint [A] and can be searched in the trace listing like a watchpoint. For more information, see chapter **Watchpoints**.

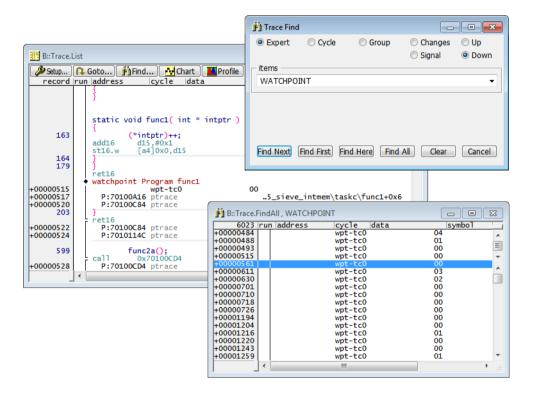

## **Watchpoints**

TRACE32 can be programmed to generate a signal or a trace message in case a certain event has occurred by using watchpoints. They are configured as breakpoints with break action WATCH.

Set a watchpoint on the entry of function sieve():

```

Break.Set sieve / Program / WATCH

```

The trace listing will show the name and the type of the watchpoint [A]:

```

B::Onchip.List DEFault

- - X

✓ Setup....

☐ Goto...

☐ Find...

☐ Chart

☐ Profile

☐ MIPS

☐ MIPS

☐ More

X Less

record | run | address | cycle | data

| symbol

busmaster

/* sieve of erathostenes */

=

register int i, primz, k;

int anzahl;

684

anzah1 = 0;

686

for ( i = 0 ; i <= SIZE ; flags[ i++ ] = TRUE ) ;

d2.#0x0</pre>

mov16

mov16 d2,#0x0

movh.a a15,#0xD000

lea a15,[a15]0x1268

mov16.aa a2,a15

for ( i = 0 ; i <= SIZE ; flags[ i++ ] = TRUE ) ;

d15,#0x1</pre>

686

lea a4,0x12

for ( i = 0 ; i \Leftarrow SIZE ; flags[ i \leftrightarrow j = TRUE ) ; st16.b [a2+],d15

686

686

for ( i = 0 ; i \leftarrow SIZE ; flags[ i++ ] = TRUE ) ; loop16 a4,0xD400082A

watchpoint Program sieve

wpt-tc0

00

```

NOTE:

The watchpoint message is independent of other messages, so it is not possible to assign it to a certain program flow or data message.

NOTE:

Watchpoints will not generate messages on successive occurrences of an event. The reason is that there must be an edge event (a transition from low to high).

This is especially important when triggering on an address- or data value, because the comparator will hold the last value until there is a new one. If the address or value does not change on consecutive accesses, the comparator value will not change and the watchpoint will miss the event.

Watchpoints can be searched, see chapter Searching the Trace.

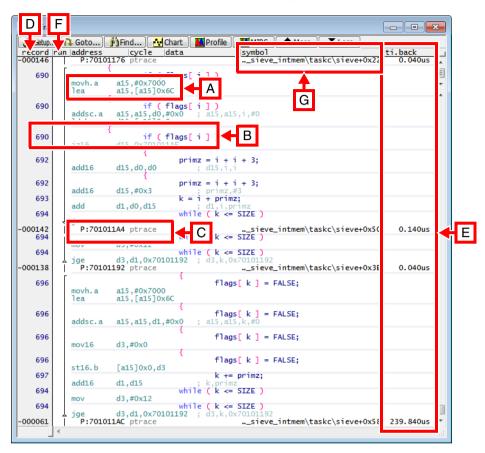

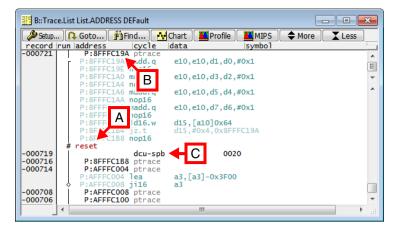

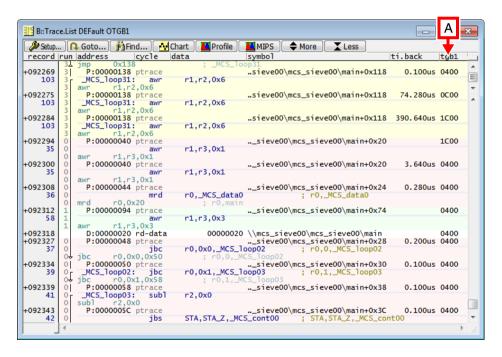

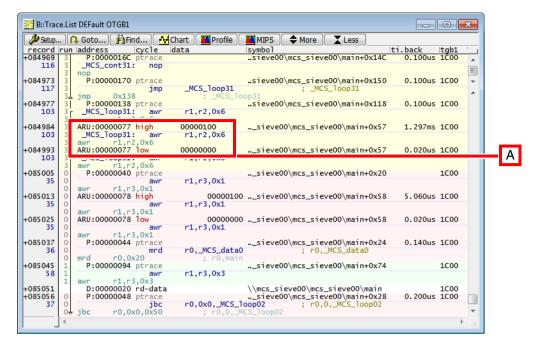

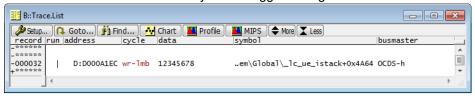

The recorded trace data can be displayed using the **Trace.List** command. TRACE32 reads the recorded trace data from the trace buffer and starts decoding the trace data. When decoding is completed, the results are shown in the **Trace.List** window as a continuous flow of the executed instructions.

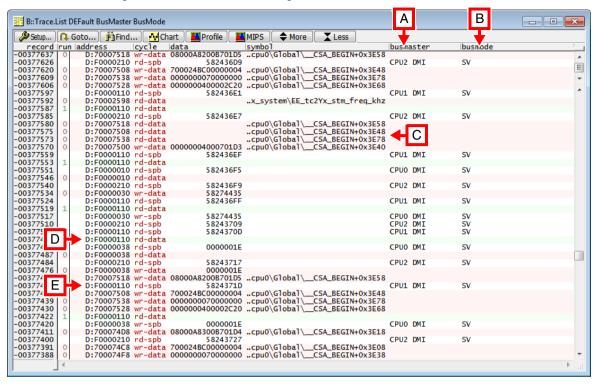

- A Executed assembler instructions.

- **B** Executed HLL instructions and line numbers.

- **C** Decoded trace information, e.g. reconstructed execution address and cycle type ptrace. The shown trace listing is based on a flow trace, so ptrace information is only generated in case of a discontinuity, e.g. branch, call, exception, ...

- **D** Record number. Negative numbers indicate cycles prior to the trace trigger, where the stop recording event occurred.

- **E** Optional timestamp information. Generated with every trace message. Tlme.Back indicates the time since the last trace message shown.

- F Run information. Indicates linearity, discontinuity and the case: branch, call, return, exception.

- **G** Symbol information related to the trace message's address.

#### NOTE:

- TRACE32 will not read the trace buffer and start decoding until requested by the user, e.g. by opening the Trace.List window.

- Only the trace buffer required for displaying the results will be read and decoded. When MCDS timestamps are enabled, the entire trace buffer is decoded.

Depending on the recorded data and the device, TRACE32 tries to improve the decoding results:

Data Cycle Assignment

In case of an unconditional program flow trace, the trace decoder tries to assign the recorded data accesses made by the core to their corresponding assembler instructions. Successfully assigned data cycles are displayed in black, otherwise in red.

NOTE:

Bus cycles cannot be assigned to instructions.

Data Cycle Reordering (TriCore only)

In some cases the recorded data cycles will not appear in the order they were executed on the device. If timestamps are available, the trace decoder is able to reconstruct the correct order. Data Cycle Reordering is mandatory for Data Cycle Assignment.

The content shown in the **Trace.List** window can be defined. Each kind of trace information is represented by a trace channel. Trace channels with related information are grouped, see the **Trace.List** command description for details.

When no trace channel is specified, the DEFault trace channel group is displayed. For MCDS the following trace channels are of interest:

BusMaster

Displays the originator (Bus Master) of a bus access. This information is only provided by MCDS if the bus address trace has been enabled.

BusMODE

Displays whether the bus was accessed in User or Supervisor mode. This information is only provided by MCDS if the bus address trace has been enabled. BusMaster and BusMODE information are displayed in light grey if the access was made in User mode, otherwise in dark grey.

TP

Displays the raw trace data. Only of interest for MCDS experts, e.g. for verifying the decoder.

MCDS

Displays the decoded message information, e.g. message source, trace type, and trace payload. This information is useful for MCDS expert users having access to the Infineon ED documentation. The message sources correspond to the MCDS unit names as defined by Infineon.

As mentioned above the MCDS trace messages also provide information about the bus master. To obtain this information, the generation of address messages has to be enabled for the related bus.

- A Information about the originator of the bus access. May contain additional information, e.g. served channel in case of DMA access.

- **B** Information about the bus access mode: SV or user.

- C Core data accesses (rd-data, wr-data) to CSA made by core 0. TriCore AURIX cannot trace read data value. No bus information available, the originator is always the core.

- D Core 1 performs data read access to D:0xF0000110 (peripheral). Data value cannot be traced.

- **E** SPB read access to D:0xF0000110 made by bus master DMI of Core 1. This corresponds to data access of **D**. Data value available (bus trace).

As the debugger is also a bus master and performs all accesses via the bus system, its accesses also generate trace messages. The debugger by default suppresses the display of these messages. Using the command **Trace.Mode SLAVE ON** these accesses will be displayed, too.

For DMA accesses MCDS generates information about the DMA controller or the Move Engine and the related channel number. As only five bits are reserved for the channel information only 32 DMA channels are supported. For TriCore devices with more DMA channels this information is ambiguous, so the DMA transfer could have happened on channel 5, 37, 69, ... For an unambiguous identification of the DMA channel the Peripheral Trace has to be used. Refer to the example **Peripheral Trace for DMA of TC277TE**.

You have the following options to search the trace data:

A text search within the Trace.List window

For a text search, press **Ctrl+F**. The text search ranges from the current trace record up to the first occurrence of the search item.

The text search compares the content of the **Trace.List** window with the search item and will find any occurrence. Because of the text comparison, the text search is very slow.

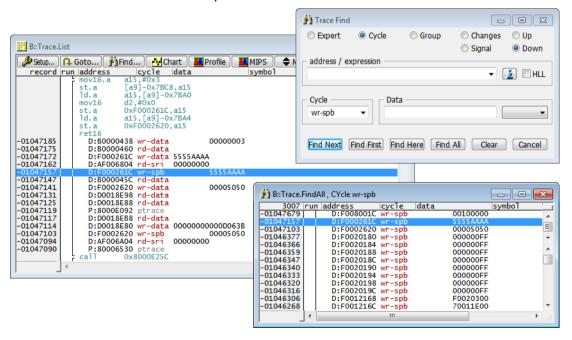

A command-based search

Events in the trace decoding can quickly be found using **Trace.Find** and **Trace.FindAll**. For a general description, please refer to the descriptions of the commands. Only options of special relevance for MCDS are described here.

For detailed information about the command based search, refer to "Application Note for the Trace.Find Command" (app\_trace\_find.pdf).

Clicking the **Find** button in the **Trace.List** window will enable implicit tracking of the **Trace.Find** and **Trace.FindAll** results with the **Trace.List** window. Otherwise tracking can be enabled with the **Track** option.

## Specific Cycles

Read- and write accesses of a specific CPU are rare and hard to find, especially if a certain value is of interest. In addition to the pre-defined cycle types, all cycle types listed in the **cycle** column of the **Trace.List** window can be searched. The example shows a search for an SPB write access:

If necessary the search can be restricted to specific data values and access widths and types.

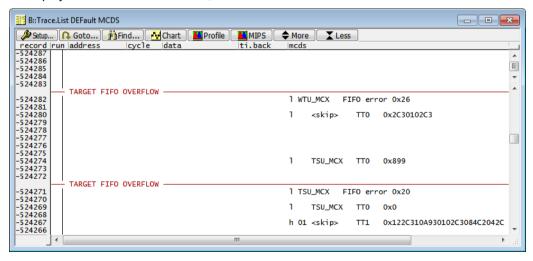

For MCDS, the following expert options are available for finding special events, depending on the device:

| Events:     | TRACEENABLE, WATCHPOINT, COUNTER  |

|-------------|-----------------------------------|

| Exceptions: | EXCEPTION, INTERRUPT, TRAP, RESET |

| Error:      | FIFOFULL, FLOWERROR               |

NOTE:

For watchpoints it is currently only possible to show the internal ID in the data column but not the breakpoint configuration name. As watchpoints are independent messages, it is also not possible to display the related symbol.

# **Exception Decoding**

The MCDS flow trace protocol does not provide any information about entries into the exception handler so displaying this event requires extra setup. For TriCore there are two methods available:

- Tables: They specify the locations of the exception handler

- DCU messages: They enable generation of extended trace data

## **Exception Decoding Using Tables**

For each TriCore core, one address range for an interrupt handler table and another one for a trap handler table can be specified. By default, these tables are filled automatically by evaluating the BIV and BTV registers of the cores before the trace decoding starts. For interrupts, it is assumed that all interrupts are used.

In some cases, e.g. when BIV and BTV are destroyed or not all interrupts are used, it might be necessary to specify the handler areas manually using the MCDS.Option exception.TABLE command:

```

; 256 interrupt handler entries

MCDS.Option eXception.TABLE Interrupt 0xC0001000++0x2FFF

; 8 trap handler entries

MCDS.Option eXception.TABLE Trap 0xC0002000++0xFF

```

In the example above, the size of an exception handler entry is fixed to 32 bytes. In the example below, the TriCore AURIX CPU uses a non-default entry size:

```

; 256 interrupt handler entries, 8 B entry size

MCDS.Option eXception.TABLE Interrupt 0x70001000++0x7FF 8.

; 8 trap handler entries, 32 B entry size

MCDS.Option eXception.TABLE Trap 0x70002000++0xFF

```

In case of multicore configurations, up to three address ranges can be specified, one for each core starting with core 0.

The advantage of tables is that in case of a static exception configuration all exceptions are identified. Additionally it is possible to distinguish between interrupts and traps.