# Microcontroller-Based Digital System Design featuring the Motorola 68HC12

# PRELIMINARY Edition of Chapters 2 & 3

David G. Meyer

# Copyright Notice

All rights reserved. No part of this Lecture-Workbook or Text may be reproduced, in any form or by any means, without permission in writing from the author.

# **Preface**

The purpose of this book is to teach students how to design and implement a microcontroller-based digital system. As such, it contains material that might typically be covered in a sequence of two courses: (1) a junior-level "microprocessor" course covering the basics of how a microprocessor works, how to program it to perform basic functions, and how to interface it to various external devices using integrated peripherals; and (2) a senior-level "digital system design project" course covering more advanced topics on microprocessor programming and interfacing, along with a series of practical system design considerations. Note that a background in basic digital system design is a necessary prerequisite, ideally obtained during the student's sophomore year. While there are a number of reasonably good texts currently available that provide such an introduction, one of the best (and my long-time personal favorite) is John F. Wakerly's *Digital Design Principles and Practices (Third Edition)*, Prentice Hall, 2000.

A unique feature of *Microcontroller-Based Digital System Design* (sub-titled *Bigger Bytes of Digital Wisdom*, or *Bigger Bytes* for short) is the availability of what I refer to as a "Lecture Workbook", i.e., a set of lecture slides (provided in PowerPoint<sup>TM</sup> format) with *carefully chosen* portions to be annotated or completed in class. The Lecture Workbook concept is based on the premise that notes taken during a classroom lecture serve more than mere archival of information – an encoding process occurs in the student's brain as he/she writes. By focusing this encoding process on *key words* or *selected aspects* of hardware/software design, the time and effort spent in class can be optimized. A special set of PowerPoint<sup>TM</sup> slides, which include an *animated*, *successive annotation* of the Lecture Workbook slides (including completed exercises), is available for instructor use. (The "skeleton" slides can also be made into overhead transparencies and annotated "manually", for those instructors who prefer that mode of presentation.)

Another student- and instructor-friendly feature is the availability of an "Exercise Workbook" that contains a set of (full-size) printable homework problems in PDF format along with solutions to selected exercises. Also included are a number of source files that are to be completed as part of these problems. Individual students can print out selected problems and complete them in a structured, "easy-to-grade" fashion.

The availability of a complete 'Lab Workbook" – based on a low-cost evaluation board (EVB) available directly from Motorola University Support – is another feature of this text. The Motorola EVBs have a small prototyping area that makes them ideal not only for introductory courses on microcontrollers, but also for use in senior design projects.

# Table of Contents

| 2 | DESI   | DESIGN OF A SIMPLE COMPUTER                        |    |  |  |  |

|---|--------|----------------------------------------------------|----|--|--|--|

|   | 2.1    | Computer Design Basics                             | 3  |  |  |  |

|   | 2.2    | Simple Computer Big Picture                        | 5  |  |  |  |

|   | 2.3    | Simple Computer Floor Plan                         |    |  |  |  |

|   | 2.4    | Simple Computer Programming Example                |    |  |  |  |

|   | 2.5    | Simple Computer Block Diagram                      |    |  |  |  |

|   | 2.6    | Instruction Execution Tracing                      | 18 |  |  |  |

|   | 3.7    | Bottom-Up Implementation of Simple Computer        | 24 |  |  |  |

|   |        | 3.7.1 Memory                                       | 24 |  |  |  |

|   |        | 3.7.2 Program Counter                              | 28 |  |  |  |

|   |        | 3.7.3 Instruction Register                         | 30 |  |  |  |

|   |        | 3.7.4 Arithmetic Logic Unit                        | 31 |  |  |  |

|   |        | 3.7.5 Instruction Decoder and Micro-sequencer      | 35 |  |  |  |

|   | 3.8    | System Timing Analysis                             | 40 |  |  |  |

|   | 3.9    | Simple Computer Extensions                         | 42 |  |  |  |

|   |        | 3.9.1 Input/Output Instructions                    | 42 |  |  |  |

|   |        | 3.9.2 Transfer-of-Control Instructions             | 47 |  |  |  |

|   |        | 3.9.3 Multiple Execute Cycle Instructions          | 50 |  |  |  |

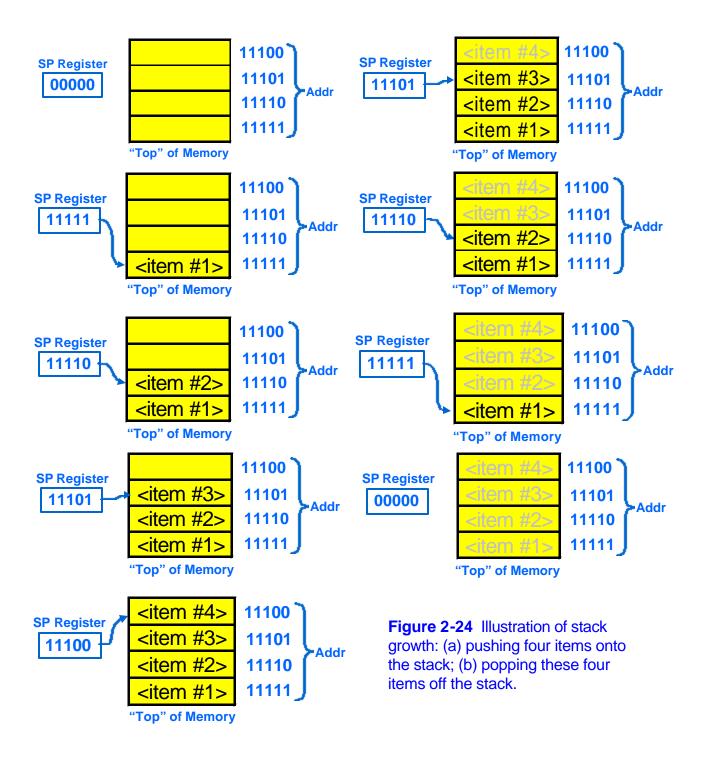

|   |        | 3.9.4 Stack Manipulation Instructions              | 53 |  |  |  |

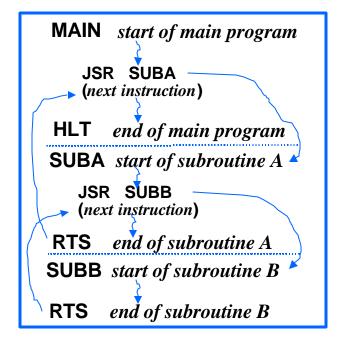

|   |        | 3.9.5 Subroutine Linkage Instructions              | 58 |  |  |  |

|   |        | 3.9.6 Other Possibilities                          | 63 |  |  |  |

|   | 2.10   | Summary and References                             | 64 |  |  |  |

|   | Proble | ems                                                | 65 |  |  |  |

|   |        |                                                    |    |  |  |  |

| 3 | INTRO  |                                                    |    |  |  |  |

|   |        | AND PROGRAMMING MODEL                              |    |  |  |  |

|   | 3.1    | Differing World Views                              | 2  |  |  |  |

|   | 3.2    | Characteristics That Distinguish Microprocessors   | 4  |  |  |  |

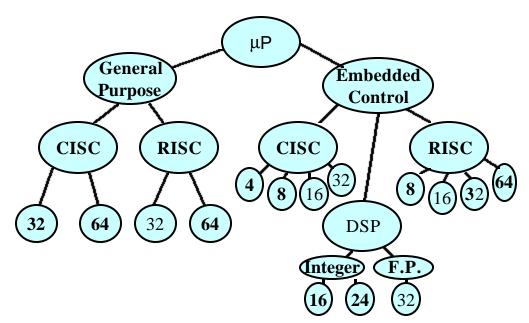

|   | 3.3    | Taxonomy of Microprocessors                        | 6  |  |  |  |

|   | 3.4    | Choosing an Education-Appropriate Microprocessor   | 9  |  |  |  |

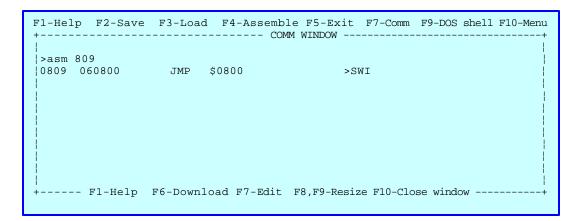

|   | 3.5    | Tools of the Trade                                 | 12 |  |  |  |

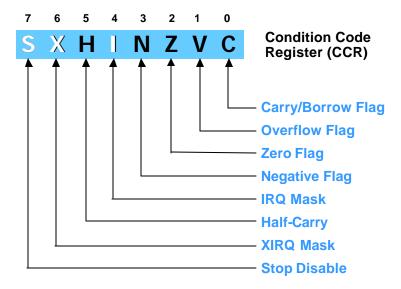

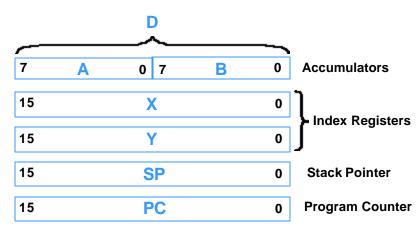

|   | 3.6    | Motorola 68HC12 Architecture and Programming Model | 26 |  |  |  |

|   | 3.10   | Addressing Modes                                   | 30 |  |  |  |

|   |        | 3.7.1 Non-Indexed Modes                            | 31 |  |  |  |

|   |        | 3.7.2 Indexed Modes                                | 33 |  |  |  |

|   |        | 3.7.3 Addressing Mode Summary                      | 38 |  |  |  |

|   | 3.8    | Motorola 68HC12 Instruction Set Overview           | 40 |  |  |  |

|   |        | 3.8.1 Data Transfer Group Instructions             | 40 |  |  |  |

|   |        | 3.8.2 Arithmetic Group Instructions                | 46 |  |  |  |

|   |        | 3.8.3 Logical Group Instructions                   | 57 |  |  |  |

|   |        | 3.8.4 Transfer-of-Control Group Instructions       | 64 |  |  |  |

|   |        | 3.8.5 Machine Control Group Instructions           | 76 |  |  |  |

|   |        | 3.8.6 Special Group Instructions                   | 79 |  |  |  |

|   | 3.9    | 82                                                 |    |  |  |  |

|   | Proble | Problems                                           |    |  |  |  |

#### CHAPTER 2

#### DESIGN OF A SIMPLE COMPUTER

Before we launch into the details associated with a relatively complex, contemporary microcontroller, it will be helpful for us to examine the design and implementation of a simple computer. In particular, the overall approach – based on a *top-down* specification of functionality, followed by a bottom-up implementation of the various functional blocks - will prove useful to our basic understanding of how a "real" microcontroller works.

top-down, bottom-up

In Chapter 1, we reviewed a number of digital system building blocks. This included combinational elements such as decoders, priority encoders, and multiplexers as well as sequential elements such as latches and flip-flops. We then reviewed how these combinational and sequential elements can be combined to build digital systems. We also reviewed how digital systems could be specified using a hardware description language and subsequently implemented usina programmable logic devices (PLDs).

programmable logic devices

Our purpose here is to apply this background to the design of a simple computer. Before we go any further, though, some basic definitions are in order. First, what is a *computer*? What distinguishes computers from random combinations of logic or from simple "light flashing" state machines? Simply stated, a computer is a device that sequentially stored program executes a stored program. The program executed is typically called software if it is a user-programmable ("general purpose") computer system; or called firmware if it is a single-purpose, non-userprogrammable system (also referred to as a "turn-key" system). A given program consists of a series of instructions that the machine understands. Instructions are simply bit patterns that tell the computer what operation to perform on specified data. That a program is stored implies the existence of *memory*. To perform the series of instructions stored in memory, two basic operations need to be performed. First, an instruction must be *fetched* (read) from memory. Second. that instruction must be executed, e.g., two numbers are added together to produce a result. The memory that is used to store a program can take many different forms - ranging from removable media devices such as CD-ROMs to patterns in the metal layer of an integrated circuit. While the physical implementation of the memory in which the program is

computer

software firmware

memory

stored may vary, the information stored in memory is interpreted (i.e., fetched and executed) the same way.

Given the basic definition of a computer, above, what is a *microprocessor*? Classically, it is a single-chip embodiment of the major functional blocks of a computer. Today, though, the term "microprocessor" is often applied to a wide range of single- and multichip computational devices, ranging from "mainframes on a chip" (used in personal computers and workstations) to small dedicated controllers (used in a wide variety of "intelligent" devices). They can range in physical size from packages with several hundred pins to packages with only a few pins; some examples are illustrated in Figure 2-1. They can range in cost from less than one dollar to hundreds of dollars. The simple computer we will be designing here can be implemented using a modest-size PLD; we could therefore rightfully call this single-chip embodiment of our simple computer a "microprocessor."

microprocessor

**Figure 2-1** Contrasting contemporary microprocessors: (a) an 8-bit PIC microcontroller; (b) a 16-bit Motorola 68HC12 microcontroller; and (c) a 64-bit MIPS microprocessor.

Finally, what is a microcontroller, and how does it differ from a microprocessor? Typically a microcontroller integrates, in addition to a microprocessor, a number of peripheral devices that are commonly used in control-type applications onto a single integrated circuit (and are thus often referred to as "single-chip microcontrollers"). Peripheral devices get their name from the fact that they provide interfaces with devices that are external (i.e., "peripheral") to the computer. For example, a common series of operations often performed in control applications is: (1) input analog signals from sensors, (2) process them according to some algorithm, (3) and output analog control voltages to actuators. A device that digitizes an analog input voltage is called an analog-to-digital (A-to-D) converter. Conversely, a device that produces an analog output voltage based on a digital code is called a digital-to-analog (D-to-A) converter. A-to-D and D-to-A converters are examples of peripherals one might find integrated onto a microcontroller chip.

microcontroller

peripheral devices

Other common peripherals include communication controllers, timer modules, and pulse-width modulation (PWM) generators. Later, we will see a variety of applications for all of these integrated peripherals.

#### 2.1 Computer Design Basics

How can we apply what we have learned thus far about basic digital system building blocks toward building a simple computer? Basically, what we need is some way to structure and break down this design problem, because now it is a somewhat bigger than drawing a single state transition diagram or filling out a truth table. We will need a structured approach that enables us to take a written description of the functions performed by our simple computer and create a high-level block diagram. Based on this diagram, we can proceed to define what each block does, and ultimately design the circuitry required to implement each block.

Before starting this process, though, we need to define what we mean by the structure of a computer. "Architecture" is a word commonly architecture used to depict the arrangement and interconnection of a computer's functional blocks. While some might argue that this definition of computer architecture is a bit simplistic, it will serve our purposes for the discussion that follows.

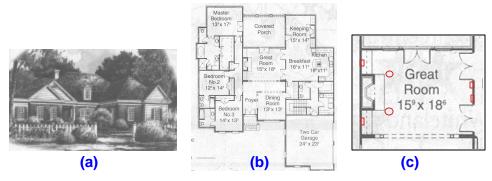

Before starting to design our simple computer, let us first consider a "real world" analogy: building a house. Where is the logical place to start? Probably with a "big picture" - i.e., an exterior elevation or plan big picture view of the entire project. Of course, the floor plan and exterior elevation are greatly influenced by the size, shape, and grade of the lot chosen for the house. Once we know the physical constraints dictated by our choice of lot, we can then begin to develop a floor plan. At this stage we can define the overall "functionality" of the house, i.e., the purpose of each room. Once we have defined the functionality of each room, the next step is to determine their arrangement and interconnection. Once we have a working floor plan, we can begin to embellish it with a number of details - for example, the location and size of windows, the location of light fixtures and their associated wall switches, the location of power outlets, the routing of plumbing, etc. The important thing to note from this analogy is that we have described a top-down design process: starting with a "big picture", and progressively embellishing it with layers of details. Figure 2-2 depicts such a progression.

**Figure 2-2** Top-down design of a house: (a) the "big picture", (b) the floor plan, (c) details of a particular room.

Once all the design specifications have been formulated, how would we proceed to build our house? From the ground up — assuming we have adequate financing, of course. We have to dig a hole first (perhaps analogous to going into debt), then pour a foundation, "stick-build" the basic structure, put a roof on it, complete the exterior walls, and finally embellish each room with its finishing details. Note that the *order* in which this "bottom up" implementation proceeds is quite important — certainly one would not wish to start hanging drywall before the roof is in place, or run plumbing lines before the floor joists are in place. Clearly, there is a structured, ordered way in which the entire process must take place — an approach strikingly similar to the one we will follow in designing our simple computer.

What would be a good name for the overall process described above? Ignoring the financial aspects for a moment, we could aptly call it the top-down specification of functionality followed by bottom-up implementation of each basic step (or "block"). More succinctly, we could call it *top-down specification and bottom-up implementation*. This is the process we will apply to the design and implementation of our simple computer.

top-down specification

bottom-up implementation

First, a disclaimer. The initial machine we design will be very, very simple. It will be an 8-bit machine with just a few instructions. Further, there will be a single *instruction format* (layout of bit patterns) as well as a single *addressing mode* (way that the processor accesses operands in memory). By the time we finish this "first phase" design, however, we will find out that even this rather simple machine is fairly complex in terms of implementation details.

instruction format

addressing mode

Once we have mastered our simple computer, we will then add "modern conveniences" such as input and output (or "I/O"), transfer of control instructions, stack manipulation instructions, and subroutine

linkage instructions. We will have the makings of a "socially redeeming" computer once we get done, plus have a firm footing upon redeeming which to understand the architecture and instruction set of a "real" computer.

socially

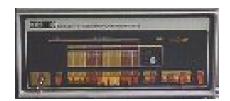

# 2.2 Simple Computer Big Picture

Just as one might begin the design of a house by sketching an exterior elevation view, we will begin the design of our simple computer with a "big picture" of its control console. In the "old days" (which was actually old days not so long ago), computers had lots of lights and switches on their front panels. The Digital Equipment Corporation PDP-8 (the first commercial "minicomputer"), illustrated in Figure 2-3, was a good minicomputer example of such a computer. The Intellect 8 microcomputer system (one of the first commercially-available microprocessor development systems) from Intel, based on the 8008 microprocessor, was another example. Frankly, these ground-breaking computer systems were a lot more interesting (and fun) to watch "crunch numbers" than today's computers...and a lot less irritating than the "this application has performed an illegal function and will be shut down" message we've all become accustomed to today.

crunch numbers

Figure 2-3 World's first "desktop" minicomputer, the PDP-8.

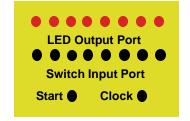

Figure 2-4 Our simple computer console.

Our computer's console, then, will have some lights that indicate the result of the most recent computation along with some switches that will be used to input data. A "START" pushbutton will be included to get the machine into a known initial state (in preparation for "running" a program), and a "CLOCK" pushbutton will be included to facilitate debugging (as we manually clock the machine from state-to-state). An "artist's conception" of our simple computer's console is shown in Figure 2-4.

Returning to the "house analogy" for a moment, the floor plan of a computer is basically its instruction set and programming model. The instruction set is simply the list of operations that the computer programming There are five fundamental groups (or categories) of model performs. machine instructions: data transfer, arithmetic, logical (or "Boolean"), transfer of control, and machine control. (Some computers include a sixth group dedicated to specific applications, e.g., multimedia The addressing modes that addressing modes extensions or graphics support.) instructions can use to access operands in memory are also a key aspect of a computer's instruction set.

instruction set

The programming model of a computer is the software writer's view of the machine. Basically, it tells what resources are available for the programmer's use, in particular, the machine's registers. A register is simply a "memory location" within the processor that can be used to store intermediate results and/or as an operand (or as a pointer to an pointer operand) used in a computation.

As alluded to above, the programming model and instruction set of our computer will be relatively simple. Initially there will only be one register, called the accumulator (or "A" register), so-named because it is the register in which the result of computations accumulate. Our computer will also include several condition code bits: a zero flag (ZF), negative flag (NF), overflow flag (VF), and carry/borrow flag (CF). Before we complete this chapter, we will add a stack pointer register and discuss the role of index registers.

condition code bits ZF**NF VF**

**CF**

The instructions executed by our simple computer will be of the fixedlength variety (i.e., all 8-bits in size, hence its designation as an "8-bit" computer) that consist of two fixed-length fields. The upper 3-bits of each instruction will indicate the operation to be performed, and is therefore called the operation code field (or "opcode" field). The lower opcode field 5-bits will indicate the memory address in which the operand is located (or, a result is to be stored). The 5-bit memory address dictates a maximum memory size of  $2^5 = 32$  locations. For those who have become jaded by multi-megabyte programs that appear to do trivial things, this may not seem like much memory! Fortunately, though, it will be enough to illustrate basic principles of instruction execution, despite being too small to contain a "practical" (i.e., useful and socially redeeming) program.

In addition to fixed-field decoding, another simplification in our initial design will be a single addressing mode. An addressing mode is the mechanism (or "function") used to generate what is often called the

addressing mode

effective address of an operand, i.e., the actual address in memory where an operand is stored. The addressing mode our machine will support might aptly be called "absolute" addressing, based on the fact that this 5-bit field directly indicates the effective address in memory where the operand is stored. It is important to note at this point that not all manufacturers of microprocessors agree on the names ascribed to certain addressing modes. What we have just referred to as an "absolute" addressing mode is typically called "extended" (by Motorola) or "direct" (by Intel).

effective address

absolute addressing mode

One other bit of terminology worth mentioning before delving into the instruction set concerns the number of addresses a given instruction (or more generally, a machine) can accommodate. Our simple computer here could be described as a "two address" machine, which means that two different locations (at two different addresses) are used in a given operation, e.g., ADD. In our computer, one location will be the "A" register (the accumulator), and the other will be contained in memory. Note that a "side-effect" of such an arrangement is that the result of the computation will overwrite one of the operands, here the value in the "A" register (the operand in memory will be unaffected). As one might guess, there are a lot of variations in instruction format and addressing capability, ranging from single-address instructions to three-address (or more) instructions.

two-address machine

# 2.3 Simple Computer Floor Plan

We are now ready to introduce the "floor plan" (instruction set) of our simple computer. Note that we will initially define six of the eight possible instructions afforded by our 3-bit opcode field. We will save the last two opcode bit patterns to define some extensions to our instruction set later in this chapter. Our simple computer's instruction set is given in Table 2-1.

**Table 2-1** Simple computer instruction set.

| Opcode | Mnemonic | Function Performed                           |

|--------|----------|----------------------------------------------|

| 000    | LDA addr | Load A with contents of location addr        |

| 0 0 1  | STA addr | Store contents of A at location addr         |

| 0 1 0  | ADD addr | Add contents of addr to contents of A        |

| 0 1 1  | SUB addr | Subtract contents of addr from contents of A |

| 100    | AND addr | AND contents of addr with contents of A      |

| 1 0 1  | HLT      | Halt – Stop, discontinue execution           |

The first two instructions, "LDA" and "STA", are examples of data transfer group instructions. As their assembly mnemonics imply, these instructions transfer data between the "A" register (accumulator) and memory. For the "load A" (LDA) instruction, the source of the data is memory location addr, and the destination is the "A" register. For the "store A" (STA) instruction, it is just the opposite: here, addr indicates the location in memory where the value in A (also referred to as the contents of A) is to be stored. As it turns out, "load" and "store" instructions are the "most popular" instructions in any machine's instruction set, often comprising as much as 30% of the compiled code for typical applications.

data transfer group instructions assembly mnemonics

LDA **STA**

A "shorthand" notation we will use throughout the remainder of this text is the use of parenthesis to indicate "the contents of" a particular register or memory location. This allows us to describe what an LDA instruction does as simply "(A)  $\leftarrow$  (addr)" and what an STA does as "(addr) ← (A)". An important point to note in both cases is that the source of the data transfer - i.e., (addr) for LDA and (A) for STA does not change (or, is unaffected) as a result of the instruction execution.

Continuing down the list of available instructions, we next find two arithmetic group arithmetic group instructions: ADD and SUB. The ADD instruction instructions performs the operation (A)  $\leftarrow$  (A) + (addr) using radix (or two's complement) arithmetic, and sets the condition code bits based on the result obtained. (Details on radix arithmetic and condition codes can be found in the review material presented in Chapter 1.) The SUB instruction performs the operation (A)  $\leftarrow$  (A) – (addr) and sets the condition code bits accordingly. Recall that there is an important arithmetic difference regarding how the carry flag (CF) is affected in an addition versus a subtraction. Following an ADD, the carry flag is the carry out of the most significant (or sign) position; whereas following a SUB, the carry flag is the *complement* of the carry out of the sign position (based on its interpretation as a borrow). Because of this difference between ADD and SUB, the CF bit is sometimes referred to as the "carry/borrow" flag - which is the way we will formally refer to it. If what we just described seems a bit "fuzzy", now would be a good time to review the material in Chapter 1.

**SUB**

two's complement

carry/borrow flag

Moving down the chart, we find that our next instruction, AND, is from the logical (or "Boolean") group. Because logical group instructions perform bit-wise operations, they are sometimes referred to as bit bit manipulation manipulation instructions. At minimum, most microprocessors worth instructions their silicon generally have at least three Boolean instructions: AND,

logical group instructions

OR, and NOT (many also include XOR). Our simple computer, however, will just implement the first of these operations, which can be described using the notation (A)  $\leftarrow$  (A)  $\cap$  (addr), where the " $\cap$ " symbol XOR is used to denote the bit-wise logical AND of the two operands to produce the corresponding result bits.

AND OR**NOT**

No instruction set would be complete without a way to stop the machine. Our sixth (and final, for now) instruction, HLT (for "halt") serves this purpose. The HLT instruction is an example of a machine machine control control group instruction. Execution of the HLT instruction will "freeze" the machine at its current point in the program being executed, and prevent the machine from fetching or executing any additional instructions until it is restarted (by pressing the START pushbutton described previously).

HLT group instructions

# 2.4 Simple Computer Programming Example

To better understand how our simple computer operates, we will "walk through" the execution of a short program. This program will exercise each instruction in our simple computer's repertoire. An important point to consider before proceeding is that it would be rather difficult to design a "simple" computer that directly interprets the instruction mnemonics (i.e., LDA, STA, etc.) we have defined. Rather, it is much easier to design a machine that directly interprets bit patterns (0's and 1's) that represent these instructions. This means that, before we can place our program in memory, we must translate the instruction mnemonics into bit patterns ("code") the machine understands, called machine code. This translation process is called assembly, since machine code machine code is created directly ("assembled") based on instruction mnemonics. As one might guess, instruction mnemonics are typically referred to as assembly level mnemonics, or simply assembly A software program that translates assembly level language. mnemonics into machine code is called an assembler. If one is unfortunate enough to perform the translation by hand, the process is called hand assembly.

assembly language

hand assembly

Fortunately, most computer programming is done at a higher level of abstraction, using high-level languages such as "C". Here, a compiler program is used to translate code written in high-level language into assembly code. An assembler program is then used to translate the compiler's output into machine code for the target processor. We will find, though, that a firm grasp of assembly language programming techniques is essential for effectively utilizing the resources integrated

high-level language compiler

into a modern microcontroller. Once we master assembly-level programming, we'll consider how to program a microcontroller using "C". But to get there, we need to start at the "basic bit" level – so let's return to the illustrative simple computer program in Table 2-2.

**Table 2-2** Programming example.

| Addr  | Instruction | Comments                                   |

|-------|-------------|--------------------------------------------|

| 00000 | LDA 01011   | Load A with contents of location 01011     |

| 00001 | ADD 01100   | Add contents of location 01100 to A        |

| 00010 | STA 01101   | Store contents of A at location 01101      |

| 00011 | LDA 01011   | Load A with contents of location 01011     |

| 00100 | AND 01100   | AND contents of 01100 with contents of A   |

| 00101 | STA 01110   | Store contents of A at location 01110      |

| 00110 | LDA 01011   | Load A with contents of location 01011     |

| 00111 | SUB 01100   | Subtract contents of location 01100 from A |

| 01000 | STA 01111   | Store contents of A at location 01111      |

| 01001 | HLT         | Stop – discontinue execution               |

One of the first things we need to know is where in memory our program needs to be located. The logical thing to do is place our program at the *beginning* of memory, i.e., starting at location 00000<sub>2</sub>. We can then design the circuitry that, after the START pushbutton is pressed, begins fetching instructions from memory at location 00000<sub>2</sub>. Recalling that instructions are of fixed length (8 bits) and that memory locations are 8-bits wide, we realize that consecutive instructions will occupy consecutive memory locations. We can then imagine a "pointer" that tells us which instruction is to be executed, and that gets incremented after each instruction is fetched. Such a pointer is typically referred to as either an instruction pointer or a program program counter counter.

instruction pointer

A "snapshot" of what our short program looks like in memory prior to execution is provided in Figure 2-5 (just the "first half" of memory, from locations 000002 to 011112 is shown). The lightly shaded part corresponds to the assembled machine code. Referring back to Table 2-2, note that the first instruction (at address 00000<sub>2</sub>) is load accumulator (LDA) with the contents of memory location 010112. Since the 3-bit opcode for LDA is "000", this instruction is encoded as the bit pattern "000 01011" in memory. Stated another way, the instruction "LDA 01011" has been assembled into the machine code "000 01011". We could go through a similar "hand assembly" process for the rest of the instructions that comprise the program, up to and

including the HLT instruction at location 01001<sub>2</sub> (note that the address field of this instruction is not used, and is shown here to be "00000").

| Location | Contents |

|----------|----------|

| 00000    | 00001011 |

| 00001    | 01001100 |

| 00010    | 00101101 |

| 00011    | 00001011 |

| 00100    | 10001100 |

| 00101    | 00101110 |

| 00110    | 00001011 |

| 00111    | 01101100 |

| 01000    | 00101111 |

| 01001    | 10100000 |

| 01010    |          |

| 01011    | 10101010 |

| 01100    | 01010101 |

| 01101    |          |

| 01110    |          |

| 01111    |          |

#### Beam in the Bits, Scotty!

One important detail we will ignore for the moment is how these bit patterns get loaded into memory. In a later chapter, we'll discuss how to write what's called a "loader" program, which – as its name implies – does just that. For now, assume Scotty (of Star Trek fame, for those of you much younger than the author) has used a molecular beam transporter to "beam the bits" into memory.

**Figure 2-5** Memory snapshot prior to program execution.

The operands used by each arithmetic (ADD, SUB) or logical (AND) operation will be stored at locations 01011<sub>2</sub> and 01100<sub>2</sub> (in the darker shaded area of Figure 2-5); note that we have initialized these two locations to *arbitrarily chosen values*. The results of each operation (ADD, AND, SUB) will be stored in three consecutive locations, starting at location 01101<sub>2</sub>. Note that our computer's memory will contain a mix of instructions and data (operands and results).

#### No Stopping It Now

What happens if the HLT instruction is omitted? Perhaps even worse than "not stopping", the computer will start *executing data*, which, as one might imagine, is not a pretty sight (or, stated less formally, causes "bits to fly all over the place") and, at best, leads to *very strange* program behavior. Any "honest" programmer (not to be confused with an honest politician), however, will confess that he/she has inadvertently done this "at least once..."

executing data

honest programmer

Given that our computer only understands 0's and 1's rather than the more human-friendly assembly mnemonics, the question that begs is: "How is our computer able to distinguish between instructions and data?" The hopefully obvious answer is: "It can't!" Rather, it has to be

told which locations contain instructions and which contain data. The convention we will use to make this distinction is that our programs will always start at location  $00000_2$  and continue until they reach a "halt" (HLT) instruction; any locations following the HLT instruction may be used for data (operands or results).

**Figure 2-6** Result after executing the first three instructions.

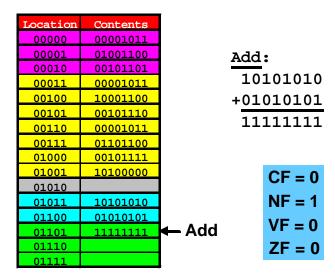

We are now ready to step through the execution of this program. Referring back to Table 2-2, we see that the purpose of the first three instructions is to add the two operands (at locations 01011<sub>2</sub> and 01100<sub>2</sub>, respectively) and store the result at location 01101<sub>2</sub>. As illustrated in Figure 2-6, the result obtained will be 11111111<sub>2</sub> (recall that this is the 8-bit representation for "-1" in two's complement notation). Also, the negative flag (NF) will be set to "1", the carry flag (CF) will be cleared to "0", the overflow flag (VF) will be cleared to "0", and the zero flag (ZF) will be cleared to "0".

#### Self-Perpetrating Programs

It is entirely possible to contrive a program that writes data into locations that contain instructions yet to be executed. The name "self-modifying code" has been used to describe such a creation. A self-modifying program, as one might guess, could prove to be excruciatingly difficult to debug. In a word, don't try this at home! (And, don't try to convince your boss that you've invented a new way to write "interesting" programs!).

self-modifying code

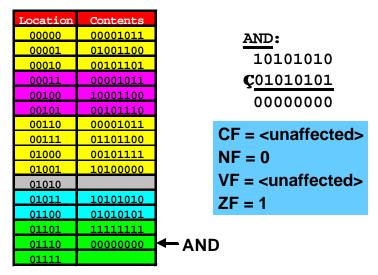

Again referring back to Table 2-2, we see that the purpose of the next three instructions is to logically AND the two operands and store the result at location 01110<sub>2</sub>. Note that, for the AND operation, the carry flag (CF) and overflow flag (VF) are meaningless, and therefore should be *unaffected* by the execution of the AND instruction. The result obtained, however, may be negative (in a two's complement sense) or zero, so the negative flag (NF) and zero flag (ZF) should be affected. A snapshot of memory following execution of the three AND-related instructions is provided in Figure 2-7. Note that, since the result obtained is 00000000<sub>2</sub>, the zero flag is set to "1".

**Figure 2-7** Result after executing the "middle" three instructions.

The purpose of the next group of three instructions is to take the difference of the two operands at locations 010112 and 011002. Specifically, we are going to subtract (SUB) the operand at location 01100<sub>2</sub> from the operand at location 01011<sub>2</sub>, and place the result at location 011112. Recall from Chapter 1 that a radix subtraction is realized by forming the two's complement of the subtrahend (here, the operand at location 01100<sub>2</sub>) and adding it to the minuend (the operand at location 01011<sub>2</sub>). Further, the easiest way to generate the radix complement of a signed number is to add one to its diminished radix complement (or *ones' complement*). Figure 2-8 shows what happens. Note that, while the result 010101012 will be stored at location 011112, it will be invalid because overflow has occurred (denoted by VF set to "1"). Note also that CF (the carry/borrow flag) is cleared to "0" due to its interpretation here as a borrow flag - recall that, following a subtract operation, CF is set to the *complement* of the carry out of the sign position (which in this case was "1"). A borrow flag of "0" following a

Sub: -01010101 CF = 0NF = 0VF = 1 1)01010101 ZF = 0**Overflow!**

subtract operation essentially means that "no borrow is propagated forward."

**Figure 2-8** Result after executing the last group of three instructions.

**←**Sub

#### **Bumbling Borrows**

Perhaps the single-most issue that causes students consternation is that of the carry/borrow flag. The interpretation of a "carry propagated forward" following an addition is no problem; but when it gets to subtraction, all "bits are off" (pardon the very bad pun). Here, the proper interpretation is as a "borrow propagated forward" to the next-most significant group of digits in an extended precision subtraction. The borrow flag (still called CF), when set, is basically telling that next group of digits to "reduce its result by one" because the previous stage "has borrowed from it." The best real-world analogy that comes to mind is that of a statement from your friendly, local banking institution listing the service charge they have extracted from your account for the privilege of serving you. The point is: since they have already taken the money, you need to adjust your idea of how much money you have left!

Before we leave this last block of code, yet another question that comes to mind is: "How should error conditions like overflow be handled?" As one might guess, we will need some "new" instructions that allow us to test the state of the various condition codes (here, VF) and transfer control to a different part of the program (typically called an "exception handler") if an error has occurred. Before we finish this chapter, we will learn how to implement such "conditional transfer of control" instructions.

The final instruction in our short program, HLT, simply tells our computer to "stop executing". Once the program has stopped, we could presumably look at the contents of each location to determine the results of the program execution. What we should find is the memory image depicted in Figure 2-8 (note that memory location 01010<sub>2</sub> was unused by our example program and may contain a "random" value).

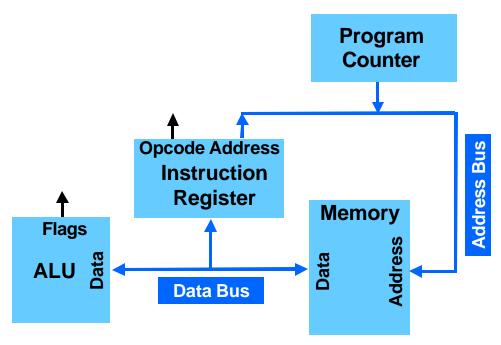

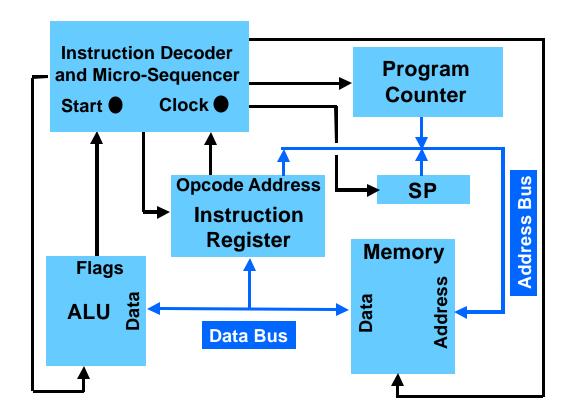

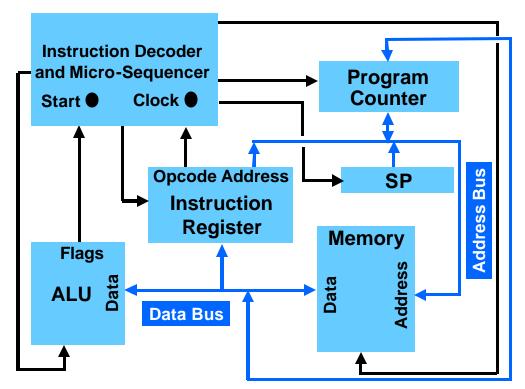

# 2.5 Simple Computer Block Diagram

Now that we know *how* our simple computer works, we are ready to consider the functional blocks necessary to *make* it work. Basically we want to build what appears to be a "big state machine" that performs the calculations just done by hand. At a fundamental level, there are two basic steps associated with the processing of each instruction. The first step is to read the instruction from memory, called an *instruction fetch cycle*. The second step is to extract the opcode and address fields from the instruction just fetched and perform the operation specified by the opcode on the data located at the specified address; this step is referred to as an *instruction execute cycle*.

instruction fetch cycle

instruction execute cycle

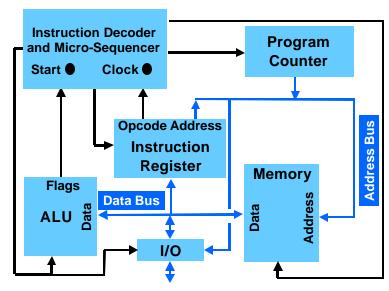

memory unit

What are the basic functional blocks, then, that are necessary to implement the simple computer described here? Clearly, a memory unit – for storing instructions and data – is one of the major functional blocks necessary. This memory unit needs to be capable of reading the contents of a specified location (indicated on its address lines) as well as writing a new value to a specified location.

Another major functional block needed is one that will keep track of which instruction is next in line to be executed. In our simple computer, the instructions are stored in consecutive memory locations, starting at location 00000<sub>2</sub>. What is needed is a pointer that keeps track of which instruction is next. Because this block is nothing more than a binary counter, we will call it the *program counter* (PC).

program counter PC

Once it is fetched from memory, a place is needed to temporarily "stage" an instruction while the opcode field is decoded and the address field is extracted. We can think of this block as a place to hold the instruction just fetched while it is being "digested". While more creative, biologically inspired names for it are certainly possible, we will simply call this functional block the *instruction register* (IR).

instruction register IR

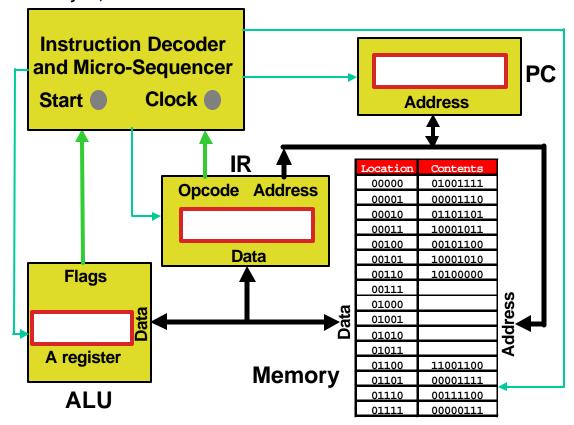

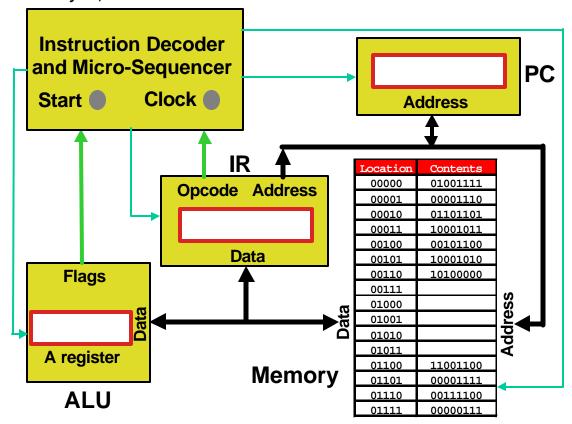

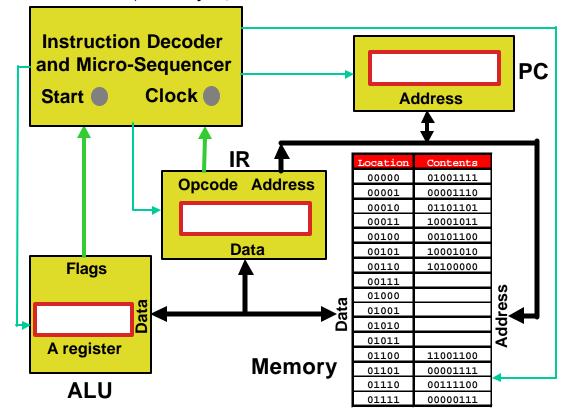

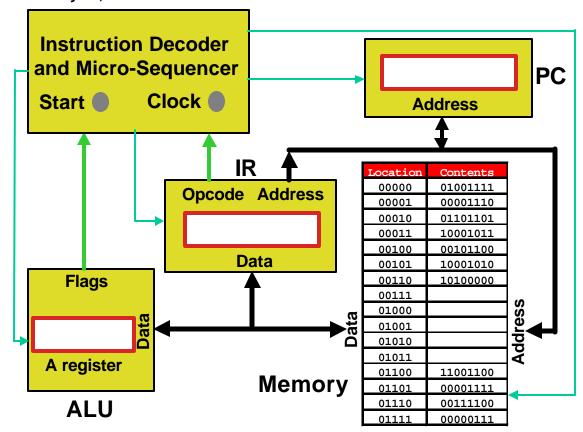

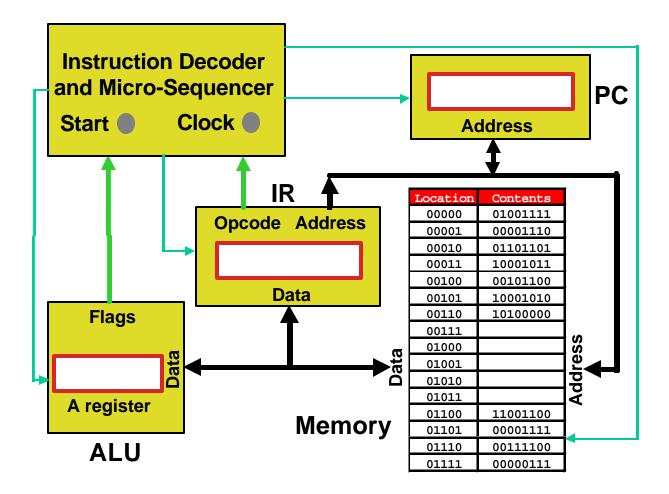

**Figure 2-9** Simple computer core block diagram.

Next we realize the need for a functional block that performs the arithmetic and logical operations we have defined in the simple computer's instruction set. Not surprisingly, this block is usually called an *arithmetic logic unit*, or simply ALU. Note that the accumulator ("A" register) and condition code bits (CF, NF, VF, ZF) are part of the ALU.

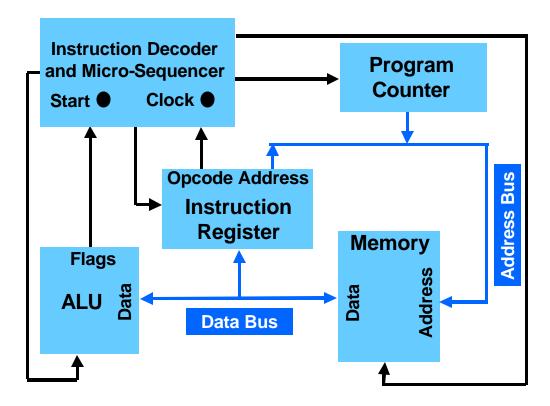

Finally, we realize that our simple computer needs a "manager" - a functional block that orchestrates the activities of all the other functional blocks delineated above. This "manager" is responsible for indicating whether a fetch or an execute cycle is to be performed and, once an instruction is fetched, for decoding the opcode field of that instruction and telling the other blocks in the system what to do in order to execute it. Because our simple computer's "manager" controls the sequencing of events that, taken together, constitute the completion of a machine instruction, we often refer to the state machine part of the manager's personality as a *micro-sequencer* (similar to, perhaps, but not to be confused with a "micro-manager"). And because decoding the opcode field of the instruction is an essential part of the sequencing process, we award our simple computer's manager the grand and glorious name: instruction decoder and micro-sequencer (IDMS). This more extravagant sounding name helps prevent images of "kicking bits around" that might be associated with a "manager" (think baseball).

arithmetic logic unit

ALU

manager

micro-sequencer

**IDMS**

Returning to the "house" analogy for a moment, what we have just done is "define the rooms" of the "structure" (or system) we wish to build. What we have not yet done, however, is interconnect the functional blocks into a working "floor plan". In order to do this, we need an understanding of the "traffic patterns" (here, of address, data, and control information) that need to flow among the various functional blocks.

Starting with the memory unit, we note that a series of address lines tell which location is being accessed; the collection of address lines is referred to as the *address bus*. (Recall that a *bus* is a set of signal lines that have a *common purpose*.) At the location in memory accessed, data can be *read* (output) or *written* (input); the memory's data lines (and the associated data bus) must therefore be *bidirectional*. Further, control signals need to be supplied to the memory unit that tell whether or not it is *enabled* to respond (or *selected*), and, if enabled to respond, whether it should perform a read operation or a write operation.

address bus

bi-directional

Next, we realize that the program counter (PC) will supply the instruction address to memory during a fetch cycle, and that the instruction register (IR) will be used to temporarily stage the instruction after it has been read from memory. Further, on an execute cycle, the IR will supply the operand address to memory, and the destination (or source) of the data in this transaction is the "A" register of the ALU. Thus, there are two potential sources of address information – the PC and the IR – on the address bus. Since only one device can "talk" on the bus at a given instant in time, we will need to provide each of these functional blocks with *three-state output* capability – and it will be our "manager's" job to keep them from talking at the same time!

three-state output capability

Further, there are two potential destinations of data read from memory. On a fetch cycle, an instruction destined for the IR is read from memory. On an execute cycle, an operand destined for the ALU is read from memory (alternately, data in the ALU is destined for memory if an STA instruction is being executed). Again, we note the need for three-state buffers in all the functional blocks involved with driving the data bus.

Putting this all together, the "core" of our simple computer is depicted in Figure 2-9. Left on their own, however, these functional blocks are incapable of doing anything "intelligent", let alone successfully executing instructions. Hence the need for a "manager" – the instruction decoder and micro-sequencer – to tell each block what to

do when. As such, the IDMS can aptly be thought of as the "heart" of the machine. The simple computer augmented with an IDMS is shown in Figure 2-10.

**Figure 2-10** Complete simple computer block diagram.

We now have a complete "floor plan" for our "house", that we have specified in a top-down fashion. Before actually building it, though, let's make sure we understand how the "rooms" work together.

# 2.6 Instruction Execution Tracing

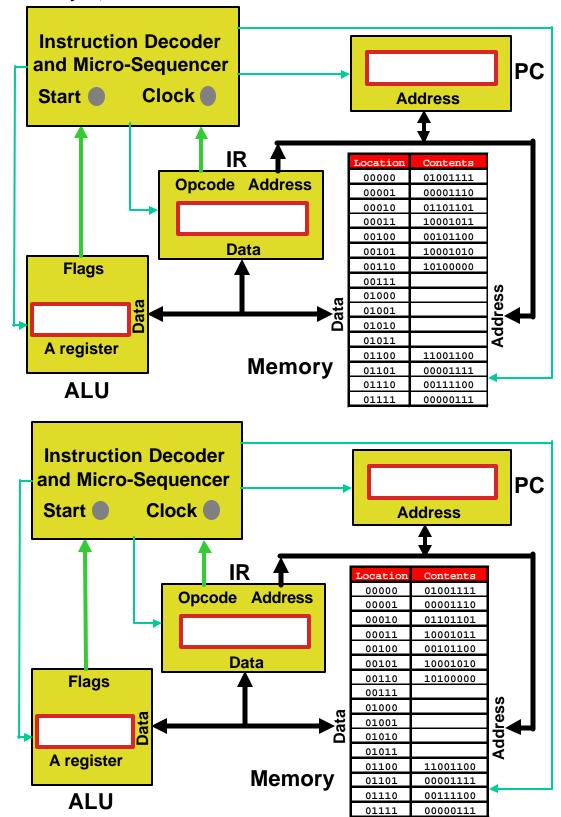

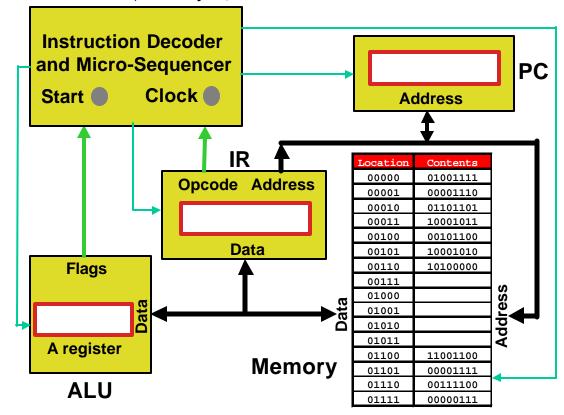

To get a better idea of how the various functional blocks of our simple computer work in concert to process instructions, we will return to our short program of Table 2-2 and use a technique called *instruction tracing* to help us visualize the flow of information. On a cycle-by-cycle basis, we will examine the address and data paths as well as the bit patterns in each register for the first three instructions of this short program. Recall that we used the term "micro-sequencer" because there is a sequence of events associated with processing an instruction: here, a fetch cycle followed by an execute cycle.

instruction tracing

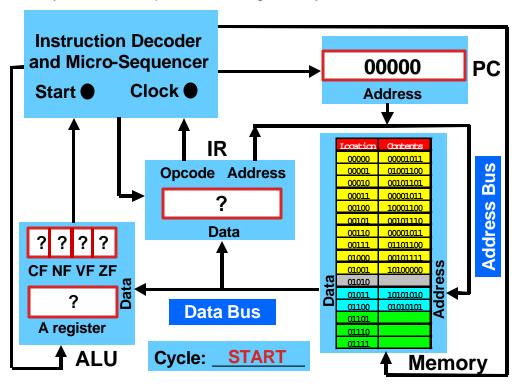

The instruction trace worksheet in Figure 2-11 sets the stage for this exercise, which shows the initial state of the machine after START is pressed. Note that there are several things we will keep track of as our machine executes the program. In particular, we will be monitoring what happens to the PC, IR, and "A" register as well as the contents of memory. We will also practice naming each cycle as it occurs.

**Figure 2-11** Instruction trace worksheet for machine state after START is pressed, prior to first fetch cycle.

Recall that pressing the START pushbutton places the machine in a known initial state: the PC is reset to "00000" and the state counter (in the IDMS) is set to "fetch". Note that the initial state of the IR and ALU may be "random" and that memory is initialized to the values indicated (although at this point we "don't care" what is in the unused location  $01010_2$  or the locations where the results will be stored,  $01101_2$ – $01111_2$ ).

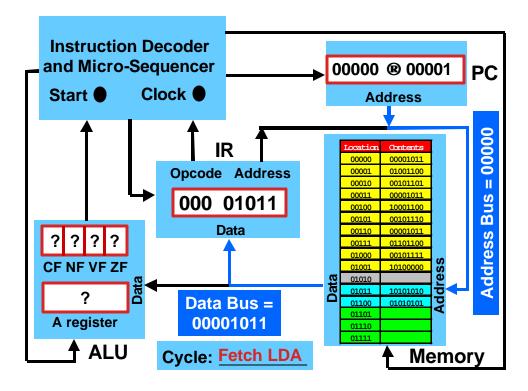

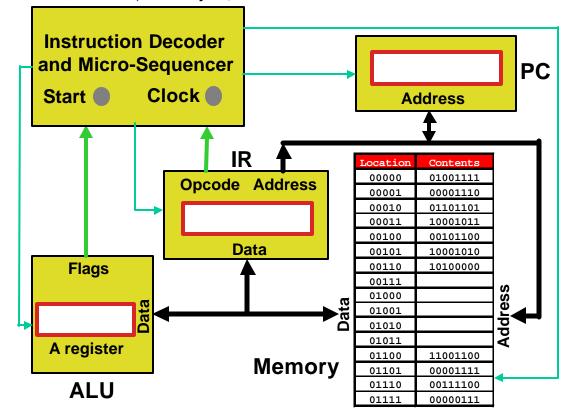

During the first fetch cycle, shown in Figure 2-12, the instruction at memory location  $00000_2$  is read and placed in the IR. As the IR is being loaded with the instruction, the PC is incremented by one (i.e., once the fetch of the current cycle is complete, the PC is pointing to the *next* instruction to execute). Note that the values in each register are those obtained *after* the "fetch LDA" cycle is *complete*.

**Figure 2-12** Instruction trace worksheet for first fetch cycle.

Figure 2-13 Instruction trace worksheet for first execute cycle.

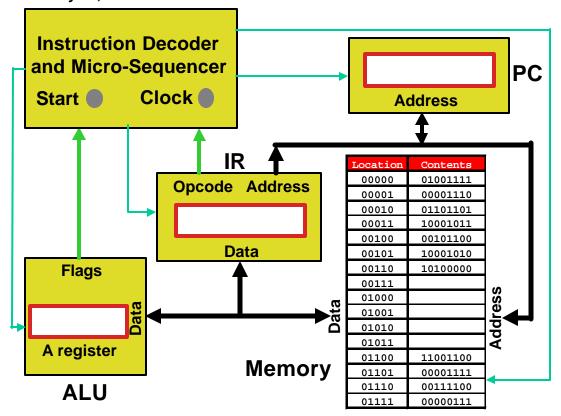

Figure 2-14 Instruction trace worksheet for second fetch cycle.

**Figure 2-15** Instruction trace worksheet for second execute cycle.

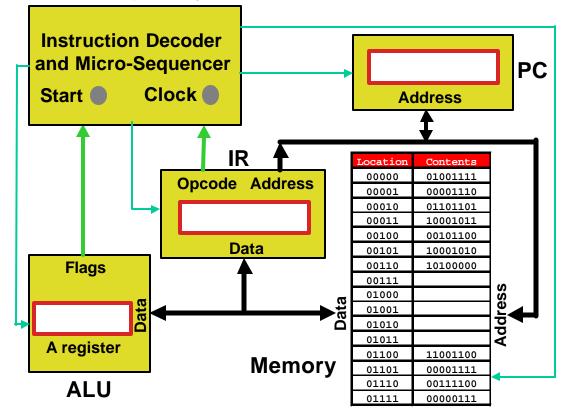

Figure 2-16 Instruction trace worksheet for third fetch cycle.

Figure 2-17 Instruction trace worksheet for third execute cycle.

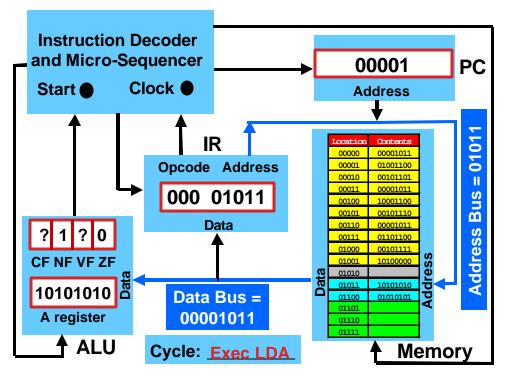

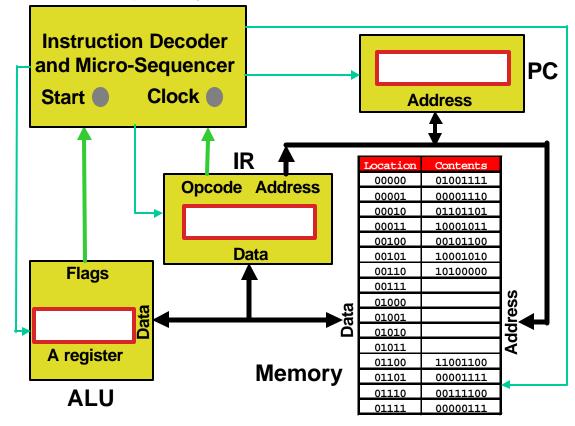

During the first execute cycle, shown in Figure 2-13, the "LDA 01011" instruction in the IR is executed. When this cycle is complete, the "A" register contains the contents of memory location 01011<sub>2</sub>, i.e., the value 10101010<sub>2</sub>. Note also that the NF is set to "1" and ZF is cleared to "0". The "execute LDA" cycle does not, however, affect the contents of any memory location, nor does it change the contents of IR or PC (condition code bits CF and VF are also unaffected).

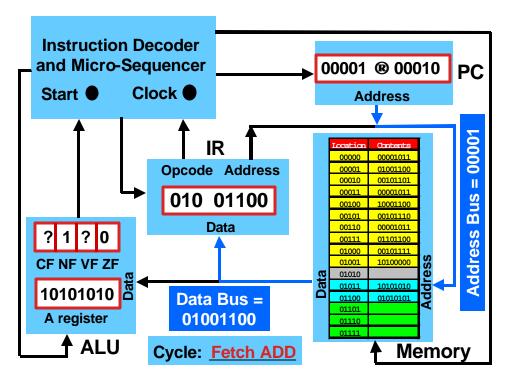

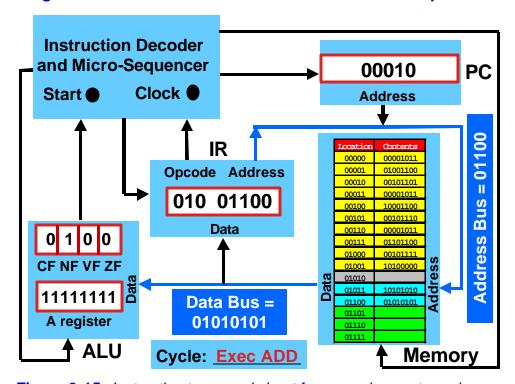

We are now ready for the second fetch cycle ("fetch ADD"), shown in Figure 2-14. Here, the instruction at memory location  $00001_2$  is fetched and placed into the IR, and as that occurs, the value in the PC is incremented by one. The results of executing the ADD instruction are shown in Figure 2-15. Here, the contents of memory location  $01100_2$  (i.e., the value  $01010101_2$ ) are added to the value previously loaded into the "A" register. A result of  $11111111_2$  is obtained, along with condition code bits CF = "0", NF = "1", ZF = "0", and VF = "0".

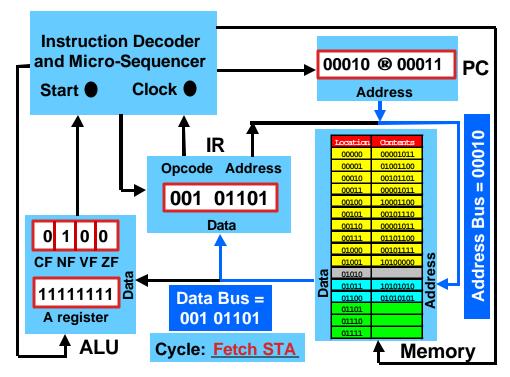

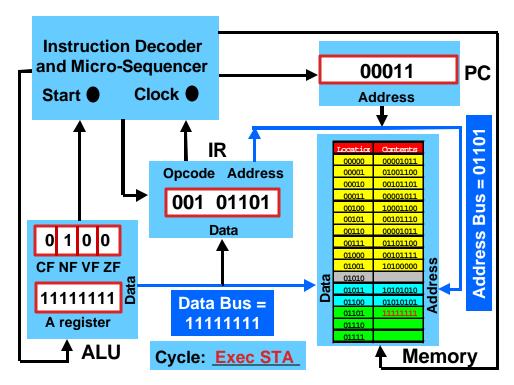

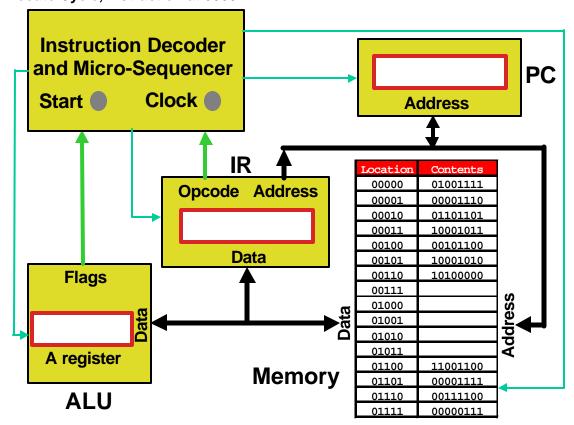

This brings us to the third fetch cycle ("fetch STA") of our tracing example, shown in Figure 2-16. Here, the instruction at memory location  $00010_2$  is fetched and placed into the IR, and as that occurs, the value in the PC is incremented by one. The results of executing the STA instruction are shown in Figure 2-17. Here, the contents of the "A" register are stored at the memory location indicated in the instruction's address field:  $01101_2$ . When the "execute STA" cycle is complete, then, memory location  $01101_2$  contains the value  $11111111_2$ . Note, however, that the "A" register as well as the condition code bits are unchanged.

Several observations are in order. First, all of our simple computer's fetch cycles are identical (i.e., they are independent of the instruction opcode). In fact, this has to be the case, since our machine basically knows nothing about the instruction being fetched until it is placed in the IR. Second, it may appear "strange" that our simple computer is incrementing the value in the PC on the same cycle that it is being used as a pointer to memory. Another way to say this is that the increment of PC is overlapped with the fetch of the instruction. The reason this can happen will become apparent when we start implementing each functional block in the next section. For now, though, suffice it to say that because each register will be implemented using edge-triggered flip-flops, the same clock edge that causes the IR to load the instruction being fetched also causes the PC to increment. The IR, though, will be loaded with the value on the data bus prior to the clock edge, while the value output by the PC (driving the address

*overlapped*

bus) will change *after* the clock edge – thus facilitating the desired overlap. This is an important point that we will revisit several times before the end of this chapter.

One final suggestion before we move to the "bottom-up" phase of our simple computer design process. Practice the "instruction tracing" process outlined in this section on other code segments to become more familiar with "what happens when" as each instruction is fetched and executed. As we say in the education industry, this is a "good test question" (GTQ)!

good test question

# 2.7 Bottom-Up Implementation of Simple Computer

Armed with a thorough understanding of how our simple computer works, we are now ready to start building it from the bottom-up. In practice, the preferred approach is to implement and test each block as it is designed. Then, when we put the various functional blocks together, we have a much better chance of the entire system working "the first time".

#### 2.7.1 Memory

The block we will start with is memory. Although most of the time we would simply choose a "memory chip" of appropriate size and speed, a knowledge of "what's under the hood" is essential to understanding how the various functional blocks of our simple computer work together.

First, some terminology. Normally, we think of memory as an entity that, from the computer's perspective, can be "read" or "written". In "read" mode, the memory unit simply outputs, on its data bus lines, the contents of the location indicated on its address bus inputs. In "write" mode, the memory unit stores the bit pattern present on its data bus lines at the location indicated on its address bus inputs. The correct acronym to describe such a "read/write memory" is RWM. Despite valiant efforts, the name RWM never caught on. Instead, it is more popular to refer to these devices as "random access memories" or RAMs – so-named because any (random) location can be accessed in the same amount of time (not because something random is read after a given value is written).

The specific type of RAM we wish to concentrate on here is *static* RAM, or SRAM. This is in contrast to *dynamic* RAM (DRAM), which

static RAM (SRAM) dynamic ram (DRAM) requires constant refreshing to retain information. (In DRAM, data is stored as a charge on a capacitor – since the charge dissipates over time, it must be periodically refreshed.) SRAM consists of a collection of D latches that will retain data (without the need for refreshing) as long as power is applied. Once power is turned off, however, all information previously stored in the SRAM is lost (this is referred to as a *volatile* memory).

volatile memory

In addition to address and data bus connections (where, for our simple computer, the address bus is 5-bits wide and the data bus is 8-bits wide), an SRAM needs three control signals. First, an SRAM needs an overall enable, typically called a "chip select" (CS) or "chip enable" (CE). This enable signal is needed to differentiate among multiple SRAMs or, as we will see later in this chapter, between memory and input/output devices. Second, an SRAM needs an output enable (OE) signal which, provided the SRAM is selected, turns on a series of three-state buffers that drive the data from the addressed location out onto the data bus. Finally, an SRAM needs a write enable (WE) signal which, if the SRAM is selected, opens the row of latches associated with the addressed location and allows it to take on the value presented to the SRAM on the data bus.

chip select (CS)

output enable

(OE)

write enable (WE)

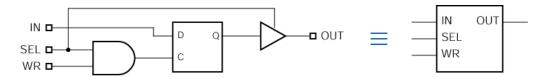

The basic building block of an SRAM is a memory cell, such as the one depicted in Figure 2-18, consisting of a D-latch and a three-state buffer. When the *select* (SEL) signal is asserted, the three-state buffer is enabled, placing the data stored in the latch on the cell's OUT line. When both SEL and WR are asserted, the latch opens and accepts the data present on the IN line (by virtue of asserting the latch enable or "C" input of the D-latch). When WR is negated, the latch closes and retains the new value.

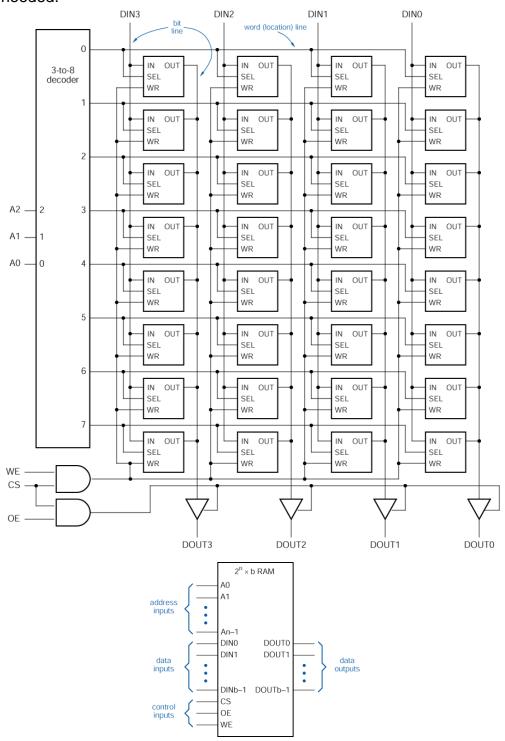

Figure 2-18 SRAM cell (adapted from Wakerly).

A complete SRAM can be constructed by combining an array of memory cells with a (large) decoder plus some additional logic. The internal structure of an eight location, 4-bit wide (or, "8x4") SRAM is shown in Figure 2-19. Note that the number of address lines needed is  $log_2(number\_of\_locations)$ ; here,  $log_2(8) = 3$ . Stated another way, the number of locations in an SRAM is  $2^n$ , where n is the number of

address lines. A "location" in the SRAM corresponds to a *row* of memory cells; to select a particular row, an n-to-2<sup>n</sup> binary decoder is needed.

memory location

Figure 2-19 SRAM internal structure and symbol (adapted from Wakerly).

#### GigaBiga Dittos

The prefixes K (kilo-), M (mega-), G (giga-), and T (tera-), when referring to memory sizes, mean  $2^{10}$  = 1024 ("about one thousand"),  $2^{20}$  = 1,048,576 ("about one million"),  $2^{20}$  = 1,073,741,824 ("about one billion"), and  $2^{40}$  = 1,099,511,627,776 ("about one trillion"), respectively. This brings up a very important question: Does this means the feared "Y2K bug" is yet to occur (in year 2048)? An even more important question, though, might be: Instead of calling a billion bytes a "gigabyte", wouldn't a better name be "bigabyte" (as in Biga (short for "Bigger") Bytes of Digital Wisdom, the subtitle for this text?

kilo-, mega-, giga-, tera-

bigabyte

In addition to a decoder, some logic is needed to "qualify" the actions associated with the OE and WE signals based on the assertion of CS (the overall chip enable). When WE is asserted in conjunction with CS, the data present on the DIN pins (DIN3 – DIN0) is written at the location specified on the address lines (note that the operation completes upon negation of the WE signal). When OE is asserted in conjunction with CS, the data output by a given row is routed to the three-state buffers that drive the external data lines.

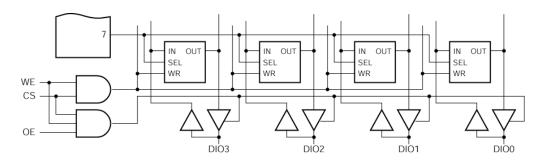

Since the read and write operations are mutually exclusive, however, there is usually no need for separate data input and output lines. Instead, the data input and output lines are tied together and connected to the rest of the system using a *bi-directional* data bus. Such a configuration is shown in Figure 2-20. Note that an additional buffer is used to receive the incoming data during a write operation, to reduce the load seen by the entity driving the bus.

bi-directional data bus

**Figure 2-20** SRAM bi-directional data bus (adapted from Wakerly).

Before moving on, a few notes concerning memory timing are in order. Because an SRAM read operation is a purely combinational function, the *order* in which the address and control signals (CS and OE) are asserted is of no consequence. As we will see in Chapter 5, though, each of these signals represents a *critical timing path* with respect to receiving valid data from memory on a read cycle:  $t_{AA}$  is the address access (propagation delay) time,  $t_{CS}$  is the chip select access time, and  $t_{OE}$  is the output enable access time. When interfacing an SRAM to a computer, all of these "read" paths need to be analyzed.

timing path  $t_{AA}$   $t_{CS}$   $t_{OE}$

critical

Since a "D" latch is used to store each bit of data in an SRAM, the *timing relationship* between the information on the address and data buses as well as the requisite control signals (CS and WE) is *more stringent* than for a read cycle. In particular, the address information needs to be stable, and the chip select (CS) needs to be asserted, for some time (t<sub>CW</sub>) before WE is asserted (opening the set of latches associated with the selected location). Also, the information supplied to the SRAM on the data bus must be stable t<sub>SETUP</sub> *prior to* the negation of the WE signal, and t<sub>HOLD</sub> *following* the negation of the WE signal. (These setup and hold timing parameters will be given specific names in Chapter 5.) The *consequence* of violating the data setup or hold timing specifications of an SRAM, or of not asserting the WE control signal for a sufficient period of time, is the *possibility of metastable behavior*. All of these "write"-related timing parameters need to be analyzed when interfacing an SRAM to a computer.

$t_{CW}$   $t_{SETUP}$   $t_{HOLD}$

metastable behavior

Returning to our simple computer, we note that by simply doubling the "width" of the SRAM depicted in Figure 2-19 (from 4-bits to 8-bits) and quadrupling the "length" (from 8 locations to 32 locations), as well as adding the bi-directional data bus interface shown in Figure 2-20, we will have the exact structure of SRAM needed. The only difference is the "unique" names we will use for our simple computer's memory control signals: "MSL" for the memory select signal, "MOE" for the memory output enable, and "MWE" for the memory write enable.

MSL MOE MWE

# 2.7.2 Program Counter

The next functional block we wish to address is the program counter (PC). Basically, this is nothing more than a (5-bit) binary "up" counter with an asynchronous reset and three-state outputs. The asynchronous reset (ARS) will be connected to the START pushbutton, so that the first instruction fetched is from location 00000<sub>2</sub>. There are two other control signals needed: one that enables the PC to increment by one when a low-to-high ("positive edge") of the system

**ARS**

CLOCK signal occurs, which we will call PCC; and one that turns on the three-state buffers that "gate" the value in the PC onto the address bus, which we will call POA. Note that if PCC is negated while a positive CLOCK edge occurs, the program counter should simply retain its current state.

PCC POA

To document the design of each functional block, we will present an ABEL ("Advanced Boolean Expression Language") source file. Those unfamiliar with the ABEL language and source file format should review the material presented on this subject in Chapter 1. The ABEL source file for the program counter module is shown in Table 2-3.

**ABEL**

#### **Table 2-3** Program counter module.

```

MODULE pc

'Program Counter Module'

TITLE

DECLARATIONS

CLOCK pin;

PC0..PC4 pin istype 'reg_D,buffer';

PCC pin; " PC count enable

POA pin; " PC output on address bus tri-state enable

ARS pin; " asynchronous reset (connected to START)

EQUATIONS

retain state count up by 1

PC0.d = !PCC&PC0.q # PCC&!PC0.q;

PC1.d = !PCC&PC1.q # PCC&(PC1.q $ PC0.q);

PC2.d = !PCC&PC2.q # PCC&(PC2.q $ (PC1.q&PC0.q));

PC3.d = !PCC&PC3.q # PCC&(PC3.q $ (PC2.q&PC1.q&PC0.q));

PC4.d = PCC&PC4.q # PCC&(PC4.q $ (PC3.q&PC2.q&PC1.q&PC0.q));

[PC0..PC4].oe = POA;

[PC0..PC4].ar = ARS;

[PC0..PC4].clk = CLOCK;

END

```

Examining the source file, we see that when PCC is negated, the next state is simply the current state. When PCC is asserted, the equations for a synchronous 5-bit binary "up" counter determine the next state. Assertion of POA causes the three-state buffers associated with each

IRL

**IRA**

register bit to be enabled, and assertion of ARS causes each flip-flop comprising the PC to be asynchronously reset.

#### 2.7.3 Instruction Register

The instruction register (IR) has a very simple mission: temporarily hold ("stage") the instruction fetched from memory so that it can be "peeled apart" and executed. As such, it is simply a series of D flipflops with two control signals. The first control signal, which we will call IRL, enables the instruction register to be loaded with the instruction read from memory; the load should occur on the positive edge of the system CLOCK. The second control signal, which we will call IRA, turns on the three-state buffers of the lower 5-bits of the IR, to "gate" the address field of the instruction onto the address bus.

**Table 2-4** Instruction register module.

```

MODULE ir

TITLE

'Instruction Register Module'

DECLARATIONS

CLOCK pin;

" IR4..IR0 connected to address bus

" IR7..IR5 supply opcode to IDMS

IR0..IR7 pin istype 'reg_D,buffer';

DB0..DB7 pin; " data bus

IRL pin; " IR load enable

IRA pin; " IR output on address bus enable

EQUATIONS

retain state

[IR0..IR7].d = !IRL&[IR0..IR7].q # IRL&[DB0..DB7];

[IR0..IR7].clk = CLOCK;

[IR0..IR4].oe = IRA;

[IR5..IR7].oe = [1,1,1];

END

```

Several items in the IR module source file, shown in Table 2-4, deserve explanation. First, when IRL is negated, note that the IR simply retains its current state. Second, note that, unlike the PC, there is no need to asynchronously reset the IR when the START pushbutton is pressed, since its (random) initial value is of no consequence. Finally, note that IRA only controls the three-state outputs associated with the lower 5-bits of the IR, and that the three-state buffers of the upper 3-bits (i.e., the opcode bits) are always enabled. The reason the three-state buffers associated with the upper 3-bits are always enabled is that they are connected *directly* to the IDMS module (i.e., they do not drive a bus). Recall that the IDMS uses the opcode bits to determine which system control signals are asserted on the next cycle, when the instruction is executed.

#### 2.7.4 Arithmetic Logic Unit

As mentioned earlier, the arithmetic logic unit (ALU) is so-named because it performs the arithmetic (add, subtract, etc.) and logical ("Boolean") operations defined by the instruction set. A "real" ALU performs a wide range of arithmetic and logical functions on operands stored in either registers or in memory. Fortunately, our ALU is relatively simple: it performs four different functions on a single register (which we have called the accumulator, or "A" register) and sets four condition code bits (or flags) based on the result obtained. As such, only four control signals are needed; an overall enable, which we will call ALE; two "function select" lines, which we will call ALX and ALY; and a three-state output enable for "gating" the value in the "A" register onto the data bus, which we will call AOE. The data bus interface must be bi-directional, in order to input data supplied by memory on LDA, ADD, SUB, and AND operations; and to output data to memory for STA operations. The condition code bits (CF, NF, VF, ZF) are output directly to the IDMS (we will see how these flags can be used to implement conditional transfer of control instructions later).

The ABEL source file for the simple computer ALU is shown in Tables 2-5, 2-6, and 2-7. Referring first to the declaration section (Tables 2-5 and 2-6), we note that signals used for "internal" purposes are declared as *nodes*. These include the carry bits and the combinational ALU outputs. In the declarations that continue in Table 2-6, the least significant bit carry-in (CIN) is defined as ALY. Noting that ALY is "0" for ADD and "1" for SUB, we realize this is exactly what is needed to add one to the diminished radix complement of the subtrahend (to obtain the radix complement) when performing a SUB operation.

arithmetic and logical operations

ALE ALX ALY

condition code bits

nodes

**Table 2-5** Declarations section of ALU module.

```

MODULE alu

TITLE 'ALU Module'

8-bit, 4-function ALU with bi-directional data bus

ADD: (Q7..Q0) \leftarrow (Q7..Q0) + DB7..DB0

SUB: (Q7..Q0) \leftarrow (Q7..Q0) - DB7..DB0

LDA: (Q7..Q0) <- DB7..DB0

AND: (Q7..Q0) <- (Q7..Q0) & DB7..DB0

OUT: Value in Q7..Q0 output on data bus DB7..DB0

AOE ALE ALX ALY Function CF ZF NF VF

0 1 0 0 ADD X X X X X 0 1 0 1 SUB X X X X

0 1 1 0 LDA

· x x ·

0 1 1 1 AND

· x x ·

X -> flag affected · -> flag not affected

" Note: If ALE = 0, the state of all register bits should be retained

DECLARATIONS

CLOCK pin;

" ALU control lines (enable & function select)

ALE pin; " overall ALU enable

AOE pin; " data bus tri-state output enable

ALX pin; " function select

ALY pin;

" Carry equations (declare as internal nodes)

CY0..CY7 node istype 'com';

" Combinational ALU outputs (D flip-flop inputs)

" Used for flag generation (declare as internal nodes)

ALU0..ALU7 node istype 'com';

" Bi-directional 8-bit data bus (also, accumulator register bits)

DB0..DB7 pin istype 'reg_d,buffer';

" Condition code register bits

CF pin istype 'reg_d,buffer'; " carry flag

VF pin istype 'reg_d,buffer'; " overflow flag

NF pin istype 'reg_d,buffer';    " negative flag

ZF pin istype 'reg_d,buffer';  " zero flag

```

**Table 2-6** Continuation of ALU source file declarations section.

```

" Declaration of intermediate equations

" Least significant bit carry-in (0 for ADD, 1 for SUB => ALY)

CIN = ALY;

" Intermediate equations for adder/subtractor SUM (S0..S7),

" selected when ALX = 0

S0 = DB0.q $ (DB0.pin $ ALY) $ CIN;

S1 = DB1.q $ (DB1.pin $ ALY) $ CY0;

S2 = DB2.q $ (DB2.pin $ ALY) $ CY1;

S3 = DB3.q $ (DB3.pin $ ALY) $ CY2;

S4 = DB4.q $ (DB4.pin $ ALY) $ CY3;

S5 = DB5.q $ (DB5.pin $ ALY) $ CY4;

S6 = DB6.q $ (DB6.pin $ ALY) $ CY5;

S7 = DB7.q $ (DB7.pin $ ALY) $ CY6;

" Intermediate equations for LOAD and AND,

" selected when ALX = 1

L0 = !ALY&DB0.pin # ALY&DB0.q&DB0.pin;

L1 = !ALY&DB1.pin # ALY&DB1.q&DB1.pin;

L2 = !ALY&DB2.pin # ALY&DB2.q&DB2.pin;

L3 = !ALY&DB3.pin # ALY&DB3.q&DB3.pin;

L4 = !ALY&DB4.pin # ALY&DB4.q&DB4.pin;

L5 = !ALY&DB5.pin # ALY&DB5.q&DB5.pin;

L6 = !ALY&DB6.pin # ALY&DB6.q&DB6.pin;

L7 = !ALY&DB7.pin # ALY&DB7.q&DB7.pin;

```

Intermediate equations for the full adder outputs (used for the ADD and SUB) functions as well as the "logical" functions (here, LDA and AND) are shown in Table 2-6. Note that the sole purpose of these intermediate equations is to simplify the task of writing the ALU equations. One can think of these as simply "definitions" (since they are part of the declaration section) of "symbols" that will be used in "higher level" equations.

The "real" equations start in Table 2-7. First are the carry equations that implement a simple ripple adder/subtractor. Next are the combinational equations that generate the ALU outputs based on the intermediate equations defined in Table 2-6. The data bus equations appear next; note that if ALE is negated, the "A" register retains its current state.

intermediate equations

#### **Table 2-7** Equations section of ALU source file.

```

EQUATIONS

" Ripple carry equations (CY7 is COUT)

CY0 = DB0.q&(ALY$DB0.pin) # DB0.q&CIN # (ALY$DB0.pin)&CIN;

CY1 = DB1.q&(ALY$DB1.pin) # DB1.q&CY0 # (ALY$DB1.pin)&CY0;

CY2 = DB2.q&(ALY$DB2.pin) # DB2.q&CY1 # (ALY$DB2.pin)&CY1;

CY3 = DB3.q&(ALY$DB3.pin) # DB3.q&CY2 # (ALY$DB3.pin)&CY2;

CY4 = DB4.q&(ALY$DB4.pin) # DB4.q&CY3 # (ALY$DB4.pin)&CY3;

CY5 = DB5.q&(ALY$DB5.pin) # DB5.q&CY4 # (ALY$DB5.pin)&CY4;

CY6 = DB6.q&(ALY$DB6.pin) # DB6.q&CY5 # (ALY$DB6.pin)&CY5;

CY7 = DB7.q&(ALY$DB7.pin) # DB7.q&CY6 # (ALY$DB7.pin)&CY6;

" Combinational ALU equations

ALU0 = !ALX&S0 # ALX&L0;

ALU1 = !ALX&S1 # ALX&L1;

ALU2 = !ALX&S2 # ALX&L2;

ALU3 = !ALX&S3 # ALX&L3;

ALU4 = !ALX&S4 # ALX&L4;

ALU5 = !ALX&S5 # ALX&L5;

ALU6 = !ALX&S6 # ALX&L6;

ALU7 = !ALX&S7 # ALX&L7;

" Register bit and data bus control equations

[DB0..DB7].d = !ALE&[DB0..DB7].q # ALE&[ALU0..ALU7];

[DB0..DB7].clk = CLOCK;

[DB0..DB7].oe = AOE;

" Flag register state equations

CF.d = !ALE&CF.q # ALE&(!ALX&(CY7 $ ALY) # ALX&CF.q);

CF.clk = CLOCK;

ZF.d = !ALE&ZF.q # ALE&(!ALU7&!ALU6&!ALU5&!ALU4&!ALU3&!ALU2&!ALU1&!ALU0);

ZF.clk = CLOCK;

NF.d = !ALE&NF.q # ALE&ALU7;

NF.clk = CLOCK;

VF.d = !ALE&VF.q # ALE&(!ALX&(CY7 $ CY6) # ALX&VF.q);

VF.clk = CLOCK;

END

```

Last, but not least, are the equations that govern the four condition code bits. All of these flags retain their current state if ALE is negated. The carry flag (CF) and overflow flag (VF) are only affected by the ADD and SUB instructions. For ADD, the CF bit is set to the carry out of the most significant position (here, CY7); for SUB, the CF bit is interpreted as a *borrow*, and is therefore set to the *complement* of the carry out of the sign position. The VF bit is simply the XOR of the *carry in* to the sign bit (CY6) with the *carry out* of the sign bit (CY7).

The negative flag (NF) and zero flag (ZF) are affected by all four functions implemented by our ALU. The NF bit is simply the sign bit (ALU7) of the result generated by the ALU, while the ZF bit is set to "1" if all the ALU result bits are zero.

Before moving on to the final block of our simple computer design, there is an important practical point worth noting. All of the functional blocks designed thus far – the memory, PC, IR, and ALU – can be independently implemented (or simulated) and tested (as well as debugged) before they are all "assembled together" into a completed computer. Independent testing and debugging of each functional block, in fact, is an important aspect of the "top-down, bottom-up" strategy we have espoused in this chapter.

independent testing and debugging

# 2.7.5 Instruction Decoder and Micro-sequencer

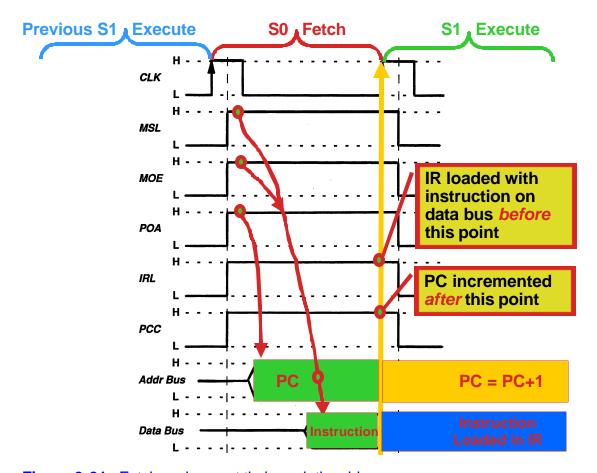

As described previously, there are two basic steps involved with "processing" each instruction, the combination of which is referred to as a micro-sequence. During a fetch cycle, the instruction pointed to by the PC is read from memory and loaded into the IR; the PC is incremented by one as the instruction is loaded. During the ensuing execute cycle, the instruction staged in the IR is "peeled" apart into an opcode field and an operand address field; the opcode field indicates the operation to be performed using data obtained from (or destined for) the memory location specified by the address field. The functional block that orchestrates the sequencing of these activities is called the instruction decoder and micro-sequencer (IDMS).

Since, in this initial version of our simple computer, there are only two different kinds of cycles (fetch and execute), a single flip-flop can be used as a state counter (SQ). In reality, this state counter is simply a single-bit binary counter (i.e., it simply toggles between "0" and "1"). Note that the state counter must be placed in the "fetch" state when START is pressed; therefore, it makes sense to assign the "reset" state

state counter (SQ)

toggles

of the SQ flip-flop (SQ=0) to the fetch cycle, and the "set" state of the SQ flip-flop (SQ=1) to the execute cycle.

With the structure of the state counter established, the next step is to determine which control signals (of the functional blocks designed previously) need to be asserted when SQ=0 (fetch) and SQ=1 (execute). To accomplish this, we will need to refer back to each of the previous sub-sections (on the design of the individual functional blocks) as well as the instruction tracing worksheets completed previously.

Referring again to Figure 2-12, we note that the following signals need to be asserted to complete a fetch cycle. First, to "gate" the value in the PC onto the address bus, the signal POA needs to be asserted by the IDMS. To read the instruction, the memory needs to be selected (MSL asserted) and its data bus output enabled (MOE asserted). To load the instruction read from memory into the IR, the signal IRL needs to be asserted. Finally, to increment the PC as the instruction is loaded, the signal PCC needs to be asserted. A total of five system control signals, therefore, needed to be asserted by the IDMS during a fetch cycle (when SQ=0): POA, MSL, MOE, IRL, and PCC.

The control signals that need to be asserted during an "ALU function" execute cycle (i.e., LDA, ADD, SUB, AND operation) can be inferred from Figure 2-13. First, to "gate" the operand address staged in the IR onto the address bus, the signal IRA needs to be asserted by the IDMS. To read the operand, the memory needs to be selected (MSL asserted) and its data bus output enabled (MOE asserted). To perform the operation specified by the instruction opcode (supplied to the IDMS from the upper 3-bits of the IR), ALE needs to be asserted along with the prescribed combination of ALX and ALY (based on the ALU design documented in Table 2-5).

The "store A" (STA) instruction execute cycle is similar, but notably different, than an "ALU function" execute cycle. Here, the address supplied to memory (from the IR, upon assertion of IRA) specifies the destination for the data in the "A" register. To complete the write to memory, it needs to be selected (MSL asserted) and write enabled (MWE asserted). To "gate" the data in the "A" register onto the data bus, AOE needs to be asserted. A total of four control signals need to be asserted, then, to execute a "store A" (STA) instruction: IRA, MSL, MWE, and AOE.

A succinct summary of all the system control signal assertions is provided in Table 2-8. Note that, for the sake of clarity, signal assertions are denoted using "H" (signals that are either negated or "don't care" are left blank). By way of contrast, the control signal negations that are effected by execution of the HLT (halt) instruction are denoted using "L".

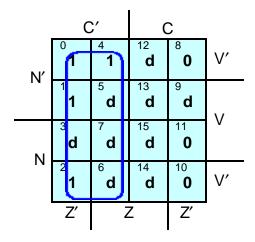

**Table 2-8** System control table.

| Decoded<br>State | Instruction<br>Mnemonic | MSL | MOE | MWE | PCC | POA | IRL | IRA | AOE | ALE | ALX | ALY |

|------------------|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| S0               | 3⁄4                     | Н   | Н   |     | Н   | Н   | Н   |     |     |     |     |     |

| <b>S</b> 1       | LDA                     | Н   | Н   |     |     |     |     | Н   |     | Н   | Н   |     |

| <b>S</b> 1       | STA                     | Н   |     | Н   |     |     |     | Н   | Н   |     |     |     |

| <b>S</b> 1       | ADD                     | Н   | Н   |     |     |     |     | Н   |     | Н   |     |     |

| S1               | SUB                     | Н   | Н   |     |     |     |     | Н   |     | Н   |     | Н   |

| <b>S</b> 1       | AND                     | Н   | Н   |     |     |     |     | Н   |     | Н   | Н   | Н   |