# USP-2 Hardware Manual

Version 1.4 — March 8, 2001

Themis Computer—Americas and Pacific Rim 3185 Laurelview Court Fremont, CA 94538, USA Phone (510) 252-0870 Fax (510) 490-5529 World Wide Web http://www.themis.com Themis Computer—Rest of World 20 rue du Tour de l'Eau 38400 St Martin d'Heres France Phone +33 476 59 60 46 Fax +33 476 59 60 49 Copyright © 2001 Themis Computer, Inc.

**ALL RIGHTS RESERVED.** No part of this publication may be reproduced in any form, by photocopy, microfilm, retrieval system, or by any other means now known or hereafter invented without the prior written permission of Themis Computer.

The information in this publication has been carefully checked and is believed to be accurate. However, Themis Computer assumes no responsibility for inaccuracies. Themis Computer retains the right to make changes to this publication at any time without prior notice. Themis Computer does not assume any liability arising from the application or use of this publication or the product(s) described herein.

**RESTRICTED RIGHTS LEGEND:** Use, duplication, or disclosure by the United States Government is subject to the restrictions set forth in DFARS 252.227-7013 (c)(1)(ii) and FAR 52.227-19.

#### TRADEMARKS

SOLARIS<sup>TM</sup> is a registered trademark of Sun Microsystems

UltraSPARC<sup>TM</sup> is a registered trademark of SPARC International

All other trademarks used in this publication are the property of their respective owners.

#### **Themis Customer Support**

North America, South America, and Pacific Rim

Telephone:510-252-0870Fax:510-490-5529E-mail:support@themis.comWeb Site:http://www.themis.com

*USP-2 Hardware Manual* March 8, 2001 Part Number: 108084

# Version Revision History

### Version 1.4: Miscellaneous typos and errors corrected. Also,

- Added VME bus addressing data-transfer mode tables..... page 2-6

- Modified audio parameters...... pages 3-3, 8-7

- Modified board jumper-pin diagrams...... pages 7-2, 7-3

- Divided Table 8-1 Signal Name column into Serial Port A and Port B ...... page 8-3

- Modified System Board VME P2 connector pin descriptions ...... pages 8-9, 8-10

### March 8, 2001

**Version 1.3**: Reorganized sections. Re-created "Reset" chapter. Added description of LED and Temperature monitoring in Chapter 4. Added paddle board diagram in Chapter 8. Fixed minor errors.

### June 30, 2000

**Version 1.2**: Misc. typos and errors corrected (Jumper 2001). Added jumper and front panel drawings

May 18, 1999

| Version 1.1: Misc. typos and errors corrected. | March 20, 1999 |

|------------------------------------------------|----------------|

| Version 1.0 (Rev X1.3): Preliminary            | May 30, 1998   |

iii

# Table of Contents

## 1 Introduction

2

3

| 1.1  | Introduction                                                                                                                                                                  | 1-1               |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1.2  | Scope                                                                                                                                                                         | 1-1               |

| 1.3  | USP-2 Systems Overview                                                                                                                                                        |                   |

| 1.4  | Getting Started                                                                                                                                                               |                   |

|      | <ul> <li>1.4.1 How to Start Quickly</li> <li>1.4.1.1 Product Warranty and Registration</li> <li>1.4.1.2 Unpacking the USP-2</li> <li>1.4.2 In Case of Difficulties</li> </ul> | 1-2<br>1-2<br>1-3 |

|      | 1.4.2 III Case of Difficulties                                                                                                                                                | 1-3               |

| Inst | allation                                                                                                                                                                      |                   |

| 2.1  | Registering                                                                                                                                                                   | 2-1               |

| 2.2  | Configuring the USP-2                                                                                                                                                         | 2-1               |

| 2.3  | Installing the USP-2 and its Paddleboard in the VME chassis                                                                                                                   |                   |

| 2.4  | Configuring The VME Interface                                                                                                                                                 | 2-3               |

|      | 2.4.1 VMEbus Memory Allocation                                                                                                                                                | 2-5               |

| 2.5  | Attaching the USP-2 To A Network                                                                                                                                              | 2-5               |

| 2.6  | Attaching a Keyboard and Mouse                                                                                                                                                | 2-5               |

| 2.7  | VME Bus Addressing Data-Transfer Modes                                                                                                                                        | 2-6               |

| USP  | P-2 Hardware Specifications                                                                                                                                                   |                   |

| 3.1  | Hardware and Performance Specifications                                                                                                                                       | 3-1               |

| 3.2  | Environmental Specifications                                                                                                                                                  |                   |

v

| 4 | Hardware Overview |

|---|-------------------|

|   |                   |

| 4.1  | Overview 4 |                                         |      |  |

|------|------------|-----------------------------------------|------|--|

| 4.2  | Themis     | USP-2 Block Diagram                     | 4-1  |  |

| 4.3  | UPA In     | UPA Interconnect                        |      |  |

|      | 4.3.1      | UPA Interconnect Overview               |      |  |

|      | 4.3.2      |                                         |      |  |

|      | 4.3.3      | UPA Address Bus                         | 4-5  |  |

|      | 4.3.4      | UPA Data Bus                            | 4-6  |  |

|      | 4.3.5      | UPA Arbitration                         | 4-6  |  |

|      | 4.3.6      | Processor Sub-system                    | 4-6  |  |

| 4.4  | Memory     | y System                                | 4-6  |  |

|      | 4.4.1      | System Controller (DSC)                 | 4-8  |  |

|      |            | 4.4.1.1 Port Interface Controller (PIF) | 4-8  |  |

|      |            | 4.4.1.2 Data Path Scheduler (DPS)       | 4-8  |  |

|      |            | 4.4.1.3 Memory Controller (MC)          | 4-8  |  |

|      |            | 4.4.1.4 EBus                            | 4-8  |  |

|      | 4.4.2      | Buffered Crossbar Chip (XB1)            | 4-8  |  |

| 4.5  | I/O Syst   | tem                                     | 4-9  |  |

|      | 4.5.1      | U2S                                     | 4-9  |  |

|      |            | 4.5.1.1 PIO Operation                   | 4-10 |  |

|      |            | 4.5.1.2 DVMA Operation                  | 4-10 |  |

|      |            | 4.5.1.3 Interrupt Dispatching           | 4-10 |  |

|      |            | 4.5.1.4 UPA Interface                   | 4-10 |  |

|      |            |                                         | 4-10 |  |

|      |            | 4.5.1.6 SBus Interface                  | 4-10 |  |

|      |            | 4.5.1.7 Streaming Buffer                | 4-10 |  |

|      |            |                                         | 4-11 |  |

|      |            |                                         | 4-11 |  |

|      | 4.5.2      |                                         | 4-11 |  |

|      | 4.5.3      |                                         | 4-11 |  |

|      | 4.5.4      |                                         | 4-12 |  |

|      | 4.5.5      | EBus Devices                            | 4-12 |  |

| 4.6  | RIC AS     | SIC                                     | 4-12 |  |

| 4.7  | USP-2 I    | Flow Diagram                            | 4-13 |  |

| 4.8  | User LE    | EDs                                     | 4-14 |  |

| 4.9  | Temper     | rature Monitoring                       | 4-14 |  |

| Rese | t          |                                         |      |  |

| 5.1 | Overvie | ew      |                  | 5-1 |

|-----|---------|---------|------------------|-----|

| 5.2 | Reset S | ources  |                  | 5-1 |

|     | 5.2.1   | Hardwar | e Reset Sources  | 5-2 |

|     |         | 5.2.1.1 | Power Supply POR | 5-3 |

|     |         | 5.2.1.2 | Push-button POR  | 5-3 |

5

|     |      | 5.2.1.3 Push-button XIR 5-                                   | -3            |

|-----|------|--------------------------------------------------------------|---------------|

|     |      | 5.2.1.4 Scan POR                                             | -3            |

|     |      | 5.2.1.5 Scan XIR                                             | -3            |

|     |      | 5.2.1.6 SYSRESET*                                            | -4            |

|     |      |                                                              | -4            |

|     |      |                                                              | -4            |

|     |      |                                                              | -4            |

|     |      |                                                              | -4            |

|     |      | L                                                            | -4            |

|     |      |                                                              | -4            |

|     | 5.3  | Effects of Resets                                            | -5            |

|     |      | J J                                                          | -5            |

|     |      | 1                                                            | -5            |

|     |      |                                                              | -6            |

|     |      |                                                              | -6            |

|     |      |                                                              | -6            |

|     |      |                                                              | -6            |

|     |      | 5.3.2.5 EBus 5-                                              | -6            |

| 6   | Cloc |                                                              |               |

| U I |      |                                                              | -1            |

|     | 6.1  |                                                              |               |

|     | 6.2  | 1                                                            | -1            |

|     | 6.3  |                                                              | -2            |

|     | 6.4  | Other Clocks                                                 | -3            |

| 7   | Jum  | per and Solder Bead Configurations                           |               |

|     | 7.1  | Overview                                                     | -1            |

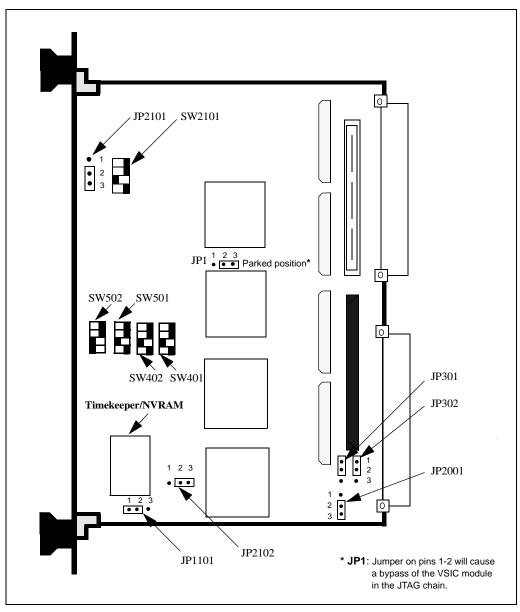

|     | 7.2  |                                                              | -2            |

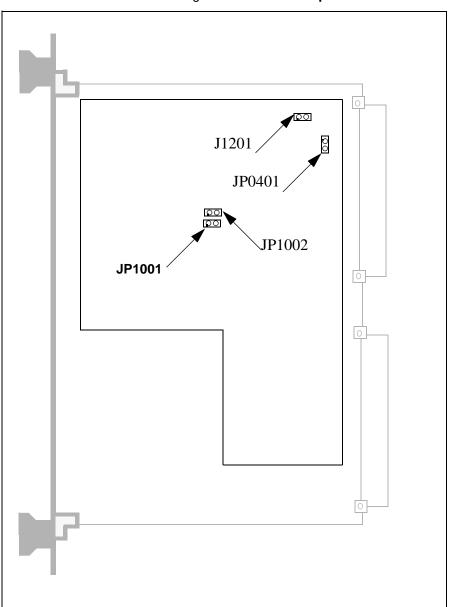

|     | 7.3  | 1                                                            | -5            |

|     | 7.4  | 6                                                            | -5            |

|     |      | •                                                            |               |

|     | 7.5  |                                                              | -6            |

|     | 7.6  |                                                              | -7            |

|     | 7.7  |                                                              | -8            |

|     | 7.8  | 5 I C                                                        | -8            |

|     | 7.9  | Flash Prom Settings   7-                                     | -9            |

|     | 7.10 | General Purpose DIP switch                                   | -9            |

|     | 7.11 | Printer/Floppy (available on the paddle board) Configuration | 10            |

| 8   | Conr | nectors and Pinouts                                          |               |

|     | 8.1  | Introduction                                                 | -1            |

|     | 8.2  |                                                              | -2            |

|     |      |                                                              | -3            |

|     |      |                                                              | $\mathcal{I}$ |

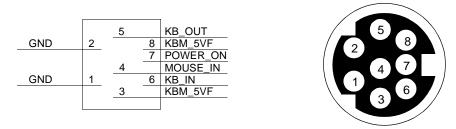

|     | 8.2.2<br>8.2.3<br>8.2.4 | Keyboard / Mouse Connector (Female)<br>Ethernet 100BaseTX A and B - RJ45 Connector<br>SCSI A and B Fast wide Connector (Female, High Density) | 8-4<br>8-4<br>8-5 |

|-----|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|     | 8.2.5                   | Audio Ports                                                                                                                                   | 8-7               |

| 8.3 | VME Co                  | onnectors                                                                                                                                     | 8-8               |

|     | 8.3.1                   | VMEbus P2 Connector (System Board)                                                                                                            | 8-9               |

|     | 8.3.2                   | VMEbus P1 Connector (I/O Board)                                                                                                               | 8-10              |

|     | 8.3.3                   | VMEbus P2 connector (I/O board).                                                                                                              | 8-12              |

| 8.4 | SBus Co                 | onnectors #1 and #2                                                                                                                           | 8-13              |

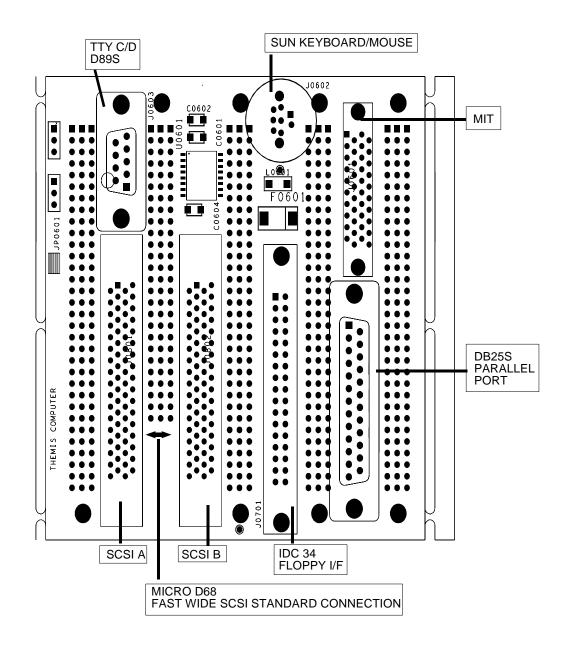

| 8.5 | Paddle b                | oard connectors                                                                                                                               | 8-14              |

|     | 8.5.1                   | Serial Ports C/D DB9 connector (J0603):                                                                                                       | 8-15              |

|     | 8.5.2                   | Fast wide SCSI port A and B (J0801 and J0802)                                                                                                 | 8-16              |

|     | 8.5.3                   | Parallel port (J0702)                                                                                                                         | 8-18              |

|     | 8.5.4                   | Floppy connector (J0701)                                                                                                                      | 8-18              |

# **Reader Comment Card**

# List of Figures

| Figure 2-1. | USP-2 Assembly                              | 2-3  |

|-------------|---------------------------------------------|------|

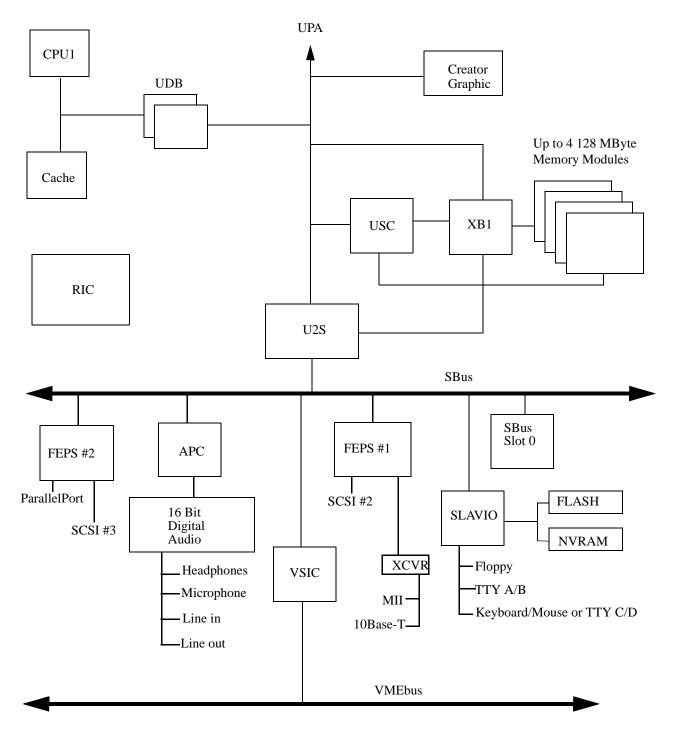

| Figure 3-1. | USP-2 System Board Block Diagram            | 4-2  |

| Figure 4-2. | UPA Interface Block Diagram                 | 4-4  |

| Figure 3-3. | Memory System Block Diagram                 | 4-7  |

| Figure 4-4. | I/O System Block Diagram                    | 4-9  |

| Figure 4-5. | USP-2 Flow Diagram                          | 4-13 |

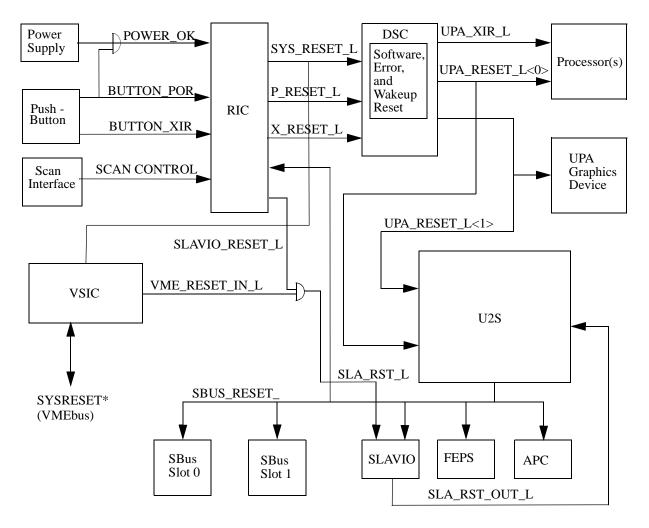

| Figure 5-1. | Reset Block Diagram                         | 5-2  |

| Figure 5-2. | Block Diagram                               | 5-7  |

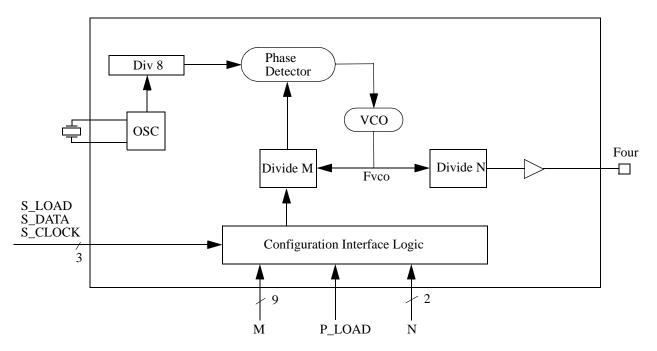

| Figure 6-1. | Simplified Block Diagram of Clock Generator | 6-2  |

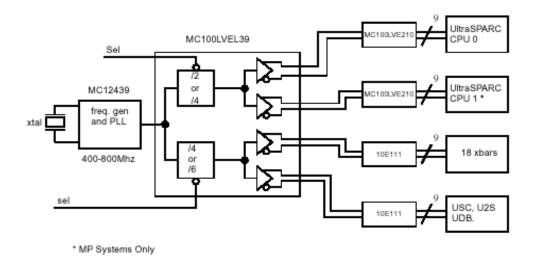

| Figure 6-2. | USP2 CPU and System Clock Schematic         | 6-3  |

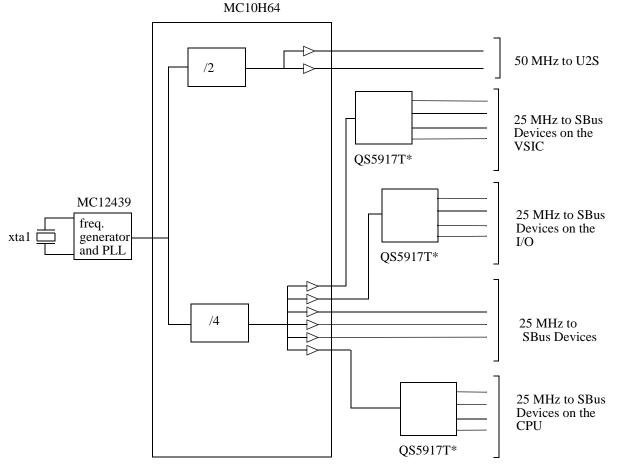

| Figure 6-3. | USP2 SBUS Clock Schematic                   | 6-4  |

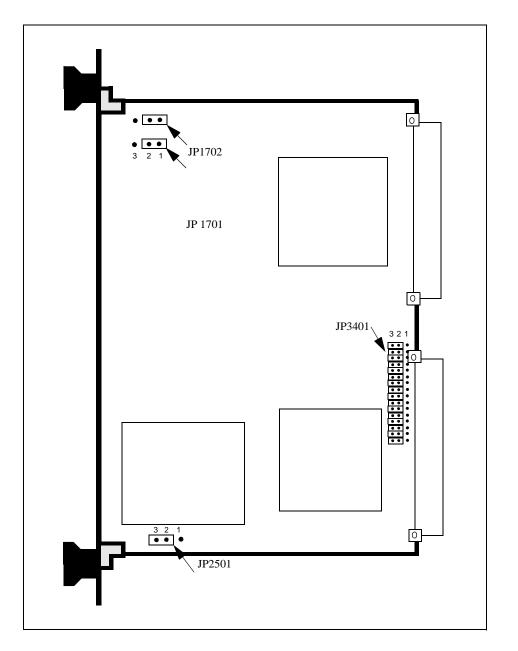

| Figure 7-1. | Base Board Jumpers                          | 7-2  |

| Figure 7-2. | I/O Board Jumpers                           | 7-3  |

| Figure 7-3. | VSIC Jumpers                                | 7-4  |

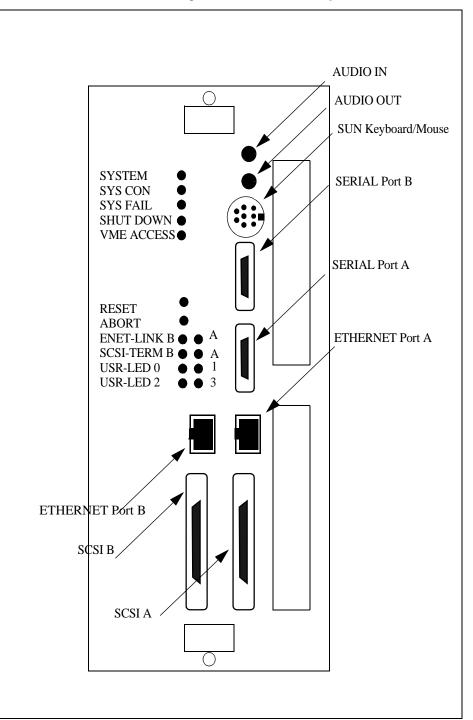

| Figure 8-1. | USP2 Front panel                            | 8-2  |

| Figure 8-2. | Keyboard / Mouse Connector Pinouts          | 8-4  |

| Figure 8-3. | 100Base-T Ethernet Connector Pinouts        | 8-4  |

| Figure 8-4. | SBus Connectors #1 and #2 Pinouts           | 8-13 |

| Figure 8-5. | Paddle Board Connectors                     | 8-14 |

X

# List of Tables

| Table 2-1. | VME Bus Addressing Data-Transfer Modes           | 2-6  |

|------------|--------------------------------------------------|------|

| Table 3-1. | USP-2 Hardware and Performance Specifications    | 3-1  |

| Table 3-2. | USP-2 Operating Environmental Specifications     | 3-4  |

| Table 3-3. | USP-2 Non-operating Environmental Specifications | 3-4  |

| Table 4-1. | UPA Port ID Assignments                          | 4-5  |

| Table 4-2. | Audio Specifications                             | 4-11 |

| Table 4-3. | LED Description                                  | 4-14 |

| Table 4-4. | Indicative Ambient Temperature Thresholds        | 4-15 |

| Table 5-1. | System Reset Effects                             | 5-5  |

| Table 6-1. | CPU to UPA Speed ratio                           | 6-2  |

| Table 7-1. | CPU Clock Settings                               | 7-5  |

| Table 7-2. | SCSI Interface Setting                           | 7-5  |

| Table 7-3. | Keyboard/Mouse, Ports C/D Settings               | 7-6  |

| Table 7-4. | Serial Port A and B settings                     | 7-7  |

| Table 7-5. | Ethernet 100 Base T Settings                     | 7-8  |

| Table 7-6. | VME Settings                                     | 7-8  |

| Table 7-7. | Flash Prom Settings                              | 7-9  |

| Table 7-8. | General Purpose DIP switch                       | 7-9  |

| Table 7-9. | Printer/floppy Configuration                     | 7-10 |

| Table 8-1. | Serial Ports A/B Connector Pinouts               | 8-3  |

| Table 8-2. | Keyboard / Mouse Connector Pinouts               | 8-4  |

| Table 8-3. | 100Base-T Ethernet Connector Pinouts             | 8-4  |

| Table 8-4. | Fast wide SCSI A and B Connector Pinout          | 8-5  |

| Table 8-5. | Audio Port Signals                               | 8-7  |

| Table 8-6. | Audio Port Functions                             | 8-7  |

| Table 8-7. | VMEbus P1 connector description (system board).  |      |

| Table 8-8. | VMEbus P2 connector description (system board)   | 8-9  |

| Table 8-9. | VMEbus P1 connector description (I/O board)      |      |

| Table 8-10. | VMEbus P2 connector description (I/O board) | 8-12 |

|-------------|---------------------------------------------|------|

| Table 8-11. | Serial Ports C/D DB9 connector              | 8-15 |

| Table 8-12. | Paddle board SCSI A and B connectors        | 8-16 |

| Table 8-13. | Paddle board parallel port                  | 8-18 |

|             | Paddle board floppy connector               |      |

# Introduction

1

# 1.1 Introduction

Thank you for purchasing the Themis USP-2 single board computer with VMEbus interface. Themis Computer is a leading manufacturer of SPARC based processor boards for the VMEbus market. We value our customers comments and concerns. Our Marketing department is eager to know what you think of our products. A "Reader Comment Card" is located at the end of this manual for your use.

**Caution** — Before you begin, carefully read each of the procedures in this manual. Improper handling can cause serious damage to the equipment.

# 1.2 Scope

The purpose of this document is to provide a hardware overview of the USP-2. This manual is written for system integrators and programmers. It contains all the necessary information to install and configure the USP-2 processor board. It is assumed that the Sun Open Boot PROM (OBP) is installed. If you intend to use another operating system or a real-time kernel such as VxWorks, please consult the appropriate documentation accompanying your OS or kernel software.

The reader is assumed to be familiar with and have a working knowledge of the UltraSPARC-II processor architecture and current VMEbus, SBus, Ethernet, and SCSI specifications. Although all USP-2 specific hardware and software features are described in detail in this manual, programmers wishing to code the USP-2 without the benefit of an operating system or real-time kernel will require additional data sheets and documentation for the system components comprising the USP-2 design.

# 1.3 USP-2 Systems Overview

The USP-2 is a high-end dual-processor desktop workstation based on Sun4u, formerly known as Sun5, system architecture.

Features of the USP-2 are

- Up to 2x64-bit V9 UltraSPARC-II processors.

- Use of Themis proprietary memory modules. Up to 2GB of memory.

- UPA coherent memory interconnect.

- Thermal management: The USP2 will shutdown if over-temp detected (2 thresholds)

- 2 RS232/RS422 serial ports (TTYA/TTYB) supporting both synchronous and asynchronous protocols. Available on the front panel.

- 2 asynchronous mode serial ports for SUN Type 5 keyboard or mouse interface that can be configured as 2 RS232 serial ports (TTYC/TTYD) on the P2 connector. Note that the SUN keyboard can be plugged on front panel or on the P2 paddle board.

- Centronic compatible parallel port interface. Available on the paddle board (P2)

- Built-in audio interface. Available on Front panel.

- 2 SBus expansion slots.(Only one is available in case of graphic configuration)

- DUAL Ethernet 10/100baseT.

- DUAL 20 Mbyte/sec fast and wide SCSI.

- VME64 Interface

**Note** — Themis distinguishes between two types of options: field options, which the customer may set in the field and factory options, which Themis sets before shipping the board or when the board is returned to Themis for re-configuration. Factory configurable options are not to be configured by the customer. An example of a field option is a jumper. An example of a factory option is a solder bead. Not all factory options are re-configurable and the customer should decide upon the desired configuration before shipment of the board.

# 1.4 Getting Started

### 1.4.1 How to Start Quickly

This document presents the Theory of Operation of the USP-2. It is intended to be a general purpose guide to the USP-2 for system architects, programmers, technicians, and other users. Technical discussions begin from an architectural perspective of a given topic and then proceed to those aspects of a general Sun architecture as it is implemented in the USP-2. board from a programmer's view. The information presented here is also written for the technician. In most cases, all that will be needed in the laboratory is this document and the appropriate toolkit. Finally the discussion retains a global view that is useful to a less technical user.

### 1.4.1.1 Product Warranty and Registration

Please review the computer warranty information packaged with your USP-2 processor board. Your USP-2 single board computer is automatically registered when it leaves the factory based on the information provided in the sales order. All computers are tracked via the serial number. The warranty service period is based on the original shipment date from the factory.

### 1.4.1.2 Unpacking the USP-2

**Caution** — The USP-2 contains statically sensitive components. Industry standard measures (use of a grounded wrist strap) must be observed when removing the USP-2 from it's shipping container and during any subsequent handling.

Remove the USP-2 and accessories from its shipping container and check the contents against the packing list. The package should include:

- Themis USP-2

- USP-2 Warranty Information

- Integration Kit (if ordered separately)

- Paddleboard

- A/B Serial Cable

- Front Panel SCSI Cable

- Flat Ribbon SCSI Cable

- USP-2 User Manual (if ordered separately).

Please report any discrepancies to the Themis Computer Customer Support department immediately.

### 1.4.2 In Case of Difficulties

Our Customer Support department is committed to providing the best product support in the industry. Customer support is available 8am - 5pm (PST), Monday through Friday via telephone, fax, e-mail or our World Wide Web site.

#### **Themis Customer Support**

Telephone: 510-252-0870 Fax: 510-490-5529 E-mail: support@themis.com Web Site: <u>http://www.themis.com</u>

2

# 2.1 Registering

Please review the Themis Computer warranty and complete the product registration card delivered with your UPS-2 board(s). Return of the registration card is not required to activate your product warranty but, by registering your USP-2, Themis Computer will be able to better provide you with timely updated information and product enhancement notifications.

At Themis Computer we value our customers comments and concerns. We have a marketing department that is eager to know what you think of our products and a customer support department that is committed to providing the best product support in the industry.

Customer support is available 8AM to 5PM PST, Monday through Friday via telephone, fax, email, or our web site.

**Customer Support:**

Phone: 510-252-0870 Fax: 510-490-5529

Email: support@themis.com

Web site: www.themis.com

# 2.2 Configuring the USP-2

Confirm the installation of all factory default jumpers. The default configuration is as follows:

- USP-2 as VME System Controller

- Keyboard/Mouse ports connect to front panel

- Active SCSI termination enabled on base and I/O boards

- Drive / Receive SYSRESET\*

- Serial Port A/B is EIA-232-E/EIA-423A compatible

- Boot from FLASH

- FLASH programming disabled

- Manual Ethernet port selection enabled

- Use normal twisted pair squelch threshold for 10BASE-T

- Bypass VMEbus interface in JTAG scan chain.

If the default jumper settings meet your requirements you are now ready to install the SPARC USP-2 in a standard VME chassis. To check the default configurations or if reconfiguration is required, refer to Chapter 4, Configurations and Options, for information concerning board jumper settings, solder bead, and memory configurations.

Note — If you are not installing the USP-2 as a system controller, jumper J1201 must be removed.

In addition to the USP-2 hardware a standard VME chassis with P1/P2 backplane is required. If you intend to use the USP-2 in a workstation configuration instead of as an embedded controller, you will also need a hard disk and graphics frame buffer or serial terminal.

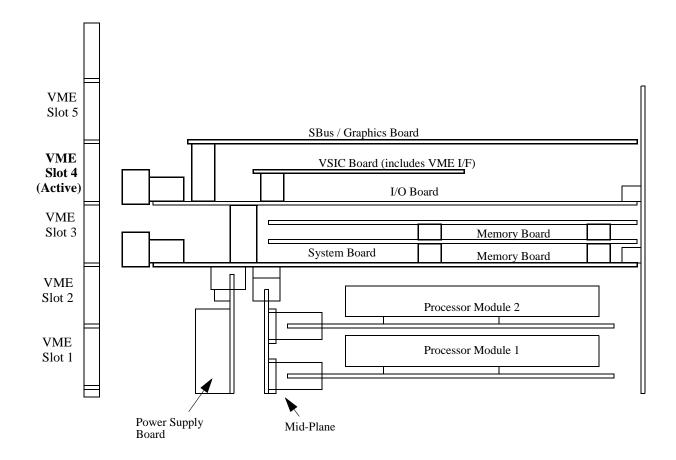

### 2.3 Installing the USP-2 and its Paddleboard in the VME chassis

The USP2 VME board takes 5 VME slots in width (see *Figure 2-1*). The "active" VME slot of the USP2 is slot #4; This means that the USP2 VME controller drives the VME signal from slot#4. In case you don't have an automatic jumpering VME chassis, this requires daisy chain signals to be jumpered on your VME chassis backplane. Failure to do so, may prevent proper interrupt and arbitration function in your VME chassis.

**Note:** If you are only planning to have "slave-only" VME boards, along with the USP2, you don't need to jumper any of those daisy chain signals:

- VME slot#1 IACKIN/OUT

- VME slot#2 IACKIN/OUT

- VME slot#3 IACKIN/OUT

- VME slot#4 : Do not place any daisy chain jumpers here

- VME slot#5 IACKIN/OUT

- VME slot#5 BUS GRANT0 IN/OUT

- VME slot#5 BUS GRANT1 IN/OUT

- VME slot#5 BUS GRANT2 IN/OUT

- VME slot#5 BUS GRANT3 IN/OUT

Figure 2-1. USP-2 Assembly

The *paddle board* is a daughter board that permits access to I/O signals on the back of the USP-2. This is done through the user defined pins (row A and row C) available on the USP-2 VME P2 connectors of the System board and the I/O board. The paddle board has 5 VME P2 connectors that plug opposite to the 5 slots occupied by the USP-2. It provides industry standard connectors for Serial Ports C and D, Ethernet, SCSI, and printer. It contains no statically sensitive components but should be handled with care to avoid bending pins on the connectors.

Caution — Always make sure the USP2 and the paddle board are properly aligned

Refer to Chapter 8, "Connectors and Pinouts", for a description of all connectors.

# 2.4 Configuring The VME Interface

Themis has implemented a variable and flexible VMEbus interface using both on-board jumpers, OpenBoot PROM (OBP) commands, and environment variables specific to the USP-2 board.

The USP-2 is typically reconfigured when VMEbus boards are added, removed, or changed in the chassis. Board configuration normally involves allocation of VMEbus master access address, interrupts, and slave base address of the USP-2.

A small number of VME interface capabilities are configured using jumpers or solder beads, including:

- the VMEbus System Controller capability

- the VMEbus isolation

All other VMEbus interface related options are configured using extensions to the Sun OpenBoot PROM monitor program. OBP stores system configuration parameters in non-volatile storage (NVRAM) using a setenv mechanism familiar to UNIX shell users.

The default configuration upon delivery of the USP-2 (or after restoring the factory default values by pressing L1-N) is:

- VME slave accesses disabled

- VME slave base address at 0x00

- Mailbox interrupts disabled

- Mailbox interrupt at CPU level 9.

The OBP command setenv must be used to set the values of the environment variables. The printenv command will list all supported environment variables and can be used to verify proper setting. You must be at the OpenBoot command prompt to enter and execute OpenBoot commands.

If autoboot is enabled, interrupt the boot sequence by pressing L1-A (STOP-A); on an serial terminal press BREAK.

If BOOTMON compatibility mode is enabled, you will initially see the BOOTMON prompt. Enter n to start OpenBoot:

| Type b (boot), c (continue), or n (new command mode) |  |

|------------------------------------------------------|--|

| >n                                                   |  |

| ok                                                   |  |

|                                                      |  |

At the ok prompt you are now able to enter OBP commands. Use setenv to modify the environment variables necessary to configure the USP-2 for your VMEbus configurations or execute the appropriate OBP commands listed above.

The following example moves the slave window for A32 accesses to 0x80000000 (decimal 2147483648) and enables slave accesses.

ok setenv vme32-slave-base 2147483648 ok

The OBP automatically programs the SCV64 interface chip with the correct register values and retains your settings in NVRAM. Please refer to the USP2 Programmer's manual for more information.

**Warning** — Unless you are familiar with the Forth Monitor and are experienced in interacting with your system PROM, restrict yourself to the most basic Forth Monitor operations. That is, to syncing your disks, ejecting floppies from the diskette drive, booting your system and configuring the VME interface. More advanced commands can do damage to your system's operation.

### 2.4.1 VMEbus Memory Allocation

The U2S SBus address space contains seven (7) physical SBus slots, with 256 MBytes assigned to each slot (Refer to USP-2 Programmer's Guide for the USP-2 Memory Map). Each slot is logically divided into sixteen (16), 16 MByte segments. Any unused 16 MByte segment may be mapped to the VMEbus address space through the VME MMU translation table located on the VSIC. Any segment allocated to the VMEbus can be programmed to access anywhere in the 4GByte VMEbus address space using any data path option supported

# 2.5 Attaching the USP-2 To A Network

The USP-2 features both a 10Base-T and AUI Ethernet interface connectors. OBP determines the active interface upon power-up.

After attaching the USP-2 to a network, you can verify proper physical connection by executing the FORTH network selftest (test net). This test will indicate external loopback failure on each of the network interfaces when there is not a proper physical connection. As only one interface can be active, the inactive network interface will always return an external loopback error.

ok test net Using AUI Ethernet Interface Lance Register test -- succeeded Internal loopback test -- succeeded External loopback test -- Lost Carrier (transceiver cable problem?) send failed Using TP Ethernet Interface Lance Register test -- succeeded Internal loopback test -- succeeded External loopback test -- succeeded send ok net selftest succeeded

# 2.6 Attaching a Keyboard and Mouse

A standard SUN type 4 or type 5 keyboard/mouse combination can be attached to the front panel keyboard connector or on the paddle board if you prefer to have it connected to the back of the board.

**Note** — The POST (power on self test) displays the message "Warning: no keyboard detected" if no keyboard is attached to the USP-2. This message may alternately indicate that configuration jumpers J0301 and J0302 (on the I/O board) are not configured for the front panel mouse/keyboard interface.

# 2.7 VME Bus Addressing Data-Transfer Modes

Table 2-1 describes the VME bus addressing data-transfer modes supported by the USP-2:

| Master     |     |     |     |  |

|------------|-----|-----|-----|--|

|            | A16 | A24 | A32 |  |

| D08        | Y   | Y   | Y   |  |

| D16        | Y   | Y   | Y   |  |

| D32        | N   | Y   | Y   |  |

| D32:BLT    | N   | Ν   | Ν   |  |

| MBLT (D64) | Ν   | Ν   | Ν   |  |

Table 2-1. VME Bus Addressing Data-Transfer Modes

| DMA     |     |     |     |

|---------|-----|-----|-----|

|         | A16 | A24 | A32 |

| D08     | Ν   | Ν   | Ν   |

| D16     | Ν   | Y   | Y   |

| D32     | Ν   | Y   | Y   |

| D32:BLT | Ν   | Y   | Y   |

| MBLT    | Ν   | Ν   | Y   |

| Slave   |     |     |     |

|---------|-----|-----|-----|

|         | A16 | A24 | A32 |

| D08     | Ν   | Y   | Y   |

| D16     | Ν   | Y   | Y   |

| D32     | Ν   | Y   | Y   |

| D32:BLT | Ν   | Y   | Y   |

| MBLT    | Ν   | Y   | Y   |

| D16:BLT | Ν   | Y   | Y   |

# USP-2 Hardware Specifications

3

This chapter describes these USP-2 specifications:

- Hardware and performance specifications

- Electrical power specifications

- Environmental specifications.

# 3.1 Hardware and Performance Specifications

### Table 3-1. USP-2 Hardware and Performance Specifications

| Physical Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                             |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|--|

| CPU Board Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6U                          |  |  |

| Number of VME slots taken:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5                           |  |  |

| CPU Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             |  |  |

| Number of Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | One or two UltraSparcII CPU |  |  |

| Estimated SPECint95 Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12.10 (est. single 300MHZ)  |  |  |

| Estimated SPECfp95 Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20.2(est. single 300MHZ)    |  |  |

| Estimated SPECint_rate95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 219 (est. dual 300MHZ)      |  |  |

| Power requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                             |  |  |

| The CPU modules utilizes a large amount of 3.3V power in addition to standard 5V. Since 3.3V is not distributed on standard VME backplanes, a pair of DC/DC converters are provided on board to convert 5V to 3.3V. The two converters generate 3.3V and 3.3V_CORE respectively. A five slot wide power and I/O distribution paddle board is connected to the P2 connectors of both boards at the rear of the backplane. This paddle board distributes additional 5V power to the boards via auxiliary power pins. An auxiliary power connector on the paddle board couples directly to the backplane power lugs, in order to deliver the required 5V power. Please contact factory for power requirement values. |                             |  |  |

| Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                             |  |  |

### Table 3-1. USP-2 Hardware and Performance Specifications

An on-board thermal sensor circuitry ensures that the USP2 functions at an acceptable temperature. The monitoring is done thru a thermistor placed on the CPU module. In case of over temperature, the system defines two thresholds:

Warning threshold: The thermal circuitry sends an interrupt to Solaris which prints the following message:

WARNING: Severe over-temperature condition detected!

WARNING: Powering down

THE SYSTEM IS BEING SHUT DOWN NOW!!!! Log off now or risk your files being damaged.

**Shutdown threshold:** The thermal circuitry will shutdown the DC TO DC converters that are powering the CPU modules. The front panel SHUTDOWN LED will be ON.

| Input / Output                                 |                                                                                                                                                                        |  |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SBus Slots                                     | Two physical slots (One only if Creator graphic option)                                                                                                                |  |

| SBus Standard                                  | SBus specifications, IEEE 1496 - 1993                                                                                                                                  |  |

| SBus Data Size                                 | 64-Bit Full Master / Slave                                                                                                                                             |  |

| Sbus Clock Rate                                | 25MHz                                                                                                                                                                  |  |

| SBus Write Sizes                               | Maximum 64-byte burst                                                                                                                                                  |  |

| Sbus Writes                                    | 64/32/16/8-byte burst mode supported                                                                                                                                   |  |

| SCSI Port #1                                   | A 68-pin, high density connector located on the front panel AND on the Paddle Board via the P2 (I/O).                                                                  |  |

| SCSI Port #2                                   | A 68-pin, high density connector located on the front panel AND on the Paddle Board via the P2 (I/O).                                                                  |  |

| SCSI Standard                                  | ANSI X3.133                                                                                                                                                            |  |

| SCSI Types                                     | Dual FAST/WIDE - 20MB/sec                                                                                                                                              |  |

| Ethernet #1 Connectors                         | RJ-45 jack for 10Base-T (twisted-pair)<br>Standard connector (T-bases 10/100) on the Front<br>Panel.<br>Standard connector (DB-15) on the Paddle Board via<br>P2 (I/O) |  |

| Ethernet #2 Connectors                         | #2 will be twisted-pair.                                                                                                                                               |  |

| Ethernet Standard                              | IEEE 802.3                                                                                                                                                             |  |

| Printer (Parallel)                             | DB-25 Connector on the Paddle Board via P2 (I/O)                                                                                                                       |  |

| Printer Standards                              | IEEE 1284                                                                                                                                                              |  |

| Serial A/B Ports                               | One 26-pin D-Sub                                                                                                                                                       |  |

| Serial Standard                                | EIA-232-E / EIA-423-A                                                                                                                                                  |  |

| Serial Types                                   | Synchronous / Asynchronous                                                                                                                                             |  |

| Serial Configuration                           | DTE                                                                                                                                                                    |  |

| Serial Performance                             | 19,200 (19.2-Kbit) baud<br>Hardware to 76.8 Kbaud<br>Solaris to 38.4 Kbaud                                                                                             |  |

| Keyboard / Mouse Port                          | 8-pin mini-circular jack                                                                                                                                               |  |

| Floppy Diskette Drive (Intel 82077 compatible) | 34-pin ribbon connector                                                                                                                                                |  |

| Audio Headphone       | Audio jack connector (stereo)<br>(EIA standard 3.5mm/0.125" jacks)                                                                                                                                                                                                                                                                |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Audio Line In         | Audio Jack connector (stereo)<br>(EIA standard 3.5mm/0.125" jacks)                                                                                                                                                                                                                                                                |  |

| Audio Performance     | Voice standard (8-bit, 8 Khz) and CD quality (16-bit,<br>48 Khz)                                                                                                                                                                                                                                                                  |  |

| On-board M            | lain Memory                                                                                                                                                                                                                                                                                                                       |  |

| Description of Memory | Up to 2 Modules mounted on top of the System board.<br>Any combination of 512 MBytes and 1 GByte modules<br>may be used.                                                                                                                                                                                                          |  |

| NVRAM / TOD Clock     | The module provides 8KB of NVRAM space<br>implemented via a SGS Thomson M48T59 hybrid<br>module. The module contains an encapulated lithium<br>cell for non-volatility.                                                                                                                                                           |  |

| PROM                  | The I/O Board provides mounting sites for two Flash<br>EPROM devices. It is intended that two 2MB devices<br>be used, providing a total of 4MB of Flash space.<br>The devices are sector erasable and operate from a<br>single 5V supply. The flash space is accessible on the<br>SBus through the Slave I/O ASIC as 8 bit space. |  |

|                       | A connector is provided on board which allows the<br>Flash EPROM to be factory programmed on board.<br>The device can also be reprogrammed over the<br>network or from CD-ROM, in the field, to support<br>upgrades to the OBP or Power Up Self Test.                                                                             |  |

| SBus                  |                                                                                                                                                                                                                                                                                                                                   |  |

| SBus Controller Chip  | Sun STP 2220BGA U2S ASIC                                                                                                                                                                                                                                                                                                          |  |

| SBus Connectors       | 2 Female SBus headers (Only one in graphic configu-<br>ration)                                                                                                                                                                                                                                                                    |  |

### Table 3-1. USP-2 Hardware and Performance Specifications

# 3.2 Environmental Specifications

*Table 3-2* and *Table 3-3* on page 3-4 contain the environmental specifications for the USP-2 under operating and non-operating conditions.

When measuring the operating environment air temperature for the USP-2, measure the air temperature as close to the air intake port on the enclosure as possible.

For cooling purposes, maximum air flow should be across the USP-2 board processor section, including the UltraSPARC processor, external cache SRAMS, and UDBs.

| Description                                             | Minimum Value          | Maximum Value             |

|---------------------------------------------------------|------------------------|---------------------------|

| Temperature Range                                       | 0 C                    | 50 C                      |

| Humidity Range (relative non-condensing at 104 F (40 C) | 5%                     | 95%                       |

| Wet Bulb Maximum                                        | Not applicable         | 77 F (25 C)               |

| Altitude Range                                          | 0 feet (0 meters)      | 10,000 feet (3,408meters) |

| Air Flow                                                | 300 lfm airfow at 50 C |                           |

### Table 3-2. USP-2 Operating Environmental Specifications

### Table 3-3. USP-2 Non-operating Environmental Specifications

| Description                                                  | Minimum Value     | Maximum Value              |

|--------------------------------------------------------------|-------------------|----------------------------|

| Temperature Range                                            | -40 C             | +85 C                      |

| Humidity Range (relative non-con-<br>densing at 104 F (40 C) | 5%                | 95%                        |

| Wet Bulb Maximum                                             | Not applicable    | 115 F (46 C)               |

| Altitude Range                                               | 0 feet (0 meters) | 38,370 feet (12000 meters) |

# Hardware Overview

4

### 4.1 Overview

This chapter provides a brief hardware overview of the USP-2. Detailed information about each component can be found in the respective component specification. Operations of individual peripheral devices will not be covered.

The UPA interconnect provides interconnection at the highest level. Components interfacing through the UPA interconnect are processor subsystem, System Controller, Buffered Crossbar Chip, memory, and I/O subsystem. Processor subsystem includes the UltraSPARC-II processor, E-cache Tag and Data RAM, and the UDBs. The System Controller provides overall control to the UPA interconnect and memory. The I/O subsystem consists of the SCV64, VMEbus, U2S, SBus slots, FEPS, SLAVIO, APC/CS4231, and other on-board devices. The RIC ASIC is independent of system interconnects. It provides JTAG, reset and clock control functions that are important to the system. The RIC ASIC communicates with other chips through direct interfaces.

### 4.2 Themis USP-2 Block Diagram

The CPU board at the block level is described below:

- Processor a dual-processor system with the processor subsystem on the CPU board.

- SBus Slots supports up to two external SBus slots.

- Memory Modules supports from one 512 MByte and up to two 1 GByte Memory Modules.

### 4.3 UPA Interconnect

**Note** — Throughout the UPA documentation, the term MID, master ID, is used. At times this is confusing because it is really a UPA *port* ID. For devices which are masters, there is no difference between port ID and master ID; however, devices which are slaves only have a port ID. Slave Devices can not have a Master ID. Port IDs are unique.

### 4.3.1 UPA Interconnect Overview

The UPA interconnect is a packet based, cache coherent interconnect. Non-coherent operations are also provided for accesses to I/O devices and other devices that do not support cache coherency. The physical connection among devices can be a bus or point to point. The USP-2 adopts multiple buses to achieve cost / performance requirements. The major components defined in the UPA Interconnects are UPA Ports, System Controller, Data Path and Memory. Physical connections among these devices are provided by Address Bus, Data Bus and Data Path Control, and Snoop Bus. A distributed arbitration algorithm is used to arbitrate among master ports sharing the same Address Bus. It is described in Chapter 3.3.5, UPA Arbitration.

Each UPA port can support one or more of the following functions: master, slave, interrupter, and interrupt receiver. A UPA master is a device capable of issuing UPA transactions to the interconnect. A UPA slave receives and services transactions requested by a UPA master or the System Controller. An interrupter is a device capable of generating interrupts to the interconnect and handling interrupt flow control as defined by the interconnect. An interrupt receiver is a device capable of handling interrupt and providing necessary flow control on interrupt packet across the interconnect.

The System Controller is the key element of the UPA interconnect. The services it provides are coherence control, memory control, datapath control, flow control, transaction ordering, and address routing. A brief description of the System Controller will be provided in a later section.

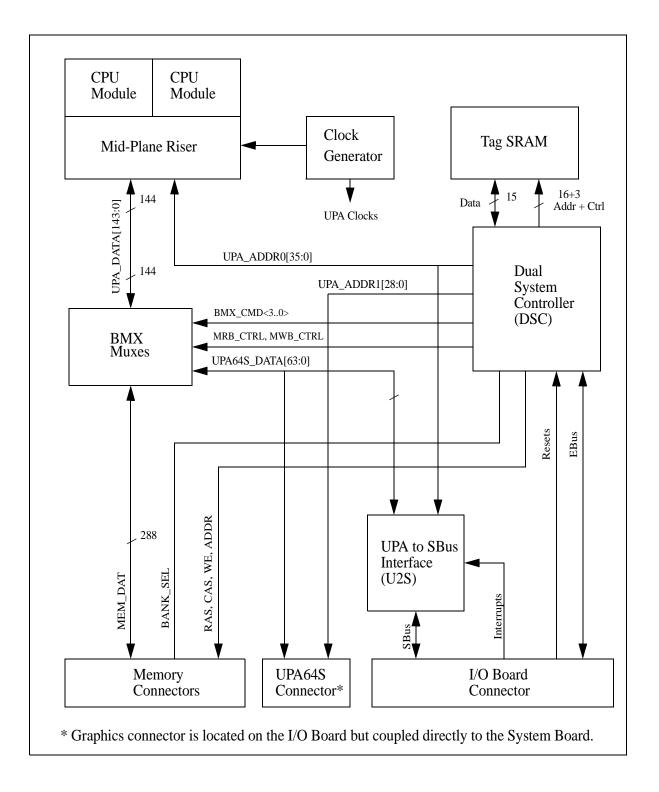

*Figure 4-2* shows the physical connections among UPA devices in the USP-2 system. The following sections provide introductory information about the UPA. For more detailed description of how the UPA works, please refer to 'UPA Interconnect Architecture'.

Figure 4-2. UPA Interface Block Diagram

### 4.3.2 UPA Data Transfer

Data transfers can happen between UPA devices or between a UPA device and memory. Data transfer is initiated by the master interface of a UPA port. The UPA port first asserts a request and waits for its turn to get the ownership of UPA Address Bus. It then sends a transaction request to the UPA Address Bus together with UPA\_Addr\_Valid signal. Examples of simplified data transfer operations are given here to help in understanding how the UPA works.

- Non-cacheable Read: The System Controller decodes the request packet and makes a transaction request to arbitrate for the address bus where the selected device resides. It then forwards the packet to the UPA slave. The UPA slave services the request and returns a P\_Reply to the System Controller when data is available or there is an error. The UPA slave must respond to the transaction request which is directed to it. Failing to do so may cause the system to hang. Based on the P\_Reply received, the System Controller schedules the datapath and sends a separate S\_Reply to both parties involved in the transaction. The S\_Reply tells the UPA slave to send data on the data bus and UPA master to receive data from the data bus.

- Non-cacheable Write: The System Controller forwards the request packet to the UPA slave. It then schedules the datapath and issues a separate S\_Reply to both UPA master and UPA slave. The S\_Reply tells the master port to drive data to its data bus and slave port to receive data from its data bus. Either the address packet or data can arrive to the slave port earlier than the other. If the slave port needs to use the data to schedule internal operations, it has to wait until data is received on its UPA port. After the slave port drains the data out of its UPA port interface, it can send a P\_Reply to the System Controller. The purpose of this P\_Reply is to provide flow control of data. It informs the System Controller that it has room for further incoming data. Precise transfer errors cannot be reported by a P\_Reply. The error will be dropped, or reported as an interrupt.

- Coherent Read: When the System Controller detects a coherent request, it will perform a snoop operation to the external dual tag if DTAG is provided. It also starts a memory request in parallel with snoop operation. In the case of a snoop miss, data will be provided by memory. The System Controller schedules the datapath based on the availability of memory data and issues S\_Reply to the requesting master. In the case of a snoop hit, the System Controller issues a copyback, or copyback invalidate request to the UPA port that owns the block. If the coherent read also requires invalidation of another cache, invalidate requests will be issued to other UPA ports that also have this block in their cache. When the UPA slave port is ready to send out copyback data, it issues a P\_Reply to the System Controller. If no invalidation is involved, the System Controller will schedule the datapath and issue a S\_Reply to both the UPA slave port and the UPA master port to send / receive data. Otherwise, the System Controller has to wait until all invalidate operations are completed before issuing a S\_Reply.

- **Coherent Write:** Coherent write requests are handled in the same fashion as coherent reads. The tag state is updated in the dual tags.

### 4.3.3 UPA Address Bus

The UPA Address Bus is a 35-bit wide packet-switched bus. The address bus is protected by a parity bit (UPA\_Address\_Parity). Odd parity is generated by the UPA masters; that is, the total number of bits, including parity, is odd. The UPA address bus carries transaction request packets generated by the master ports. The packet includes information such as transaction type, address, class, master ID (MID), and others.

Forty-one bits of physical address are carried in the packet, bits <40:4> come directly from the packet. Bits <3:0> can be derived from the 16 bits of Byte Mask field in the packet. The Master ID is a 5-bit field used to identify the master that initiated the transaction. Each slot gets its port ID from hardwired inputs to the UPA connector, from a software programmable register (in the case of U2S), or from its implicit location in the system. *Table 4-1* below shows the UPA Port ID assignments in the USP-2 system.

| UPA Slot Number  | UPA Port ID <4:0> |

|------------------|-------------------|

| Processor slot 0 | 0x0               |

| U2S              | 0x1F              |

| Processor slot 1 | 0x1               |

Table 4-1. UPA Port ID Assignments

The UPA interconnect allows multiple UPA address busses in the system. UPA address bus 0 is shared by the processor port(s) and U2S. The System Controller is the only master device on the bus. Arbitration among device in accessing the address bus 0 is described in a later section. The USP-2 may implement a second address bus used for graphics (I/O Graphic option).

The UPA interconnect uses geographical addressing to select the target device. Each port is assigned with an address range to respond to. The System Controller hardwires the address range of each UPA slave port and routes UPA packets to the proper destination. The UPA\_Address\_Valid signal is driven active to indicate a valid address on the address bus.

Associated with each address packet is a reply packet. There are two sets of reply signals for each UPA port: a UPA port reply and a System Controller reply. Each port has to supply dedicated UPA port reply signals to the System Controller. The System Controller also needs to supply each port with a dedicated System Controller reply signals. UPA protocol requires that each UPA device respond to the access targeted to its slave port. Failure to reply to a slave access may hang the system indefinitely. The encoding of replies is such that connected ports indicate a P\_REPLY code representing idle immediately after reset. Unconnected ports normally return a P\_REPLY code of "UPA read time out," if they are present. Ports which are present must return idle after being reset. Any other code is interpreted as device not present.

### 4.3.4 UPA Data Bus

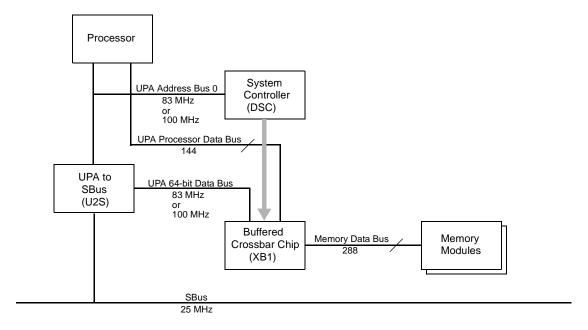

The UPA data bus provides data path connections between both UPA ports and memory and among UPA ports themselves. Three data busses, the processor data bus, the memory data bus, and the UPA 64-bit data bus, are implemented in USP-2 systems. They are interconnected by the Buffer Crossbar chip (XB1).

The Processor data bus is 144 bits wide with 128 bits of data and 16 ECC check bits. The Memory data bus, connecting the memory modules and the XB1 chip, is 288 bits wide with 256 bits of data and 32 ECC check bits. The UPA 64-bit data bus provides connection between the U2S and the XB1 chip. It is 72 bits wide with 64 bits of data and 8 ECC check bits.

### 4.3.5 UPA Arbitration

The UPA Interconnect uses a distributed arbitration protocol to decide which master port has the ownership of the UPA address bus. It allows a maximum of four UPA master ports and an System Controller port. Every master interface has its own arbitration logic and uses the same algorithm. The master interfaces run synchronously.

Each master port presents one request and that request is connected to all other master ports and the System Controller. The System Controller also provides a request that is connected to all the UPA master ports. System Controller requests have a higher priority than other ports in order to access the address bus if multiple requests are active at the same time. Among other master ports, the priority assignment is based on round-robin according to the value of current master. No matter which master port gets ownership of the bus, the value of current master is incremented by 1 and wraps around to 0 after it reaches 3. The current master has to give up the bus when another request is asserted.

### 4.3.6 Processor Sub-system

The USP-2 is a next-generation SPARC CPU incorporating, on chip, 16 KByte Instruction and 16 Kilobyte Data caches, integrated Level 2 cache management, a floating point unit, fixed point units, multi-instruction issue logic, and a 128-bit wide data bus.

The processor requires external synchronous SRAMs for the second level cache plus cache tags, and two data bus interface chips (UDBs). The processor complex is soldered onto the CPU Module Subsystem.

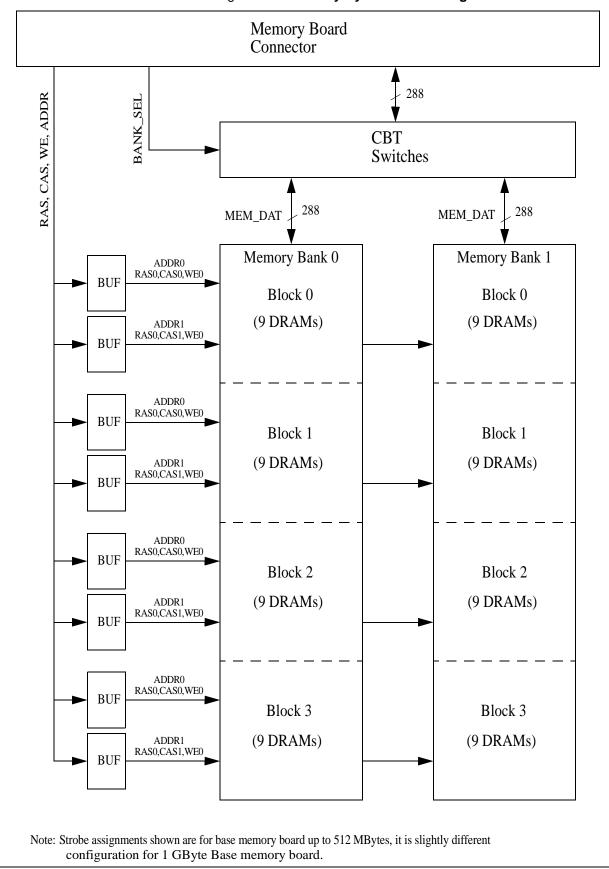

### 4.4 Memory System

The USP-2 memory system consists of three major components:

- the System Controller

- DRAM Memory Modules

- Buffered Crossbar Chips (XB1).

### 4.4.1 System Controller (DSC)

The System Controller contains several major blocks:

- Port Interface Controller (PIF)

- Data Path Scheduler (DPS)

- Memory Controller (MC)

- EBus.

### 4.4.1.1 Port Interface Controller (PIF)

This block of logic considers all UPA transactions and determines the intended target of the transaction. The PIF is responsible for the control flow for packets. It also performs the function of the Coherence Controller (CC).

### 4.4.1.2 Data Path Scheduler (DPS)

The Data Path Scheduler (DPS) controls all of the data flow in the machine coordinating the activity of the XB1 chips.

#### 4.4.1.3 Memory Controller (MC)

This block implements all of the memory control for the system. All operations affecting DRAM are contained in this block. These include sizing, timing, and refresh

#### 4.4.1.4 EBus

Since pins are limited on the DSC a low pin count interface was chosen. This block provides an interface to the generic bus. Reset functionality is located in this block.

### 4.4.2 Buffered Crossbar Chip (XB1)

The Buffered Crossbar Chip (XB1) is the hub of all data transfers in the system. It coordinates activity among memory (at 288 bits wide), the processor UPA bus (at 144 bits wide), and the system UPA bus (at 72 bits wide). Transfers can take place among any of the ports. To minimize the cost, the chip is bit-sliced such that 18 parts are required to implement a full connection to the system.

# 4.5 I/O System

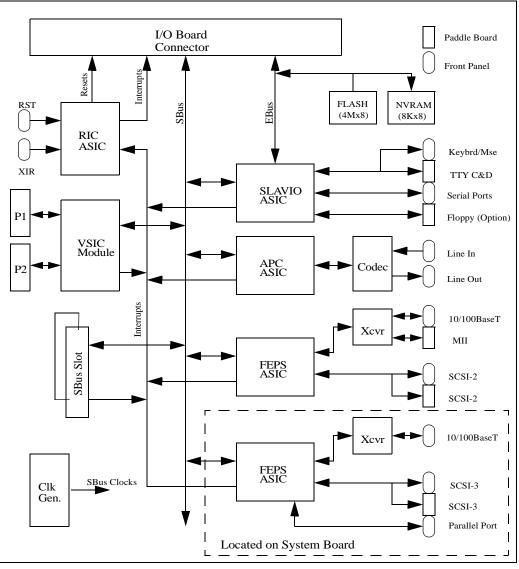

Figure 4-4. I/O System Block Diagram

### 4.5.1 U2S

The U2S is the bridge chip between the UPA and the SBus. In addition to providing simple bridge functions, it acts as the I/O hub and provides such necessary features as the IOMMU and Streaming Buffers. This is done to speed up sequential I/O accesses.

#### 4.5.1.1 PIO Operation

A processor which wishes to access the SBus makes a UPA request which is forwarded to the U2S. The U2S processes the request, and if it is intended for the SBus, routes it down to that bus. Write operations are buffered. Errors are reported asynchronously. Refer to Chapter 9 of the Programmer's Guide, Error Handling, for more details on the error behavior.

Note — Hardware detection of synchronization between DVMA writes and PIO reads to the SBus is not provided.

#### 4.5.1.2 DVMA Operation

All DMA transactions from SBus are actually DVMA transactions. This means that a virtual address is put on the SBus, and the U2S chip performs translation of that virtual address into a physical address recognized by the system. Translation is performed by the IOMMU. Bypass is provided for when translation is not desired.

#### 4.5.1.3 Interrupt Dispatching

All interrupts on the UPA are performed as transactions (packets). The U2S works in conjunction with the RIC ASIC to translate level sensitive interrupts into packets which are delivered to the processor. Registers are present to control the mapping between the physical interrupt wire, and the corresponding code delivered in the interrupt packet. Registers also control the target of the interrupt. Interrupt transactions which go out on the UPA will never pass DVMA transactions which occurred prior to the interrupt. DVMA transactions may pass an interrupt.

#### 4.5.1.4 UPA Interface

The U2S implements a 72 bit UPA interface.

#### 4.5.1.5 ECC Checking / Generation

All packets to or from the UPA have ECC. The U2S logic performs ECC generation and checking.

#### 4.5.1.6 SBus Interface

One of the major functions of the U2S is to bridge the UPA and SBus. It implements an IEEE P1496 compliant SBus interface.

#### 4.5.1.7 Streaming Buffer

Streaming Buffers perform read-ahead / write-behind transfers to speed up sequential I/O activity. The transfers act to buffer data on the way to or from memory.

### 4.5.1.8 IOMMU

As mentioned in § 4.5.1.2 DVMA Operation, the IOMMU performs translation between the virtual SBus address and a physical address. In addition, it supports bypass operation for devices not needing address translation, and pass through when not enabled.

### 4.5.1.9 Timer / Counter

Two Timer / Counters generate interrupts when the counter matches the programmed timer value and are useful for interrupting the system at specified intervals in the future. Two Timer / Counters are provided by the U2S.

## 4.5.2 FEPS #1 and #2

The FEPS chips implement the SBus interface to three master I/O devices: Ethernet, SCSI, and the parallel port. It contains three DMA channels implemented in its DMA2 block, one for each device supported.

Note — On FEPS #2, the parallel port is not supported.

## 4.5.3 Audio (APC)

The APC audio chip supports 16-bit digital audio along with an SBus interface. It provides an interface to a 16 bit CODEC with DMA.

The specifications below assume use of the Audio Tool format setting "CDROM" or "DAT" has been selected. The microphone input specifications are for the Sun Microphone II.

| Stereo             | Specifications                                                                     |

|--------------------|------------------------------------------------------------------------------------|

| Line In            | 2V typical, 4V max.; 5-50 ohm impedance                                            |

| Frequency Response | 20 Hz- 17 kHz +/-0.5 dB                                                            |

| Internal CD Input  |                                                                                    |

| Input Level        | 0.1 Vrms typical at 10 kohm; 2Vpp max.                                             |

| Distortion         | 0.01%, typical at 1kHz                                                             |

| S/N Ratio          | 84 dB, typical IEC 179 A-weighted                                                  |

| Frequency Response | 20 Hz-17 kHz +/-0.5 dB                                                             |

| Microphone Input   | 15mV typical, 0.6-1.0 kohm impedance;<br>+5 VDC input bias via a 2.2 kohm resistor |

| Headphones Output  | 1V typical, 2.4V max.; 16ohm- 1 kohm impedance                                     |

| Line Out           | 1V typical, 2.4V max.; 5-50 kohm impedance                                         |

Table 4-2. Audio Specifications

## 4.5.4 SLAVIO

The SLAVIO is an I/O chip implementing three slave devices on the SBus. These are the serial ports, a keyboard / mouse, and the floppy disk controller.

## 4.5.5 EBus Devices

Auxiliary devices not conveniently fitting into an existing chip are implemented on the 8-bit expansion bus called the 'EBus'. Devices found on this interface include the Flash EPROM, the NVRAM/TOD chip, the System Controller interface, and the frequency margining registers.

## 4.6 RIC ASIC

The RIC ASIC contains logic for dock generation, reset control, interrupt concentration, and JTAG control.

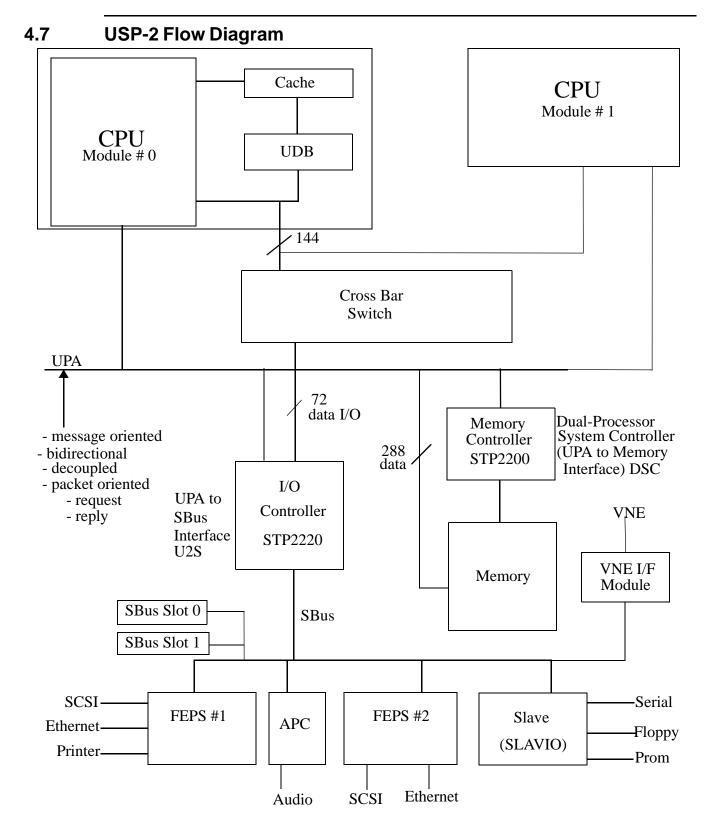

Figure 4-5. USP-2 Flow Diagram

# 4.8 User LEDs

The following table contains a description of the LEDs located on the front panel of the USP-2.

### Table 4-3. LED Description

| LED             | Description                                                                                                                                                                                                                                                                                                          | Color |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|