Series PMC424, APC424, AcPC424 24 Differential I/O and 16 TTL I/O with 4 Counter Timers

**USER'S MANUAL**

ACROMAG INCORPORATED 30765 South Wixom Road P.O. BOX 437 Wixom, MI 48393-7037 U.S.A.

Copyright 2003, Acromag, Inc., Printed in the USA.

Data and specifications are subject to change without notice.

8500-709-D10B008

Tel: (248) 624-1541 Fax: (248) 624-9234

# TABLE OF CONTENTS

#### **IMPORTANT SAFETY CONSIDERATIONS**

You must consider the possible negative effects of power, wiring, component, sensor, or software failure in the design of any type of control or monitoring system. This is very important where property loss or human life is involved. It is important that you perform satisfactory overall system design and it is agreed between you and Acromag, that this is your responsibility.

### 1.0 General Information

The information of this manual may change without notice. Acromag makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Further, Acromag assumes no responsibility for any errors that may appear in this manual and makes no commitment to update, or keep current, the information contained in this manual. No part of this manual may be copied or reproduced in any form without the prior written consent of Acromag, Inc.

|     | KEY 424 FEATURES PCI INTERFACE FEATURES SIGNAL INTERFACE PRODUCTS Board DLL Control Software Board VxWORKS Software Board QNX Software | 4<br>6<br>7<br>7 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 2.0 | PREPARATION FOR USE                                                                                                                    | •                |

|     | UNPACKING AND INSPECTION                                                                                                               | 8                |

|     | CARD CAGE CONSIDERATIONS                                                                                                               | 8                |

|     | BOARD CONFIGURATION                                                                                                                    | 8                |

|     | Default Hardware Jumper Configuration                                                                                                  | 8                |

|     | Front Panel I/O                                                                                                                        | 9                |

|     | Rear J4 Field I/O Connector (PMC Only)                                                                                                 | 10               |

|     | Non-Isolation Considerations                                                                                                           | 10               |

| •   |                                                                                                                                        |                  |

| 3.0 | PROGRAMMING INFORMATION                                                                                                                |                  |

|     | PCI CONFIGURATION ADDRESS SPACE                                                                                                        | 11               |

|     | Configuration registers                                                                                                                | 11               |

|     | MEMORY MAP                                                                                                                             | 12               |

|     | Interrupt Register                                                                                                                     | 14               |

|     | Interrupt Status/Clear Counter/Timer                                                                                                   | 15               |

|     | Interrupt Status/Clear Differential I/O                                                                                                | 15               |

|     | Interrupt Status/Clear Digital I/O                                                                                                     | 16               |

|     | Differential Input/Output Registers                                                                                                    | 16               |

|     | Digital Input/Output Registers                                                                                                         | 17               |

|     | Direction Control Register                                                                                                             | 17               |

|     | Interrupt Enable Registers                                                                                                             | 18               |

|     | Interrupt Type Configuration Registers                                                                                                 | 18               |

|     | Interrupt Polarity Registers                                                                                                           | 19               |

|     | Debounce Duration Select & Enable                                                                                                      | 20               |

|     | Counter Trigger Register                                                                                                               | 21               |

|     | Counter Stop Register                                                                                                                  | 21               |

|     | Counter Readback Registers                                                                                                             | 22               |

|     | Counter Constant A Registers                                                                                                           | 22               |

|     | Counter Constant B Registers                                                                                                           | 22               |

|     | Counter Control Registers                                                                                                              | 23               |

|     | Pulse Width Modulation                                                                                                                 | 24               |

|     | Watchdog Timer Operation                                                                                                               | 26               |

|     | Event Counting Operation                                                                                                               | 28               |

| Frequency Measurement OperationInput Pulse Width Measurement | 30<br>32 |          |

|--------------------------------------------------------------|----------|----------|

| Input Period Measurement                                     | 34       | TABLE OF |

| One-Shot Pulse Mode                                          | 36       | CONTENTS |

| PROGRAMMING EXAMPLES                                         | 38       | CONTENTS |

| Pulse Width Modulation Example                               | 38       |          |

| Watchdog Timer Operation Example                             | 39       |          |

| Event Counting Operation Example                             | 40       |          |

| Frequency Measurement Operation Example.                     | 42       |          |

| Input Pulse Width Measurement Example                        | 43       |          |

| Input Period Measurement Example                             | 45       |          |

| One-Shot Pulse Mode Example                                  | 46       |          |

| 4.0 THEORY OF OPERATION                                      |          |          |

| LOGIC/POWER INTERFACE                                        | 49       |          |

| PCI INTERFACE LOGIC                                          | 49       |          |

| DIGITAL INPUT/OUTPUT LOGIC                                   | 49       |          |

| COUNTER TIMER CONTROL LOGIC                                  | 49       |          |

| 5.0 SERVICE AND REPAIR                                       |          |          |

| SERVICE AND REPAIR ASSITANCE                                 | 50       |          |

| PRELIMINARY SERVICE PROCEDURE                                | 50       |          |

| WHERE TO GET HELP                                            | 50       |          |

| 6.0 SPECIFICATIONS                                           |          |          |

| PHYSICAL                                                     | 51       |          |

| ENVIRONMENTAL                                                | 51       |          |

| RELIABILITY PREDICTION                                       | 53       |          |

| DIFFERENTIAL INPUT/OUTPUT                                    | 53       |          |

| DIGITAL INPUT/OUTPUT                                         | 54       |          |

| COUNTER CLOCK FREQUENCIES                                    | 55       |          |

| BOARD CRYSTAL OSCILLATOR                                     | 55       |          |

| PCI LOCAL BUS INTERFACE                                      | 55       |          |

| APPENDIX                                                     |          |          |

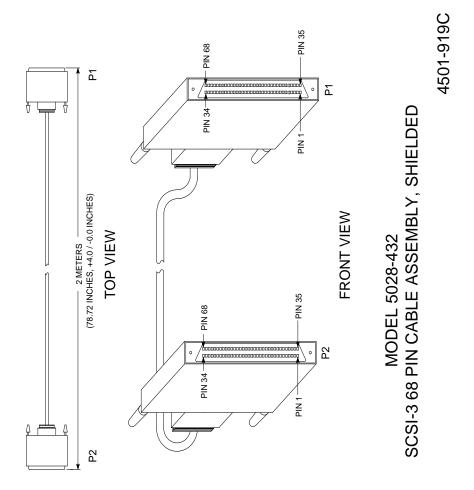

| CABLE: MODEL 5028-432                                        | 56       |          |

| TERMINATION PANEL: MODEL 5025-288                            | 56       |          |

| DRAWINGS                                                     |          |          |

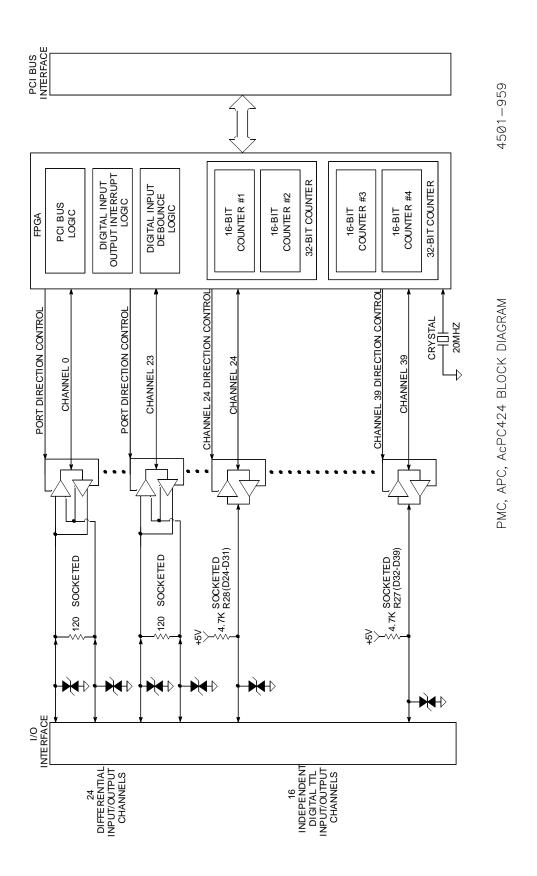

| 4501-959 424 BLOCK DIAGRAM                                   | 57       |          |

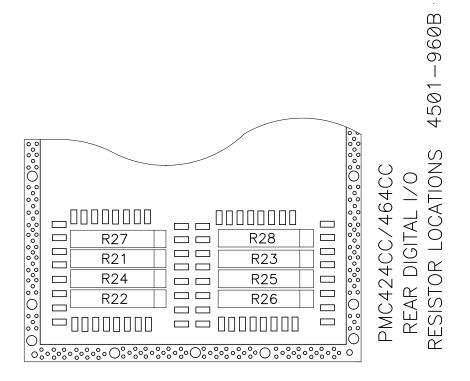

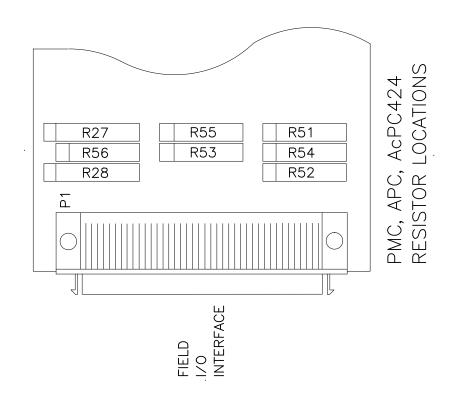

| 4501-960 424 RESISTOR LOCATION                               | 58       |          |

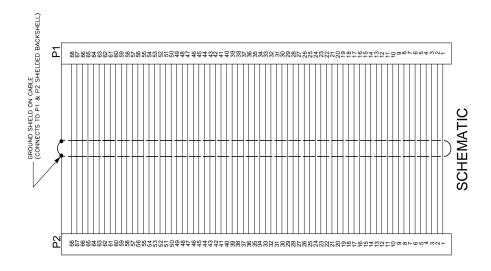

| 4501-919 CABLE 5028-432 (SHIELDED)                           | 59       |          |

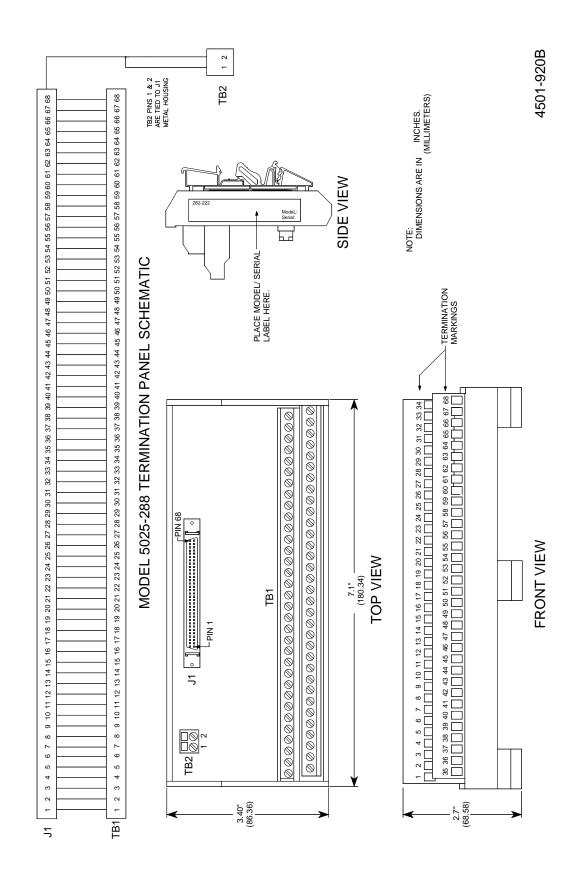

| 4501-920 TERMINATION PANEL 5025-288                          | 60       |          |

Trademarks are the property of their respective owners.

# 1.0 GENERAL INFORMATION

The 424 board has 24 differential input/output and 16 digital input/output channels. In addition, four 16-bit multifunction counter/timers are provided.

The 16 digital input/output channels can be programmed for input or output on a channel basis and are used for counter timer control. The 24 differential input/output channels are programmed for input or output on a 4-channel port basis. All input channels can be enabled for change of state, low, or high level transition interrupts.

Four 16-bit multifunction counters/timers can be configured for pulse width modulated output, watchdog timer, event counter, frequency measurement, pulse width measurement, period measurement, or one shot pulse output. The four 16-bit counters can also be configured into two 32-bit counter/timers.

Signal input noise spikes can be filtered with use of the debounce logic provided on each of the input channels.

**Table 1.1:** The 424 boards are available in standard and extended temperature ranges

| MODEL    | Board Form<br>Factor             | 16-bit<br>Counter | I/O Type             | OPERATING<br>TEMPERATURE<br>RANGE   |

|----------|----------------------------------|-------------------|----------------------|-------------------------------------|

| PMC424   | PCI Mezzanine<br>Card            | Four              | 24 Differ.<br>16 TTL | 0°C to +70°C                        |

| PMC424R  | PCI Mezzanine<br>Card (Rear I/O) | Four              | 24 Differ.<br>15 TTL | 0°C to +70°C                        |

| APC424   | Short PCI                        | Four              | 24 Differ.<br>16 TTL | 0°C to +70°C                        |

| AcPC424  | 3U CompactPCI                    | Four              | 24 Differ.<br>16 TTL | 0°C to +70°C                        |

| PMC424E  | PCI Mezzanine<br>Card            | Four              | 24 Differ.<br>16 TTL | -40°C to +85°C                      |

| PMC424CC | PCI Mezzanine<br>Card (Rear I/O) | Four              | 24 Differ.<br>15 TTL | -40°C to +85°C<br>Conduction Cooled |

| APC424E  | Short PCI                        | Four              | 24 Differ.<br>16 TTL | -40°C to +85°C                      |

| AcPC424E | 3U CompactPCI                    | Four              | 24 Differ.<br>16 TTL | -40°C to +85°C                      |

Note: PMC424R and PMC424CC are rear field I/O models, only. All other models have front I/O. The PMC424RE model is replaced by the PMC424CC model.

#### **KEY 424 FEATURES**

- 16 Digital Input/Output Channels Interface with up to 16 input/output channels (15 Rear I/O channels for PMCxxxR models) which can be configured for input or output on an individual channel basis. Four of these signals are used for each enabled counter/timer.

- **24 Differential Input/Output Channels** 24 channels of differential RS422 can be configured for input or output in groups of 4-channels.

- Programmable Change of State/Level Interrupts Interrupts are software programmable for any bit Change-Of-State or level on all input channels.

- Input Signal Filtering Debounce Logic Input signals can be filtered from noise spikes. Four programmable debounce filter durations from 1.6μs to 3.2ms can be selected.

• Pulse Width Modulation – Each counter can be programmed for pulse width modulation. The duration of the logic high and low levels of the output signal can be independently controlled. An external gate signal can also be used to start/stop generation of the output signal.

# **KEY 424 FEATURES**

- Watchdog Timer Each counter can be configured as a countdown timer for implementation as a watchdog timer. A gate-off signal is available for use to stop the count down operation. Interrupt generation upon a countdown to zero condition is available.

- Event Counter Each counter can be configured to count input pulses or events. A gate-off signal is provided to control count-up or count down with each event. Interrupt generation upon programmed count condition is available.

- Frequency Measurement Each counter can be configured to count how many active edges are received during a period defined by an external count enable signal. An interrupt can be generated upon measurement complete.

- Pulse-Width or Period Measurement Each counter can be configured to measure pulse-width or waveform period. In addition, an interrupt can be generated upon measurement complete.

- One-Shot and Repetitive One-Shot A one-shot pulse waveform may also be generated by each counter. The duration of the pulse and the delay until the pulse goes active is user programmable. A repetitive one-shot can be initiated with repetitive trigger pulses.

- **Power Up and System Reset is Failsafe** For safety, the digital channels are configured for input upon power-up.

#### **PCI INTERFACE FEATURES**

- High density Target board.

- Field Connections All counter/timer, digital I/O, and power connections are made through a single 68-pin SCSI front panel I/O connector. Models PMC424R and PMC424CC, only use a 64 pin rear I/O connector.

- **32**, **16**, **8-bit I/O** Register Read/Write is performed through data transfer cycles in the PCI memory space. All registers can be accessed via 32, 16, or 8-bit data transfers.

- Compatibility Complies to PCI Local Bus Specification Revision 2.2.

Provides one multifunction interrupt. Board is 5V signaling compliant and 3.3V signaling tolerant.

### SIGNAL INTERFACE PRODUCTS

The following signal interface products are for front I/O models which are accessed via a 68 pin SCSI-3 front panel connector.

Cables and a termination panel are also available to interface with this board.

#### Cable:

Model 5028-432: A 2-meter, round 68 conductor shielded cable with a male SCSI-3 connector at both ends and 34 twisted pairs. The cable is used for connecting the board to Model 5025-288 termination panels. For optimum performance, use the shortest possible length of shielded input cable.

See the Appendix for further information on these products.

#### **Termination Panel:**

Model 5025-288: DIN-rail mountable panel provides 68 screw terminals for universal field I/O termination. Connects to Acromag board, via SCSI-3 to twisted pair cable described above.

Acromag provides a software product (sold separately) to facilitate the development of Windows (98/Me/NT4/2000/XP®) applications accessing Acromag PMC I/O board products, PCI I/O Cards, and CompactPCI I/O Cards. This software (Model PCISW-API-WIN) consists of low-level drivers and Windows 32 Dynamic Link Libraries (DLLs) that are compatible with a number of programming environments including Visual C++TM, Visual Basic®, Borland C++ Builder® and others. The DLL functions provide a high-level interface to boards eliminating the need to perform low-level reads/writes of registers, and the writing of interrupt handlers.

### BOARD DLL CONTROL SOFTWARE

Acromag provides a software product (sold separately) consisting of board VxWorks® software. This software (Model PMCSW-API-VXW) is composed of VxWorks® (real time operating system) libraries for all Acromag PMC I/O board products, PCI I/O Cards, and CompactPCI I/O Cards. The software is implemented as a library of "C" functions which link with existing user code to make possible simple control of all Acromag PMC boards.

BOARD VxWORKS

SOFTWARE

Acromag provides a software product (sold separately) consisting of board QNX® software. This software (Model PCISW-API-QNX) is composed of QNX® (real time operating system) libraries for all Acromag PMC I/O board products, PCI I/O Cards, and CompactPCI I/O Cards. The software is implemented as a library of "C" functions which link with existing user code to make possible simple control of all Acromag PMC boards.

BOARD QNX SOFTWARE

# 2.0 PREPARATION FOR USE UNPACKING AND INSPECTION

WARNING: This board utilizes static sensitive components and should only be handled at a static-safe workstation.

# CARD CAGE CONSIDERATIONS

**IMPORTANT:** Adequate air circulation or conduction cooling must be provided to prevent a temperature rise above the maximum operating temperature.

### BOARD CONFIGURATION

Default Hardware Jumper Configuration

Upon receipt of this product, inspect the shipping carton for evidence of mishandling during transit. If the shipping carton is badly damaged or water stained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is absent when the carton is opened and the contents of the carton are damaged, keep the carton and packing material for the agent's inspection.

For repairs to a product damaged in shipment, refer to the Acromag Service Policy to obtain return instructions. It is suggested that salvageable shipping cartons and packing material be saved for future use in the event the product must be shipped.

This board is physically protected with packing material and electrically protected with an anti-static bag during shipment. However, it is recommended that the board be visually inspected for evidence of mishandling prior to applying power.

Refer to the specifications for loading and power requirements. Be sure that the system power supplies are able to accommodate the power requirements of the carrier/CPU board, plus the installed boards, within the voltage tolerances specified.

Adequate air circulation must be provided to prevent a temperature rise above the maximum operating temperature and to prolong the life of the electronics. If the installation is in an industrial environment and the board is exposed to environmental air, careful consideration should be given to air-filtering.

In a conduction cooled assembly, adequate thermal conduction must be provided to prevent a temperature rise above the maximum operating temperature.

Remove power from the system before installing board, cables, termination panels, and field wiring.

The board may be configured differently, depending on the application. When the board is shipped from the factory, it is configured as follows:

- J3 is open. Plus 3.3 volts is provided from an on board regulator.

- The default configuration of the programmable software control register bits at power-up are described in section 3.

- The control registers must be programmed to the desired configuration before starting data input or output operation.

The front panel connector provides the field I/O interface connections. It is a SCSI-3 68-pin female connector (AMP 787082-7 or equivalent) employing latch blocks and 30 micron gold in the mating area (per MIL-G-45204, Type II, Grade C). Connects to Acromag termination panel 5025-288 from the front panel via round shielded cable (Model 5028-432).

Differential channels 0 to 23 are controlled on an 4-bit port basis. Digital channels 24 to 39 are controlled on an individual bit basis. The counter/timer input and output control signals share Digital I/O channels 24 to 39. Each counter uses three input signals and one output signal. An enabled counter/timer has its required input and output signals automatically dedicated via the field connector. If the counter is not used then the ports are available for independent channel digital I/O.

| Pin Description            | Pin | Pin Description            | Pin |

|----------------------------|-----|----------------------------|-----|

| CH0+                       | 1   | COMMON                     | 35  |

| CH0-                       | 2   | COMMON                     | 36  |

| CH1+                       | 3   | CH12+                      | 37  |

| CH1-                       | 4   | CH12-                      | 38  |

| CH2+                       | 5   | CH13+                      | 39  |

| CH2-                       | 6   | CH13-                      | 40  |

| CH3+                       | 7   | CH14+                      | 41  |

| CH3-                       | 8   | CH14-                      | 42  |

| CH4+                       | 9   | CH15+                      | 43  |

| CH4-                       | 10  | CH15-                      | 44  |

| CH5+                       | 11  | CH16+                      | 45  |

| CH5-                       | 12  | CH16-                      | 46  |

| CH6+                       | 13  | CH17+                      | 47  |

| CH6-                       | 14  | CH17-                      | 48  |

| CH7+                       | 15  | CH18+                      | 49  |

| CH7-                       | 16  | CH18-                      | 50  |

| COMMON                     | 17  | CH19+                      | 51  |

| COMMON                     | 18  | CH19-                      | 52  |

| CH8+                       | 19  | CH20+                      | 53  |

| CH8–                       | 20  | CH20-                      | 54  |

| CH9+                       | 21  | CH21+                      | 55  |

| CH9–                       | 22  | CH21-                      | 56  |

| CH10+                      | 23  | CH22+                      | 57  |

| CH10-                      | 24  | CH22-                      | 58  |

| CH11+                      | 25  | CH23+                      | 59  |

| CH11-                      | 26  | CH23-                      | 60  |

| Digital CH24/Counter 1A    | 27  | Digital CH32/Counter 3A    | 61  |

| Digital CH25/Counter 1B    | 28  | Digital CH33/Counter 3B    | 62  |

| Digital CH26/Counter 1C    | 29  | Digital CH34/Counter 3C    | 63  |

| Digital CH27/Counter 1OUT  | 30  | Digital CH35/Counter 3 OUT | 64  |

| Digital CH28/Counter 2A    | 31  | Digital CH36/Counter 4A    | 65  |

| Digital CH29/Counter 2B    | 32  | Digital CH37/Counter 4B    | 66  |

| Digital CH30/Counter 2C    | 33  | Digital CH38/Counter 4C    | 67  |

| Digital CH31/Counter 2 OUT | 34  | Digital CH39/Counter 4 OUT | 68  |

### Front Panel Field I/O Connector

**Table 2.1:** Board Field I/O Pin Connections

The board has 4 TTL 16-bit counters available. Two 16-bit counters can be configured as one 32-bit counter. If counters 1 and 2 were configured as a 32-bit counter, then the input and output corresponding to Counter 1 are used. Similarly, counters 3 and 4 can also be configured as 32-bit counters. The signals corresponding to the first counter in the pair will be used.

# 10

#### Rear J4 Field I/O Connector

On models with rear I/O, the J4 PMC connector provides the field I/O interface connections. This connector is a 64-pin female receptacle header (AMP 120527-1 or equivalent) which mates to the male connector on the carrier/CPU board (AMP 120521-1 or equivalent).

**Table 2.2:** Board Rear Field I/O Pin Connections

The board has 4 TTL 16-bit counters available. Two 16-bit counters can be configured as one 32-bit counter. If counters 1 and 2 were configured as a 32-bit counter, then the input and output corresponding to Counter 1 are used. Similarly, counters 3 and 4 can also be configured as 32-bit counters. The signals corresponding to the first counter in the pair will be used.

| Pin Description            | Pin | Pin Description            | Pin |

|----------------------------|-----|----------------------------|-----|

| CH0+                       | 1   | CH12+                      | 33  |

| CH0-                       | 2   | CH12-                      | 34  |

| CH1+                       | 3   | CH14+                      | 35  |

| CH1-                       | 4   | CH14-                      | 36  |

| CH2+                       | 5   | CH14+                      | 37  |

| CH2-                       | 6   | CH14-                      | 38  |

| CH3+                       | 7   | CH15+                      | 39  |

| CH3-                       | 8   | CH15-                      | 40  |

| CH4+                       | 9   | CH16+                      | 41  |

| CH4-                       | 10  | CH16-                      | 42  |

| CH5+                       | 11  | CH17+                      | 43  |

| CH5-                       | 12  | CH17-                      | 44  |

| CH6+                       | 13  | CH18+                      | 45  |

| CH6-                       | 14  | CH18-                      | 46  |

| CH7+                       | 15  | CH19+                      | 47  |

| CH7-                       | 16  | CH19-                      | 48  |

| CH8+                       | 17  | CH20+                      | 49  |

| CH8-                       | 18  | CH20-                      | 50  |

| CH9+                       | 19  | CH21+                      | 51  |

| CH9-                       | 20  | CH21-                      | 52  |

| CH10+                      | 21  | CH22+                      | 53  |

| CH10-                      | 22  | CH22-                      | 54  |

| CH11+                      | 23  | CH23+                      | 55  |

| CH11-                      | 24  | CH23-                      | 56  |

| Digital CH24/Counter 1A    | 25  | Digital CH32/Counter 3A    | 57  |

| Digital CH25/Counter 1B    | 26  | Digital CH33/Counter 3B    | 58  |

| Digital CH26/Counter 1C    | 27  | Digital CH34/Counter 3C    | 59  |

| Digital CH27/Counter 1OUT  | 28  | Digital CH35/Counter 3 OUT | 60  |

| Digital CH28/Counter 2A    | 29  | Digital CH36/Counter 4A    | 61  |

| Digital CH29/Counter 2B    | 30  | Digital CH37/Counter 4B    | 62  |

| Digital CH30/Counter 2C    | 31  | Digital CH38/Counter 4C    | 63  |

| Digital CH31/Counter 2 OUT | 32  | COMMON                     | 64  |

Note: On rear I/O models, Counter 4 Output is not connected to J4.

### Non-Isolation Considerations

The board is non-isolated, since there is electrical continuity between the logic and field I/O grounds. As such, the field I/O connections are not isolated from the system. Care should be taken in designing installations without isolation to avoid noise pickup and ground loops caused by multiple ground connections. This is particularly important for analog inputs and outputs when a high level of accuracy/resolution is needed.

11

This Section provides the specific information necessary to program and operate the board.

3.0 PROGRAMMING INFORMATION

This board is a PCI Specification version 2.2 compliant PCI bus target only board.

The PCI bus is defined to address three distinct address spaces: I/O, memory, and configuration space. This board can be accessed via the PCI bus memory space and configuration spaces, only.

The card's configuration registers are initialized by system software at power-up to configure the card. The board is a Plug-and-Play PCI card. As a Plug-and-Play card the board's base address and system interrupt request line are not selected via jumpers but are assigned by system software upon power-up via the configuration registers. A PCI bus configuration access is used to read/write the PCI card's configuration registers.

When the computer is first powered-up, the computer's system configuration software scans the PCI bus to determine what PCI devices are present. The software also determines the configuration requirements of the PCI card.

The system software accesses the configuration registers to determine how many blocks of memory space the carrier requires. It then programs the board's configuration registers with the unique memory base address.

The configuration registers are also used to indicate that the board requires an interrupt request line. The system software then programs the configuration registers with the interrupt request line assigned to the board.

Since this board is relocatable and not fixed in address space, its device driver must use the mapping information stored in the board's Configuration Space registers to determine where the board is mapped in memory space and which interrupt line will be used.

The PCI specification requires software driven initialization and configuration via the Configuration Address space. This board provides 256 bytes of configuration registers for this purpose. It contains the configuration registers, shown in Table 3.1, to facilitate Plug-and-Play compatibility.

The Configuration Registers are accessed via the Configuration Address and Data Ports. The most important Configuration Registers are the Base Address Registers and the Interrupt Line Register which must be read to determine the base address assigned to the board and the interrupt request line that goes active on a board interrupt request.

PCI Configuration Address Space

CONFIGURATION REGISTERS

Table 3.1 Configuration Registers

| Reg.<br>Num. | D31 D24  | D23      | D16            | D15                      | D8        | D7          | D0   |

|--------------|----------|----------|----------------|--------------------------|-----------|-------------|------|

| 0            | Device   | ID=424   | 3              | \                        | /endor ID | )= 16D5     |      |

| 1            | St       | atus     |                |                          | Comn      | nand        |      |

| 2            |          | ode=1180 | 8000 Rev ID=00 |                          |           | D=00        |      |

| 3            | BIST     | He       | ader           | Latency Cache            |           | che         |      |

| 4            | 32-bi    | t Memor  | y Base A       | ddress fo                | r 4K-Byte | Block       |      |

| 5:10         |          |          | Not            | Used                     |           |             |      |

| 11           | Subsyste | m ID=00  | 000            | Subsystem Vendor ID=0000 |           |             | 0000 |

| 12           | Not Used |          |                |                          |           |             |      |

| 13,14        | Reserved |          |                |                          |           |             |      |

| 15           | Max_Lat  | Min      | _Gnt           | Inter                    | . Pin     | Inter. Line |      |

#### **MEMORY MAP**

This board is allocated a 4K byte block of memory that is addressable in the PCI bus memory space to control the boards multiple functions. Three types of information are stored in the memory space: control, status, and data.

The memory space address map for the board is shown in Table 3.2. Note that the base address for the board in memory space must be added to the addresses shown to properly access the board registers. Register accesses as 32, 16, and 8-bit in memory space are permitted.

Table 3.2: Memory Map

- 1. The board will return 0 for all addresses that are "Not Used".

- 2. The board has 4 TTL 16-bit counters available. Via counter 1 control register, 16bit counters 1 and 2 can be configured as one 32-bit counter. This is also an option for counter pairs 3 and 4.

- 3. The numbers in the left most column represent the User Manual page containing a description of the corresponding register

| Base<br>Addr+      | D31                      | D16                                      | D15 D00                                                          | Base<br>Addr+ |  |

|--------------------|--------------------------|------------------------------------------|------------------------------------------------------------------|---------------|--|

| 14 <sup>3</sup> 03 |                          | Not Used <sup>1</sup>                    | Interrupt Register                                               | 00            |  |

| 15 <b>07</b>       |                          | Not Used <sup>1</sup>                    | Counters 1 to 4 Interrupt Status/Clear Reg.                      | 04            |  |

| <b>0B</b>          | Interi<br>23-1           | rupt Status/Clear<br>6 Differential I/O  | Interrupt Status/Clear<br>15-0 Differential I/O                  | 08            |  |

| <b>0F</b>          |                          | Not Used <sup>1</sup>                    | Interrupt Status/Clear<br>39-24 Digital TTL I/O                  | 0C            |  |

| <b>13</b>          | Not<br>Used <sup>1</sup> | 23-16 Differential<br>I/O Register       | 15-0 Differential I/O<br>Register                                | 10            |  |

| <b>17</b>          |                          | Not Used <sup>1</sup>                    | 39-24 Digital TTL I/O<br>Register                                | 14            |  |

| 1B<br>17           | Dire<br>Dig. Ti          | ection Register<br>「L Channels 39-24     | egister Direction Register nels 39-24 Differential Channels 23-0 |               |  |

| <b>1F</b>          | Not<br>Used <sup>1</sup> | Interrupt Enable<br>Differential 23-16   | Interrupt Enable<br>Differential Channels 15-0                   | 1C            |  |

| 18 <b>23</b>       |                          | Not Used <sup>1</sup>                    | Interrupt Enable<br>Digital Channels 39-24                       | 20            |  |

| 18 <b>27</b>       | Not<br>Used <sup>1</sup> | Interrupt Type<br>Differential 23-16     | Interrupt Type Differential Channels 15-0                        | 24            |  |

| <b>2B</b> 18       |                          | Not Used <sup>1</sup>                    | Interrupt Type<br>Digital Channels 39-24                         | 28            |  |

| <b>2F</b> 19       | Not<br>Used <sup>1</sup> | Interrupt Polarity<br>Differential 23-16 | 2C                                                               |               |  |

| <b>33</b>          |                          | Not Used <sup>1</sup>                    | Interrupt Polarity<br>Digital Channels 39-24                     | 30            |  |

| 21              | 37  | Counter Stop Register                                     | Counter Trigger Register                         | 34  |  |  |

|-----------------|-----|-----------------------------------------------------------|--------------------------------------------------|-----|--|--|

| 23              | 3B  | Counter 1 Co<br>(32-bit Counter C                         | ntrol Register<br>Control Register) <sup>2</sup> | 38  |  |  |

| 23              | 3F  | Counter 2 Co                                              | ntrol Register                                   | 3C  |  |  |

| 23              | 43  | Counter 3 Co<br>(32-bit Counter C                         | ntrol Register<br>Control Register) <sup>2</sup> | 40  |  |  |

| 23              | 47  | Counter 4 Co                                              | ntrol Register                                   | 44  |  |  |

| 22              | 4B  | Counter 2 Read Back Register Counter 1 Read Back Register |                                                  |     |  |  |

| 22              | 4F  | Counter 4 Read Back<br>Register                           | 4C                                               |     |  |  |

| 22 <sup>3</sup> | 53  | Counter 2<br>Constant A Register                          | Counter 1<br>Constant A Register                 | 50  |  |  |

| 22              | 57  | Counter 4<br>Constant A Register                          | Counter 3<br>Constant A Register                 | 54  |  |  |

| 22              | 5B  | Counter 2<br>Constant B Register                          | Counter 1<br>Constant B Register                 | 58  |  |  |

| 22              | 5F  | Counter 4<br>Constant B Register                          | Counter 3<br>Constant B Register                 | 5C  |  |  |

| 20              | 63  |                                                           | Select and Enable<br>Is 0 to 7                   | 60  |  |  |

| 20              | 67  |                                                           | Select and Enable<br>s 8 to 15                   | 64  |  |  |

| 20              | 6B  |                                                           | Select and Enable<br>3 16 to 23                  | 68  |  |  |

| 20              | 6F  | Debounce Duration Select and Enable<br>Channels 24 to 31  |                                                  |     |  |  |

| 20              | 73  | Debounce Duration Select and Enable<br>Channels 32 to 39  |                                                  |     |  |  |

|                 | 77  | Not Used <sup>1</sup>                                     |                                                  |     |  |  |

|                 |     |                                                           | ļ                                                |     |  |  |

| ı               | FFF | Not U                                                     | Jsed <sup>1</sup>                                | FFC |  |  |

This memory map reflects byte accesses using the "Little Endian" byte ordering format. Little Endian uses even-byte addresses to store the low-order byte. The Intel x86 family of microprocessors uses "Little Endian" byte ordering. Big Endian is the convention used in the Motorola 68000 microprocessor family and is the VMEbus convention. In Big Endian, the lower-order byte is stored at odd-byte addresses.

#### **MEMORY MAP**

When a 32-bit counter is enabled, the readback and constant registers of the two 16-bit counters that make the 32-bit counter become 32-bit register values.

3. The numbers in the left most column represent the User Manual page containing a description of the corresponding register.

### INTERRUPT REGISTERS

### Interrupt Register (Read/Write) – (Base + 00H)

This read/write register is used to enable board interrupt operation, determine the pending status of interrupts, and release pending interrupts.

The function of each of the interrupt register bits is described in Table 3.3. This register can be read or written with either 8-bit, 16-bit, or 32-bit data transfers. A power-up or system reset sets all interrupt register bits to 0.

Table 3.3: Interrupt Register

| BIT     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | Board Interrupt Enable Bit. (Read/Write Bit) 0 = Disable Interrupt 1 = Enable Interrupt If enabled via this bit an interrupt request from the board will be issued to the system upon any of its interrupt conditions. The interrupt request will remain active until the interrupt release bit is set, or by disabling interrupts via this bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1       | Board Interrupt Pending Status Bit. (Read Only Bit)  0 = Interrupt Not Pending  1 = Interrupt Pending This bit can be read to determine the interrupt pending status of the board. When this bit is logic "1" an interrupt is pending and will cause an interrupt request if bit-0 of the register is set. When this bit is a logic "0" an interrupt is not being requested. Once the bit is in the pending status it will remain until the pending interrupt is removed via the source of the interrupt. This bit will remain active even if interrupts are disabled via bit-0.  When this bit is set the pending interrupt can originate from any of the 4 counter timers, the 24 differential I/O, or 16 digital I/O channels. To identify the source of the pending interrupt base address plus 04H is read to identify a Counter/Timer Interrupt, while base address plus 08H is read to identify a digital input Interrupt, and 0CH is read to identify a digital input Interrupt. |

| 2 to 13 | Not Used <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 14      | Software Reset: The board is reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 15      | Not Used <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

1. All bits labeled "Not Used" will return logic "0" when read.

# Interrupt Status/Clear Counter/Timer Register (Read/Write) – (Base + 04H)

This read/write register is used to determine the pending status of Counter/Timer interrupts, and release pending Counter/Timer interrupts.

The Counter/Timer interrupt status/clear bits 0 to 3 reflect the status of each of the Counter/Timers. **Read** of this bit reflects the interrupt pending status. Read of a "1" indicates that an interrupt is pending for the corresponding counter/timer. **Write** of a logic "1" to this bit to release a counter timer pending interrupt. Writing "0" to a bit location has no effect, a pending interrupt will remain pending. The Counter/Timer and its corresponding interrupt Pending/Clear bits are as shown in Table 3.4.

| BIT  | FUNCTION                                |

|------|-----------------------------------------|

| 0    | Counter/Timer 1 Interrupt Pending/Clear |

| 1    | Counter/Timer 2 Interrupt Pending/Clear |

| 2    | Counter/Timer 3 Interrupt Pending/Clear |

| 3    | Counter/Timer 4 Interrupt Pending/Clear |

| 4-31 | Not Used <sup>1</sup>                   |

The board has 4 TTL 16-bit counters available. Two 16-bit counters can be configured as one 32-bit counter. For example, counter 1 and 2 can be combined to form a 32-bit counter. A counter configured as a 32-bit counter has its interrupt status/clear function controlled via the odd counter. For example, counter 3 and 4 when combined have their interrupt status/clear function controlled via bit-2.

# Interrupt Status/Clear Differential I/O (Read/Write) – (Base + 08H)

This read/write register is used to determine the pending status of Differential input interrupts, and release pending Differential input interrupts.

The Differential input interrupt status/clear registers reflect the status of each of the Differential channels. **Read** of this bit reflects the interrupt pending status. Read of a "1" indicates that an interrupt is pending for the corresponding differential channel. **Write** of a logic "1" to this bit releases the corresponding differential channel's pending interrupt. Writing "0" to a bit location has no effect, a pending interrupt will remain pending.

Differential input channel 0 interrupt status is identified via data bit-0 while Differential input channel 23 status is identified via data bit-23 at base address plus 08H.

| Reg.<br>Num. | D31    | D24 | D23    | D16         | D15         | D8          | D7     | D0        |

|--------------|--------|-----|--------|-------------|-------------|-------------|--------|-----------|

| 08H          | Not Us | sed | 23-0 [ | Differentia | al Input Ir | nterrupt St | atus/C | lear Bits |

### INTERRUPT REGISTERS

**Table 3.4:** Board Counter/Timer Interrupt Status/Clear

All bits labeled "Not Used" will return logic "0" when read.

### DIGITAL INPUT/OUTPUT REGISTERS

# Interrupt Status/Clear Digital TTL (Read/Write) – (Base + 0CH)

This read/write register is used to determine the pending status of Digital TTL input interrupts, and release pending Digital TTL interrupts.

The Digital TTL interrupt status/clear registers reflect the status of each of the Digital TTL channels. **Read** of this bit reflects the interrupt pending status. Read of a "1" indicates that an interrupt is pending for the corresponding Digital TTL channel. **Write** of a logic "1" to this bit releases the corresponding Digital TTL channel's pending interrupt. Writing "0" to a bit location has no effect, a pending interrupt will remain pending.

Digital TTL input channel 24 interrupt status is identified via data bit-0 while Digital TTL input channel 39 status is identified via data bit-15 at base address plus 0CH.

| Reg.<br>Num. | D31      | D24 | D23 | D16 | D15                                              | D8 | D7 | D0 |

|--------------|----------|-----|-----|-----|--------------------------------------------------|----|----|----|

| 0CH          | Not Used |     |     |     | 39-24 Digital TTL Interrupt<br>Status/Clear Bits |    |    |    |

# Differential Input/Output Register (Read/Write) – (Base + 10H)

Twenty-four differential channels numbered 0 through 23 may be individually accessed via this register. Channels 23 to 0 are accessed at the carrier base address +10H via data bits 23 to 0. Channel input signal levels are determined by reading this register. Likewise, channel output signal levels are set by writing to this register. Note the data direction, input or output, must first be set via the Direction register at base address plus 18H.

Channel read/write operations use 8-bit, 16-bit, or 32-bit data transfers with the lower ordered bits corresponding to the lower-numbered channels for the register of interest. All input/output channels are configured as inputs on a power-on or software reset.

# Digital Input/Output Registers (Read/Write) – (Base + 14H)

Sixteen possible input/output channels numbered 24 through 39 may be individually accessed via these registers. Channels 39 to 24 are accessed at the carrier base address +14H via data bits 15 to 0. Channel input signal levels are determined by reading this register. Likewise, channel output signal levels are set by writing to this register. Note the data direction, input or output, must first be set via the Direction register at base address plus 1AH.

Channel read/write operations use 8-bit, 16-bit, or 32-bit data transfers with the lower ordered bits corresponding to the lower-numbered channels for the register of interest. All input/output channels are configured as inputs on a power-on or software reset.

|       | Digital I/O Channel and Corresponding Register Bits |       |       |       |       |       |       |

|-------|-----------------------------------------------------|-------|-------|-------|-------|-------|-------|

| Ch 31 | Ch 30                                               | Ch 29 | Ch 28 | Ch 27 | Ch 26 | Ch 25 | Ch 24 |

| D7    | D6                                                  | D5    | D4    | D3    | D2    | D1    | D0    |

|       |                                                     |       |       |       |       |       |       |

| Ch 39 | Ch 38                                               | Ch 37 | Ch 36 | Ch 35 | Ch 34 | Ch 33 | Ch 32 |

| D15   | D14                                                 | D13   | D12   | D11   | D10   | D9    | D8    |

### Direction Control Register (Read/Write) - (Base + 18H)

The data direction (input or output) of the 24 differential channels and 16 digital channels is selected via this register. The data direction of channels 0 to 23 is controlled as groups of 4 bits. Channels 0 to 23 are set/controlled via bits 0 to 5 as shown below. The data direction of digital channels 24 to 39 is controlled on an individual channel basis via bits 16 to 31 as shown below. Setting a bit low configures the corresponding channel data direction for input. Setting the control bit high configures the corresponding channel data direction for output.

The counter/timer input and output control signals share Digital I/O channels 24 to 39. Each counter uses three input signals and one output signal. An enabled counter/timer has its required input and output signals automatically set by hardware and control via this register is disabled. If the counter is not used, then the ports are available for independent channel digital I/O.

|          | Channels and Corresponding Register Bits |      |        |   |          |        |   |      |       |   |         |

|----------|------------------------------------------|------|--------|---|----------|--------|---|------|-------|---|---------|

| Ch23 - 2 | 20                                       | Ch19 | 9 - 16 | O | h15 - 12 | Ch11 - | 8 | Ch7  | ' - 4 | • | Ch3 - 0 |

| D5       |                                          | D    | D4     |   | D3       | D2     |   | D    | D1    |   | D0      |

|          |                                          |      |        |   |          |        |   |      |       |   |         |

| Ch 31    | О                                        | h 30 | Ch 2   | 9 | Ch 28    | Ch 27  | С | h 26 | Ch 2  | 5 | Ch 24   |

| D23      | [                                        | D22  | D21    |   | D20      | D19    | [ | D18  | D17   | 7 | D16     |

|          |                                          |      |        |   |          |        |   |      |       |   |         |

| Ch 39    | С                                        | h 38 | Ch 3   | 7 | Ch 36    | Ch 35  | С | h 34 | Ch 3  | 3 | Ch 32   |

| D31      | [                                        | D30  | D29    | ) | D28      | D27    | [ | D26  | D25   | 5 | D24     |

DIGITAL INPUT/OUTPUT REGISTERS

18

The default power-up state of these registers is logic low. Thus, all channels are configured as inputs on system reset or power-up. Register bits D6 to D15 of this register are "Not Used" and will always read low (0's). Reading or writing to this register is possible via 32-bit, 16-bit or 8-bit data transfers.

### DIGITAL INTERRUPT REGISTERS

# Interrupt Enable Registers (Read/Write) – (Base + 1CH and 20H)

The Interrupt Enable Registers provide a mask bit for each of the 40 channels. A "0" bit will prevent the corresponding input channel from generating an external interrupt. A "1" bit will allow the corresponding channel to generate an interrupt.

The Interrupt Enable register at the base address + offset 1CH is used to control differential channels 0 through 23 via data bits 0 to 23. Digital channels 39 to 24 are accessed at the carrier base address +20H via data bits 15 to 0.

All channel interrupts are disabled (set to "0") following a power-on or software reset. Reading or writing to this register is possible via 32-bit, 16-bit or 8-bit data transfers.

## Interrupt Type (COS or H/L) Configuration Registers (Read/Write) - (Base + 24H and 28H)

The Interrupt Type Configuration Registers determine the type of input channel transition that will generate an interrupt for each of the 40 possible interrupting channels. A "0" bit selects interrupt on level. An interrupt will be generated when the input channel level specified by the Interrupt Polarity Register occurs (i.e. Low or High level transition interrupt). A "1" bit means the interrupt will occur when a Change-Of-State (COS) occurs at the corresponding input channel (i.e. any state transition, low to high or high to low).

The Interrupt Type Configuration register at base address + offset 24H is used to control differential channels 0 through 23. For example, channel 0 is controlled via data bit-0. Digital channels 39 to 24 are accessed at the carrier base address +28H via data bits 15 to 0. For example, channel 24 is controlled via data bit-0.

All bits are set to "0" following a reset which means that, if enabled, the inputs will cause interrupts for the levels specified by the digital input channel Interrupt Polarity Register.

Channel read or write operations use 8-bit, 16-bit, or 32-bit data transfers. Note that no interrupts will occur unless they are enabled by the Interrupt Enable Register.

# Interrupt Polarity Registers (Read/Write) – (Base + 2CH and 30H)

DIGITAL INTERRUPT REGISTERS

The Interrupt Polarity Register determines the level that will cause a channel interrupt to occur for each of the channels enabled for level interrupts. A "0" bit specifies that an interrupt will occur when the corresponding input channel is low (i.e. a "0" in the digital input channel data register). A "1" bit means that an interrupt will occur when the input channel is high (i.e. a "1" in the digital input channel data register). Note that no interrupts will occur unless they are enabled by the Interrupt Enable Register. Further, the Interrupt Polarity Register will have no effect if the Change-of-State (COS) interrupt type is configured by the Interrupt Type Configuration Register.

The Interrupt Polarity register at the carrier's base address + offset 2CH is used to control differential channels 0 through 23. Digital channels 39 to 24 are accessed at the carrier base address +30H via data bits 15 to 0. For example, digital channel 24 is controlled via data bit-0.

All bits are set to "0" following a reset which means that the inputs will cause interrupts when they are logic low (provided they are enabled for interrupt on level).

### DEBOUNCE DURATION REGISTERS

# Debounce Duration Select and Enable Registers (Read/Write) – (Base + 60H to 70H)

This register controls debounce enable and duration selection for each of the 40 digital channels. Debounce, when enabled, will filter noise present on a channel's input line. All noise spikes with a duration less than the debounce time, selected via Table 3.5, are ignored when present on the input signal/channel.

**Table 3.5a:** Debounce Duration Select

Not Used Bits: 3, 7, 11, 15, 19, 23, 27, and 31 will return logic "0" when read.

| Channels and Corresponding Register Bits |     |                |      |      |      |  |

|------------------------------------------|-----|----------------|------|------|------|--|

| Reg.                                     |     | Offset Address |      |      |      |  |

| Bits                                     | 60H | 64H            | 68H  | 6CH  | 70H  |  |

| 2,1,0                                    | Ch0 | Ch8            | Ch16 | Ch24 | Ch32 |  |

| 6,5,4                                    | Ch1 | Ch9            | Ch17 | Ch25 | Ch33 |  |

| 10,9,8                                   | Ch2 | Ch10           | Ch18 | Ch26 | Ch34 |  |

| 14,13,12                                 | Ch3 | Ch11           | Ch19 | Ch27 | Ch35 |  |

| 18,17,16                                 | Ch4 | Ch12           | Ch20 | Ch28 | Ch36 |  |

| 22,21,20                                 | Ch5 | Ch13           | Ch21 | Ch29 | Ch37 |  |

| 26,25,24                                 | Ch6 | Ch14           | Ch22 | Ch30 | Ch38 |  |

| 30,29,28                                 | Ch7 | Ch15           | Ch23 | Ch31 | Ch39 |  |

The bits listed in the Register Bits column above must be set as shown in the Debounce Duration Select Table 3.5b.

**Table 3.5b:** Debounce Duration Select

| BIT           | FUNCTION          |

|---------------|-------------------|

| 000           | Debounce Disabled |

| 001           | 1.6µs             |

| 010           | 10.4μs            |

| 011           | 408.8μs           |

| 100           | 3.276ms           |

| 101 ,110, 111 | Reserved          |

For example, to enable channel 33 and channel 37 for a debounce level of  $10.4\mu s$ , and 3.276ms respectively, the value 400020H must be written to base address plus 70H. Notice bits 3, 7, 11, 15, 19, 23, 27, and 31 are don't care bits and are represented by an "X" in the following table. Note that writing 400020 Hex, to base address plus 70H, also disables debounce for channels 32, 34, 35, 36, 38, and 39.

| Ch39               | Ch38    | Ch37   | Ch36    | Ch35    | Ch34      | Ch33     | Ch32    |

|--------------------|---------|--------|---------|---------|-----------|----------|---------|

| Bits 31 down to 16 |         |        |         |         | Bits 15 d | own to 0 |         |

| X000               | X000    | X100   | X000    | X000    | X000      | X010     | X000    |

| 0                  | 0       | 4      | 0       | 0       | 0         | 2        | 0       |

| Disable            | Disable | 3.27ms | Disable | Disable | Disable   | 10.4μs   | Disable |

The Debounce Duration Select and Enable register bits are set to "0" following reset. Thus, on reset and power-up debounce will be disabled by default. These registers are read/write registers that can be accessed with 8-bit, 16-bit, or 32-bit data transfers.

### Counter Trigger Register (Write) - (Base + 34H)

This register is used to implement software triggering for all counter timers. Writing a 1 to the counter's corresponding trigger bit of this register will cause the counter function to be triggered. Table 3.6 identifies the trigger bit location corresponding to each of the counters. The contents of this register are not stored and merely act to trigger the corresponding counters.

| BIT  | FUNCTION              |                          |

|------|-----------------------|--------------------------|

| 0    | Counter 1 Trigger     | (32-bit Counter Trigger) |

| 1    | Counter 2 Trigger     |                          |

| 2    | Counter 3 Trigger     | (32-bit Counter Trigger) |

| 3    | Counter 4 Trigger     |                          |

| 4-15 | Not Used <sup>1</sup> |                          |

Triggering may be used to initiate pulse width modulation, watchdog timer (initiates countdown), event counting, frequency measurement, pulsewidth measurement, period measurement, or one-shot.

Writing to this register is possible via 32-bit, 16-bit or 8-bit data transfers.

### Counter Stop Register (Read/Write) - (Base + 36H)

This register is used to stop one or a group of Counter/Timers. Writing a "1" to the counter's corresponding stop bit of this register will cause the counter to be disabled. That is, bits 2,1, and 0 of the counter control register are cleared to "000", thus disabling and stopping the counter. Table 3.7 identifies the stop bit location corresponding to each of the counters. The bits of this register are not stored and merely act to stop the corresponding counter when set to logic high.

Writing to this register is possible via 32-bit, 16-bit or 8-bit data transfers.

| BIT   | FUNCTION                             |

|-------|--------------------------------------|

| 16    | Counter 1 Stop (32-bit Counter Stop) |

| 17    | Counter 2 Stop                       |

| 18    | Counter 3 Stop (32-bit Counter Stop) |

| 19    | Counter 4 Stop                       |

| 20-31 | Not Used <sup>1</sup>                |

#### **COUNTER REGISTERS**

**Table 3.6:** Board Counter Trigger Register

1. All bits will return logic "0" when read

**Table 3.7:** Board Counter Stop Register

1. All bits will return logic "0" when read

# COUNTER REGISTERS

# Counter Readback Registers (Read Only) – (Base + 48H and 4CH)

The Counter Readback register is a dynamic function register that returns the current value held in the counter. It is updated with the value stored in the internal counter, each time it is read.

The internal counter is generally initialized with the value in the Counter Constant Register, and its value is incremented or decremented according to the application.

The Counter Readback register at base address + offset 48H corresponds to counters 1 and 2. Counters' 3 and 4 Readback registers are accessed at the carrier base address +4CH.

This register must be read using 32-bit long-word accesses for 32-bit enabled counters, but it may be read using 16-bit accesses for 16-bit enabled counters.

Note that the Counter Constant Registers are cleared (set to 0) following a system or software reset.

# Counter Constant A Registers (Write Only) – (Base + 50H and 54H)

This write-only register is used to store the counter/timer constant A value (initial value) for the various counting modes. Accesses to this register are allowed on a 16-bit or 32-bit long-word basis, only. It is necessary to load the constant value into the counter in one clock cycle. Thus, for a 16-bit counter a 16-bit or 32-bit write access is required, while a 32-bit write access is required for a 32-bit counter.

Base address + offset 50H corresponds to the Counter Constant A register for counters 1 and 2. Base address + offset 54H corresponds to the Counter Constant A register for counters 3 and 4.

# Counter Constant B Registers (Read/Write) – (Base + 58H and 5CH)

This read/write register is used to store the counter/timer constant B value. It is necessary to load the constant value into the counter in one clock cycle. Thus, for a 16-bit counter a 16-bit or 32-bit write access is required, while a 32-bit write access is required for a 32-bit counter.

Base address + offset 58H corresponds to the Counter Constant B register for counters 1 and 2. Base address + offset 5CH corresponds to the Counter Constant B register for counters 3 and 4.

# Counter Control Registers (Read/Write) – (Base + 38H, 3CH, 40H, 44H)

COUNTER CONTROL REGISTERS

This register is used to configure counter/timer functionality. It defines the counter mode, output polarity, input polarity, clock source, counter size, and interrupt enable.

The memory map addresses corresponding to the control registers are given in Table 3.2. The Counter Control Register is cleared (set to 0) following a reset, thus disabling the counter/timer. Reading or writing to this register is possible via 32-bit, 16-bit, or 8-bit data transfers.

The board has four 16-bit Counter/Timers. A pair of counters can be grouped to form a 32-bit counter. Control register bit-14 when set high enables 32-bit counter mode. When a 32-bit counter is enabled it must be selected via control register 1 for counters 1 and 2. Likewise, control register 3 is used when counters 3 and 4 are enabled as a 32-bit counter.

The counter timer functions of the board provide seven modes of operation: pulse width modulation, watchdog timer, event counting, frequency measurement, pulse width measurement, period measurement, and one-shot pulse mode. The following sections describe the features of each method of operation and how to best use them.

# 24

# COUNTER CONTROL REGISTERS

#### **Pulse Width Modulation**

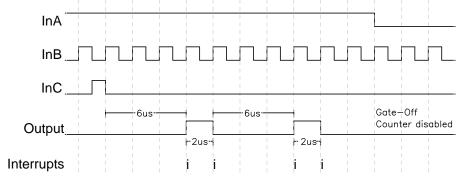

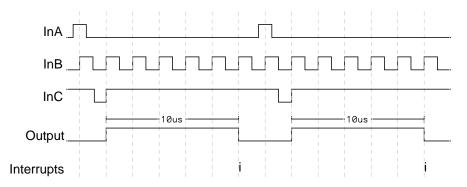

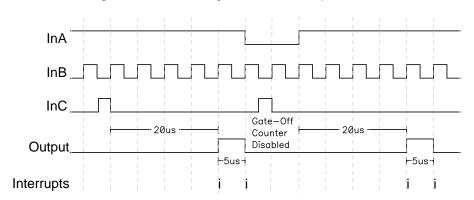

Pulse width modulated waveforms may be generated at the counter timer output. The pulse width modulated waveform is generated continuously. Pulse Width Modulation generation is selected by setting Counter Control Register bits 2 to 0 to logic "010".

Counter Constant A value controls the time until the pulse goes active. The duration of the pulse is set via the Counter Constant B register. Note that a high pulse will be generated if active high output is selected while a low pulse will be generated if active low output is selected.

The counter goes through a countdown sequence for each Counter Constant value. When the 0 count is detected, the output toggles to the opposite state. Then the second Counter Constant value is loaded into the counter, and countdown resumes, decrementing by one for each rising edge of the clock selected via Control Register bits 12, 11, and 10. For example, a counter constant value of 3 will provide a pulse duration of 3 clock cycles of the selected clock. Note, when the internal 20MHz clock is selected, a delay of one extra clock cycle will be added to the counter constant value.

InA can be used as a Gate-Off signal to stop and start the counter and thus the pulse-width modulated output. When InA is enabled via bits 5 and 4 of the control register for active low Gate-Off input, a logic low input will enable pulse-width modulation counting while a logic high will stop PWM counting. When InA is enabled for active high Gate-Off operation, a logic high will enable PWM counting while a logic low will stop PWM counting.

InB can be used to input an external clock for use in PWM. Bits 7 and 6 must be set to either logic "01" or "10". Additionally, the clock source bits 12, 11, and 10 must be set to logic "101" to enable external clock input. PWM can alternatively be clocked via an internal 1.25MHz, 2.5MHz, 5MHz, 10MHz, or 20MHz clock as selected via control register bits 12, 11, and 10.

InC can be used to externally trigger Pulse Width Modulation generation. Additionally PWM can be triggered internally via the Counter Trigger Register at the base address + offset 34H. An initial trigger, software or external, causes the pulse width modulated signal to be generated. After an initial trigger, do not issue additional triggers. Triggers issued while running will cause the Constant A and B values to load at the wrong time. In addition, changing the Control register setting while running can also cause the Constant A and B values to load at the wrong time.

If the Interrupt Enable bit of the Counter Control Register is set (bit 15) and bit-0 of the Interrupt register is set, an interrupt is generated when the output pulse transitions from low to high and also for transitions from high to low. Thus, an interrupt is generated at each pulse transition.

| Bit(s)   | FUNCT    | ION                                                               |

|----------|----------|-------------------------------------------------------------------|

| 2,1,0    | Specifie | es the Counter Mode:                                              |

|          | 010      | Pulse Width Modulation                                            |

| 3        | Output   | Polarity (Output Pin ACTIVE Level):                               |

|          | 0        | Active LOW (Default)                                              |

|          | 1        | Active HIGH                                                       |

| 5, 4     | InA Pola | arity / Gate-Off Polarity                                         |

|          | 00       | Disabled (Default)                                                |

|          | 01       | Active LOW In A=0; Counter is Enabled In A=1; Counter is Disabled |

|          | 10       | Active HIGH In A=0 Counter is Disabled In A=1 Counter is Enabled  |

|          | 11       | Disabled                                                          |

| 7, 6     |          | arity / External Clock Input                                      |

|          | 00       | Disabled (Default)                                                |

|          | 01       | External Clock Enabled                                            |

|          | 10       | External Clock Enabled                                            |

|          | 11       | Disabled                                                          |

| 9,8      |          | arity / External Trigger                                          |

|          | 00       | Disabled (Default)                                                |

|          | 01       | Active LOW External Trigger                                       |

|          | 10       | Active HIGH External Trigger                                      |

|          | 11       | Disabled                                                          |

| 12,11,10 | Clock S  |                                                                   |

|          | 000      | Internal @ 1.25MHz (Default)                                      |

|          | 001      | Internal @ 2.5MHz                                                 |

|          | 010      | Internal @ 5MHz                                                   |

|          | 011      | Internal @ 10MHz                                                  |

|          | 100      | Internal @ 20MHz                                                  |

|          | 101      | External Clock (Up to 8MHz)                                       |

| 13       |          | ed (bit is read as logic "0")                                     |

| 14       | Counter  |                                                                   |

|          | 0        | 16-bit Counter (Default) <sup>1</sup>                             |

|          | 1        | 32-bit Counter                                                    |

| 15       |          | t Enable                                                          |

|          | 0        | Disable Interrupt Service (Default)                               |

|          | 1        | Enable Interrupt Service                                          |

### **Pulse Width Modulation**

**Table 3.8:** Counter Control Register (Pulse Width Modulation)

<sup>1.</sup> When two 16-bit counters are selected to implement a 32-bit counter the control register corresponding to the first 16-bit counter is used for control of the 32 bit counter.

### **Watchdog Timer Operation**

The watchdog operation counts down from a programmed (Counter Constant A) value until it reaches 0. While counting, the counter output will be in its active state (the output polarity is programmable). Upon time-out, the counter output will return to its inactive state, and an optional interrupt may be generated. Watchdog operation is selected by setting Counter Control Register bits 2 to 0 to logic "011".

A timed-out watchdog timer will not re-cycle until it is reloaded and then followed with a new trigger. Failure to cause a reload would generate an automatic time-out upon re-triggering, since the counter register will contain the 0 it previously counted down to.

InA input can be used to reload the counter with the Constant A register value. InA reload input is enabled via Control register bits 5 and 4. The counter can also be reloaded via a software write to the Counter Constant A register. Writing to the Counter Constant A register will load the value directly into the counter even if watchdog counting is active.

InB can be used to input an external clock for watchdog timing. Bits 7 and 6 must be set to either logic "01" or "10". Additionally, the clock source bits 12, 11, and 10 must be set to logic "101" to enable external clock input. The timer can alternatively be clocked via an internal 1.25MHz, 2.5MHz, 5MHz, 10MHz, or 20MHz clock as selected via control register bits 12, 11, and 10.

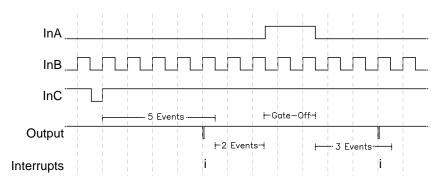

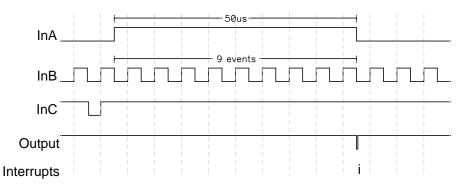

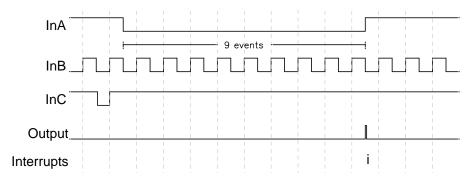

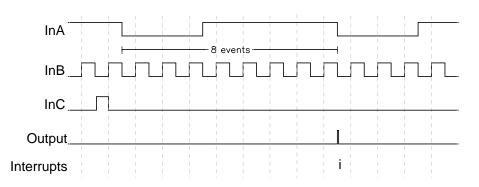

InC can be used to either continue/stop watchdog counting or as an external trigger input. When control register bits 9 and 8 are set to logic "11", InC functions as a Continue/Stop signal. When the Continue/Stop signal is high the counter continues counting (when low the counter stops counting). Alternately, when control register bits 9 and 8 are set to logic "01" or "10", the InC input functions as an external trigger input. The watchdog timer may also be internally triggered (via the Trigger Control Register at the base address + offset 34H).