D/7164\_FI-1.x/FI-2.x/FI-4.x/FI-6.x/22 May 2015

## **DATASHEET**

Provisional Issue

## 7164FI-1.x, 7164FI-2.x, 7164FI-4.x and 7164FI-6.x Multi Mode Modem

## **Features**

- Half-duplex modem supports multiple modulations and channel spacings

- 7164FI-1.x

- o GMSK/GFSK with BT=0.5, 0.3, 0.27 or 0.25

- Over-air compatible with FX/MX909B and CMX7143FI-1.x

- o Two frame sync detectors

- o Automatic frame sync detect

- o Rx carrier frequency correction

- Receive signal quality measurement

- 7164FI-2.x

- 2/4/8/16-FSK up to 10ksymbols/s in 25kHz e.g. 40kbps for 16-FSK

- Compatible FEC for CMX7143 and FX/MX919B 4-FSK (not 2-FSK)

- Over-air compatibility with CMX969 for RD-LAP Tx/Rx

- Two frame sync detectors

- Automatic frame sync detect

- Rx carrier frequency correction

- Receive signal quality measurement

- 7164FI-4.x

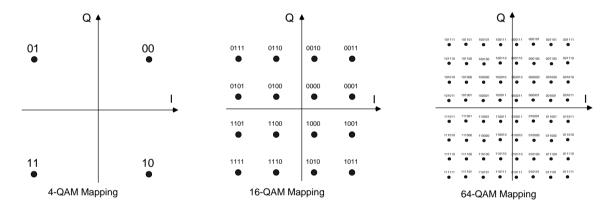

- o 4/16/64 QAM up to 96kbps in 25kHz

- o Different rate, robust FEC choices

- o Channel estimation and equalisation

- Two frame sync detectors

- Automatic frame sync detect

- o Rx carrier frequency and phase correction

- o Receive signal quality measurement

- 7164FI-6.x

- o V.23 modulation

- o Two frame sync detectors

- o Automatic frame sync detect

- Rx carrier frequency correction

- o Receive signal quality measurement

- High Performance I/Q Radio Analogue Interface

- Tx and Rx: 'direct connect' to zero IF transceiver

- Simple external RC filters

- Digital IF filter reconfigures for multiple RF channel spacings (Rx)

- Deviation control without manual trim (Tx)

- o I/Q trims

- C-BUS host Serial Interface

- SPI-like with register addressing

- Read/Write 128-byte FIFOs and data buffers streamline transfers and relax host service latency

- Auxiliary Functions

- o Four 10-bit DACs

- o Autonomous RAMDAC sequencer

- Automatic support for dc calibration of CMX998

- o Four 10-bit ADCs

- ADC averaging and trip on high/low 'watch' modes

- o Four GPIO

- Sequence GPIO on Tx or Rx trigger

- Start Tx on digital trigger input

- Master C-BUS/SPI Serial Interface

- For external slave devices e.g. RF transceiver and synthesiser

- Pass-through mode expands host C-BUS/SPI capacity

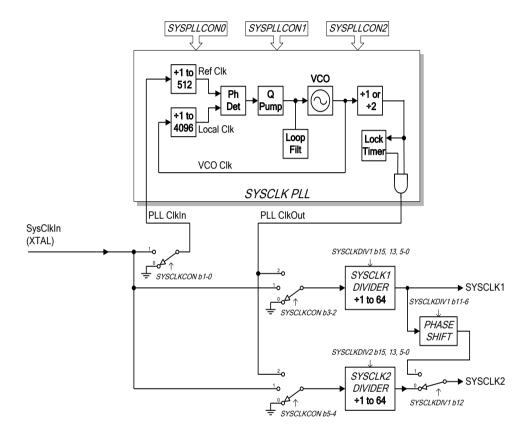

- Two Synthesised Clock Generators

- Low Power 3.3V Operation with Powersave Functions

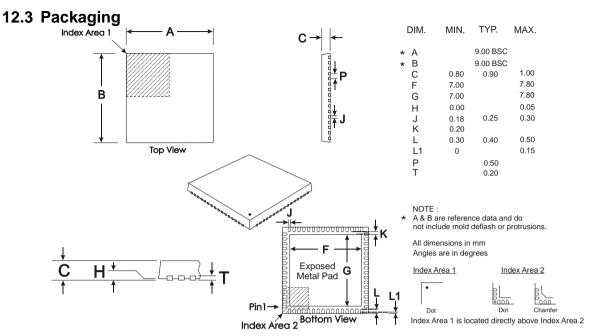

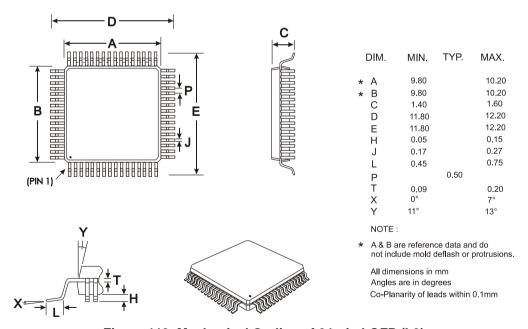

- Small 64-pin VQFN and LQFP Packages

## **Applications**

- High Performance Narrowband Data Radio

- Telemetry/SCADA/data modems

- 6.25kHz to 25kHz RF channel spacing

- Compatible worldwide e.g. ETSI, FCC, ARIB, etc.

- FCC Part 90 per new spectral efficiency requirements

- Digital Software Defined Radio (SDR)

- High-speed Wireless Data

- Mobile Data over Fading Channels

- V.23 compatibility for interoperability with legacy equipment in the field

## 1 Brief Description

The CMX7164 Multi Mode Modem is a half-duplex device currently supporting GMSK/GFSK, 4/16/64-QAM, 2/4/8/16-Level FSK and V.23 modes in multiple channel spacings under host control. Its \*Function Image (FI) is loaded to initialise the device and determine modulation types.

The 7164FI-1.x supports GMSK/GFSK modulation, with BT=0.5, 0.3, 0.27, or 0.25. User-programmable filters are also possible (contact CML Technical Support for further information). The 7164FI-1.x supports up to 20kbps. Flexible bit rates support a wide range of applications requiring a selectable bit rate and robustness. The 7164FI-1.x supports zero IF (I/Q) and two-point modulation (Mod1/2) transmit modes, with zero IF receive mode. The GMSK/GFSK data is over-air compatible with the FX/MX909B and the CMX7143FI-1.x.

The 7164Fl-2.x supports 2-FSK, 4-FSK, 8-FSK, and 16-FSK modulations, root raised cosine filtered with  $\alpha$ =0.2 with optional sinc filtering. User-programmable filters are also possible (contact CML Technical Support for further information). The 7164Fl-2.x supports up to 10ksymbols/s in a 25kHz channel. Flexible bit rates support a wide range of applications requiring a selectable bit rate and robustness. The 7164Fl-2.x supports zero IF (I/Q) and two-point modulation (Mod1/2) transmit modes, with zero IF receive mode. The data is over-air compatible with the FX/MX919B and the (CMX)7143Fl-2.x. Additionally, 4-FSK coded mode also supports RD-LAP channel coding which is over-air compatible with CMX969.

The 7164FI-4.x supports 4-, 16- and 64-QAM modulations, root raised cosine filtered with  $\alpha$ =0.2, 0.35 or a user programmable filter (contact CML Technical Support for further information). The 7164FI-4.x supports up to 96kbps in a 25kHz channel, with channel estimation and equalisation to provide robust performance under realistic channel conditions. The 7164FI-4.x supports zero IF (I/Q) transmit and receive. QAM data is over-air compatible with the CMX7163FI-4.x.

The 7164FI-6.x supports V.23 modulation at 1200 baud to provide half-duplex modem functionality for interoperability with legacy equipment in the field. The 7164FI-6.x supports 1 to 8 byte data blocks with start bit, stop bit and parity generation in transmit and start bit, stop bit and parity checking and removal in receive.

Within this Datasheet and the accompanying User Manual any reference to FI1-x, FI-2.x, FI-4.x or FI-6.x is intended to refer to 7164FI1.x, 7164FI-2.x, 7164FI-4.x or 7164FI-6.x respectively.

Forward error correction and raw modes are available and support user-defined packet structures to support a range of applications. For greater flexibility, in FI-4.x only, different rate FEC modes are

provided. Receive signal quality measurement is supported, making a useful assessment of link conditions.

High-performance digital IF filters may be reconfigured to support multiple channel spacings via host command. This feature may eliminate the need to switch between multiple discrete IF filters.

An integrated analogue interface supports 'direct connection' to zero IF I/Q radio transceivers with few external components; no external codecs are required.

Intelligent auxiliary ADC, DAC and GPIO sub-systems perform valuable functions and minimise host interaction and host I/O resources. Two synthesised system clock generators develop clock signals for off-chip use. The C-BUS/SPI master interface expands host C-BUS/SPI ports to control external devices.

\*Function Image™. The device utilises CML's proprietary FirmASIC® component technology. On-chip sub-systems are configured by a Function Image™ data file that is uploaded during device initialisation and defines the device's function and feature set. The Function Image™ can be loaded automatically from a host μC over the C-BUS serial interface or from an external memory device. The device's functions and features can be enhanced by subsequent Function Image™ releases, facilitating in-the-field upgrades.

The CMX7164 operates from a 3.3V supply and includes selectable powersaving modes. It is available in 64-VQFN and 64-LQFP packages.

Note that text shown in pale grey indicates features that will be supported in future versions of the device.

This Data Sheet is the first part of a two-part document.

## **CONTENTS**

| <u>Sect</u> | <u>ion</u>   | ļ                                                                     | Page |

|-------------|--------------|-----------------------------------------------------------------------|------|

| 1           | Brief Descri | ption                                                                 | 2    |

|             | 1.1 Histo    | ory                                                                   | 10   |

| 2           | Block Diagr  | ams                                                                   | 13   |

|             | •            |                                                                       |      |

| 3           | Signal List  |                                                                       | 16   |

| 4           | PCB Layout   | Guidelines and Power Supply Decoupling                                | 19   |

| 5           | External Co  | mponents                                                              | 20   |

|             | 5.1 Xtal     | Interface                                                             | 20   |

|             |              | US Interface                                                          |      |

|             |              | Output Reconstruction Filter                                          |      |

|             |              | nput Antialias Filter                                                 |      |

|             | 5.5 GPI      | O Pins                                                                | 21   |

| 6           | General Des  | scription                                                             | 22   |

|             | 6.1 CM       | K7164 Features                                                        | 22   |

|             | •            | al Interfaces (I/Q Tx and Rx)                                         |      |

|             | 6.3 Sign     | al Interfaces (Two-point Tx and I/Q Rx)                               | 24   |

| 7           | Detailed De  | scriptions                                                            | 25   |

|             | 7.1 Xtal     | Frequency                                                             | 25   |

|             | 7.2 Hos      | t Interface                                                           | 25   |

|             |              | C-BUS Operation                                                       |      |

|             |              | ction Image™ Loading                                                  |      |

|             |              | FI Loading from Host Controller                                       |      |

|             |              | ng C-BUS may be used to load the Modem Command FIFO Word - \$49 write |      |

|             | _            | with the Function Image™, and the<br>FI Loading from Serial Memory    |      |

|             |              | ice Control                                                           |      |

|             |              | Normal Operation Overview                                             |      |

|             |              | Basic Tx and Rx Operation                                             |      |

|             |              | Device Configuration (Using the Programming Register)                 |      |

|             | 7.4.4        | Device Configuration (Using dedicated registers)                      | 34   |

|             | 7.4.5        | Interrupt Operation                                                   | 34   |

|             | 7.4.6        | Signal Control                                                        | 34   |

|             |              | Tx Mode                                                               |      |

|             |              | Rx Mode                                                               |      |

|             |              | Carrier Sense Mode                                                    |      |

|             |              | The Transmit Sequence                                                 |      |

|             |              | CMX998 DC Offset Calibration (I/Q Transmit Only)                      |      |

|             |              | Other Modem Modes Data Transfer                                       |      |

|             |              | Data Buffering                                                        |      |

|             |              | Raw Data Transfer                                                     |      |

|             |              | Formatted Data Transfer                                               |      |

|             |              | Pre-loading Commands                                                  |      |

|             |              | GPIO Pin Operation                                                    |      |

|             |              |                                                                       |      |

|    | 7.4.                | 19 Auxiliary ADC Operation                                 | 52  |  |  |

|----|---------------------|------------------------------------------------------------|-----|--|--|

|    | 7.4.2               | 20 Auxiliary DAC/RAMDAC Operation                          | 52  |  |  |

|    | 7.4.2               | 21 SPI Thru-Port                                           | 53  |  |  |

|    | 7.4.2               | 22 SPI/C-BUS AGC                                           | 54  |  |  |

|    |                     | Digital System Clock Generators                            |     |  |  |

|    | 7.5.                |                                                            |     |  |  |

|    | 7.5.2               | ·                                                          |     |  |  |

|    |                     | Signal Level Optimisation                                  |     |  |  |

|    | 7.6.                |                                                            |     |  |  |

|    | 7.6.2               | , -                                                        |     |  |  |

|    |                     | C-BUS Register Summary                                     |     |  |  |

| 0  |                     | 1.x Features                                               |     |  |  |

| 8  |                     | 7164FI-1.x Modulation                                      |     |  |  |

|    |                     | 7164FI-1.x Radio Interface                                 |     |  |  |

|    | 8.2.                |                                                            |     |  |  |

|    | 8.2.2               |                                                            |     |  |  |

|    |                     | 2 Two-point Modulation Transmit with I/Q Receive Interface |     |  |  |

|    |                     |                                                            |     |  |  |

|    |                     | 7164FI-1.x Typical Transmit Performance                    |     |  |  |

|    |                     | 7164FI-1.x Typical Receive Performance                     |     |  |  |

|    | 8.5.                | 1 Signal-to-Noise and Co-channel Performance               | 70  |  |  |

| 9  | 7164FI-2            | 2.x Features                                               | 74  |  |  |

|    | 9.1                 | 7164FI-2.x Modulation                                      | 74  |  |  |

|    | 9.2                 | 7164FI-2.x Radio Interface                                 | 76  |  |  |

|    | 9.2.                | 1 I/Q Transmit and I/Q Receive Interfaces                  | 76  |  |  |

|    | 9.2.2               | 2 Two-point Modulation Transmit with I/Q Receive Interface | 78  |  |  |

|    | 9.3                 | 7164FI-2.x Formatted Data                                  | 79  |  |  |

|    | 9.4                 | 7164FI-2.x Receiver Response Equaliser                     | 83  |  |  |

|    | 9.5                 | 7164FI-2.x Typical Transmit Performance                    | 84  |  |  |

|    | 9.6                 | 7164FI-2.x Typical Receive Performance                     | 91  |  |  |

|    | 9.6.                | 1 4-FSK                                                    | 91  |  |  |

|    | 9.6.2               | 2 8-FSK and 16-FSK                                         | 95  |  |  |

|    | 9.6.3               | 3 Receiver Dynamic Range                                   | 99  |  |  |

|    | 9.6.4               | 4 Receiver Response Equaliser Performance                  | 99  |  |  |

| 10 | 7164FI-4            | 4.x Features                                               | 104 |  |  |

|    |                     | 7164FI-4.x Modulation                                      |     |  |  |

|    |                     | 7164FI-4.x Radio Interface                                 |     |  |  |

|    |                     | 2.1 Control interfaces                                     |     |  |  |

|    |                     | 7164FI-4.x Formatted Data                                  |     |  |  |

|    |                     | 7164FI-4.x Receiver Response Equaliser                     |     |  |  |

|    |                     | 7164FI-4.x Typical Transmit Performance                    |     |  |  |

|    |                     | 7164FI-4.x Typical Receive Performance                     |     |  |  |

|    | 10.6                |                                                            |     |  |  |

|    |                     | 6.2 Adjacent Channel Performance                           |     |  |  |

|    |                     | 6.3 Receiver Dynamic Range                                 |     |  |  |

|    |                     | 6.4 Receiver Response Equaliser Performance                |     |  |  |

| _  |                     |                                                            |     |  |  |

| 11 | 7164FI-6.x Features |                                                            |     |  |  |

| 11.1 7164FI-6.x Modulation                                                   | 125         |

|------------------------------------------------------------------------------|-------------|

| 11.2 7164FI-6.x Radio Interface                                              | 125         |

| 11.2.1 I/Q Transmit and I/Q Receive Interfaces                               | 125         |

| 11.3 7164FI-6.x Formatted Data                                               | 125         |

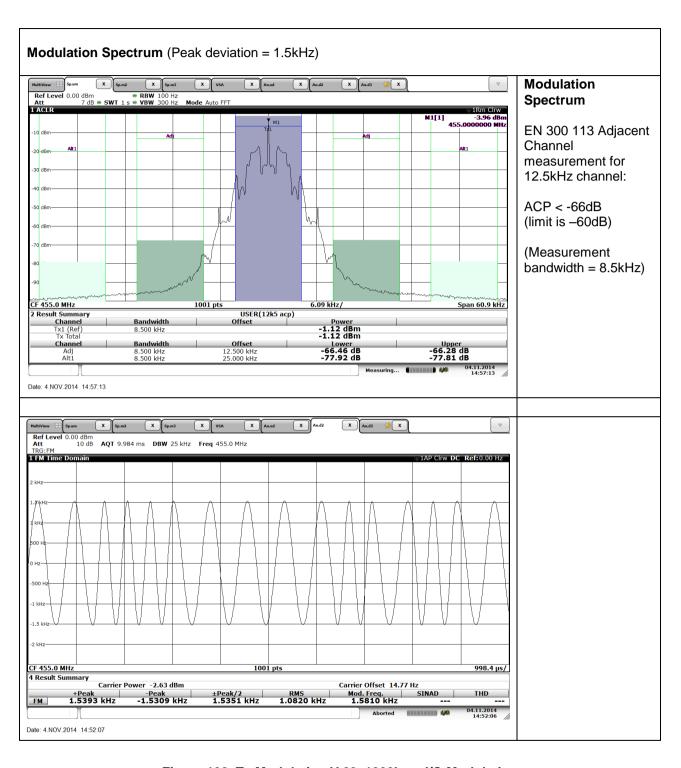

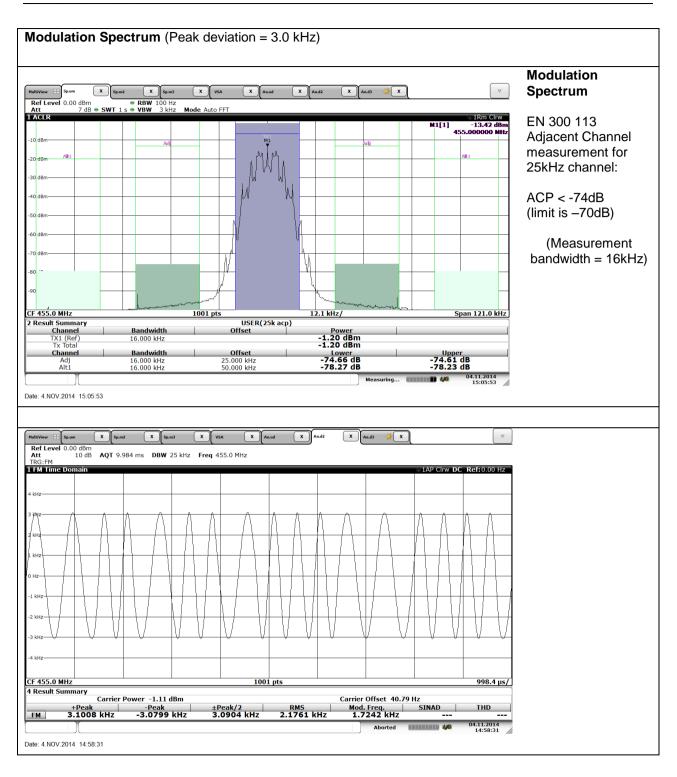

| 11.4 7164FI-6.x Typical Transmit Performance                                 | 125         |

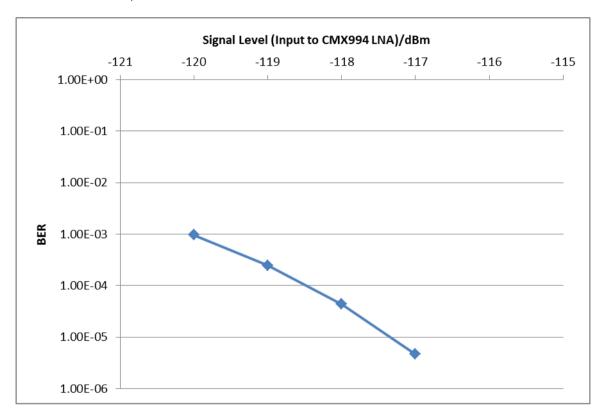

| 11.5 7164FI-6.x Typical Receive Performance                                  | 128         |

| 11.5.1 Signal-to-Noise Performance                                           | 128         |

| 11.5.2 Adjacent Channel Performance                                          | 128         |

| 12 Performance Specification                                                 | 130         |

| 12.1 Electrical Performance                                                  |             |

| 12.1.1 Absolute Maximum Ratings                                              |             |

| 12.1.2 Operating Limits                                                      |             |

| 12.1.3 Operating Characteristics                                             |             |

| 12.1.4 7164FI-1.x Parametric Performance                                     |             |

| 12.1.5 7164FI-2.x Parametric Performance                                     |             |

| 12.1.6 7164FI-4.x Parametric Performance                                     |             |

| 12.1.7 7164FI-6.x Parametric Performance                                     |             |

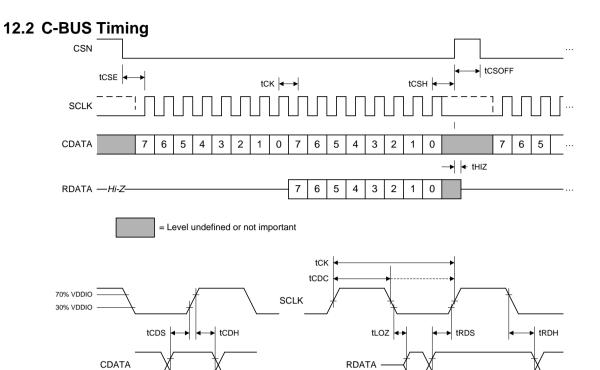

| 12.2 C-BUS Timing                                                            |             |

| 12.3 Packaging                                                               |             |

|                                                                              |             |

| <u>Table</u>                                                                 | <u>Page</u> |

| Table 1 BOOTEN Pin States                                                    | 28          |

| Table 2 C-BUS Registers                                                      |             |

| Table 3 Formatted Block Types and Sizes (FI-1.x)                             |             |

| Table 4 Native Formatted Block Types, Sizes and Rates for 4-FSK (FI-2.x)     |             |

| Table 5 Native Formatted Block Types, Sizes and Rates for 8-FSK (FI-2.x)     |             |

| Table 6 Native Formatted Block Types, Sizes and Rates for 16-FSK (FI-2.x)    |             |

| Table 7 RD-LAP Block Types, Sizes and Rates (FI-2.x)                         |             |

| Table 8 Formatted Block Types, Sizes and Rates (FI-4.x)                      |             |

| Table 9 ACR Rejection Performance                                            | 119         |

|                                                                              |             |

| <u>Figure</u>                                                                | Page        |

| Figure 1 Overall Block Diagram                                               | _           |

| Figure 2 FI-4.x Block Diagram – I/Q Tx and Rx                                |             |

| Figure 3 FI-1.x / FI-2.x Block Diagram – I/Q Tx and Rx                       |             |

| Figure 4 FI-1.x / FI-2.x Block Diagram – two-point Tx with I/Q Rx            |             |

| Figure 5 FI-6.x Block Diagram - I/Q Tx and Rx                                |             |

| Figure 6 FI-6.x Block Diagram - Two-point Tx with I/Q Rx                     |             |

| Figure 7 CMX7164 Power Supply and De-coupling                                |             |

| Figure 8 Recommended External Components – Xtal Interface                    |             |

| Figure 9 Recommended External Components – C-BUS Interface                   |             |

| Figure 10 Recommended External Components – I/Q Output Reconstruction Filter |             |

| Figure 11 CMX7164 I/Q Tx, I/Q Rx                                             |             |

| Figure 12 CMX7164 Two-point Tx, I/Q Rx                                       |             |

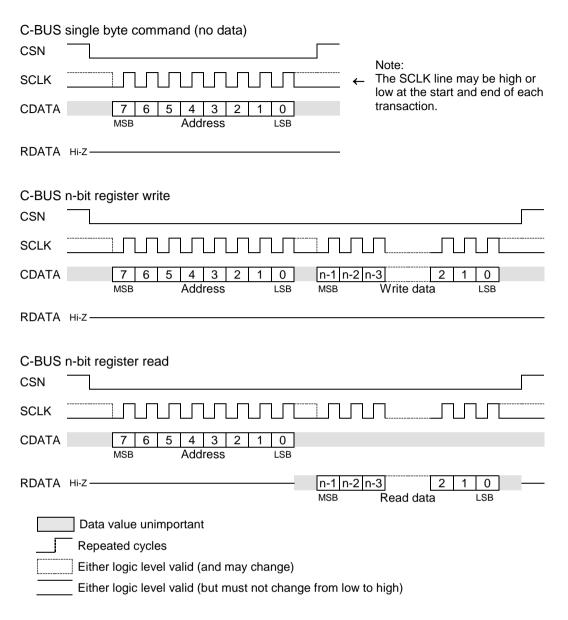

| Figure 13 Basic C-BUS Transactions                                           |             |

| Figure 14 C-BUS Data Streaming Operation                                     |             |

|                                                                              | 41          |

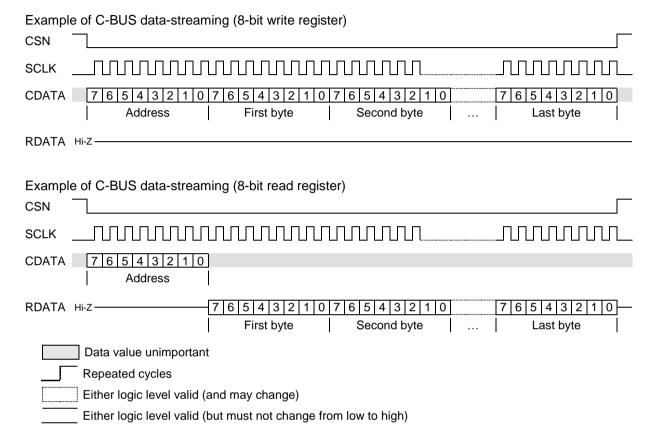

| Figure 15 | FI Loading from Host                                                              | 29 |  |  |  |

|-----------|-----------------------------------------------------------------------------------|----|--|--|--|

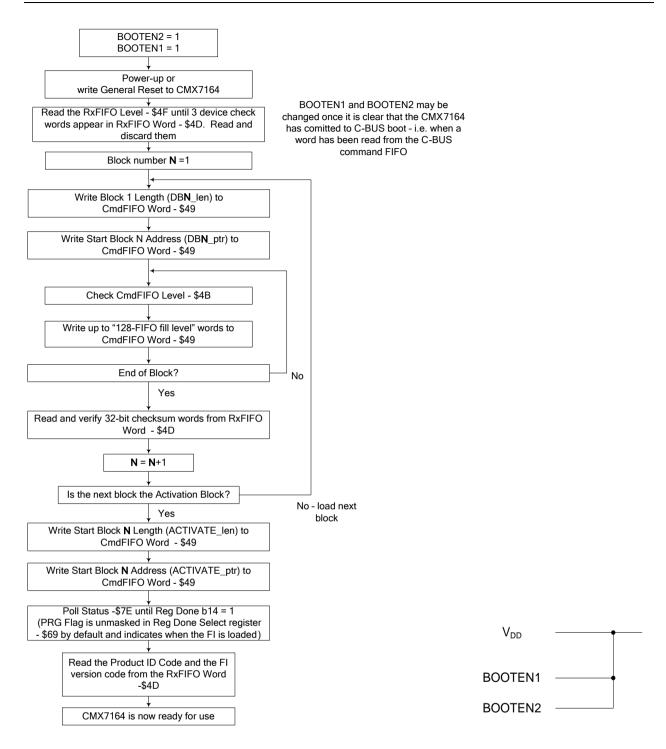

| Figure 16 | FI Loading from Serial Memory                                                     |    |  |  |  |

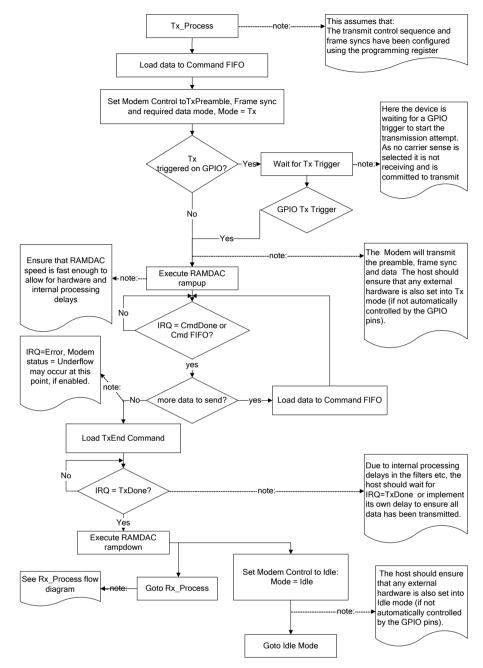

| Figure 17 | Host Tx Data Flow (No Tx Sequence/Carrier Sense)                                  | 36 |  |  |  |

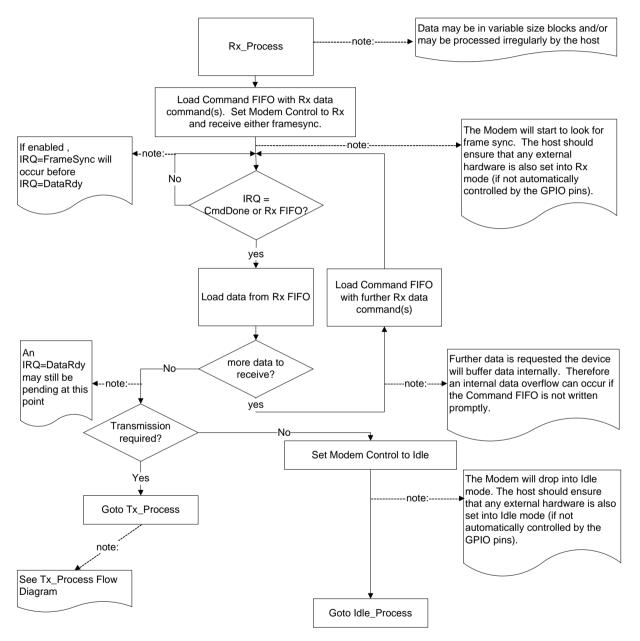

| Figure 18 | Host Rx Data Flow                                                                 | 37 |  |  |  |

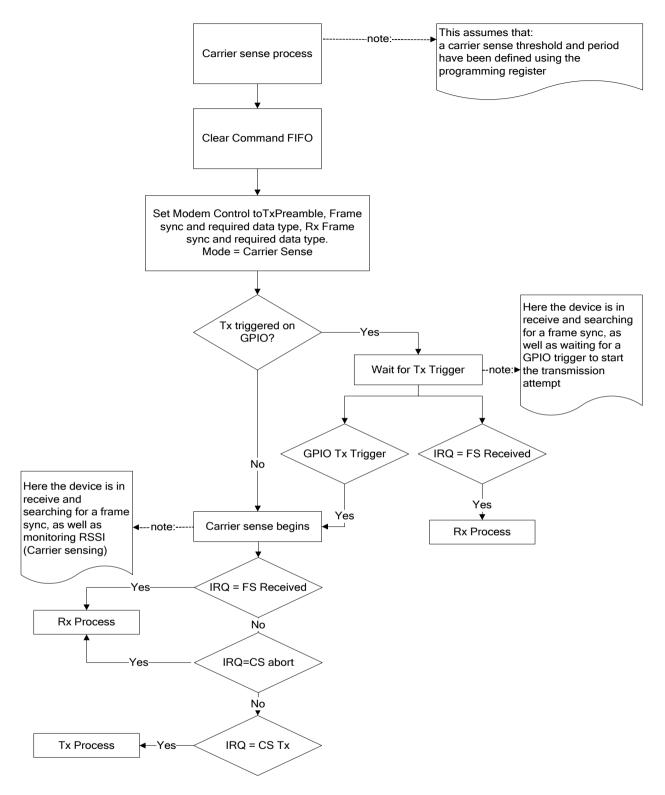

| Figure 19 | Carrier Sense                                                                     | 39 |  |  |  |

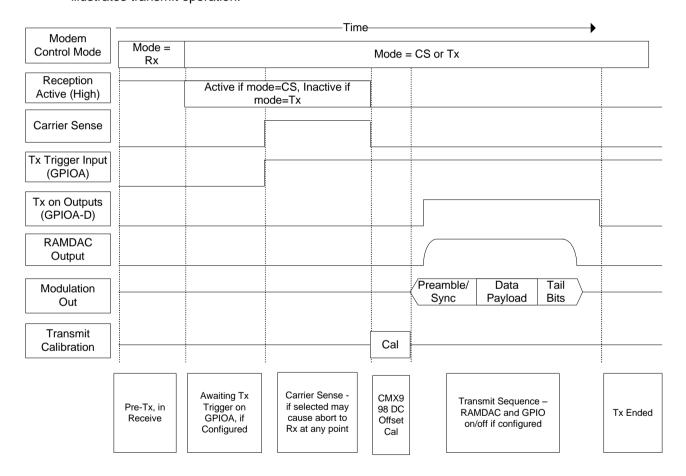

| Figure 20 | Transmit Sequence                                                                 | 40 |  |  |  |

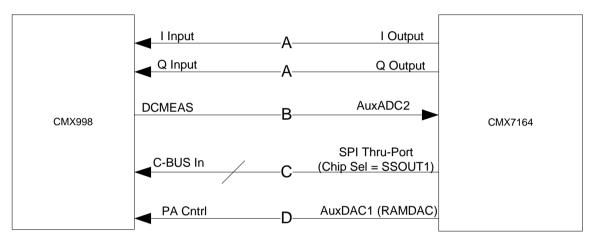

| Figure 21 | CMX998 DC Calibration Interfaces                                                  | 41 |  |  |  |

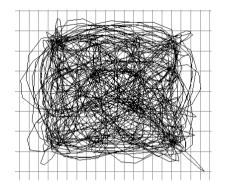

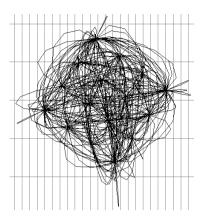

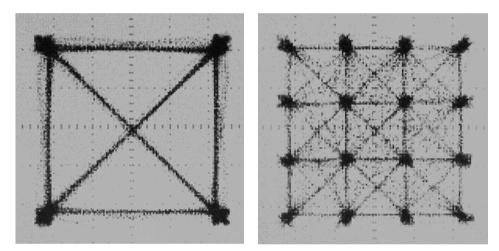

| Figure 22 | Transmit Constellation (7164FI-4.x)                                               | 43 |  |  |  |

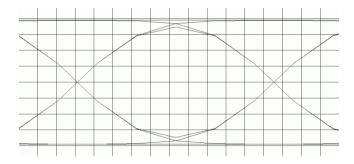

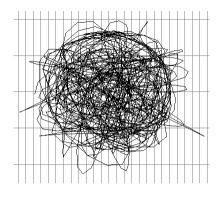

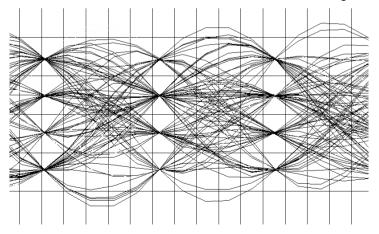

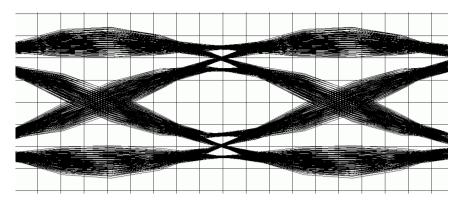

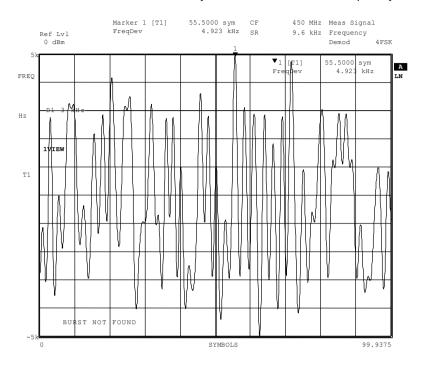

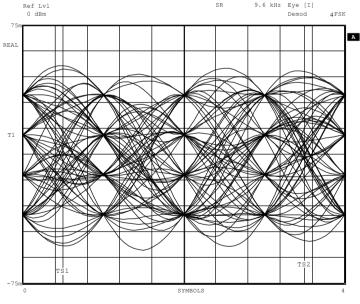

| Figure 23 | Transmit Eye Diagram (7164FI-2.x)                                                 | 43 |  |  |  |

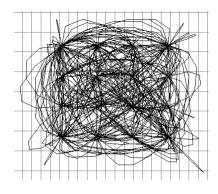

| Figure 24 | Transmit Eye Diagram (7164FI-1.x)                                                 | 43 |  |  |  |

| Figure 25 | Constellation Diagram – no frequency or phase error                               | 44 |  |  |  |

| Figure 26 | Constellation Diagram – phase error                                               | 44 |  |  |  |

| Figure 27 | Constellation Diagram – frequency error                                           | 44 |  |  |  |

| Figure 28 | Received Eye Diagram7164 FI-2.x (4-FSK mode)                                      | 44 |  |  |  |

| Figure 29 | Received Eye Diagram7164 FI-1.x                                                   | 45 |  |  |  |

| Figure 30 | Sample at Symbol Timing with I/Q DC Offset Diagnostic Mode (no frequency error)   | 45 |  |  |  |

| Figure 31 | Sample at Symbol Timing with I/Q DC Offset Diagnostic Mode (with frequency error) | 45 |  |  |  |

| Figure 32 | Normalised Constellation (even with a frequency or phase error)                   | 46 |  |  |  |

| Figure 33 | Normalised Constellation (noisy received signal)                                  | 46 |  |  |  |

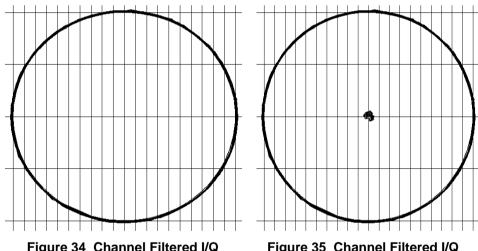

| Figure 34 | Channel Filtered I/Q Signals                                                      | 46 |  |  |  |

| Figure 35 | Channel Filtered I/Q Signals with I/Q DC Offset Estimate                          | 46 |  |  |  |

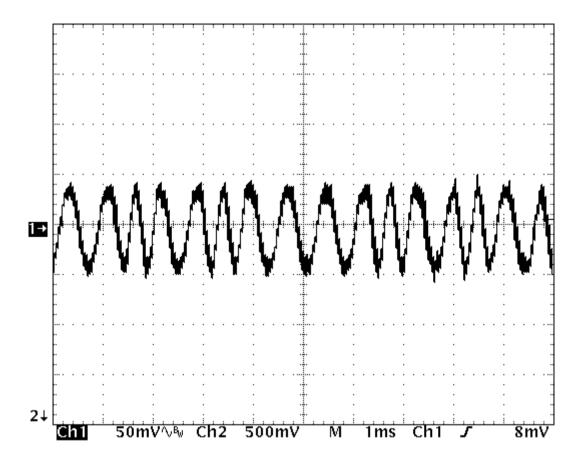

|           | Received Signal (First FM Demodulator) 7164FI-6.x.                                |    |  |  |  |

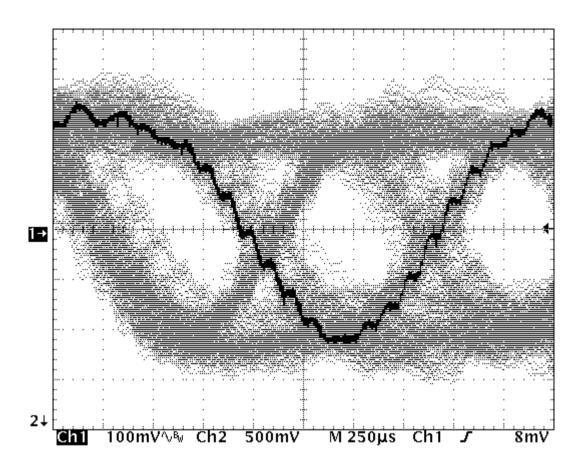

| Figure 37 | Received Signal (Second FM Demodulator) 7164FI-6.x                                | 48 |  |  |  |

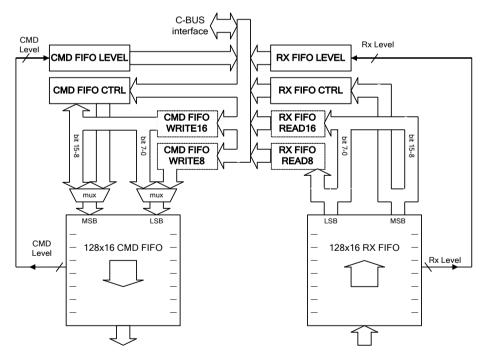

| Figure 38 | Command and Rx Data FIFOs                                                         | 49 |  |  |  |

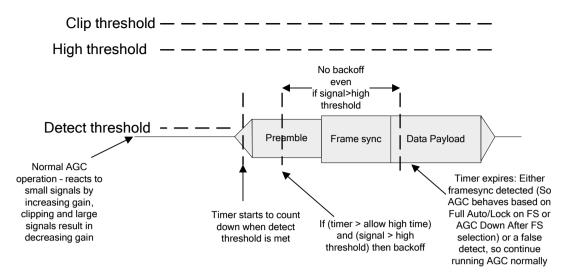

| Figure 39 | AGC using SPI Thru-Port                                                           | 54 |  |  |  |

| Figure 40 | AGC using SPI Thru-Port and external LNA                                          | 55 |  |  |  |

| Figure 41 | AGC Behaviour During Burst Reception                                              | 56 |  |  |  |

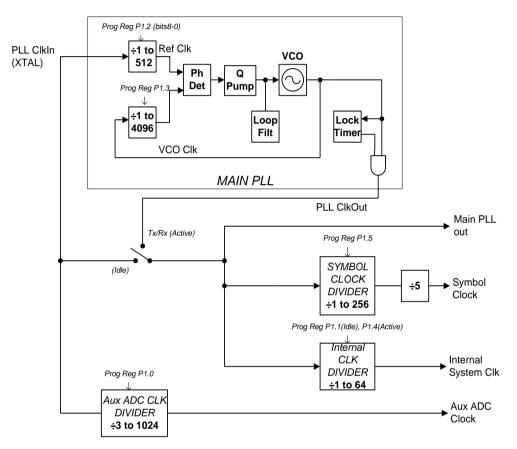

| Figure 42 | Main Clock Generation                                                             | 57 |  |  |  |

| Figure 43 | Digital System Clock Generation Schemes                                           | 58 |  |  |  |

| Figure 44 | Outline Radio Design (I/Q in/out for GMSK/GFSK)                                   | 62 |  |  |  |

| Figure 45 | Outline Radio Design (GMSK/GFSK – I/Q in, two-point mod out)                      | 63 |  |  |  |

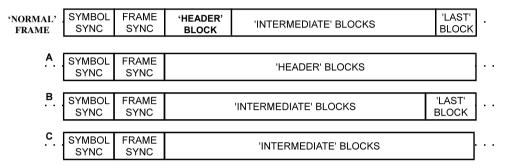

| Figure 46 | Formatted Data Over Air Signal Format                                             | 64 |  |  |  |

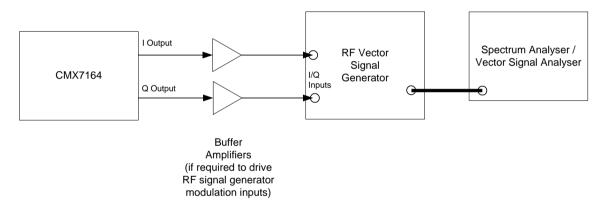

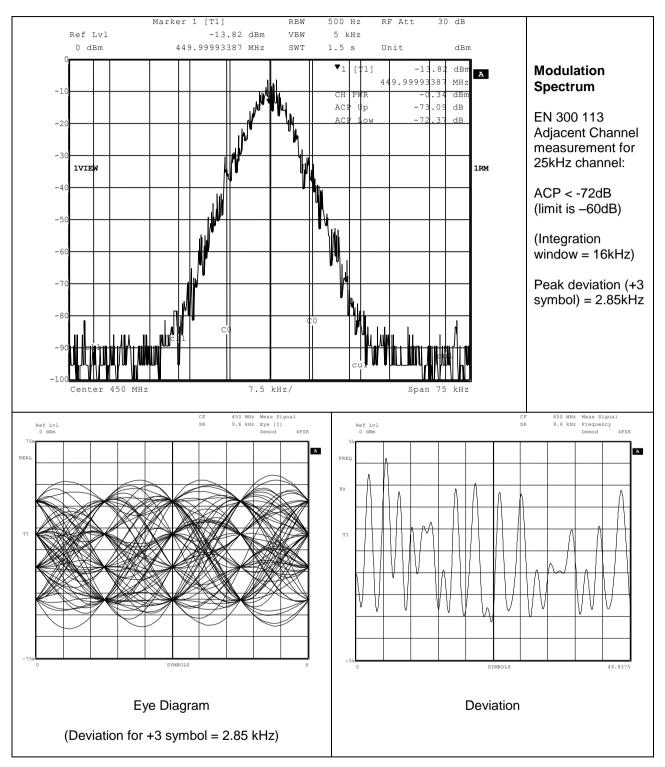

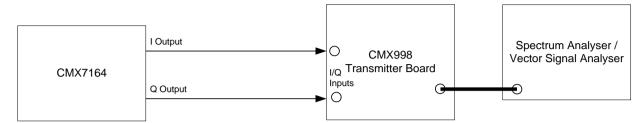

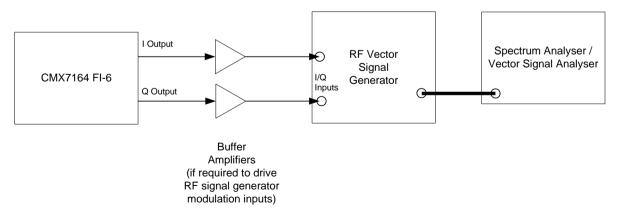

| Figure 47 | Tx Spectrum and Modulation Measurement Configuration for I/Q Operation            | 65 |  |  |  |

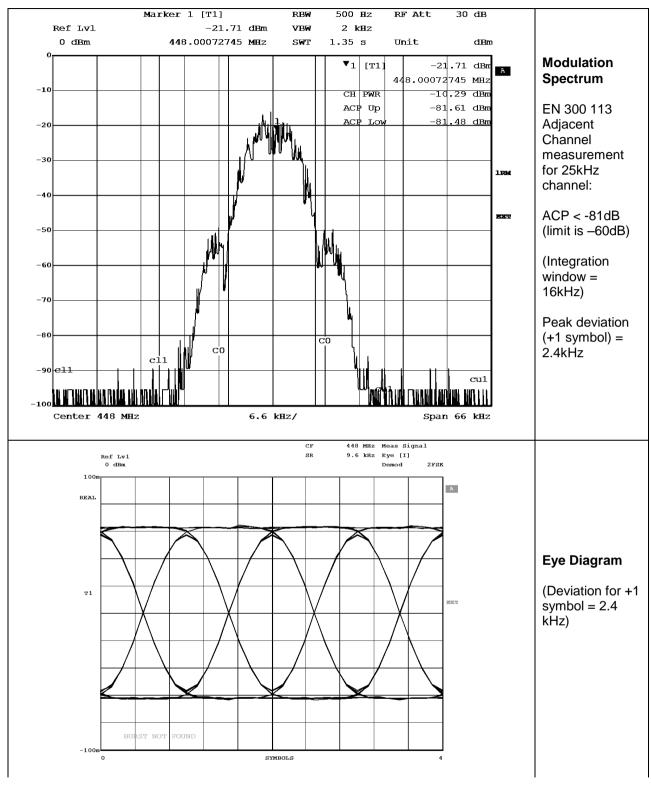

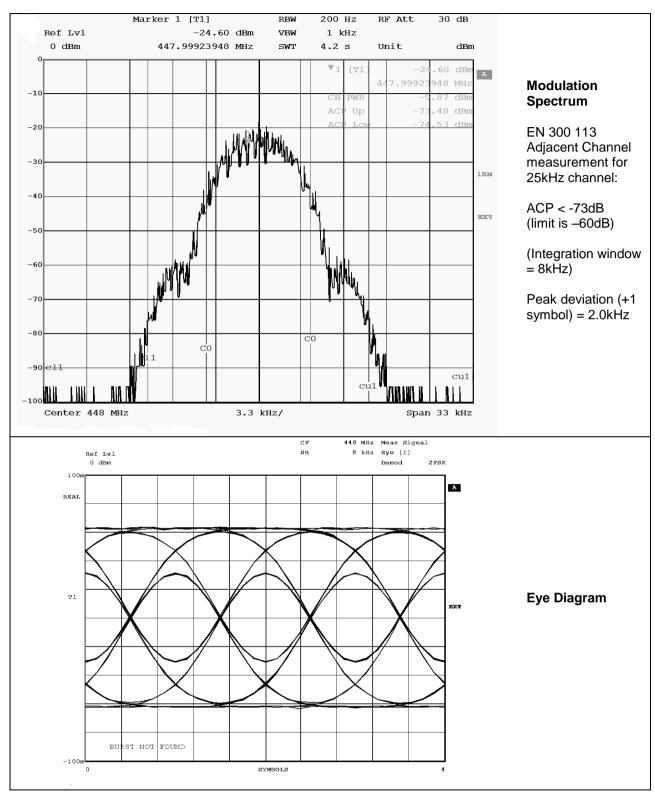

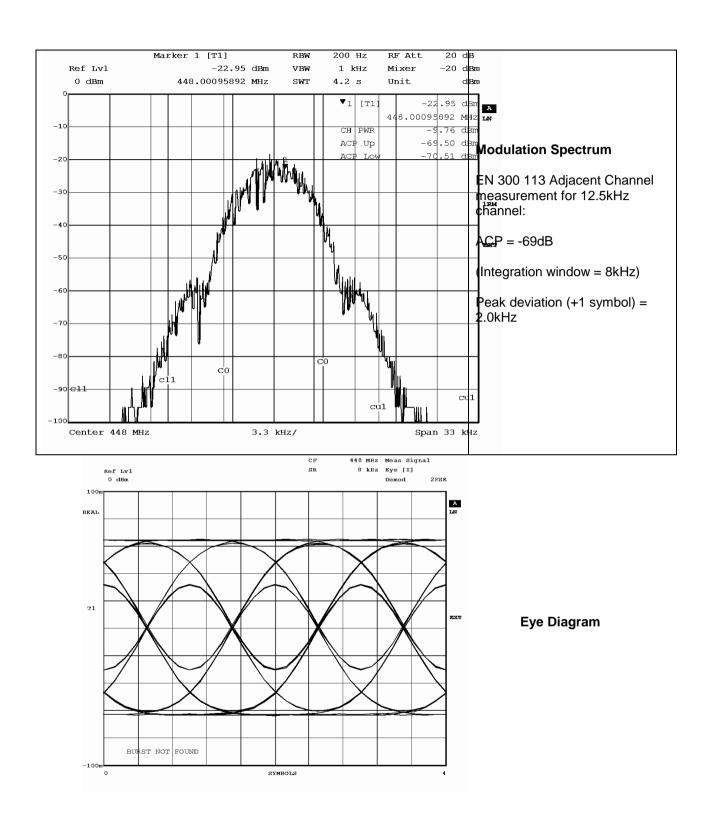

| Figure 48 | Tx Modulation Spectra (GMSK), 9.6kbps (BT=0.5), I/Q Modulation                    | 66 |  |  |  |

| Figure 49 | Tx Modulation Spectra (GMSK), 8kbps, BT=0.3 I/Q Modulation                        | 67 |  |  |  |

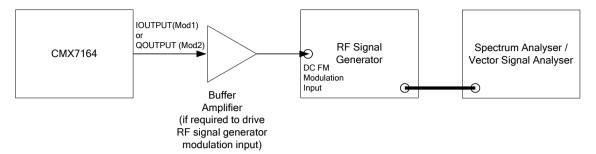

| Figure 50 | Tx Spectrum and Modulation Measurement Configuration for Two-point Modulation     | 68 |  |  |  |

| Figure 51 | Tx Modulation Spectra (GMSK), 8kbps, BT=0.3 Two-point Modulation                  | 69 |  |  |  |

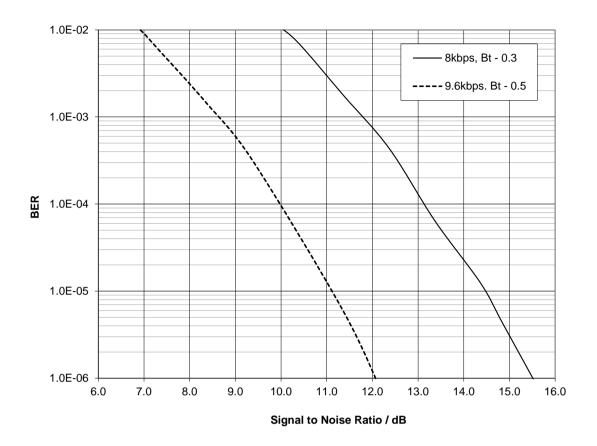

| Figure 52 | Modem Sensitivity Performance                                                     | 71 |  |  |  |

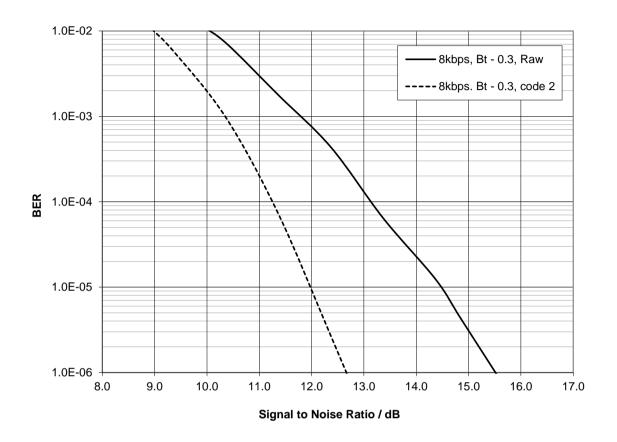

| Figure 53 | Sensitivity: 12.5kHz Channel, 8ksymbols/s With and Without Coding                 | 72 |  |  |  |

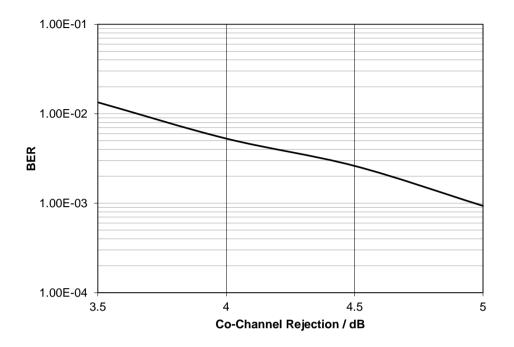

| Figure 54 | Modem Co-channel Rejection with FM Interferer (as EN 300 113)                     | 73 |  |  |  |

| Figure 55 | PRBS Waveform (Two-point Modulation)                                              | 76 |  |  |  |

| Figure 56 | Outline Radio Design (I/Q in/out for 2 or 4-FSK)                                  | 77 |  |  |  |

| Figure 57 | Outline Radio Design (2 or 4-FSK – I/Q in, two-point mod out)                     | 78 |  |  |  |

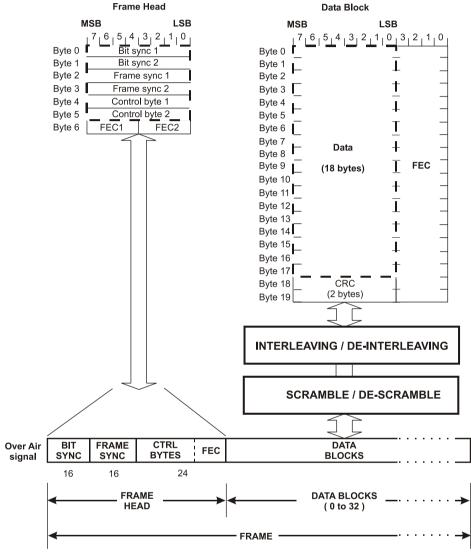

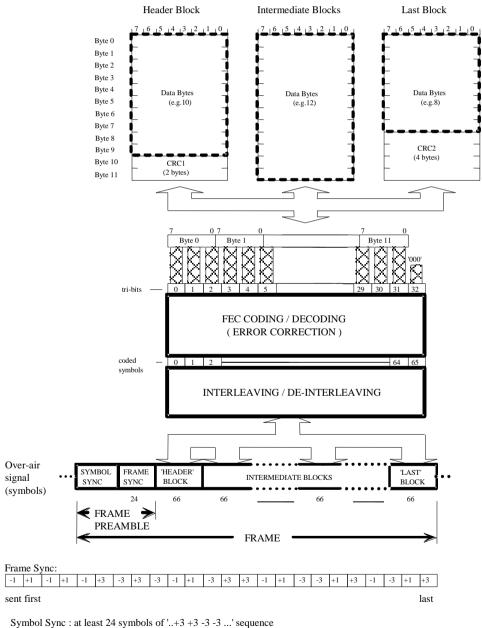

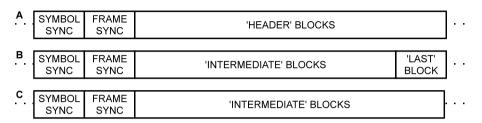

| Figure 58 | Native Formatted Data Over Air Signal Format                                      | 79 |  |  |  |

| Figure 59 | Suggested Frame Structures                                                        | 80 |  |  |  |

| Figure 60 | RD-LAP Over Air Signal Format                                                     | 82 |  |  |  |

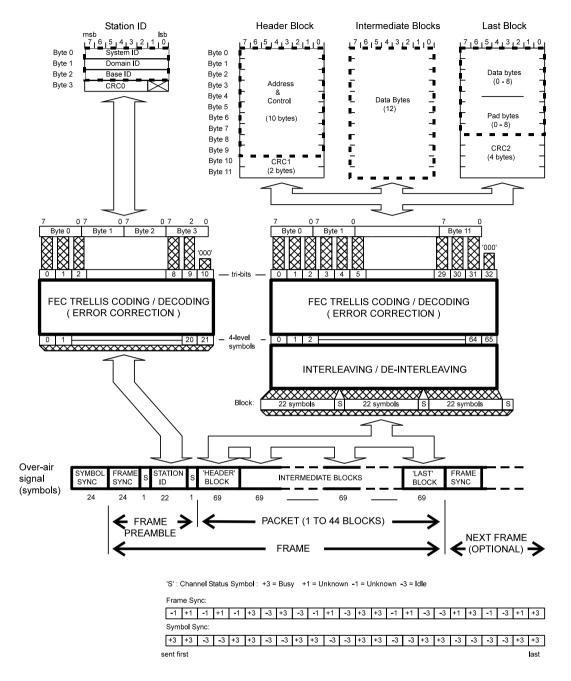

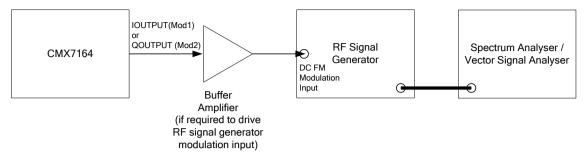

| Figure 61 | Tx Spectrum and Modulation Measurement Configuration for I/Q Operation            | 84 |  |  |  |

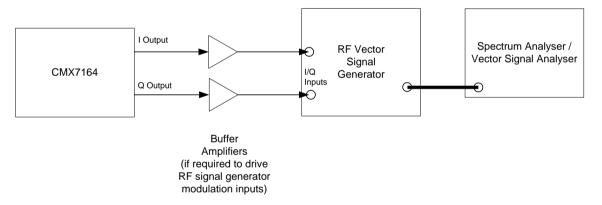

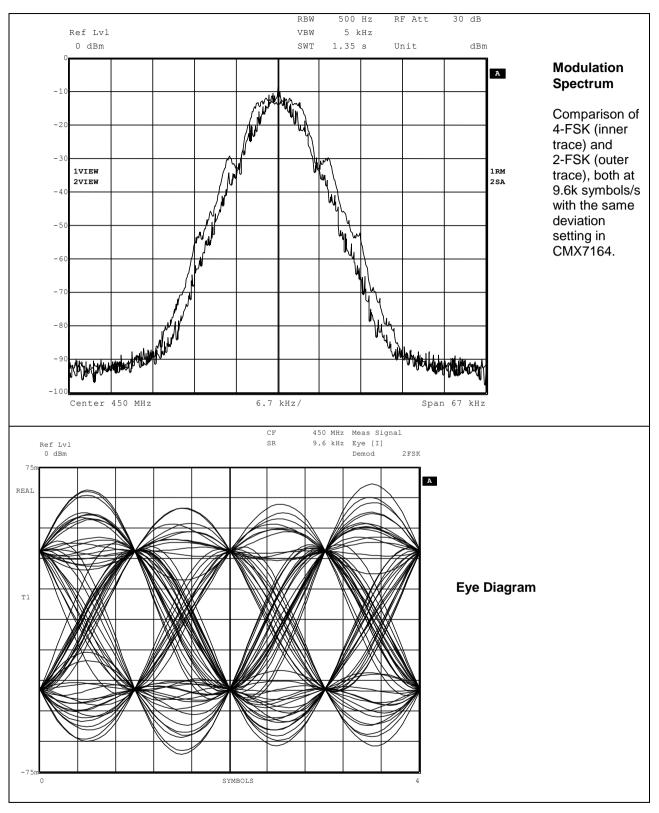

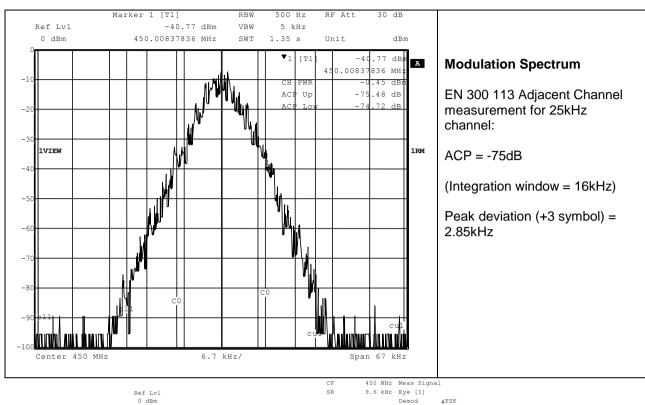

| Figure 62 | Tx Modulation Spectra (4-FSK), 9.6ksymbols/s (19.2kbps), I/Q Modulation           | 85 |  |  |  |

| Figure 63             | Tx Modulation Spectra (2-FSK), 9.6k symbols/s (9.6kbps), I/Q Modulation        | . 86 |  |  |

|-----------------------|--------------------------------------------------------------------------------|------|--|--|

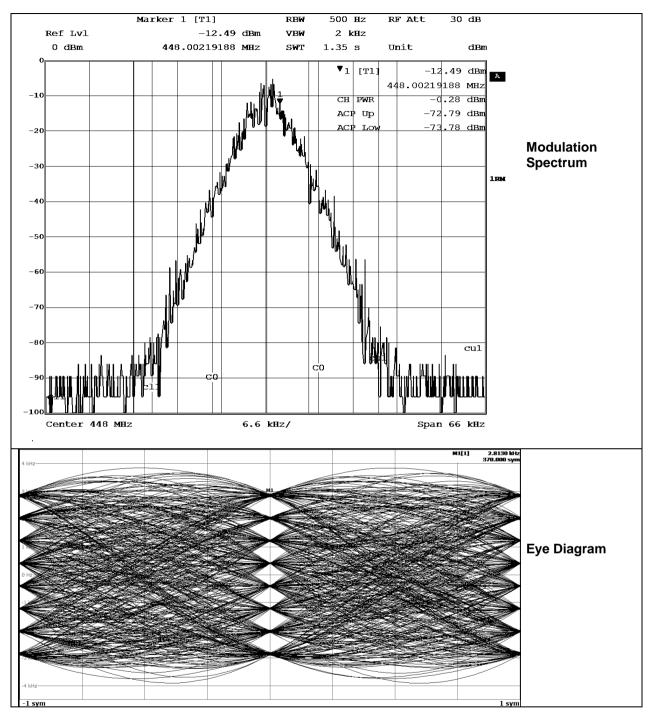

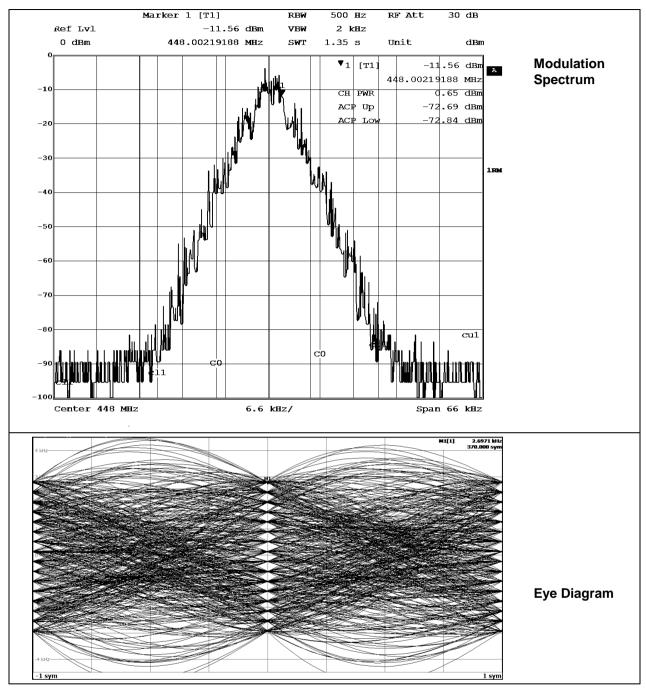

| Figure 64             | Tx Modulation Spectra (8-FSK), 9.6k symbols/s (28.8kbps), I/Q Modulation       | . 87 |  |  |

| Figure 65             | Tx Modulation Spectra (16-FSK), 9.6k symbols/s (38.4kbps), I/Q Modulation      | . 88 |  |  |

| Figure 66             | Tx Spectrum and Modulation Measurement Configuration for Two-point Modulation  | . 89 |  |  |

| Figure 67             | Tx Modulation Spectra (4-FSK), 19.2kbps, Two-point Modulation                  | . 90 |  |  |

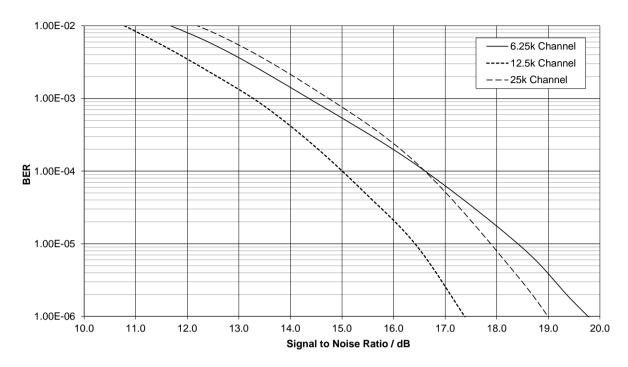

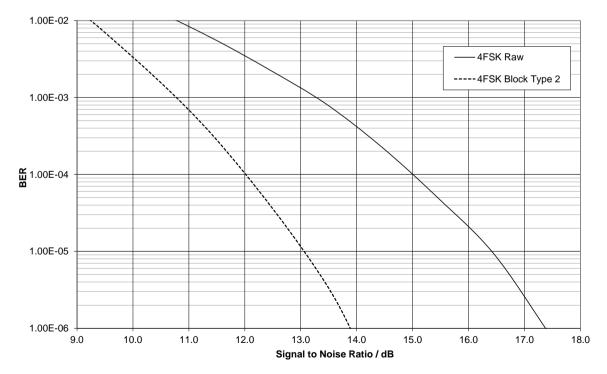

| Figure 68             | Modem Sensitivity Performance (Root Raised Cosine Pulse Shaping)               | . 92 |  |  |

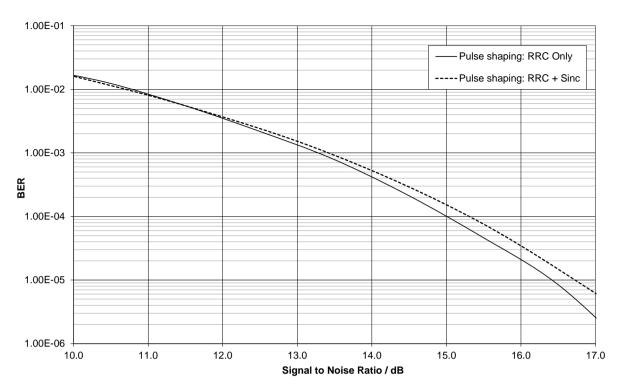

| Figure 69             | 12.5kHz Channel Sensitivity With and Without Sinc Filter Comparison            | . 93 |  |  |

| Figure 70             | Sensitivity: 12.5kHz Channel, 4.8ksymbols/s With and Without Coding            | . 93 |  |  |

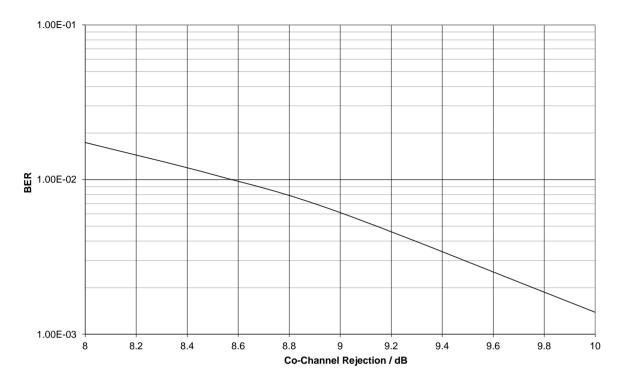

| Figure 71             | Modem Co-channel Rejection with FM Interferer (as EN 300 113)                  | . 94 |  |  |

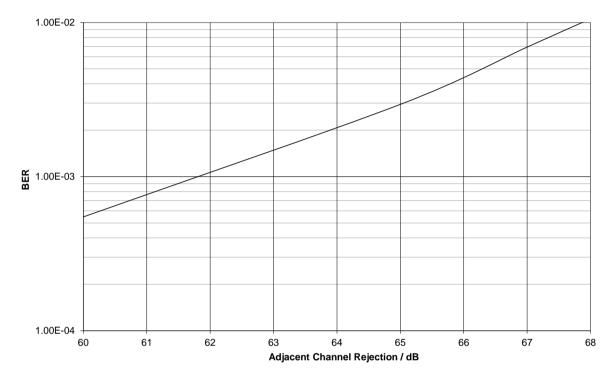

| Figure 72             | ACR Rejection Performance                                                      | . 95 |  |  |

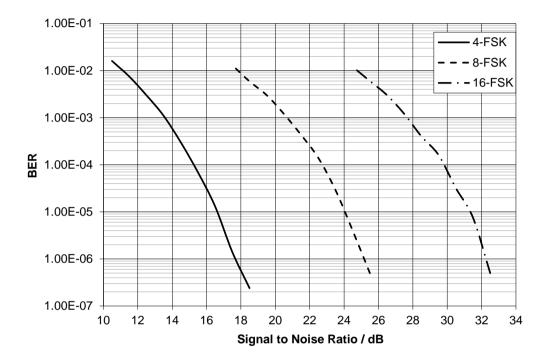

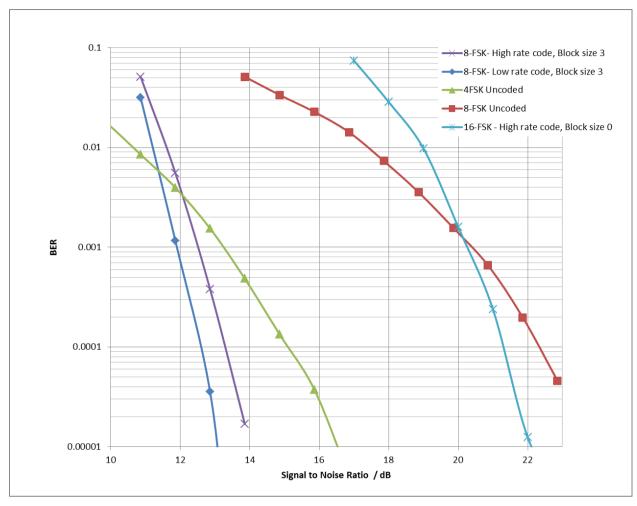

|                       | Signal to Noise Performance - Comparison of uncoded (raw) 4-FSK, 8-FSK and     |      |  |  |

|                       |                                                                                |      |  |  |

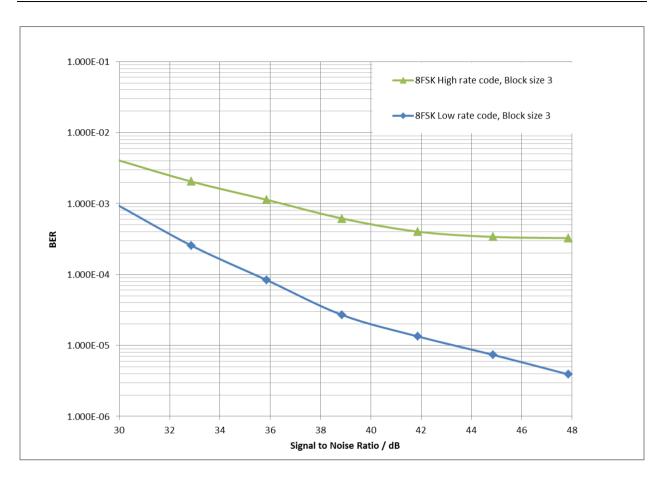

| •                     | 8-FSK and 16-FSK Coding Performance in Static Channel                          |      |  |  |

| •                     | 8-FSK Coding Performance in TU50 Fading Channel, 150MHz                        |      |  |  |

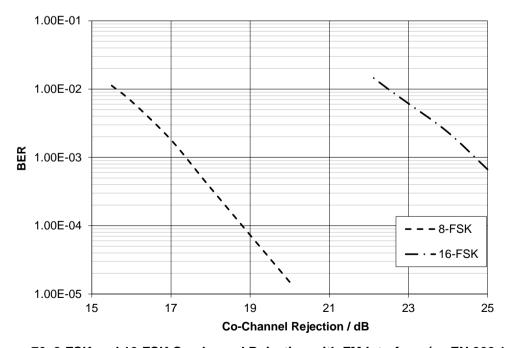

| -                     | 8-FSK and 16-FSK Co-channel Rejection with FM Interferer (as EN 300 113)       |      |  |  |

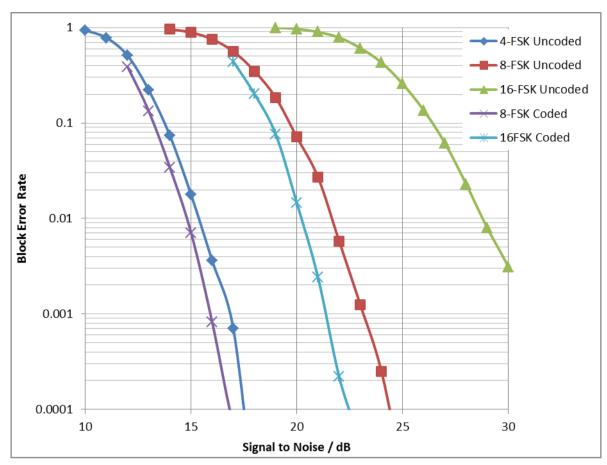

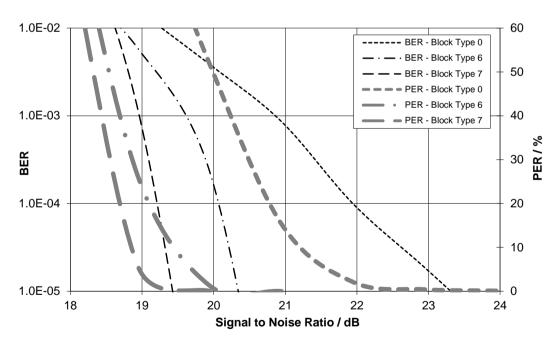

| _                     | 8-FSK and 16-FSK Block Error Rate, Block Size 0, High Rate Code, 12 Byte Block |      |  |  |

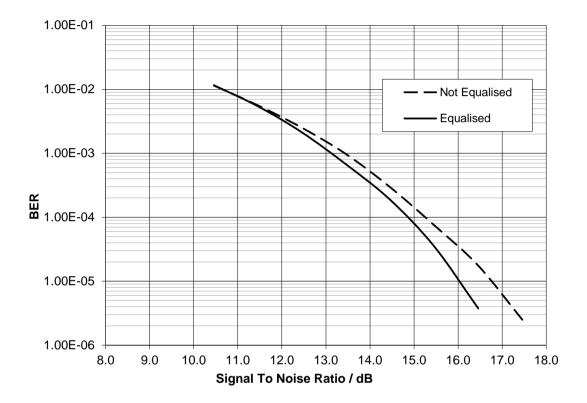

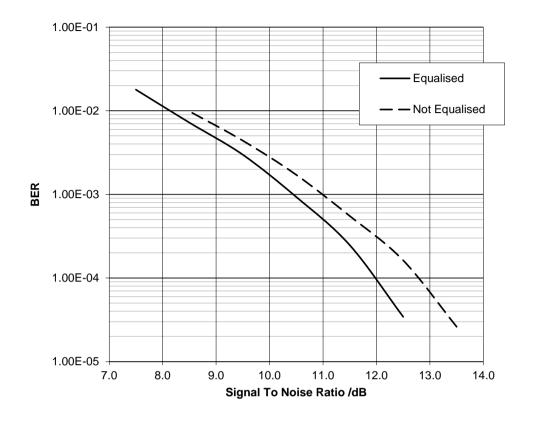

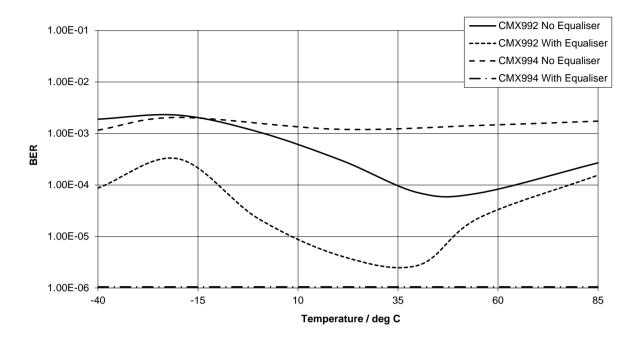

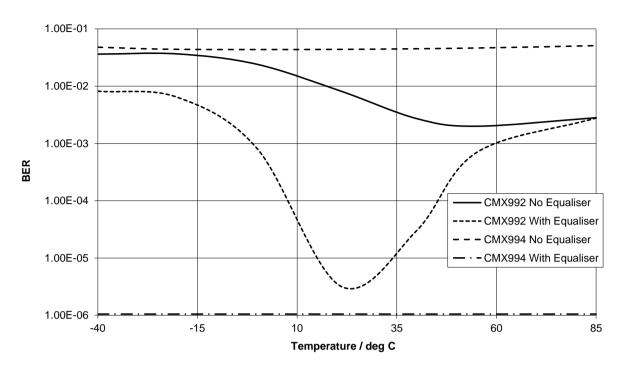

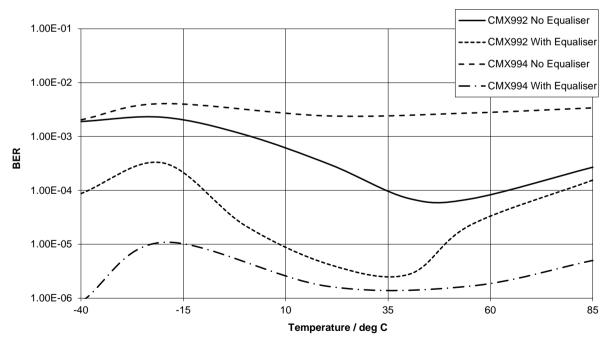

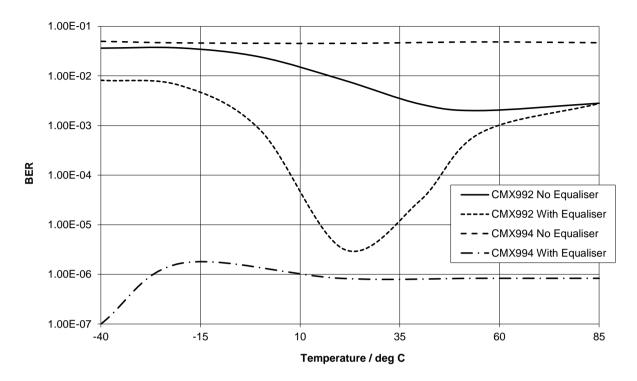

|                       | 4-FSK Signal-to-Noise Performance, Equalised and Non-Equalised                 |      |  |  |

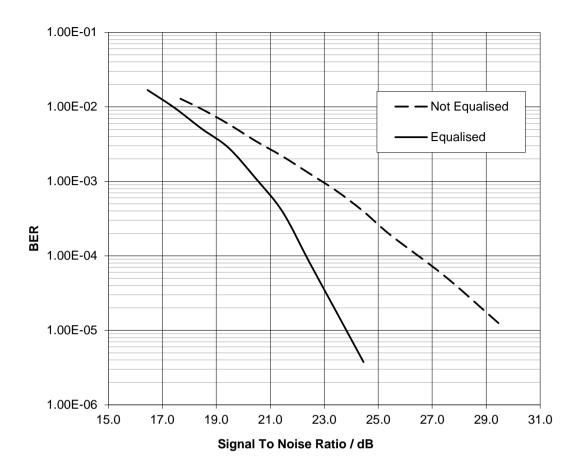

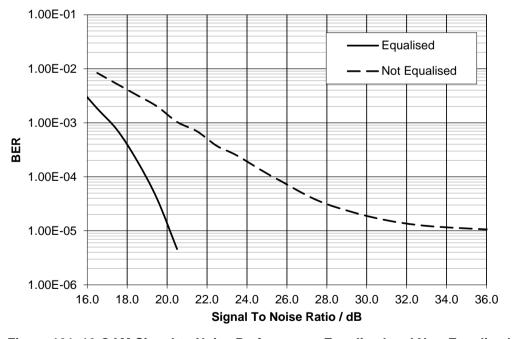

| -                     | 8-FSK Signal-to-Noise Performance, Equalised and Non-Equalised                 |      |  |  |

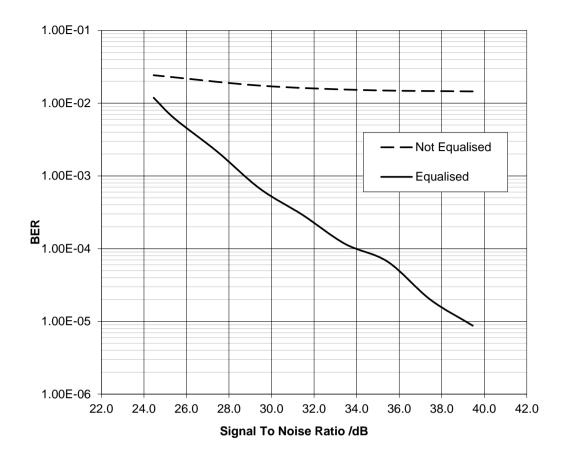

| •                     | 16-FSK Signal-to-Noise Performance, Equalised and Non-Equalised                |      |  |  |

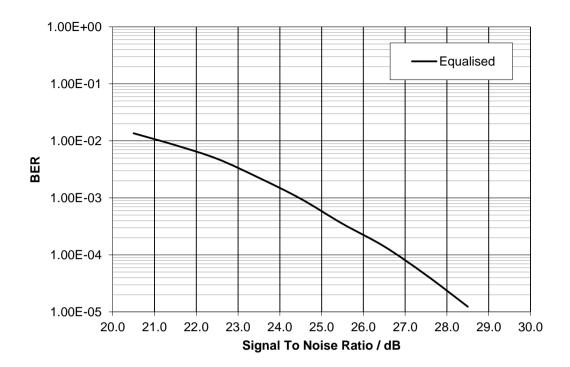

| •                     | ·                                                                              |      |  |  |

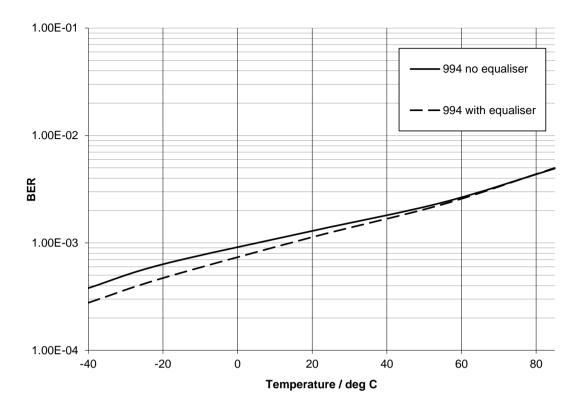

| _                     | Performance of Equalised Signals with Temperature Variation                    |      |  |  |

| -                     | QAM Mappings                                                                   |      |  |  |

|                       | Outline Radio Design (I/Q in/out for QAM)                                      |      |  |  |

| -                     |                                                                                |      |  |  |

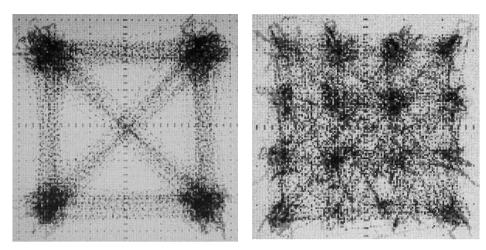

| -                     | Received 4 and 16-QAM signals, no equalisation                                 |      |  |  |

| •                     | Received 4 and 16-QAM signals with equalisation                                |      |  |  |

| •                     | Tx Spectrum and Modulation Measurement Configuration for I/Q Operation         |      |  |  |

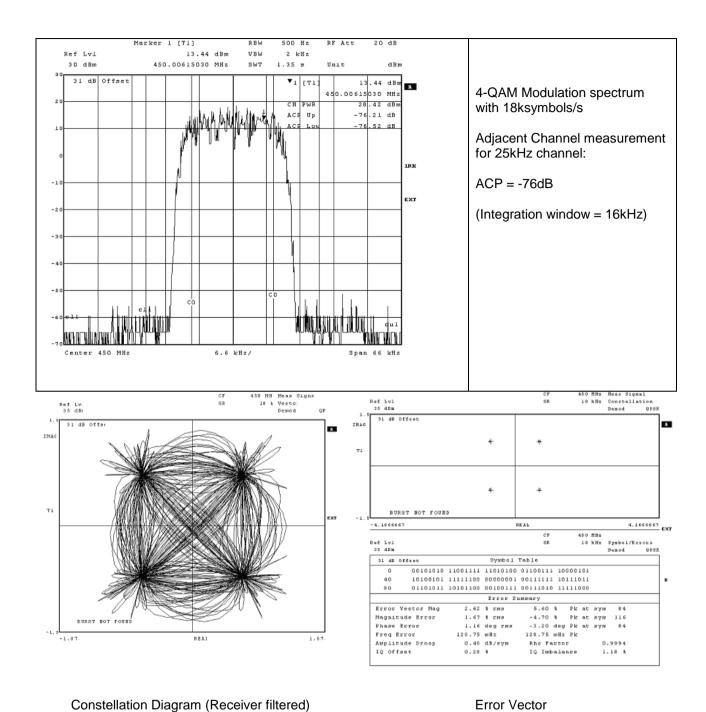

| •                     | Tx Modulation Spectra (4-QAM), 18ksymbols/s I/Q Modulation into CMX998         |      |  |  |

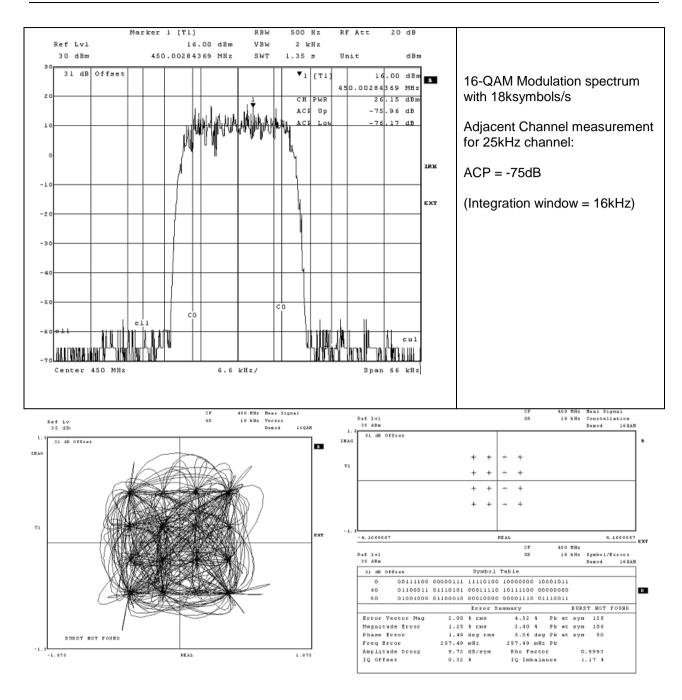

| •                     | Tx Modulation Spectra (16-QAM), 18ksymbols/s I/Q Modulation into CMX998        |      |  |  |

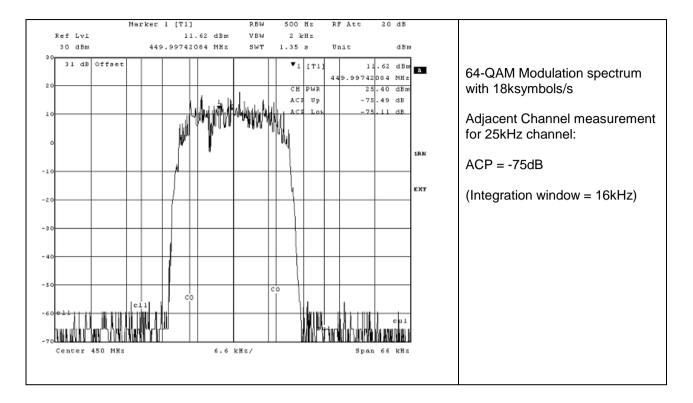

|                       | Tx Modulation Spectra (64-QAM), 18ksymbols/s I/Q Modulation into CMX998        |      |  |  |

|                       | Tx Modulation Spectra (16-QAM), 9ksymbols/s I/Q Modulation into CMX998         |      |  |  |

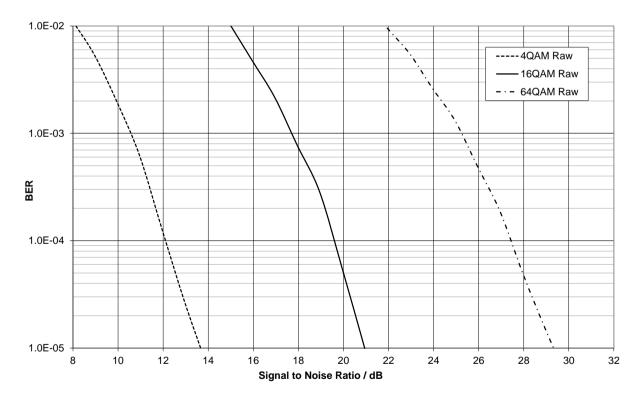

| -                     | Modern Sensitivity Performance                                                 |      |  |  |

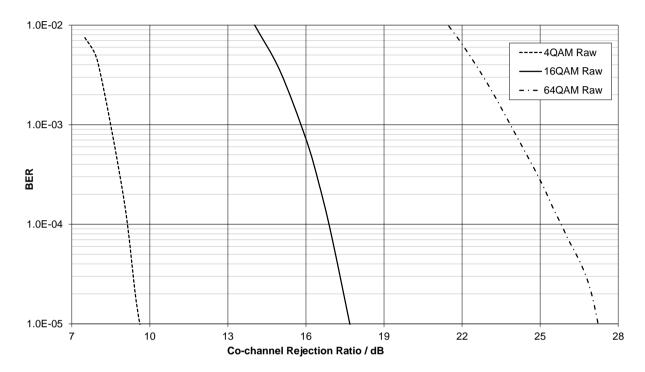

| •                     | Modem Co-channel Rejection with FM Interferer (as EN 300 113)                  |      |  |  |

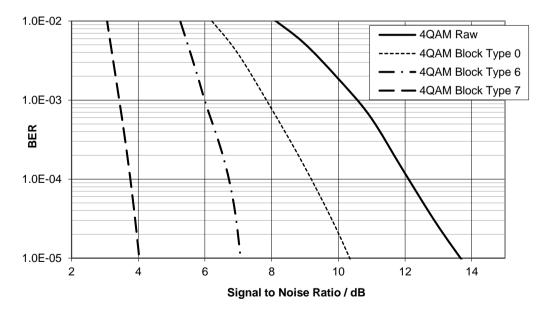

| _                     | 4-QAM Performance with Different Coding Schemes                                |      |  |  |

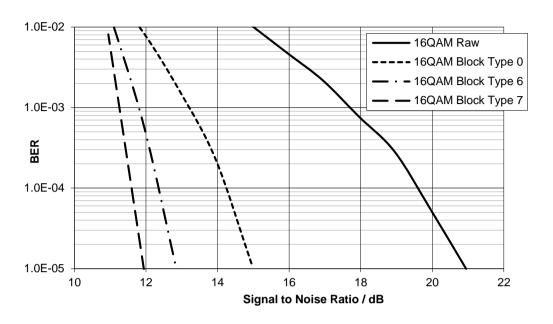

| -                     | 16-QAM Performance with Different Coding Schemes                               |      |  |  |

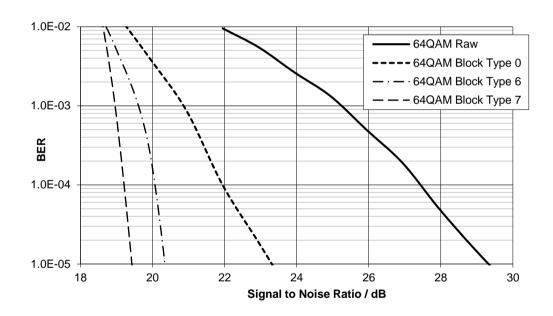

|                       | 64-QAM Performance with Different Coding Schemes                               |      |  |  |

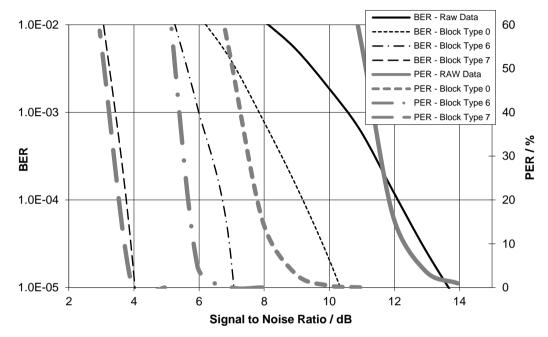

| -                     | Comparison of BER and PER for 4-QAM Modulation                                 |      |  |  |

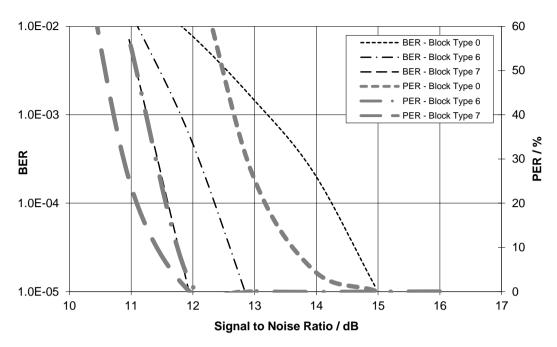

| -                     | Comparison of BER and PER for 16-QAM Modulation                                |      |  |  |

|                       | Comparison of BER and PER for 64-QAM Modulation                                |      |  |  |

| •                     | 4-QAM Signal-to-Noise Performance, Equalised and Non-Equalised                 |      |  |  |

| -                     | I 16-QAM Signal-to Noise Performance, Equalised and Non-Equalised              |      |  |  |

| •                     | 2 64-QAM Signal-to-Noise Performance, Equalised                                |      |  |  |

| •                     | Performance of 16-QAM Equalised Signals with Temperature Variation             |      |  |  |

| -                     | Performance of 64-QAM Equalised Signals with Temperature Variation             |      |  |  |

| -                     | 5 Performance of 16-QAM Equalised Signals with Temperature Variation and Cons  |      |  |  |

| •                     | 6 Performance of 64-QAM Equalised Signals with Temperature Variation and Cons  |      |  |  |

| Signal-to-Noise Ratio |                                                                                |      |  |  |

| Figure 107 | Tx Spectrum and Modulation Measurement Configuration for I/Q Operation | 125 |

|------------|------------------------------------------------------------------------|-----|

| Figure 108 | Tx Modulation V.23, 1200bps, I/Q Modulation                            | 126 |

| Figure 109 | Tx Modulation V.23, 1200bps, I/Q Modulation                            | 127 |

| Figure 110 | Signal Level vs BER                                                    | 128 |

| Figure 111 | C-BUS Timing                                                           | 144 |

| Figure 112 | Mechanical Outline of 64-pin VQFN (Q1)                                 | 145 |

| Figure 113 | Mechanical Outline of 64-pin LQFP (L9)                                 | 145 |

Information in this datasheet should not be relied upon for final product design. It is always recommended that you check for the latest product datasheet version from the CML website: [www.cmlmicro.com].

# 1.1 History

| Version | ersion Changes                                                                                                                                       |                     |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|

| 22      | Added information covering 7164FI-6.x                                                                                                                | (D/M/Y)<br>11/05/15 |  |

|         | Section 7.4.22: AGC control algorithm can now be used to control a second                                                                            |                     |  |

|         | device using one of the available GPIO pins.                                                                                                         |                     |  |

|         | Section 10.1 Updated Figure 82 (QAM Mappings)                                                                                                        |                     |  |

|         | Section 12.2: Original C-BUS timing diagram replaced by latest version                                                                               |                     |  |

|         | <ul> <li>Section 13.1.22:Register \$B3 – changed reserved bit 9 set value and added<br/>example settings</li> </ul>                                  |                     |  |

|         | <ul> <li>Section 13.1.31: description for register \$77: b11-0 description corrected to<br/>describe RSSI averaging period set by P4.3</li> </ul>    |                     |  |

|         | <ul> <li>Section 13.2.6 (Prog Block 4 – Modulation Control): P4.5 entry corrected to<br/>indicate that the parameter also supports FI-1.x</li> </ul> |                     |  |

|         | Section 13.2.6: Added description for P4.3                                                                                                           |                     |  |

|         | Section 13.2.7: Transmit sequence – added description for minimum pulse                                                                              |                     |  |

|         | period on GPIOA to trigger transmission and corrected the explanation of DC Calibration Sequence delays for default values                           |                     |  |

|         | <ul> <li>Descriptions for registers \$5D, \$5E, \$5F, \$60, \$61, \$65 – added note<br/>regarding delay between successive writes</li> </ul>         |                     |  |

|         | <ul> <li>Section 13.2.9: Added Program Block 7.17 for AGC control of external device<br/>via GPIO pins.</li> </ul>                                   |                     |  |

|         | Section 15.10: App Note updated for clarification                                                                                                    |                     |  |

|         | Section 12: Performance figures replace TBDs                                                                                                         |                     |  |

| 21      | <ul> <li>Section 13.1.22: \$B3 register table corrected and note added describing<br/>correct settings for the I/Q output drivers</li> </ul>         | 02/09/14            |  |

|         | <ul> <li>Section 13.2.2: Table for P0.0, b11-0 corrected to show value of 1 as invalid</li> </ul>                                                    |                     |  |

|         | <ul> <li>Section 13.2.5: Table showing new program registers P3.3 to P3.6 and<br/>associated description</li> </ul>                                  |                     |  |

|         | • Section 13.2.6: Summary table, and subsequent description, Program Block 4, P4.5 corrected to say that two of the values apply also to FI-1.x.     |                     |  |

|         | <ul> <li>Section 13.2.6: Summary table for Program Block 4, P4.8:b15-2 corrected to<br/>say "reserved, set to 1"</li> </ul>                          |                     |  |

|         | <ul> <li>Section 15.10: New Application Note - Aborting Rx and Restarting Frame Sync<br/>Search</li> </ul>                                           |                     |  |

|         | Miscellaneous typographical and editorial improvements                                                                                               |                     |  |

| 20      | <ul> <li>Section 13.2.4: Clarification to description on frame sync detection and error<br/>tolerance.</li> </ul>                                    | 19/06/14            |  |

|         | <ul> <li>Section 13.2.6: Entries and descriptions for P4.8 to P4.10 which offer<br/>additional control</li> </ul>                                    |                     |  |

| 19      | Added 16-FSK operation                                                                                                                               | 12/05/14            |  |

|         | Section 11: Performance figures replace TBDs                                                                                                         |                     |  |

|         | Section 12.2.4: Entire section rewritten to improve clarity                                                                                          |                     |  |

| 18      | Described the state of GPIO pins after reset and before a Function Image is loaded                                                                   | 12/02/14            |  |

|         | <ul> <li>Added voltage differential between power supplies to section 11 specification</li> </ul>                                                    | 1                   |  |

|         | Added description of RAMDAC ramp profile scaling                                                                                                     |                     |  |

|         | Added description of modulation envelope ramp control                                                                                                |                     |  |

|         | Added control method for narrower channel filter options in FI-1.x                                                                                   |                     |  |

|         | Added information on 8/16 FSK, channel coding                                                                                                        |                     |  |

|         | Figure 5 replaced by new drawing showing removal of unused components                                                                                |                     |  |

|         | Miscellaneous typographical and editorial improvements                                                                                               |                     |  |

| 16/17  | • Update of graphs to improve datasheet clarity in v14. Datasheet becomes v16.                                                                                             | 21/10/13 |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

| 14/15  | Added details of FI-2 Equaliser operation                                                                                                                                  | 01/08/13 |  |

|        | Added programming register control for I/Q dc offset acquisition                                                                                                           |          |  |

|        | Added corrections to framesync programming register description                                                                                                            |          |  |

|        | Added power connection to pin 37 in Figure 7                                                                                                                               |          |  |

|        | Enhancements for custom filter support                                                                                                                                     |          |  |

|        | Added payload byte lengths to Tables 3, 4, 5 and 6                                                                                                                         |          |  |

|        | Document formatting corrected and typos/clarifications                                                                                                                     |          |  |

| 11/12/ | <ul> <li>Added RD-LAP channel coding block types in FI-2.x</li> </ul>                                                                                                      | 15/03/13 |  |

| 13     | Clarification of FI-1.x channel coding                                                                                                                                     |          |  |

| 10     | Add 8-FSK and 16-FSK operation in FI-2.x                                                                                                                                   | 10/01/13 |  |

| 9      | Add GMSK/GFSK operation in FI-1.x                                                                                                                                          | 30/4/12  |  |

| 8      | Added details of FI-4 Equaliser operation and control: Mode register,  programming block                                                                                   | 9/1/12   |  |

|        | <ul><li>programming block</li><li>Added details of programming block read mechanism (Available for selected</li></ul>                                                      |          |  |

|        | programming registers only)                                                                                                                                                |          |  |

|        | <ul> <li>Updated receive performance curves for FI-4</li> </ul>                                                                                                            |          |  |

|        | Added description of soft decision output bits for FI-2 only                                                                                                               |          |  |

|        | Added details of bus hold function for unused inputs                                                                                                                       |          |  |

|        | Added details of Core regulator select                                                                                                                                     |          |  |

|        | Corrected conditions under which current measurements were made                                                                                                            |          |  |

|        | Changed reference to input impedance of I/Q INPUTs                                                                                                                         |          |  |

|        | Typos/clarifications                                                                                                                                                       |          |  |

| 7      | Remove constraint on use of document with FI-2.x, as the latter is now                                                                                                     | 21/09/11 |  |

|        | updated.                                                                                                                                                                   |          |  |

| 6      | <ul> <li>Advice in section 5.5 greyed out as not implemented in current FI.</li> </ul>                                                                                     | 22/08/11 |  |

| 5      | <ul> <li>Added advice about terminating unconnected GPIO pins in section 5.5</li> </ul>                                                                                    | 17/8/11  |  |

| 4      | <ul> <li>Added details of default and inverting gains to the description of the I/Q Output<br/>Control - \$5D, \$5E registers</li> </ul>                                   | 3/8/11   |  |

|        | • Pointed out correct use of handshaking when using signal control (Register                                                                                               |          |  |

|        | \$61) to select I and Q offset measurements (Registers \$75 and \$76)                                                                                                      |          |  |

|        | • Clarified behaviour of the I and Q offset registers (Rx dc offset correction) when                                                                                       |          |  |

|        | using automatic Rx IQ dc mode                                                                                                                                              |          |  |

|        | Clarified behaviour and scaling of RSSI measurements                                                                                                                       |          |  |

|        | Documented further AGC controls added in FI-4.0.5.4, and described AGC                                                                                                     |          |  |

|        | operation in detail                                                                                                                                                        |          |  |

|        | <ul> <li>Documented the PII On bit added to the mode register in FI-4.0.5.4, which<br/>provides a fast idle mode for programming register modifications without</li> </ul> |          |  |

|        | powersave, but with improved speed                                                                                                                                         |          |  |

|        | Added parameters in Program Block 1 to reduce delay when transitioning from                                                                                                |          |  |

|        | Idle to Tx or Rx modes                                                                                                                                                     |          |  |

|        | Added information about receive dynamic range                                                                                                                              |          |  |

|        | Corrected and clarified scaling of Tx output fine control.                                                                                                                 |          |  |

|        | Idle to Tx or Rx modes  • Added information about receive dynamic range                                                                                                    |          |  |

| 3 | <ul> <li>Remove information indicating that a reset with no FI load is possible. See sections 11.1.1 Reset Operations, 7.3 Function image loading</li> <li>FIFO level interrupts to the host require re-arming using \$50 FIFO control. See 11.1.4 FIFO Control \$50</li> <li>Include description for "I/Q Input dc correction loop gain". See 11.1.10 Signal</li> </ul> | 15/4/11 |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|   | <ul> <li>control \$61</li> <li>Spectrum figure ACP mislabeled as for 25kHz when it is for 12.5kHz. See fig 58</li> </ul>                                                                                                                                                                                                                                                 |         |

|   | <ul> <li>Expand description of FI-2 4-FSK deviation configuration. See 11.1.10 Signal<br/>control \$61</li> </ul>                                                                                                                                                                                                                                                        |         |

|   | <ul> <li>Include over-air symbol sequence for FI-2 (2-FSK and 4-FSK) and FI-4 data.</li> <li>See 7.4.15, 11.1.3 and 11.1.26. Specifically this matters for bit wise transfers, indicating which bits are valid</li> </ul>                                                                                                                                                |         |

|   | • Default values in 11.1.9 to be changed: \$07FF becomes \$0400; \$0801 becomes \$0C00                                                                                                                                                                                                                                                                                   |         |

|   | <ul> <li>Addition of "Tx Done flag set on completion of DC Calibration" to 7.4.11,<br/>11.1.18 and 11.1.36. Also indicate that AuxADC paths, etc in 7.4.11 are fixed<br/>permanently, by changing the description "assumed" to "required"</li> </ul>                                                                                                                     |         |

|   | <ul> <li>Figure 34 to show "Main PLL out" sourced directly from the Xtal in Idle mode</li> <li>Update Figure 3 and correct minor typographical errors (Fig 43)</li> </ul>                                                                                                                                                                                                |         |

| 2 | <ul> <li>Clarify text at the end of section 12.3.2</li> <li>Change b11 to b9 in section 11.1.14</li> </ul>                                                                                                                                                                                                                                                               | 22/3/11 |

|   | <ul> <li>Remove FI Load Activation Block references and describe default states in<br/>section11.1.2 and Table 5</li> </ul>                                                                                                                                                                                                                                              |         |

|   | <ul> <li>Clarify bit names in section 11.1.20, to avoid duplication</li> <li>Add missing action #20 in section 11.2.1</li> </ul>                                                                                                                                                                                                                                         |         |

| 1 | Original document, prepared for first alpha release of FI.                                                                                                                                                                                                                                                                                                               | 24/2/11 |

## 2 Block Diagrams

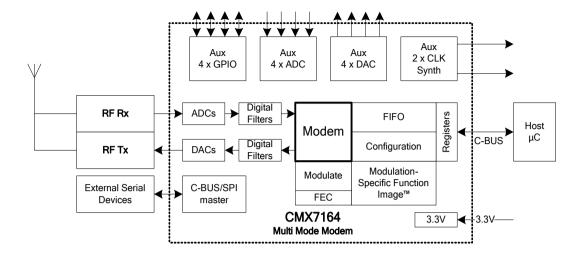

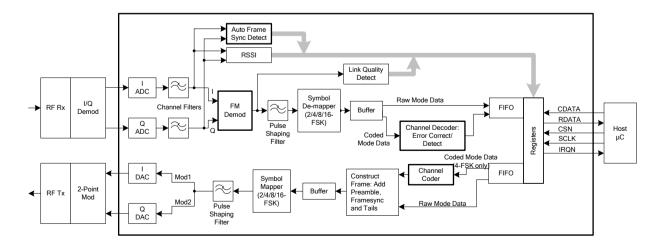

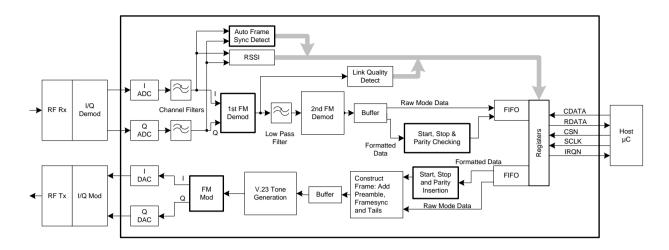

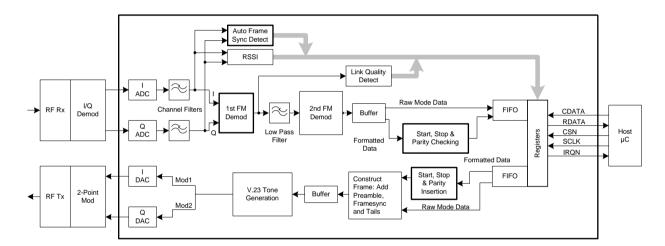

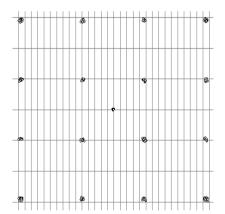

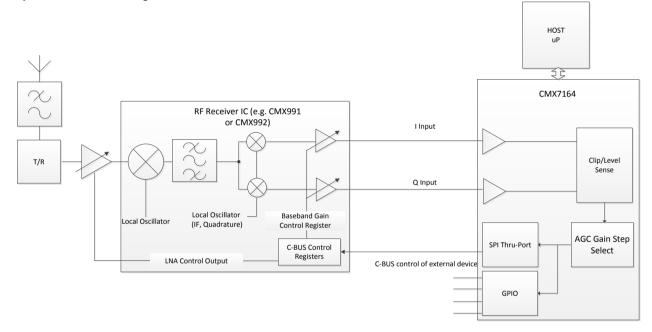

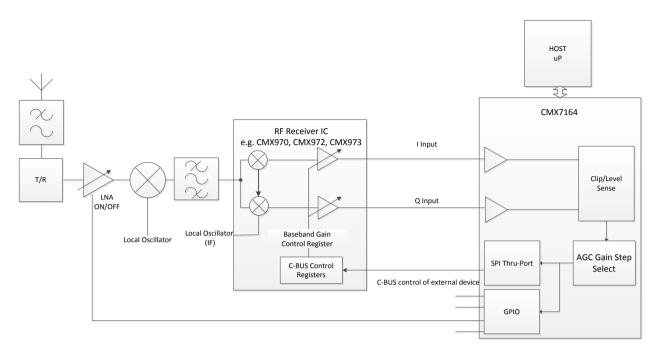

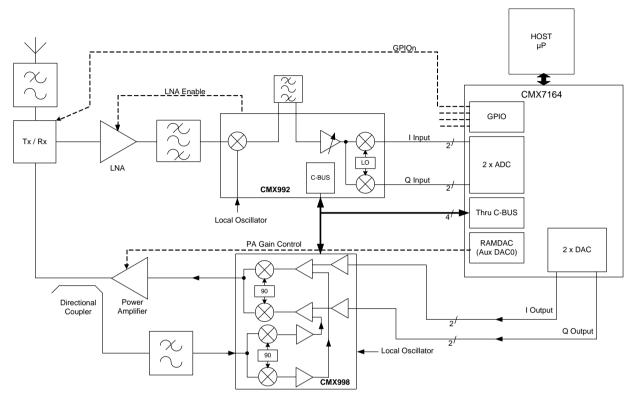

Figure 1 Overall Block Diagram

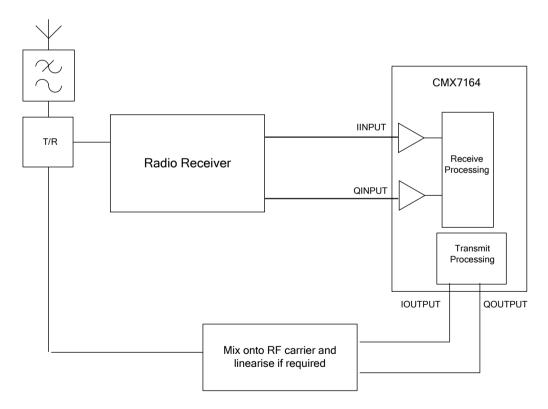

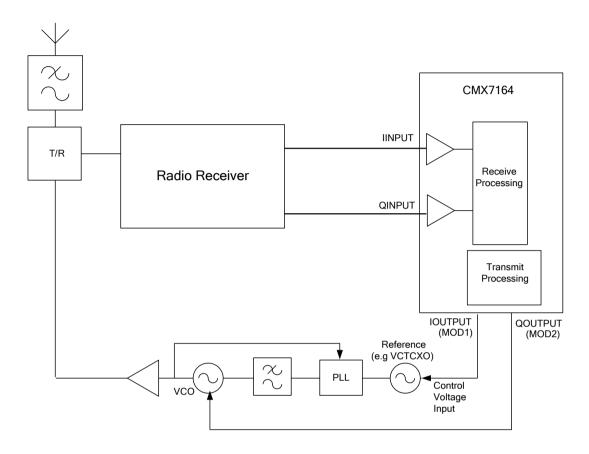

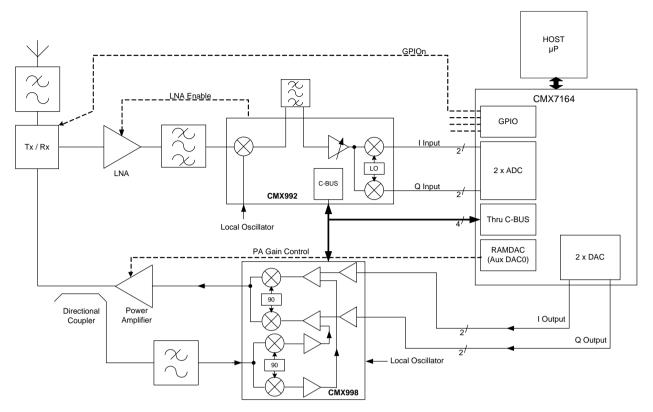

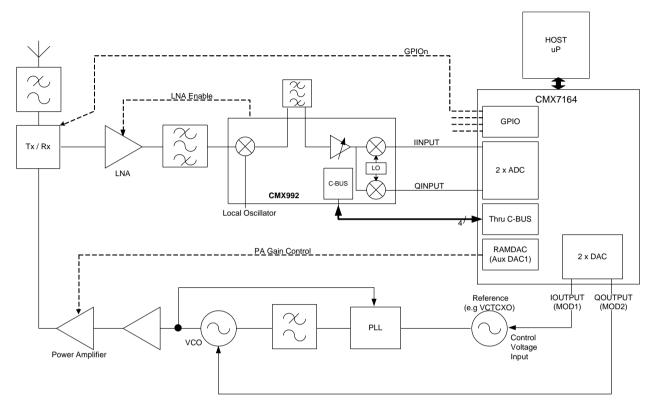

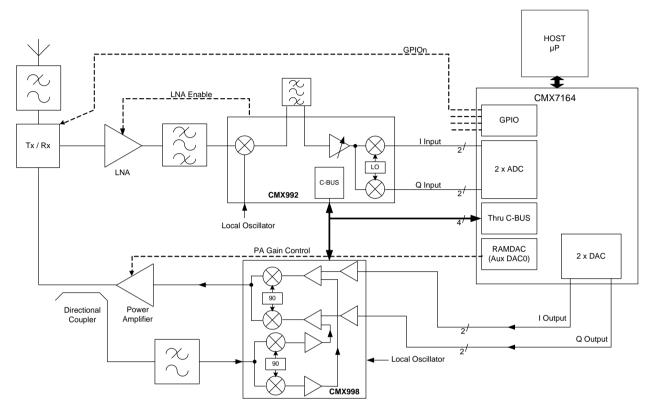

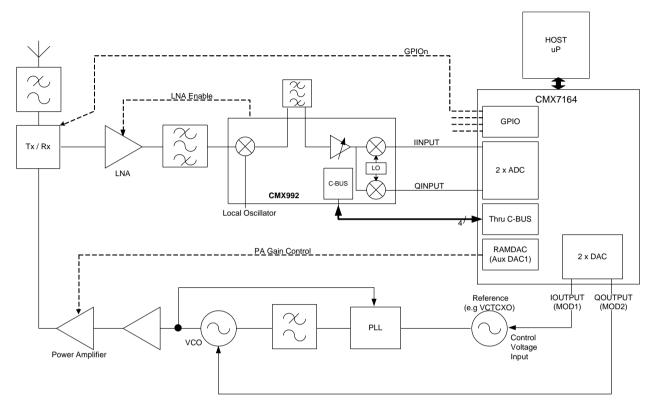

Figure 1 illustrates the overall functionality of the CMX7164, detailing the auxiliary functions. The following figures expand upon the transmit and receive functions.

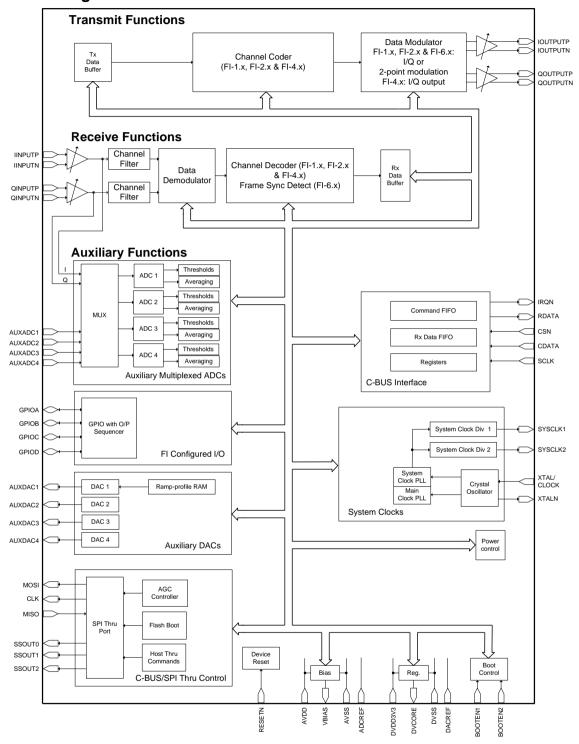

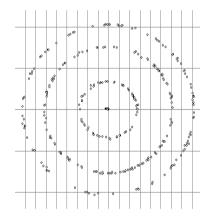

Figure 2 FI-4.x Block Diagram - I/Q Tx and Rx

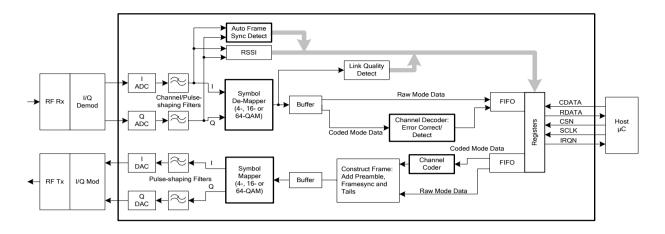

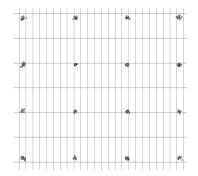

Figure 3 FI-1.x / FI-2.x Block Diagram - I/Q Tx and Rx

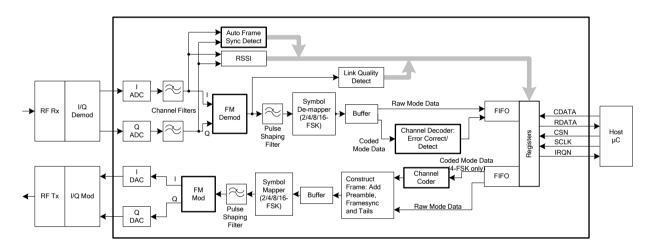

Figure 4 FI-1.x / FI-2.x Block Diagram – two-point Tx with I/Q Rx

Figure 5 FI-6.x Block Diagram - I/Q Tx and Rx

Figure 6 FI-6.x Block Diagram - Two-point Tx with I/Q Rx

# 3 Signal List

| 64-pin<br>Q1/L9 Pin |          |       | Description                                                                                                                                                                                                                |

|---------------------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.             | Name     | Туре  |                                                                                                                                                                                                                            |

| 1                   | GPIOB    | BI    | General Purpose I/O                                                                                                                                                                                                        |

| 2                   | BOOTEN1  | IP+PU | The combined state of BOOTEN1 and BOOTEN2, upon RESET, determine the Function Image™ load interface                                                                                                                        |

| 3                   | BOOTEN2  | IP+PU | The combined state of BOOTEN1 and BOOTEN2, upon RESET, determine the Function Image™ load interface                                                                                                                        |

| 4                   | DVSS     | PWR   | Negative supply rail (ground) for the digital on-chip circuits                                                                                                                                                             |

| 5                   | DVDD 3V3 | PWR   | 3.3V positive supply rail for the digital on-chip circuits. This pin should be decoupled to DVSS by capacitors mounted close to the supply pins.                                                                           |

| 6                   | SSOUT2   | OP    | SPI: Slave Select Out 2                                                                                                                                                                                                    |

| 7                   | RESETN   | IP    | Logic input used to reset the device (active low)                                                                                                                                                                          |

| 8                   | GPIOC    | BI    | General Purpose I/O                                                                                                                                                                                                        |

| 9                   | GPIOD    | BI    | General Purpose I/O                                                                                                                                                                                                        |

| 10                  | DVSS     | PWR   | Negative supply rail (ground) for the digital on-chip circuits                                                                                                                                                             |

| 11                  | NC       | NC    | Do not connect                                                                                                                                                                                                             |

| 12                  | AVDD     | PWR   | Positive 3.3V supply rail for the analogue on-chip circuit. Levels and thresholds within the device are proportional to this voltage. This pin should be decoupled to AVSS by capacitors mounted close to the device pins. |

| 13                  | NC       | NC    | May also be connected to AVSS                                                                                                                                                                                              |

| 14                  | NC       | NC    | Do not connect                                                                                                                                                                                                             |

| 15                  | NC       | NC    | Do not connect                                                                                                                                                                                                             |

| 16                  | NC       | NC    | May also be connected to AVDD                                                                                                                                                                                              |

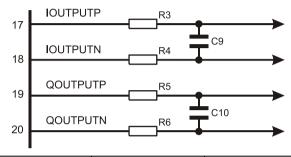

| 17                  | IOUTPUTP | OP    | Differential outputs for I channel; 'P' is positive, 'N' is                                                                                                                                                                |

| 18                  | IOUTPUTN | ОР    | negative. Together these are referred to as the I Output. When the 7164 FI-1 or FI-2 is in two-point modulation mode the I Output is used as 'Mod 1'.                                                                      |

| 19                  | QOUTPUTP | OP    | Differential outputs for Q channel; 'P' is positive, 'N' is                                                                                                                                                                |

| 20                  | QOUTPUTN | ОР    | negative. Together these are referred to as the Q Output. When the 7164 FI-1 or FI-2 is in two-point modulation mode the Q Output is used as 'Mod 2'.                                                                      |

| 21                  | AVSS     | PWR   | Negative supply rail (ground) for the analogue on-chip circuits                                                                                                                                                            |

| 22                  | DACREF   |       | DAC reference voltage, connect to AVSS                                                                                                                                                                                     |

| 23                  | NC       | NC    | Do not connect                                                                                                                                                                                                             |

| 24                  | NC       | NC    | Do not connect                                                                                                                                                                                                             |

| 25                  | NC       | NC    | Do not connect                                                                                                                                                                                                             |

| 64-pin<br>Q1/L9 | Pin        |      | Description                                                                                                                                                                                                                                          |

|-----------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.         | Name       | Туре |                                                                                                                                                                                                                                                      |

| 26              | NC         | NC   | Do not connect                                                                                                                                                                                                                                       |

| 27              | VBIAS      | OP   | Internally generated bias voltage of approximately $AV_{DD}/2$ . If $V_{BIAS}$ is powersaved this pin will be connected via a high impedance to $AV_{DD}$ . This pin must be decoupled to $AV_{SS}$ by a capacitor mounted close to the device pins. |

| 28              | IINPUTP    | IP   | Differential inputs for I channel signals; 'P' is positive, 'N' is                                                                                                                                                                                   |

| 29              | IINPUTN    | IP   | negative. Together these are referred to as the I Input.                                                                                                                                                                                             |

| 30              | ADCREF     |      | ADC reference voltage; connect to AV <sub>SS</sub>                                                                                                                                                                                                   |

| 31              | QINPUTP    | IP   | Differential inputs for Q channel signals; 'P' is positive, 'N' is                                                                                                                                                                                   |

| 32              | QINPUTN    | IP   | negative. Together these are referred to as the Q Input.                                                                                                                                                                                             |

| 33              | AUXADC1    | IP   | Auxiliary ADC input 1                                                                                                                                                                                                                                |

| 34              | AUXADC2    | IP   | Auxiliary ADC input 2                                                                                                                                                                                                                                |

| 35              | AUXADC3    | IP   | Auxiliary ADC input 3                                                                                                                                                                                                                                |

| 36              | AUXADC4    | IP   | Auxiliary ADC input 4                                                                                                                                                                                                                                |

| 37              | AVDD       | PWR  | Positive 3.3V supply rail for the analogue on-chip circuit. Levels and thresholds within the device are proportional to this voltage. This pin should be decoupled to AV <sub>SS</sub> by capacitors mounted close to the device pins.               |

| 38              | AVSS       | PWR  | Negative supply rail (ground) for the analogue on-chip circuits                                                                                                                                                                                      |

| 39              | AUXDAC1    | OP   | Auxiliary DAC output 1 (Optionally the RAMDAC output)                                                                                                                                                                                                |

| 40              | AUXDAC2    | OP   | Auxiliary DAC output 2                                                                                                                                                                                                                               |

| 41              | AUXDAC3    | OP   | Auxiliary DAC output 3                                                                                                                                                                                                                               |

| 42              | AUXDAC4    | OP   | Auxiliary DAC output 4                                                                                                                                                                                                                               |

| 43              | DVSS       | PWR  | Negative supply rail (ground) for the digital on-chip circuits                                                                                                                                                                                       |

| 44              | DVCORE     | PWR  | Internally generated digital core voltage of approximately 1.8V. This pin should be decoupled to DV <sub>SS</sub> by capacitors mounted close to the device pins                                                                                     |

| 45              | DVDD3V3    | PWR  | 3.3V positive supply rail for the digital on-chip circuits. This pin should be decoupled to $DV_SS$ by capacitors mounted close to the supply pins.                                                                                                  |

| 46              | NC         | NC   | Do not connect                                                                                                                                                                                                                                       |

| 47              | NC         | NC   | May also be connected to DVSS                                                                                                                                                                                                                        |

| 48              | DVSS       | PWR  | Negative supply rail (ground) for the digital on-chip circuits                                                                                                                                                                                       |

| 49              | XTALN      | OP   | Output of the on-chip Xtal oscillator inverter                                                                                                                                                                                                       |

| 50              | XTAL/CLOCK | IP   | Input to the oscillator inverter from the Xtal circuit or external clock source                                                                                                                                                                      |

| 51              | SYSCLK1    | OP   | Synthesised digital clock output 1                                                                                                                                                                                                                   |

| 64-pin<br>Q1/L9      | Pin       |       | Description                                                                                                                                                                                                                  |

|----------------------|-----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.              | Name      | Туре  |                                                                                                                                                                                                                              |

| 52                   | SYSCLK2   | OP    | Synthesised digital clock output 2                                                                                                                                                                                           |

| 53                   | SCLK      | IP    | C-BUS serial clock input from the μC                                                                                                                                                                                         |

| 54                   | RDATA     | TS OP | 3-state C-BUS serial data output to the $\mu$ C. This output is high impedance when not sending data to the $\mu$ C.                                                                                                         |

| 55                   | CDATA     | IP    | C-BUS serial data input from the μC                                                                                                                                                                                          |

| 56                   | CSN       | IP    | C-BUS chip select input from the μC                                                                                                                                                                                          |

| 57                   | IRQN      | OP    | 'wire-Orable' output for connection to the Interrupt Request input of the $\mu$ C. This output is pulled down to DV <sub>SS</sub> when active and is high impedance when inactive. An external pull-up resistor is required. |

| 58                   | DVCORE    | PWR   | Internally generated digital core voltage of approximately 1.8V. This pin should be decoupled to DV <sub>SS</sub> by capacitors mounted close to the device pins                                                             |

| 59                   | MOSI      | OP    | SPI: Master Out Slave In                                                                                                                                                                                                     |

| 60                   | SSOUT1    | OP    | SPI: Slave Select Out 1                                                                                                                                                                                                      |

| 61                   | MISO      | IP    | SPI: Master In Slave Out                                                                                                                                                                                                     |

| 62                   | SSOUT0    | OP    | SPI: Slave Select Out 0                                                                                                                                                                                                      |

| 63                   | CLK       | OP    | SPI: Serial Clock                                                                                                                                                                                                            |

| 64                   | GPIOA     | ВІ    | General Purpose I/O                                                                                                                                                                                                          |

| EXPOSED<br>METAL PAD | SUBSTRATE | ~     | On this device, the central metal pad (which is exposed on the Q1 package only) may be electrically unconnected or, alternatively, may be connected to Analogue ground (AVss).  No other electrical connection is permitted. |

**Notes:** IP = Input (+ PU/PD = internal pull-up / pull-down resistor of approximately  $75k\Omega$ )

OP = Output

BI = Bidirectional

TS OP = 3-state Output

PWR = Power Connection

NC = No Connection - should NOT be connected to any signal

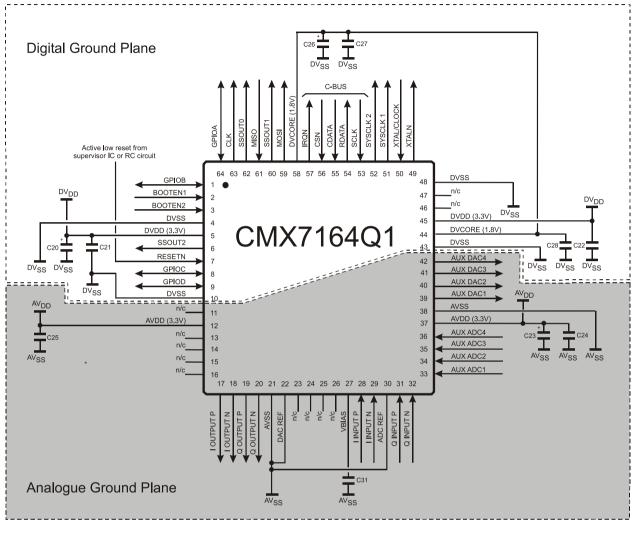

## 4 PCB Layout Guidelines and Power Supply Decoupling

| C20 | 10μF | C26 | 22µF  |

|-----|------|-----|-------|

| C21 | 10nF | C27 | 10nF  |

| C22 | 10nF | C28 | 10nF  |

| C23 | 10µF | C31 | 100nF |

| C24 | 10nF |     |       |

| C25 | 10nF |     |       |

Figure 7 CMX7164 Power Supply and De-coupling

#### Notes:

To achieve good noise performance,  $AV_{DD}$  and  $V_{BIAS}$  decoupling and protection of the receive path from extraneous in-band signals is very important. It is recommended that the printed circuit board is laid out with a ground plane in the CMX7164 analogue area to provide a low impedance connection between the AVSS pins and the  $AV_{DD}$  and  $V_{BIAS}$  decoupling capacitors.

## 5 External Components

## 5.1 Xtal Interface

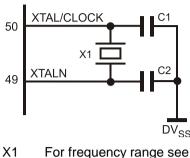

X1 For frequency range see12.1.2 Operating Limits

C1 22pF Typical

C2 22pF Typical

Figure 8 Recommended External Components - Xtal Interface

#### Notes:

The clock circuit can operate with either a Xtal or external clock generator. If using an external clock generator it should be connected to the XTAL/CLOCK pin and the xtal and other components are not required. For external clock generator frequency range see 12.1.2 Operating Limits. When using an external clock generator the Xtal oscillator circuit may be disabled to save power, see 13.2.3 Program Block 1 – Clock Control for details. Also refer to section 7.1 Xtal Frequency.

The tracks between the Xtal and the device pins should be as short as possible to achieve maximum stability and best start up performance. It is also important to achieve a low impedance connection between the Xtal capacitors and the ground plane.

The  $DV_{SS}$  to the Xtal oscillator capacitors C1 and C2 should be of low impedance and preferably be part of the  $DV_{SS}$  ground plane to ensure reliable start up. For correct values of capacitors C1 and C2 refer to the documentation of the Xtal used.

#### 5.2 C-BUS Interface

Figure 9 Recommended External Components - C-BUS Interface

#### Note:

If the IRQN line is connected to other compatible pull-down devices only one pull-up resistor is required on the IRQN node.

## 5.3 I/Q Output Reconstruction Filter