# AN-1150 COP8™ FLASH ISP HANDBOOK—Intro to ISP

#### **ABSTRACT**

This application note describes the COP8™ In System Programming (ISP) Software. ISP method of programming the flash memory are thoroughly discussed.

|            | Contents                                                                  |    |

|------------|---------------------------------------------------------------------------|----|

| 1          | Introduction                                                              |    |

| 2          | Introduction to ISP—Software Topics                                       |    |

| 3<br>4     | ADVANCED ISP—SOFTWARE TOPICS                                              |    |

| 4<br>Apper |                                                                           |    |

|            |                                                                           |    |

|            | List of Figures                                                           |    |

| 1          | Block Diagram of ISP                                                      |    |

| 2          | Sample Application Circuit                                                | 8  |

| 3          | Flow for the Sequencer Program                                            | 13 |

| 4          | ISP Boot ROM Interface                                                    | 13 |

| 5          | COP8 FLASH Memory Layout                                                  | 14 |

| 6          | MICROWIRE/PLUS Example                                                    | 16 |

| 7          | MICROWIRE/PLUS Interface Timing, Normal SK Mode, SK Idle Phase being High | 16 |

| 8          | Parallel Port Connection Diagram                                          | 17 |

| 9          | MICROWIRE/PLUS Interface Timing, Normal SK Mode, SK Idle Phase being High | 17 |

| 10         | ISP Command Frame                                                         | 18 |

| 11         | Cascade Delay Requirement                                                 | 18 |

| 12         | Byte Write Waveform (Relative Bytes are Shown)                            | 19 |

| 13         | Block Write Waveform (Relative Bytes are Shown)                           | 19 |

| 14         | Page Erase Waveform (Relative Bytes are Shown)                            | 20 |

| 15         | Mass Erase Waveform (Relative Bytes are Shown)                            | 20 |

| 16         | The ISP—MICROWIRE Control                                                 | 21 |

| 17         | The Set PGMTIM Command                                                    | 21 |

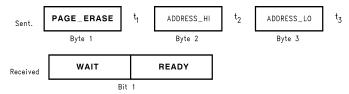

| 18         | The PAGE ERASE Command                                                    | 22 |

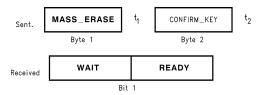

| 19         | The MASS_ERASE Command                                                    | 23 |

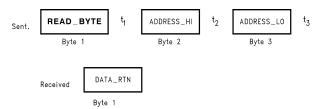

| 20         | The READ_BYTE Command                                                     | 23 |

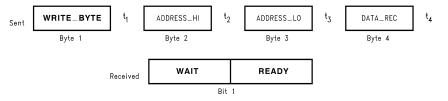

| 21         | The WRITE_BYTE Command                                                    | 23 |

| 22         | The Block Write Routine                                                   | 24 |

| 23         | The Block Read Command                                                    | 24 |

| 24         | The EXIT Command                                                          | 25 |

| 25         | Interfacing the COP8SGR and COP8CBR Microcontrollers                      | 25 |

| 26         | Flow Chart for the Initialization Routine                                 | 26 |

COP8, MICROWIRE/PLUS, WATCHDOG are trademarks of Texas Instruments.

ICE is a trademark of Intel Corporation.

MetaLink is a trademark of dcl\_owner.

All other trademarks are the property of their respective owners.

| 27 | Flow for the PGMTIM_SET Program                                                                                        | 27 |

|----|------------------------------------------------------------------------------------------------------------------------|----|

| 28 | Flow for the Page Erase Function                                                                                       | 29 |

| 29 | Flow for the Mass Erase Function                                                                                       | 32 |

| 30 | Flow for the Read Byte Routine                                                                                         | 35 |

| 31 | Flow for the Write Byte Function                                                                                       | 38 |

| 32 | Flow for the Block Write Function                                                                                      | 41 |

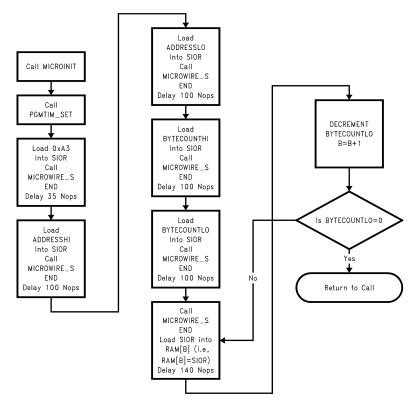

| 33 | Flow for the BLOCK_READ Function                                                                                       | 45 |

| 34 | Flow for the Exit Routine                                                                                              | 48 |

|    | List of Tables                                                                                                         |    |

| 1  | High Byte of ISP Address                                                                                               | 4  |

| 2  | Low Byte of ISP Address                                                                                                | 4  |

| 3  | ISP Read Data Register                                                                                                 | 5  |

| 4  | ISP Write Data Register                                                                                                | 5  |

| 5  | Key Register Write Format                                                                                              | 5  |

| 6  | Key Register Read Format                                                                                               | 6  |

| 7  | Bit Patterns for the Sample Program                                                                                    | 12 |

| 8  | Option and TCON Register Bit Assignments                                                                               | 14 |

| 9  | Initialization of the MICROWIRE/PLUS by the Firmware                                                                   | 16 |

| 10 | MICROWIRE/PLUS Mode Selected by the Firmware                                                                           | 16 |

| 11 | Parallel Port <-> MICROWIRE/PLUS Conversion                                                                            | 17 |

| 12 | Initialization of the MICROWIRE/PLUS by the Firmware                                                                   | 17 |

| 13 | MICROWIRE/PLUS Mode Selected by the Firmware                                                                           | 17 |

| 14 | Required time delays (in instruction cycles) for cascading command frames <b>after</b> an initial command was executed | 18 |

| 15 | Required Time Delays (In Instruction Cycles)                                                                           |    |

| 16 | MICROWIRE/PLUS Commands                                                                                                |    |

| 17 | Valid PGMTIM Values                                                                                                    |    |

| 18 | Required Initialization of the MICROWIRE/PLUS                                                                          |    |

| 19 | MICROWIRE/PLUS Mode Required for Communication                                                                         |    |

| 20 | User Entry Points and Their Associated Labels                                                                          |    |

| 21 | Registers                                                                                                              |    |

| 22 | User Entry Points                                                                                                      |    |

| 23 | Required Interrupt Lockout Time (in Instruction Cycles)                                                                | 52 |

| 24 |                                                                                                                        | 52 |

| 25 |                                                                                                                        | 53 |

| 26 | Resource Utilization for the Command: cmserase (Mass Erase)                                                            | 54 |

| 27 | Resource Utilization for the Command: creadbf (Read a Byte of Flash Memory)                                            | 54 |

| 28 |                                                                                                                        | 55 |

| 29 | · · · · · · · · · · · · · · · · · · ·                                                                                  | 56 |

| 30 |                                                                                                                        | 57 |

| 31 | Resource Utilization for the Command: exit (reset the microcontroller)                                                 | 58 |

www.ti.com Introduction

## 1 Introduction

In-System Programming (ISP) allows the user to re-program a microcontroller without physical removal. The COP8™ ISP Software allows the user to program the flash memory in three ways. A user may choose to program the flash memory by using the Boot ROM's user support portion, the MetaLink™ support portion (via the Flash emulator module) or the MICROWIRE/PLUS™ support portion. The use of a user and/or MICROWIRE/PLUS™ support portions are fully documented and their requirements are specified. Other application notes that relate to the COP8™ FLASH ISP software include AN-1151 (Parallel Port Programming Adapter), AN-1152 (FLASHDOS Programmer Source), AN-1153 (Virtual E² Guide), AN-1154 (FLASHWIN Programmer's Guide) and AN-1161 (FLASHDOS Programmer's Guide).

## 2 Introduction to ISP—Software Topics

The Flash Family provides the capability to program the Program Memory while installed in an application board. This feature is called In System Programming (ISP). It provides a means of ISP by using the MICROWIRE/PLUS™, or the user can provide his own, customized ISP routine. This customized routine may use any of the capabilities of the device, such as USART, parallel port, etc. The factory installed ISP uses only the MICROWIRE/PLUS™ port.

## 2.1 Functional Description

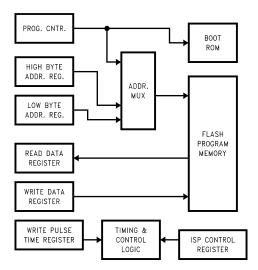

The organization of the ISP feature consists of the user flash program memory, the factory Boot ROM, and some registers dedicated to performing the ISP function. See Figure 1 for a simplified block diagram. The factory installed ISP that uses MICROWIRE/PLUS is located in the Boot ROM. The size of the Boot ROM is 1K bytes and also includes the ICE™ monitor code. If a user chooses to write his own ISP routine, it must be located in the flash program memory.

In the next section, ADVANCED ISP SOFTWARE TOPICS, a discussion regarding the FLEX bit is presented. The FLEX bit controls whether the device exits RESET executing from the flash memory or the Boot ROM. The user must program this Configuration Register bit as appropriate for the application. In the erased state, the FLEX bit = 0 and the device will power-up executing from Boot ROM. When FLEX = 0, this assumes that either the MICROWIRE/PLUS<sup>TM</sup> ISP routine or external programming is being used to program the device. If using the MICROWIRE/PLUS<sup>TM</sup> ISP routine, the software in the Boot ROM will monitor the MICROWIRE/PLUS<sup>TM</sup> for commands to program the flash memory. When programming the flash program memory is complete, the FLEX bit will have to be programmed to a 1 and the device will have to be reset, either by pulling external Reset to ground or by software, before execution from flash program memory will occur.

If FLEX = 1, upon exiting Reset, the device will begin executing from location 0000 in the flash program memory. The assumption here, is that either the application is not using ISP, but is using MICROWIRE/PLUS<sup>TM</sup> ISP by jumping to it within the application code or is using a customized ISP routine. If a customized ISP routine is being used, then it must be programmed into the flash memory by means of MICROWIRE/PLUS<sup>TM</sup> ISP or external programming as described in the preceding paragraph.

Figure 1. Block Diagram of ISP

#### 2.1.1 REGISTERS

There are six registers required to support ISP: Address Register Hi byte (ISPADHI), Address Register Low byte (ISPADLO), Read Data Register (ISPRD), Write Data Register (ISPWR), Write Timing Register (PGMTIM), and the Control Register (ISPCNTRL).

## 2.1.1.1 ISP Address Registers

The address registers (ISPADHI and ISPADLO) are used to specify the address of the byte of data being written or read. For page erase operations, the address of the beginning of the page should be loaded. When reading the Option register, FFFF should be placed into the address registers. Registers ISPADHI and ISPADLO are cleared to 00 on Reset. These registers can be loaded from either flash program memory or Boot ROM and must be maintained for the entire duration of the operation.

Table 1. High Byte of ISP Address

|            | ISPADHI    |            |            |            |            |           |           |

|------------|------------|------------|------------|------------|------------|-----------|-----------|

| Bit 7      | Bit 6      | Bit 5      | Bit 4      | Bit 3      | Bit 2      | Bit 1     | Bit 0     |

| Addr<br>15 | Addr<br>14 | Addr<br>13 | Addr<br>12 | Addr<br>11 | Addr<br>10 | Addr<br>9 | Addr<br>8 |

Table 2. Low Byte of ISP Address

|           | ISPADLO   |           |           |           |           |           |           |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Bit 7     | Bit 6     | Bit 5     | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0     |

| Addr<br>7 | Addr<br>6 | Addr<br>5 | Addr<br>4 | Addr<br>3 | Addr<br>2 | Addr<br>1 | Addr<br>0 |

## 2.1.1.2 ISP Read Data Register

The Read Data Register (ISPRD) contains the value read back from a read operation. This register can be accessed from either flash program memory or Boot ROM. This register is undefined on Reset. CAUTION: Read/Modify/Write instructions are not allowed to be used on this register.

## Table 3. ISP Read Data Register

|       | ISPRD                                           |  |  |  |  |  |  |

|-------|-------------------------------------------------|--|--|--|--|--|--|

| Bit 7 | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |  |  |  |  |  |  |

| Bit7  | Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0         |  |  |  |  |  |  |

#### 2.1.1.3 ISP Write Data Register

The Write Timing Register (PGMTIM) is used to control the width of the timing pulses for write and erase operations. The value to be written into this register is dependent on the frequency of CKI and is shown in Table 17. This register must be written before any write or erase operation can take place. It only needs to be loaded once, for each value of CKI frequency. If a dedicated E² block exists on the device and it's in the process of writing, this register should not be changed until the E² write cycle is completed.

Table 4. ISP Write Data Register

|       | ISPWR                                           |  |  |  |  |  |  |

|-------|-------------------------------------------------|--|--|--|--|--|--|

| Bit 7 | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |  |  |  |  |  |  |

| Bit7  | Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0         |  |  |  |  |  |  |

## 2.1.1.4 ISP Write Timing Register

The Write Timing Register (PGMTIM) is used to control the width of the timing pulses for write and erase operations. The value to be written into this register is dependent on the frequency of CKI and is shown in Table 17. This register must be written before any write or erase operation can take place. It only needs to be loaded once, for each value of CKI frequency. This register can be loaded from either flash program memory or Boot ROM and must be maintained for the entire duration of the operation. If a dedicated  $E^2$  block exists on the device and it's in the process of writing, this register should not be changed until the  $E^2$  write cycle is completed.

#### 2.1.2 MANEUVERING BACK AND FORTH BETWEEN FLASH MEMORY AND BOOT ROM

When using ISP, at some point, it will be necessary to maneuver between the flash program memory and the Boot ROM, even when using customized ISP routines. This is because it's not possible to execute from the flash program memory while it's being programmed.

The JSRB instruction is used to Jump to the Boot ROM. Refer to the COP8™ Flash Family User Manual for specific details on the operation of this instruction. The JSRB instruction must be used in conjunction with the Key register. This is to prevent jumping to the Boot ROM in the event of run-away software. For the JSRB instruction to actually jump to the Boot ROM, the Key bit must be set. This is done by writing the value shown in Table 5 to the Key register. The Key is a 6-bit key and, if the key matches, the KEY bit will be set for 8 instruction cycles. The JSRB instruction must be executed while the KEY bit is set. If the KEY does not match, then the KEY bit will not be set and the JSRB will jump to the specified location in the flash memory. In emulation mode, if a breakpoint is encountered while the KEY is set, the counter that counts the instruction cycles will be frozen until the breakpoint condition is cleared. The Key register is a memory mapped register. Its format when writing is shown in Table 5. Its format when reading is shown in Table 6. In normal operation, it is not necessary to test the KEY bit before using the JSRB instruction. The reading of the Key register is primarily used for testing. Also, located in the Key register is a bit called EFLEX. This bit is also used for testing.

Table 5. Key Register Write Format

|       | KEY when Writing                                |  |  |  |  |  |  |

|-------|-------------------------------------------------|--|--|--|--|--|--|

| Bit 7 | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |  |  |  |  |  |  |

| 1     | 1 0 0 1 1 0 X X                                 |  |  |  |  |  |  |

Bits 7-2:— Key value that must be written to set the KEY bit.

Bits 1-0:—Don't care.

**Table 6. Key Register Read Format**

|       | KEY when Reading |       |       |       |       |       |       |  |

|-------|------------------|-------|-------|-------|-------|-------|-------|--|

| Bit 7 | Bit 6            | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

| 0     | 0                | 0     | 0     | 0     | 0     | EFLEX | KEY   |  |

| R     | R                | R     | R     | R     | R     | R     | R     |  |

Bits 7–2:—Read back as 0.

**EFLEX (FLASH EXECUTION):**—This is the bit that actually controls whether program execution occurs from flash memory or Boot ROM. It uses data from the Option Register bit in combination with other logic controlled by the JSRB instruction, and the G6 hardware override. When EFLEX = 1, execution is from the flash program memory. When EFLEX = 0, program execution occurs from the Boot ROM. This is a Read Only bit.

**KEY:**— This is the state of the Key. If it is set, it indicates that a valid key was written to the Key register and the JSRB instruction will jump correctly to the Boot ROM. If it's cleared, the key is not valid and the JSRB instruction will jump to the specified address in flash program memory. Once set, the hardware will clear it to 0 after 8 instruction cycles. This is used primarily for testing. This is a Read Only bit.

#### 2.1.3 FORCED EXECUTION FROM BOOT ROM

When the user is developing his own ISP routine, he may encounter code lockups due to mistakes in his software. There is a hardware method to get out of these lockups and force execution from the Boot ROM's MICROWIRE/PLUS routine, so that the customer can erase his flash code and start over. The method to force this condition is to drive the G6 pin to high voltage (2X V<sub>CC</sub>) and activate Reset. As a note for user of the parallel printer port connects, it is advisable that the user remove the G6 line from the PC when applying high voltage. The voltage may be high enough to permanently damage the PC parallel port logic circuits. The high voltage condition on G6 must be held for at least 3 instruction cycles longer than Reset is active. This special condition will start execution from location 0000 in the Boot ROM where the user can input the appropriate commands, using MICROWIRE/PLUS<sup>TM</sup>, to erase the flash program memory and reprogram it.

## 2.1.4 RETURN TO FLASH WITHOUT HARDWARE RESET

After programming the entire program memory, including options (and setting the FLEX bit in the Option Register), it is necessary to exit the Boot ROM and return to the flash program memory for program execution. This can be accomplished through the use of the MICROWIRE/PLUS™ ISP Exit command as described later.

#### 2.1.5 MICROWIRE/PLUS ISP COMMANDS

The MICROWIRE/PLUS™ ISP will support the following features and commands:

- Read a byte from a specified address.

- Write a byte from a specified address.

- Erase a page at a specified address.

- Erase the entire flash program memory (mass erase).

- · Read multiple bytes starting at a specified address.

- Write multiple bytes starting at a specified address.

- Read Option register.

- Exit ISP by resetting the device and return execution to flash program memory if the FLEX bit is set in the Option Register.

#### 2.1.6 VIRTUAL E<sup>2</sup> COMMANDS

The following commands will support transferring blocks of data from RAM to flash program memory, and vice-versa.

- Erase a page of flash memory at a specified address.

- Copy a block of data from RAM into flash program memory.

- Copy a block of data from program flash memory to RAM.

## **2.1.7 SAMPLE PROGRAM:** A Light Sequencer.

Since we have completed our introduction to Flash Family device, lets begin to work on our sample application program.

The goal of this section is to familiarize the user with the following:

- 1. Writing and saving a program for the COP8™ Flash Family devices

- 2. Using the MICROWIRE/PLUS™ flash command: Set PGMTIM (write timing register)

- 3. Using the internal flash command: cwritebf (write a byte to the flash)

- 4. Using the internal flash command: creadbf (read a byte from the flash)

- 5. Using the internal/ MICROWIRE/PLUS™ flash command: EXIT (reset the microcontroller).

We will achieve the above commands by using the FLASHWIN Programmer's Guide. See Application Note–1154 for additional information.

## 2.1.7.1 Description of the Sample Application Program

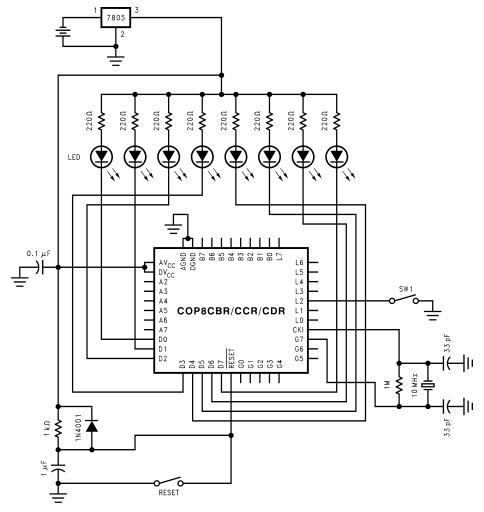

The goal of the sample program is to teach the user the basics of using the COP8<sup>TM</sup> flash family devices. The schematic in Figure 2 shows the circuit we are going to use. We will be attaching 8 LEDs, Each LED will be connected in such a way as to sink current from the microcontroller. The cathode (long leg of the LED) will be connected toward the COP8<sup>TM</sup> Flash Family devices. The short leg of the LED (anode) will be connected through a resistor toward the  $V_{CC}$  power supply.

Figure 2. Sample Application Circuit

## 2.1.7.2 Writing the Program

We will begin first by writing the program. Launch the Windows 95 *Editor* by going to the taskbar and clicking on the **Start** button. Then click on **Run**. At the Run dialog **Open** window type in the Open field**edit**. Type in exactly as is listed in **Example 1**. When done, Click on **File** and then **Save**. At the new dialog window type in c:\asm\sequencer.asm (where asm is the directory in which the assembler is installed in). When done, click on **File** and then click on **Exit**.

## Example 1. Sample Application Code (sequence.asm)

```

; Program: Sequence.asm

; Purpose: Demonstrate the use of flash routines

; Date: 02/5/00

.INCLD COP8CBR.INC

; INCLUDE FILE FOR THE COP8CBR

creadbf = 011

; Entry point for the read byte of flash command

cwritebf = 014

; Entry point for the write byte of flash command

exit = 062

; Entry point for Resetting the microcontroller

.sect data,reg,abs=0xF4

; FOR RAM STORAGE AREA

LED_BITPOS:.DSB 1

;STORAGE FOR THE LED POSITION

DELAY_NUM: .DSB 1

;STORAGE FOR THE NUMBER OF DELAYS

.sect code,rom,abs=0

;BEGINNING CODE SPACE

.org 0

;START AT LOCATION 0

MAIN:

```

## Example 1. Sample Application Code (sequence.asm) (continued)

```

;USE PORTL.2 AS AN INPUT

RBIT 2, PORTLC

SBIT 2, PORTLD

; CAUSE PORTL. 2 TO BE AN INPUT WITH PULL-UP

LD PGMTIM, #07B

FOR A 10MHZ CLOCK

LD ISPADHI, #000

;LOAD THE HIGH BYTE ADDRESS

LD ISPADLO, #0A0

;LOAD THE LOW BYTE ADDRESS

LD ISPWR, #080

;FOR LED POSITION 10000000

LD ISPKEY, #098

;LOAD THE KEY

; CALL THE ROUTINE

JSRB cwritebf

LD ISPADLO, #0A1

;LOAD THE LOW BYTE ADDRESS

LD ISPWR, #040

FOR LED POSITION 01000000

LD ISPKEY, #098

;LOAD THE KEY

JSRB cwritebf

; CALL THE ROUTINE

LD ISPWR.#020

FOR LED POSITION 00100000

LD ISPADLO, #0A2

;LOAD THE LOW BYTE ADDRESS

LD ISPKEY, #098

;LOAD THE KEY

JSRB cwritebf

; CALL THE ROUTINE

LD ISPWR.#010

FOR LED POSITION 00010000

LD ISPADLO, #0A3

;LOAD THE LOW BYTE ADDRESS

LD ISPKEY, #098

;LOAD THE KEY

JSRB cwritebf

; CALL THE ROUTINE

LD ISPWR, #008

; FOR LED POSITION 00001000

LD ISPADLO,#0A4

; LOAD THE LOW BYTE ADDRESS

LD ISPKEY.#098

; LOAD THE KEY

JSRB cwritebf

; CALL THE ROUTINE

LD ISPWR, #004

; FOR LED POSITION 00000100

LD ISPADLO,#0A5

; LOAD THE LOW BYTE ADDRESS

LD ISPKEY,#098

; LOAD THE KEY

JSRB cwritebf

; CALL THE ROUTINE

LD ISPWR, #002

; FOR LED POSITION 00000010

LD ISPADLO, #0A6

; LOAD THE LOW BYTE ADDRESS

LD ISPKEY, #098

; LOAD THE KEY

JSRB cwritebf

; CALL THE ROUTINE

LD ISPWR, #001

; FOR LED POSITION 00000001

LD ISPADLO, #0A7

; LOAD THE LOW BYTE ADDRESS

LD ISPKEY, #098

; LOAD THE KEY

JSRB cwritebf

; CALL THE ROUTINE

; BEGINNING OF THE LOOP

LOOP:

LD LED_BITPOS,#0A0

; POSITION IS INITIALIZED TO #0A0

SEQUENCE:

; BEGINING OF THE SEQUENCE

JSR DELAY

; JUMP TO THE DELAY ROUTINE

LD A, LED_BITPOS

; GET THE BIT POSITION

; SWAP IT WITH THE ISP LOW ADDRESS BYTE

X A, ISPADLO

LD ISPKEY, #098

; LOAD THE KEY

JSRB creadbf

; CALL THE ROUTINE

LD A. ISPRD

; LOAD THE RESULTS INTO THE ACCUMULATOR

; SWAP IT WITH PORTD

X A.PORTD

LD A, LED_BITPOS

; LOAD THE LED_BITPOS VARIABLE

; ROTATE THROUGH THE BIT POSITIONS

INC A

; INCREMENT THE ACCUMULATOR

X A, LED_BITPOS

; SWAP IT WITH THE LED BITPOS

; STOP AT THE EIGHTH BIT POSITION SHIFT

IFEQ A,#0A7

JP LOOP

; RETURNING TO THE MAIN LOOP

JP SEQUENCE

; RETURN TO THE MAIL LOOP SEQUENCE

DELAY:

LD DELAY_NUM, #0FF

; CREATE 256 NOPS

DELAY LOOP:

; THE DELAY ROUTINE

NOP

; CREATE A 1 CYCLE DELAY

NOP

; CREATE A 1 CYCLE DELAY

DRSZ DELAY NUM

; COUNT DOWN UNTIL ZERO

; OTHERWISE JUST JUMP INTO THE DELAY

JP DELAY LOOP

RET

IFBIT 2, PORTLP

; DETECT IF THE SWITCH IS OFF

JP NEXT2

; IF OFF THEN GOTO NEXT COMMAND

```

## Example 1. Sample Application Code (sequence.asm) (continued)

```

JP QUIT ; OTHERWISE QUIT

NEXT2: ; NEXT COMMAND

RET ; RETURN FROM THE SUBROUTINE

QUIT: ; THIS ROUTINE WILL EXIT WITH AN INTERNAL RESET

LD ISPKEY,#098 ; LOAD THE KEY

JSRB exit ; CALL THE EXIT

.END MAIN ; END OF PROGRAM

```

## 2.1.7.3 Assembling and Linking the Sample Program

Example 2 shows the assembled code. Linking must occur after assembling the code. This can be accomplished via the command: "Incop sequencer". A hex file named sequencer.hex will be produced as a result of this command. To launch the FLASHWIN application, see the FLASHWIN Programmer's Guide AN-1154. Click on the Set CLOCK button to set the write timer register. A dialog box will appear. Enter 10 for a 10 MHz CKI frequency. Next, click on the "Upload from a hex file" command. Click on the "Select File" button. Either click on the file or enter it by click on it. Click Ok and the upload process will begin. After the upload is complete perform a write byte to the Configuration Operation. Write a 1 to location 0xFFFF (See Table 8 for additional information) in order to program the microcontroller for execution out of the flash memory. Next click Reboot to exit the MICROWIRE/PLUS ISP routine. Execution will be from the flash array once the reset cycle has completed.

## Example 2. The Listing of the Assembled Code (sequence.lis)

```

NSC ASMCOP, Version 5.3 (April 12 17:13

2000) SEQUENCE 13-Sep-00

14:45

PAGE 1

1 ; Program: Sequence.asm

2 ; Purpose: Demonstrate the use of the flash routines

3 ; Date: 02/5/00

5 .INCLD COP8CBR.INC ; INCLUDE FILE FOR THE COP8CBR

7 0011 creadbf = 011; Entry point for the read byte of flash command

8 0014 cwritebf = 014; Entry point for the write byte of flash command

9 0062 exit = 062; Entry point for Resetting the microcontroller

10

11 00F4 .sect data,reg,abs=0xF4 ; For RAM storage area

12 00F4 LED_BITPOS:.DSB 1 ; Storage for the LED position

13 00F5 DELAY_NUM: .DSB 1 ; Storage for the number of delays

14 0000 .sect code,rom,abs=0 ; Beginning code space

15 0000 .org 0

16

17 0000 MAIN:

18 0000 DF00 3 LD S, #000 ; Use PORTL.2 as an input

19 0002 BDD16A 4 RBIT 2, PORTLC; Cause PORTL.2 to be an input with pull-up

20 0005 BDD07A 4 SBIT 2, PORTLD ; For a 10MHz clock

22 0008 BCA900 3 LD ISPADHI, #000 ; Load the high byte address

23 000B BCA8A0 3 LD ISPADLO, #0A0 ; Load the low byte address

24 000E BCAB80 3 LD ISPWR, #080 ; For LED position 10000000

25 0011 BCE298 3 LD ISPKEY, #098 ; Load the key

26 0014 6114 5 JSRB cwritebf; Call the routine

2.7

28 0016 BCA8A1 3 LD ISPADLO, #0A1 ; Load the low byte address

29 0019 BCAB40 3 LD ISPWR, #040 ; for the LED poistion 01000000

30 001C BCE298 3 LD ISPKEY, #098 ; Load the key

31 001F 6114 5 JSRB cwritebf ; Call the routine

32

33 0021 BCAB20 3 LD ISPWR, \#020 ; For the LED poistion 00100000

```

## Example 2. The Listing of the Assembled Code (sequence.lis) (continued)

```

34 0024 BCA8A2 3 LD ISPADLO, #0A2; Load the low byte address

35 0027 BCE298 3 LD ISPKEY, #098 ; Load the key

36 002A 6114 5 JSRB cwritebf ; Call the routine

37

38 002C BCAB10 3 LD ISPWR, #010 ; For the LED poistion 00010000

39 002F BCA8A3 3 LD ISPADLO, #0A3 ; Load the low byte address

40 0032 BCE298 3 LD ISPKEY, #098 ; Load the key

41 0035 6114 5 JSRB cwritebf ; Call the routine

43 0037 BCAB08 3 LD ISPWR, #008 ; For the LED poistion 00001000

44 003A BCA8A4 3 LD ISPADLO, #0A4 ; Load the low byte address

45 003D BCE298 3 LD ISPKEY, #098 ; Load the key

46 0040 6114 5 JSRB cwritebf ; Call the routine

48 0042 BCAB04 3 LD ISPWR, #004 ; For the LED poistion 00000100

49 0045 BCA8A5 3 LD ISPADLO, #0A5 ; Load the low byte address

50 0048 BCE298 3 LD ISPKEY, #098 ; Load the key

51 004B 6114 5 JSRB cwritebf ; Call the routine

53 004D BCAB02 3 LD ISPWR, #002 ; For the LED poistion 00000100

54 0050 BCA8A6 3 LD ISPADLO, #0A6 ; Load the low byte address

55 0053 BCE298 3 LD ISPKEY, #098 ; Load the key

56 0056 6114 5 JSRB cwritebf ; Call the routine

NSC ASMCOP, Version 5.3 (April 12 17:13

2000) SEQUENCE 13-Sep-00

14:45

PAGE 2

57

58 0058 BCAB01 3 LD ISPWR, #001 ; For the LED poistion 00000100

59 005B BCA8A7 3 LD ISPADLO, #0A7; Load the low byte address

60 005E BCE298 3 LD ISPKEY, #098 ; Load the key

61 0061 6114 5 JSRB cwritebf ; Call the routine

63 0063 LOOP: ; Beginning of the Loop

64 0063 D4A0 3 LD LED_BITPOS, #0A0 ; Position is initialized to #0A0

66 0065 SEQUENCE: ; Beginning of the sequence

67 0065 307D 5 JSR DELAY; Jump to the delay routine

68 0067 9DF4 3 LD A, LED_BITPOS ; Get the bit positon

69 0069 9CA8 3 X A,ISPADLO ; Swap it with the ISP low address byte

70 006B BCE298 3 LD ISPKEY, #098 ; Load the key

71 006E 6111 5 JSRB creadbf ; Call the routine

72 0070 9DAA 3 LD A,ISPRD ; Load the results into the accumulator

73 0072 9CDC 3 X A, PORTD ; Swap it with PORTD

75 0074 9DF4 3 LD A, LED_BITPOS ; Load the LED_BITPOS variable

77 ; Rotate through the bit positions

78 0076 8A 1 INC A ; Increment the accumulator

79

80 0077 9CF4 3 X A, LED_BITPOS ; Swap it with the LED_BITPOS

81

82 0079 92A7 2 IFEQ A, #0A7 ; Stop at the eighth bit position shift

83 007B E7 3 JP LOOP ; Returning to the main loop

84 007C E8 3 JP SEQUENCE; Return to the main loop sequence

85

86 007D DELAY:

87 007D D5FF 3 LD DELAY_NUM, #0FF; Create 256 NOPs

88 007F DELAY_LOOP: ; The delay routine

89 007F B8 1 NOP; Create a 1 cycle delay

90 0080 B8 1 NOP; Create a 1 cycle delay

91 0081 C5 3 DRSZ DELAY_NUM ; Count down until zero

92 0082 FC 3 JP DELAY_LOOP; Otherwise just jump into the delay

93 0083 8E 5 RET

```

## Example 2. The Listing of the Assembled Code (sequence.lis) (continued)

```

94 0084 BDD272 4 IFBIT 2, PORTLP; Detect if the switch is off

95 0087 01 3 JP NEXT2; If off then goto next command

96 0088 01 3 JP QUIT; Otherwise quit

97 0089 NEXT2: ; Next command

98 0089 8E 5 RET; Return from the subroutine

100 008A QUIT: ; This routine will exit with an internal reset

101 008A BCE298 3 LD ISPKEY, #098 ; Load the key

102 008D 6162 5 JSRB exit ; Call the exit

103 008F .END MAIN ; End of program

**** Errors: 0, Warnings: 0

Checksum: 0x543B

Byte Count: 0x008F (143)

Input File: c:\nsc\sequence.asm

Output File: c:\nsc\sequence.obj

Memory Model: Large

Chip: 8CBR

```

## 2.1.7.4 1.8.4 Analysis of the Program

The best way to understand a program is to cut it apart line by line. Lines 14-53 shows how to use the function cwritebf (customer write byte). They also show the correct calling format and usage of the JSRB instruction. Loading the KEY register bit is also shown in the code sample. The code will write the bit patterns listed in Table 7 to the flash memory.

Lines 66-86 makes up the main calling routine. The code will use the creadbf function to read flash memory. Lines 92-104 makes up the delay and detect\_exit routine. Lines 106-109 makes up the exit routine. The exit routine calls the reset function and will cause the microcontroller to reset.

The flow to this program is represented in Figure 3.

Sequence Pattern Sequence # n n n O n

Table 7. Bit Patterns for the Sample Program

Figure 3. Flow for the Sequencer Program

## 3 ADVANCED ISP—SOFTWARE TOPICS

## 3.1 IN SYSTEM PROGRAMMING (ISP) SUPPORT BLOCKS

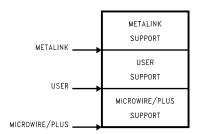

The Flash Family's Boot ROM consists of three main blocks: The user support portion, the MetaLink support portion and the MICROWIRE/PLUS support portion. Figure 4 shows the relative organization of these support blocks. Each command portion is both independent and self contained. The entire Boot ROM is 1 Kbytes. This document assumes that the reader is fluent in the use of MICROWIRE/PLUS and its transmission protocol. For reference please refer the MICROWIRE/PLUS section of the Flash Family datasheet.

Figure 4. ISP Boot ROM Interface

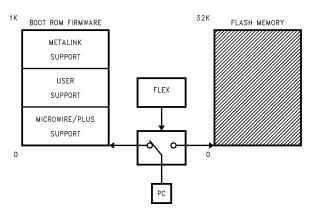

## 3.2 Boot ROM Memory Layout

Figure 5 shows how the Boot ROM is organized. FLEX is a hardware bit that controls whether program execution occurs from flash memory of Boot\_ROM. It uses data from the Option register. When the FLEX bit option register=1, execution is from the flash program memory. When bit FLEX=0, program execution occurs from the Boot ROM.

Figure 5. COP8 FLASH Memory Layout

## 3.3 PROGRAMMABLE OPTIONS DESCRIPTION

The programmable configuration options for this device are listed below.

- Program Memory Security

- · Watchdog feature

- Halt Enable feature

- Power-up execution feature

The options will be stored in the highest location in program memory. This location will be called the Option Register. For devices with 32K of Program Memory, the options are stored at location 7FFF. For 16K devices, they will be stored at 3FFF, for 8K devices 1FFF, and for 4K devices 0FFF, however the Option Register can always be accessed by referencing Flash address FFFF. The options are programmed with either external programming or ISP. The location must be erased before programming. The user must not store instructions in the Option register location. If the software tries to execute from the Option register, 00 data will be returned to the instruction register and the device will execute the Software Trap.

#### 3.4 OPTION REGISTER BIT ASSIGNMENTS

The format of the Option Register bit locations are shown in Table 8.

**Table 8. Option and TCON Register Bit Assignments**

|          | Option Register                                 |  |  |  |  |  |  |  |

|----------|-------------------------------------------------|--|--|--|--|--|--|--|

| Bit 7    | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |  |  |  |  |  |  |  |

| Reserved | Reserved Reserved Reserved WD HALT FLEX         |  |  |  |  |  |  |  |

Bit 7 -- Reserved

Bit 6 - Reserved

Bit 5 - SEC - Security bit

=1 Security enabled

=0 Security disabled

Bits 4,3 - Reserved

Bit 2 - WD - Watchdog

=1 Watchdog feature is disabled with G1 being a standard I/O.

=0 Watchdog feature is enabled to G1 output with weak pull-up enabled when output is not valid.

- Bit 1 HALT Halt Enable

- =1 Halt mode is disabled

- =0 Halt mode is enabled

- Bit 0 FLEX Flash execution

- =1 Execute from Flash program memory upon exiting Reset

- =0 Execute from Boot ROM upon exiting Reset

#### 3.5 SECURITY

The device has a security feature, when enabled, it prevents reading, writing, and page erases of the flash program memory. Bit-5 in the Option register determines whether security is enabled or disabled. If the security option is disabled, the contents of the internal flash program memory is not protected. If the security feature is enabled;

When executing from user ISP:

1. Reads, writes, page erases, mass erases are all allowed. The user is expected to enforce security within the application code.

When executing from NSC (Boot ROM) ISP or ICE emulation. All writes, reads, and page erases are prohibited.

- 1. Reads will return FF.

- 2. Mass erase is permitted. This also erases the Option register.

- 3. The Option register is readable by reading location FFFF.

- 4. Reads, writes, page erases are prohibited.

#### 3.6 MICROWIRE/PLUS SUPPORT BLOCKS

#### 3.6.1 2.5.1 Introduction

MICROWIRE/PLUS is a synchronous SPI compatible serial communication system that allows this device to communicate with any other device that also supports the MICROWIRE/PLUS system. Examples of such devices include A/D converters, comparators, EEPROMs, display drivers, telecommunications devices, and other processors. The MICROWIRE/PLUS serial interface uses a simple and economical 3-wire connection between devices.

Several MICROWIRE/PLUS devices can be connected to the same 3-wire system. One of these devices, operating in what is called the master mode, supplies the synchronous clock for the serial interface and initiates the data transfer. Another device, operating in what is called the slave mode, responds by sending (or receiving) the requested data. The slave device uses the master's clock for serially shifting data out (or in), while the master device shifts the data in (or out).

On this device, the three interface signals are called SI (Serial Input), SO (Serial Output), and SK (Serial Clock). To the master, SO and SK are outputs (connected to slave inputs), and SI is an input (connected to slave outputs).

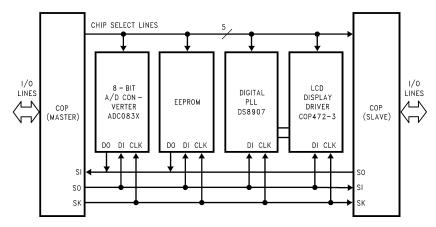

This device can operate either as a master or a slave, depending on how it is configured by the software. Figure 6 shows an example of how several devices can be connected together using the MICROWIRE/PLUS system, with the device (on the left) operating as the master, and other devices operating as slaves. The protocol for selecting and enabling slave devices is determined by the system designer.

Figure 6. MICROWIRE/PLUS Example

#### 3.6.2 Firmware—MICROWIRE/PLUS Initialization

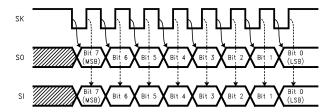

The MICROWIRE/PLUS support block will initialize the internal communication block with the following parameters: CTRL.MSEL=1, PORTGD.SO=1, PORTGD.SK=1, PORTGC.SI=1, and PORTGC.SK=0. Table 9 and Table 10 contain information about the MICROWIRE/PLUS mode. Figure 7 shows the waveforms that are from the MICROWIRE/PLUS block.

Table 9. Initialization of the MICROWIRE/PLUS by the Firmware

| Port G Config. Reg.<br>Bits G5-G4 | MICROWIRE/PLUS<br>Operation    | G4 Pin Function | G5 Pin Function | G6 Pin Function |

|-----------------------------------|--------------------------------|-----------------|-----------------|-----------------|

| 0-1                               | Slave, Data Out and<br>Data In | SO Output       | SK Input        | SI Input        |

Table 10. MICROWIRE/PLUS Mode Selected by the Firmware

| Poi                    | Port G      |                    | SI Sampled On: | SK Idle Phase  |  |

|------------------------|-------------|--------------------|----------------|----------------|--|

| G6 (SKSEL) Config. Bit | G5 Data Bit | SO Clocked Out On: | or Sampled On. | on luie Filase |  |

| 1                      | 1           | SK Falling Edge    | SK Rising Edge | High           |  |

Figure 7. MICROWIRE/PLUS Interface Timing, Normal SK Mode, SK Idle Phase being High

## 3.7 PC to Boot from MICROWIRE/PLUS Connection Diagram

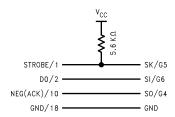

Figure 8 shows the necessary connections to attach the MICROWIRE/PLUS to the PC's parallel port. The flash microcontroller connection to the PC will be accomplished via a four wire interface.

Figure 8. Parallel Port Connection Diagram

Table 11 shows the necessary connections used in the building of the parallel adapter for the COP8 Flash Family microcontroller.

Table 11. Parallel Port <-> MICROWIRE/PLUS Conversion

| Parallel Port<br>Printer Port<br>Pin Names | Parallel<br>Printer Port<br>Pin Numbers | MICROWIRE/PLUS<br>Pin Names |

|--------------------------------------------|-----------------------------------------|-----------------------------|

| STROBE                                     | 1                                       | SK/G5                       |

| DO                                         | 2                                       | SI/G6                       |

| NEG(ACK)                                   | 10                                      | SO/G4                       |

| GND                                        | 18                                      | GND                         |

#### 3.8 FIRMWARE—MICROWIRE/PLUS INITIALIZATION

The MICROWIRE/PLUS support block will initialize the internal communication block with the following parameters: CTRL.MSEL=1, PORTGD.SO=1, PORTGD.SK=1, PORTGC.SI=1, and PORTGC.SK=0. Table 9 and Table 10 contains information about the MICROWIRE/PLUS mode. Figure 7 shows the waveforms that are from the MICROWIRE/PLUS block.

Table 12. Initialization of the MICROWIRE/PLUS by the Firmware

| Port G Config. Reg.<br>Bits G5-G4 | MICROWIRE/PLUS<br>Operation    | (34 Pin Flinction |          | G6 Pin Function |  |

|-----------------------------------|--------------------------------|-------------------|----------|-----------------|--|

| 0-1                               | Slave, Data Out and<br>Data In | SO Output         | SK Input | SI Input        |  |

Table 13. MICROWIRE/PLUS Mode Selected by the Firmware

| Por                    | rt G        | SO Clocked Out On:  | SI Sampled On: | SK Idle Phase |  |

|------------------------|-------------|---------------------|----------------|---------------|--|

| G6 (SKSEL) Config. Bit | G5 Data Bit | 30 Clocked Out Oil. | Si Sampleu On. |               |  |

| 1                      | 1           | SK Falling Edge     | SK Rising Edge | High          |  |

Figure 9. MICROWIRE/PLUS Interface Timing, Normal SK Mode, SK Idle Phase being High

## 3.8.1 The MICROWIRE/PLUS Packet Composition

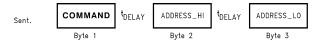

A typical MICROWIRE/PLUS packet is composed of a three byte frame (although this varies with the chosen command). Figure 10 is a symbolic representation of the ISP-MICROWIRE/PLUS packet. A trigger byte is a value which will cause a ISP (In System Programming) command to be executed (e.g. erase, read or write a byte of flash). The COMMAND Byte holds this trigger byte value. Refer to Table 16 for valid MICROWIRE/PLUS commands and their trigger byte values. Bytes ADDRESS\_HI and ADDRESS\_LO refer to the high and low byte address of the flash memory that is to be operated upon. The symbol t<sub>delay</sub> represents the delay that is required when sending the command, ADDRESS\_HI and ADDRESS\_LO bytes.

Figure 10. ISP Command Frame

## 3.8.2 Required Delays In Cascading Microwire Command Frames

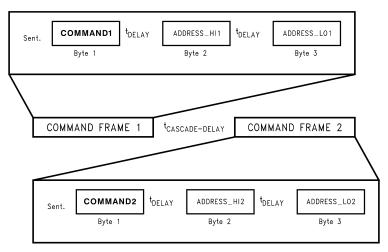

A certain amount of delay must be observed when sending multiple command frames in a data stream. The symbol  $t_{cascade-delay}$  represents the delay that is required when sending several commands in a data stream. The host must wait  $t_{cascade-delay}$  cycles before sending the next command frame to the COP8 Flash Family device. Figure 11 shows the delay relationship. Refer to Table 14 for the values of  $t_{cascade-delay}$ . Refer to Table 15 for the values of  $t_{delay}$ . The symbol  $t_1...t_N$  denotes individual delay requirements (which varies among different commands).

Table 14. Required time delays (in instruction cycles) for cascading command frames after an initial command was executed

| Command    | t <sub>CASCADE-DELAY</sub> |

|------------|----------------------------|

| READ_BYTE  | 6                          |

| WRITE_BYTE | 6                          |

| BLOCKR     | 13                         |

| BLOCKW     | 6                          |

| PGERASE    | 6                          |

| MASS_ERASE | 6                          |

| EXIT       | N/A                        |

| PGMTIM_SET | 6                          |

Figure 11. Cascade Delay Requirement

| Table 15.  | Required    | Time Delay   | vs (In   | Instruction  | Cycles)  |

|------------|-------------|--------------|----------|--------------|----------|

| I UDIC IO. | 1 toquii ou | I IIIIC DCIU | , 5 (111 | IIIOU GOUOII | Cy CiCS) |

| COMMAND    | t <sub>1</sub> | t <sub>2</sub> | t <sub>3</sub> | t <sub>4</sub> | <b>t</b> <sub>5</sub> | t <sub>6</sub> | t <sub>N</sub> |

|------------|----------------|----------------|----------------|----------------|-----------------------|----------------|----------------|

| READ_BYTE  | 35             | 100            | 100            | N/A            | N/A                   | N/A            | N/A            |

| WRITE_BYTE | 35             | 100            | 20             | 10             | N/A                   | N/A            | N/A            |

| BLOCKR     | 35             | 100            | 100            | 100            | 140                   | 140            | 140            |

| BLOCKW     | 35             | 100            | 100            | 100            | 100                   | 100            | 52             |

| PGERASE    | 35             | 100            | 100            | N/A            | N/A                   | N/A            | N/A            |

| MASS_ERASE | 25             | 100            | N/A            | N/A            | N/A                   | N/A            | N/A            |

| EXIT       | N/A            | N/A            | N/A            | N/A            | N/A                   | N/A            | N/A            |

| PGMTIM_SET | 35             | 35             | N/A            | N/A            | N/A                   | N/A            | N/A            |

## 3.8.3 Variable Host Delay

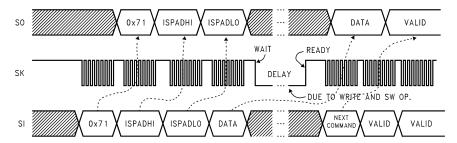

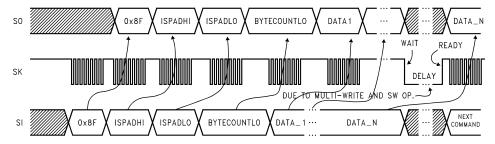

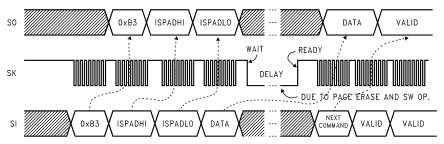

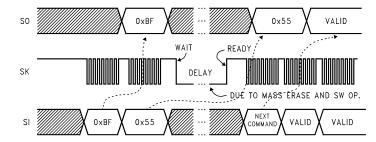

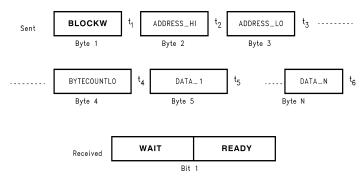

A special type of communication has been implemented in the device firmware in order to allow the microcontroller enough time to complete a write or erase operation. This type of communication was developed since the microcontroller may be used in situations where the clock is extremely slow and writes to the flash memory will take a large amount of time. This implementation relieves the user of having to manually change the write delays in their host software. Figure 12 shows how the VARIABLE HOST DELAY configuration is implemented on a byte write. Figure 13 shows how the VARIABLE HOST DELAY configuration is implemented on a block write. Figure 14 shows how the VARIABLE HOST DELAY configuration is implemented on a page erase. Figure 15 shows how the VARIABLE HOST DELAY configuration is implemented on a mass erase. Since the SK (Serial CLOCK) is normally high, the microcontroller brings SK low to indicate to the host that a WAIT condition (i.e. the SK pin is low) exists. The host then goes into a loop until the WAIT condition changes to a READY condition (i.e., the SK pin is high again). The controller then returns to command decode and waits for the next command.

Figure 12. Byte Write Waveform (Relative Bytes are Shown)

Figure 13. Block Write Waveform (Relative Bytes are Shown)

Figure 14. Page Erase Waveform (Relative Bytes are Shown)

Figure 15. Mass Erase Waveform (Relative Bytes are Shown)

#### 3.8.4 MICROWIRE/PLUS—Boot ROM Startup Behavior

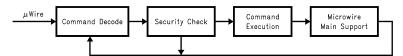

Upon start-up the ISP Boot ROM will detect if the G6 pin is high. This is used to detect if a high voltage condition on the G6 pin is present (i.e., a forced Boot ROM re-entry due to code lockup, for additional information refer to Section 2.1.3.) By using this technique the Boot ROM avoids any bit that may be inadvertently entered on to the SI pin. If the G6 pin is not high at start-up, the ISP Boot ROM will try to detect if a valid command is received on a transmission. If a valid command is received, the Boot ROM firmware will check to see if the SECURITY bit is set. Table 16 shows the valid MICROWIRE/PLUS commands. If security is set, the Boot ROM will disable all ISP functions except the reading of the **OPTION** register at 0xFFFF, the execution of a mass erase on the flash memory and the setting of the PGMTIM Register. Read attempts of flash memory, other than location 0xFFFF, Option Register, while security is set, will result with a 0xFF sent back through the MICROWIRE/PLUS. In general, the Boot ROM firmware will decode the command, check security, execute the command (if security is off) and execute the MICROWIRE/PLUS Main Support Block (e.g., triggering the PSW.BUSY bit in order to send the data back to the host.) See Figure 16 for the ISP—MICROWIRE/PLUS Control flow.

|                | Table 16. MICROWIRE/PLUS Commands |      |                                                                                             |                                     |                                                                         |  |  |  |  |

|----------------|-----------------------------------|------|---------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------|--|--|--|--|

| Command        | Function Byte Value Parameters    |      | Parameters                                                                                  | Variable Host Delay<br>Implemented? | Return Data                                                             |  |  |  |  |

| PGMTIM_SET     | Write Pulse<br>Timing<br>Register | 0x3B | Value                                                                                       | No                                  | N/A                                                                     |  |  |  |  |

| PAGE_ERASE     | Page Erase                        | 0xB3 | Starting Address of Page                                                                    | Yes                                 | N/A                                                                     |  |  |  |  |

| MASS_ERAS<br>E | Mass Erase                        | 0xBF | Confirmation Code                                                                           | Yes                                 | N/A (The entire Flash<br>Memory will be erased)                         |  |  |  |  |

| READ_BYTE      | Read Byte                         | 0x1D | Address High, Address<br>Low                                                                | No                                  | Data Byte if Security not set. 0xFF if Security set.                    |  |  |  |  |

| BLOCKR         | Block Read                        | 0xA3 | Address High, Address<br>Low, Byte Count (n) High,<br>Byte Count (n) Low (0 ≤ n<br>≤ 32767) | No                                  | n Data Bytes if Security<br>not set. n Bytes of 0xFF if<br>Security set |  |  |  |  |

0x71

WRITE\_BYTE Write Byte

N/A

Yes

Address High, Address

Low, Data Byte

| Command | Function    | Byte Value | Parameters                                                                                                                                                                                                    | Variable Host Delay<br>Implemented? | Return Data             |  |

|---------|-------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------|--|

| BLOCKW  | Block Write | 0x8F       | Address High, Address Low, Byte Count (0 ≤ n ≤ 16), n Data Bytes Data location must be within a 64 byte segment for a 32k device, 32 byte for 1k and 4k devices (1/2 page) due to multi-byte write limitation | Yes                                 | N/A                     |  |

| EXIT    | EXIT        | 0xD3       | N/A                                                                                                                                                                                                           | No                                  | N/A (Device will Reset) |  |

| INVALID | N/A         |            | Any other invalid command will be ignored                                                                                                                                                                     | N/A                                 | N/A                     |  |

Table 16. MICROWIRE/PLUS Commands (continued)

Figure 16. The ISP—MICROWIRE Control

#### 3.9 MICROWIRE COMMANDS AVAILABLE

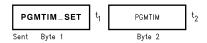

#### 3.9.1 **PGMTIM SET**

Sets the flash write timing register to match that of the CKI frequency. See Table 17 for values.

Description: Figure 17 shows the format of the PGMTIM SET command. The PGMTIM SET command will transfer the next byte sent into the flash programming time register. No acknowledgment will be sent. The symbol t<sub>1</sub> denotes the time delay between the command byte and the setting of the PGMTIM register. This command is always available. This command must be used before any "writes" can occur (i.e., page erase, mass erase, write byte or block write). See Table 21 for the value(s) of t<sub>1</sub> and t<sub>2</sub>. Table 17 shows valid values for the PGMTIM register. This command is security independent.

Figure 17. The Set PGMTIM Command

**Table 17. Valid PGMTIM Values**

|   | Bit | t Values | for the | PGMTII | M Regis | ter |   | Hex Value | CKI Frequency Range |

|---|-----|----------|---------|--------|---------|-----|---|-----------|---------------------|

| 7 | 6   | 5        | 4       | 3      | 2       | 1   | 0 | nex value | CKI Frequency Kange |

| 0 | 0   | 0        | 0       | 0      | 0       | 0   | 1 | 0x01      | 25 kHz-33.3 kHz     |

| 0 | 0   | 0        | 0       | 0      | 0       | 1   | 0 | 0x02      | 37.5 kHz–50 kHz     |

| 0 | 0   | 0        | 0       | 0      | 0       | 1   | 1 | 0x03      | 50 kHz-66.67 kHz    |

| 0 | 0   | 0        | 0       | 0      | 1       | 0   | 0 | 0x04      | 62.5 kHz-83.3 kHz   |

| 0 | 0   | 0        | 0       | 0      | 1       | 0   | 1 | 0x05      | 75 kHz–100 kHz      |

| 0 | 0   | 0        | 0       | 0      | 1       | 1   | 1 | 0x07      | 100 kHz-133 kHz     |

| 0 | 0   | 0        | 0       | 1      | 0       | 0   | 0 | 0x08      | 112.5 kHz–150 kHz   |

| 0 | 0   | 0        | 0       | 1      | 0       | 1   | 1 | 0x0B      | 150 kHz-200 kHz     |

| 0 | 0   | 0        | 0       | 1      | 1       | 1   | 1 | 0x0F      | 200 kHz-266.67 kHz  |

| 0 | 0   | 0        | 1       | 0      | 0       | 0   | 1 | 0x11      | 225 kHz-300 kHz     |

| 0 | 0   | 0        | 1       | 0      | 1       | 1   | 1 | 0x17      | 300 kHz-400 kHz     |

| 0 | 0   | 0        | 1       | 1      | 1       | 0   | 1 | 0x1D      | 375 kHz–500 kHz     |

|   | Bit | Values | for the | PGMTII | M Regis | ter |     | Hew Welvie | CKI Francisco Banco |

|---|-----|--------|---------|--------|---------|-----|-----|------------|---------------------|

| 7 | 6   | 5      | 4       | 3      | 2       | 1   | 0   | Hex Value  | CKI Frequency Range |

| 0 | 0   | 1      | 0       | 0      | 1       | 1   | 1   | 0x39       | 500 kHz-666.67 kHz  |

| 0 | 0   | 1      | 0       | 1      | 1       | 1   | 1   | 0x2F       | 600 kHz-800 kHz     |

| 0 | 0   | 1      | 1       | 1      | 1       | 1   | 1   | 0x3F       | 800 kHz-1.067 MHz   |

| 0 | 1   | 0      | 0       | 0      | 1       | 1   | 1   | 0x47       | 1 MHz-1.33 MHz      |

| 0 | 1   | 0      | 0       | 1      | 0       | 0   | 0   | 0x48       | 1.125 MHz-1.5 MHz   |

| 0 | 1   | 0      | 0       | 1      | 0       | 1   | 1   | 0x4B       | 1.5 MHz–2 MHz       |

| 0 | 1   | 0      | 0       | 1      | 1       | 1   | 1   | 0x4F       | 2 MHz-2.67 MHz      |

| 0 | 1   | 0      | 1       | 0      | 1       | 0   | 0   | 0x54       | 2.625 MHz-3.5 MHz   |

| 0 | 1   | 0      | 1       | 1      | 0       | 1   | 1   | 0x5B       | 3.5 MHz-4.67 MHz    |

| 0 | 1   | 1      | 0       | 0      | 0       | 1   | 1   | 0x63       | 4.5 MHz–6 MHz       |

| 0 | 1   | 1      | 0       | 1      | 1       | 1   | 1   | 0x6F       | 6 MHz–8 MHz         |

| 0 | 1   | 1      | 1       | 1      | 0       | 1   | 1   | 0x7B       | 7.5 MHz–10 MHz      |

| R | R/W | R/W    | R/W     | R/W    | R/W     | R/W | R/W |            |                     |

Table 17. Valid PGMTIM Values (continued)

#### 3.9.2 PAGE\_ERASE—Erase a Page of Flash Memory

Description: Figure 18 shows the format of the PAGE\_ERASE command. The PAGE\_ERASE command will erase a 128 bytes page (depends on the array size, 64 bytes for devices containing 1k and 4k) from the flash memory. The next two bytes after the PAGE\_ERASE byte refer to the beginning high and low bytes of the beginning address of the target flash page. A WAIT/READY technique is used to delay the host when the controller is executing and writing to the flash memory. For a full description of the WAIT/READY command refer to the section regarding **VARIABLE HOST DELAY** (Section 3.8.3). The symbol  $t_1$ ,  $t_2$  denote the time delay between the command byte, the delay required after loading the high address byte, and the delay after loading of the low address byte. The symbol  $t_3$  denotes the time delay after loading the ADDRESS\_LO value. The PAGE\_ERASE command is **NOT** always available (i.e., it is security dependent). If security is set, then the command will be aborted and no acknowledgment will be sent back. See section 10.4 for details on the number of endurance cycles and the number of page erase commands that should be issued prior to writing data into the erased page. See Table 15 for the value(s) of  $t_1$ ,  $t_2$ , and  $t_3$ .

Figure 18. The PAGE ERASE Command

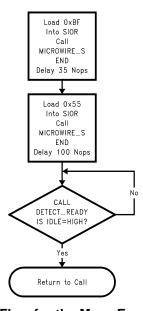

## 3.9.3 MASS\_ERASE—Erase the Entire Flash Memory Array

Description: Figure 19 shows the format of the MASS\_ERASE command. The MASS\_ERASE command will erase the entire flash memory, including the Option Register. The next byte after the MASS\_ERASE command refers to the confirmation key used to double check that a mass erase request was actually sent. The confirmation key must equal 0x55 in order for the MASS\_ERASE command to continue. The symbol t<sub>1</sub> denotes the time delay between the command byte and the transmission of the CONFIRM\_KEY. The symbol t<sub>2</sub> denotes the time delay after the CONFIRM\_KEY has been checked. A WAIT/READY technique is used to delay the host when the controller is executing and writing to the flash memory. For a full description regarding the WAIT/READY command refer to the section regarding VARIABLE HOST DELAY (Section 3.8.3). The MASS\_ERASE command is always available. It is security independent. See Table 15 for the value(s) of t<sub>1</sub>, and t<sub>2</sub>.

Figure 19. The MASS\_ERASE Command

## 3.9.4 READ BYTE—Read a Byte from the Flash Memory Array

Description: Figure 20 shows the format of the READ\_BYTE command. The READ\_BYTE command will read a byte from the flash memory. The next two bytes after the READ\_BYTE refer to the address of the target flash location. The symbol t<sub>1</sub>, t<sub>2</sub> denotes the time delay between the command byte, the delay after loading of the high address byte. Data is sent back after t<sub>3</sub> delay(s) has elapsed. If security is set, the user is only allowed to read location 0xFFFF (Option Register). In other words, if security is set and ADDRESS\_HI and ADDRESS\_LO=0xFFFF then the firmware will allow that operation, otherwise it will send back a 0xFF in the DATA\_RTN byte. See Table 15 for the value(s) of t<sub>1</sub>, t<sub>2</sub>, and t<sub>3</sub>.

Figure 20. The READ\_BYTE Command

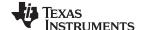

#### 3.9.5 WRITE\_BYTE—Write a Byte to the Flash Memory Array

Description: Figure 21 shows the format of the WRITE\_BYTE routine. The WRITE\_BYTE command will write a byte to the flash memory. The next two bytes after the WRITE\_BYTE byte refer to the high and low byte address of the target flash location. The next byte (DATA\_REC) after the ADDRESS\_LO byte will contain the value that will be stored into the flash location. The symbols  $t_1$ ,  $t_2$  denote the time delay between the command byte and the delay after loading of the high address byte. The symbol  $t_3$  denotes the time delay after loading the ADDRESS\_LO value. Data is saved into the flash location after a  $t_4$  delay. A WAIT/READY signal is used to delay the host. For a full description of the WAIT/READY command refer to the section regarding **VARIABLE HOST DELAY** (Section 3.8.3). The WRITE\_BYTE command is **NOT** always available (i.e. it is security dependent.) If security is set, then the command will be aborted and no acknowledgment will be sent back. See Table 15 for the value(s) of  $t_1$ ,  $t_2$ ,  $t_3$ , and  $t_4$ .

Figure 21. The WRITE\_BYTE Command

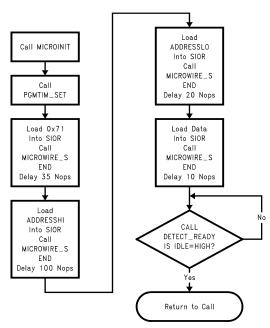

## 3.9.6 BLOCK WRITE—Write a Block of Data to the Flash Memory Array

Description: Figure 22 is a symbolic representation of the BLOCK\_WRITE routine. Data is written in sequential order. This routine is intended to write bytes of data which will reside in a page of flash memory. The next two bytes after the BLOCK\_WRITE byte refer to the beginning high and low byte address of the target flash location. The next byte after the ADDRESS\_LO byte refers to the BYTECOUNTLO variable. The BYTECOUNTLO variable is used by the microcontroller to transfer N bytes (i.e, N=BYTECOUNTLO). The maximum number of bytes that can be written is 16. If the number of bytes

exceeds 16, it may not be guaranteed that all of the bytes were written. The data cannot cross page boundaries. Data must be placed with-in the same 1/2 page segment, 64 bytes for 32k devices and 32 bytes for 1k and 4k devices. This is due to the multi-byte write limitation. If N=0 then the firmware will abort. The symbols  $t_1$  and  $t_2$  denotes the time delay between the command byte and the delay after loading of the high address byte. The symbol  $t_3$  denotes the time delay after loading the ADDRESS\_LO value. The symbol  $t_4$  denotes the necessary time delay after loading the BYTECOUNTLO variable. Data arrives at  $t_5$  cycles after the ADDRESS\_LO value is loaded (i.e. DATA1 - DATA2 have the same delay as DATA2 - DATA3). After the last byte (DATA\_N) is received, a WAIT/ READY signal will be sent to delay the host. For a full description of the WAIT/READY command refer to the section regarding **VARIABLE HOST DELAY** (Section 3.8.3). The command (BLOCK\_WRITE) is **NOT** always available (i.e. it is security dependent). If security is set, then the command will be aborted after the last data (DATA\_N) is received and no acknowledgment will be sent back. See Table 15 for the value(s) of  $t_1$ ,  $t_2$ ,  $t_3$ ,  $t_4$ ,  $t_5$ , and  $t_6$ .

Figure 22. The Block Write Routine

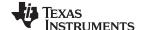

## 3.9.7 BLOCK\_READ—Read a Block from the Flash Memory Array

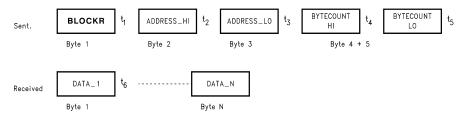

Description: Figure 23 shows the format of the BLOCK\_READ command. The BLOCK\_READ command will read multiple bytes from the flash memory. The next two bytes after the BLOCK\_READ byte refer to the beginning high and low byte address of the target flash location. The next two bytes after the ADDRESS\_LO byte refer to the upper and lower byte of BYTECOUNT. The BYTECOUNT variable is used by the microcontroller to send back N number of bytes (i.e, N=BYTECOUNT). The maximum value of N is 32 kBytes. If N=0 then the firmware will abort. The symbols  $t_1$ ,  $t_2$ and ,  $t_3$  denotes the time delay between the command byte, the delay in loading of the ADDRESS\_HI, and the delay after loading the ADDRESS\_LO. The symbol  $t_4$  denotes the required time delay between loading BYTECOUNTHI and BYTECOUNTLO. Subsequent data is sent to the host at  $t_5$  cycles after BYTECOUNTLO (i.e. DATA1-DATA2 have the same delay as DATA2-DATA3). This command is capable of sending up to 32 kB of flash memory through the MICROWIRE/PLUS. This command is always available however, if security is set, the user is only allowed to read 0xFFFF (Option Register). In other words, if at any time ADDRESS\_HI and ADDRESS\_LO=0xFFFF, the firmware will allow that operation. If at any time ADDRESSHI and ADDRESS\_LO do not equal 0xFFFF and security is set, then the firmware will return 0xFF. This routine will acknowledge by returning data to the host.

Figure 23. The Block Read Command

www.ti.com ISP DOWNLOADER

#### 3.9.8 EXIT—Reset the Microcontroller

Description: Figure 24 shows the format of the EXIT command. The EXIT command will reset the microcontroller. There is no additional information required after the EXIT byte is received. No acknowledgment will be sent back regarding the operation. This command is always available. It is security independent.

Figure 24. The EXIT Command

#### 4 ISP DOWNLOADER

#### 4.1 IMPLEMENTATION EXAMPLE—BUILDING A FIRMWARE MODIFIER/DOWNLOADER

The following section deals with construction of a portable downloader. Several microcontrollers exist which have the MICROWIRE/PLUS compatible peripheral built in. National's COP8SGx line of microcontrollers are used to demonstrate the construction of a portable downloader.

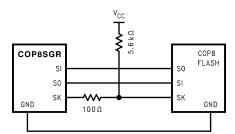

National's COP8SGx microcontrollers are easily interfaced to the COP8 Flash Family microcontrollers. Communication is established via the built-in MICROWIRE/PLUS peripheral block. A 3 + GND wire setup is used. Code samples are provided and documented procedures are given. Figure 25 shows how to interface the COP8SGR to the COP8 Flash Family devices. The  $100\Omega$  resistor is used to protect both devices from bus contention. The 5.6 k $\Omega$  pull-up resistor is used by the firmware to detect an idle condition on the bus.

Figure 25. Interfacing the COP8SGR and COP8CBR Microcontrollers

### 4.1.1 COP8SGR Initialization Routine

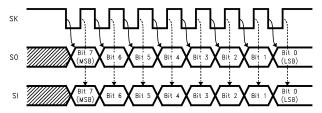

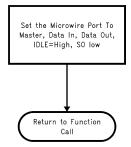

The COP8SGR microcontroller must initialize the internal communication block with the following parameters: CTRL.MSEL=1,PORTGD.SO=1,PORTGD.SK=1,PORTGC.SI=1, and PORTGC.SK=1.Table 18 andTable 19 contain information about the MICROWIRE/PLUS mode. Figure 7 shows the waveforms from the MICROWIRE/PLUS block. Figure 26 shows the flow for the initialization routine.

Table 18. Required Initialization of the MICROWIRE/PLUS

| Port G Config. Reg.<br>Bits G5-G4 | MICROWIRE/PLUS<br>Operation     | G4 Pin Function |          | G6 Pin Function |  |

|-----------------------------------|---------------------------------|-----------------|----------|-----------------|--|

| 1-1                               | Master, Data Out and<br>Data In | SO Output       | SK Input | SI Input        |  |

Example 3 Example 4 shows the sample assembly and C source for the routine.

Table 19. MICROWIRE/PLUS Mode Required for Communication

| Poi                    | t G         | SO Clocked Out On:  | SI Sampled On: | SK Idle Phase |  |

|------------------------|-------------|---------------------|----------------|---------------|--|

| G6 (SKSEL) Config. Bit | G5 Data Bit | 30 Clocked Out Oil. | Si Sampled On. |               |  |

| 1                      | 1           | SK Falling Edge     | SK Rising Edge | High          |  |

ISP DOWNLOADER www.ti.com

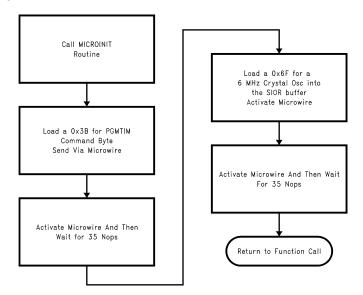

Figure 26. Flow Chart for the Initialization Routine

## Example 3. Required Initialization Routine—Assembly Version

```

; MICROWIRE/PLUS COP8SGR Initialization Routine

; Assume That The Wire Are Connected As In Figure 29

.INCLD cop8sgr.INC

; INCLUDE FILE FOR THE COP8SGR

.sect

code,rom,abs=0

; BEGINING CODE SPACE

; Main Routine

MAIN:

jsr MICROINIT

; CALL THE ROUTINE

MIAM qj

; RETURN TO MAIN

; INITIALIZATION CODE

MICROINIT:

sbit MSEL, CNTRL

; CNTRL.MSEL= 1, SET MICROWIRE INTO

sbit SK, PORTGC

; PORTGC.SK = 1, MODE, DATA OUT,

sbit SO, PORTGC

; PORTGC.SO = 1 ,DATA IN

; PORTGD.SO = 0 to let the firmware know that

rbit SO,PORTGD

; you want to go into ISP Mode

; Set MICROWIRE/PLUS into standard sk mode,

; IDLE = High, SET ACCORDING TO Table 20

sbit SK, PORTGD

; PORTGD.SK=1

sbit SI, PORTGC

; PORTGC.SI = 1

; RETURN FROM THE CALL

ret

.END MAIN

; END OF PROGRAM

```

## Example 4. Required Initialization Routine—C Version

```

#include 28sgr.h2;

// Include file for the COP8SGR Microcontroller

void microinit(void);

// The MICROWIRE/PLUS initialization routine

void main(){

// The main

microinit();

// Set up MICROWIRE/PLUS for CBR Xmission

// Endless loop

while(1);

// End of the main

void microinit(){

// MICROWIRE/PLUS Initialization Routine

CNTRL.MSEL=1;

// The MICROWIRE/PLUS Control Select Bit is set.

PORTGC.SK=1;

// Set the MICROWIRE/PLUS into PORTGC.SK=1

PORTGC.SO=1;

// MODE: DATA OUT, PORTGC.SO=1

PORTGD.SO=0;

// To tell the firmware that you want to go into

// ISP Mode

// Set MICROWIRE/PLUS into standard sk mode, IDLE=High, Set According

// to Table 2

PORTGD.SK=1;

// Set IDLE MODE=High

PORTGC.SI=1;

// Set the configuration bit

// End of microinit routine

```

www.ti.com ISP DOWNLOADER

#### 4.1.2 The PGMTIM SET Routine

Sets the flash write timing register to match that of the CKI frequency. See Table 11.5 for values. Example 5 shows the flow of the PGMTIM\_SET routine. Example 5 Example 6 shows the assembly and C version of the routine.

Figure 27. Flow for the PGMTIM\_SET Program

## Example 5. Code Sample For PGMTIM\_SET. Assembly Version: COP8SGR

```

; MICROWIRE/PLUS COP8SGR Write PGMTIME routine

; Assume That The Wire Are Connected As In Figure 29

.INCLD cop8sgr.INC

; INCLUDE FILE FOR THE COP8SGR

.sect data,reg,abs=0xF0

; FOR RAM STORAGE AREA

DELAY_NUM: .DSB 1

;STORAGE FOR THE NUMBER OF DELAYS

;BEGINING CODE SPACE

.sect code,rom,abs=0

MAIN:

jsr MICROINIT

; CALL THE MICROWIRE INITIALIZATION ROUTINE

jsr PGMTIM_SET

; CALL THE SET PROGRAMMING TIMING

; RETURN TO THE MAIN LOOP

jp MAIN

PGMTIM_SET: ;THE SET WRITE TIMING ROUTINE

ld SIOR, #03B

; PGMTIM_SET COMMAND Byte

; Send the command byte out

jsr MICROWIRE_SEND

ld A,#023

;The amount of delay cycles required, For more info

;see Table 18 regarding required time delay cycles

jsr DELAY

;The delay routine

ld SIOR,# 06F

;Send the Write Time - Assume a 10MHz CKI CBR CKI

;frequency, See Table 2-13 for additional information

jsr MICROWIRE_SEND

; Send the value out to the COP8CBR

;end of the PGMTIM_SET routine

ret.

MICROWIRE_SEND:

;The MICROWIRE/PLUS send routine

sbit BUSY, PSW

;SET THE PSW.BUSY BIT TO TURN ON

ld B, #PSW

;while (PSW.BUSY)

wait_uwire:

;THE MICROWIRE WAIT ROUTINE

ifbit 02,[B]

; IF THE BIT IS ON THEN WAIT

jp wait_uwire

;Otherwise stay in the loop

; RETURN FROM THE FUNCTION CALL

ret

MICROINIT:

sbit MSEL, CNTRL

;CNTRL.MSEL= 1, SET MICROWIRE INTO

sbit SK, PORTGC

; PORTGC.SK = 1, MODE, DATA OUT,

sbit SO, PORTGC

; PORTGC.SO = 1, DATA IN

rbit SO, PORTGD

; PORTGD.SO = 0 to let the firmware know that

; you want to go into ISP Mode

```

ISP DOWNLOADER www.ti.com

## Example 5. Code Sample For PGMTIM\_SET. Assembly Version: COP8SGR (continued)

```

; Set MICROWIRE/PLUS into standard sk mode, sk high during idle

; IDLE = High, SET ACCORDING TO Table 20

sbit SK, PORTGD

; PORTGD.SK=1

sbit SI, PORTGC

; PORTGC.SI=1

RETURN FROM THE CALL

ret

DELAY:

;THE DELAY ROUTINE

; ASSUME THE AMOUNT OF NOPS IS STORED IN

; THE ACCUMULATOR A

LD DELAY_NUM, #023

;Corresponds to 35 cycles

; POINT WHERE THE LOOP ACTUALLY OCCURS

LOOP_POINT:

;THE ACTUAL NOPS

drsz DELAY_NUM

; DECREMENT DELAY_NUM, SKIP NEXT INSTR. IF

jp LOOP_POINT

; ZERO

; RETURN FROM TO THE FUNCTION CALL

ret

.END MAIN

; END OF PROGRAM

```

## Example 6. The PGMTIM\_Set Routine—C Version

```

#include "8sgr.h";

// Include file for the COP8SGR Microcontroller

void pgmtim_set(void);

// The pgmtim_set routine

void delay(unsigned int delay_num);

// The actual num of delays

void microwire_send(void);

void microinit(void);

// The main

void main(){

microinit();

// Initialize the MICROWIRE/PLUS port

// For a 10 MHZ CKI Frequency

pgmtim_set(0x7B);

delay(6);

// Just in case of cascading

while(1);

// Endless loop

void pgmtim_set(unsigned int frequency){    // The PGMTIM_SET

SIOR=0x3B;

// Routine, Send out the PGMTIM_SET command byte

microwire_send();

// Start up the MICROWIRE/PLUS and send the byte

// Wait for 35 NOPs as required in the time delay

delay(35);

req.

// Now send out the frequency

SIOR=frequency;

// Start out the MICROWIRE/PLUS

microwire_send();

// End of the routine

// The routine that starts the microwire

void microwire_send(void){

CNTRL.MSEL=1;

// Set the MICROWIRE/PLUS Control Bit

PSW.BUSY=1;

// Set the PSW busy bit

while(PSW.BUSY);

// Wait until the bit has cleared

// end of the routine

void delay(unsigned int delay_num){

// The delay routine

unsigned int i;

// temp variable

for (i=0;i<delay_num; i++)</pre>

// The loop control

NOP;

// Wait on NOP

// End of the delay routine

void microinit(){

// MICROWIRE/PLUS Initialization Routine

CNTRL.MSEL=1;

// The MICROWIRE/PLUS Control Select Bit is set.

PORTGC.SK=1;

// Set the MICROWIRE/PLUS into PORTGC.SK=1

PORTGC.SO=1;

// MODE: DATA OUT, PORTGC.SO=1

// To tell the firmware that you want to go

PORTGD. SO=0;

// into ISP Mode

// Set MICROWIRE/PLUS into standard sk mode,

IDLE=High,

// Set According to Table 2

PORTGD.SK=1;

// Set IDLE MODE=High

PORTGC.SI=1;

// Set the configuration bit

// End of microinit routine

```

www.ti.com ISP DOWNLOADER

## 4.1.3 PAGE\_ERASE—Erase a Page of Flash Memory

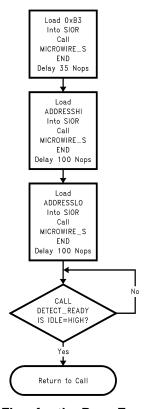

Figure 28 shows the flow for the PAGE\_ERASE routine. Example 7 and Example 8 shows the assembly and C code versions for the routines.

Figure 28. Flow for the Page Erase Function