# Artisan Technology Group is your source for quality new and certified-used/pre-owned equipment

#### FAST SHIPPING AND DELIVERY

- TENS OF THOUSANDS OF IN-STOCK ITEMS

- EQUIPMENT DEMOS

- HUNDREDS OF MANUFACTURERS SUPPORTED

- LEASING/MONTHLY RENTALS

- ITAR CERTIFIED

SECURE ASSET SOLUTIONS

#### SERVICE CENTER REPAIRS

Experienced engineers and technicians on staff at our full-service, in-house repair center

#### WE BUY USED EQUIPMENT

Sell your excess, underutilized, and idle used equipment We also offer credit for buy-backs and trade-ins **www.artisantg.com/WeBuyEquipment** *>*

# Instra View REMOTE INSPECTION

Remotely inspect equipment before purchasing with our interactive website at **www.instraview.com** *>*

#### LOOKING FOR MORE INFORMATION?

Visit us on the web at <u>www.artisantg.com</u> for more information on price quotations, drivers, technical specifications, manuals, and documentation

# DBS 8750

High-Precision Arbitrary Waveform Synthesizer

The World Resource for Precision Signal Technology

-----

i.....

# **Proprietary Statement**

The information contained in this publication is derived in part from proprietary and patent data of the Analogic Corporation. This information has been prepared for the express purpose of assisting operating and maintenance personnel in the efficient use of the instrument described herein. Publication of this information does not convey any rights to reproduce it or to use it for any purpose other than in connection with the installation, operation, and maintenance of the equipment described herein.

P/N 82-5106 Revision 2

Ħ

Copyright © Analogic Corporation 1995. All rights reserved. Printed in U.S.A.

DBS 8701, DBS 8710, and DBS 8750 are trademarks of Analogic Corporation.

# Warranty

Analogic warrants only to the original purchaser that this product, as purchased from Analogic or an Analogic distributor or dealer, will conform to the written specifications for a period of one year from the date of purchase. If the product fails to conform to these warranties, Analogic, as its sole and exclusive liability hereunder, will repair or replace the product and/or its components within a reasonable period of time if the product is returned to a Tektronix service center within the warranty period. These warranties are made upon the express condition that:

- a. The purchaser promptly notify Tektronix in writing of any non-conformity with the above warranty including a detailed explanation of the alleged deficiencies.

- b. The product is returned to a Tektronix service center at the buyer's expense after making suitable arrangements for performance of service.

- c. When the product is returned for repair, a copy of the original bill of sale or invoice is sent with the product .

- d. Analogic will not be liable for any incidental or consequential damages.

-

- e. In the opinion of Analogic upon inspection, the product has not been misused, altered, or damaged due to abnormal handling and/or operation.

- f. Repairs to the product and/or its components have not been made by anyone other than Analogic or one of its authorized repair agents.

- g. The product has not been modified, altered, or changed in any manner by anyone other than Analogic or one of its authorized repair agents.

THIS WARRANTY EXCLUDES ALL OTHER WARRANTIES, WHETHER EXPRESSED OR IMPLIED, ORAL OR WRITTEN, INCLUDING WITHOUT LIMITATION WARRANTIES OF MERCHANTABILITY AND/OR FITNESS FOR A PARTICULAR PURPOSE.

No term, condition, understanding or agreement purporting to modify the terms of this warranty shall have any legal effect unless made in writing and signed by an authorized officer of Analogic and the purchaser.

iv

# Contents

| 1 | Inti | roduction                          |     |

|---|------|------------------------------------|-----|

|   | 1.1  | PRODUCT DESCRIPTION                | 1-1 |

|   |      | 1.1.1 Functional Overview          | 1-1 |

|   |      | 1.1.2 Accessories                  | 1-3 |

|   | 1.2  | TECHNICAL SUPPORT                  | 1-3 |

| 2 | Pre  | eparation & Installation           |     |

|   | 2.1  | OVERVIEW                           | 2-1 |

|   | 2.2  | HARDWARE JUMPERS                   | 2-1 |

|   |      | 2.2.1 Selecting the Base Address   | 2-3 |

|   |      | 2.2.2 Selecting the Address Space  | 2-3 |

|   |      | 2.2.3 Selecting TTL Trigger Lines  | 2-4 |

|   |      | 2.2.4 Deglitching Filter Selection | 2-5 |

|   | 2.3  | INSTALLATION                       | 2-5 |

|   |      | 2.3.1 Input/Output Connections     | 2-5 |

|   |      | 2.3.2 Analog Outputs               | 2-5 |

|   | 2.4  | START-UP AND VERIFICATION          | 2-6 |

|   |      | 2.4.1 Power-Up Status              | 2-6 |

|   |      | 2.4.2 Initial Checkout             | 2-7 |

| 3 | Ор   | eration                            |     |

|   | 3.1  | OVERVIEW                           | 3-1 |

|   | 3.2  | CONTROLS AND INDICATORS            | 3-1 |

|   | 3.3  | GENERATING STANDARD WAVEFORMS      | 3-3 |

|   |      | 3.3.1 Selecting the Waveshape      | 3-4 |

|   |      | 3.3.2 Selecting the Frequency      | 3-4 |

|   |      | 3.3.3 Selecting the Amplitude      | 3-4 |

|   |      | 3.3.4 Selecting the DC Offset      | 3-4 |

|   |      | 3.3.5 Selecting the Drive Mode     | 3-5 |

|   |      | 3.3.6 Selecting Attenuation        | 3-6 |

|   |      | 3.3.7 Selecting the Filter         | 3-6 |

The second second

v

|     | 3.3.8  | Using T  | rack-and-Hold                         | 3-7          |

|-----|--------|----------|---------------------------------------|--------------|

|     |        |          | Tracking Mode                         | 3-7          |

|     |        |          | Track-and-Hold Synchronization        | 3-8          |

|     |        | 3.3.8.3  | Controlling Track-and-Hold with       |              |

|     |        | •••••    | a Front Panel CLOCK                   | 3-8          |

|     |        |          | e Deglitching Filter                  | 3-9          |

|     | 3.3.10 | Switchir | ng the Output Channel State to On/Off | 3-10         |

|     | 3.3.11 | Selectin | g the GATE Delay                      | 3-10         |

|     | 3.3.12 | Synchro  | onizing the Output Channels           | 3-11         |

|     |        | -        | ne TTL Trigger Lines                  | 3-11         |

|     | 3.3.14 | Genera   | ting Clean SquareStaircase Waves      | 3-12         |

| 3.4 | GENE   | RATING   | ARBITRARY WAVEFORMS                   | 3-14         |

|     | 3.4.1  | SOURc    | e:FUNCtion USER Waveforms             | 3-14         |

|     | 3.4.2  | SOURc    | e:FUNCtion MEMory Waveforms           | 3-17         |

| 3.5 | DSP/   | JSER M   | EMORY                                 | 3-17         |

|     | 3.5.1  | Creating | g Memory Buffers                      | 3-17         |

|     | 3.5.2  | Saving   | Waveforms                             | 3-18         |

|     | 3.5.3  | Read/M   | /rite VXI Memory                      | 3-20         |

|     | 3.5.4  | Acquirir | ng LOCALbus Data                      | 3-20         |

|     | 3.5.5  | Allocati | ng Memory                             | 3-21         |

|     | 3.5.6  | Memory   | y Status                              | 3-22         |

|     | 3.5.7  | Deleting | g Buffers                             | 3-23         |

| 3.6 | TRIG   | GERING   | i                                     | 3-23         |

|     | 3.6.1  | Internal | Trigger                               | 3-23         |

|     | 3.6.2  | Externa  | ll Trigger                            | 3-23         |

|     | 3.6.3  | Trigger  | Sequences                             | 3-24         |

|     |        |          | Programming Guidelines                | 3-24         |

|     |        | 3.6.3.2  | Example #1: Complex Wave Burst -      |              |

|     |        |          | Internal Trigger                      | 3-26         |

|     |        | 3.6.3.3  | Example #2: Sine Wave Burst -         | 0.07         |

|     |        |          | External Trigger                      | 3-27<br>3-28 |

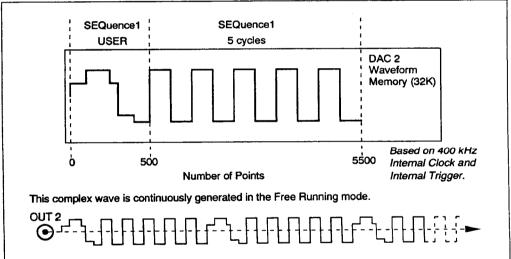

|     |        |          | Example #3: Free Running Complex Wave | 3-28         |

| 3.7 |        |          | RCES                                  | 3-29         |

| 3.8 |        |          | TESTS                                 | 3-30         |

|     | 3.8.1  |          | M Checksum Test                       | 3-30         |

|     | 3.8.2  | SRAM     | Test                                  | 3-30         |

head to be

|     |     | 3.8.3 DAC Output Test 3-3                  | 30 |

|-----|-----|--------------------------------------------|----|

|     |     | 3.8.4 DAC Waveform Memory Test 3-3         | 31 |

|     |     | 3.8.5 Register Test 3-3                    | 31 |

|     |     | 3.8.6 Running All Diagnostic Tests 3-3     | 31 |

| 4   | DB  | S 8750 Command Reference                   |    |

|     | 4.1 | INTRODUCTION 4-                            | 1  |

|     | 4.2 | COMMAND SYNTAX 4-                          | 1  |

|     |     | 4.2.1 Abbreviated Commands 4-              | 1  |

|     |     | 4.2.2 Command Concatenation 4-             | 1  |

|     |     | 4.2.3 Command Parameters 4-3               | 3  |

|     |     | 4.2.4 Optional Keywords and Parameters 4-3 | 3  |

|     |     | 4.2.5 Output Channel Selection 4-3         | 3  |

|     |     | 4.2.6 Query Commands 4-3                   | 3  |

|     | 4.4 | DBS 8750 COMMAND INDEX 4-                  | 4  |

| Арр | end | lix A Specifications                       |    |

| Apr | end | lix B VXI Connections                      |    |

Appendix C Error Messages

.....

Appendix D Revision 0 Hardware

# **Tables**

| 2-1 | Hardware Jumper Setup Summary         | 2-1  |

|-----|---------------------------------------|------|

| 2-2 | Logical Address Setup Examples        | 2-3  |

| 2-3 | Address Mode Selections               | 2-3  |

| 2-4 | TTL Trigger Line Output Selections    | 2-4  |

| 2-5 | Deglitching Filter Jumper Selections  | 2-5  |

| 2-6 | OUT 1 & 2 Default Power-On State      | 2-6  |

| 3-1 | Mathematical Mnemonics and Symbols    | 3-13 |

| 3-2 | Trigger Sequence Control Commands     | 3-24 |

| 4-1 | CALC:MATH Command Mnemonics & Symbols | 4-7  |

# Figures

-----

.....

\_\_\_\_

| 1-1  | Waveform Synthesizer Block Diagram                  | 1-1  |

|------|-----------------------------------------------------|------|

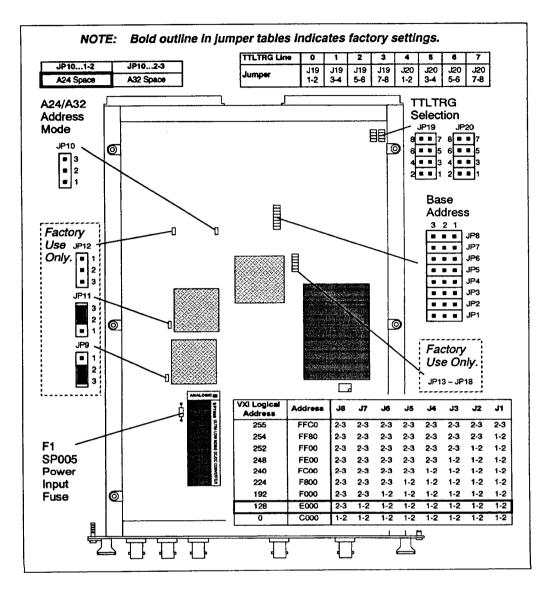

| 2-1  | DBS 8750 Jumper Selection Locations                 | 2-2  |

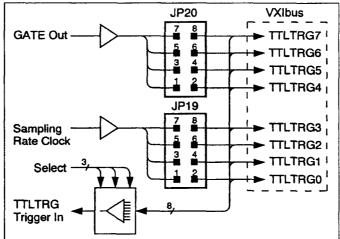

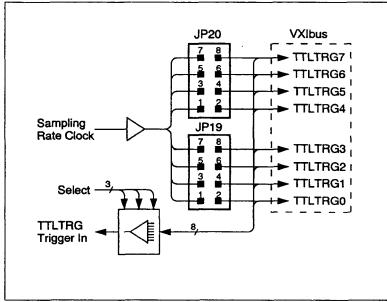

| 2-2  | TTLTRG Interface                                    | 2-4  |

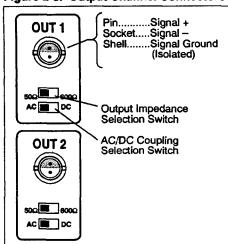

| 2-3  | Output Channel Connectors 1 & 2                     | 2-6  |

| 3-1  | DBS 8750 Command Set Quick Reference                | 3-2  |

| 3-2  | DBS 8750 Front Panel                                | 3-3  |

| 3-3  | Simplified Output Stage Schematic                   | 3-5  |

| 3-4  | Output Voltage Characteristics                      | 3-6  |

| 3-5  | Output vs. Tracking Mode                            | 3-7  |

| 3-6  | Synchronizing the Track/Hold                        | 3-8  |

| 3-7  | Track/Hold Control for Sine Function                | 3-9  |

| 3-8  | TRIG-GATE Timing                                    | 3-10 |

| 3-9  | TTLTRG I/O Functions                                | 3-11 |

| 3-10 | Square Wave Generation with Internal/External Clock | 3-13 |

| 3-11 | Complex Waveform By Segments                        | 3-15 |

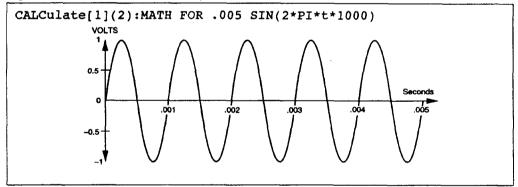

| 3-12 | 1-kHz Sine Wave Output                              | 3-15 |

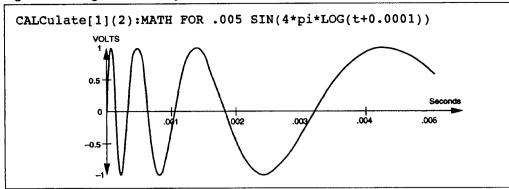

| 3-13 | Log Function Output                                 | 3-16 |

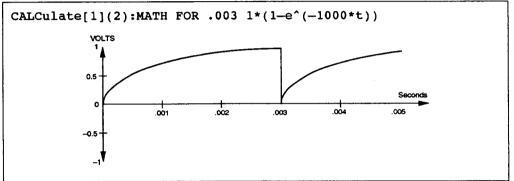

| 3-14 | Exponential Output Waveform                         | 3-16 |

| 3-15 | Rectification Using Absolute Function               | 3-16 |

| 3-16 | DSP/User Memory Example                             | 3-19 |

| 3-17 | LOCALbus Timing Diagram                             | 3-20 |

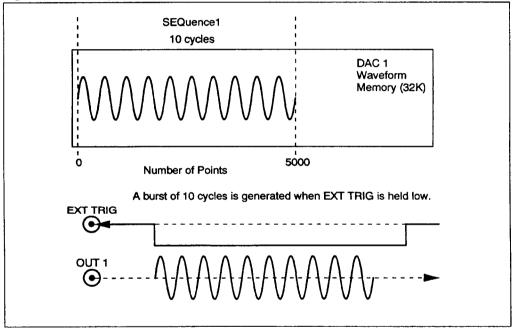

| 3-18 | Example #1 Output Wave                              | 3-26 |

| 3-19 | Example #2 Output Wave                              | 3-27 |

| 3-20 | Example #3 Output Wave                              | 3-28 |

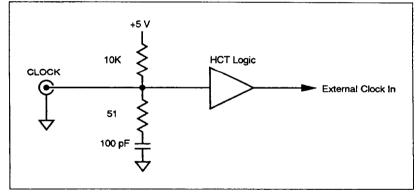

| 3-21 | Front Panel CLOCK Input Circuit                     | 3-29 |

| 4-1  | DBS 8750 Command Tree                               | 4-3  |

| 4-2  | Comcatenating Commands                              | 4-3  |

| B-1  | Connector P1                                        | B-2  |

| B-2  | Connector P2                                        | B-2  |

viii

# Section 1 Introduction

# 1.1 **PRODUCT DESCRIPTION**

The DBS 8750 is a 400 kHz, 16-bit precision, VXI Message-Based Arbitrary Waveform Synthesizer. Using its command set, the DBS 8750 can generate highly-accurate standard and arbitrary waveforms on either of its two differential or single-ended output channels. Combining the superior performance of a dual digital-to-analog converter (DAC) with the speed and processing capability of a digital signal processor (DSP), the DBS 8750 provides precision analog output signals.

# 1.1.1 Functional Overview

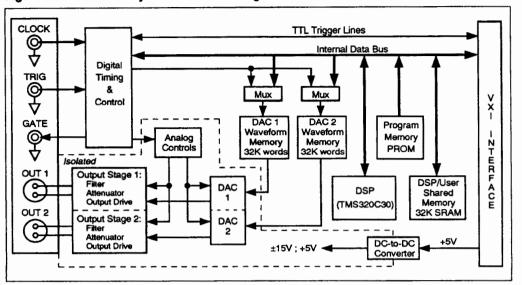

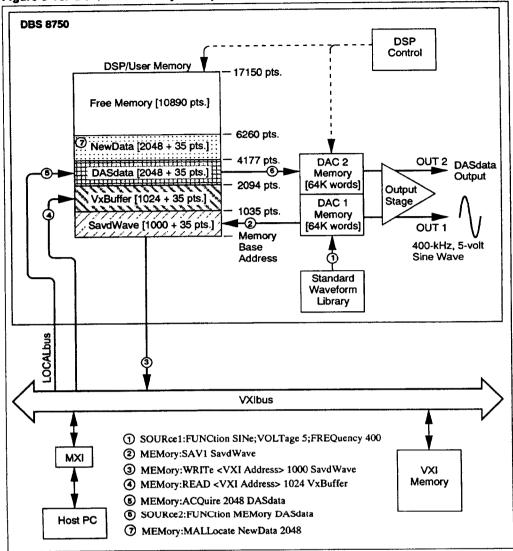

The DBS 8750 (Figure 1-1) generates waveforms using the data placed in the DAC 1 or 2 Waveform Memory (32K words maximum per channel). The DAC Sampling Rate is controlled by either the 400-kHz Internal Sampling Rate Clock or an External Sampling Rate Clock received from the Front Panel CLOCK input or one of the TTL Trigger lines via the VXIbus. The waveform data can be obtained from any of the following sources:

- (1) Standard Waveform Library Sine, Square, Triangle, Noise and DC functions.

- (2) User-Defined Waveform Function Complex waveforms calculated by the DSP according to a prescribed formula and user-specified parameters. Maximum waveform size is 32K points.

- (3) DSP/User Memory. The shared DSP/User memory has 17150 words of user-accessible read/write space for saving waveforms and acquiring waveform data from the VXI system.

All control functions, complex waveform calculations and digital signal processing are implemented by the DSP. The DSP serves as an intelligent DMA controller for transferring digital data between the VXIbus and the DSP/User Memory. The DSP also acts as a counter/timing sequencer for cross-synchronization with other VXI instruments.

#### Figure 1-1. Waveform Synthesizer Block Diagram

On the front panel, an External Trigger input, an External Clock input and a Gate output provide synchronization controls. To cross-synchronize its operation with another VXI instrument, such as a DBS 8700 Digitizer, the DBS 8750 uses the VXIbus TTL Trigger lines to provide a Sampling Rate Clock and/or GATE output, or to receive an External Sampling Rate Clock.

#### NOTE: The DAC Waveform Memories are not accessible from the VXIbus. The shared DSP/User Memory has 17150 words of user-acccessible read/write space for data transfers to/from VXI memory or from the LOCALbus via connector P2.

After data has been loaded or processed, the DSP writes the final values into the DAC 1 or 2 Waveform Memory. In the write mode the memory is addressed by the DSP, while in the read mode the memory is addressed by a set of address counters. In turn, each DAC memory has its own independent address counter which allows independent waveform generation at each of the two outputs. While operating from pre-loaded commands and after the address counter has reached its last address, the channel loops back and continues to output the same waveform until a new command is entered at which time generation of a new waveform begins. The analog output section is isolated from the digital section of the card by a 500-volt dc barrier. High-speed pulse transformers couple the data and control signals across the barrier. As each waveform memory outputs 16-bit parallel data words, a parallel-to-serial shift register feeds a serial bit stream over the barrier, while on the floating side, a serial-to-parallel shift register reverses the process. To maintain proper DAC synchronization, the 16-MHz master clock as well as the track-and-hold and load control signals are passed across the barrier using separate transformers.

Under precision timing control, digital data from each DAC memory is converted to analog signals by a highly-accurate 18-bit dual DAC. Each DAC converts data at the sampling rate and provides its own stable reference and two distortion-suppressing output deglitcher amplifiers.

Each DAC output is fed into a 6-pole reconstruction low-pass filter which can be switched into the analog path to eliminate higher frequencies when harmonically clean signals are required. A programmable attenuator feeds the filtered signal to the output amplifier. The output amplifier can be configured for either a single-ended or differential output, with AC or DC coupling, and with 50 or 600 ohms of output impedance. When finer attenuation steps are required, sending the appropriate commands to the DSP produces digitally scaled data within the full 16-bit resolution of the DACs.

A very low noise DC-to-DC converter designed to accommodate the stringent demands of a highly-accurate 16-bit waveform synthesizer provides power to the isolated analog section. Powered by +5 volts from connectors P1 and P2, the DC-to-DC converter provides regulated and filtered +15, -15 and +5 volts for the entire analog output circuitry.

### 1.1.2 Accessories

DVX05-3 3-foot cable/connector assembly

DVX05-5 5-foot cable/connector assembly

These assemblies consist of a TWBNC connector attached to either a 3-foot or 5-foot length of twisted shielded-pair cable. The other end of the cable has two cable conductors and a shield available for direct connection to the user's hardware application.

# 1.2 TECHNICAL SUPPORT

For service, contact your nearest Tektronix Service Center.

For technical support, call 1-800-835-4894 for technical support in the U.S., or contact your nearest Tektronix Office outside the U.S.

# Section 2 Preparation & Installation

# 2.1 OVERVIEW

This section provides instructions for setting up hardware jumpers and installing the instrument in a VXI chassis. After unpacking, carefully inspect the hardware for any damage that may have occurred during shipment. If necessary, contact the carrier to file a claim. Save the shipping carton and packing materials if for any reason you need to return the product for repair or replacement. For technical support or to return this product to the factory, refer to Section 1.2 for instructions.

This product contains components which are sensitive to electrostatic discharge (ESD). Be sure to follow proper procedures for handling, storing and transporting ESDsensitive assemblies.

# 2.2 HARDWARE JUMPERS

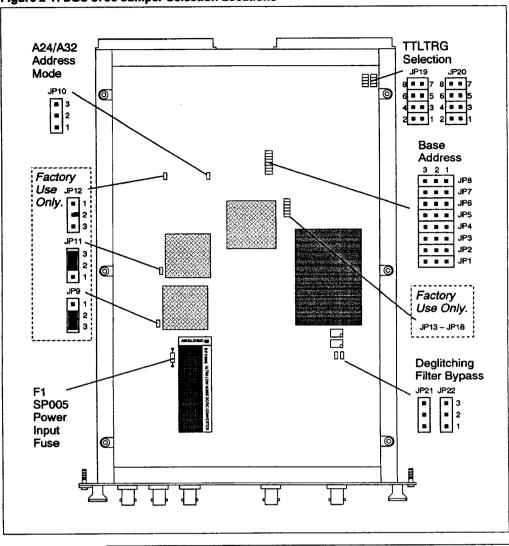

Before installing this instrument in a chassis, check Table 2-1 which lists jumper selections made at the factory before shipment To change any factory selection, refer to Figure 2-1 and the referenced Section.

| Function                   | Sect  | Factory<br>Selection | Jumpers                                                                                                                                      |

|----------------------------|-------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| VXI Logical Address        | 2.2.1 | 132                  | JP1-1 to JP1-2<br>JP2-1 to JP2-2<br>JP3-2 to JP3-3<br>JP4-1 to JP4-2<br>JP5-1 to JP5-2<br>JP6-1 to JP6-2<br>JP7-1 to JP7-2<br>JP8-2 to JP8-3 |

| Address Space              | 2.2.2 | A24                  | JP10-1 to JP10-2                                                                                                                             |

| Sampling Rate Clock Output | 2.2.3 | TTLTRG0              | JP19-1 to JP19-2                                                                                                                             |

| Deglitching Filter         | 2.2.4 | In Line              | JP21-2 to JP21-3<br>JP22-2 to JP22-3                                                                                                         |

| Factory Setup Only         | N/A   | N/A                  | JP9-2 to JP9-3<br>JP11-2 to JP11-3                                                                                                           |

Table 2-1. Hardware Jumper Factory Setup Summary\*

For hardware revision 1 and up only. See Appendix D for revision 0 hardware jumpers.

For hardware revision 1 and up only. See Appendix D for revision 0 hardware jumpers.

# 2.2.1 Selecting the Base Address

The Base address of a VXI instrument is determined by the following:

Base Address = (Logical Address x 64) + 49152

The Logical Address of this instrument can be set from 0 to 255d using jumpers JP1 through JP8. However, Logical Address 0 and 1 cannot be used as these addresses are used by various VXI embedded controllers. Table 2-2 list some examples.

# NOTE: Do not use Logical Address 0 or 1. These are reserved for system controllers.

|                    |             | VXibus      | Addres      | s Lines     | & Jun      | nper Se    | lections   |            |

|--------------------|-------------|-------------|-------------|-------------|------------|------------|------------|------------|

| Logical<br>Address | VA13<br>JP8 | VA12<br>JP7 | VA11<br>JP6 | VA10<br>JP5 | VA9<br>JP4 | VA8<br>JP3 | VA7<br>JP2 | VA6<br>JP1 |

| 255                | 2-3         | 2-3         | 2-3         | 2-3         | 2-3        | 2-3        | 2-3        | 2-3        |

| 254                | 2-3         | 2-3         | 2-3         | 2-3         | 2-3        | 2-3        | 2-3        | 1-2        |

| 252                | 2-3         | 2-3         | 2-3         | 2-3         | 2-3        | 2-3        | 1-2        | 1-2        |

| 248                | 2-3         | 2-3         | 2-3         | 2-3         | 2-3        | 1-2        | 1-2        | 1-2        |

| 240                | 2-3         | 2-3         | 2-3         | 2-3         | 1-2        | 1-2        | 1-2        | 1-2        |

| 224                | 2-3         | 2-3         | 2-3         | 1-2         | 1-2        | 1-2        | 1-2        | 1-2        |

| 192                | 2-3         | 2-3         | 1-2         | 1-2         | 1-2        | 1-2        | 1-2        | 1-2        |

| 132                | 2-3         | 1-2         | 1-2         | 1-2         | 1-2        | 2-3        | 1-2        | 1-2        |

| 2                  | 1-2         | 1-2         | 1-2         | 1-2         | 1-2        | 1-2        | 2-3        | 1-2        |

#### 2.2.2

### Selecting the Address Space

The setting of hardware jumper JP10 enables the instrument to operate in either the A24 or A32 addressing mode. Refer to Table 2-3.

| A24 Space        | A32 Space        |

|------------------|------------------|

| JP10-1 to JP10-2 | JP10-2 to JP10-3 |

# 2.2.3 Selecting TTL Trigger Lines

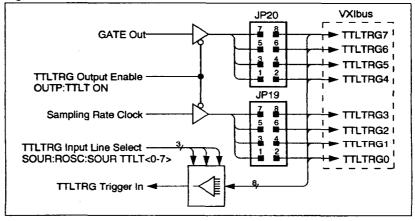

The TTL trigger lines can be used for additional triggering and synchronization capabilities. As shown in Figure 2-2, the selected Sampling Rate Clock can be jumper-selected to drive TTLTRG line 0, 1, 2 or 3. The GATE output from the front panel can be jumper-selected to drive TTLTRG 4, 5, 6 or 7. Table 2-4 lists the available jumper selections. Before one of these signals can drive the bus, the TTLTRG line drivers must first be enabled by command OUTPut:TTLTrg ON | OFF.

Also, an External Sampling Rate Clock input can be received on any unused TTLTRG line. The input clock is software selected using the command, SOURce:ROSCillator:SOURce TTLTRG <0-7>.

### Figure 2-2. TTLTRG interface<sup>†</sup>

#### Table 2-4. TTL Trigger Line Output Selections\*

| Jumper                  | Setting | Connection                       |

|-------------------------|---------|----------------------------------|

| JP19                    | 1 to 2* | Sampling Rate Clock onto TTLTRG0 |

|                         | 3 to 4  | Sampling Rate Clock onto TTLTRG1 |

|                         | 5 to 6  | Sampling Rate Clock onto TTLTRG2 |

|                         | 7 to 8  | Sampling Rate Clock onto TTLTRG3 |

| JP20 1 to 2 GATE output |         | GATE output pulse onto TTLTRG4   |

|                         | 3 to 4  | GATE output pulse onto TTLTRG5   |

|                         | 5 to 6  | GATE output pulse onto TTLTRG6   |

|                         | 7 to 8  | GATE output pulse onto TTLTRG7   |

\* Factory Selection

<sup>†</sup> For hardware revision 1 and up only. See Appendix D for revision 0 hardware jumpers.

# 2.2.4 Deglitching Filter Selection\*

Each channel of the dual D/A Converter (DAC) is fed to a deglitching filter network where the filter can be connected in line with the DAC output or bypassed (Table 2-5). Bypassing the filter provides improved DC performance. For more information, refer to Section 3.3.9

Table 2-5. Deglitching Filter Jumper Selections

| Selection | Channel 1        | Channel 2        | Application                          |  |

|-----------|------------------|------------------|--------------------------------------|--|

| In Line   | JP21-2 to JP21-3 | JP22-2 to JP22-3 | Sine, Triangle                       |  |

| Bypassed  | JP21-1 to JP21-2 | JP22-1 to JP22-2 | Square, Pulse, Step<br>Functions, DC |  |

# 2.3 INSTALLATION

The 8750 can be installed in any slot except slot 0. Any module used in synchronous operation with the 8750 via the LOCALbus on connector P2 must be installed in the adjacent slot to the right of the 8750.

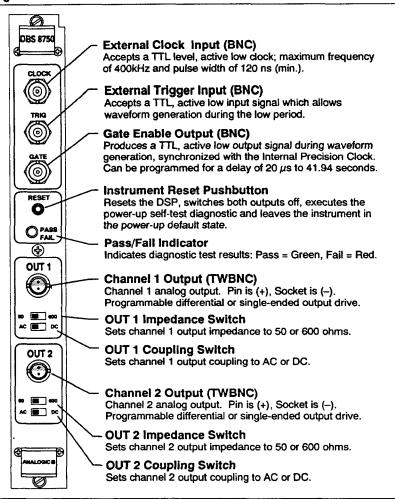

# 2.3.1 Input/Output Control Connections

The front panel controls and indicators are described in detail in Section 3. However, for installation purposes, the characteristics of the input/output connections are provided here.

- CLOCK External clock input (BNC,  $50\Omega$ ) accepts a TTL, negative-going pulse (120 ns, min.), maximum frequency of 400 kHz.

- TRIG External trigger input (BNC,  $50\Omega$ ) accepts a TTL, active-low signal to allow waveform generation.

- GATE Gate output (BNC) a TTL, active-low output during waveform generation, synchronized with the Internal Sampling Rate Clock.

# 2.3.2 Analog Outputs

The analog outputs OUT 1 and OUT 2 (Figure 2-2) are provided on TWBNC connectors. The outputs are switch selectable for 50 or 600 ohms output impedance and AC/DC coupling. The output stage is software selectable for a single-ended or differential configuration.

CAUTION: The output driver current should not exceed 40 mA, max.

For hardware revision 1 and up only.

Figure 2-3. Output Channel Connectors 1 & 2

# 2.4 START-UP AND VERIFICATION

# 2.4.1 Power-Up Status

At power-on, a self-test is executed. The Pass/Fail indicator is red during the test (4.8 seconds) and switches to green when the test passes (see \*TST? command in Section 4). Both output channels assume the default parameters listed in Table 2-6 following the self-test.

| Function               | State        |

|------------------------|--------------|

| Output Filters         | Bypassed     |

| Attenuation            | 0.00 dB      |

| Output Drive           | Differential |

| On/Off State           | OFF          |

| Waveshape              | DC           |

| Frequency              | 1000.00 Hz   |

| Voltage                | 0.00 V       |

| Offset Voltage         | 0.00 V       |

| Memory Buffers         | None defined |

| Oscillator Source      | Internal     |

| Trigger Source         | Internal     |

| Trigger Sequence Count | 0            |

| Trigger Loop Count     | 0            |

|                        |              |

Table 2-6. OUT 1 & 2 Default Power-On State

# 2.4.2 Initial Checkout

The following procedure describes tests that can be performed to verify that the instrument is in good operating condition.

# NOTE: For proper operation, the Data Low Register must be read following every command sent to this instrument except for the command, \*RST. Normal response is the new line character (x0A) or a status message.

|      | Action                                  | Response                                                                       |

|------|-----------------------------------------|--------------------------------------------------------------------------------|

| (1)  | Send *RST.                              | System reset.                                                                  |

| (2)  | Send *IDN?                              | Module identification query.                                                   |

| (3)  | Read Data Low Register                  | "Analogic, DBS8750, Rev n, Firmware<br>Revision"                               |

| (4)  | Send DIAG:ALL.                          | All diagnostics run. PASS/FAIL is red, switches to green after all tests pass. |

| (5)  | Read Data Low Register                  | x0A                                                                            |

| (6)  | Send DIAG?                              | Diagnostic status query.                                                       |

| (7)  | Read Data Low Register                  | "No errors, self test PASSED"                                                  |

| (8)  | Connect an oscilloscope probe to OUT1.  |                                                                                |

| (9)  | Send SOUR1:FUNC SIN.                    | Selects sine function.                                                         |

| (10) | Read Data Low Register.                 | x0A                                                                            |

| (11) | Send SOUR1:VOLT 5                       | Selects 5-volt amplitude.                                                      |

| (12) | Read Data Low Register.                 | x0A                                                                            |

| (13) | Send OUTP1:DRIV DIFF.                   | Selects differential output drive.                                             |

| (14) | Read Data Low Register.                 | x0A                                                                            |

| (15) | Send OUTP1:STAT 1.                      | 1-kHz, 5-volt sine wave on OUT 1.                                              |

| (16) | Read Data Low Register.                 | x0A                                                                            |

| (17) | Repeat steps (8) through (16) for OUT2. | 1-kHz, 5-volt sine wave on OUT 2.                                              |

| (18) | Send *RST.                              | System reset. Ready for operation.                                             |

2-8

.

......

# Section 3 Operation

# 3.1 OVERVIEW

This section describes how to operate the DBS 8750 using the DBS 8750 Command Set (Figure 3-1). This command set is used to control the generation of standard and arbitrary waveforms, data transfers to and from memory, triggering, clock selection and diagnostic tests. See Section 4, the DBS 8750 Command Reference, for more information.

NOTES: When programming this instrument it is necessary to read the Data Low Register after sending every command except Reset, \*RST. The normal response is the new line character (x0A) or a status message.

The DAC Waveform Memories are not accessible from the VXIbus. The shared DSP/User Memory has 17150 words of user-acccessible read/write space for data transfers to/from VXI memory or from the LOCALbus via connector P2.

If this instrument is to be controlled using a software driver, refer to the Software User's Manual received with the driver for software installation and operating instructions.

Error messages are generated for operational errors that are related to command entry, execution, triggering, data entry, or memory usage. See Appendix C for a list of possible error messages.

# 3.2 CONTROLS AND INDICATORS

Figure 3-2 describes the control inputs and indicators on the front panel. After making jumper selections and installing the instrument, all inputs and outputs are operated by software commands. Note that input coupling and input impedance are selected using front panel switches rather than using software commands.

| Figure 3-1. | DBS 8750 | ) Command | Set | Quick | Reference |

|-------------|----------|-----------|-----|-------|-----------|

|             |          |           |     |       |           |

| CALCulate Subsystem  | CALCulate<br>:MATH <segment 1=""> <segment 2=""> <segment 3=""> <segment 16=""></segment></segment></segment></segment>                                                                                                                                                                                                                                                                                                                                                 |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DiAGnostic Subsystem | DIAGnostic<br>:EPRom<br>:SRAM<br>:ANALog<br>:DRAM<br>:REGS<br>:ALL                                                                                                                                                                                                                                                                                                                                                                                                      |

| MEMory Subsystem     | MEMory<br>:WRITe <sp><vxi addr=""><sp><npts><sp>&gt;Buffer Name&gt;<br/>:READ<sp><vxi addr=""><sp><npts><sp>&gt;Buffer Name&gt;<br/>:SAV1(2)<sp>&gt;Buffer Name&gt;<br/>:ACQuire<sp><npts><sp>&gt;Buffer Name&gt;<br/>:CATalog[:ALL]?   BINary?<br/>:DELete<sp>&gt;Buffer Name&gt;   ALL<br/>:FREE[:ALL]?   BINary?<br/>:MALLocate<sp>&gt;Buffer Name&gt;<sp><npts></npts></sp></sp></sp></sp></npts></sp></sp></sp></npts></sp></vxi></sp></sp></npts></sp></vxi></sp> |

| OUTPut Subsystem     | OUTPut[1](2)<br>:ATTenuation <sp>&lt;0 to 90&gt;<br/>:FILTer<sp>ON   OFF<br/>:STATe<sp>ON   OFF<br/>:DRIVe<sp>SINGle-ended   DIFFerential<br/>:TRACk<sp>ON   OFF<br/>:GAT<br/>:DELay<sp>&lt;0.00002 to 41.945&gt;<br/>:SYNC<br/>TTLTrg<sp>ON   OFF</sp></sp></sp></sp></sp></sp></sp>                                                                                                                                                                                   |

| SOURce Subsystem     | :FREQuency <sp>&lt;12.5 to 20000&gt;<br/>:VOLTage<sp>&lt;-10 to +10&gt;<br/>:OFFSet<sp>&lt;-10 to +10&gt;<br/>:FUNCtion<sp>DC   SiNe   SQUare   TRiangle   NOISe   USER   MEMory<br/>:ROSCillator<br/>:SOURce<sp>INT   EXT   TTLTrg&lt;0-7&gt;<br/>:AUTO SHON   SHOF</sp></sp></sp></sp></sp>                                                                                                                                                                           |

| TRIGger Subsystem    | ::::::::::::::::::::::::::::::::::::::                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                      | INITiate[1](2)<br>ABORt[1](2)                                                                                                                                                                                                                                                                                                                                                                                                                                           |

\_

#### Figure 3-2. DBS 8750 Front Panel

3.3

# **GENERATING STANDARD WAVEFORMS**

The commands used to generate standard waveforms are found in the SOURce and OUTput subsystems of the DBS 8750 Command Tree. Although the commands that determine waveform characteristics may be written in any order, it is recommended that all characteristics be setup before changing the state of the output to ON.

# NOTE: The filter should be ON when generating waveforms. If it is OFF and the internal clock is used to generate square or triangle waves, the acurracy is limited due to spikes introduced from the Track and Hold control circuit (Section 3.3.8).

# 3.3.1 Selecting the Waveshape

Standard waveshapes are set up by sending the following command:

SOURce[1](2):FUNCtion DC | SINe | SQUare | TRIangle | NOISe

| DC       | DC output level |

|----------|-----------------|

| SINe     | Sine wave       |

| SQUare   | Square wave     |

| TRIangle | Triangle wave   |

| NOISe    | Random noise    |

|          |                 |

After all other parameters are set up (frequency, amplitude, DC offset, etc.), the selected output function appears at the output connector when the output channel is switched on by sending OUTPut[1](2):STATe ON.

# 3.3.2 Selecting the Frequency

The output signal frequency is set up by sending the following command (does not apply to DC and NOISe functions):

SOURce[1](2):FREQuency n,

where n = 12.5 to 20000 Hz for the Sine function, 12.5 to 30000 Hz for the Square and Triangle functions.

### 3.3.3 Selecting the Amplitude

The output amplitude is set up by sending the following command:

SOURce[1](2):VOLTage n,

where n = +10.000 to -10.000 volts for a single-ended output drive; +5.000 to -5.000 volts for a differential output drive.

The numeric value "n" represents peak voltage. To prevent clipping, amplitude plus offset should not exceed full scale.

### 3.3.4 Selecting the DC Offset

The dc output offset is set up by sending the following command: SOURce[1](2):VOLTage:OFFset n where n = -10.000 to + 10.000 volts

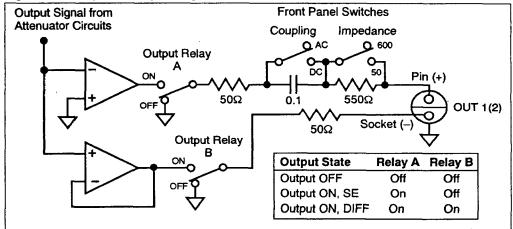

#### 3.3.5 Selecting the Drive Mode

Each channel can be configured for single-ended or differential output drive mode. Figure 3-3 shows a simplified schematic of the output stage. The output coupling and impedance switches are located on the front panel. As you can see, the output drive can be configured for a single-ended or differential output drive depending upon the state of the relay switches. To program the output drive, send the following command:

# OUTPut[1](2):DRIVe SINGle-ended | DIFFerential

SINGle-ended .... Single-ended output drive

DIFFerential ..... Differential output drive

### NOTE: The Single-Ended output drive has a range of 20 (±10) volts. The Differential output drive has a range of 10 (±5) volts. Maximum output current should not exceed 40 mA.

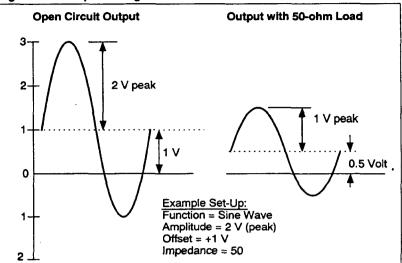

As shown in Figure 3-4, the actual programmed peak voltage amplitude and voltage offset value are produced at the output connector under open circuit conditions only. When a load is connected, the programmed voltage values are reduced. The amount of reduction depends upon the output impedance of the DBS 8750 and the input impedance of the load. As you can see, applying a load to the output creates a voltage divider with the series output resistance (50 or 600 ohms) of the instrument. The actual voltage level measured at the output depends upon the ratio of the input and output impedances.

#### Figure 3-3. Simplified Output Stage Schematic

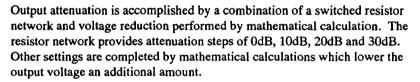

# 3.3.6 Selecting Attenuation

The output signal can be attenuated from 0 to 90dB by sending,

OUTPut[1](2):ATTenuation n, where n = 0 to 90

## 3.3.7 Selecting the Filter

An output reconstruction filter is available for low-distortion sine wave generation. The filter is connected in line or bypassed by sending the following command:

OUTPut[1](2):FILTer ON or 1 | OFF or 0

ON or 1 ..... to connect the filter

OFF or 0 ..... to bypass the filter

Normally, the filter should be switched ON. However, the instrument may be used with the filter switched OFF for certain step functions. Always switch the filter ON to generate low distortion SINe waves. See also Section 3.3.8 for use of Track-and-Hold with SINe waves.

# 3.3.8 Using Track-and-Hold

# 3.3.8.1 Tracking Mode

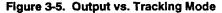

The Tracking Mode is selected by using the following command:

OUTput[1](2):TRACk ON or 1 | OFF or 0

ON or 1 ..... Track Only

OFF or 0 ..... Track and Hold

Figure 3-5 shows the affects of the Tracking Modes on the Digital-to-Analog (DAC) output signal. When generating sine waves, always switch to the Track-and-Hold Mode which reduces the code-dependent glitch energy on the DAC output. For DC levels, switch to the Track Only Mode to prevent Track/Hold switching noise on the DAC output. The Track Only Mode is also useful for reducing square wave settling times. However, glitch energy at major DAC code transitions will be higher.

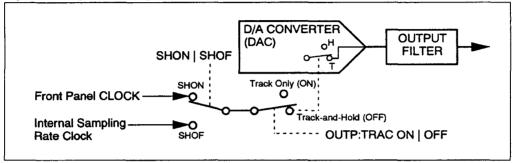

# 3.3.8.2 Track-and-Hold Synchronization

The Track-and-Hold Mode can be synchronized with either the 400-kHz Internal Sampling Rate Clock or an External Sampling Rate Clock via the front panel CLOCK input (Figure 3-6). To synchronize the Track-and-Hold, use the following command:

SOURce:ROSCillator:SOURce:AUTO SHON | SHOF

- SHON ... Synchronize Track-and-Hold with Front Panel CLOCK input.

- SHOF .... Synchronize Track-and-Hold with Internal Sampling Rate Clock (Default).

## Figure 3-6. Synchronizing the Track/Hold

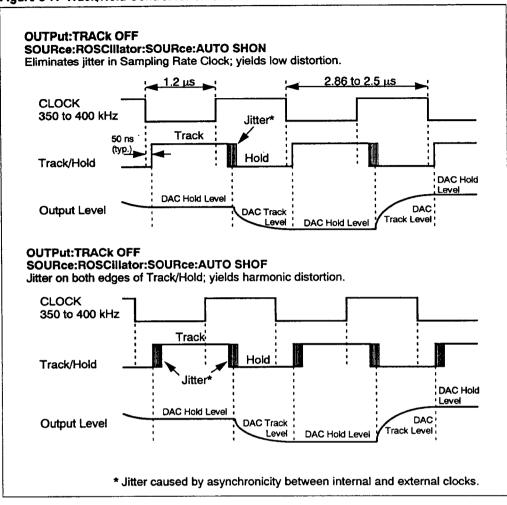

# 3.3.8.3 Controlling Track-and-Hold with a Front Panel CLOCK

An External Sampling Rate Clock connected to the Front Panel CLOCK input (not the TTLTRG lines) can be used to control the DAC Track-and-Hold Output Amplifiers (Figure 3-7). This feature is especially useful for generating low-distortion Sine waves. For this purpose, the CLOCK input should be a 350 to 400-kHz, negative-going pulse with a pulse width of 1.2us  $\pm$ 50ns, and less than 100 pS of jitter. Refer to Section 3.7 for information on selecting clock sources.

Figure 3-7 shows the affect of clock synchronization on the Track-and-Hold control. In the top half of the diagram, Track-and-Hold is synchronized with the External Sampling Rate Clock from the Front Panel. The bottom half shows synchronization with the Internal Sampling Rate Clock. This diagram clearly shows that low-distortion sine waves can be generated while Track-and-Hold is synchronized with an External Sampling Rate Clock because there is less jitter on the Track-and-Hold control signal.

# 3.3.9 Using the Deglitching Filter

By jumper selection, the output signal of each DAC may be passed through a deglitching filter (see Section 2.2.4) to reduce the affect of noise and glitch energy on the output. Bypassing the deglitching filter\* provides improved DC output performance and a reduction in square wave settling time.

\* For hardware revision 1 and up only.

#### 3.3.10 Switching the Output Channel State to On/Off

As shown previously in Figure 3-3, each of the two analog output channels can be connected or disconnected independently with a relay switch. These relays are switched on/off by sending the following command:

# OUTPut[1](2):STATe ON or 1 | OFF or 0

ON or 1 ..... Connects the output

OFF or 0 ..... Disconnects the output

The ON state closes a relay to connect the output amplifier to the front panel OUT 1(2) connector. The OFF state opens the relay and switches the connector output pin to ground through 50 or 600 ohms. During waveform calculations and initialization, you may wish to keep the outputs OFF, and only switch them ON after all other parameters have been specified.

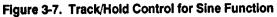

#### 3.3.11 Selecting the GATE Delay

The front panel GATE output produces a TTL, active-low output signal, synchronized with the Sampling Rate Clock, during waveform generation. The GATE output can be programmed for an output delay of 20  $\mu$ s to 41.945 seconds in 2.5- $\mu$ s increments (Figure 3-8). This output can be used as an external trigger or start signal for another VXI instrument such as a DBS 8700 Digitizer. By jumper selection (Section 2.2.3), this output can be made available on TTL trigger line 4, 5, 6, or 7 (Section 3.3.13)\*. To program the GATE delay, send the following command:

OUTput:GAT:DELay n, where n = 0.00002 to 41.945 secs in 2.5-µs steps

### Figure 3-8. TRIG-GATE Timing

For hardware revision 1 and up only. See Appendix D for revision 0 hardware jumpers.

#### 3.3.12 Synchronizing the Output Channels

The channel 1 and 2 output waveforms can be synchronized with each other, regardless of their current phase relationship, by sending the OUTPut:SYNC command (the [1](2) designation not required). This simultaneously resets the DAC memory address generator for both channels and starts generating the waveforms from their starting addresses. The waveforms stay synchronized providing they have a harmonic relationship from the start.

### 3.3.13 Using the TTL Trigger Lines

The TTL Trigger Lines can be used to synchronize 8750 operation with another instrument. Before using any particular line, a hardware jumper must be installed (Figure 3-9).

An External Sampling Rate Clock that is being driven onto the bus from another source can be received on any TTLTRG line. The input line is selected by the command SOURce:ROSCillator:SOURce TTLTRG<0-7>.

The 8750 can drive two signals onto the VXIbus: the Sampling Rate Clock and the GATE output pulse, the same signal generated from the GATE connector on the front panel. The Sampling Rate Clock can be driven onto TTLTRG 0, 1, 2 or 3. The GATE output pulse can be driven onto TTLTRG 4, 5, 6 or 7. Once the jumpers have been correctly installed, the TTLTRG signals are enabled by sending the OUTPut:TTLTrg ON command. Refer to Section 2.2.3 for jumper selection information.

#### Figure 3-9. TTLTRG I/O Functions\*

\* For hardware revision 1 and up only. See Appendix D for revision 0 hardware jumpers. 3-11

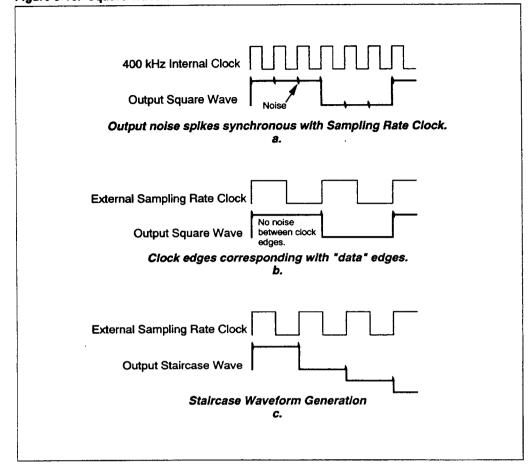

# 3.3.14 Generating Clean Square/Staircase Waves

When generating standard square waves using the 400-kHz Internal Sampling Rate Clock, clock-related noise is evident on the output wave whenever the data point values stay the same across multiple clock edges (Figure 3-10a). This happens because the internal Track-and-Hold circuit of the DAC is switched at every rising clock edge.

One solution to this problem is to switch the Track-and-Hold mode to "Track Only" but this creates a different set of problems. The recommended technique is to use an External Sampling Rate Clock and create the square wave so that each different data point value corresponds with a single rising clock edge (Figure 3-10b). The secret to this technique is to remember that the 8750 always calculates waveforms based on a 400 kHz sampling rate. If you want a square wave to change state on every rising clock edge, you must select a frequency of 200 kHz. This forces the 8750 to create a data pattern consisting of exactly two data points. Now, if a 20 kHz external clock is applied, for example, the output waveform is a 10-kHz square wave (half the external sampling rate) with clock-related noise spikes appearing only at the rising edges of the external clock.

This same technique applies to other DC-accurate applications such as for generating staircase (Figure 3-10c) or pulse waveforms.

Figure 3-10. Square Wave Generation with Internal/External Clock

# 3.4 GENERATING ARBITRARY WAVEFORMS

Arbitrary waveforms can be generated by either of the two commands SOURce[1](2):FUNCtion USER or SOURce[1](2):FUNCtion MEMory.

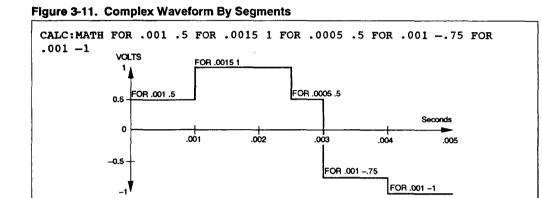

# 3.4.1 SOURce:FUNCtion USER Waveforms

The USER function generates waveforms which have been calculated by the CALCulate[1](2):MATH command. USER-defined waveforms may consist of up to 16 user-defined segments, but the total waveform length must be no more than 32K-words (Refer to Section 3.5 on memory and waveform size).

The format of the CALCulate[1](2):MATH command is as follows:

CALCulate[1](2):MATH<sp><segment 1><sp>......

where <segment n> = FOR<sp><duration><sp><voltage>,

a mathematical expression of the waveform segment where

FOR ..... Is a directive which begins the mathematical definition.

| <duration></duration> | . Specifies the period of time (in seconds) during which  |

|-----------------------|-----------------------------------------------------------|

|                       | the voltage function takes place. Do not use commas or    |

|                       | suffixes such as "m" (milli), "µ" (micro), "k" (kilo),or  |

|                       | "M" (Mega) - these are not recognized by the firmware.    |

| <voltage></voltage>   | Specifies the output voltage with respect to time. It can |

|                       | be expressed as a simple decimal value or a complex       |

be expressed as a simple decimal value or a complex mathematical expression using any of the mnemonics and symbols described in Table 3-1.

In general, when writing math expressions, use parentheses to group quantities properly and note that expressions are always evaluated from right to left. Do not exceed 16 FOR statements or 859 characters per command.

| Mnemonic<br>or Symbol | Function or<br>Meaning      | Mnemonic<br>or Symbol | Function or<br>Meaning       |

|-----------------------|-----------------------------|-----------------------|------------------------------|

| +                     | Positive value; addition    | cos                   | Cosine                       |

| -                     | Negative value; subtraction | TAN                   | Tangent                      |

| •                     | Multiply                    | ASIN                  | Arc sine                     |

| 1                     | Divide                      | ACOS                  | Arc cosine                   |

| •                     | Raised to the power         | ATAN                  | Arc tangent                  |

| ()                    | Parentheses                 | LN                    | Natural log (base e)         |

| e                     | 2.7182818                   | LOG                   | Common log (base 10)         |

| PI                    | 3.1415927                   | ABS                   | Absolute value               |

| SIN                   | Sine                        | t                     | Time variable (t=0 at start) |

# Table 3-1. Mathematical Mnemonics and Symbols

Following a power-on cycle or a system reset, the last USER function calculated is lost making the USER function undefined.

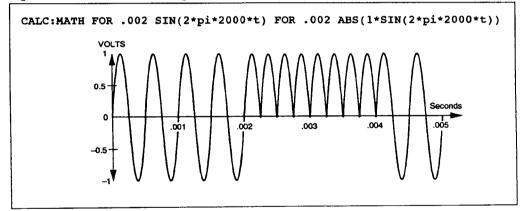

To generate a USER waveform, first define the waveform using the CALCulate[1](2):MATH command and then send the command, SOURce[1](2):FUNCtion USER which transfers the user-defined waveform into Waveform Memory. To change the USER function, send another CALCulate[1](2):MATH command to replace the previously calculated waveform. Example waveforms are shown in Figures 3-11 through 3-15. These examples were performed with a single-ended output, internal clock, no filter and no attenuation.

NOTE: Because of the methods used to calculate waveforms, the actual output may not appear exactly as illustrated.

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

#### 3.4.2 SOURce: FUNCtion MEMory Waveforms

A MEMory waveform is defined by the contents of a memory buffer which was previously created in the 8750 DSP/User Memory. A memory buffer is created whenever waveform data is transferred to the DSP/User Memory from VXI memory or an adjacent Digitizer module via the LOCALbus. To select a MEMory waveform, send

SOURce[1](2):FUNCtion MEMory <Buffer Name>

This transfers the data in <Buffer Name> from DSP/User Memory into DAC Waveform Memory from which the DAC generates the waveform.

If you wish to switch between several user-defined output waveforms, it is best to place them in individual memory buffers and then select the waveforms using the SOURce:FUNCtion MEMory command. This is faster than the USER function because each time you select USER, the DBS 8750 requires time to re-evaluate the CALC statement before placing the results in the DAC Waveform Memory. The DSP/User Memory provides useraccessible read/write space for 17,150 words (See Section 3.5.).

## 3.5 DSP/USER MEMORY

The DSP/User Memory has a total of 17,150 words of user space available for saving a waveform currently residing in DAC Waveform Memory, or for transferring data from VXI memory or an external source, such as an adjacent Digitizer module, via the LOCALbus.

NOTE: The DSP/User Memory is RAM. All data is lost when power is removed from the DBS 8750. Be sure to save all important data to another memory device before switching power off. After power-on, this memory contains random data. This memory is not initialized during the power-on sequence.

3.5.1

#### **Creating Memory Buffers**

Memory buffers are created in the DSP/User Memory whenever any of the following commands are used: MEMory:SAV1(2), MEMory:READ, MEMory:ACQuire, and MEMory:MALLocate.

The creation of each new memory buffer requires 35 words of space for identification and housekeeping. Therefore, when estimating memory space requirements, bear in mind that the size of each buffer is determined by the number of points (words) comprising the waveform plus 35. This means that if three 1000-point waveforms are saved, the amount of actual memory space occupied is 3,105 points  $[(3 \times 1000) + (3 \times 35) = 3105]$ .

A maximum of 20 memory buffers may be created. Any attempt to create more than that generates an error message. However, the number of buffers that can be created also depends upon the number of data points (words) being written into each buffer. The number of data points (Npts) in a waveform is determined by dividing the Sampling Rate Clock Frequency by the frequency of the output waveform [Equation 1]. For example, using the 400-kHz Internal Sampling Rate Clock, a 400-Hz sine wave consists of 1,000 points [Equation 2]. At the same rate, a 20 kHz sinewave consists of only 20 points, but a 23.5 Hz sinewave consists of 17021 pts which nearly fills the entire user memory space by itself.

| Sampling Rate Clock Frequency | = Npts     | [Equation 1] |

|-------------------------------|------------|--------------|

| Output Function Frequency     |            |              |

| 400 kHz<br>400 Hz             | = 1000 pts | [Equation 2] |

## NOTE: A DC function always generates 100 points and the NOISe function always generates 8192 points.

The user memory space is written contiguously, starting at the Memory Base Address, as each buffer is created. That is, the memory is filled with one buffer after another with no gaps in between. The scenario depicted in Figure 3-16 demonstrates how this memory might be used. In this diagram, the numbered arrows indicate the direction of data transfer; the numbers indicate the sequence in which the commands were performed. First, the user generated (1) a standard 400-kHz (1000 pts.) sine wave on channel 1 and saved it (2) to a buffer named "SavdWave." The user then transferred that buffer (3) to the VXI Memory. Next, 1024 data points were read (4) from the VXI Memory and stored in the buffer named "VxBuffer." After that, the user acquired 2048 data points (5) from a DAS module via the LOCALbus and generated that waveform in the DAC 2 channel (6). Finally, a 2048-word space was allocated (7) in the memory for "NewData."

#### 3.5.2 Saving Waveforms

To save a particular waveform, first select it by the command,

SOURce:FUNCtion DC|SINe|SQUare|TRIangle|NOISe|USER|MEMory

This creates the waveform data in the DAC 1/2 Waveform Memory. The waveform data can then be saved using the command,

MEMory:SAV1(2) <Buffer Name>

Figure 3-16. DSP/User Memory Example

## 3.5.3 Read/Write VXI Memory

#### NOTE: The MEMory:READ and MEMory:ACQuire functions automatically allocate the named buffer if it does not already exist.

The DBS 8750 can read/write VXI Memory data using the MEMory:READ and MEMory:WRITe commands (Refer to Figure 3-14.). A READ transfers data from VXI memory to DSP/User memory. A WRITe transfers data from the DSP/User Memory to VXI Memory.

For example, to read 1024 points of VXI memory data, starting at VXI address 200000h, into a DSP/User Memory buffer named "VDATA," send

MEMory:READ 200000 1024 VDATA

To WRITe 1024 points of DSP/User memory buffer "VDATA" into VXI Memory starting at VXI address 200000h, send

MEMory:WRITe 200000 1024 VDATA

The DBS 8750 is a Bus Master during data transfers.

#### 3.5.4 Acquiring LOCALbus Data

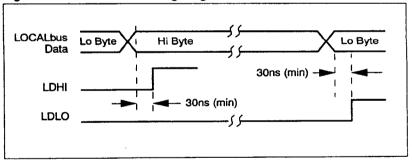

Waveform data can be acquired via the LOCALbus from an external source such as a DBS 8700 Digitizer. The strobe signals and timing requirements are shown in Figure 3-17. The 16-bit word is received in two bytes using two individual strobe signals: LDHI (P2c17) is the high byte strobe signal (loaded first), and LDLO (P2c18) is the low byte strobe signal.

To acquire 2048 points of waveform data via the LOCALbus and store it in a buffer named DIGDATA, send

MEMory: ACQuire 2048 DIGDATA

#### Figure 3-17. LOCALbus Timing Diagram

# NOTE: This command requires that a complete data transfer occurs in order to terminate successfully. Otherwise, the command will "hang" waiting for the transfer to complete.

The data is stored in the specified memory buffer as 16-bit words. The maximum word rate is 300 kHz. As long as the timing requirements are met, this port can receive data from any custom device without burdening the VXIbus. See Appendix A for signal connection pin assignments.

3.5.5 Allocating Memory

The MEMory:MALLocate command can be used to allocate a block of DSP/User memory. This command creates a buffer of a specified point size. After allocation, any waveform data may be written into this space.

To allocate a block of DSP/User Memory, send

MEMory:MALLocate<sp><Buffer Name><sp><Npts>

- <Buffer Name>.. Name of buffer, 31 characters max., excluding whitespace, colons, and semicolons.

- <Npts> ...... Number of points A positive decimal integer for the number of 16-bit words to be written to memory (maximum is amount of free memory minus 35 words overhead). No default value. Failure to specify causes a syntax error.

For example, sending MEMory:MALLocate NewWave 1000 would create a buffer named "NewWave" starting at the next free location in DSP/User Memory and allocate 1000 + 35 points of memory space for this buffer.

In response to this command, the DBS 8750 returns either the A24 base address offset (in ASCII) of the buffer, or the error message; "-225, Out of memory; cannot allocate memory for buffer."

When specifying buffer size, keep in mind that the buffer must be loaded into contiguous memory. Thus, if you have been adding and deleting buffers, this command may fail, even if the total amount of free memory is sufficient.

Data may be written to the allocated memory in the A24, D16 space, but since only 16-bit transfers are allowed, only even addresses are valid.

This command can also be used to re-allocate an existing buffer. However, if a sufficient amount of contiguous memory space is not available, the command may fail. Note that the DBS 8750 frees the existing buffer memory before attempting to reallocate the buffer. If resizing fails, the

buffer re-allocates memory to the original size and data in the existing buffer may be corrupted. If failure occurs, the error message "-225, Out of memory; cannot resize the buffer" is generated.

## NOTE: Buffers which are allocated by this command are not initialized by the DBS 8750.

The DBS 8750 assumes that the whole allocated buffer area is used for the waveform.

The DBS 8750 does not provide any bounds checking while writing to a user buffer. Writing to memory which has not been allocated, or writing more points than have been allocated may cause unpredictable results, including "hanging" the VXI bus.

#### 3.5.6 Memory Status

A status of the DSP/User Memory can be obtained using the MEMory:CATalog? and MEMory:FREE? query commands.

The MEMory:CATalog? command responds with a continuous data string in the following format:

<filled memory>,<free memory>,<buffer name>,<type>,<size>,<buffer name>,<type>,<size>... etc.

If there are no existing buffers, the response to MEM:CAT? is 0,17150.

Conversely, the MEM:FREE? response is <free memory>,<filled memory>; or 17150, 0.

If the memory is filled as shown in Figure 3-14, MEM:CAT? responds with the following which is formatted in a column for the purpose of this presentation. Formatting is left up to the user.

6260,10890, SAVDWAVE,BIN,1000, VXBUFFER,BIN,1024, DASDATA,BIN,2048, NEWDATA,BIN,2048

And the MEM:FREE? response is,

10890,6260.

#### 3.5.7 Deleting Buffers

Buffers can be deleted from DSP/User Memory all at once or one at a time by name using the MEMory:DELete command.

To delete the first buffer in the Figure 3-14 example, send

MEM:DEL SavdWave

To delete all buffers, send

MEM:DEL ALL

## 3.6 TRIGGERING

The DBS 8750 can be triggered internally by the software, or externally via the front panel TRIG input or one of the TTL Trigger lines. Use the following command for trigger control:

TRIGger:SOURce INT | EXT | TTLtrg<0-7>

INT ...... Internal Software Command

EXT ..... Front Panel TRIG Input

TTLtrg<0-7> ..... TTL Trigger line 0-7

#### 3.6.1 Internal Trigger

To select internal triggering, send TRIGger:SOURce INT. Since this is the power-on default setting, in a sense the DBS 8750 is always triggerred. With the internal trigger mode, waveform generation begins immediately after it is defined, assuming that the output is switched on.

To use this command effectively,

- (1) Send TRIG:SOUR EXT.

- (2) Define the waveform.

- (3) Send TRIG:SOUR INT to start the waveform.

## 3.6.2 External Trigger

The TRIG input (via the front panel connector or a TTLTRG line) accepts a TTL, active low signal to enable waveform generation. An uncertainty of 60ns to 120ns may be introduced due to internal synchronization.

By sending TRIGger:SOURce EXT, the TRIG input signal can be used to control waveform generation.

#### 3.6.3 Trigger Sequences

A Trigger Sequence is a set of command functions which are executed under control of the Internal/External Trigger signal and the Trigger Sequence Commands (Table 3-2). Trigger Sequences allow you combine various types of standard and/or user-defined wave shapes to generate complex output waveforms. The defined Trigger Sequence can be generated as a single burst of a defined number of cycles or it can be generated continuously in a Free Running mode.

The following three examples describe an internally-triggerred complex wave burst, an externally-triggerred sine wave burst and a free running complex wave.

NOTE: In order for Trigger Sequences to run correctly, the DBS 8750 must be equipped with firmware revision 2.0 or higher. To determine hardware/software revision levels, refer to the \*IDN? command in Section 4.

#### 3.6.3.1 Programming Guidelines

When creating Trigger Sequences, bear in mind the following guidelines:

- (1) Only two trigger sequences are allowed per channel. When sending the commands, SEQuence1 must always precede SEQuence2.

- (2) The beginning and end of a sequence must be defined by a TRIG[1](2):SEQ[1](2):STARt command and a TRIG[1](2):SEQ[1](2):STOP command, respectively.

- (3) Since the defined sequence is created in 32K-word DAC Waveform Memory, the aggregate number of points generated by the trigger sequence(s) must be less than or equal to 32K-points.

- (4) As a general pratice, always strive to fill waveform memory with as many waveform cycles as possible (TRIG:SEQ:COUNt <Highest Possible Value>) and set the repeat count as low as possible (TRIG:COUNt <Lowest Possible Value>). This generates the minimum number of interrupts to the DSP and ensures better performance.

- (5) Always send the INITiate command last after the complete sequence has been defined.

- (6) OUTPut commands may be included in a trigger sequence, but are executed only once following the INITiate command.

- (7) When using an External Trigger signal, it must be held low for the entire duration of the Trigger Sequence output including all repeat loops.

- (8) To generate a waveform in the free running mode, set the repeat count to zero. In other words, include the command TRIG:COUN 0.

| Command                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRIGger[1](2):SEQuence[1](2):STARt | Defines the beginning of a Trigger Sequence.<br>SEQ1 must always precede SEQ2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TRIGger[1](2):SEQuence[1](2):STOP  | Defines the end of a Trigger Sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TRIGger[1](2):SEQuence[1](2):COUNt | Sets the sequence counter which controls the<br>number of times to repeat the commands of the<br>sequence. This statement must be sent between<br>the STARt and STOP commands. This count<br>determines the number of waveform cycles that<br>are to be written in waveform memory. This value<br>should always be as high as possible. However,<br>maximum COUNt is limited by waveform memory<br>size. The total number of points generated by the<br>trigger sequences must be less than or equal to<br>32K words, the maximum number of points that<br>each DAC Waveform Memory can hold. |

| TRIGger:COUNt                      | Sets the repeat counter which controls the number<br>of times to repeat all trigger sequences. Actually,<br>this specifies the number of times the program<br>reads through waveform memory.                                                                                                                                                                                                                                                                                                                                                                                                  |

| INITiate[1](2)                     | Arms the Trigger Sequence for execution. If this<br>command is sent while in the Internal Trigger<br>Mode, the trigger sequence is executed<br>immediately. If in the External Trigger Mode, the<br>sequence is executed when a positive TTL level is<br>present on the TRIG input.                                                                                                                                                                                                                                                                                                           |

| ABORt[1](2)                        | Stops execution of the Trigger Sequence. Trigger<br>Sequence information is saved and the instrument<br>is returned to its previous state.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### Table 3-2. Trigger Sequence Control Commands

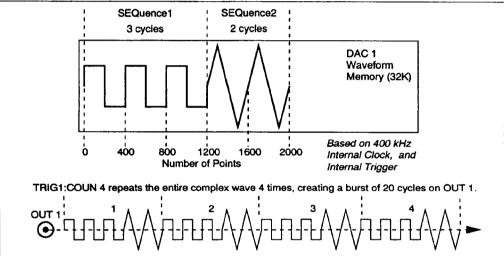

## 3.6.3.2 Example #1: Complex Wave Burst – Internal Trigger

This Trigger Sequence creates three cycles of a 1-kHz square wave followed by two cycles of a 1-kHz triangle wave and repeats the composite waveform three times. The Internal Trigger is selected by a reset default setting.

| *RST                    | Reset the instrument.              |

|-------------------------|------------------------------------|

| TRIG1:SEQ1:STARt        | Start of SEQuence1 for OUT 1.      |

| SOUR1:FUNC SQU          | Select square wave.                |

| SOUR1:VOLT 5;FREQ 1000  | Select 5-volt amplitude; 1 kHz.    |

| OUTP1:DRIV SING         | Select single-ended output.        |

| OUTP1:FILT OFF;STAT ON  | Select filter off; output ON.      |

| TRIG1:SEQ1:COUN 3       | Set SEQuence1 Counter to 3.        |

| TRIG1:SEQ1:STOP         | End of SEQuence1.                  |

| TRIG1:SEQ2:STARt        | Start of SEQuence2 for OUT 1.      |

| SOUR1:FUNC TRI          | Select triangle wave.              |

| SOUR1:VOLT 10;FREQ 1000 | . Select 10-volt amplitude; 1 kHz. |

| TRIG1:SEQ2:COUN 2       | Set SEQuence2 Counter to 2.        |

| TRIG1:SEQ1:STOP         | End of SEQuence2.                  |

| TRIG1:COUN 4            | Set Repeat Counter to 4.           |

| INIT1                   | . Arm trigger sequence for OUT1.   |

NOTE: Because of the methods used to calculate waveforms, the actual output may not appear exactly as illustrated.

## 3.6.3.3 Example #2: Sine Wave Burst – External Trigger

The following generates 10 cycles of a 800-Hz Sine Wave, triggerred externally. Note that the EXT TRIG input signal is held high for the entire output burst.

| TRIG1:SEQ1:STARt    Start of SEQuence1 for OUT 1.      SOUR1:FUNC SIN    Select sine wave.      SOUR1:VOLT 5.75    Select 5.75-volt amplitude.      SOUR1:FREQ 1000    Select 1 kHz.      OUTP1:FILT ON;STAT ON    Select filter OFF; output ON.      TRIG1:SEQ1:COUN 10    Select External Trigger from front panel.      TRIG1:SEQ1:STOP    End of SEQuence1. | *RST                  | Reset the instrument.                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------|

| SOUR1:VOLT 5.75    Select 5.75-volt amplitude.      SOUR1:FREQ 1000    Select 1 kHz.      OUTP1:FILT ON;STAT ON    Select filter OFF; output ON.      TRIG1:SEQ1:COUN 10    Set SEQuence1 Counter to 10.      TRIG:SOUR EXT    Select External Trigger from front panel.                                                                                        | TRIG1:SEQ1:STARt      | Start of SEQuence1 for OUT 1.             |

| SOUR1:FREQ 1000                                                                                                                                                                                                                                                                                                                                                 | SOUR1:FUNC SIN        | Select sine wave.                         |

| OUTP1:FILT ON;STAT ON Select filter OFF; output ON.<br>TRIG1:SEQ1:COUN 10 Set SEQuence1 Counter to 10.<br>TRIG:SOUR EXT Select External Trigger from front panel.                                                                                                                                                                                               | SOUR1:VOLT 5.75       | Select 5.75-volt amplitude.               |

| TRIG1:SEQ1:COUN 10 Set SEQuence1 Counter to 10.<br>TRIG:SOUR EXT Select External Trigger from front panel.                                                                                                                                                                                                                                                      | SOUR1:FREQ 1000       | Select 1 kHz.                             |

| TRIG:SOUR EXT Select External Trigger from front panel.                                                                                                                                                                                                                                                                                                         | OUTP1:FILT ON;STAT ON | Select filter OFF; output ON.             |

|                                                                                                                                                                                                                                                                                                                                                                 | TRIG1:SEQ1:COUN 10    | Set SEQuence1 Counter to 10.              |

| TRIG1:SEQ1:STOP End of SEQuence1.                                                                                                                                                                                                                                                                                                                               | TRIG:SOUR EXT         | Select External Trigger from front panel. |

|                                                                                                                                                                                                                                                                                                                                                                 | TRIG1:SEQ1:STOP       | End of SEQuence1.                         |

| INIT1 Initiate trigger sequence.                                                                                                                                                                                                                                                                                                                                | INIT1                 | . Initiate trigger sequence.              |

NOTE: Because of the methods used to calculate waveforms, the actual output may not appear exactly as illustrated.

## 3.6.3.4 Example #3: Free Running Complex Wave

The following sequence continuously generates 1 cycle of a pre-defined USER function followed by 5 cycles of a 400-Hz, 1-volt square wave on channel 2. Notice that the Free Running Mode is set by the TRIG2:COUNt 0 command.

| *RST                   | Reset the instrument.            |

|------------------------|----------------------------------|

| TRIG2:SEQ1:STAR        | Start of SEQuence1 for OUT 2.    |

| SOUR2:FUNC USER        | Select user-defined function.    |

| OUTP2:FILT OFF;STAT ON | Select filter off; output ON.    |

| TRIG2:SEQ1:COUN 1      | Set SEQuence1 Counter to 1.      |

| TRIG2:SEQ1:STOP        | End of SEQuence1.                |

| TRIG2:SEQ2:STAR        | Start of SEQuence2 for OUT2.     |

| SOUR2:FUNC SQU         | Select square wave.              |

| SOUR2:VOLT 1;FREQ 400  | Select 1-volt amplitude; 400 Hz. |