# Graphical Editors User Manual for the HDL Designer Series

Software Version 2008.1

September 18, 2008

# © 1996-2008 Mentor Graphics Corporation All rights reserved.

This document contains information that is proprietary to Mentor Graphics Corporation. The original recipient of this document may duplicate this document in whole or in part for internal business purposes only, provided that this entire notice appears in all copies. In duplicating any part of this document, the recipient agrees to make every reasonable effort to prevent the unauthorized use and distribution of the proprietary information.

This document is for information and instruction purposes. Mentor Graphics reserves the right to make changes in specifications and other information contained in this publication without prior notice, and the reader should, in all cases, consult Mentor Graphics to determine whether any changes have been made.

The terms and conditions governing the sale and licensing of Mentor Graphics products are set forth in written agreements between Mentor Graphics and its customers. No representation or other affirmation of fact contained in this publication shall be deemed to be a warranty or give rise to any liability of Mentor Graphics whatsoever.

MENTOR GRAPHICS MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

MENTOR GRAPHICS SHALL NOT BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL, OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATED TO THIS PUBLICATION OR THE INFORMATION CONTAINED IN IT, EVEN IF MENTOR GRAPHICS CORPORATION HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

#### **RESTRICTED RIGHTS LEGEND 03/97**

U.S. Government Restricted Rights. The SOFTWARE and documentation have been developed entirely at private expense and are commercial computer software provided with restricted rights. Use, duplication or disclosure by the U.S. Government or a U.S. Government subcontractor is subject to the restrictions set forth in the license agreement provided with the software pursuant to DFARS 227.7202-3(a) or as set forth in subparagraph (c)(1) and (2) of the Commercial Computer Software - Restricted Rights clause at FAR 52.227-19, as applicable.

#### Contractor/manufacturer is:

Mentor Graphics Corporation 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777.

Telephone: 503.685.7000

Toll-Free Telephone: 800.592.2210

Website: www.mentor.com

SupportNet: supportnet.mentor.com/

Send Feedback on Documentation: supportnet.mentor.com/user/feedback\_form.cfm

**TRADEMARKS**: The trademarks, logos and service marks ("Marks") used herein are the property of Mentor Graphics Corporation or other third parties. No one is permitted to use these Marks without the prior written consent of Mentor Graphics or the respective third-party owner. The use herein of a third-party Mark is not an attempt to indicate Mentor Graphics as a source of a product, but is intended to indicate a product from, or associated with, a particular third party. A current list of Mentor Graphics' trademarks may be viewed at: www.mentor.com/terms\_conditions/trademarks.cfm.

| Chapter 1                                           |    |

|-----------------------------------------------------|----|

| Introduction                                        | 17 |

| The Design Creation Editors                         | 18 |

| DesignPad Text Editor                               | 18 |

| Block Diagram and IBD View Editors                  | 18 |

| Component Interface Editor                          | 18 |

| State Diagram and Algorithmic State Machine Editors | 18 |

| Flow Chart Editor                                   | 18 |

| Truth Table Editor                                  | 19 |

| Editor Windows                                      | 19 |

| The Menu Bar                                        | 19 |

| Toolbars                                            | 20 |

| Standard Toolbar                                    | 20 |

| Keyboard Shortcuts                                  | 21 |

| Mnemonic Keys                                       | 22 |

| Command Auto-repeat                                 | 22 |

| Strokes                                             | 22 |

| Common Features                                     | 23 |

| Setting the Hardware Description Language           | 23 |

| Setting Package References                          | 23 |

| Example VHDL Package List                           | 25 |

| Setting Compiler Directives                         | 26 |

| Formatting Text                                     | 27 |

| Format Text Toolbar                                 | 27 |

| Opening the Parent View                             | 28 |

| Editing the Parent Interface                        | 28 |

| Using the Same Window                               | 29 |

| Saving Graphic Editor Views                         | 29 |

| Automatic Backup and Recovery                       | 31 |

| Saving the Window Position and Size                 | 32 |

| Editing Object Properties                           | 32 |

| Redrawing a Window                                  | 32 |

| Undo and Redo                                       | 32 |

| Selecting Objects                                   | 33 |

| Copying and Pasting Objects                         | 34 |

| Deleting Objects                                    | 34 |

| Finding and Replacing Text Strings                  | 35 |

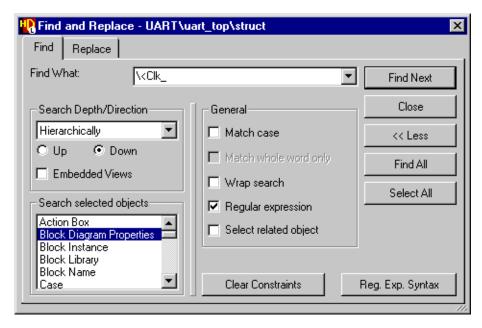

| More Search Options                                 | 35 |

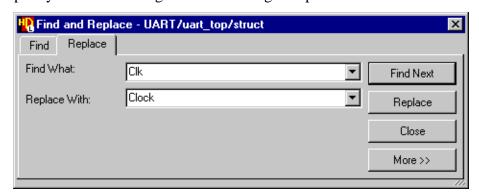

| Replacing a Text String                             | 37 |

| Object Linking and Embedding                        | 38 |

| Using Drag and Drop                                 | 40 |

| Opening an OLE View                                 | 41 |

| Generating HDL                            | 41<br>44<br>44 |

|-------------------------------------------|----------------|

| Viewing the Generated HDL                 | 44             |

| Chapter 2                                 |                |

| Graphical Editor Windows                  | 47             |

|                                           |                |

| Diagram Editor Windows                    | 48             |

| Setting Preferences for Diagram Views     | 48             |

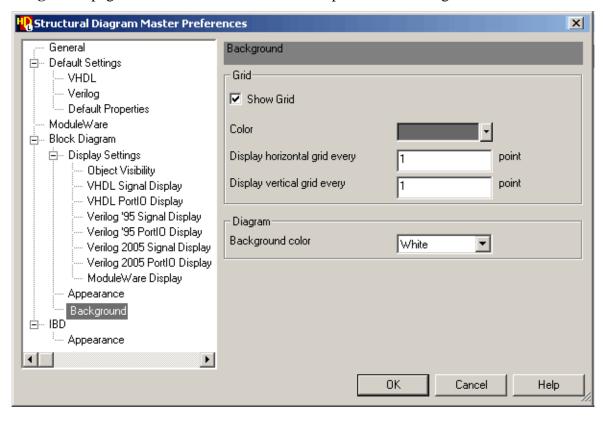

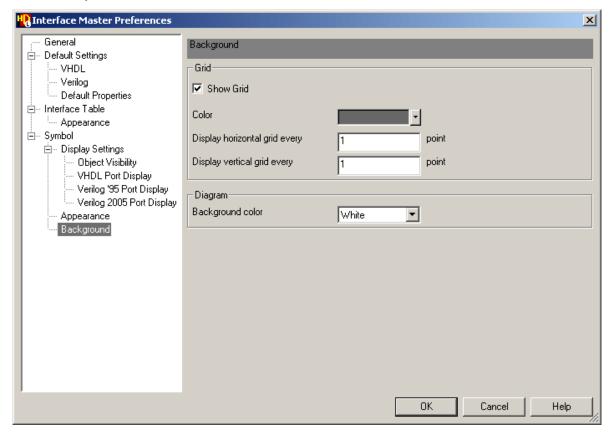

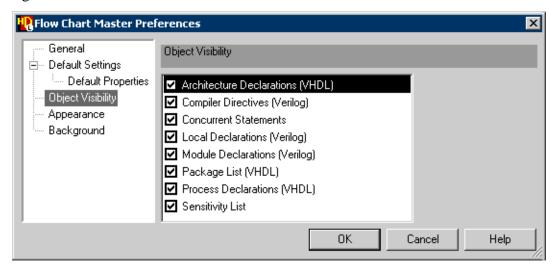

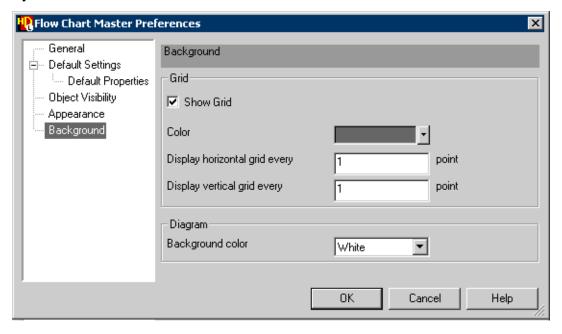

| Setting Diagram Master Preferences        | 49             |

| Setting Background Preferences            | 50             |

| Moving and Copying Diagram Objects        | 51             |

| Resizing Objects                          | 53             |

| Arranging Objects                         | 53             |

| Arrange Object Toolbar                    | 53             |

| Aligning or Distributing Objects          | 54             |

| Rotating and Flipping Objects             | 54             |

| Layering Comment Text and Graphics        | 55             |

| Grouping Comment Text and Graphics        | 55             |

| Adding Comment Text                       | 56             |

| Editing Text Properties                   | 58             |

| Editing Text on a Diagram                 | 59             |

| Text Editing Shortcuts                    | 60             |

| Editing Text in the Text Editor           | 61             |

| Moving Text                               | 62             |

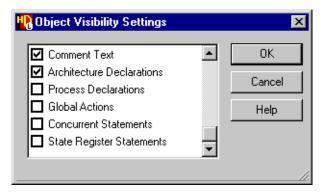

| Changing Text Visibility                  | 63             |

| Adding Comment Graphics                   | 67             |

| Comment Graphics Toolbar                  | 67             |

| Adding a Line or Polyline                 | 69             |

| Adding an Arc                             | 69             |

| Adding a Rectangle or Polygon             | 70             |

| Adding an Ellipse or Circle               | 70             |

| Adding a Bitmap                           | 71             |

| Adding a Title Block                      | 71             |

| Displaying Object Information             | 72             |

| Panels                                    | 73             |

| Adding a Panel                            | 73             |

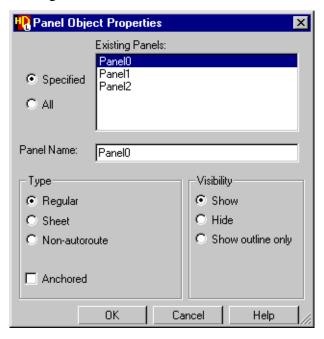

| Editing Panel Object Properties           | 74             |

| Displaying a Panel                        | 75             |

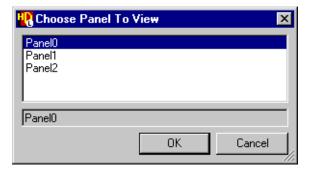

| Viewing a Panel                           | 75             |

| Protecting Panels                         | 75             |

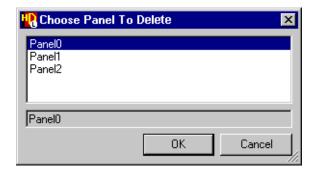

| Deleting a Panel                          | 76             |

| Printing a Panel                          | 76             |

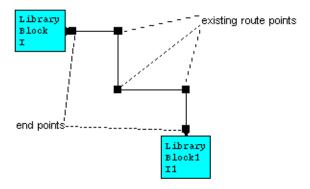

| Editing Route Points                      | 77             |

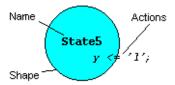

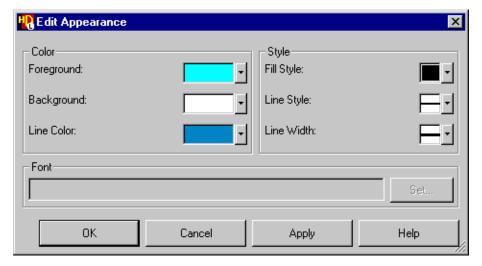

| Setting Visual Attributes                 | 78             |

| Appearance Toolbar                        | 79             |

| Setting Color Attributes                  | 80             |

| Toggling the Grid Visibility and Snapping | 80             |

| Changing the Diagram View                                        | 81  |

|------------------------------------------------------------------|-----|

| Table Editor Windows                                             | 81  |

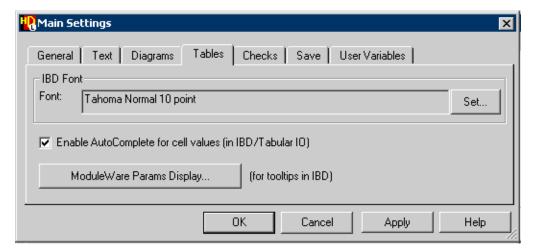

| Setting Preferences for Table Views                              | 82  |

| Selecting Table Cells                                            | 83  |

| Editing a Table Cell                                             | 83  |

| Changing the Table View                                          | 84  |

| Resizing a Column or Row                                         | 84  |

| Exporting a Table                                                | 85  |

| The Diagram Browser                                              | 86  |

| Browsing Diagram Structure                                       | 87  |

| Browsing Diagram Content                                         | 89  |

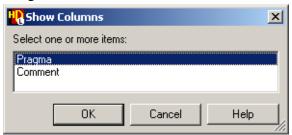

| Changing the Columns in the Content Pane                         | 91  |

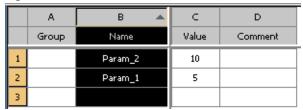

| Sorting the Content Pane                                         | 92  |

| Using Groups in the Content Pane                                 | 92  |

| Using Flow Help                                                  | 92  |

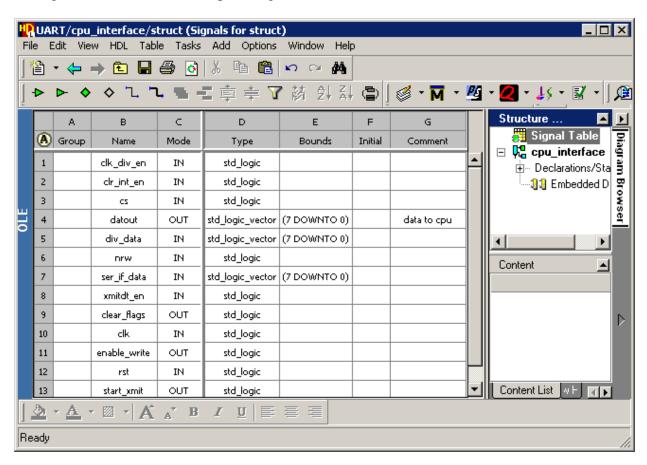

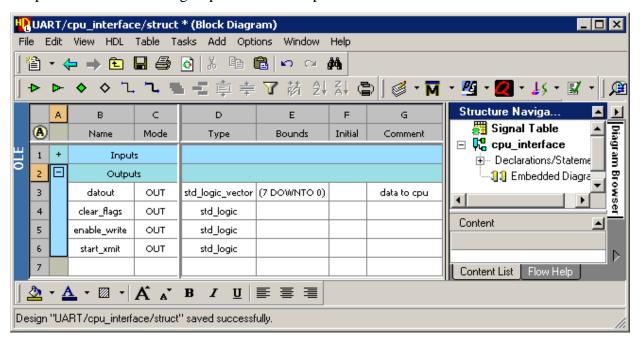

| Signals Table                                                    | 94  |

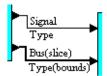

| Signals Table Notation                                           | 95  |

| Signal Declaration Columns                                       | 95  |

| Signals Table Toolbars                                           | 95  |

| Adding Port or Local Signal Declarations                         | 96  |

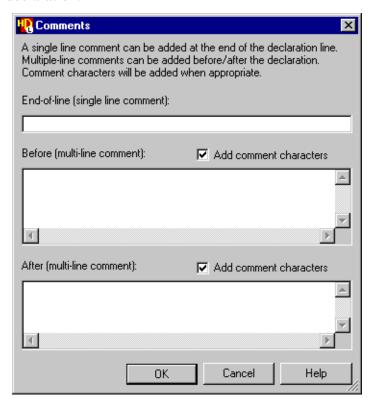

| Adding Comments to a Port or Local Signal Declaration            | 97  |

| Resizing Columns                                                 | 98  |

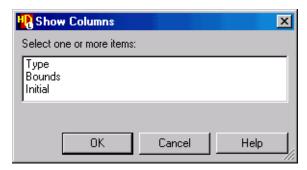

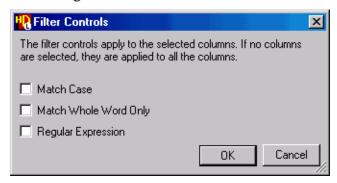

| Hiding Columns                                                   | 99  |

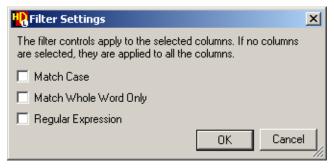

| Filtering Columns                                                | 99  |

| Grouping Signal Rows                                             | 99  |

| Sorting Signal Rows                                              | 101 |

|                                                                  |     |

| Chapter 3                                                        |     |

| Block Diagram and IBD Views                                      | 103 |

| Editing Block Diagram and IBD Views                              | 104 |

| Adding Blocks and Components                                     | 104 |

| Assigning Automatic Instance Names                               | 105 |

| Instantiating a Block                                            | 105 |

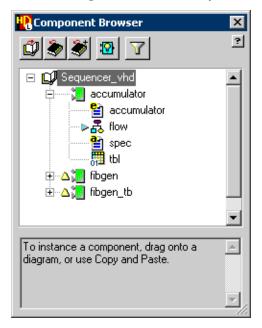

| Instantiating a Component                                        |     |

| Instantiating Verilog 2005 or System Verilog 3.0 Text Components | 108 |

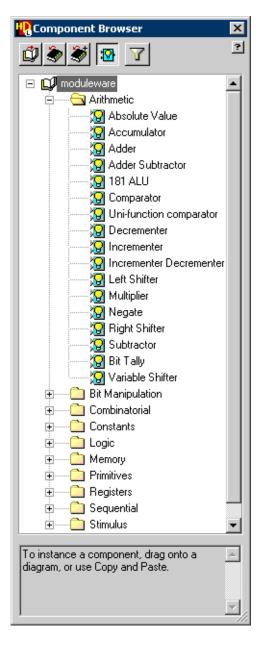

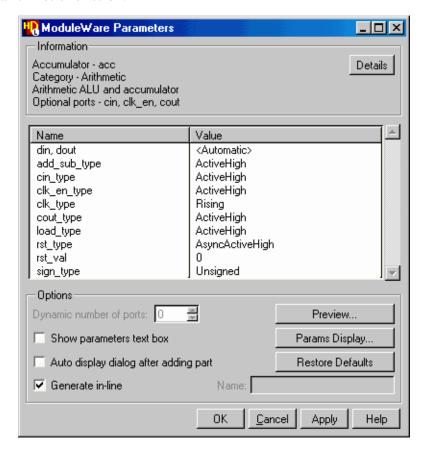

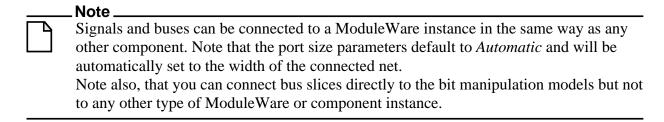

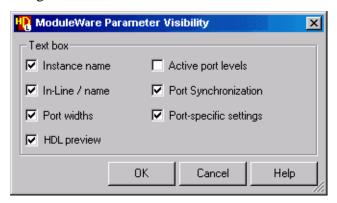

| Instantiating a ModuleWare Component                             | 110 |

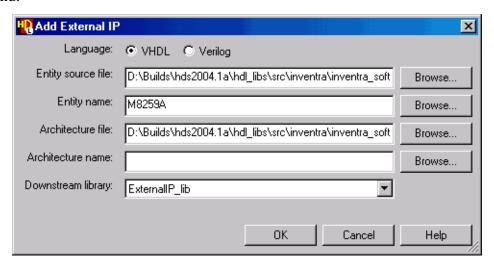

| Instantiating an External HDL Model                              | 114 |

| Using a Soft Pathname for External HDL                           | 117 |

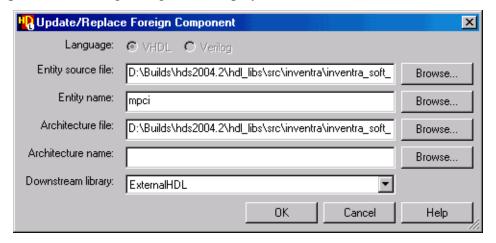

| Updating an External HDL Model                                   | 118 |

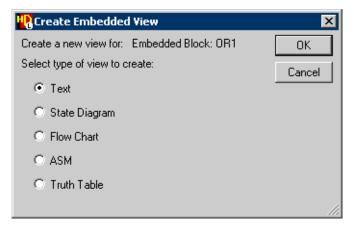

| Adding an Embedded Block                                         | 118 |

| Opening an Embedded View                                         | 119 |

| Adding Embedded HDL Text                                         | 120 |

| Updating an Instance.                                            | 121 |

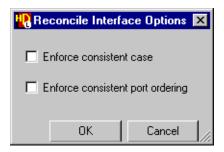

| Reconciling Interfaces                                           | 122 |

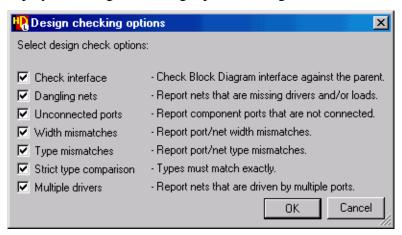

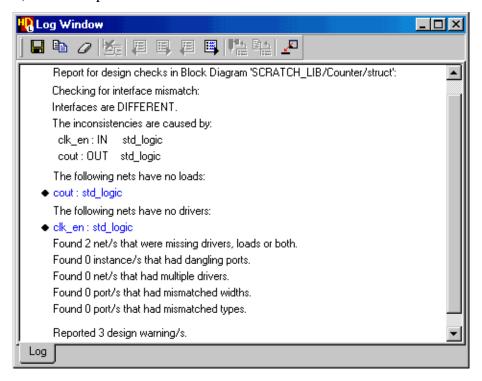

| Checking the Design                                              | 125 |

| Checking Through Hierarchy                                       | 126 |

| Editing Object Properties                                        | 127 |

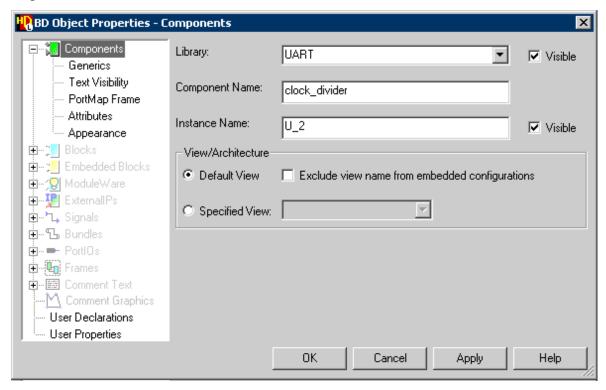

| Editing Component Properties                                     | 127 |

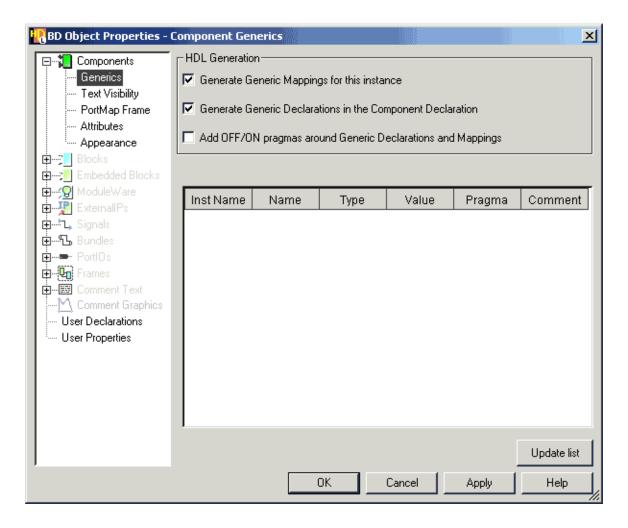

|   | Editing Component Generics and Parameters               |     |

|---|---------------------------------------------------------|-----|

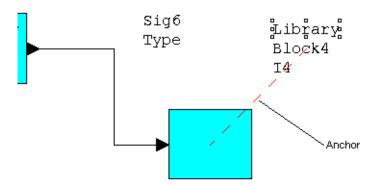

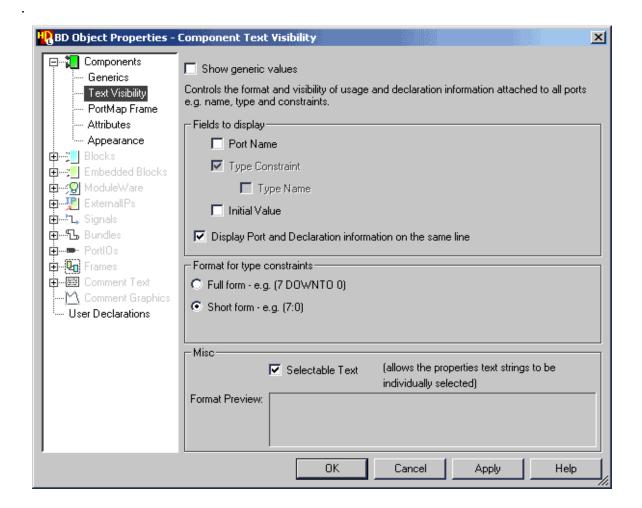

|   | Editing Component Text Visibility                       | 129 |

|   | Editing Component Port map Frame                        | 130 |

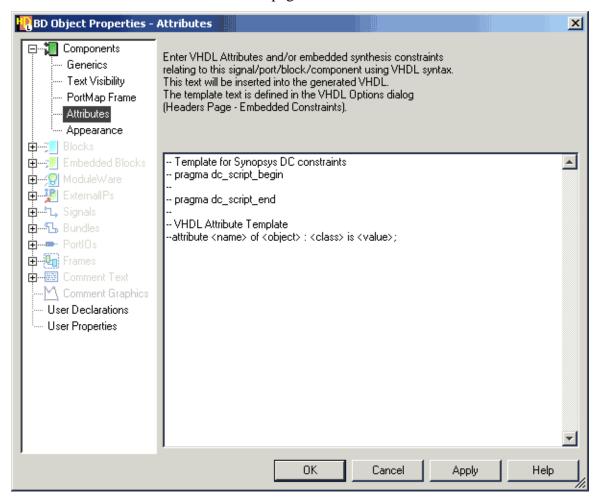

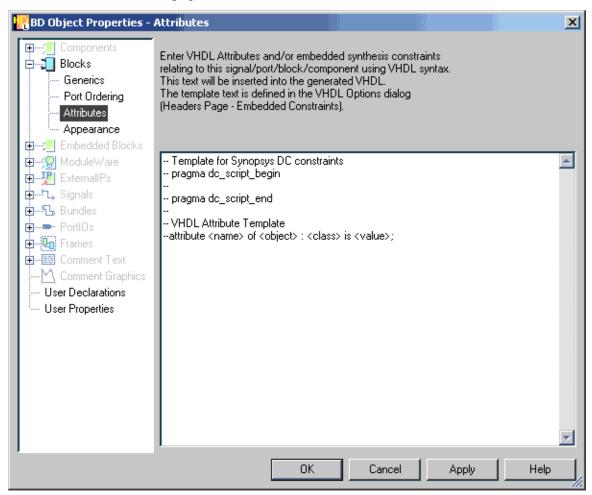

|   | Setting Component Attributes and Embedded Constraints   | 132 |

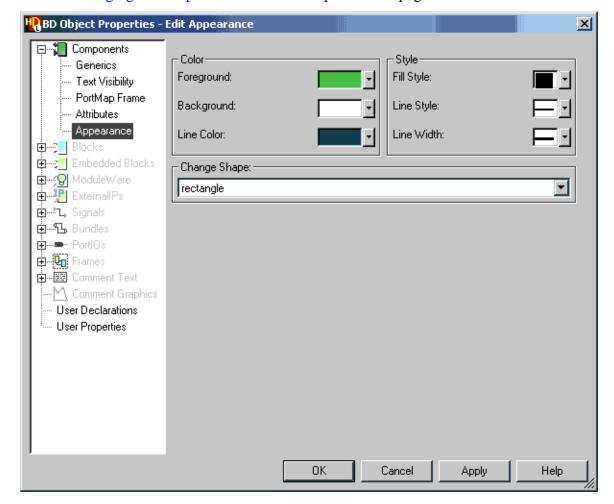

|   | Modifying Component Appearance                          | 132 |

|   | Editing Block Properties                                | 133 |

|   | Editing Block Generics and Parameters                   | 134 |

|   | Modifying Block Port Ordering                           | 134 |

|   | Setting Block Attributes and Embedded Constraints       | 135 |

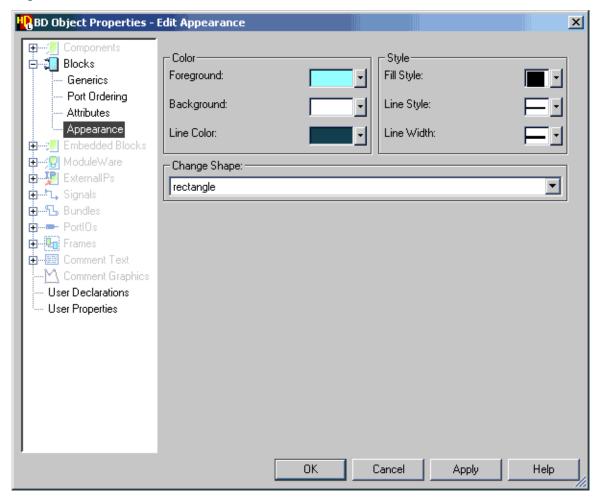

|   | Setting Block Appearance                                | 135 |

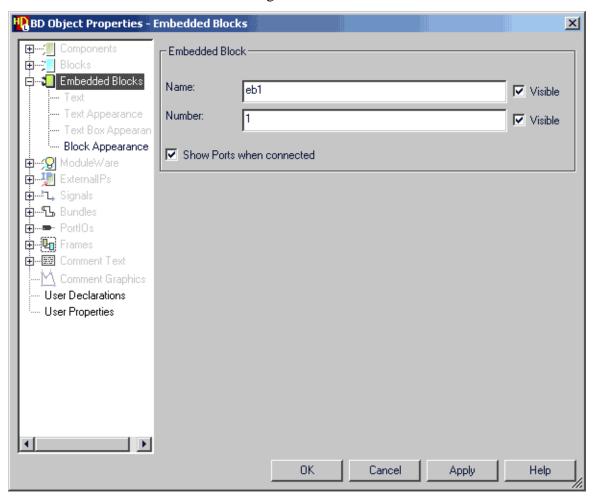

|   | Editing Embedded Block Properties                       | 137 |

|   | Editing Embedded Blocks HDL Text                        | 138 |

|   | Modifying Embedded Blocks Text Appearance               | 138 |

|   | Modifying Embedded Blocks Text Box Appearance           | 138 |

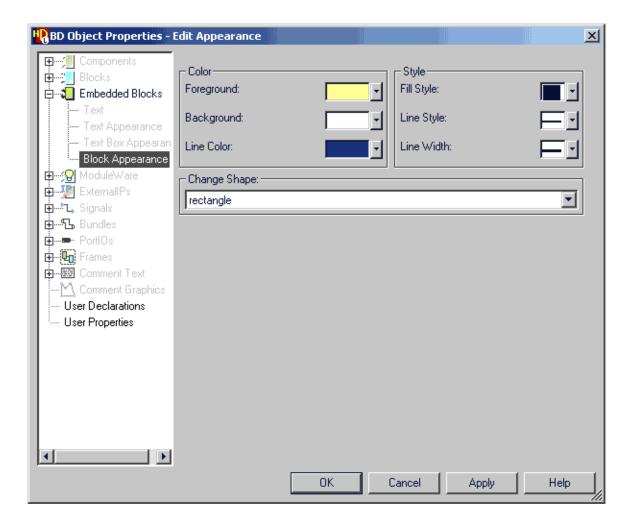

|   | Modifying Embedded Blocks Appearance                    | 138 |

|   | Editing ModuleWare Properties                           | 139 |

|   | Editing Moduleware Port map Frames.                     | 140 |

|   | Setting ModuleWare Attributes and Embedded Constraints  | 140 |

|   | Editing External IPs Properties                         | 140 |

|   | Editing External IP Generics                            | 141 |

|   | Editing External IP Text Visibility                     | 141 |

|   | Editing External IP Port map Frame                      |     |

|   | Setting External IP Attributes and Embedded Constraints | 141 |

|   | Modifying External IP Appearance                        |     |

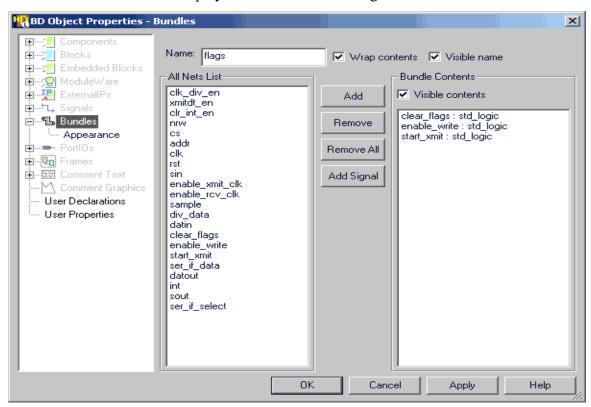

|   | Editing Bundle Properties                               | 142 |

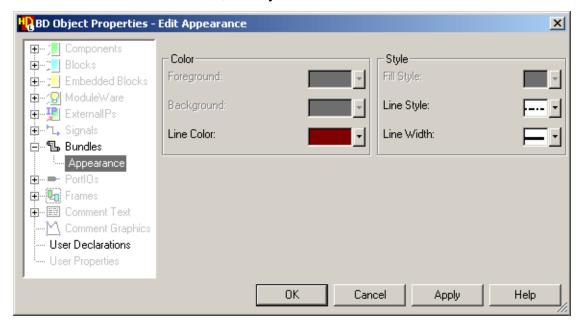

|   | Modifying Bundle Appearance                             | 143 |

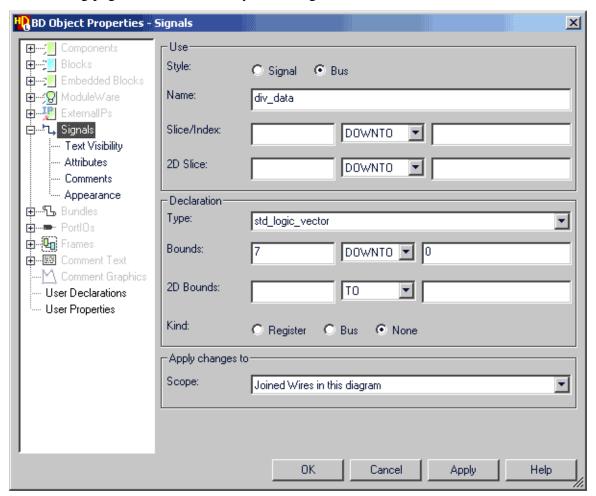

|   | Editing Signal Properties                               | 143 |

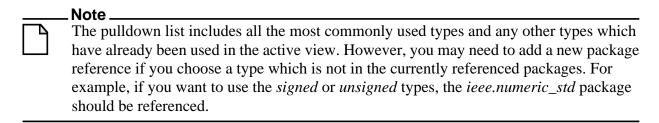

|   | Editing VHDL Signal Declarations                        | 144 |

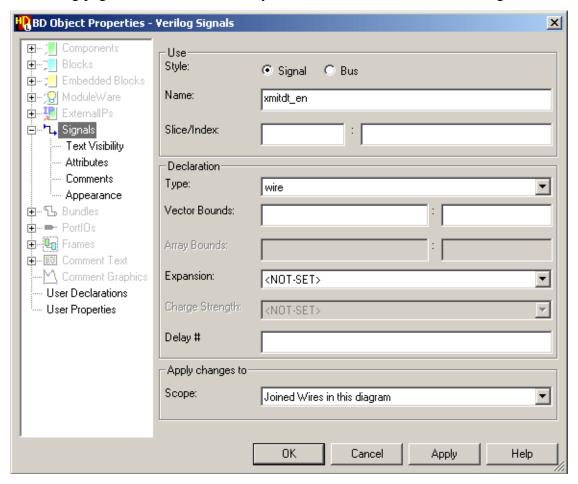

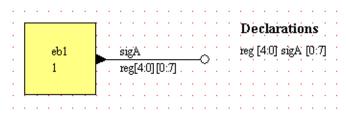

|   | Editing Verilog Signal Declarations.                    | 146 |

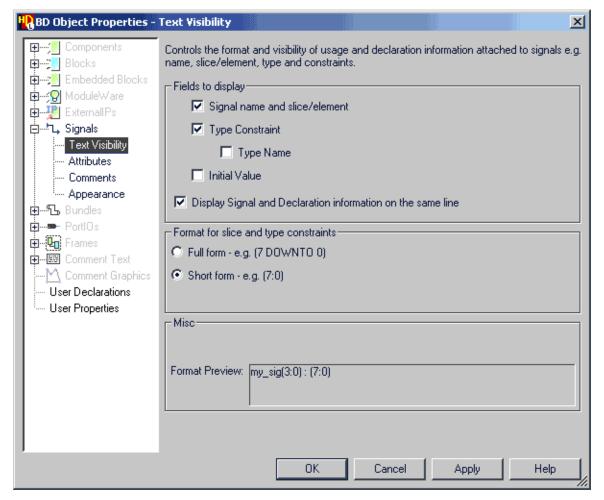

|   | Editing Signal Text Visibility                          | 147 |

|   | Setting Signal Attributes and Embedded Constraints      | 148 |

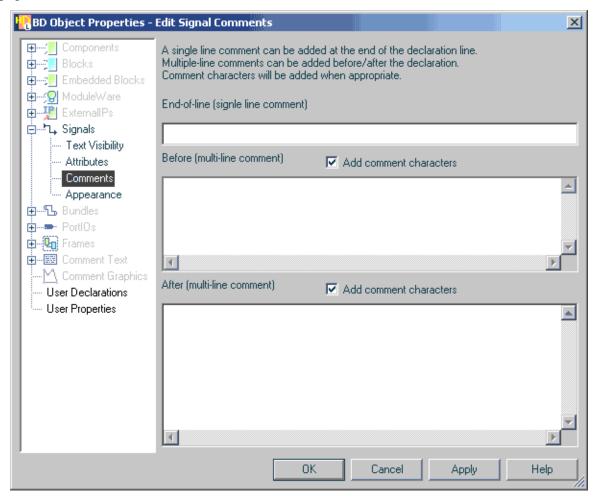

|   | Editing Signal Comments.                                | 149 |

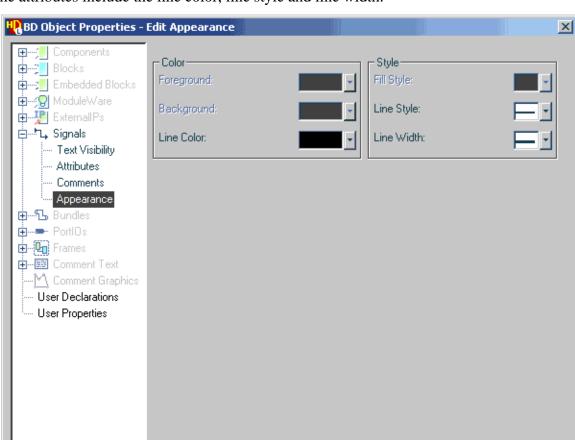

|   | Modifying Signal Appearance                             | 149 |

|   | Editing Port IOs Properties                             | -   |

|   | Editing Port IO Toyt Visibility                         | 150 |

|   | Editing Port IO Text Visibility                         |     |

|   | Editing Frame Properties                                | 151 |

|   |                                                         | 151 |

|   | Modifying Frame Appearance                              | 151 |

|   | Editing Comment Text Appearance                         | 152 |

|   | Modifying Comment Text Appearance                       | 152 |

|   | Modifying Comment Text Box Appearance                   | 152 |

|   | Editing Comment Graphics Properties                     | 152 |

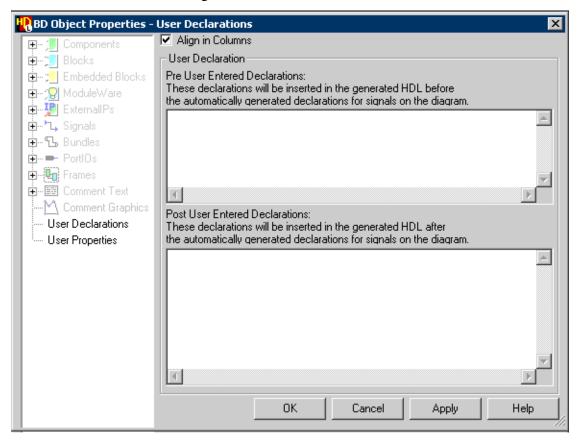

|   | Editing User Declarations                               | 153 |

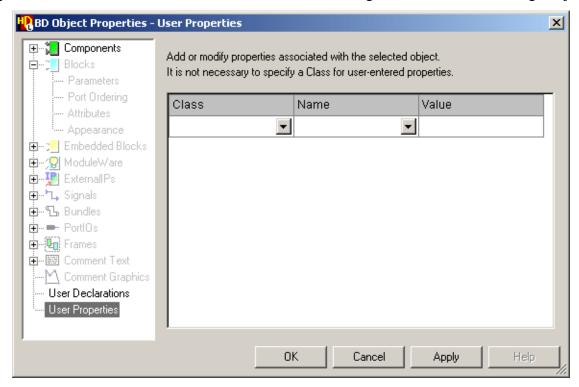

|   | Editing User Properties                                 | _   |

|   | Setting the Scope for Net Changes                       | 154 |

|   | Adding Comments to a Signal or Port Declaration         | 155 |

| ъ | Setting Attributes and Embedded Constraints             | 157 |

|   | ropagating Net Changes                                  | 158 |

|   | Inserting and Removing Nets                             | 101 |

| Ordering Port and Signal Declarations          | 163        |

|------------------------------------------------|------------|

| Adding or Removing Design Hierarchy            | 164        |

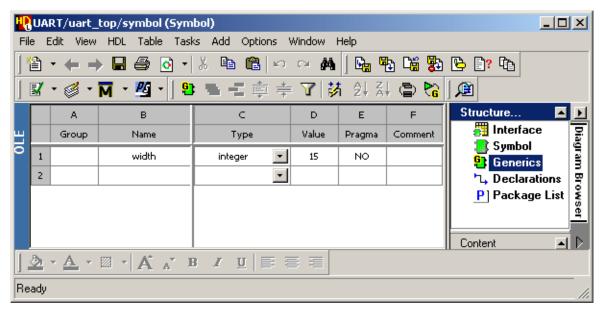

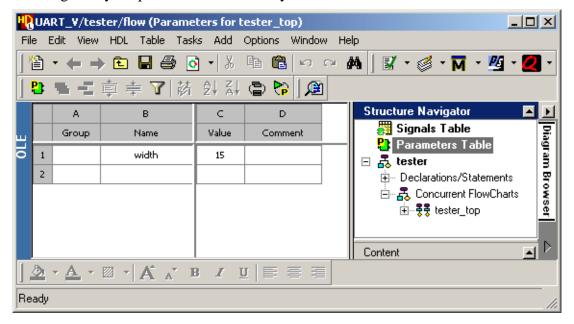

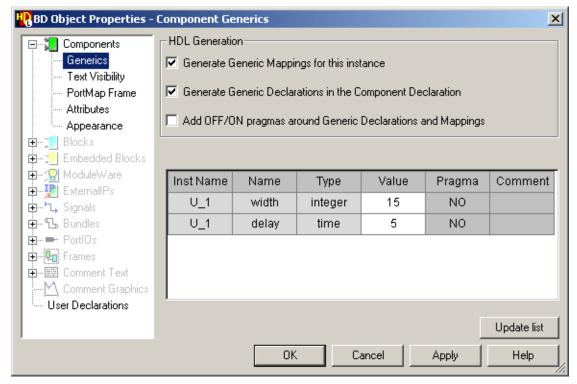

| Generics and Parameters                        | 166        |

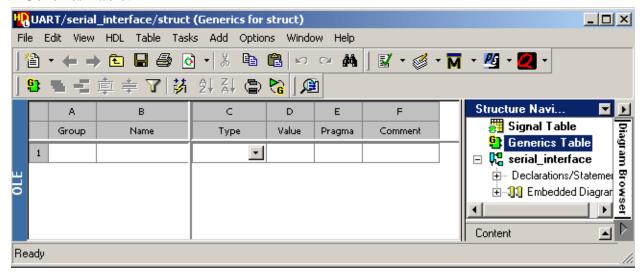

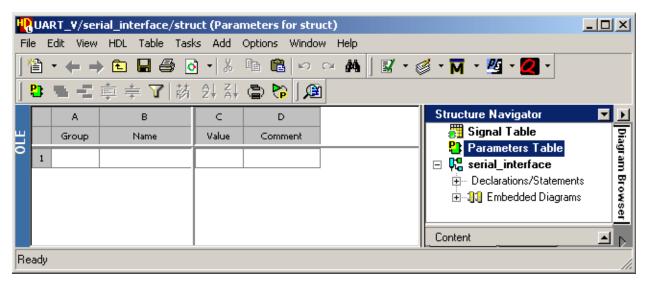

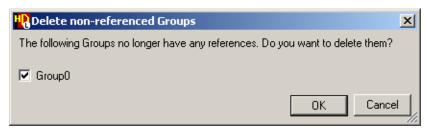

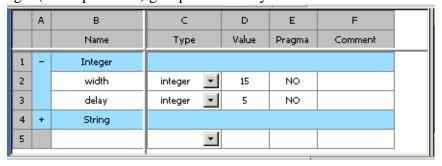

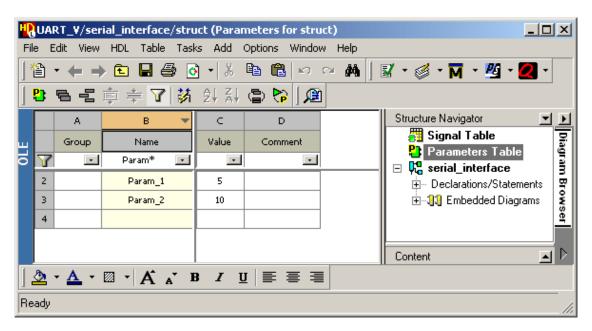

| Generics and Parameters Tables                 | 168        |

| Accessing the Generics or Parameters Table     | 168        |

| Generics Table Controls                        | 169        |

| Parameters Table Controls                      | 170        |

| Using the Generics and Parameters Table        |            |

| Related Topics                                 |            |

| Defining Generics and Parameters               |            |

| Defining Generics for Components and Blocks    | 176        |

| Defining Parameters for Components and Blocks  | 177        |

| Editing Generics and Parameters for Instances  |            |

| Editing VHDL Generic Values for Instances      | 179        |

|                                                | 181        |

| Editing Verilog Parameter Values for Instances |            |

| Generics and Parameters Synchronization        | 184        |

| Related Topics                                 | 185        |

| Opening Block and Component Views              | 185        |

| View Initialization                            | 186        |

| Setting the Default View                       |            |

| Mixed Language Designs                         |            |

| VHDL Instantiation of Verilog Components       |            |

| Verilog Instantiation of VHDL Components       | 189        |

|                                                |            |

| Chapter 4                                      | 101        |

| Block Diagram Editor                           |            |

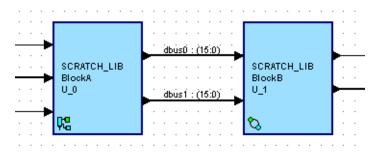

| Block Diagrams                                 | 192        |

| Block Diagram Notation                         | 193        |

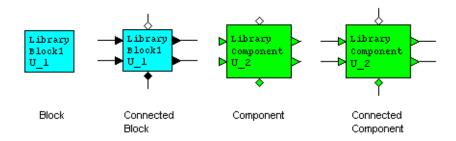

| Blocks and Components                          | 194        |

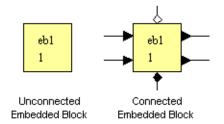

| Embedded Blocks and Embedded Views             | 195        |

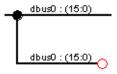

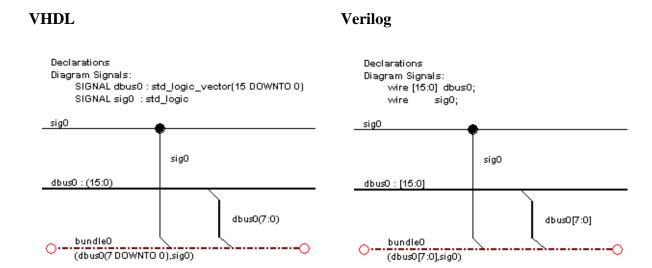

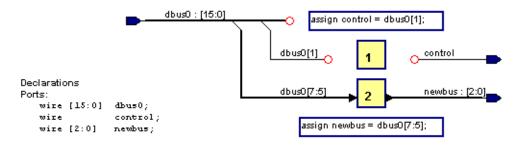

| Signals, Buses and Bundles                     | 196        |

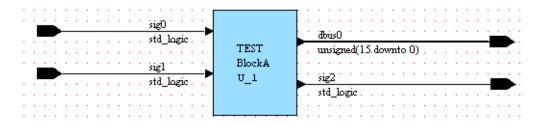

| Ports and Signals                              | 197        |

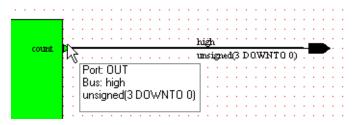

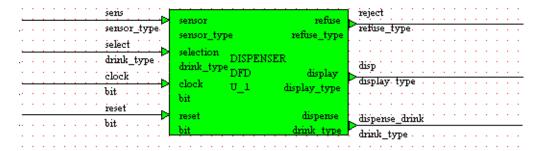

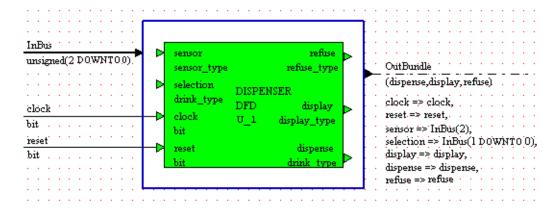

| Changing the Display of Port Properties        | 198        |

| Changing the Display of Signal Properties      |            |

| Block Diagram Editor Toolbar                   | 203        |

| Adding Nets on a Block Diagram                 | 204        |

| Routing Nets                                   | 204        |

| Adding a Signal or Bus on a Block Diagram      | 205        |

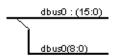

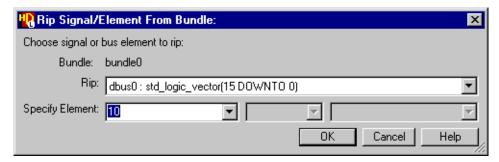

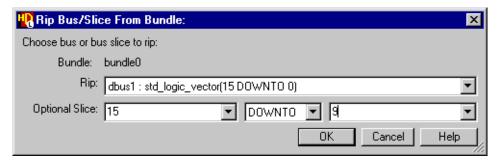

| Ripping from a Bus                             | 207        |

| Adding Signal Stubs on a Block Diagram         | 209        |

| Adding a Bundle on a Block Diagram             | 209        |

| Adding Signals to a Bundle                     | 210        |

|                                                | 210        |

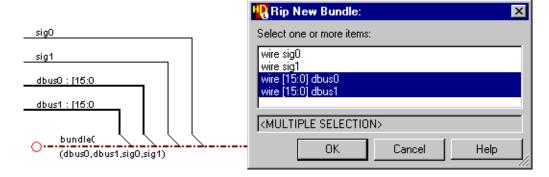

| Ripping from a Bundle                          |            |

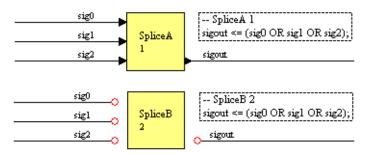

| Using HDL Text to Combine or Split Signals     | つ1つ        |

| Adding Ports on a Block Diagram                | 212        |

|                                                | 212        |

| Adding Ports to Existing Nets                  | 212<br>213 |

|                                                | 212        |

| Rotating a Port                                           | . 214 |

|-----------------------------------------------------------|-------|

| Rotating Signal Names                                     |       |

| Adding a Global Connector on a Block Diagram              | . 214 |

| Connecting Overlapping Nets                               | . 214 |

| Connecting Nets to a Block or Component                   | . 215 |

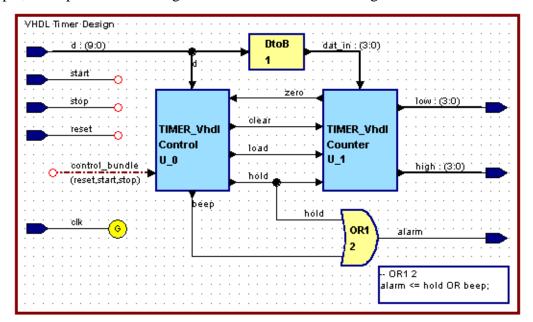

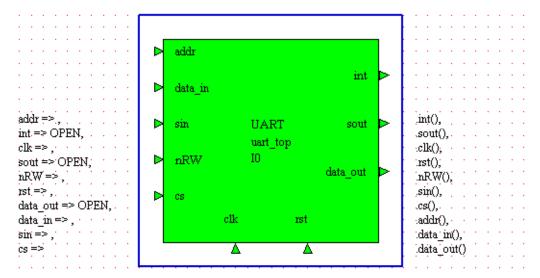

| VHDL Port Mapping                                         | . 216 |

| Connecting Nets to a Port Map Frame                       | . 217 |

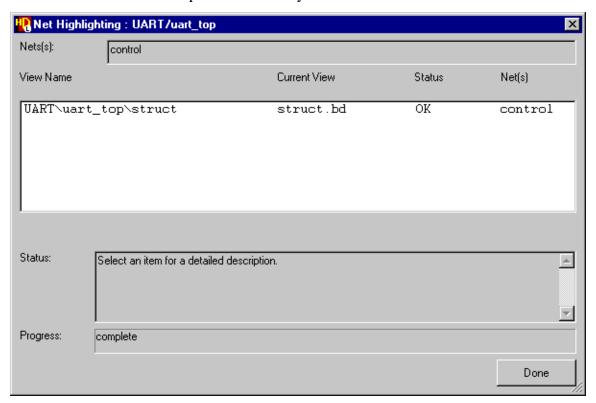

| Highlighting a Net on a Block Diagram                     | . 217 |

| Logic Shape Notation                                      |       |

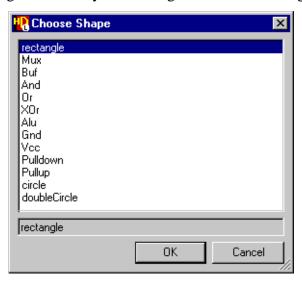

| Changing the Shape of a Block or Component                | . 220 |

| Choosing a Standard Shape                                 | . 221 |

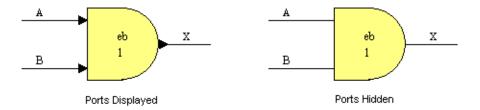

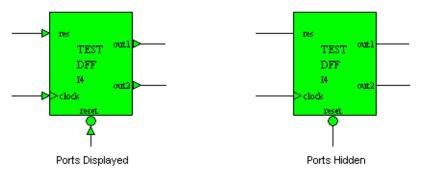

| Hiding Ports on a Block or Component                      | . 222 |

| Indicating Not or Clocked Ports                           |       |

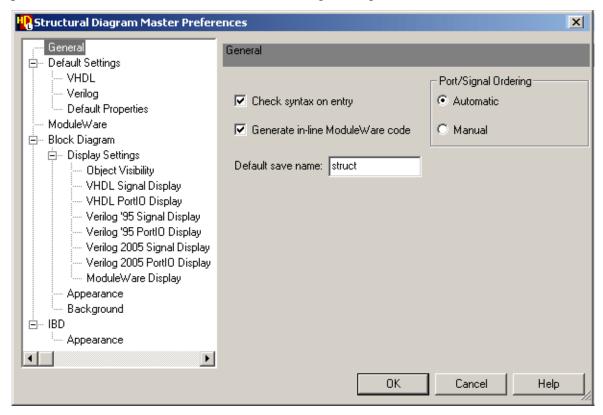

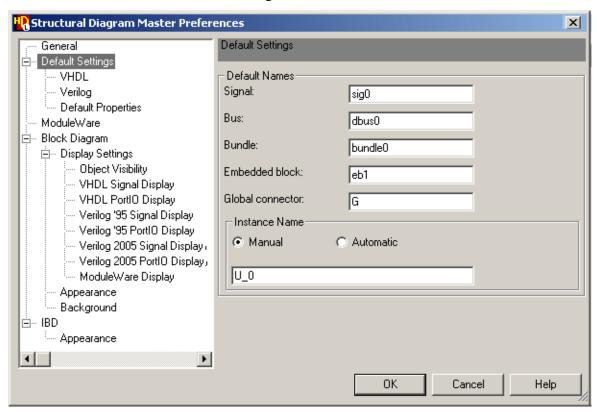

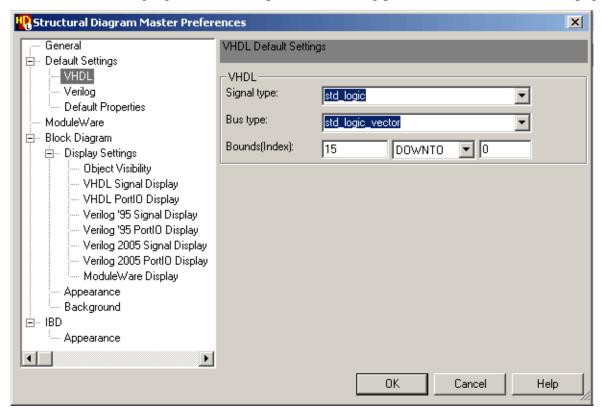

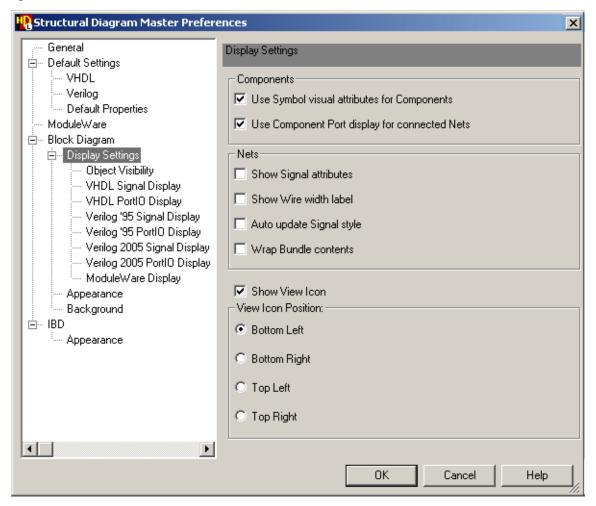

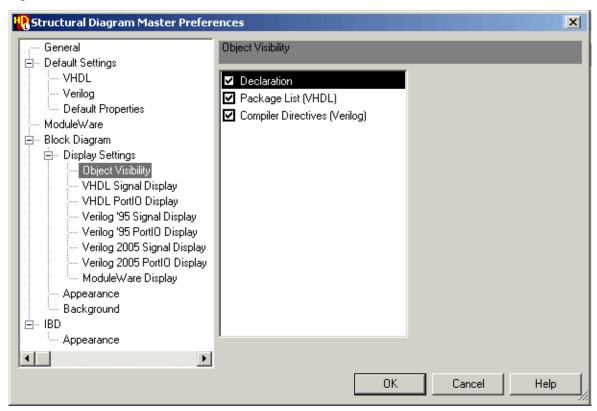

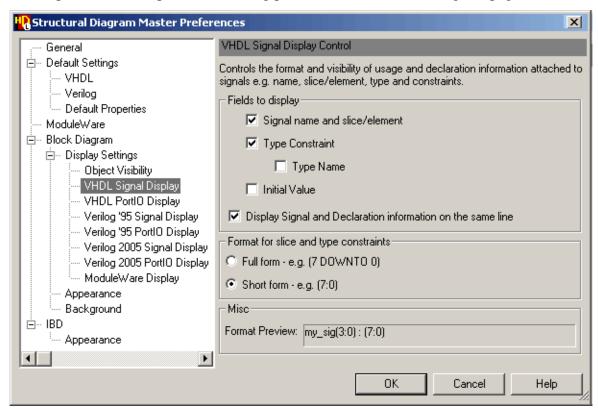

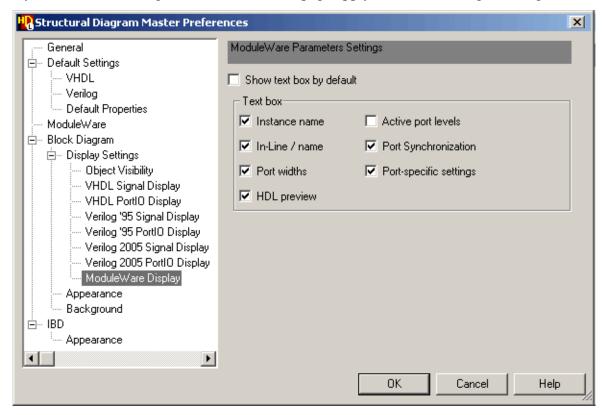

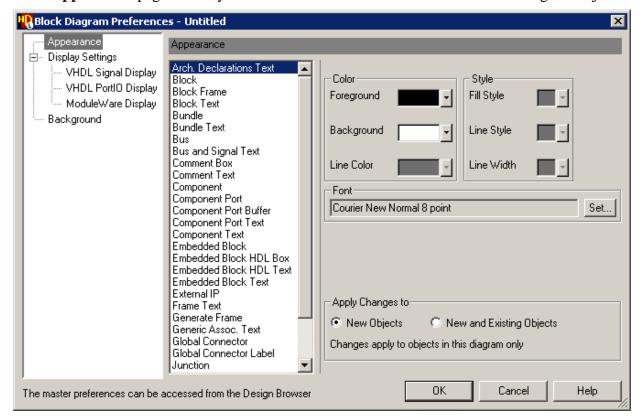

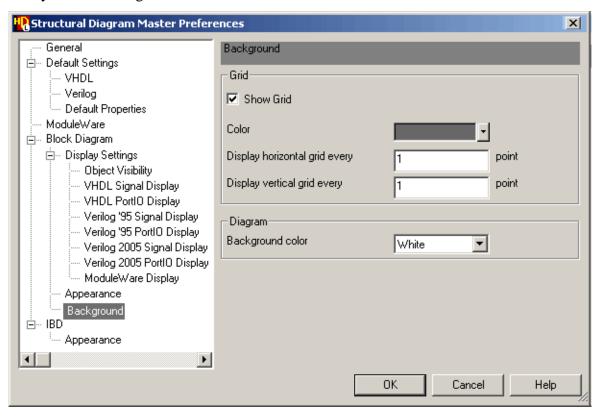

| Setting Block Diagram Preferences                         |       |

|                                                           |       |

| Chapter 5                                                 |       |

| IBD View Editor                                           | . 237 |

| Interface-Based Design                                    | . 238 |

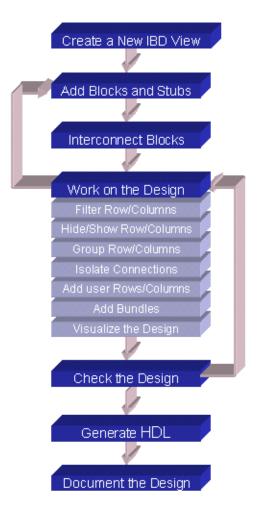

| New Design Creation Flow                                  |       |

| Code Re_Use Flow                                          |       |

| Design Assembly Flow                                      | . 240 |

| IBD Working Environment                                   |       |

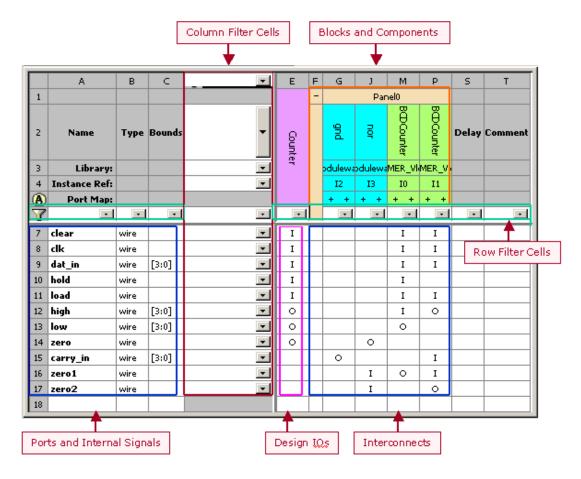

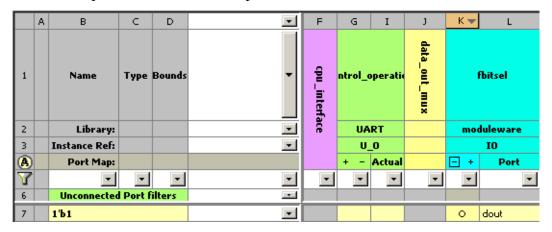

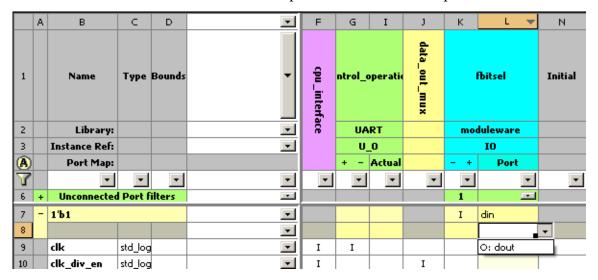

| IBD View Matrix                                           |       |

| IBD View Toolbar                                          |       |

| Getting Designs into IBD Editor                           |       |

| Working on a Previously Created HDS Design                |       |

| Creating a New Design View                                |       |

| Adding Design Elements                                    |       |

| Adding Components                                         |       |

| Adding Blocks                                             |       |

| Adding Embedded Blocks                                    |       |

| Adding Nets                                               |       |

| Adding a Signal or Bus.                                   |       |

| Adding Ports                                              |       |

| Adding a Net Slice                                        |       |

| Adding Generate Frames                                    |       |

| Using Generate Frames for Repeating Instances             |       |

| Using Generate Frames for Repeating Structures            | . 250 |

| Using Generate Frames for Conditional Structures          | . 250 |

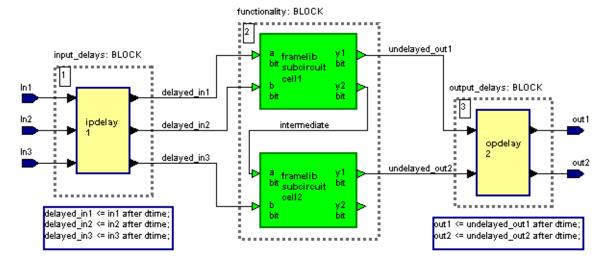

| Using a BLOCK Generate Frame.                             |       |

| Connecting Design Elements.                               |       |

| Connecting Nets to Component Ports.                       |       |

| Connecting Existing Nets: Net_Centric_Connection Approach |       |

| Connecting Ports: Port_Centric_Connection Approach        |       |

| Mapping Expressions or Function Calls to Component Ports  | . 251 |

| Another Port_Centric_Connection Convention                |       |

|                                                           |       |

| Organizing View Layout                                    |       |

| LADARURIE ARU CURAUSIRE IDD VICWS                         | . ∠၁၁ |

| Moving Rows and Columns in an IBD View           | 256 |

|--------------------------------------------------|-----|

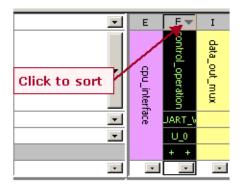

| Sorting Rows and Columns in an IBD View          |     |

| Grouping IBD Rows and Columns                    |     |

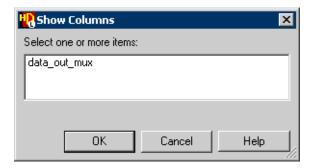

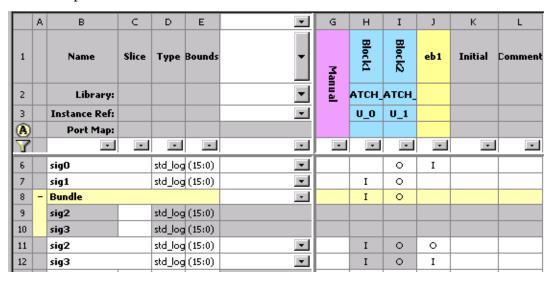

| Showing/Hiding Columns in an IBD View            |     |

| Adding Bundles to your IBD view                  | 257 |

| Adding Net/Component Comments                    | 258 |

| Adding Property Columns/Rows                     | 258 |

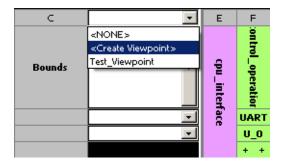

| Creating Filtered Views of the Design            |     |

| Defining Filter Settings and Logic               | 259 |

| Creating Persistent Subset Views of the Design   | 259 |

| Pruning IBD Designs                              | 261 |

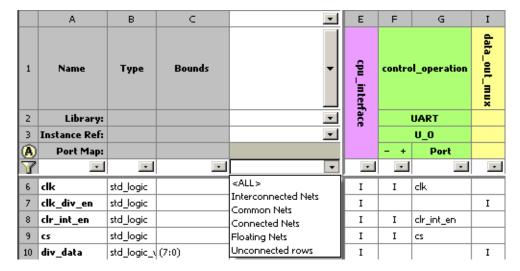

| Filtering Nets in an IBD view                    |     |

| Filtering Components in an IBD View              | 262 |

| Managing Design Hierarchy                        | 263 |

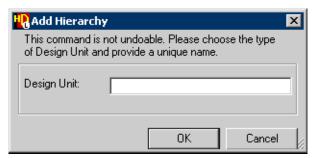

| Adding a Level of Hierarchy                      | 263 |

| Flattening Design Hierarchy                      | 264 |

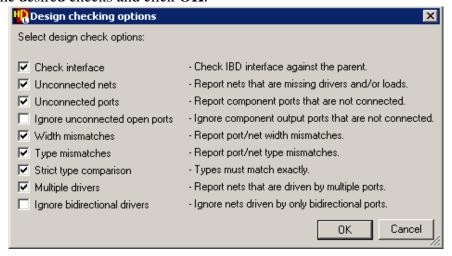

| Checking a Design in IBD Editor                  |     |

| Generating HDL from IBD views                    | 265 |

| Controlling the Generated HDL Code               | 265 |

| Setting Generation Order                         | 265 |

| Setting the Style of the VHDL or Verilog code    | 266 |

| Setting the Generation Hierarchy Level           | 266 |

| Enforcing Generation                             | 266 |

| Cross Referencing Generation Errors              | 267 |

| Setting a Black Box for Synthesis                | 267 |

| Documenting IBD Design Views                     | 268 |

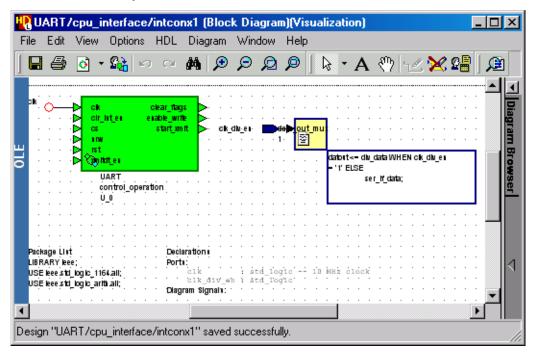

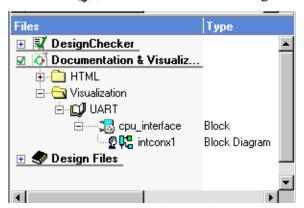

| Creating Visualization Views                     | 268 |

| Exporting to HTML                                | 269 |

| Exporting to TSV or CSV Files                    | 269 |

| Compiler Directives                              | 270 |

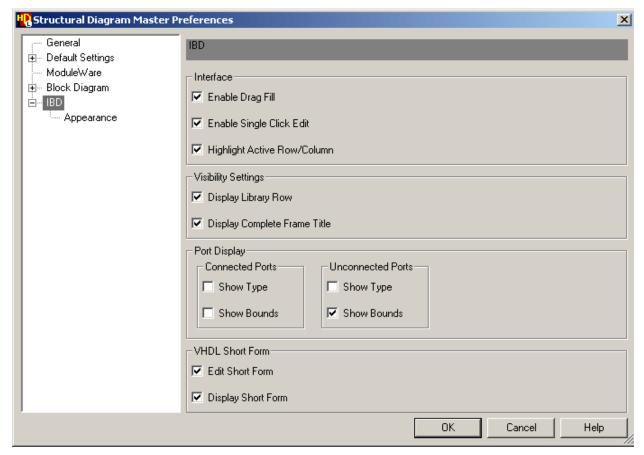

| Setting IBD Preferences                          | 270 |

|                                                  |     |

| Chapter 6                                        |     |

| Port Map and Generate Frames                     | 273 |

| Port Map Frames                                  | 273 |

| Adding a Port Map Frame                          | 273 |

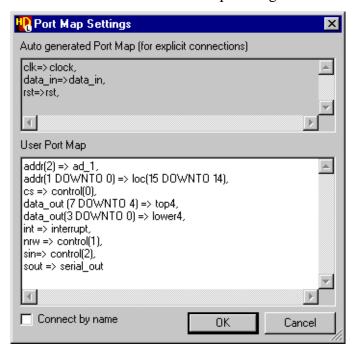

| Editing a Port Map                               | 274 |

| VHDL Port Map Example                            | 275 |

| Verilog Port Map Example                         | 276 |

| Generate Frames                                  | 277 |

| Adding a Generate Frame                          | 278 |

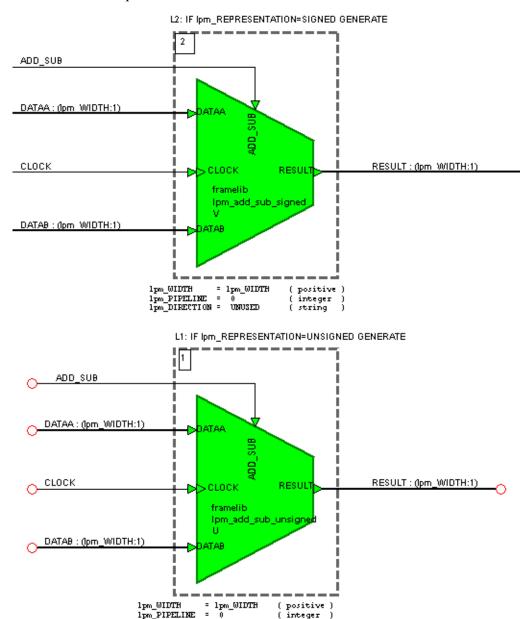

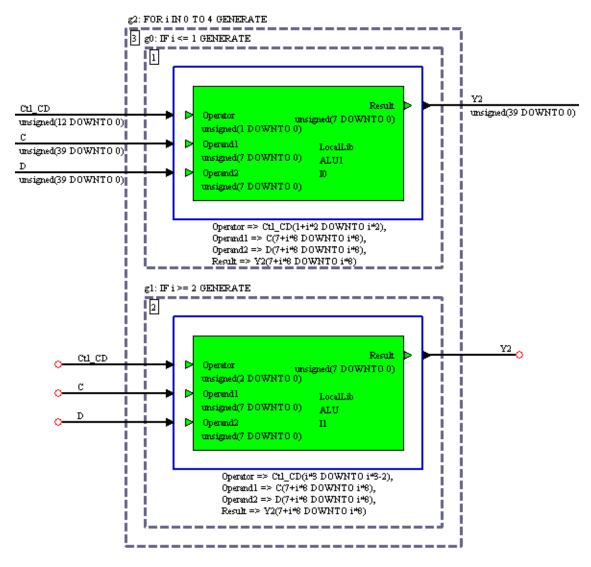

| Using Generate Frames for Repeating Instances    | 279 |

| Using Generate Frames for Repeating Structures   | 281 |

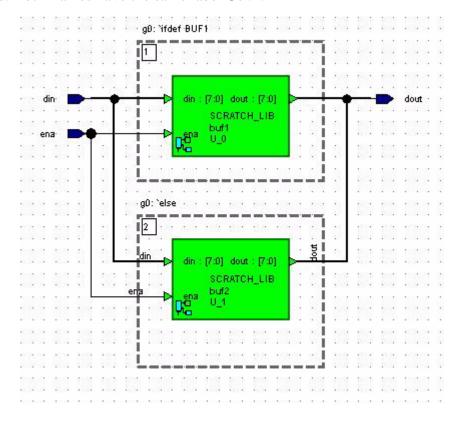

| Using Generate Frames for Conditional Structures | 282 |

| Using a BLOCK Generate Frame                     | 286 |

| Using Nested Generate Frames                     | 288 |

| Editing Generate Frame Properties                | 292 |

| Chapter 7                             |     |

|---------------------------------------|-----|

|                                       | 295 |

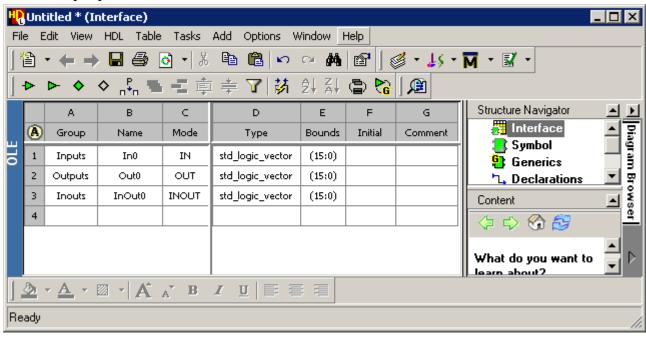

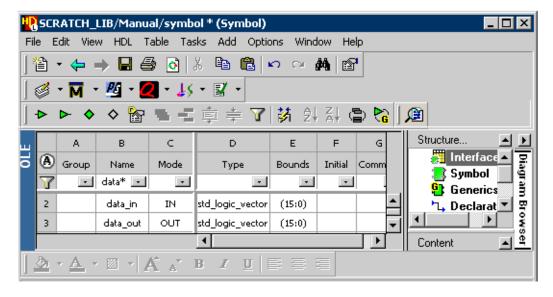

| Opening a Component Interface         | 295 |

|                                       | 296 |

| J                                     | 297 |

|                                       | 298 |

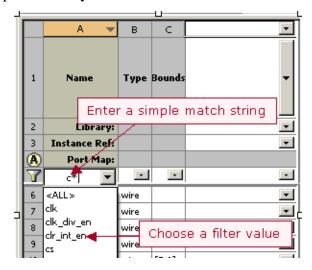

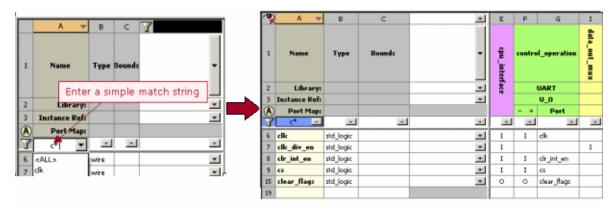

| Filtering Columns                     | 299 |

| Tabular IO Toolbar                    | 300 |

| Sorting the Rows in a Tabular IO View | 301 |

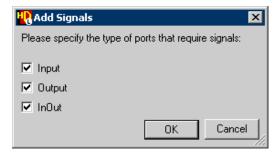

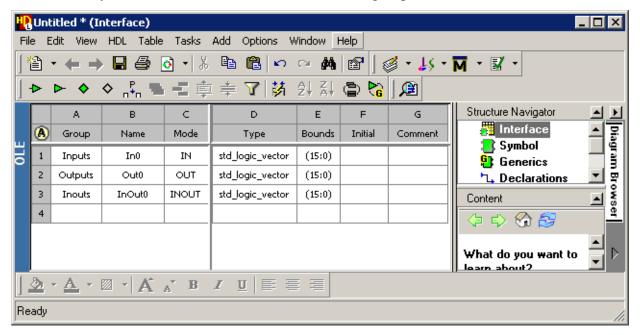

| Adding Ports in the Tabular IO View   | 301 |

| Grouping Port Rows                    | 302 |

|                                       | 304 |

|                                       | 305 |

|                                       | 305 |

|                                       | 306 |

|                                       | 307 |

| E                                     | 308 |

| $\mathcal{C}$                         | 309 |

|                                       | 310 |

|                                       | 310 |

| $\mathcal{C}$                         | 311 |

|                                       | 311 |

| $\mathcal{C}^{-1}$                    | 312 |

| $\mathcal{C}$                         | 314 |

| $\mathcal{C}^{-1}$                    | 314 |

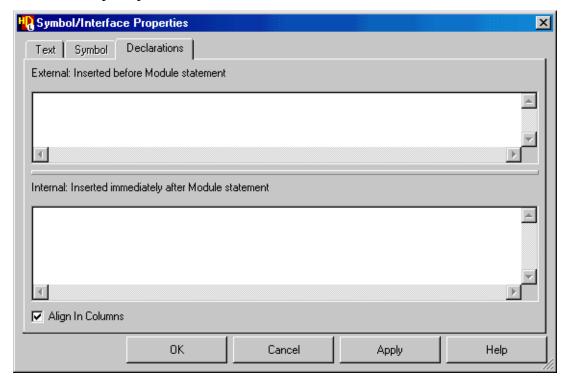

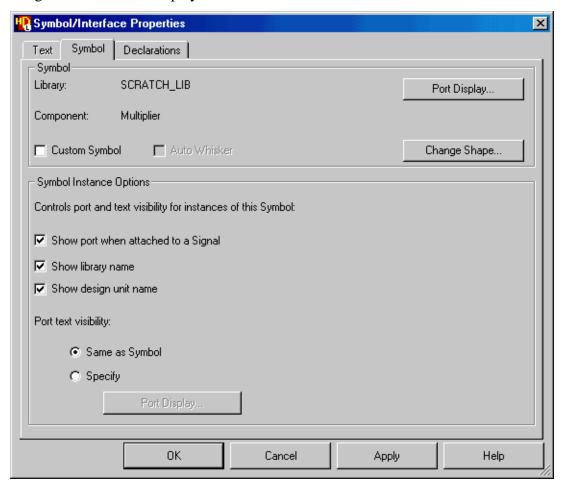

| Editing Symbol Body Properties        | 317 |

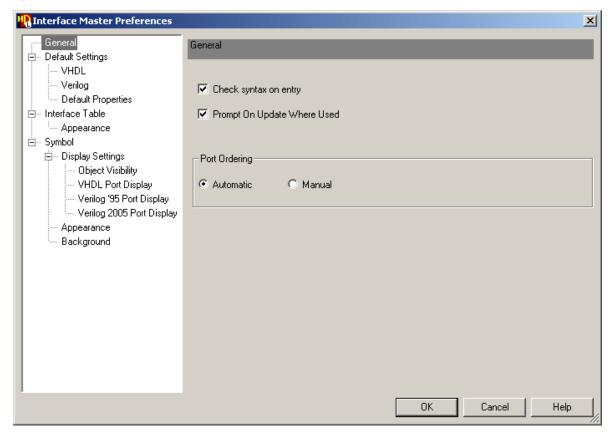

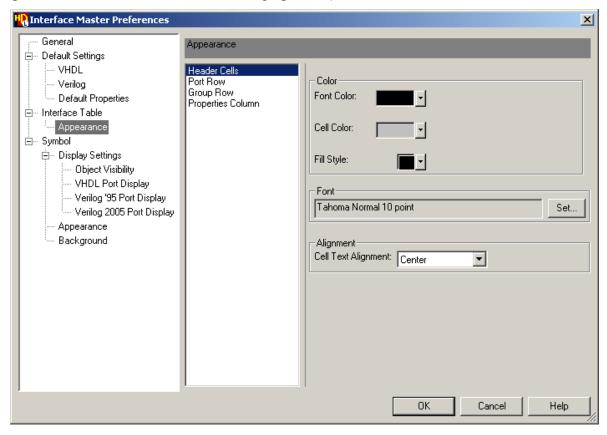

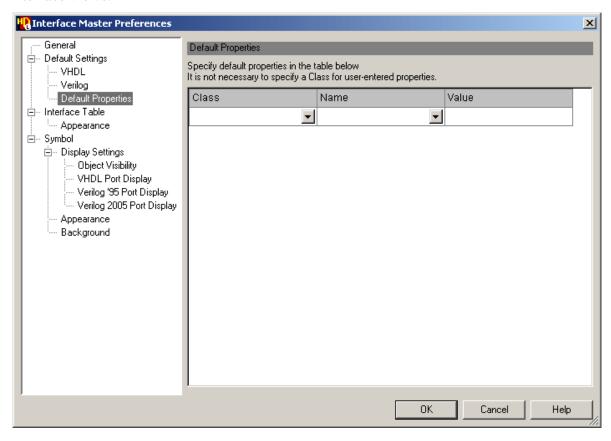

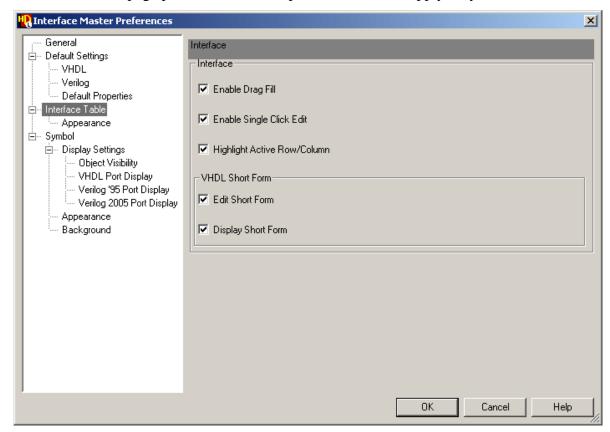

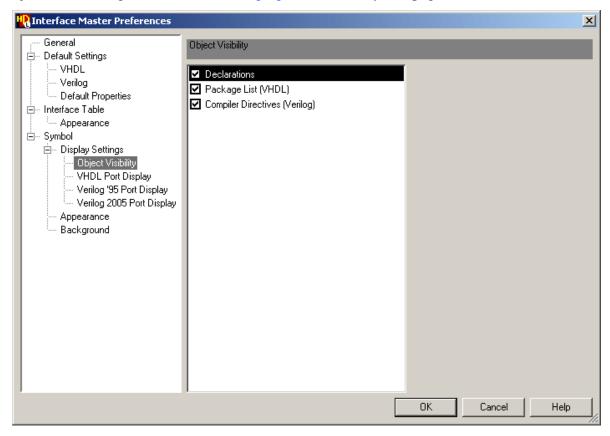

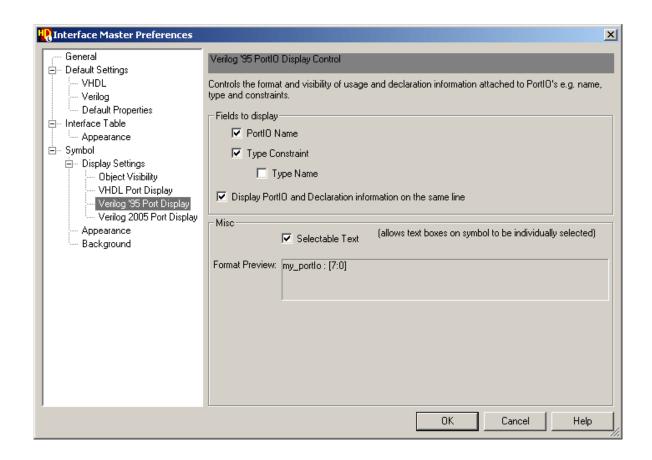

| Setting interface Freferences         | 317 |

| Chapter 8                             |     |

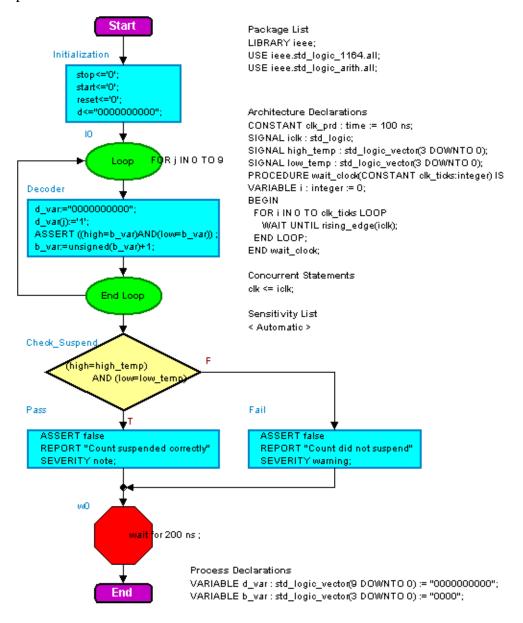

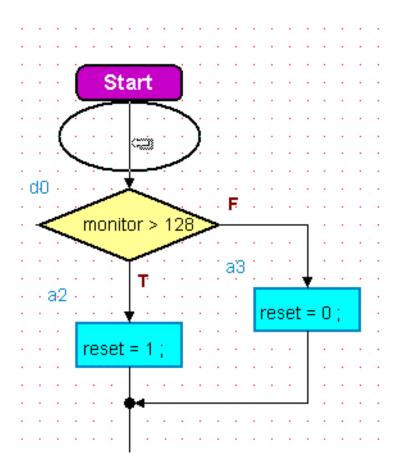

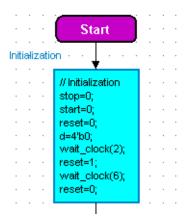

| Flow Chart Editor                     | 329 |

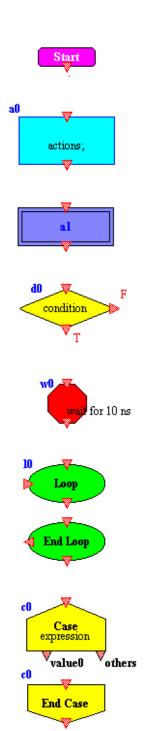

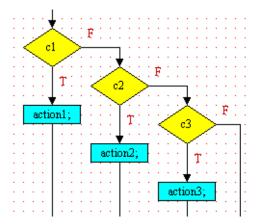

| Flow Chart Notation                   | 330 |

|                                       | 332 |

|                                       | 333 |

|                                       | 335 |

| Adding an Action Box                  | 336 |

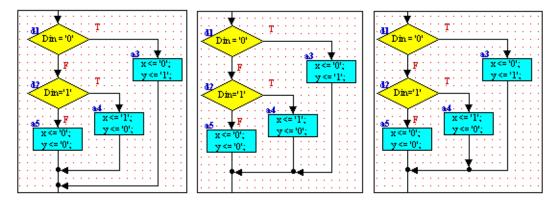

| Adding a Decision Box                 | 337 |

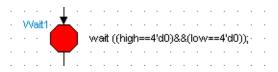

| Adding a Wait Box                     | 338 |

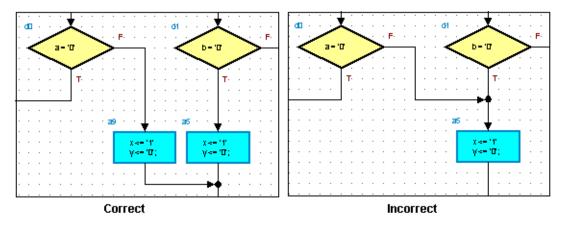

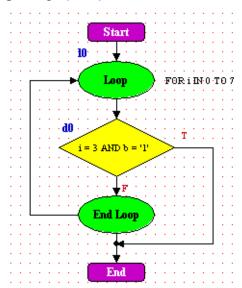

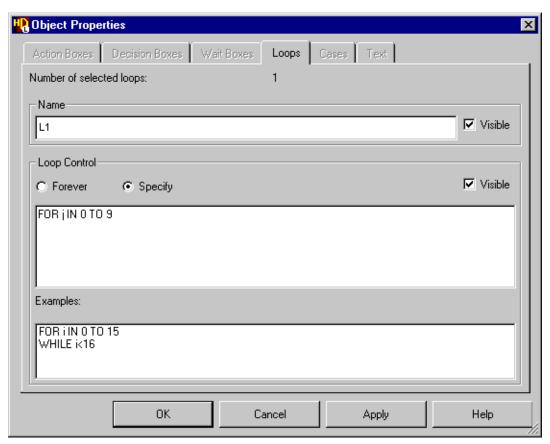

| Adding a Loop                         | 338 |

| Breaking Out of a Loop                | 339 |

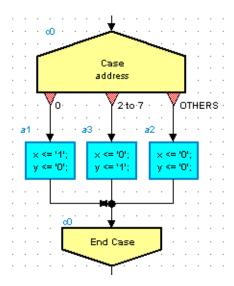

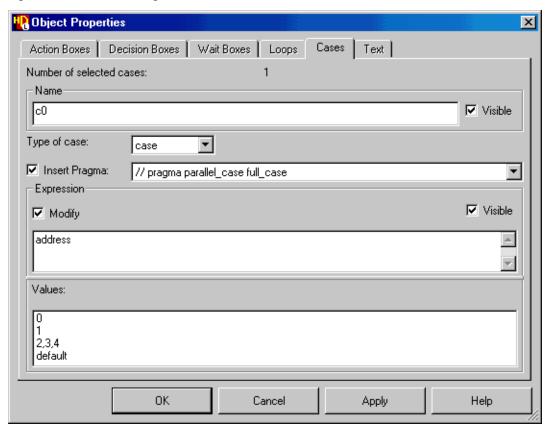

| Adding a Case Box                     | 339 |

| Adding a Flow                         | 341 |

| Adding an End Point                   | 342 |

| Adding Other Objects on a Flow Chart  | 342 |

| Hierarchical Flow Charts              | 342 |

| Concurrent Flow Charts                | 344 |

| Adding a Concurrent Flow Chart        | 345 |

| Opening a Concurrent Flow Chart       | 345 |

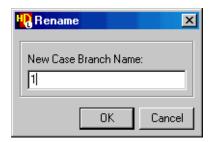

| Renaming a Concurrent Flow Chart      | 345 |

| Deleting a Concurrent Flow Chart            | 346 |

|---------------------------------------------|-----|

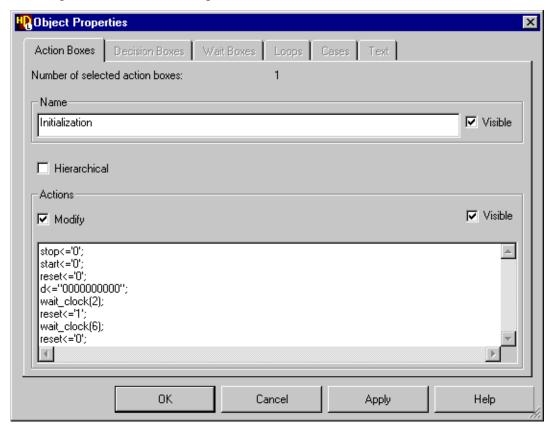

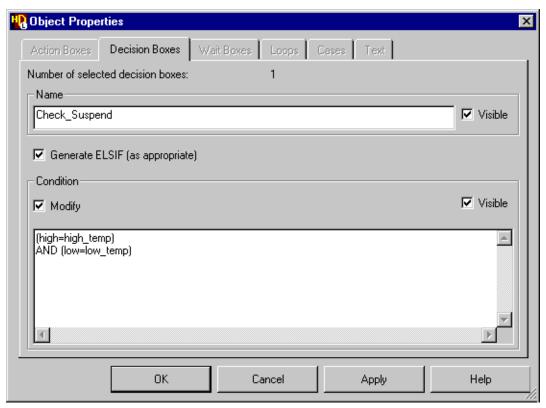

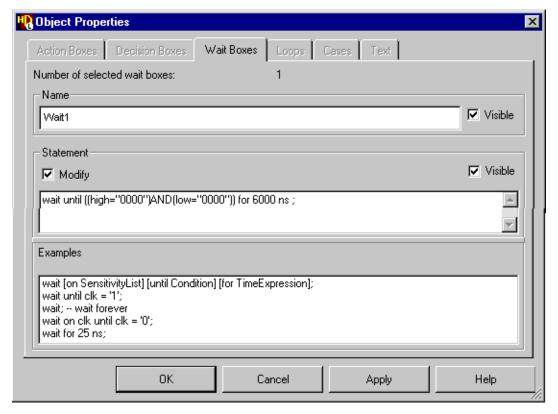

| Editing Flow Chart Object Properties        | 346 |

| Editing Action Box Object Properties        | 346 |

|                                             | 348 |

| Editing Wait Box Object Properties          | 350 |

|                                             | 352 |

| Editing Case Object Properties              | 353 |

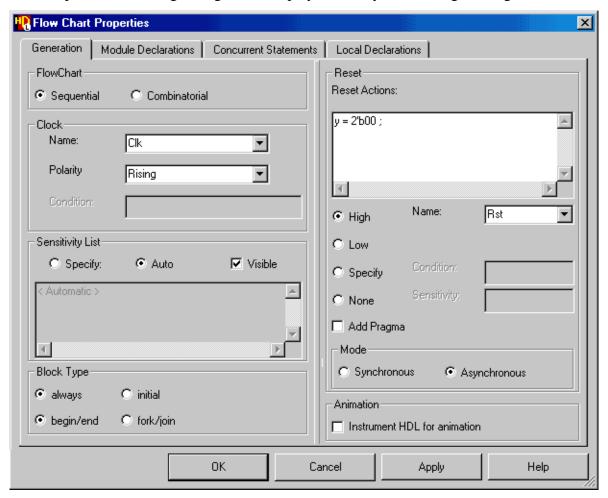

| Setting Flow Chart Properties               | 354 |

| Setting Flow Chart Generation Properties    | 355 |

|                                             | 356 |

| Clock Signal                                | 357 |

| Reset Signal                                | 357 |

| Sensitivity List                            | 357 |

| Block Type                                  | 358 |

| Animation                                   | 358 |

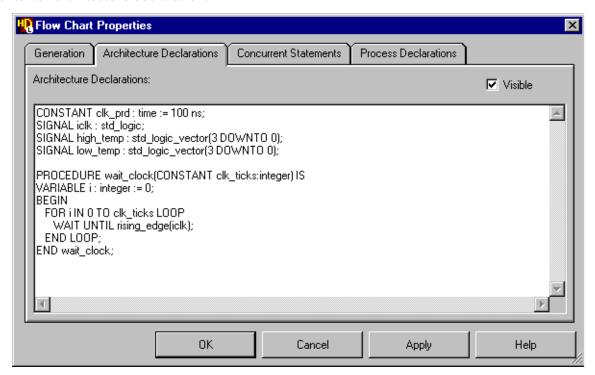

| Editing Architecture or Module Declarations | 359 |

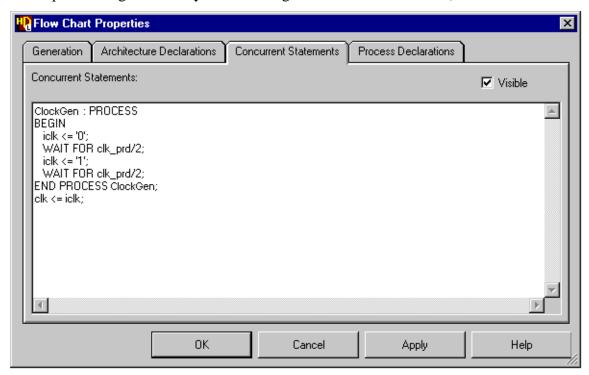

| Editing Concurrent Statements               | 360 |

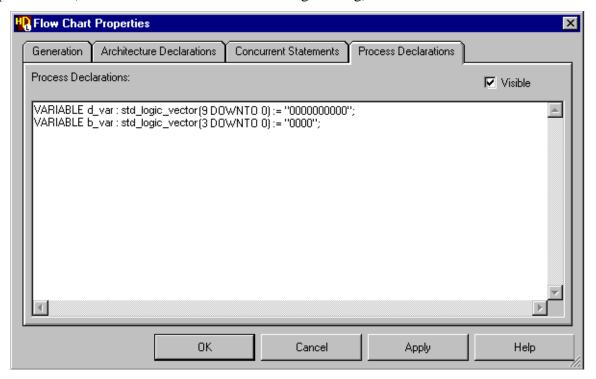

| Editing Process or Local Declarations       | 362 |

|                                             | 363 |

|                                             |     |

| Chapter 9                                   |     |

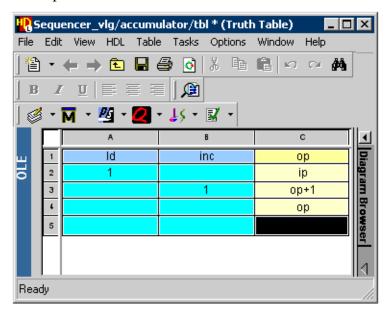

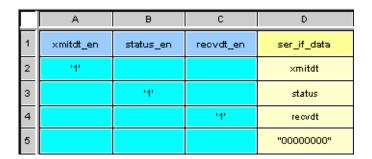

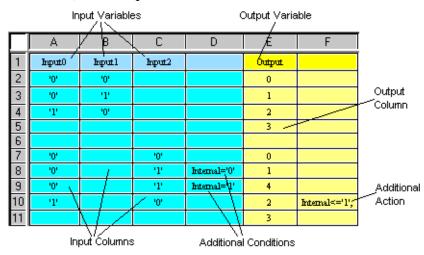

| Truth Table Editor                          | 367 |

| Truth Table Notation                        | 369 |

| Truth Table Toolbars                        | 370 |

|                                             | 370 |

| Comparison Operators                        | 370 |

|                                             | 371 |

|                                             |     |

|                                             | 371 |

|                                             | 372 |

|                                             | 373 |

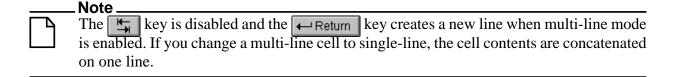

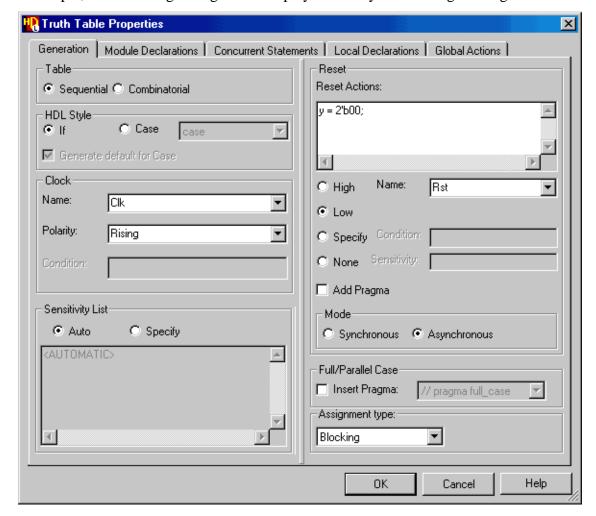

| HDL Style                                   | 373 |

| Clock Signal                                | 374 |

| Reset Signal                                |     |

|                                             | 375 |

| Full/Parallel Case                          | 375 |

| Assignment Type                             | 375 |

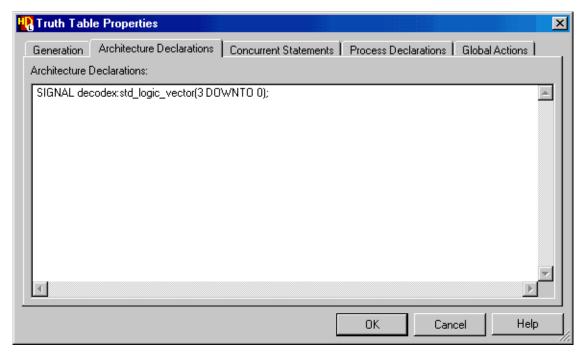

| Editing Architecture or Module Declarations | 376 |

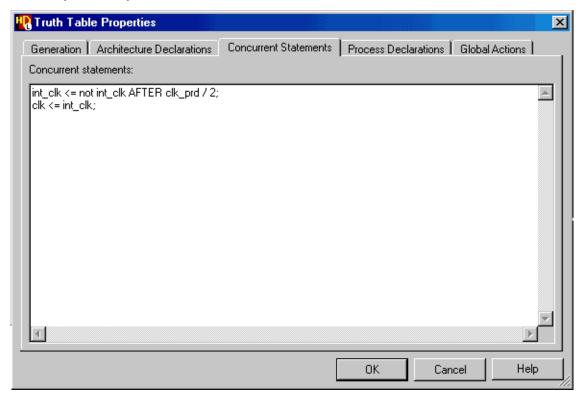

| Editing Concurrent Statements               | 377 |

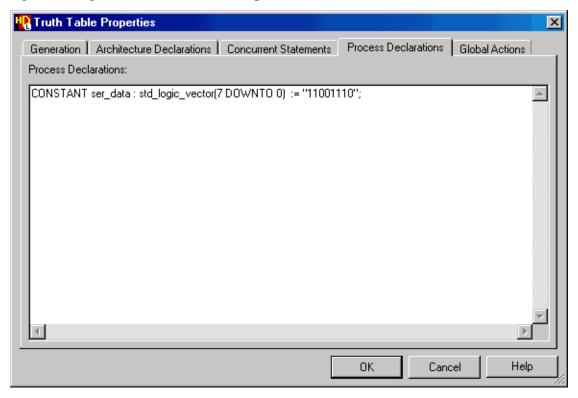

| Editing Process or Local Declarations       | 377 |

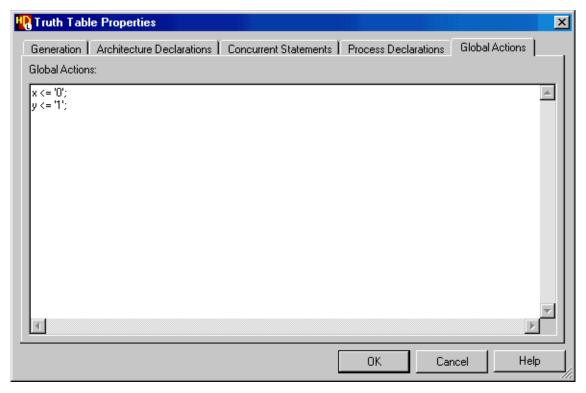

| Editing Global Actions                      | 378 |

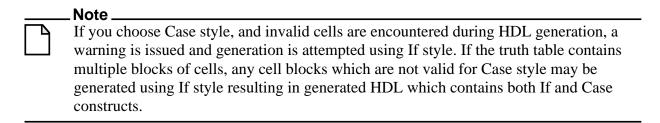

| Case and IF Style Truth Tables              | 379 |

| Case Style with a Single Input Expression   | 380 |

| Case Style with Multiple Input Expressions  | 380 |

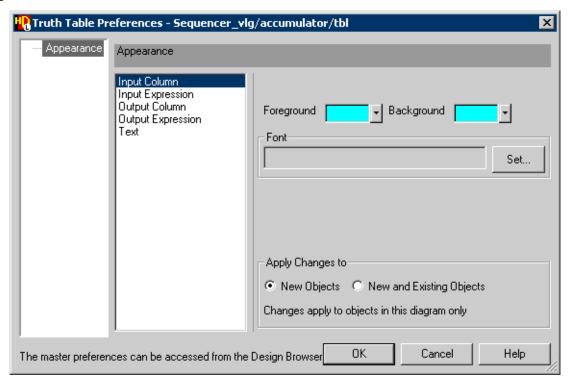

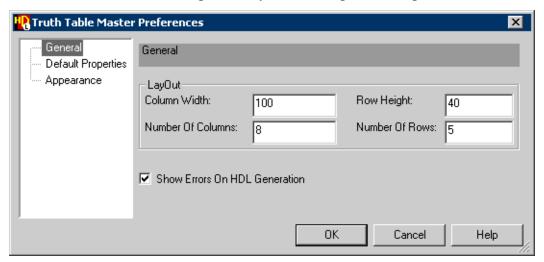

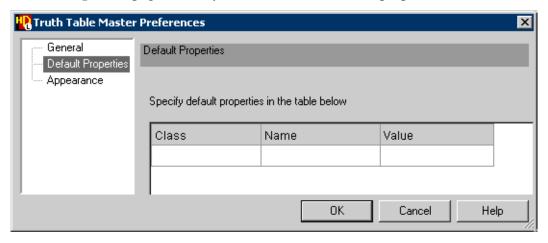

| Setting Truth Table Preferences             | 381 |

| Chapter 10                                  |            |

|---------------------------------------------|------------|

| Graphical Rendering                         | 385        |

| Design Extraction                           | 385        |

| Recovering Design Structure                 | 386        |

| Recovering Verilog Parameters               | 388        |

| Recovering State Machines                   | 388        |

| Recognizing State Machines                  | 389        |

| Recovering Flow Charts                      | 389        |

| Incremental Recovery                        | 391        |

| Using the Convert to Graphics Wizard        | 391        |

| Setting Convert to Graphics View Styles     | 392        |

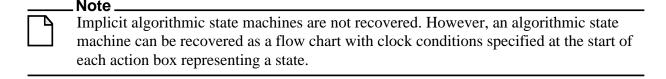

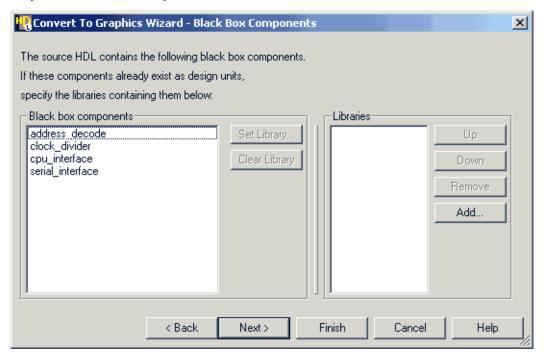

| Setting Libraries for Black Box Components  | 393        |

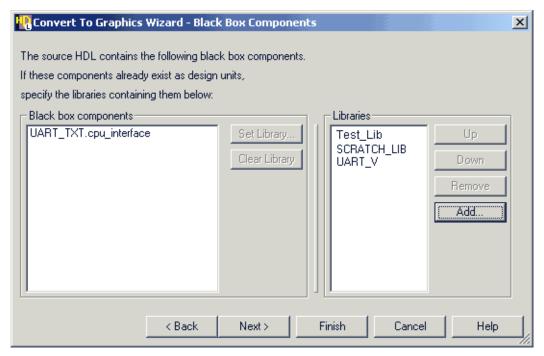

| Setting Convert to Graphics Wizard Options  | 394        |

| Setting Convert to Graphics Options         | 395        |

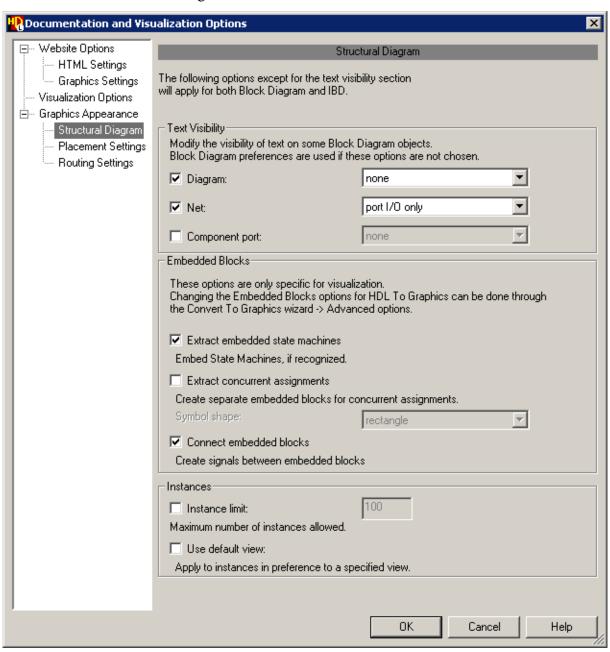

| Block Diagram Options                       | 396        |

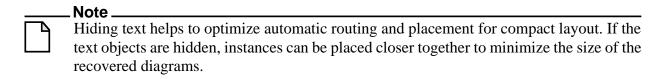

| Routing Options                             | 397        |

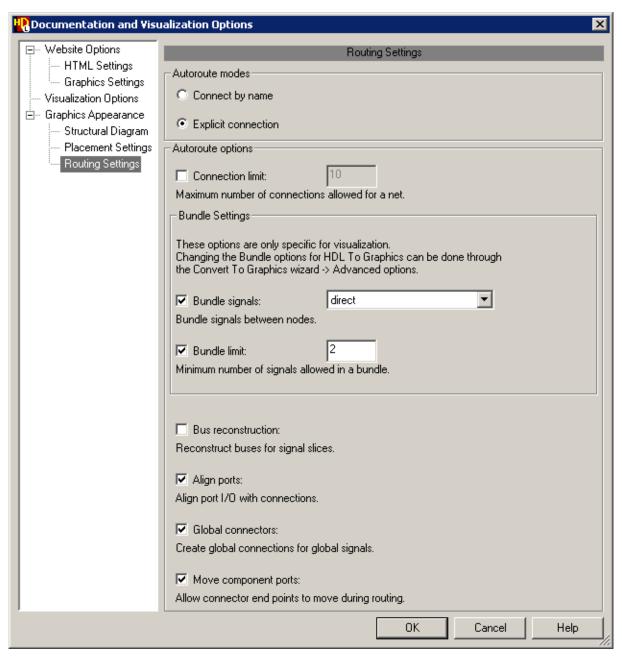

| Placement Options                           | 398        |

| Updating a Graphics View from Generated HDL | 399        |

| Visualizing HDL Text as Graphical Views     | 399        |

| Block Diagram Layout and Routing            | 399        |

| Changing the Layout of a Block Diagram      | 400        |

| Automatic Routing                           | 400        |

| Autoroute                                   | 401        |

| Autoconnect                                 | 401        |

| Autobundle                                  | 401        |

| Connect by Name                             | 402        |

| Bus Reconstruction                          | 402        |

| Chapter 11                                  |            |

| Simulation and Animation                    | 405        |

|                                             |            |

| Simulator Cross-Probing                     | 405<br>406 |

| Simulation Toolbar                          |            |

| Adding Signals to Simulator Windows         | 408<br>408 |

| Removing Signals from Simulator Windows     | 408        |

| Adding Signals to the Simulator Log         | 409        |

| Highlighting Signals in the Simulator       | 409        |

| Reporting Signal Information                | 409        |

| Enabling and Disabling Breakpoints          | 410        |

| Reporting Breakpoint Status                 | 410        |

| Adding and Removing Simulation Probes       | 411        |

| Setting Probe Properties                    | 413        |

| Forcing Signal Values                       | 413        |

| Choosing the Simulation Instance            | 414        |

| Setting the Simulator Environment.          | 415        |

| Running the Simulator                       | 416        |

| Running a Simulation                        | 416        |

| Stepping Through a Simulation               |            |

|                                             |            |

| Disalouing Cinculator Windows             | 117 |

|-------------------------------------------|-----|

| Displaying Simulator Windows              |     |

| Restarting the Simulator                  | 41/ |

| $\boldsymbol{c}$                          |     |

| Cross-Probing from ModelSim               | 418 |

| State Diagram and Flow Chart Animation    | 421 |

| Animation Toolbar                         |     |

| Enabling Data Capture                     | 423 |

| Setting the Activity Trail                | 424 |

| Graphical Highlighting                    | 425 |

| Reviewing Animation                       | 426 |

| Linking Diagrams for Animation            | 427 |

| Mixed Language Animation                  | 427 |

|                                           |     |

| Chapter 12                                |     |

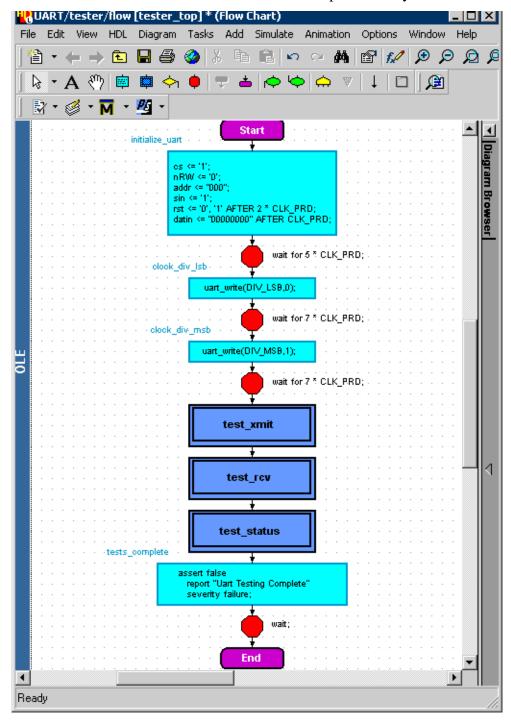

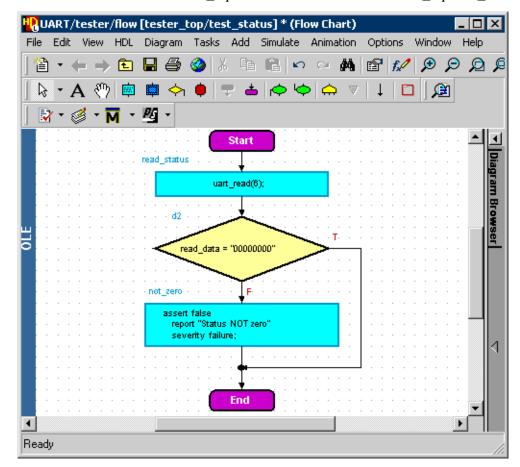

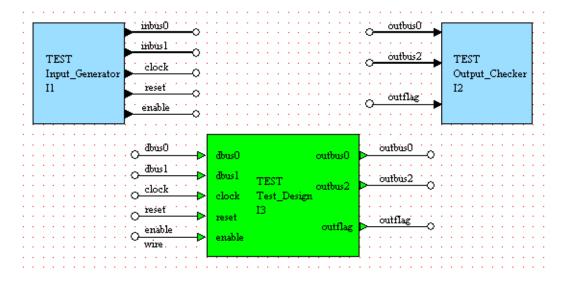

| Using a Test Bench                        | 429 |

| Test Benches                              | 429 |

|                                           | 430 |

| Defining Stimulus                         | 431 |

| Using ModuleWare Stimulus Generator Parts | 431 |

|                                           | 431 |

| Wait Statements                           | 432 |

| Loop Statements                           | 433 |

| Case Statements                           | 433 |

|                                           | 433 |

| Defining Stimulus using TextIO            | 434 |

| Defining Stimulus using a State Machine   | 436 |

| Generating a Clock using HDL Statements   | 436 |

| Analyzing Results                         | 437 |

| Re-using a Test Bench                     |     |

| Re-using a rest deficit                   | 430 |

#### Glossary

Index 465

**Index**

**End-User License Agreement**

# **List of Tables**

| Table 1-1. Standard Toolbar                                                       | 20  |

|-----------------------------------------------------------------------------------|-----|

| Table 1-2. Format Text Toolbar                                                    | 27  |

| Table 2-1. Arrange Object Toolbar                                                 | 53  |

| Table 2-2. Text Editing Shortcuts                                                 | 60  |

| Table 2-3. Comment Graphics Toolbar                                               | 67  |

| Table 2-4. Comment Graphics Palettes                                              | 67  |

| Table 2-5. Comment Graphics Menu Commands                                         | 67  |

| Table 2-6. Appearance Toolbar                                                     | 79  |

| Table 2-7. Appearance Palettes                                                    | 80  |

| Table 2-8. Structure Navigator Notation — Block Diagram                           | 87  |

| Table 2-9. Structure Navigator Notation — State Machine, ASM, Flow Chart          | 88  |

| Table 2-10. Structure Navigator Notation — Symbol                                 | 88  |

| Table 2-11. Structure Navigator Notation — Text Objects                           | 89  |

| Table 2-12. Content List Notation — Block Diagram, IBD                            | 90  |

| Table 2-13. Content List Notation — Flow Chart                                    | 90  |

| Table 2-14. Content List Notation — State Diagram                                 | 91  |

| Table 2-15. Content List Notation — ASM                                           | 91  |

| Table 2-16. Flow Help Notation                                                    | 93  |

| Table 2-17. Signals Table Toolbar                                                 | 95  |

| Table 2-18. Tabular IO View Commands for Adding Port or Local Signal Declarations | 96  |

| Table 3-1. Block Diagram/ IBD Commands for Adding Blocks and Components           | 104 |

| Table 3-2. Supported Verilog2001/System Verilog 3.0 Types                         | 108 |

| Table 3-3. Generics Toolbar                                                       | 169 |

| Table 3-4. Generics Table Content                                                 | 170 |

| Table 3-5. Parameters Toolbar                                                     | 170 |

| Table 3-6. Parameters Table Content                                               | 170 |

| Table 3-7. Object Properties — Parameters Page Controls                           | 182 |

| Table 4-1. Graphical Editor and HDL Text Views Notation                           | 194 |

| Table 4-2. Block Diagram Editor Toolbar                                           | 203 |

| Table 4-3. Block Diagram Commands for Adding Nets                                 | 204 |

| Table 5-1. IBD View Toolbar                                                       | 242 |

| Table 7-1. Tabular IO Toolbar                                                     | 300 |

| Table 7-2. Tabular IO View Commands for Adding Ports                              | 301 |

| Table 7-3. Symbol Toolbar                                                         | 305 |

| Table 7-4. Symbol View Commands for Adding Ports                                  | 306 |

| Table 8-1. Flow Chart Notation                                                    | 330 |

| Table 8-2. Flow Chart Toolbar                                                     | 332 |

| Table 8-3. Verilog Declarations                                                   | 359 |

| Table 11-1. Simulation Toolbar Commands in State Diagram and Flow Chart Views     | 406 |

| Table 11-2 Simulation Toolbar Commands in Block Diagram Views                     | 407 |

#### **List of Tables**

| Table 11-3. Simulation Toolbar Additional Commands in State Diagram | 407 |

|---------------------------------------------------------------------|-----|

| Table 11-4. ModelSim Main Window Commands                           | 418 |

| Table 11-5. ModelSim Source Window Commands                         | 418 |

| Table 11-6. ModelSim Wave Window Commands                           | 418 |

| Table 11-7. ModelSim Structure Window Commands                      | 418 |

| Table 11-8. ModelSim List Window Commands                           | 419 |

| Table 11-9. ModelSim Signals Window Commands                        | 419 |

| Table 11-10 Animation Toolbar                                       | 422 |

# **Chapter 1 Introduction**

This chapter introduces the HDL Designer Series graphical design creation editors, their basic user interface and features that are common to all of the graphical editors.

| The Design Creation Editors                         | 18 |

|-----------------------------------------------------|----|

| DesignPad Text Editor                               | 18 |

| Block Diagram and IBD View Editors                  | 18 |

| Component Interface Editor                          | 18 |

| State Diagram and Algorithmic State Machine Editors | 18 |

| Flow Chart Editor                                   | 18 |

| Truth Table Editor                                  | 19 |

| Editor Windows                                      | 19 |

| The Menu Bar                                        | 19 |

| Toolbars                                            | 20 |

| Keyboard Shortcuts                                  | 21 |

| Common Features                                     | 23 |

| Setting the Hardware Description Language           | 23 |

| Setting Package References                          | 23 |

| Setting Compiler Directives                         | 26 |

| Formatting Text                                     | 27 |

| Opening the Parent View                             | 28 |

| Using the Same Window                               | 29 |

| Saving Graphic Editor Views                         | 29 |

| Editing Object Properties                           | 32 |

| Redrawing a Window                                  | 32 |

| Undo and Redo                                       | 32 |

| Selecting Objects                                   | 33 |

| Copying and Pasting Objects                         | 34 |

| Deleting Objects                                    | 34 |

| Finding and Replacing Text Strings                  | 35 |

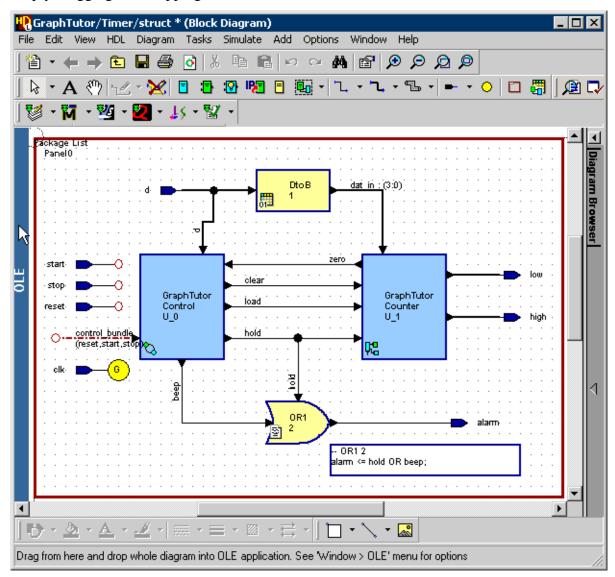

| Object Linking and Embedding                        | 38 |

| Using Drag and Drop                                 | 40 |

| Opening an OLE View                                 | 41 |

| Generating HDL                                      | 41 |

| VHDL Component Declarations                         | 44 |

| Setting a Black Box for Synthesis                   | 44 |

| Viewing the Generated HDL                           | 44 |

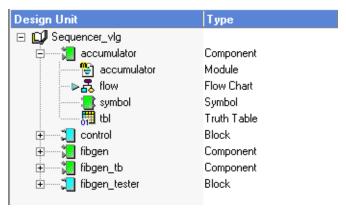

## **The Design Creation Editors**

All of the *HDL Designer Series* tools include an integrated language sensitive HDL text editor and may also include one or more *graphical editors* for opening *diagram editor* and *table editor* views.

## **DesignPad Text Editor**

The built-in *DesignPad* HDL text editor can be used can be used for editing and viewing HDL text views (or viewing the HDL generated from the graphical views). This editor is described in a separate *DesignPad Text Editor User Guide*.

#### **Block Diagram and IBD View Editors**

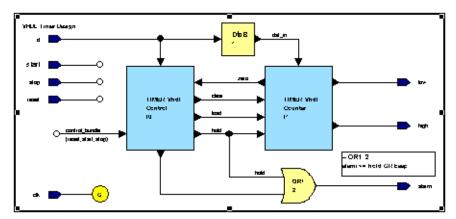

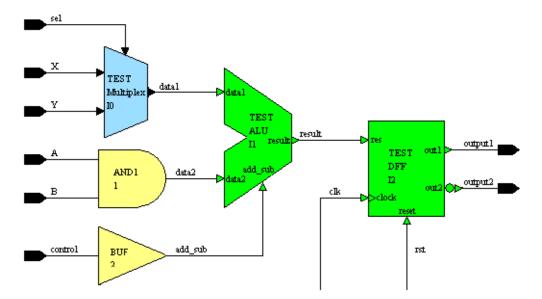

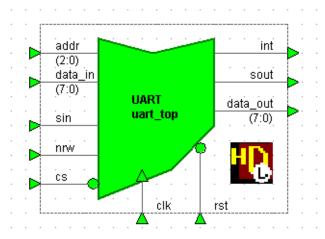

The *block diagram* editor represents the design structure by blocks and re-usable components connected by signals, buses or bundles. The tabular *IBD view* editor represents the design structure by describing the signal interfaces between the blocks and components in the design. Blocks and components can be defined using *state diagram*, *ASM chart*, *flow chart* or *truth table* or *HDL text* views and HDL generated or compiled for individual views or hierarchies.

## **Component Interface Editor**

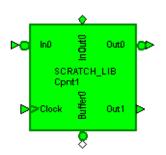

The *tabular IO* view can be used to define component interfaces in the form of a table showing its inputs and outputs. The *symbol* diagram view can be used for creating and updating the graphical symbol used for a component on a block diagram.

#### State Diagram and Algorithmic State Machine Editors

The state diagram editor can be used to describe the behavior of a block or component view as a number of states and the transitions between them. The ASM chart editor describes an algorithmic state machine (*ASM*) in terms of a sequence of operations represented by flow chart style notation. Hierarchical or concurrent state machines are supported and HDL can be generated for the active state machine. These editors are described in a separate *State Machine Editor User Manual*.

#### Flow Chart Editor

The flow chart diagram editor can be used to describe a block or component view in terms of standard flow chart symbols including action boxes, decision boxes, loops, wait and case boxes. Hierarchical or concurrent flow charts are supported and HDL can be generated for the active flow chart.

#### **Truth Table Editor**

A tabular truth table editor which can be used to represent a block or component view as a spreadsheet defining output actions as a function of input conditions or expressions. Sequential or combinatorial HDL can be generated for the truth table using Case or If-then-else style HDL.

#### **Editor Windows**

A new window is opened for each new graphical block diagram, IBD view, state diagram, ASM chart, flow chart, truth table or symbol including separate windows for hierarchical, concurrent or embedded views.

Each window can be moved, resized or iconized and has its own menu bar, one or more toolbars and a status bar. Refer to the *HDL Designer Series User Manual* for general information about the graphical user interface.

You are prompted to save any changes to the active view when you close a window which is the last open view of a diagram or table and prompted to exit from the tool if the window is the last open window.

#### The Menu Bar

The following pulldown menus are provided in most graphical editor windows although some menus or commands may not always be available:

A short message describing the associated command is displayed in the status bar when the cursor is moved over any pulldown menu item or toolbar button. When tooltips are enabled, the command name appears in a small window beneath the button if the cursor is held over a toolbar button.

Many commands are also available in a context-sensitive popup menu which is displayed when you press and release the **Right** mouse button.

All menu items can be accessed by a keyboard shortcut using the **F10** key and the underlined mnemonic letter. For example, to save the current view, you can use the keyboard shortcut: F10  $\mathbf{F10} + \mathbf{F} + \mathbf{S}$ .

There are additional keyboard shortcuts defined for standard commands (such as saving a view) using the **Ctrl** and **Shift** keys.

#### **Editor Windows**

Commands which add an object normally repeat for you to add another similar object until you select another command or use the **Right** mouse button (or the **Esc** key) to terminate the command. However, you can set a preference in the **General** tab of the Main settings dialog box to remain active or activate only once or you can toggle this mode for the current command by holding down the **Ctrl** key while selecting the button or menu option.

#### **Toolbars**

The most commonly used commands are available from toolbars. The toolbars are normally docked against the upper or lower edge of the active window but each toolbar can be moved independently to an alternative edge or allowed to float freely.

Refer to "Toolbars" in the *HDL Designer Series User Manual* for general information about the toolbars including procedures for "Docking and Undocking Toolbars".

Additional toolbars are defined for tasks, HDL tools, version management and for commands specific to each editor window. Special simulation and animation toolbars are available in the graphical editors when a supported simulator is invoked. Refer to the *HDL Designer Series User Manual* for information about the tasks, HDL tools and version management toolbars. The other toolbars which are available in each graphical editor are described later in this manual.

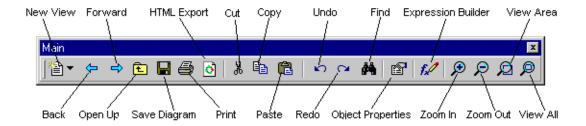

#### **Standard Toolbar**

The standard toolbar in the graphical editors typically includes the buttons shown below:

The following commands are usually available from the standard toolbar which is displayed in the block diagram, IBD view, state diagram, flow chart, truth table, tabular IO and symbol windows:

Table 1-1. Standard Toolbar

| Icon     | Description                                          |

|----------|------------------------------------------------------|

| <b>*</b> | Create a new view                                    |

| 1        | Display the previous window when in same window mode |

| 1        | Display the next window when in same window mode     |

Table 1-1. Standard Toolbar (cont.)

| Icon     | Description                                      |

|----------|--------------------------------------------------|

|          | Open the parent view                             |

|          | Save all changes made to the current view        |

|          | Print the current window                         |

| <u></u>  | Export the current view to create a website      |

| *        | Move selection to the clipboard                  |

|          | Copy selection to the clipboard                  |

|          | Paste the contents of the clipboard              |

|          | Display the Object Properties dialog box         |

| f.✓      | Build a VHDL or Verilog expression               |

| <b>N</b> | Undo the last command                            |

| 2        | Redo the last undo command                       |

| <b>#</b> | Find a specified text string                     |

| €        | Increase the magnification of the active diagram |

| P        | Decrease the magnification of the active diagram |

| Q        | View a specified diagram area                    |

| P        | View the entire diagram                          |

The button discloses a menu which allows you to choose the type of view to create. The button is available in a state diagram or flow chart window only. The , , and buttons are not available in truth table, tabular IO or IBD view windows.

## **Keyboard Shortcuts**

Many commands are also available using keyboard shortcuts. Refer to "Keyboard Shortcuts" in the *HDL Designer Series User Manual* for general information about keyboard shortcuts including menu accelerator keys, dialog box shortcuts and mouse buttons.

Refer to the **Quick Reference Index** in the Help and Manuals tab of the HDS InfoHub for lists of the keyboard shortcuts supported in each window. To open the InfoHub, select **Help and Manuals** from the **Help** menu.

#### **Mnemonic Keys**

Single-press keys (which correspond to the underlined mnemonic character in the menu command) are defined to add specific objects in diagram editor windows.

| Note                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note that mnemonic keys and shortcuts using the <b>Shift</b> key with an alphabetic character are not available in the table editors where these keys are used to enter characters in a table cell. |

#### **Command Auto-repeat**

After adding an object in a graphical editor window using a toolbar or menu command, the command normally repeats until you use the **Esc** key (or **Right** mouse button) to terminate the repeating command. However, you can set a preference for the command to **Remain active** or **Activate only once** in the **General** tab of the Main Settings dialog box which is displayed when you choose **Main** from the **Options** menu.

Alternatively, you can toggle this mode for the current command by using the **Ctrl** key. For example, you can use **Ctrl**+ to add a single panel on a diagram when auto-repeat mode is on or to add multiple panels when auto-repeat mode is off.

#### **Strokes**

You can execute a command in a diagram editor using a stroke by simply holding the **Middle** mouse button down and dragging across the window. The command to be executed is shown on the screen while the mouse button is held down and executed when you release the button.

A further set of strokes can be performed by holding down the **Shift** key while dragging the **Middle** mouse button.

You can cancel a stroke by returning to the starting position before releasing the **Middle** mouse button or by using the **Esc** key.

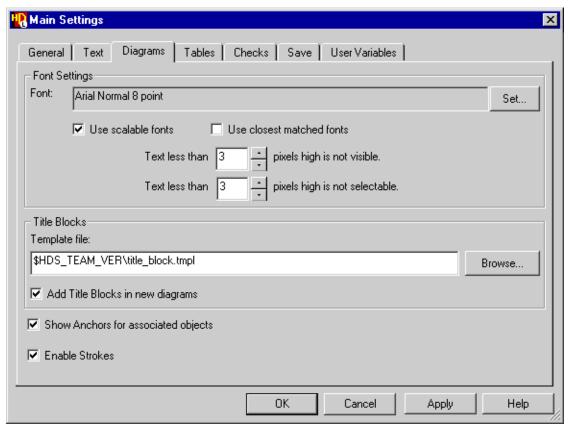

Strokes can be enabled or disabled by setting an option in the Main Settings dialog box as described "Setting Preferences for Diagram Views" on page 48.

Refer to the **Quick Reference Index** in the Help and Manuals tab of the HDS InfoHub for lists of the supported strokes. To open the InfoHub, select **Help and Manuals** from the **Help** menu.

## **Common Features**

This section describes features that are available in all of the graphical editors.

## **Setting the Hardware Description Language**

You can set the default hardware description language (VHDL or Verilog) used for new *graphical editor* views from the **General** tab of the Main Settings dialog box which can be displayed by choosing **Main** from the **Options** menu.

You can also override the default language by choosing VHDL or Verilog in the File Creation wizard when you create a new graphic editor view.

Refer to "Using the Design Content Creation Wizard" in the *HDL Designer Series User Manual* for information about creating design views.

When *VHDL* is selected, a default *package list* is shown on all graphical diagrams and VHDL syntax is used in *port* and *signal* declarations. *VHDL generics* can be defined on a *symbol* or *tabular IO* interface and individual generic values set for each instance in a *block diagram*, *IBD view*, *state diagram*, *flow chart* and *truth table*.

When *Verilog* is selected, default *compiler directives* are shown and Verilog syntax is used in *port* and *signal* declarations. *Verilog parameters* can be defined on a *symbol* or *tabular IO* interface and individual parameter values set for each instance in a *block diagram*, *IBD view*, *state diagram*, *flow chart* and *truth table*.

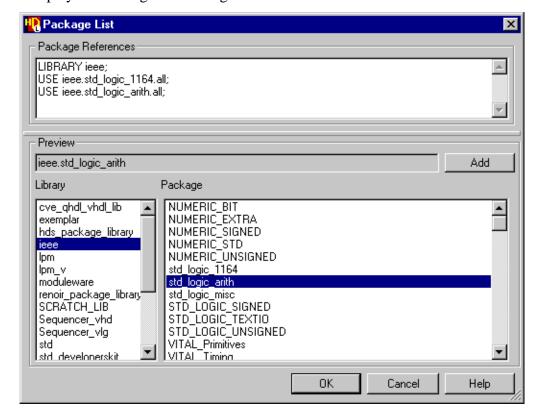

#### **Setting Package References**

When you are creating VHDL based designs, you can reference *VHDL packages* that define VHDL types subtypes, functions, procedures or constants. These packages can be referenced at any level of the design hierarchy and may be standard library packages containing pre-defined VHDL type definitions or user-defined packages in your design data libraries.

The default shared project file (*shared.hdp*) contains mappings for all the standard packages supplied with the HDL Designer Series tool.

You can also define your own standard packages or use an existing package supplied by another vendor. You can create your own local packages as HDL views stored with other block or component design unit views in a design data library or by referencing an existing external package.

You can set package references for a graphic editor view by double-clicking over the package list on a diagram, or by choosing **Package References** from the **Diagram**, **Table** or popup menu to display the Package List dialog box.

The dialog box displays any existing package references that are set for the current view (or the default packages references set in your preferences for a new view).

You can add references by selecting from the available libraries and choosing any of the packages contained in them. The supplied package libraries include all the standard types supported by Model*Sim*. Any packages contained in the currently mapped user-defined libraries will also be available.

Library and use statements for the selected package are added to the list of package references when you use the **Add** button and the updated list of references is applied to the active view when you choose the **Ok** button.

You can also add packages by entering any valid library or use statements in the list or by editing an existing library or use statement. For example, you could add a reference to the package <code>ieee.std\_logic\_unsigned</code> then replace the suffix <code>.all</code> by a function name (such as <code>CONV\_INTEGER</code>) to explicitly add a reference:

```

USE ieee.std_logic_unsigned.CONV_INTEGER

```

You can remove references from the package list by simply deleting the reference in the dialog box.

The package list can also be edited by direct text entry and may optionally include comments or pragmas entered using the standard VHDL comment characters (--). The syntax is automatically checked on entry in a diagram editor unless syntax checking has been disabled in the master diagram preferences.

## \_\_\_\_\_Note . Defau

Default package references can be set by choosing **VHDL** from the **Options** menu and selecting the **Default Package References** tab of the VHDL Options dialog box. The default packages are available on all editor views unless you have explicitly removed them.

The referenced packages are parsed during VHDL generation to verify the type definitions used in your design views.

Refer to "Setting Default Package References" in the *HDL Designer Series User Manual* for information about setting default package references. The default references are included for all views unless you have explicitly removed them.

#### **Example VHDL Package List**

The VHDL package list can be edited to include any valid LIBRARY and USE statements of the form:

```

LIBRARY <library_name>;

USE <library_name>.<package_name>.<item_name>;

USE <library_name>.<package_name>.all;

USE <library_name>.all;

```

The package list can also include pragmas or comments prefixed by the VHDL comment characters (--).

#### For example:

```

LIBRARY ieee;

-- Use the definition of std_logic from IEEE std_logic_1164

USE ieee.std_logic_1164.std_logic;

-- Use all contents of the IEEE std_logic_arith package

USE iee.std_logic_arith.all

-- Ignore the following package references for synthesis

-- pragma synthesis_off

LIBRARY std_developerskit;

USE std_developerskit.mempak.all;

-- pragma synthesis_all

LIBRARY my_parts; -- declare my library

```

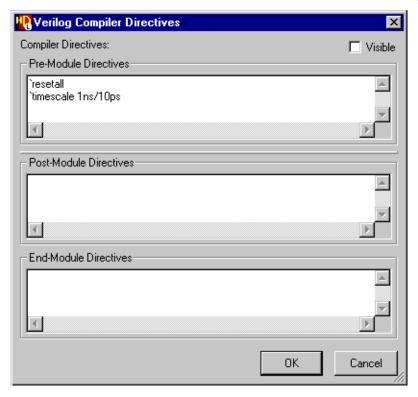

## **Setting Compiler Directives**

When you are creating Verilog based designs, you can insert compiler directives for the HDL generated from any graphic editor view.

In general, a compiler directive passes information to the Verilog compiler or other downstream tool and any directive recognized by your tools can be entered.

You can set Verilog compiler directives by double-clicking over the compiler directives list on a diagram or by choosing **Compiler Directives** from the **Diagram**, **Table** or popup menu to display the Verilog Compiler Directives dialog box listing any existing compiler directives that are set for the current view.

#### Note

The **Diagram** menu is available in a diagram editor or the **Table** editor in a table editor.

The dialog box allows you to enter pre-module directives which are included in the generated Verilog before the *module* keyword, post-module directives which are included after the *module* keyword and end-module directives which are included at the end of the Verilog module.

The compiler directives list can also be edited by direct text entry and may optionally include comments entered using the standard Verilog comment characters (//).

The directive syntax is automatically checked on entry in a diagram editor unless syntax checking has been disabled in the master diagram preferences.

Refer to "Setting Default Compiler Directives" in the *HDL Designer Series User Manual* pr for information about setting default compiler directives. The default directives are included for all views unless you have explicitly removed them.

#### **Formatting Text**

You can format text in the block diagram, state diagram, flow chart, symbol and truth table editors using the Format Text toolbar.

#### **Format Text Toolbar**

The following commands are available from the Format Text toolbar or as shortcut keys:

**Button** Shortcut **Description** Ctrl + BВ Applies bold formatting to text I Ctrl + IApplies italic formatting to text Ctrl + UUnderlines selected text U Left aligns text none Centers text in cell none Right aligns text none Increases size of the selected text none Decreases size of the selected text none

**Table 1-2. Format Text Toolbar**

If multiple cells are selected in a table, the formatting for each cell is toggled when you use the **B**, **Z** or **U** buttons.

The , and buttons are available to align the text when one or more cells are selected in a table editor view and when embedded or comment text is selected on a diagram.

You can increase the font size used for the selected text by using the button or decrease the font size using the button. When scalable fonts are selected, the size is increased (or decreased) by one point size. For non-scalable fonts the next available font size is used.

#### **Common Features**

You can change the text color used for any selected text object in a diagram editor window by using the button in the Appearance toolbar.

The toolbar can be displayed or hidden by setting the **Format Text** option in the **Toolbars** cascade of the **View** menu.

Refer to "Toolbars" on page 20 for more information about toolbars.

## **Opening the Parent View**

You can open up into the parent view using the button, **Ctrl + Shift + o** shortcut or by choosing **Open Up** from the popup menu or the **Open** cascade of the **File** menu in any graphic editor window.

If the active window is a view of a block, the parent block diagram or IBD view is opened. If it is a view of a component, the component interface is opened in the symbol or tabular IO editor.

In a hierarchical state machine or hierarchical flow chart, the parent state diagram or flow chart is opened, unless you are already at the top level when the parent block diagram, IBD view, tabular IO or symbol editor view is opened.

You cannot open up from a symbol although you can use the popup menu to open down into any of its child views.

#### **Editing the Parent Interface**

You can edit the parent interface for any graphic editor view by choosing **Interface** from the **Open** cascade of the **File** menu.

If the view in the active window has a parent block diagram or IBD view, this view is opened.

If the parent view is a block diagram it is opened with the block representing the interface to the child view in the middle of the window.

If the view in the active window describes a component, the component interface is opened in the symbol or tabular IO editor.

## **Using the Same Window**

You can re-use the current window when you open up or open down into an existing view from a graphic editor by setting the **Use Same Window** option in the **Window** menu. When this option is checked, the related diagram or table is opened in the same window without changing its position or size.

If the previous window has been edited and is the last open view of the diagram or table, you are prompted whether to save your changes before the view is closed. Note however, that a new tab is always opened when you create a concurrent view or hierarchical view for a state diagram or flow chart.

A new tab is also used when you display alternative block diagram and IBD views (or symbol and tabular IO views).

The window mode is saved as a preference and used as your default mode the next time you invoke a HDL Designer Series tool.

**Tip**: You can temporarily change the window mode by holding down the **Ctrl** key when you open the related view.

For example, **Ctrl** + to open up, **Ctrl** +double-click on object to open down or **Ctrl** + menu option.

When same window mode is set, you can use the button to go back to the previous window or the button to go forward to the next window (if a forward travel log exists).

Travel log information is only recorded when a view has been named. Therefore, if you create a hierarchical state machine or flow chart and navigate around it without saving, no travel log information is recorded.

If you have renamed a design unit or design unit view since it was last traversed, the travel log will reference the old name and an error message is issued when you attempt to navigate into the diagram or table.

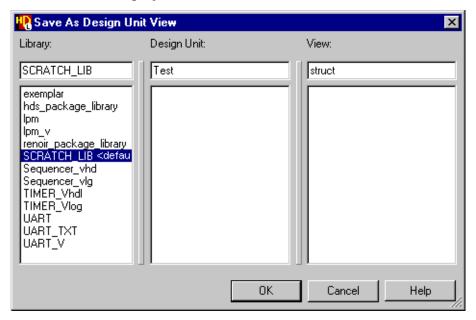

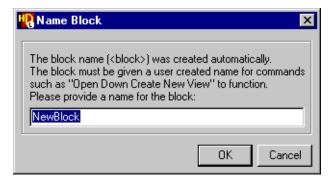

## **Saving Graphic Editor Views**

You can save the active graphic editor view by using the 🖫 button, choosing **Save** from the **File** menu or using the **Ctrl + S** shortcut.

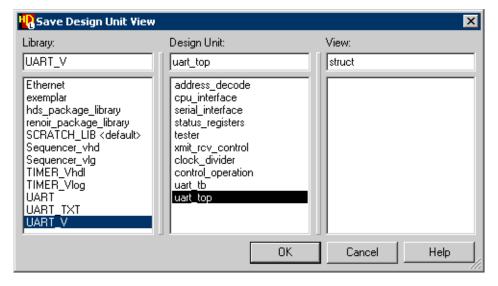

If the view has not been previously saved the Save As Design Unit View dialog box is displayed for you to enter a library name, design unit name and design unit view name. You can save an existing view with a new library, unit or view name, by using the **Save As** command. However, this option is not available in a block diagram or IBD view.

The current default library is automatically selected or you can choose from a list of other *Regular* libraries in the active project.

You can choose from the existing design units within a library or the existing views of each design unit. Alternatively, you can enter a new design unit or view name.

You can use any name for a library, design unit or view name but all names must be valid identifiers for the hardware description language you are using. A two or three character extension (.bd for a block diagram, .ibd for an IBD view, .sm for a state machine, .fc for a flow chart or .tt for a truth table) is added automatically to identify the type of view you are saving. For example: struct.bd or flow.fc.

If you do not specify a view name, the default names *struct* (for a block diagram or IBD view) or *fsm* (for a state machine view), *flow* for a flow chart view or *tbl* for a truth table view are used. These defaults can be changed by setting preferences.

The library, design unit and view name of the view is shown in the title bar (or untitled for a new view which has not been saved). An asterisk (\*) after the name in the title bar indicates that there are changes which need to be saved.

When you save a hierarchical state machine or flow chart, child views are named after the parent diagram and the hierarchical state that represents the child on its parent diagram.

Many hierarchical operations (for example, opening a child view or generating HDL) automatically perform a save on the parent design unit.

#### **Automatic Backup and Recovery**

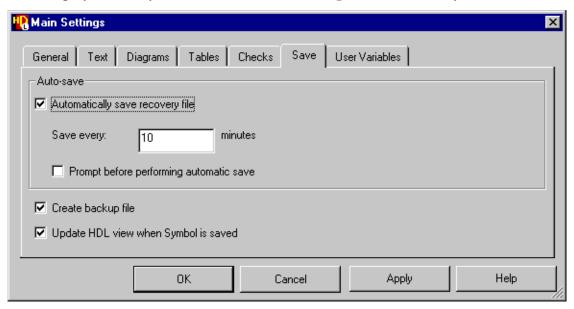

You can set preferences to control whether backup and recovery files are saved for graphic editor views. These preferences can be set from the **Save** tab of the Main Settings dialog box which is displayed when you choose **Main** from the **Options** menu in any window.

You can choose to automatically save a recovery file (for example: *struct.bd.\$rec*) at saved at a specified time interval (minimum one minute) if the file has been edited since it was last saved.

#### Note:

On a Windows workstation, you can also check an option to prompt before performing an automatic save.

You can choose to create a backup file by saving the existing version of each view (for example: *struct.bd.bak*) when the view is edited. The backup files are not deleted but are overwritten each time a view is explicitly saved.

You should not normally need to access a backup file, but it is possible to open these files after renaming the normal file and removing the .bak extension from the backup file.

The temporary recovery files are automatically deleted when a view is saved or closed normally. However, in the event of a power interruption or other system crash, the recovery file is detected when you attempt to re-open the view and you can choose to open the recovery file or to open the last normally saved file. (The unopened file is saved as a backup file in case the chosen file has been corrupted and cannot be opened.)

Autosave for a block diagram or IBD view does not update related interface data on disk and you may need to reconcile interfaces after recovering these views.

#### **Common Features**

The save options are ignored for HDL text views. Save options for these views are determined by the preferences or defaults set in the text editor. However, when a text view containing HDL interface information exists, you can control whether the interface definition is updated when a symbol is edited by setting **Update HDL view when symbol is saved**.

Unsetting this option may be useful if your text editor is not sensitive to an open file being updated by another application. It can also be used to ensure that comments or code in the HDL text view header are not overwritten when the symbol is saved. However, if this option is unset, any interface changes must be made in the text file and propagated to the parent view by updating the component instances on the parent view.

These options are saved in the master preferences file when you confirm the dialog box and are used as default settings for the current and later sessions.

| _ Note                                                                         |

|--------------------------------------------------------------------------------|

| Note that no backup or recovery files are written until a view has been saved. |

#### Saving the Window Position and Size

When you save any graphic editor view, the current view, window position and size is also saved and used when the view is next opened.

## **Editing Object Properties**

You can edit the properties for objects in a block diagram, IBD view, state diagram, flow chart, symbol, or tabular IO view by using the button, Alt + Return shortcut or by choosing **Object Properties** from the **Edit** or popup menus when one or more objects is selected.

An Object Properties dialog box is displayed which allows you to modify the properties of the selected objects in the diagram. Objects that do not exist in the selection set are disabled.

The Object Properties Dialog box pages or tabs are described in the appropriate sections for each editor later in this manual.

#### **Redrawing a Window**

A graphic editor window may sometimes become cluttered after moving text objects or when the window has been partially obscured by another application. If this occurs, you can redraw the window by choosing **Refresh** from the **View** menu.

#### Undo and Redo

At any time during an edit, you can reverse the previous command by using the Undo command in the Edit menu, the  $\Box$  toolbar button or the Ctrl + Z shortcut. The last command which can

be undone is shown on the menu (for example, after completing a move operation, the menu option **Undo** (**Move**) is available.

If any command cannot be undone you are warned before it is executed.

The **Redo** command (which also available from the **Edit** menu, using the **Ctrl** + **V** shortcut) allows you to restore the most recent 'undo' command.

Successive commands can be used to undo or redo any previous operations since the application was invoked.

## **Selecting Objects**

You can select objects in a diagram editor or table editor window by clicking the **Left** mouse button with the cursor over the object and extend the current selection set using **Shift** + **Left** or add objects to (or remove objects from) the selection by using **Ctrl** + **Left**.

When an object is selected, small "handles" are displayed at each vertex. Solid handles are used for resizable objects or unfilled handles for non-resizable objects.

When there are several objects near the cursor in a diagram editor, the default select mode selects the closest object. Typically, this means that when you click over an object with associated text (for example, a block), the text (in this case the name text) is selected. To select an object and its associated text, hold the **Left** mouse button and drag a select rectangle around one or more objects. Any objects within (or partially within) the rectangle are included in the select set.

All objects in the active graphic editor window can be selected by choosing **Select All** from the **Edit** menu or using the  $\mathbf{Ctrl} + \mathbf{A}$  shortcut.

Three different selection modes are available in a diagram editor window. The default mode (indicated by the toolbar button and cursor) selects any object.

You can change the selection mode by using the button to display a menu which allows you to select text only (the button changes to and the cursor to an and the cursor to an analysis and the cursor to an

In a block diagram or flow chart, you can use the  $\mathbf{Alt} + \mathbf{Left}$  keys to select an individual segment of a net or flow. This combination can also be used with the  $\mathbf{Shift}$  and  $\mathbf{Ctrl}$  keys to select multiple segments. The selected segments can then be moved or deleted independently from other connected segments.

## **Copying and Pasting Objects**

You can copy any graphic or text object in a graphic editor using the **Copy** command from the **Edit** menu or the **Ctrl** + **C** shortcut.

Alternatively, use the 3 toolbar button, the **Cut** command from the **Edit** menu or the **Ctrl** +  $\mathbf{X}$  shortcut to move the object to the clipboard.

If any graphics objects are copied, an internal paste buffer is used. However, if any text objects are copied (or only text objects) they are copied to the system clipboard and can be pasted into an external application.

On a Windows PC, you can also use the **Copy Picture** command from the **Diagram** or **Table** menu to copy the entire window view into the system clipboard. This command can be used to copy a diagram or table into an external application as a Windows bitmap or enhanced metafile.

You can paste any graphic or text object that has been cut or copied to another position on the same graphic editor view (or in another window of the same type) using the toolbar button, the **Ctrl** + **V** shortcut or the **Paste** command from the **Edit** menu or popup menu.

Graphic objects cannot be pasted using this command to diagrams of a different type or to another application. However, text objects can normally be pasted into any other window.

You can also use the **Paste from system clipboard** option which is available as a cascade from the **Paste Special** option in the popup menu to explicitly paste text objects into another text object, ignoring any graphic objects in the internal paste buffer.

When you paste a named object (such as a block or state) and the name already exists in the diagram, the new object is given a unique name by adding an integer to the object name. (For example: *Block*, *Block1*, *Block2*...). In a diagram editor, a ghosted image of the pasted object is attached to the cursor and can be placed by dragging the mouse and clicking at the required location.

You can also copy an object (or objects) by using the **Ctrl** key and dragging with the **Left** mouse button or by dragging with the **Right** mouse button and using the **Copy Here** option from the popup menu to paste a copy at the position of the cursor.

#### **Deleting Objects**

You can delete an object (or set of selected objects) from a diagram editor or table editor window by using the **Del** key or choosing the **Delete** command from the **Edit** or popup menus.

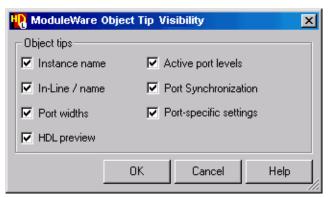

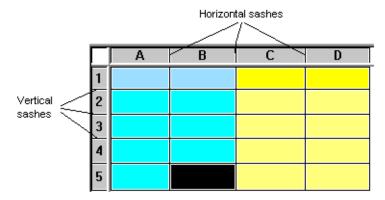

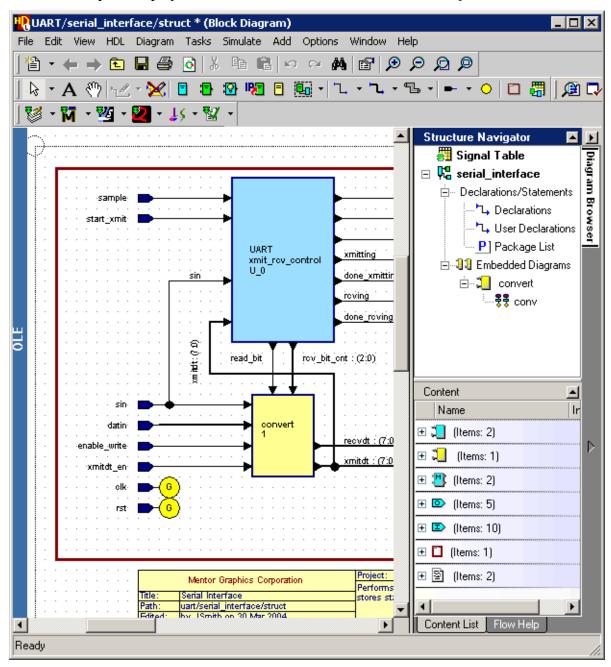

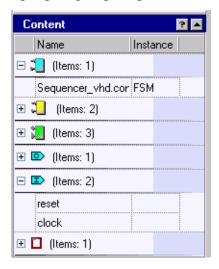

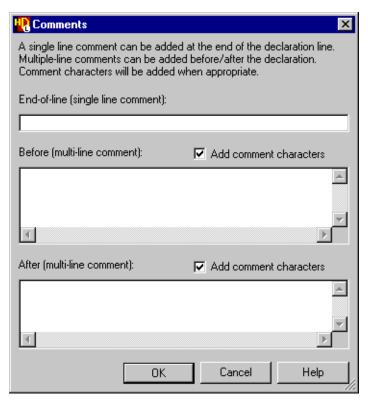

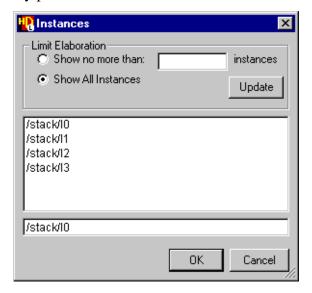

Unlike the **Cut** command, the erased objects are not copied to the clipboard but the delete operation can be undone during the current editing session.