## Artisan Technology Group is your source for quality new and certified-used/pre-owned equipment

#### FAST SHIPPING AND DELIVERY

- TENS OF THOUSANDS OF IN-STOCK ITEMS

- EQUIPMENT DEMOS

- HUNDREDS OF MANUFACTURERS SUPPORTED

- LEASING/MONTHLY RENTALS

- ITAR CERTIFIED

SECURE ASSET SOLUTIONS

#### SERVICE CENTER REPAIRS

Experienced engineers and technicians on staff at our full-service, in-house repair center

#### WE BUY USED EQUIPMENT

Sell your excess, underutilized, and idle used equipment We also offer credit for buy-backs and trade-ins **www.artisantg.com/WeBuyEquipment** *>*

#### Instra View REMOTE INSPECTION

Remotely inspect equipment before purchasing with our interactive website at **www.instraview.com** *>*

#### LOOKING FOR MORE INFORMATION?

Visit us on the web at <u>www.artisantg.com</u> for more information on price quotations, drivers, technical specifications, manuals, and documentation

## **CPC358** Octal Synchronous Serial Communications Processor

# **Hardware Manual**

Performance Technologies 205 Indigo Creek Drive Rochester, NY 14626 USA 585.256.0248 support@pt.com

www.pt.com

© 2009 Performance Technologies, Inc. All Rights Reserved.

Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

#### **Document Revision History**

| Part Number | Date     | Explanation of changes                                                                                   |

|-------------|----------|----------------------------------------------------------------------------------------------------------|

| 126P042710  | 08/01/03 | Initial Production Release                                                                               |

| 126P042711  | 11/18/03 | Certification Modifications                                                                              |

| 126P042712  | 08/18/04 | Modification to RS-232C tables in Pinout and Rear<br>Transition Modules Chapter                          |

| 126P042713  | 03/11/09 | Updated format. Added to jumper K5 description.                                                          |

| 126P042714  | 04/29/09 | Updated Table 6-4, "EIA-530 Connector Pin Assignments,"<br>on page 132, to add cable shield description. |

#### **Copyright Notice**

© Copyright 2003-2009 Performance Technologies, Inc. All Rights Reserved.

The Performance Technologies logo is a registered trademark of Performance Technologies, Inc.

All product and brand names may be trademarks or registered trademarks of their respective owners. This document is the sole property of Performance Technologies, Inc.

#### **Errors and Omissions**

Although diligent efforts are made to supply accurate technical information to the user, occasionally errors and omissions occur in manuals of this type. Refer to the Performance Technologies, Inc. web site to obtain manual revisions or current customer information:

#### http://www.pt.com.

Performance Technologies, Inc., reserves its right to change product specifications without notice.

#### **Symbol Conventions in This Manual**

The following symbols appear in this document:

#### Caution:

There is risk of equipment damage. Follow the instructions.

#### Warning:

Hazardous voltages are present. To reduce the risk of electrical shock and danger to personal health, follow the instructions.

#### Caution:

Electronic components on printed circuit boards are extremely sensitive to static electricity. Ordinary amounts of static electricity generated by your clothing or work environment can damage the electronic equipment. It is recommended that anti-static ground straps and antistatic mats are used when installing the board in a system to help prevent damage due to electrostatic discharge.

Additional safety information is available throughout this guide and in the topic "Safety Precautions" on page 183.

Contents

| Chapter 1: About This Guide            | 19 |

|----------------------------------------|----|

| Overview                               | 19 |

| Additional Documentation               | 20 |

| Text Conventions                       |    |

| Customer Support and Services          |    |

| Customer Support Packages              | 23 |

| Other Web Support                      | 23 |

| Return Merchandise Authorization (RMA) | 23 |

| Product Warranty                       | 23 |

| Chapter 2: Introduction                | 25 |

| Product Description                    | 25 |

| Features of the CPC358                 |    |

| Rear Transition Module Features        | 27 |

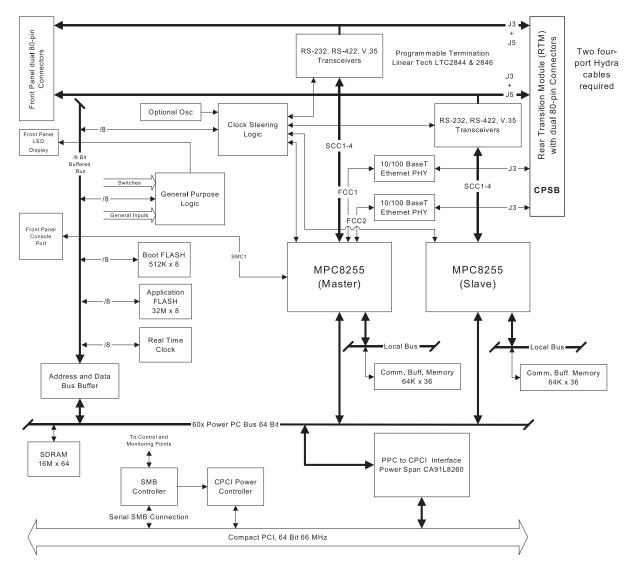

| CPC358 Architecture Overview           | 27 |

| Processors                             | 27 |

| Serial Communication Controllers       | 27 |

| Ethernet Ports                         | 28 |

| Selectable Line Interface              | 28 |

| Clock Steering                         | 28 |

| Monitor Port                           |    |

| Electrical                             | 28 |

| Universal I/O                                                                                                                                                                                                                                         | 28                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Media Connections                                                                                                                                                                                                                                     | 28                                                                                                                                             |

| Rear Transition Module Options                                                                                                                                                                                                                        | 29                                                                                                                                             |

| Battery                                                                                                                                                                                                                                               | 29                                                                                                                                             |

| Mechanical                                                                                                                                                                                                                                            | 29                                                                                                                                             |

| Form Factor                                                                                                                                                                                                                                           | 29                                                                                                                                             |

| CompactPCI Connectors                                                                                                                                                                                                                                 | 29                                                                                                                                             |

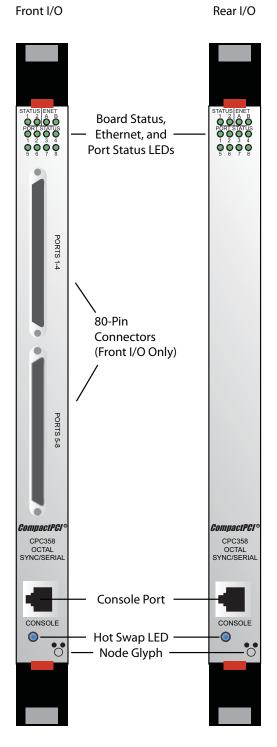

| Front Panel                                                                                                                                                                                                                                           | 30                                                                                                                                             |

| CompactPCI Interface                                                                                                                                                                                                                                  | 30                                                                                                                                             |

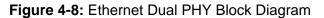

| Ethernet Ports                                                                                                                                                                                                                                        | 30                                                                                                                                             |

| Ethernet PHY                                                                                                                                                                                                                                          | 30                                                                                                                                             |

| Ethernet MII Management                                                                                                                                                                                                                               | 30                                                                                                                                             |

| Ethernet Status Indicators                                                                                                                                                                                                                            | 30                                                                                                                                             |

| Diagnostic Facilities                                                                                                                                                                                                                                 | 30                                                                                                                                             |

| Power-On Confidence (POC)                                                                                                                                                                                                                             | 31                                                                                                                                             |

| Model Designations                                                                                                                                                                                                                                    | 31                                                                                                                                             |

|                                                                                                                                                                                                                                                       |                                                                                                                                                |

| Chapter 3: Installation                                                                                                                                                                                                                               | 33                                                                                                                                             |

| Chapter 3: Installation         Working with the CPC358                                                                                                                                                                                               |                                                                                                                                                |

|                                                                                                                                                                                                                                                       | 33                                                                                                                                             |

| Working with the CPC358                                                                                                                                                                                                                               | 33<br>33                                                                                                                                       |

| Working with the CPC358 Installing the CPC358                                                                                                                                                                                                         | 33<br>33<br>34                                                                                                                                 |

| Working with the CPC358<br>Installing the CPC358<br>Removing the CPC358                                                                                                                                                                               | 33<br>33<br>34<br>35                                                                                                                           |

| Working with the CPC358<br>Installing the CPC358<br>Removing the CPC358<br>LEDs                                                                                                                                                                       | 33<br>33<br>34<br>35<br>38                                                                                                                     |

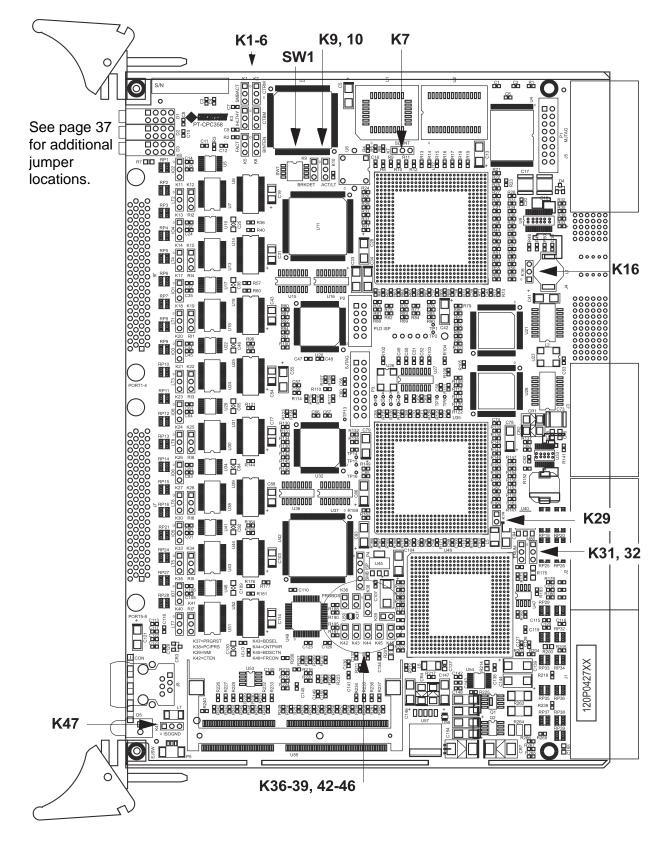

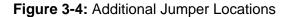

| Working with the CPC358 .<br>Installing the CPC358 .<br>Removing the CPC358 .<br>LEDs .<br>Jumpers and DIP Switches .                                                                                                                                 | 33<br>33<br>34<br>35<br>38<br>38                                                                                                               |

| Working with the CPC358 .<br>Installing the CPC358 .<br>Removing the CPC358 .<br>LEDs .<br>Jumpers and DIP Switches .<br>Switch SW1 .                                                                                                                 | <ul> <li>33</li> <li>33</li> <li>34</li> <li>35</li> <li>38</li> <li>38</li> <li>38</li> <li>38</li> </ul>                                     |

| Working with the CPC358<br>Installing the CPC358<br>Removing the CPC358<br>LEDs<br>Jumpers and DIP Switches<br>Switch SW1<br>Jumpers                                                                                                                  | <ul> <li>33</li> <li>33</li> <li>34</li> <li>35</li> <li>38</li> <li>38</li> <li>38</li> <li>38</li> <li>41</li> </ul>                         |

| Working with the CPC358         Installing the CPC358         Removing the CPC358         LEDs         Jumpers and DIP Switches         Switch SW1         Jumpers         Rear Transition Module Ethernet Routing and Ground         Reset and Abort | <ul> <li>33</li> <li>33</li> <li>34</li> <li>35</li> <li>38</li> <li>38</li> <li>38</li> <li>41</li> </ul>                                     |

| Working with the CPC358         Installing the CPC358         Removing the CPC358         LEDs         Jumpers and DIP Switches         Switch SW1         Jumpers         Rear Transition Module Ethernet Routing and Ground         Reset and Abort | <ul> <li>33</li> <li>33</li> <li>34</li> <li>35</li> <li>38</li> <li>38</li> <li>38</li> <li>41</li> <li>42</li> <li>43</li> </ul>             |

| Working with the CPC358 .<br>Installing the CPC358 .<br>Removing the CPC358 .<br>LEDs .<br>Jumpers and DIP Switches .<br>Switch SW1 .<br>Jumpers .<br>Rear Transition Module Ethernet Routing and Ground .<br>Reset and Abort                         | <ul> <li>33</li> <li>33</li> <li>34</li> <li>35</li> <li>38</li> <li>38</li> <li>38</li> <li>41</li> <li>42</li> <li>43</li> <li>44</li> </ul> |

|     | Hard Reset                                               |

|-----|----------------------------------------------------------|

|     | Soft Reset                                               |

|     | Tundra PowerSpan Resets    47                            |

|     | Peripheral Resets                                        |

| Ge  | eneral CPU Section                                       |

|     | Master MPC8255 Initial Configuration 48                  |

|     | Master MPC8255 Internal Initial Configuration 50         |

|     | Slave MPC8255 Initial Configuration 51                   |

|     | Slave MPC8255 Internal Initial Configuration 53          |

|     | Master MPC8255 Memory Map 53                             |

|     | Slave MPC8255 Memory Map 54                              |

|     | 60x Bus Connections                                      |

|     | Master MPC8255 Interrupt Sources 55                      |

|     | Slave MPC8255 Interrupt Sources 56                       |

|     | Master MPC8255 Local Bus Connections 56                  |

|     | Slave MPC8255 Local Bus Connections (Unsupported Option) |

|     | Master MPC8255 Parallel I/O Ports 57                     |

|     | Slave MPC8255 Parallel I/O Ports 59                      |

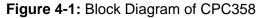

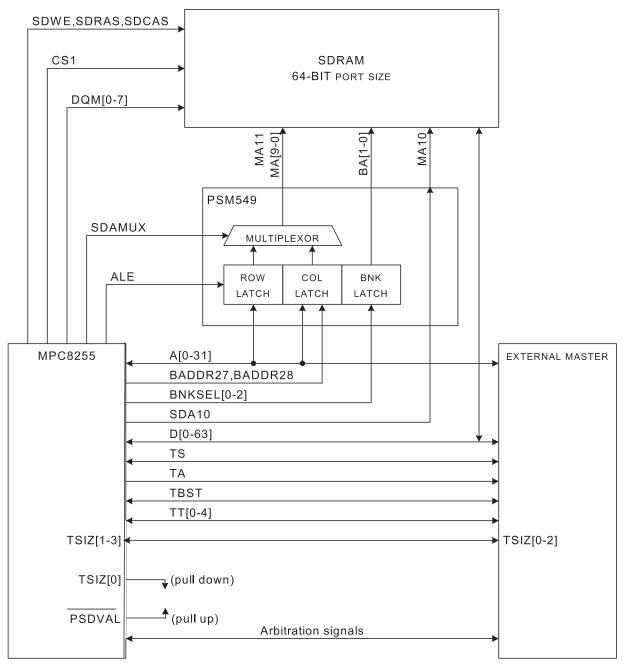

| SE  | DRAM                                                     |

|     | External Master Support                                  |

|     | SDRAM Controller Initialization 62                       |

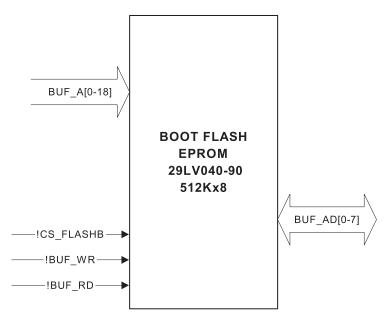

| Bo  | oot Flash Memory                                         |

|     | Master MPC8255 Related Flash Settings 64                 |

|     | General Boot Flash Information                           |

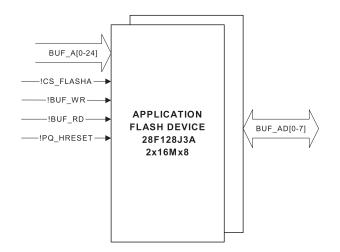

| Ap  | plication Flash Memory                                   |

|     | Master MPC8255 Related Flash Settings 66                 |

|     | General Application Flash Information                    |

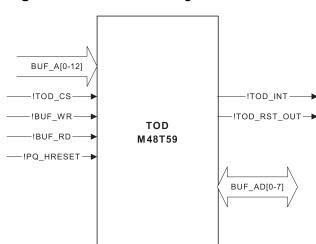

| Tir | ne of Day Timer                                          |

|     | MPC8255 Related TOD Settings                             |

|     | General TOD Information                                  |

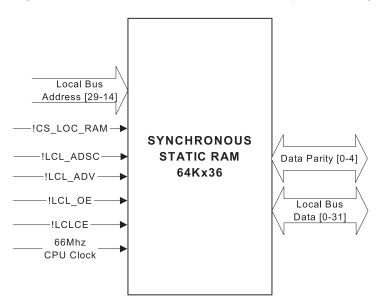

| Сс  | ommunications Buffer Memory                              |

| -   | MPC8255 Related Communications Buffer Memory Settings    |

|     | UPMB Table Settings                                      |

|     |                                                          |

| CompactPCI Interface                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PowerSpan Signal Connections and Hardware Configuration                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                 |

| PowerSpan Reset Configuration Word                                                                                                                                                                                                                                                                                                                                                                                                           | 72                                                                                                                                                                                                                                                                                                                              |

| PCI Device and Vendor ID                                                                                                                                                                                                                                                                                                                                                                                                                     | 73                                                                                                                                                                                                                                                                                                                              |

| Local 60x Bus Connections to the PowerSpan                                                                                                                                                                                                                                                                                                                                                                                                   | 73                                                                                                                                                                                                                                                                                                                              |

| PowerSpan Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                 |

| Fast Ethernet Controller                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                 |

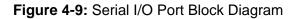

| Serial I/O Interface                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                 |

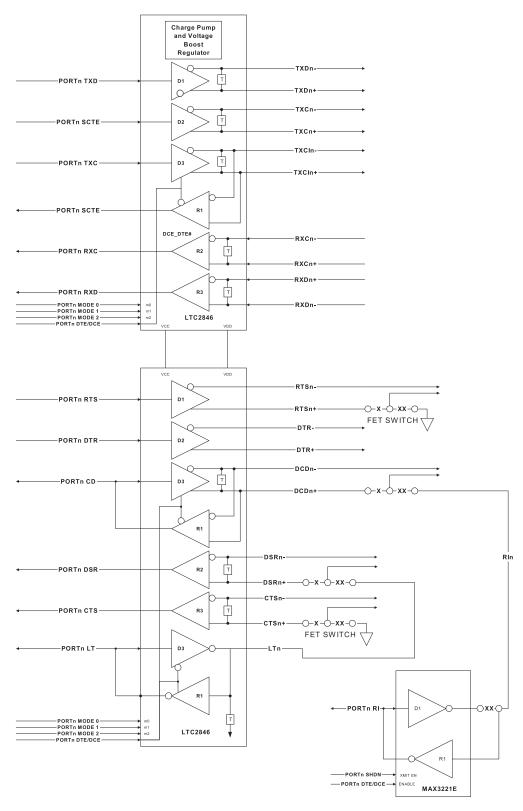

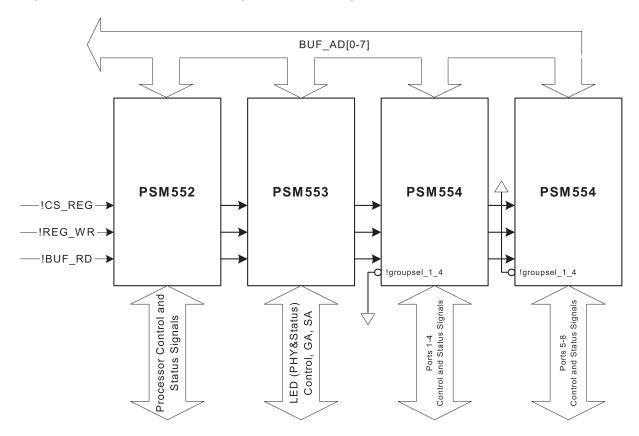

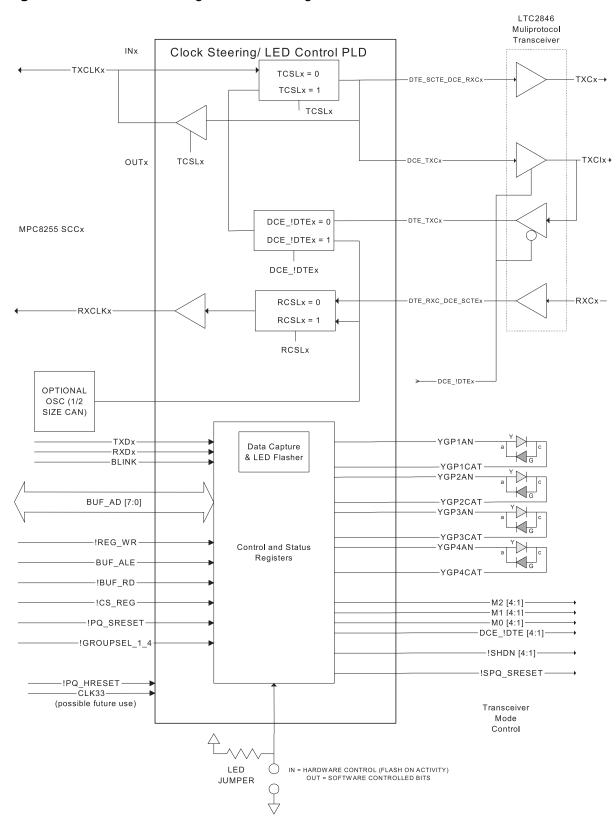

| Clock Steering                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                 |

| DTE / DCE Control                                                                                                                                                                                                                                                                                                                                                                                                                            | 80                                                                                                                                                                                                                                                                                                                              |

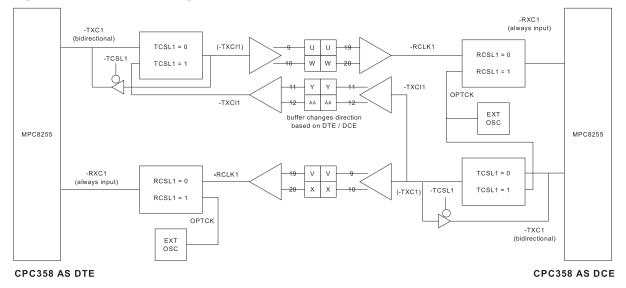

| General Purpose Registers                                                                                                                                                                                                                                                                                                                                                                                                                    | 81                                                                                                                                                                                                                                                                                                                              |

| PSM552 General Purpose Registers                                                                                                                                                                                                                                                                                                                                                                                                             | 83                                                                                                                                                                                                                                                                                                                              |

| PSM553 General Purpose Registers                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                 |

| PSM554 Port Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                | 93                                                                                                                                                                                                                                                                                                                              |

| Suctom Monogoment Bug                                                                                                                                                                                                                                                                                                                                                                                                                        | 103                                                                                                                                                                                                                                                                                                                             |

| System Management Bus                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                 |

| Chapter 5: Boot PROM and Forth Monitor                                                                                                                                                                                                                                                                                                                                                                                                       | 105                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                 |

| Chapter 5: Boot PROM and Forth Monitor                                                                                                                                                                                                                                                                                                                                                                                                       | 105                                                                                                                                                                                                                                                                                                                             |

| Chapter 5: Boot PROM and Forth Monitor<br>Boot PROM Initialization                                                                                                                                                                                                                                                                                                                                                                           | 105                                                                                                                                                                                                                                                                                                                             |

| Chapter 5: Boot PROM and Forth Monitor<br>Boot PROM Initialization                                                                                                                                                                                                                                                                                                                                                                           | 105<br>105<br>105                                                                                                                                                                                                                                                                                                               |

| Chapter 5: Boot PROM and Forth Monitor<br>Boot PROM Initialization                                                                                                                                                                                                                                                                                                                                                                           | 105<br>105<br>105<br>105                                                                                                                                                                                                                                                                                                        |

| Chapter 5: Boot PROM and Forth Monitor<br>Boot PROM Initialization                                                                                                                                                                                                                                                                                                                                                                           | 105<br>105<br>105<br>105<br>106                                                                                                                                                                                                                                                                                                 |

| Chapter 5: Boot PROM and Forth Monitor<br>Boot PROM Initialization                                                                                                                                                                                                                                                                                                                                                                           | 105<br>105<br>105<br>105<br>106<br>106                                                                                                                                                                                                                                                                                          |

| Chapter 5: Boot PROM and Forth Monitor<br>Boot PROM Initialization                                                                                                                                                                                                                                                                                                                                                                           | 105<br>105<br>105<br>105<br>106<br>106<br>110                                                                                                                                                                                                                                                                                   |

| Chapter 5: Boot PROM and Forth Monitor<br>Boot PROM Initialization                                                                                                                                                                                                                                                                                                                                                                           | 105<br>105<br>105<br>105<br>106<br>106<br>110<br>110                                                                                                                                                                                                                                                                            |

| Chapter 5: Boot PROM and Forth Monitor<br>Boot PROM Initialization                                                                                                                                                                                                                                                                                                                                                                           | 105<br>105<br>105<br>105<br>106<br>106<br>110<br>110<br>110                                                                                                                                                                                                                                                                     |

| Chapter 5: Boot PROM and Forth Monitor Boot PROM Initialization Reset Configuration MPC8255 Reset Configuration Word Slave MPC8255 Rest Configuration Word PowerSpan Reset Configuration Word Bootup and Initialization Hot-Swap/High Availability System Support Resources Used by the Monitor Boot PROM                                                                                                                                    | 105<br>105<br>105<br>105<br>106<br>106<br>110<br>110<br>110<br>110                                                                                                                                                                                                                                                              |

| Chapter 5: Boot PROM and Forth Monitor<br>Boot PROM Initialization                                                                                                                                                                                                                                                                                                                                                                           | 105<br>105<br>105<br>105<br>106<br>106<br>110<br>110<br>110<br>110<br>110<br>110                                                                                                                                                                                                                                                |

| Chapter 5: Boot PROM and Forth Monitor<br>Boot PROM Initialization                                                                                                                                                                                                                                                                                                                                                                           | 105<br>105<br>105<br>105<br>106<br>106<br>110<br>110<br>110<br>110<br>110<br>110<br>110                                                                                                                                                                                                                                         |

| Chapter 5: Boot PROM and Forth Monitor<br>Boot PROM Initialization .<br>Reset Configuration .<br>MPC8255 Reset Configuration Word .<br>Slave MPC8255 Rest Configuration Word .<br>PowerSpan Reset Configuration Word .<br>Bootup and Initialization .<br>Hot-Swap/High Availability System Support .<br>Resources Used by the Monitor .<br>Boot PROM .<br>SDRAM .<br>Console Port .<br>Port C bit 4                                          | 105         105         105         105         105         105         105         105         105         106         110         110         110         110         110         110         110         110         110         110         110         110         110         1110         1110         1110         1111 |

| Chapter 5: Boot PROM and Forth Monitor<br>Boot PROM Initialization .<br>Reset Configuration .<br>MPC8255 Reset Configuration Word .<br>Slave MPC8255 Rest Configuration Word .<br>PowerSpan Reset Configuration Word .<br>Bootup and Initialization .<br>Hot-Swap/High Availability System Support .<br>Resources Used by the Monitor .<br>Boot PROM .<br>SDRAM .<br>Console Port .<br>Port C bit 4 .<br>Power On Checks and POC Signature . |                                                                                                                                                                                                                                                                                                                                 |

| Host PCI Interface Command Set 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Flash Error Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7                                                        |

| Locally Resident Applications 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                        |

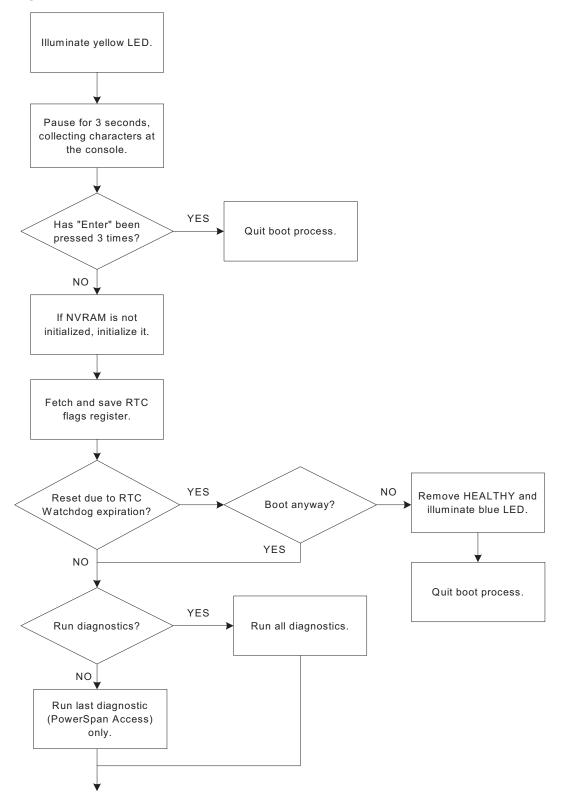

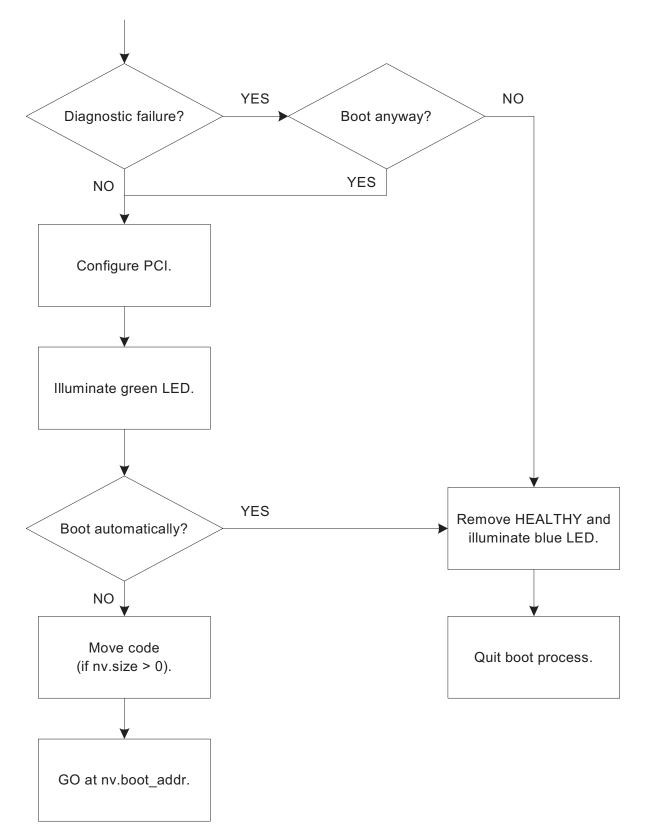

| Built-In Boot Sequence with Initialization from NVRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                                        |

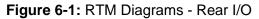

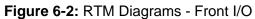

| hapter 6: Pinouts and Rear Transition Modules 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3                                                        |

| Rear Transition Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23                                                       |

| Pinouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26                                                       |

| Rear Transition Module Ethernet Ports 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26                                                       |

| RS-232 Supported Signals 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26                                                       |

| RS-449/422 Supported Signals 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29                                                       |

| V.35 Supported Signals 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35                                                       |

| Front Panel Serial Port (Console) 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2                                                        |

| Master MPC8255 JTAG Support 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3                                                        |

| Slave MPC8255 JTAG Support 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                                                        |

| Mictor Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |

| CompactPCI Bus Connectors 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6                                                        |

| CompactPCI Bus Connectors       14         hapter 7: System Management Bus and Intelligent Platform Management       15                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5                                                        |

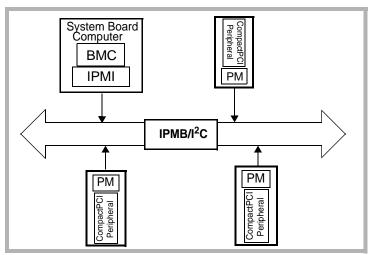

| hapter 7: System Management Bus and Intelligent Platform Management 15                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55<br>55                                                 |

| hapter 7: System Management Bus and Intelligent Platform Management 15<br>Overview of SMB                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55<br>55                                                 |

| hapter 7: System Management Bus and Intelligent Platform Management       15         Overview of SMB       15         Intelligent Platform Management Interface (IPMI)       15                                                                                                                                                                                                                                                                                                                                               | 55<br>55<br>56                                           |

| <ul> <li>hapter 7: System Management Bus and Intelligent Platform Management</li> <li>Overview of SMB</li> <li>Intelligent Platform Management Interface (IPMI)</li> <li>Baseboard Management Controller</li> </ul>                                                                                                                                                                                                                                                                                                           | 55<br>55<br>56<br>56                                     |

| hapter 7: System Management Bus and Intelligent Platform Management       15         Overview of SMB       15         Intelligent Platform Management Interface (IPMI)       15         Baseboard Management Controller       15         Peripheral Management Controller       15                                                                                                                                                                                                                                            | 55<br>55<br>56<br>56<br>57                               |

| hapter 7: System Management Bus and Intelligent Platform Management       15         Overview of SMB       15         Intelligent Platform Management Interface (IPMI)       15         Baseboard Management Controller       15         Peripheral Management Controller       15         Intelligent Platform Management Bus (IPMB)       15                                                                                                                                                                                | 55<br>55<br>56<br>56<br>57<br>57                         |

| hapter 7: System Management Bus and Intelligent Platform Management       15         Overview of SMB       15         Intelligent Platform Management Interface (IPMI)       15         Baseboard Management Controller       15         Peripheral Management Controller       15         Intelligent Platform Management Bus (IPMB)       15         Intelligent Platform Management Bus (IPMB)       15                                                                                                                    | 55<br>55<br>56<br>57<br>57<br>57                         |

| hapter 7: System Management Bus and Intelligent Platform Management15Overview of SMB15Intelligent Platform Management Interface (IPMI)15Baseboard Management Controller15Peripheral Management Controller15Intelligent Platform Management Bus (IPMB)15IPMB Compatibility15System-Side IPMI Management15                                                                                                                                                                                                                      | 55<br>55<br>56<br>57<br>57<br>57<br>58                   |

| hapter 7: System Management Bus and Intelligent Platform Management       15         Overview of SMB       15         Intelligent Platform Management Interface (IPMI)       15         Baseboard Management Controller       15         Peripheral Management Controller       15         Intelligent Platform Management Bus (IPMB)       15         IPMB Compatibility       15         System-Side IPMI Management       15         IPMI Network Function Codes (netFn)       15                                          | 55<br>55<br>56<br>57<br>57<br>58<br>58                   |

| hapter 7: System Management Bus and Intelligent Platform Management       15         Overview of SMB       15         Intelligent Platform Management Interface (IPMI)       15         Baseboard Management Controller       15         Peripheral Management Controller       15         Intelligent Platform Management Bus (IPMB)       15         IPMB Compatibility       15         System-Side IPMI Management       15         IPMI Network Function Codes (netFn)       15         Completion Codes       15        | 55<br>55<br>56<br>56<br>57<br>57<br>57<br>58<br>88<br>88 |

| hapter 7: System Management Bus and Intelligent Platform Management       15         Overview of SMB       15         Intelligent Platform Management Interface (IPMI)       15         Baseboard Management Controller       15         Peripheral Management Controller       15         Intelligent Platform Management Bus (IPMB)       15         IPMB Compatibility       15         System-Side IPMI Management       15         IPMI Network Function Codes (netFn)       15         IPMI Commands Supported       15 | 55<br>55<br>56<br>56<br>57<br>57<br>58<br>88<br>88<br>59 |

|        | Cold Reset                                        | 160 |

|--------|---------------------------------------------------|-----|

|        | Warm Reset                                        | 161 |

|        | Set Manufacturing Test Mode ON                    | 161 |

|        | Get Self Test Results                             | 161 |

|        | Set ACPI Power State                              | 161 |

|        | Get ACPI Power State                              | 162 |

|        | Get Device GUID                                   | 162 |

|        | Broadcast Get Device ID                           | 162 |

| FR     | U Inventory Device Commands (netFn = 0x0A, 0x0B)  | 163 |

|        | Common FRU Inventory Device Commands              | 163 |

|        | Get FRU Inventory Area                            | 164 |

|        | Read FRU Inventory Data                           | 165 |

|        | Write FRU Inventory Data                          | 165 |

| OE     | M (Vendor Specific) Commands (netFn = 0x30, 0x31) | 166 |

|        | Common OEM Commands                               | 166 |

|        | Diagnostic Echo                                   | 167 |

|        | Get Card Power Status                             | 168 |

|        | Set Card Power State                              | 169 |

|        | Get Card Power State                              | 170 |

|        |                                                   |     |

| Chapte | er 8: MPC8255 Parallel Port Pin Utilization       | 171 |

| N4-    |                                                   | 474 |

|        | ster MPC8255 I2C Bus                              |     |

| Ma     | ster MPC8255 Parallel Port Pin Assignments        |     |

|        | Master MPC8255 Port A Pin Assignments             |     |

|        | Master MPC8255 Port B Pin Assignments             |     |

|        | Master MPC8255 Port C Pin Assignments             |     |

|        | Master MPC8255 Port D Pin assignments             |     |

| Sla    | ve MPC8255 Parallel Port Pin Assignments          |     |

|        | Slave MPC8255 Port A Pin assignments              |     |

|        | Slave MPC8255 Port B Pin assignments              |     |

|        | Slave MPC8255 Port C Pin Assignments              |     |

|        | Slave MPC8255 Port D Pin assignments              | 181 |

183

## Chapter 9: Agency Approvals

| Safety Precautions                            | 183 |

|-----------------------------------------------|-----|

| Certifications 1                              | 184 |

| FCC Notice                                    | 184 |

| CE Notice                                     | 184 |

| Compliance with RoHS and WEEE Directives      | 185 |

| Non-Performance Technologies Branded Products | 185 |

Tables

| Table 1-1: Manufacturer Part Numbers    21                                             |

|----------------------------------------------------------------------------------------|

| Table 2-1: CPC358 Model Numbers    31                                                  |

| Table 2-2: CPC358 Accessory Cables    31                                               |

| Table 3-1: Jumpers         38                                                          |

| Table 3-2: Routing Jumpers for Ethernet Port A       41                                |

| Table 3-3: Routing Jumpers for Ethernet Port B    41                                   |

| Table 3-4: Rear Transition Module Ground                                               |

| Table 4-1: Preliminary Typical Board Power Consumption Estimates       44              |

| Table 4-2: On Pin Control Sources    45                                                |

| Table 4-3: Local Voltages    45                                                        |

| Table 4-4: !PQ_HRESET Control Signals and Select Jumpers.       46                     |

| Table 4-5: Peripheral Resets    48                                                     |

| Table 4-6: Master MPC8255 System Clock Control Register Bit Field Definitions       49 |

| Table 4-7: Master MPC8255 Hard Reset Configuration Word Settings       49              |

| Table 4-8: Master MPC8255 SIUMCR Register Settings       50                            |

| Table 4-9: Slave MPC8255 System Clock Control Register Bit Field Definitions       51  |

| Table 4-10: Slave MPC8255 Hard Reset Configuration Word Settings       52              |

| Table 4-11: Slave MPC8255 SIUMCR Register Settings       53                            |

| Table 4-12: Master MPC8255 Chip Select Assignments.       54                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 4-13: Slave MPC8255 Chip Select Assignments.       54                                                                                                                             |

| Table 4-14: Master MPC8255 Interrupt Sources       55                                                                                                                                   |

| Table 4-15: CS0 Base Register Settings    64                                                                                                                                            |

| Table 4-16: CS0 Option Register Settings.       64                                                                                                                                      |

| Table 4-17: CS3 Base Register Settings    66                                                                                                                                            |

| Table 4-18: CS3 Option Register Settings                                                                                                                                                |

| Table 4-19: CS8 Base Register Settings    68                                                                                                                                            |

| Table 4-20: CS8 Option Register Settings                                                                                                                                                |

| Table 4-21: CS2 Base Register Settings    70                                                                                                                                            |

| Table 4-22: CS2 Option Register Settings                                                                                                                                                |

| Table 4-23: Signal Variations From Between PowerSpan and the Master MPC8255                                                                                                             |

| Table 4-24: PowerSpan Reset Pins.    73                                                                                                                                                 |

| Table 4-25: PowerSpan Interrupt Connections       74                                                                                                                                    |

| Table 4-26: CS8952 Configuration Pins    75                                                                                                                                             |

| Table 4-27: V.35 DTE / DCE Signal Continuity       80                                                                                                                                   |

| Table 4-28: CS4 Base Register Settings    82                                                                                                                                            |

| Table 4-29: CS4 Option Register Settings                                                                                                                                                |

| Table 4-30: Peripheral Reset Control Register Bit Fields       83                                                                                                                       |

| Table 4-31: Peripheral Reset Control Register Bit Field Definitions       84                                                                                                            |

| Table 4-32: Ejector Switch Interrupt Enable Control Register Bit Fields       84                                                                                                        |

|                                                                                                                                                                                         |

| Table 4-33: Ejector Switch Interrupt Enable Control Register Bit Field Definitions       84                                                                                             |

|                                                                                                                                                                                         |

| Table 4-33: Ejector Switch Interrupt Enable Control Register Bit Field Definitions       84                                                                                             |

| Table 4-33: Ejector Switch Interrupt Enable Control Register Bit Field Definitions       84         Table 4-34: Ejector Switch Interrupt Status Register Bit Field Definitions       85 |

| Table 4-38: General Purpose Latch Register Bit Fields       87                          |

|-----------------------------------------------------------------------------------------|

| Table 4-39: Register Bit Field Definitions    87                                        |

| Table 4-40: General Purpose Switch and P1 Reset Register Bit Fields       87            |

| Table 4-41: General Purpose Switch and P1 Reset Register Bit Field Definitions       87 |

| Table 4-42: P1 Reset Control Register Bit Fields    88                                  |

| Table 4-43: P1 Reset Control Register Bit Field Definitions       88                    |

| Table 4-44: Hot Swap Status and Control Register Bit Fields       88                    |

| Table 4-45: Hot Swap Status and Control Register Bit Field Definitions       89         |

| Table 4-46: Board ID Register 1 Bit Fields       90                                     |

| Table 4-47: Board ID Register 1 Bit Field Definitions       90                          |

| Table 4-48: Board ID Register 2 Bit Fields    90                                        |

| Table 4-49: Board ID Register 2 Bit Field Definitions       90                          |

| Table 4-50: Board Status LED Control Register Bit Fields       91                       |

| Table 4-51: Board Status LED Control Register Bit Field Definitions       91            |

| Table 4-52: Compact PCI Geographic Address Register Bit Fields       92                 |

| Table 4-53: Compact PCI Geographic Address Register Bit Field Definitions       92      |

| Table 4-54: CT Bus Shelf Address Register Bit Fields       92                           |

| Table 4-55: CT Bus Shelf Address Register Bit Field Definitions       92                |

| Table 4-56: Transceiver Mode Control Selection Bits    95                               |

| Table 4-57: Transceiver 1-2 (5-6) Mode Control Register Bit Fields       95             |

| Table 4-58: Transceiver 1-2 (5-6) Mode Control Register Bit Field Definitions       95  |

| Table 4-59: Transceiver 3-4 (7-8) Mode Control Register Bit Fields       96             |

| Table 4-60: Transceiver 3-4 (7-8) Mode Control Register Bit Field Definitions       96  |

| Table 4-61: Receive Clock Steering Control Register Bit Fields       97                 |

| Table 4-62: Receive Clock Steering Control Register Bit Field Definitions       97      |

| Table 4-63: Transmit Clock Steering Control Register Bit Fields       98                |

| Table 4-64: Transmit Clock Steering Control Register Bit Field Definitions - DTE       98 |

|-------------------------------------------------------------------------------------------|

| Table 4-65: Transmit Clock Steering Control Register Bit Field Definitions - DCE       99 |

| Table 4-66: Port 1-2 (5-6) Status LED Control Register Bit Fields       99                |

| Table 4-67: Port 1-2 (5-6) Status LED Control Register Bit Field Definitions       100    |

| Table 4-68: Port 3-4 (7-8) Status LED Control Register Bit Fields       100               |

| Table 4-69: Port 3-4 (7-8) Status LED Control Register Bit Field Definitions       101    |

| Table 4-70: Transceiver Shutdown Control Register Bit Fields       101                    |

| Table 4-71: Transceiver Shutdown Control Register Bit Field Definitions       101         |

| Table 4-72:       LED Mode/Slave Reset Control Register Bit Fields       102              |

| Table 4-73: LED Mode/Slave Reset Control Register Bit Field Definitions       102         |

| Table 4-74: CompactPCI SMB to CPC358 SMB Interface       103                              |

| Table 5-1: POC Signature                                                                  |

| Table 5-2: Flash Error Codes    117                                                       |

| Table 5-3: NVRAM Structure    118                                                         |

| Table 6-1: Ethernet Connector J3 and J4 Pinout.    126                                    |

| Table 6-2: RS-232C Connector Pin Assignments       126                                    |

| Table 6-3:    RS-449 Connector Pin Assignments    129                                     |

| Table 6-4: EIA-530 Connector Pin Assignments       132                                    |

| Table 6-5: V.35 Connector Pin Assignments       136                                       |

| Table 6-6: V.35 Signals and Pins - DCE    138                                             |

| Table 6-7: Console Pin Assignments.    142                                                |

| Table 6-8: Master JTAG Pinout                                                             |

| Table 6-9: Slave JTAG Pinout                                                              |

| Table 6-10: J9 Mictor Pinout, 60X Bus Address    144                                      |

| Table 6-11: J10 Mictor Pinout, 60X Bux Data    145                                        |

| Table 6-12: J11 Mictor Pinout, 60X Bus Data    145                                        |

| Table 6-13: J1 CompactPCI Connections    147                           |

|------------------------------------------------------------------------|

| Table 6-14: J2 CompactPCI Connections    148                           |

| Table 6-15: J3 RS-422, RS449, RS-530 Signal pinouts       149          |

| Table 6-16: DTE RS232 Adjustments for J3       150                     |

| Table 6-17: DTE V.35 Adjustments for J3       150                      |

| Table 6-18: J4 CompactPCI Connections    151                           |

| Table 6-19: J5 RS-422, RS-449, RS-530 Signal Pinouts       152         |

| Table 6-20: DTE RS232 Adjustments for J5       153                     |

| Table 6-21: DTE V.35 Adjustments for J5       153                      |

| Table 7-1: IPMB Slave Address Map       157                            |

| Table 7-2: Supported Network Function Codes       158                  |

| Table 7-3: IPM Device Request (Commands) Message Format       159      |

| Table 7-4: IPM Device Response Message Format       159                |

| Table 7-5: Get Device ID Response Message    160                       |