# Rabbit<sup>®</sup> RIO™

**User's Manual**

019-0158 • 080930-E

#### Rabbit RIO User's Manual

Part Number 019-0158 • 080930–E • Printed in U.S.A. ©2006–2008 Digi International Inc. • All rights reserved.

No part of the contents of this manual may be reproduced or transmitted in any form or by any means without the express written permission of Digi International.

Permission is granted to make one or more copies as long as the copyright page contained therein is included. These copies of the manuals may not be let or sold for any reason without the express written permission of Digi International.

Digi International reserves the right to make changes and improvements to its products without providing notice.

#### **Trademarks**

Rabbit and Dynamic C are registered trademarks of Digi International Inc.

Rabbit RIO is a trademark of Digi International Inc.

The latest revision of this manual is available on the Rabbit Web site, www.rabbit.com, for free, unregistered download.

Digi International Inc.

www.rabbit.com

# **TABLE OF CONTENTS**

| Chapter 1. The Rabbit RIO                                                              | 1        |

|----------------------------------------------------------------------------------------|----------|

| 1.1 Overview                                                                           | 1        |

| 1.2 Key Features                                                                       | 2        |

| 1.3 Development and Evaluation Tools                                                   |          |

| 1.4 Block Diagram of Rabbit RIO I/O Blocks                                             |          |

| 1.5 Pin Functions and Descriptions                                                     |          |

| 1.6 Pinouts                                                                            |          |

| 1.7 Mechanical Dimensions and Land Pattern — TQFP Package                              |          |

| 1.8 DC Characteristics                                                                 |          |

| 1.9 AC Characteristics                                                                 |          |

| 1.10 Memory Access Times                                                               |          |

| 1.10.1 Parallel Mode                                                                   |          |

| 1.10.2 SPI/RabbitNet Mode                                                              |          |

| 1110.2 bi Pittaoota tet Piode                                                          | 13       |

| Chapter 2. Master-Level Features                                                       | 17       |

| 2.1 Overview                                                                           | 17       |

| 2.2 Block Diagram                                                                      |          |

| 2.3 Clocks                                                                             |          |

| 2.4 Reset.                                                                             |          |

| 2.5 Bus Interface                                                                      |          |

| 2.5.1 Parallel Mode                                                                    |          |

| 2.5.2 Serial Mode — Clocked Serial Interface                                           |          |

| 2.5.3 Serial Mode — RabbitNet Device Interface                                         |          |

| 2.5.4 Serial Mode — RabbitNet Hub Interface                                            | 27       |

| 2.6 Synchronization                                                                    |          |

| 2.7 Interrupts                                                                         |          |

| 2.8 Registers                                                                          | 29       |

| 2.9 Register Descriptions                                                              | 31       |

| 2.9.1 Master Control Register                                                          | 31       |

| 2.9.2 Master Status Register                                                           |          |

| 2.9.3 Master Prescale Register                                                         |          |

| 2.9.4 Master Alternate Data Register                                                   |          |

| 2.9.5 Master Protection Command Register     2.9.6 Master Protection Prescale Register | 34<br>25 |

| 2.9.7 Watchdog Timer Registers                                                         | 35       |

| 2.9.8 Pointer Registers                                                                |          |

| 2.9.9 Indirect Registers                                                               |          |

| Chapter 3. Block-Level Features                 | 37       |

|-------------------------------------------------|----------|

| 3.1 Overview                                    | 37       |

| 3.1.1 Simplified Block Diagram                  |          |

| 3.2 Internal Block Registers                    |          |

| 3.3 Block Control                               |          |

| 3.4 Register Descriptions                       |          |

| 3.4.1 Pointer and Indirect Registers            |          |

| 3.4.2 Command Register                          | 42       |

| 3.4.3 Mode Register                             | 43       |

| 3.4.4 Interrupt Enable and Status Registers     | 44       |

| 3.4.5 Counter Toggle Register                   | 46       |

| 3.4.6 Synch Control Register                    | 47       |

| 3.4.7 Increment/In-Phase/Begin Control Register | 48       |

| 3.4.8 Decrement/Quadrature/End Control Register | 49<br>50 |

| 3.4.10 Pin Control Registers                    | 50<br>51 |

| 3.4.11 Match Registers                          | 51       |

| 3.4.12 Count Limit Registers                    | 52       |

| 3.4.13 Count Begin Registers                    |          |

| 3.4.14 Count End Registers                      | 52       |

| 3.4.15 Count Value Registers                    | 53       |

|                                                 |          |

| Chapter 4. General-Purpose I/O                  | 55       |

| 4.1 Overview                                    | 55       |

| 4.1.1 Block Diagram                             |          |

| 4.2 Dependencies                                | 55       |

| 4.3 Operation                                   |          |

| 4.3.1 Setup                                     |          |

| 4.3.2 Example of Operation                      | 56       |

| 4.3.3 Pattern Mode                              | 56       |

| 4.4 Register Descriptions                       | 57       |

| Chapter 5. Pulse-Width Modulator                | 59       |

| •                                               |          |

| 5.1 Overview                                    |          |

| 5.1.1 Block Diagram                             |          |

| 5.2 Dependencies                                |          |

| 5.3 Operation                                   |          |

| 5.3.1 Setup                                     | 60       |

| 5.3.2 Example                                   |          |

| 5.4.1 General-Purpose I/O                       |          |

| 5.4.1 General-Purpose I/O                       |          |

| 5.4.3 Interrupts                                |          |

| 5.4.4 Higher Drive Current Operations           |          |

|                                                 |          |

| Chapter 6. Variable-Phase Pulse-Width Modulator | 63       |

| 6.1 Overview                                    | 63       |

| 6.1.1 Block Diagram                             |          |

| 6.2 Dependencies                                |          |

| 6.3 Operation                                   | 65       |

| 6.3.1 Setup                                     |          |

| 6.3.2 Example of Operation                      |          |

| 6.4 Other Comments                              | 67       |

| Chapter 7. Input Capture              | 69 |

|---------------------------------------|----|

| 7.1 Overview                          | 69 |

| 7.1.1 Block Diagram                   | 69 |

| 7.2 Dependencies                      |    |

| 7.3 Operation                         | 70 |

| 7.3.1 Setup                           | 70 |

| 7.3.2 Example                         | 71 |

| 7.4 Other Comments                    |    |

| 7.4.1 General-Purpose I/O             |    |

| 7.4.2 Interrupts                      | 72 |

| Chapter 8. Quadrature Decoder         | 73 |

| 8.1 Overview                          | 73 |

| 8.1.1 Block Diagram                   | 73 |

| 8.2 Dependencies                      |    |

| 8.3 Operation                         | 74 |

| 8.3.1 Setup                           | 75 |

| 8.3.2 Example                         | 75 |

| 8.4 Other Comments                    |    |

| 8.4.1 General-Purpose I/O             | 76 |

| 8.4.2 External Synchronization        |    |

| 8.4.3 Interrupts                      | /6 |

| Chapter 9. RabbitNet Hub              | 77 |

| 9.1 Overview                          | 77 |

| 9.2 Hub Functions                     | 77 |

| 9.3 Hub Commands                      | 77 |

| 9.4 Reset and Enumeration             | 79 |

| 9.5 Additional RabbitNet Information  | 79 |

| 9.6 Registers                         |    |

| 9.6.1 RabbitNet Status Register       |    |

| 9.6.2 RabbitNet Parameter Register    |    |

| 9.6.3 RabbitNet ID Register           | 81 |

| 9.6.4 RabbitNet Reset Status Register | 82 |

| Index                                 | 83 |

# 1. THE RABBIT RIO

#### 1.1 Overview

The Rabbit RIO is a peripheral device designed to be incorporated into systems requiring versatile timing controls and a broader range of functionality. The Rabbit RIO can be used with any microprocessor.

The Rabbit RIO communicates with the microprocessor in either a parallel or a serial mode. The particular communication mode is determined during power-up. In the parallel mode, the chip communicates with the microprocessor through a parallel bus with eight data bits, five address bits, and four control bits. The serial mode can be used for bidirectional data flow on one wire or via the SPI and RabbitNet protocols. In the serial mode, the parallel data lines are available to be used as general-purpose I/O. The multiple communication modes allow the Rabbit RIO to be a part of a wide variety of systems that use any one of these communication methods.

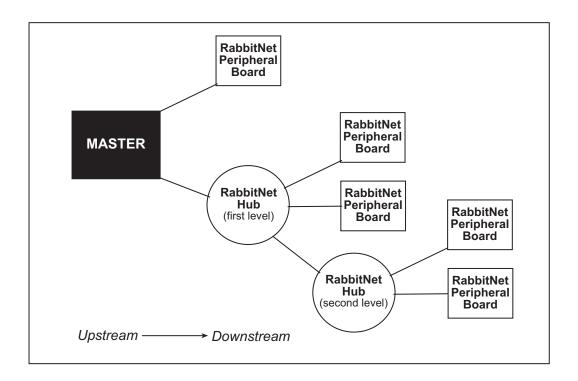

Implementing the Rabbit RIO as a RabbitNet hub provides a simple, efficient, and flexible means of establishing a network of RabbitNet peripheral cards. The RabbitNet architecture allows a hub to connect to seven peripheral cards, and support for two levels of hubs allows a master device to control up to 49 RabbitNet peripheral cards.

The design of the Rabbit RIO's I/O blocks allows any of the eight identical I/O blocks, each with four bits or I/O pins, to be programmed to perform any number of different functions, including a pulse-width modulator, a pulse-position modulator, event counters, quadrature decoders, pulse measurements, and I/O, including pin-pair protection for applications such as H-bridge drivers.

The main clock can be used directly by each I/O block, or it may be prescaled down to a lower frequency. Either clock source can be used by the 16-bit counter, which is the core of each I/O block. This counter is complemented by a number of registers that provide access and control to the counter for the various Rabbit RIO functions that it involves.

The Rabbit RIO can be incorporated without any glue logic in a Rabbit-based system, enabling a more efficient use of resources. Rabbit's Dynamic C software allows for seamless integration of hardware and software. Dynamic C provides a complete set of function calls to enable you to use the Rabbit RIO without having to write any additional drivers.

The Rabbit RIO can operate at clock speeds up to 40 MHz. It is powered by 3.3 V, but the I/O are 5 V tolerant. The Rabbit RIO is packaged in a 64-pin 10 mm ×10mm TQFP, making its small footprint and low profile ideal for embedded applications.

#### 1.2 Key Features

- 5 V tolerant

- Clock speed up to 40 MHz

- 64-pin 10 mm ×10 mm TQFP package

- Multiple communication interfaces SPI, parallel, and RabbitNet

- 8 independent functional I/O blocks with 4 pins each

- Any pin on each I/O block is capable of:

- ► Generating PWM outputs and variable-phase PWM outputs

- ▶ Pulse count

- ► Input capture (pulse length or frequency)

- ▶ Decoding quadrature signals

- ▶ Provide extended I/O pins to the microprocessor

- ▶ Pin-pair protection for driving H bridges

- Up to 32 digital I/O lines, up to 4 general-purpose inputs

- Global or block synch input to coordinate outputs

- Interrupt request pin

- RoHS compliant

2

- High-performance 8-bit device requires no glue logic to Rabbit systems

- RabbitNet hub feature allows control of up to seven RabbitNet devices in each of two levels for a total of up to 49 RabbitNet devices

- Functionality well-suited for machine control

- Dynamic C libraries allow for Rabbit RIO to be up and running in no time

- Small footprint and multiple functions allow for versatile system

## 1.3 Development and Evaluation Tools

Rabbit also has an application kit featuring the Rabbit RIO to provide the harware and software tools to help you use the Rabbit RIO for I/O expansion.

• RIO Programmable I/O Kit [Part No. 101-1147 (North American markets) and Part No. 101-1148 (overseas markets)]—comes with two CD-ROMs that includes Dynamic C 10.11 or a later version, an RCM4110 RabbitCore module, and a RIO Prototyping Board. The software bundle on the supplemental CD provides the Dynamic C function calls and sample programs that illustrate the use of the Rabbit RIO chip included on the RIO Prototyping Board and can serve as a template for you to develop your own application.

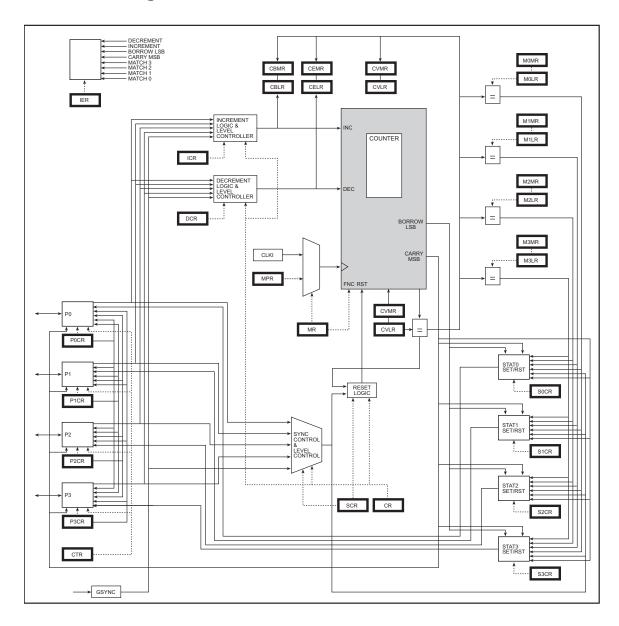

# 1.4 Block Diagram of Rabbit RIO I/O Blocks

# 1.5 Pin Functions and Descriptions

| Pin Group           | Pin Name                                                                                        | Direction     | Function                                                       |

|---------------------|-------------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------|

| Hardware            | /RESET                                                                                          | Input         | Master Reset                                                   |

|                     | CLK                                                                                             | Input         | Clock In                                                       |

| CPU Buses           | BLOCK[2:1] or GPIN[2:1]<br>BLOCK[0]<br>G//B<br>/P/I                                             | Input         | Address Bus or GPI*                                            |

|                     | D7/SERCLK D6/SERI D5/BL6Pin[3] D4/BL6Pin[2] D3/BL6Pin[1] D2/BL7Pin[3] D1/BL7Pin[2] D0/BL7Pin[1] | Bidirectional | Parallel Data Bus or<br>Serial Control Bus &<br>I/O Block Pins |

| Status &<br>Control | /CS                                                                                             | Input         | I/O Chip Select                                                |

|                     | /IORD or GPIN[4]                                                                                | Input         | I/O Read Enable or GPI*                                        |

|                     | /IOWR or GPIN[3]                                                                                | Input         | I/O Write Enable or GPI*                                       |

|                     | /INT                                                                                            | Output        | Interrupt Request                                              |

|                     | /WAIT/SERO                                                                                      | Output        | Wait Request or<br>Serial Out                                  |

|                     | SER//PAR                                                                                        | Input         | Serial/Parallel Bus Select                                     |

| Shared              | GSYNC                                                                                           | Input         | Global Sync                                                    |

| I/O Pins            | BL0Pin[3:0] –<br>BL5Pin[3:0] &<br>BL6Pin[0] &<br>BL7Pin[0]                                      | Input/Output  | I/O Block Pins                                                 |

| Power               | VDDINT<br>VDDIO                                                                                 | Power         | Internal Power I/O Power                                       |

| Ground              | VSSINT<br>VSSIO                                                                                 | Ground        | Internal Ground I/O Ground                                     |

<sup>\*</sup> The GPI options are general-purpose inputs when operating in a serial mode.

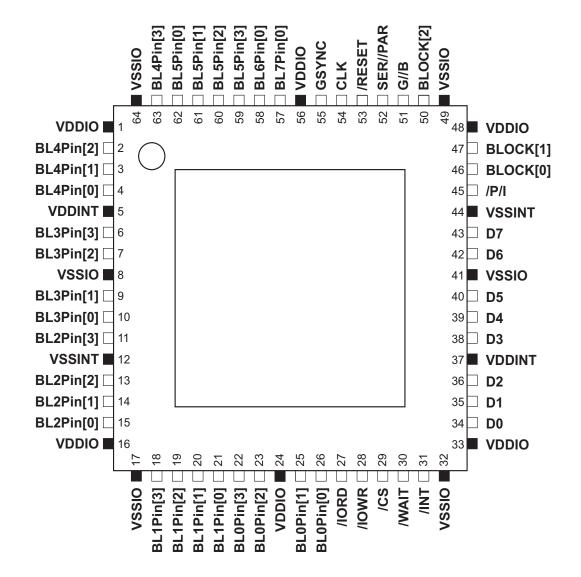

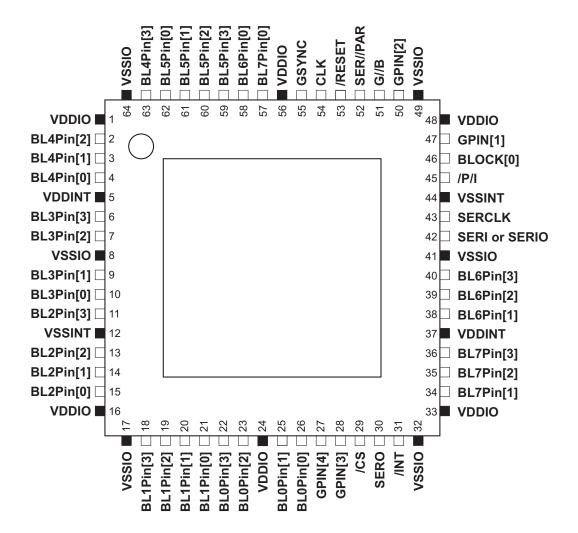

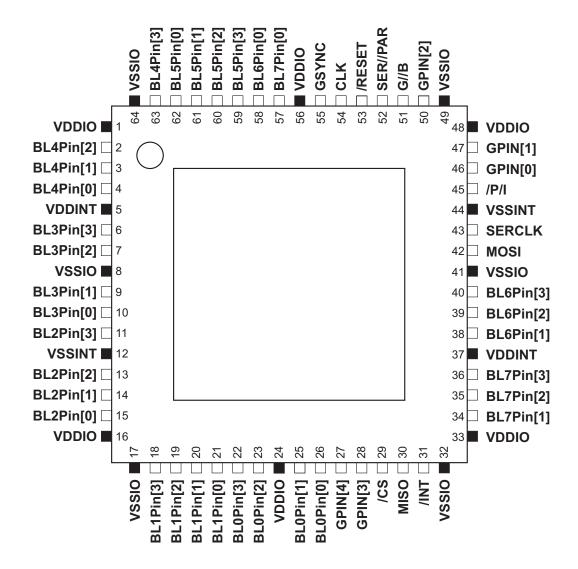

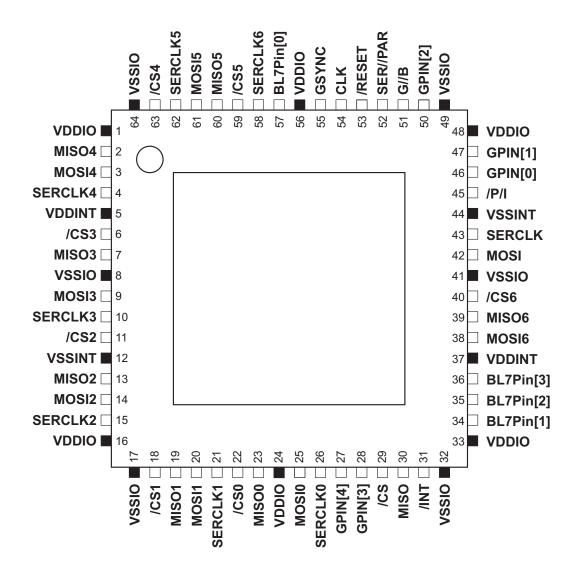

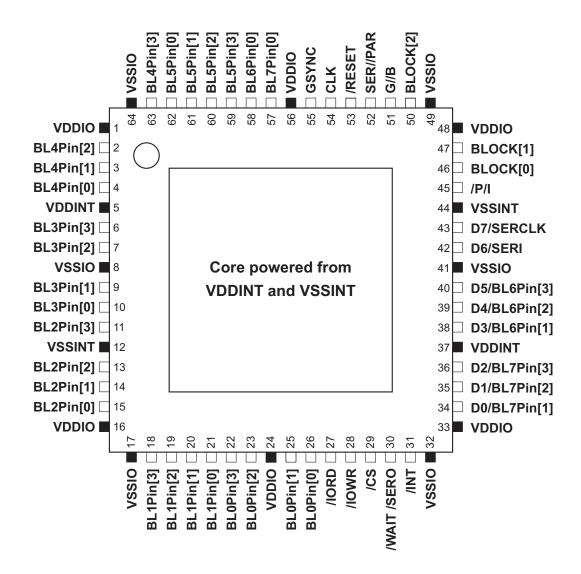

#### 1.6 Pinouts

Figure 1-1. Parallel Pinout

Figure 1-2. Serial Pinout — SPI Interface Mode

Figure 1-3. Serial Pinout — RabbitNet Device Interface Mode

Figure 1-4. Serial Pinout — RabbitNet Hub Interface Mode

Figure 1-5. General Pinout

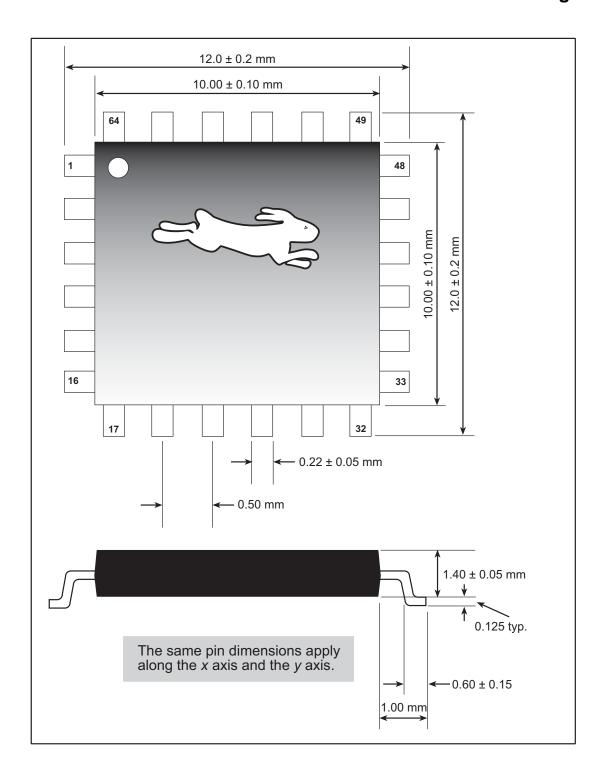

# 1.7 Mechanical Dimensions and Land Pattern — TQFP Package

Figure 1-6. Mechanical Dimensions Rabbit RIO TQFP Package

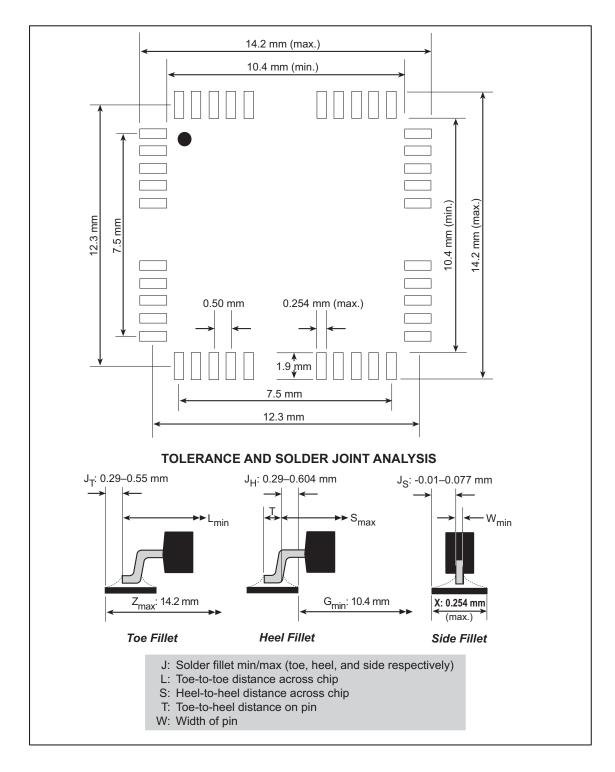

Figure 1-7 shows the PC board land pattern for the Rabbit RIO in a 64-pin TQFP package. This land pattern is based on the IPC-SM-782 standard developed by the Surface Mount Land Patterns Committee and specified in *Surface Mount Design and Land Pattern Standard*, IPC, Northbrook, IL, 1999.

Figure 1-7. PC Board Land Pattern for Rabbit RIO 64-pin TQFP

# 1.8 DC Characteristics

Table 1-1. Preliminary DC Electrical Characteristics

|                       | Parameter                                       | Symbol              | Min   | Тур     | Max   |

|-----------------------|-------------------------------------------------|---------------------|-------|---------|-------|

| Operating Temperature |                                                 | T <sub>A</sub>      | -40°C |         | 85°C  |

| Stor                  | age Temperature                                 | ¹A                  | -55°C |         | 125°C |

|                       | Core Supply Voltage                             | VDD <sub>CORE</sub> | 3.0 V | 3.3 V   | 3.6 V |

|                       | Core Current @ 22.1184 MHz, 25°C                |                     |       | 31.3 mA |       |

| Core                  | Core current @ 11.0592 MHz, 25°C                | I <sub>CORE</sub>   |       | 16.3 mA |       |

|                       | Core current @ 7.3728 MHz, 25°C                 | CORE                |       | 11.0 mA |       |

|                       | Core current @ 3.6864 MHz, 25°C                 |                     |       | 5.5 mA  |       |

|                       | I/O Ring Supply Voltage                         | $VDD_{IO}$          | 3.0 V | 3.3 V   | 3.6 V |

|                       | I/O Ring Current @ 22.1184 MHz, 25°C            | I <sub>IO</sub>     |       | 1.1 mA  |       |

|                       | I/O Ring Current @ 11.0592 MHz, 25°C            |                     |       | 1.0 mA  |       |

|                       | I/O Ring Current @ 7.3728 MHz, 25°C             | I <sub>IO</sub>     |       | 0.9 mA  |       |

| 50                    | I/O Ring Current @ 3.6864 MHz, 25°C             |                     |       | 0.9 mA  |       |

| I/O Ring              | Input Low Voltage (VDD <sub>IO</sub> = 3.3 V)   | $v_{IL}$            |       | 0.8 V   |       |

| I/C                   | Input High Voltage (VDD <sub>IO</sub> = 3.3 V)  | V <sub>IH</sub>     |       | 2.0 V   |       |

|                       | Output Low Voltage (VDD <sub>IO</sub> = 3.3 V)  | V <sub>OL</sub>     |       | 0.4 V   |       |

|                       | Output High Voltage (VDD <sub>IO</sub> = 3.3 V) | V <sub>OH</sub>     |       | 2.4 V   |       |

|                       | Maximum I/O Input Voltage                       |                     |       | 3.3 V   | 5.0 V |

|                       | Output Drive                                    | I <sub>DRIVE</sub>  |       |         | 8 mA  |

### 1.9 AC Characteristics

Table 1-2. Preliminary AC Electrical Characteristics

| Parameter       | Symbol     | Min | Тур | Max    |

|-----------------|------------|-----|-----|--------|

| Clock Frequency | $f_{main}$ |     |     | 40 MHz |

# 1.10 Memory Access Times

All access time measurements are taken at 50% of the signal height.

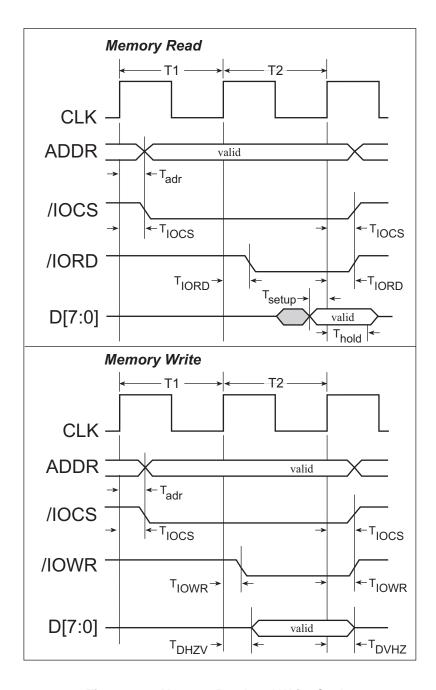

#### 1.10.1 Parallel Mode

Table 1-3. Parallel Bus Read Time Delays (VDD = 3.3 V  $\pm$  10%,  $T_A = -40^{\circ}$ C to 85°C)

| Parameter                    | Symbol             | Min  | Тур | Max  |

|------------------------------|--------------------|------|-----|------|

| Clock to Address Delay       | $T_{adr}$          |      |     | 6 ns |

| Clock to Chip Select Delay   | T <sub>IOCS</sub>  |      |     | 6 ns |

| Clock to Output Enable Delay | T <sub>IORD</sub>  |      |     | 6 ns |

| Data Setup Time              | T <sub>setup</sub> | 1 ns |     |      |

| Data Hold Time               | T <sub>hold</sub>  | 0 ns |     |      |

Table 1-4. Parallel Bus Write Time Delays (VDD = 3.3 V  $\pm$  10%,  $T_A$  = -40°C to 85°C)

| Parameter                              | Symbol            | Min | Тур | Max   |

|----------------------------------------|-------------------|-----|-----|-------|

| Clock to Address Delay                 | $T_{adr}$         |     |     | 6 ns  |

| Clock to Chip Select Delay             | T <sub>IOCS</sub> |     |     | 6 ns  |

| Clock to Write Strobe Delay            | T <sub>IOWR</sub> |     |     | 6 ns  |

| High Z to Data Valid Relative to Clock | T <sub>DHZV</sub> |     |     | 10 ns |

| Data Valid to High Z Relative to Clock | T <sub>DVHZ</sub> |     |     | 10 ns |

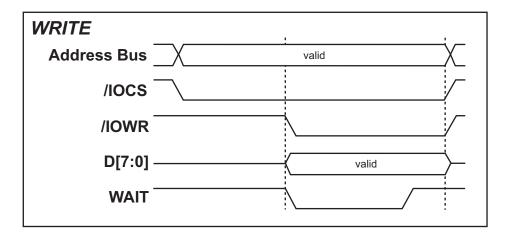

Figure 1-8. Memory Read and Write Cycles

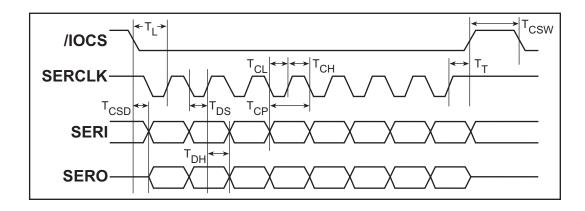

#### 1.10.2 SPI/RabbitNet Mode

Table 1-5. SPI/RabbitNet Bus Access Time Delays (VDD = 3.3 V  $\pm$  10%,  $T_{\rm A}$  = -40°C to 85°C)

| Parameter                                           | Symbol           | Min    | Тур | Max |

|-----------------------------------------------------|------------------|--------|-----|-----|

| Serial Clock Period                                 | T <sub>CP</sub>  | 25 ns  |     |     |

| Serial Clock Pulse Width High                       | T <sub>CH</sub>  | 12 ns  |     |     |

| Serial Clock Pulse Width Low                        | T <sub>CL</sub>  | 12 ns  |     |     |

| Chip Select Fall to Input Data Valid                | T <sub>CSD</sub> | 0 ns   |     |     |

| Chip Select Leading Time Before First<br>Clock Edge | $T_{ m L}$       | 25 ns  |     |     |

| Chip Select Trailing Timer After Last<br>Clode Edge | T <sub>T</sub>   | 25 ns  |     |     |

| Input Data Setup Time                               | T <sub>DS</sub>  | 12 ns  |     |     |

| Input/Output Data Hold Time                         | $T_{DH}$         | 12 ns  |     |     |

| Chip Select Pulse High                              | T <sub>CSW</sub> | 100 ns |     |     |

Figure 1-9. SPI/RabbitNet Bus Access Time Delays

# 2. Master-Level Features

#### 2.1 Overview

The Rabbit RIO uses master-level registers to access individual I/O blocks or to control their overall function. Unlike block registers, master registers can be accessed directly through the five-bit address and eight-bit data bus. In the parallel communication mode, these two buses are accessed through address and data bus pins. In the serial communication mode, the data and address must be decoded from the serial bit stream. Changing the communication mode is a simple matter of pulling the G//B, /P/I, BLOCK[0], and SER//PAR pins high or low.

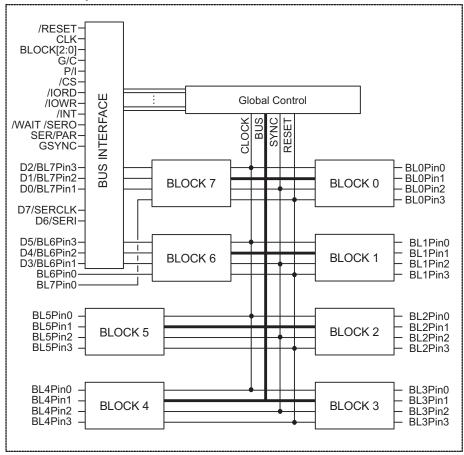

## 2.2 Block Diagram

Rabbit RIO Chip Master-Level Features

#### 2.3 Clocks

Even though the Rabbit RIO has just one **Master Clock** pin, the timing of each I/O block is still versatile because the **Master Precaler** will allow any 8-bit prescale of the master clock to be used by the I/O blocks. Once the prescale value is set in the **Master Prescale Register (MPR)**, any I/O block can be set to use either the precaled clock or the master clock directly. Resetting bit 3 of the I/O block's **Mode Register (MR)** allows the I/O block to use the master clock; setting bit 3 allows the I/O block to use the prescaler.

#### 2.4 Reset

A reset signal can be triggered from multiple sources. A *hardware reset* is generated by pulling the reset pin low. This will cause all the master and block-level registers to go back to their original startup state. Section 3.2 lists the reset states for each register. Another method of resetting all the registers is through a *software reset*, which can be accomplished by setting bit 7 of the **Master Control Register (MCR)**. Note that pin-pair protection can only be disabled through a hardware reset.

Additional hardware and software reset options are available at the block level. Such a reset will simply reset the counter for that I/O block, as opposed to resetting the whole chip. The synch signal is used to perform these resets, and there are multiple sources for the synch signal that are specified by the I/O block's **Synch Control Register (SCR)**. This register will specify whether the global synch pin or which one of the four I/O block pins will provide the synch signal.

#### 2.5 Bus Interface

The Rabbit RIO is designed to be connected to the processor data bus, the processor I/O bus, a clocked serial interface, or a RabbitNet master without any glue logic. Unless the Rabbit RIO is acting as a RabbitNet hub, it has all the same functionality regardless of the communication mode — it simply communicates differently in the various communication modes.

When using the parallel communication mode, not all the I/O blocks have complete I/O capability. With this interface, Blocks 6 and 7 each have only one pin available for I/O.

The serial mode is enabled by tying the SER//PAR input *high*. The six possibilities for the serial interface are shown in Table 2-1.

Table 2-1. Serial Mode Interfaces

|      | Pin  |          | - Selects                                       | Serial Order |

|------|------|----------|-------------------------------------------------|--------------|

| G//B | /P/I | BLOCK[0] | - Selects                                       | Serial Order |

| 0    | 0    | X        | RabbitNet Device                                | MSB first    |

| 0    | 1    | X        | RabbitNet Hub                                   | MSB first    |

| 1    | 0    | 0        | Clocked Serial with<br>Serial Out & Serial In   | LSB first    |

| 1    | 0    | 1        | Clocked Serial with<br>Serial Out & Serial In   | MSB first    |

| 1    | 1    | 0        | Clocked Serial with<br>Bidirectional Serial I/O | LSB first    |

| 1    | 1    | 1        | Clocked Serial with<br>Bidirectional Serial I/O | MSB first    |

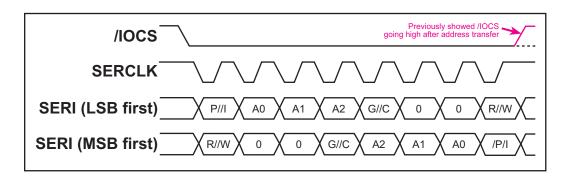

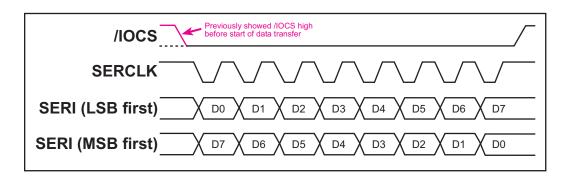

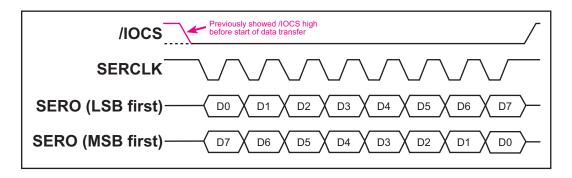

With a clocked serial interface, data are transferred to and from the Rabbit RIO in address and data cycles. First, the byte of address information is shifted into the chip, and then the byte of data is either shifted in or out of the chip. The active low chip select must remain active for the duration of each byte transfer, but is allowed to go inactive between transfers. The read/write bit is shifted with the address to signal the Rabbit RIO what kind of transfer is requested and sets the direction. Transfers can be either LSB-first or MSB-first. When using the clocked serial interface, all eight I/O blocks have full I/O capabilities.

As a RabbitNet device, the Rabbit RIO implements the RabbitNet specification, including the watchdog function. All RabbitNet transfers are either read-only or are simultaneous read and write (fully duplex). Data are always transferred MSB-first in this mode. When using the Rabbit RIO as a RabbitNet device, all eight I/O blocks have full I/O capabilities.

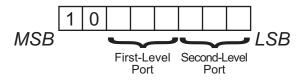

As a RabbitNet hub, the Rabbit RIO implements the RabbitNet specification for a hub and can be used as either a first- or second-level hub. Only one I/O block has I/O capability, as the pins that are normally used for the other seven I/O blocks are connected to downstream RabbitNet devices.

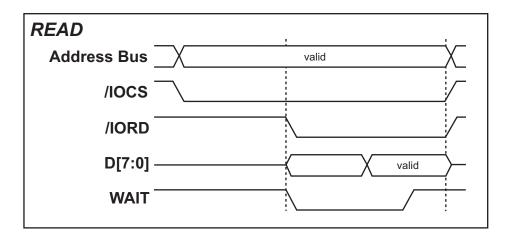

#### 2.5.1 Parallel Mode

The parallel mode is selected by tying the SER//PAR input *low*. This mode is completely asynchronous. This makes the chip useful in systems that do not use Rabbit microprocessors.

The address bus consists of a three-bit I/O block address (BLOCK[2:0]) to select the appropriate I/O block, a Pointer/Indirect (/P/I) bit to select between the two externally addressable registers in each I/O block, and the Global/Block (G//B) bit to select between a global access and a block access.

All external transactions are synchronized internally to the clock, which requires a recovery time of four clock cycles between external accesses. In other words, the maximum rate at which external accesses can occur is once every four internal clock cycles. The /WAIT signal is activated until the Rabbit RIO is ready to accept or supply data during a transaction. The /WAIT signal enforces the recovery time between external transactions, and in the case of a read, is guaranteed to be deasserted once the read data are valid.

A read transaction is shown below. The data bus is driven while /IORD and /CS are both active. The address on the address bus must remain valid for the duration of the transaction, but there is no hold time relative to the trailing edge of /IORD or /CS.

A write transaction is shown below. The data bus is latched at the end of the transaction, with no hold time. As in the case of a read, the address on the address bus must remain valid for the duration of the transaction.

Table 2-2 lists the suggested connections to the Rabbit RIO for the parallel mode using the auxiliary I/O bus.

Table 2-2. Rabbit RIO Connections

— Parallel Mode

| Rabbit<br>Microprocessor<br>Signal | Rabbit RIO Pin | Description              |

|------------------------------------|----------------|--------------------------|

|                                    | SER//PAR       | Pulled down              |

| PE1                                | /CS            | Chip select*             |

| PA0                                | D0             | Data bus line            |

| PA1                                | D1             | Data bus line            |

| PA2                                | D2             | Data bus line            |

| PA3                                | D3             | Data bus line            |

| PA4                                | D4             | Data bus line            |

| PA5                                | D5             | Data bus line            |

| PA6                                | D6             | Data bus line            |

| PA7                                | D7             | Data bus line            |

| PB2                                | /P/I           | Pointer/Indirect line    |

| PB3                                | BLOCK[0]       | Block address 0          |

| PB4                                | BLOCK[1]       | Block address 1          |

| PB5                                | BLOCK[2]       | Block address 2          |

| PB7                                | G//B           | G//B (Global/Block) line |

| PE4                                | /WAIT          | Wait signal              |

| /IORD                              | /IORD          | Read enable              |

| /IOWR                              | /IOWR          | Write enable             |

<sup>\*</sup> Rabbit RIO /CS may be connected to PE1 or any other available pin on Parallel Port E, or it may be pulled low.

#### 2.5.2 Serial Mode — Clocked Serial Interface

The clocked serial interface, which includes the two-wire data option (SPI) and the one-wire data option (bidirectional data), is selected by tying both the SER//PAR and G//B inputs *high*. The two-wire data option (SERIAL IN and SERIAL OUT) is selected by tying the /P/I pin *low*. The *LSB-first* serial data option is selected with BLOCK[0] *low*, and the *MSB-first* serial data option is selected with BLOCK[0] *high*. The direction of serial transfer is selected with a bit in the address byte, which must be shifted into the chip as the first phase of a data transfer cycle. The /CS signal will still function as the chip select for this communication mode.

The two-wire data option (SPI) is a half duplex interface where data from the microprocessor travel to the Rabbit RIO on one line, and data from the Rabbit RIO travel to the microprocessor on another line, but not at the same time. A synchronous clock is shared between the two devices, but only the microprocessor drives that signal.

The single-wire data option works similarly to the two-wire data option, except that data are transferred between devices through one line. In this case, a transfer starts with a write operation to the Rabbit RIO to indicate whether this will be a write or a read cycle and to or from which register. In this operation, the master, typically the microprocessor, will drive the data and clock lines. If the cycle happens to be a read cycle, the address write operation will be followed by a read operation. The clock will continue to be driven by the master, but the data will be driven by the Rabbit RIO. On the other hand, if the cycle happens to be a write cycle, then the address write operation will be followed by a write operation. The clock and the data will continue to be driven by the master.

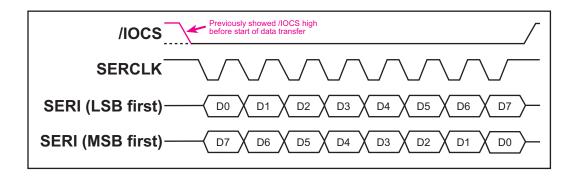

A serial mode address transfer is shown below. The five address bits function identically to the corresponding address signals in the parallel processor interface. The R//W bit controls the direction of the data transfer (high for read, low for write). Note that the value on the SERI signal is sampled by the rising edge of the SERCLK signal.

**NOTE:** The chip select needs to stay low between the address and data bytes of a transaction until all the data have been transferred. Therefore the chip select is shown as remaining low in the above diagram for the address transfer, then remaining low in the three diagrams that follow for the data transfer until all the data have been transferred.

A serial mode write transfer is shown below. Note that the recovery time restriction still applies in the serial bus cases, but now there is no mechanism to enforce this restriction since the /WAIT signal has become the serial output (SERO) signal. The wait time should not be an issue as long as SERCLK frequency is not more than CLK/4.

A serial mode read transfer is shown below for the case of separate serial input and output signals.

The same read transfer is shown below when using a bidirectional serial data signal. Note that any external driver on the serial data signal must be tristated before the falling edge of the serial clock. The serial data signal is driven by the device only until shortly after the rising edge of the serial clock to prevent possible bus contention.

Table 2-3 lists the suggested connections to the Rabbit RIO for the SPI clocked serial interface where data flow unidirectionally on two lines (two-wire data flow).

Table 2-3. Rabbit RIO Connections

— Serial Mode SPI Clocked Serial Interface

| Rabbit<br>Microprocessor<br>Signal | Rabbit RIO Pin | Description                                      |

|------------------------------------|----------------|--------------------------------------------------|

|                                    | SER//PAR       | Pulled up                                        |

|                                    | G//B           | Pulled up                                        |

|                                    | BLOCK[0]       | Pulled down (LSB first)<br>Pulled up (MSB first) |

|                                    | /P/I           | Pulled down                                      |

| PC0, PC2, or PC4                   | SERI           | Serial input to Rabbit RIO                       |

| PC1, PC3, or PC5                   | SERO           | Serial output from Rabbit RIO                    |

| PD0, PD2, or PB0                   | SERCLK         | Clock input to Rabbit RIO                        |

Table 2-4 lists the suggested connections to the Rabbit RIO for the clocked serial interface where data flow bidirectionally on one line (one-wire data flow).

Table 2-4. Rabbit RIO Connections

— Serial Mode Clocked Serial Interface (one-wire bidirectional data flow)

| Rabbit<br>Microprocessor<br>Signal | Rabbit RIO Pin | Description                                      |  |

|------------------------------------|----------------|--------------------------------------------------|--|

|                                    | SER//PAR       | Pulled up                                        |  |

|                                    | G//B           | Pulled up                                        |  |

|                                    | BLOCK[0]       | Pulled down (LSB first)<br>Pulled up (MSB first) |  |

|                                    | /P/I           | Pulled up                                        |  |

| PC0, PC2, or PC4                   | SERI           | Bidirectional data                               |  |

| PD0, PD2, or PB0                   | SERCLK         | Clock input to Rabbit RIO                        |  |

#### 2.5.3 Serial Mode — RabbitNet Device Interface

The RabbitNet device interface option is selected by tying the SER//PAR pin *high* and the G//B and /P/I pins *low*. The table below shows the RabbitNet addressing. Additional information on RabbitNet and the RabbitNet peripheral cards is available in the *RabbitNet Peripheral Card User's Manual*.

Table 2-5. RabbitNet Addressing on Rabbit RIO

| RNA[5:0] | Selects                       |  |  |

|----------|-------------------------------|--|--|

| 000000   | RabbitNet Parameters (0x00)   |  |  |

| 000001   | Product ID (0xF0)             |  |  |

| 000010   | Reserved (0x00)               |  |  |

| 000011   | Reserved (0x00)               |  |  |

| 000100   | Reserved (0x00)               |  |  |

| 000101   | Reserved (0x00)               |  |  |

| 000110   | Reserved (0x00)               |  |  |

| 000111   | Reset Status (0x00)           |  |  |

| 001xxx   | Reserved (0x00)               |  |  |

| 01xxxx   | Reserved (0x00)               |  |  |

| 1xxxxx   | Rabbit RIO "External Address" |  |  |

In order to take advantage of the SPI-like interface, the Rabbit RIO will always write back the status or echo the SERO stream, which the master can check to verify the data integrity. All data bits are transmitted and received MSB first, however, the order of bytes is little endian for RabbitNet devices transferring multiple bytes.

The protocol for communicating to the Rabbit RIO is somewhat different with RabbitNet than other forms of serial communication. To communicate with the Rabbit RIO directly from a master, a command byte must be sent out first. This byte tells the Rabbit RIO the type of transaction being initiated, determined by the two most significant bits, and which register to access, determined by the six least significant bits. At the same time the command byte is being transmitted to the Rabbit RIO, the status byte is transmitted from the Rabbit RIO. Since the status byte is transmitted automatically, its register does not have a register address. A read or a write cycle will begin immediately after the command cycle. If reading, the master will continue to drive the clock, but will be getting data driven by the Rabbit RIO. If writing, the master will drive both the clock and the data going into the Rabbit RIO.

Table 2-6 lists the suggested connections to the Rabbit RIO for the RabbitNet device interface via Serial Port C. Serial Port B or Serial Port D may also be used.

Table 2-6. Rabbit RIO Connections

— RabbitNet Device Serial Interface

| Rabbit<br>Microprocessor<br>Signal | Rabbit RIO Pin | Description                   |  |

|------------------------------------|----------------|-------------------------------|--|

|                                    | SER//PAR       | Pulled up                     |  |

|                                    | G//B           | Pulled down                   |  |

|                                    | /P/I           | Pulled down                   |  |

| PC2                                | SERI           | Serial input to Rabbit RIO    |  |

| PC3                                | SERO           | Serial output from Rabbit RIO |  |

| PD2                                | SERCLK         | Clock input to Rabbit RIO     |  |

#### 2.5.4 Serial Mode — RabbitNet Hub Interface

The RabbitNet hub interface option is selected by tying the SER//PAR and /P/I pins *high* and tying the G//B pin *low*. The table below shows the RabbitNet hub addressing.

Table 2-7. RabbitNet Hub Addressing on Rabbit RIO

| RNA[5:0] | Selects                       |

|----------|-------------------------------|

| 000000   | RabbitNet Parameters (0x00)   |

| 000001   | Product ID (0x10)             |

| 000010   | Reserved (0x00)               |

| 000011   | Reserved (0x00)               |

| 000100   | Reserved (0x00)               |

| 000101   | Reserved (0x00)               |

| 000110   | Reserved (0x00)               |

| 000111   | Reset Status (0x00)           |

| 001xxx   | Reserved (0x00)               |

| 01xxxx   | Reserved (0x00)               |

| 1xxxxx   | Rabbit RIO "External Address" |

As a RabbitNet hub, the Rabbit RIO essentially becomes a different device. A hub is responsible for switching its upstream port to one of its downstream ports. The Rabbit RIO is no longer the target device, but becomes a device that reroutes signals to the appropriate RabbitNet device on its ports. A maximum of two levels of hubs are allowed in any RabbitNet network. Each hub can multiplex at most seven downstream ports.

When the master initializes the network, it must first broadcast commands to its RabbitNet port to assign each hub as a first level hub or a second level hub. It will then proceed to enumerate all devices attached to the available hubs and list them in a tabled set in memory. In this way, all devices can be easily tracked and accessed.

Table 2-8 lists the suggested connections to the Rabbit RIO for the RabbitNet hub interface via Serial Port C. Serial Port B or Serial Port D may also be used.

Table 2-8. Rabbit RIO Connections

— RabbitNet Hub Serial Interface

| Rabbit<br>Microprocessor<br>Signal | Rabbit RIO Pin | Description                   |

|------------------------------------|----------------|-------------------------------|

|                                    | SER//PAR       | Pulled up                     |

|                                    | G//B           | Pulled down                   |

|                                    | /P/I           | Pulled up                     |

| PC2                                | SERI           | Serial input to Rabbit RIO    |

| PC3                                | SERO           | Serial output from Rabbit RIO |

| PD2                                | SERCLK         | Clock input to Rabbit RIO     |

Chapter 9 provides additional information on using the Rabbit RIO as a RabbitNet hub.

## 2.6 Synchronization

The Rabbit RIO is non-specific to any system, meaning it will work no matter what system it is incorporated into. If the Rabbit RIO is used in a Rabbit-based system, then special logic can be used to synchronize its timing. Bit 1 of the Master Control Register can be reset to disable synchronizing logic when using a non-Rabbit-based system, or set to enable the special synchronization logic when used in a Rabbit-based system.

The synchronous bus timing option can be used when the Rabbit RIO is connected to a Rabbit microprocessor, and the RIO clock is supplied by the CLK output of the Rabbit microprocessor. The option reduces the access recovery time when the Rabbit RIO is communicating directly with a Rabbit microprocessor so that back-to-back reads and writes can be supported. Much of the synchronization logic in the Rabbit RIO can be bypassed in this case because the phase relationships for the address, data, and control signals are already known. The bit is ignored in the serial communication modes and the RabbitNet mode.

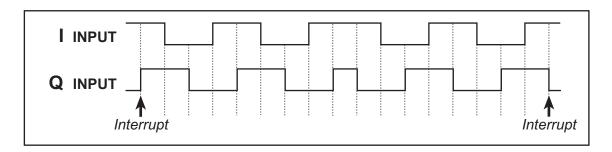

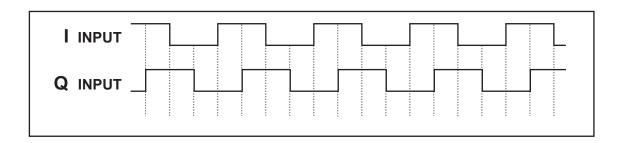

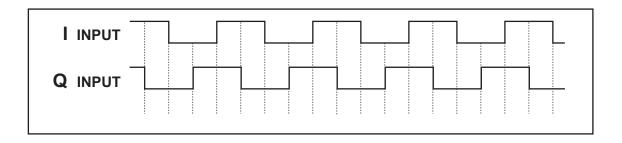

### 2.7 Interrupts

Interrupts can be enabled on the Rabbit RIO as an alternative to polling to provide a more efficient use of processor time. Master-level registers provide a means for interrupt control, but the exact nature of the interrupt is determined by block-level interrupt registers. To enable interrupts, Bit 0 of the Master Control Register must be set. When an I/O block triggers an interrupt, the Rabbit RIO will pull /INT low. Upon receiving the interrupt, the master can read the Master Status Register from the Rabbit RIO to determine which I/O block(s) invoked the interrupt, service the interrupt, and clear that particular interrupt in the block's Status Register.

## 2.8 Registers

The external address bus selects the registers according to Table 2-9 below. Each I/O block is accessed indirectly through just two external I/O addresses.

The addressing in the RabbitNet mode is similar, except the RabbitNet addresses are six bits wide, with many of the lowest address reserved for commands and configuration. In this case, the Rabbit RIO addresses are relocated to the upper 32 bytes of the RabbitNet address space, that is, the most significant bit of the RabbitNet address is set to one to access these Rabbit RIO registers (see Table 2-7).

Table 2-9. External I/O Register Addresses

| Pins |            |      |                                     |     |          |

|------|------------|------|-------------------------------------|-----|----------|

| G//B | BLOCK[2:0] | /P/I | Selects                             | R/W | Reset    |

| 1    | 000        | 0    | Master Control Register             | R/W | 00000000 |

| 1    | 000        | 1    | Master Status Register              | R/W | 00000000 |

| 1    | 001        | 0    | Master Prescale Register            | W   | 00000000 |

| 1    | 001        | 1    | Master Alternate Data Register      | R/W | 00000000 |

| 1    | 010        | 0    | Master Protection Command Register  | W   | 00000000 |

| 1    | 010        | 1    | Master Protection Prescale Register | W   | 00000000 |

| 1    | 110        | 0    | Watchdog Timer 0 Register           | R/W | 00000000 |

| 1    | 110        | 1    | Watchdog Timer 1 Register           | R/W | 00000000 |

| 1    | 111        | 0    | Watchdog Timer 2 Register           | R/W | 00000000 |

| 0    | 000        | 0    | Block 0 Pointer Register            | R/W | 00000000 |

| 0    | 000        | 1    | Block 0 Indirect Register           | R/W | xxxxxxx  |

| 0    | 001        | 0    | Block 1 Pointer Register            | R/W | 00000000 |

| 0    | 001        | 1    | Block 1 Indirect Register           | R/W | xxxxxxx  |

| 0    | 010        | 0    | Block 2 Pointer Register            | R/W | 00000000 |

Table 2-9. External I/O Register Addresses (continued)

|      | Pins       |      | 0.1                       | D/M Doort |          |

|------|------------|------|---------------------------|-----------|----------|

| G//B | BLOCK[2:0] | /P/I | Selects                   | R/W       | Reset    |

| 0    | 010        | 1    | Block 2 Indirect Register | R/W       | xxxxxxx  |

| 0    | 011        | 0    | Block 3 Pointer Register  | R/W       | 00000000 |

| 0    | 011        | 1    | Block 3 Indirect Register | R/W       | xxxxxxx  |

| 0    | 100        | 0    | Block 4 Pointer Register  | R/W       | 00000000 |

| 0    | 100        | 1    | Block 4 Indirect Register | R/W       | xxxxxxx  |

| 0    | 101        | 0    | Block 5 Pointer Register  | R/W       | 00000000 |

| 0    | 101        | 1    | Block 5 Indirect Register | R/W       | xxxxxxx  |

| 0    | 110        | 0    | Block 6 Pointer Register  | R/W       | 00000000 |

| 0    | 110        | 1    | Block 6 Indirect Register | R/W       | xxxxxxx  |

| 0    | 111        | 0    | Block 7 Pointer Register  | R/W       | 00000000 |

| 0    | 111        | 1    | Block 7 Indirect Register | R/W       | xxxxxxx  |

#### 2.9 Register Descriptions

A number of external addresses are used for registers that provide global control and status for the Rabbit RIO. Master-level registers are accessed directly through the address bus, and block-level registers are accessed indirectly through the pointer registers.

#### 2.9.1 Master Control Register

The Master Control Register has three functions:

- provide software reset,

- set bus synchronization,

- enable or disable interrupts.

When the Rabbit RIO is interfaced with a Rabbit microprocessor, faster operation is possible by enabling synchronous bus timing via bit 1. This option can be used when the Rabbit RIO is connected to a Rabbit microprocessor, and the RIO clock is supplied by the CLK output of the Rabbit microprocessor.

|        | Master Control Register |                                                                         | (MCR)       | (External Address = 0x10) |

|--------|-------------------------|-------------------------------------------------------------------------|-------------|---------------------------|

| Bit(s) | Value                   |                                                                         | Description | on                        |

| 7      | 0                       | No effect on the device.                                                |             |                           |

|        | 1                       | Reset the entire device.                                                |             |                           |

| 6:2    |                         | These bits are ignored during writes and always return zeros when read. |             |                           |

| 1      | 0                       | Normal bus timing (used with non-Rabbit hosts).                         |             |                           |

|        | 1                       | Synchronous bus timing (Rabbit 2000/3000/4000).                         |             |                           |

| 0      | 0                       | Disable interrupts for this device.                                     |             |                           |

|        | 1                       | Enable interrupts for this de                                           | vice.       |                           |

#### 2.9.2 Master Status Register

The Master Status Register allows a processor to determine which I/O block signaled an interrupt.

|        | Master St | tatus Register (MSR) (External Address = 0x11) |  |  |  |

|--------|-----------|------------------------------------------------|--|--|--|

| Bit(s) | Value     | Description                                    |  |  |  |

| 7      | 0         | No interrupt pending for Block 7.              |  |  |  |

|        | 1         | Interrupt pending for Block 7.                 |  |  |  |

| 6      | 0         | No interrupt pending for Block 6.              |  |  |  |

|        | 1         | Interrupt pending for Block 6.                 |  |  |  |

| 5      | 0         | No interrupt pending for Block 5.              |  |  |  |

|        | 1         | Interrupt pending for Block 5.                 |  |  |  |

| 4      | 0         | No interrupt pending for Block 4.              |  |  |  |

|        | 1         | Interrupt pending for Block 4.                 |  |  |  |

| 3      | 0         | No interrupt pending for Block 3.              |  |  |  |

|        | 1         | Interrupt pending for Block 3.                 |  |  |  |

| 2      | 0         | No interrupt pending for Block 2.              |  |  |  |

|        | 1         | Interrupt pending for Block 2.                 |  |  |  |

| 1      | 0         | No interrupt pending for Block 1.              |  |  |  |

|        | 1         | Interrupt pending for Block 1.                 |  |  |  |

| 0      | 0         | No interrupt pending for Block 0.              |  |  |  |

|        | 1         | Interrupt pending for Block 0.                 |  |  |  |

#### 2.9.3 Master Prescale Register

Each of the eight I/O blocks has the option of either using the master clock directly or using a scaled version of that clock determined by the Master Prescale Register. The prescale value will apply universally to all the I/O blocks.

| Master Prescale Register |       | (MPR)                        | (External Address = 0x12) |                                                                                                                   |

|--------------------------|-------|------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------|

| Bit(s)                   | Value | Description                  |                           |                                                                                                                   |

| 7:0                      |       | next time that the prescaler | counts down to z          | time constant will take effect the tero. The prescaler counts modulo at. The output of the prescaler is also ges. |

#### 2.9.4 Master Alternate Data Register

In the serial mode, certain pins that were used in the parallel mode for bus control are available as general-purpose input-only pins. The Master Alternate Data Register will allow the processor to read the state of these pins.

| Ma     | ster Altern | ate Data Register                                 | (MADR)                                         | (External Address = 0x13) |  |

|--------|-------------|---------------------------------------------------|------------------------------------------------|---------------------------|--|

| Bit(s) | Value       |                                                   | Descriptio                                     | n                         |  |

| 7      | Read        | Current state of SER//PAR pi                      | in.                                            |                           |  |

| 6      | Read        | Current state of /IORD pin (s                     | Current state of /IORD pin (serial mode only). |                           |  |

| 5      | Read        | Current state of /IOWR pin (serial mode only).    |                                                |                           |  |

| 4      | Read        | Current state of G//B pin (serial mode only).     |                                                |                           |  |

| 3      | Read        | Current state of BLOCK[2] pin (serial mode only). |                                                |                           |  |

| 2      | Read        | Current state of BLOCK[1] pin (serial mode only). |                                                |                           |  |

| 1      | Read        | Current state of BLOCK[0] pin (serial mode only). |                                                |                           |  |

| 0      | Read        | Current state of /P/I pin (seria                  | al mode only).                                 |                           |  |

Bits 7, 4, 1, and 0 are used to establish the type of serial communication interface, and their pins are not generally used as general-purpose inputs. These pins are used to set the communication mode, and their use should not be changed since that would affect the chip's behavior.

#### 2.9.5 Master Protection Command Register

Pin-pair protection is enabled by writing to the Master Protection Command Register to protect the upper two bits or the lower two bits of any I/O block. The "safe" state is considered to be the state of the protected pins at the time this register is written to; therefore, an "unsafe" state is the bitwise complement of that output. The other two possible bit combinations are considered "active" states since they are allowable outputs.

| Master | Protectio | n Command Register (MPCR) (External Address = 0x14)                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|--------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit(s) | Value     | Description                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 7:4    |           | These bits are reserved and should not be used.                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 3:0    |           | Writing to this register enables the hardware protection for a pair of pins. This protection can only be enabled. Removing the protection requires a hardware reset. This command samples the state of the selected pins to determine the "safe" state. Hardware then enforces this "safe" state between any possible transitions on these pins when they are used as outputs. |  |  |  |  |

| 3:1    | 000       | Enable pin-pair protection in Block 0.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|        | 001       | Enable pin-pair protection in Block 1.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|        | 010       | Enable pin-pair protection in Block 2.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|        | 011       | Enable pin-pair protection in Block 3.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|        | 100       | Enable pin-pair protection in Block 4.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|        | 101       | Enable pin-pair protection in Block 5.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|        | 110       | Enable pin-pair protection in Block 6.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|        | 111       | Enable pin-pair protection in Block 7.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 0      | 0         | Enable protection for Pin[1:0].                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|        | 1         | Enable protection for Pin[3:2].                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

For example, let's say that "11" is the disallowed state (but "00", "01", and "10" are allowed). To enable pin-pair protection on two pins of an I/O block, set the output on both pins to 0 (the "safe" state, which is the complement of the disallowed state) and write the appropriate value to MPCR to enable pin-pair protection. Once this value is written, the protection will be enabled for the selected pair of pins, resulting in the following outputs.

| Written to Pin         | Output from Pin  |

|------------------------|------------------|

| 00                     | 00               |

| 01                     | 01               |

| 10                     | 10               |

| 11 (disallowed output) | 00 (safe output) |

**NOTE:** When pin-pair protection is enabled, the pins will be forced to the safe state between each output transition for a period determined by the Master Protection Prescale Register.

#### 2.9.6 Master Protection Prescale Register

The value written to this register determines the dead-time time constant, a number between 0 and 255. The dead time is useful in preventing overlap during pin-output transitions. When pin-pair protection is enabled on a pair of pins, the Rabbit RIO forces the pins into a "safe" state during the dead time between signal transitions on those pins.

The main Rabbit RIO clock will be divided by (n + 1) to give the dead-time time constant. The actual dead-time will vary between (n + 1) and (2\*n + 2) Rabbit RIO clocks.

| Master Protection Prescale Register |       | (MPPR)                                                      | (External Address = 0x15)                                 |                                                                                                                                                |  |

|-------------------------------------|-------|-------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit(s)                              | Value | Description                                                 |                                                           |                                                                                                                                                |  |

| 7:0                                 |       | where <i>n</i> is the programmed time the dead time for the | I time constant. The pin-pair protection is guaranteed to | the prescaler counts modulo $n + 1$ , the output of the prescaler is used to a. Since this prescaler runs be at least one time constant and no |  |

For example, let's say that "11" is the disallowed state ("00" is then the "safe" state, and "01" and "10" are allowed). When pin-pair protection is enabled for a pair of pins, to switch from "01" to "10", the output will first switch from "01" to "00" for the dead-time specified in MPPR, and then to "10".

#### 2.9.7 Watchdog Timer Registers

All RabbitNet devices and hubs implement a watchdog timer. This timer is restarted on receipt of any command from the master. If it times out, then the device assumes that the communication link has been lost, and the device places itself in a fail-safe state. Once in the fail-safe state, the device must ignore any commands that would cause its output state to change until a soft reset is triggered through the RabbitNet Reset Status Register. This watchdog register is enable only when the Rabbit RIO is being used in the RabbitNet communication mode.

| V      | Vatchdog T | imer x Registers                                                                                                                                                                                                        | (WDT0R)<br>(WDT1R)<br>(WDT2R) | (External Address = 0x1C)<br>(External Address = 0x1D)<br>(External Address = 0x1E) |

|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------|

| Bit(s) | Value      | Description                                                                                                                                                                                                             |                               |                                                                                     |

| 7:0    |            | These registers return the current count of the 23-bit watchdog timer counter, and are primarily for testing, so the entire 23-bit value is not latched. An individual byte may still be used as a pseudo-random value. |                               |                                                                                     |

#### 2.9.8 Pointer Registers

Each I/O block has a Pointer Register that will allow access to the block's internal registers. The lower five bits of this register holds the pointer (or address) to the internal registers. The most significant bit allows auto-incrementing of this pointer for fast configuration.

| Pointer Register x               |       | (PR0)<br>(PR1)<br>(PR2)<br>(PR3)<br>(PR4)<br>(PR5)<br>(PR6)<br>(PR7)   | (External Address = 0x00) (External Address = 0x02) (External Address = 0x04) (External Address = 0x06) (External Address = 0x08) (External Address = 0x0A) (External Address = 0x0C) (External Address = 0x0E) |  |  |

|----------------------------------|-------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit(s)                           | Value | Description                                                            |                                                                                                                                                                                                                 |  |  |

| 7                                | 0     | Disable pointer auto-increment.                                        |                                                                                                                                                                                                                 |  |  |

| 1 Enable pointer auto-increment. |       |                                                                        |                                                                                                                                                                                                                 |  |  |

| 6:5                              |       | These bits are ignored during writes and always return zero when read. |                                                                                                                                                                                                                 |  |  |

| 4:0                              |       | These five bits hold the block re                                      | These five bits hold the block register address for indirect access.                                                                                                                                            |  |  |

#### 2.9.9 Indirect Registers

The Indirect Register of each I/O block allows reads and/or writes to the address pointed to by the Pointer Register.

| Indirect Register x |       | t Register x (IR0) (External Address = 0x01) (IR1) (External Address = 0x03) (IR2) (External Address = 0x05) (IR3) (External Address = 0x07) (IR4) (External Address = 0x09) (IR5) (External Address = 0x0B) (IR6) (External Address = 0x0D) (IR7) (External Address = 0x0F) |  |  |

|---------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit(s)              | Value | Description                                                                                                                                                                                                                                                                  |  |  |

| 7:0                 | Read  | Data from the register addressed by the Pointer Register are returned.                                                                                                                                                                                                       |  |  |

| 7.0                 | Write | Data is written to the register addressed by the Pointer Register.                                                                                                                                                                                                           |  |  |

## 3. BLOCK-LEVEL FEATURES

#### 3.1 Overview

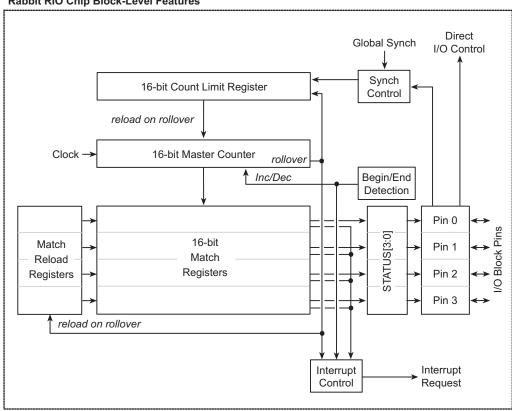

The Rabbit RIO has eight identical I/O blocks. Although these I/O blocks can operate in a number of different modes, the core of each I/O block is a 16-bit counter that can be clocked by the master clock for the device, by the 8-bit Master Prescaler, or by an external source. This counter is accompanied by a number of registers that are updated with control register values each time the counter rolls over. This buffering allows the control register to be updated during the current count cycle with values to be used during the next count cycle. The registers that are buffered this way are the 16-bit reload register and the four 16-bit match registers. The four 16-bit match registers each generate an output pulse when the count is equal to the value programmed into that register. These pulses can be used to set or reset any of the outputs from the I/O block. The 16-bit limit register determines when the counter will be reloaded. Some of the different operating modes that are possible are described in more detail in the later chapters.

#### 3.1.1 Simplified Block Diagram

Rabbit RIO Chip Block-Level Features

# 3.2 Internal Block Registers

| Register Name                                | Mnemonic | Address  | R/W | Reset    |

|----------------------------------------------|----------|----------|-----|----------|

| Pointer Register                             | PR       | External | R/W | 00000000 |

| Indirect Register                            | IR       | External | R/W | xxxxxxx  |

| Command Register                             | CR       | PR=0x00  | W   | 11111111 |

| Mode Register                                | MR       | PR=0x01  | R/W | 00000000 |

| Interrupt Enable Register                    | IER      | PR=0x02  | R/W | 00000000 |

| Status Register                              | SR       | PR=0x03  | R/W | 00000000 |

| Counter Toggle Register                      | CTR      | PR=0x04  | W   | 00000000 |

| Synch Control Register                       | SCR      | PR=0x05  | W   | 00000000 |

| Increment/In-Phase/Begin<br>Control Register | ICR      | PR=0x06  | W   | 00000000 |

| Decrement/Quadrature/End<br>Control Register | DCR      | PR=0x07  | W   | 00000000 |

| Status 0 Control Register                    | S0CR     | PR=0x08  | W   | 00000000 |

| Status 1 Control Register                    | S1CR     | PR=0x09  | W   | 00000000 |

| Status 2 Control Register                    | S2CR     | PR=0x0A  | W   | 00000000 |

| Status 3 Control Register                    | S3CR     | PR=0x0B  | W   | 00000000 |

| Pin 0 Control Register                       | P0CR     | PR=0x0C  | R/W | 00000000 |

| Pin 1 Control Register                       | P1CR     | PR=0x0D  | R/W | 00000000 |

| Pin 2 Control Register                       | P2CR     | PR=0x0E  | R/W | 00000000 |

| Pin 3 Control Register                       | P3CR     | PR=0x0F  | R/W | 00000000 |

| Match 0 LSB Register                         | M0LR     | PR=0x10  | W   | 00000000 |

| Match 0 MSB Register                         | M0MR     | PR=0x11  | W   | 00000000 |

| Match 1 LSB Register                         | M1LR     | PR=0x12  | W   | 00000000 |

| Match 1 MSB Register                         | M1MR     | PR=0x13  | W   | 00000000 |

| Match 2 LSB Register                         | M2LR     | PR=0x14  | W   | 00000000 |

| Match 2 MSB Register                         | M2MR     | PR=0x15  | W   | 00000000 |

| Match 3 LSB Register                         | M3LR     | PR=0x16  | W   | 00000000 |

| Match 3 MSB Register                         | M3MR     | PR=0x17  | W   | 00000000 |

| Count Limit LSB Register                     | CLLR     | PR=0x18  | W   | 00000000 |

| Count Limit MSB Register                     | CLMR     | PR=0x19  | W   | 00000000 |

| Count Begin LSB Register                     | CBLR     | PR=0x1A  | R   | 00000000 |

| Count Begin MSB Register                     | CBMR     | PR=0x1B  | R   | 00000000 |

| Count End LSB Register                       | CELR     | PR=0x1C  | R   | 00000000 |

| Count End MSB Register                       | CEMR     | PR=0x1D  | R   | 00000000 |

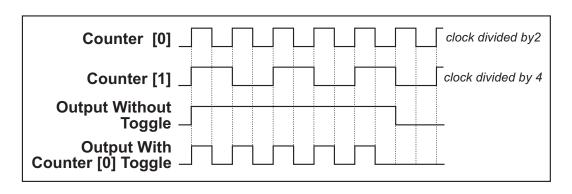

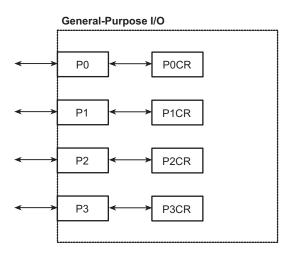

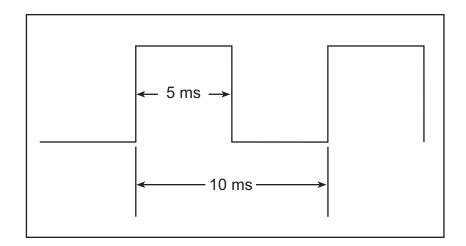

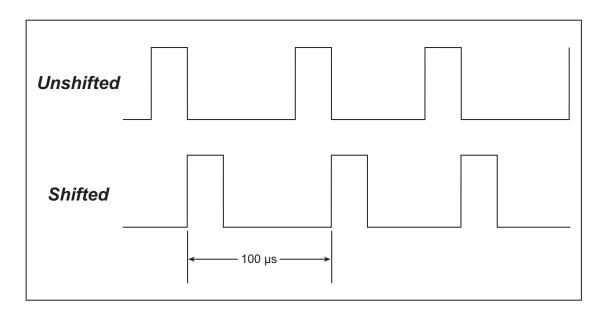

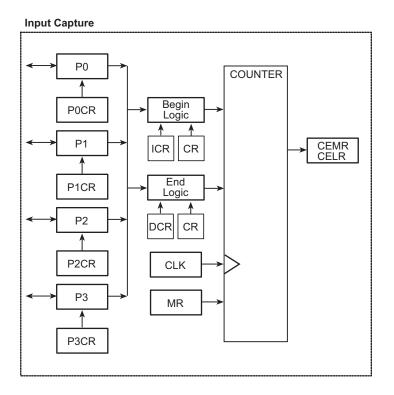

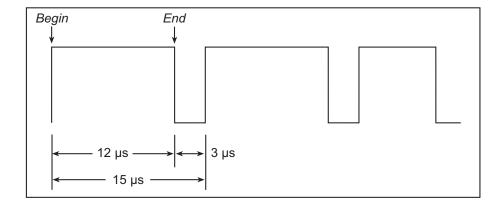

| Count Value LSB Register                     | CVLR     | PR=0x1E  | R   | 00000000 |