# **TDC-V4** Time to Digital Converter

# **User Manual**

v1.1 - July 2013

LUMAT – DTPI (CNRS – UPSud)

# **Revision History**

- Formatting improvements

- Rephrasing to clarify explanations

- Correcting of TRIGGER\_GATE and EXTERNAL\_GATE inversion of FORWARD\_MODE configuration register

# **Table of contents**

| Re | 2 2 2                                    |                                            |    |  |  |  |  |  |

|----|------------------------------------------|--------------------------------------------|----|--|--|--|--|--|

| 1. | Preliminary5                             |                                            |    |  |  |  |  |  |

| 2. | TDC                                      | C-V4 board architecture                    | 6  |  |  |  |  |  |

|    | 2.a.                                     | location of the main electronic components | 6  |  |  |  |  |  |

|    | 2.b.                                     | logical architecture                       | 7  |  |  |  |  |  |

|    | 2.c.                                     | Inputs/Outputs (SCSI-2 50p connector)      | 8  |  |  |  |  |  |

| 3. | Fun                                      | ctions Modes                               | 9  |  |  |  |  |  |

|    | 3.a.                                     | Event definition                           | 9  |  |  |  |  |  |

|    | 3.b.                                     | Acquisition Modes                          | 10 |  |  |  |  |  |

|    | 3.c.                                     | Trigger Modes                              | 12 |  |  |  |  |  |

|    | 3.d.                                     | Analysis Durations                         | 13 |  |  |  |  |  |

|    | 3.e.                                     | Coding Modes                               | 16 |  |  |  |  |  |

|    | 3.f.                                     | Acknowledgment Modes                       | 20 |  |  |  |  |  |

|    | 3.g.                                     | Modes of Function summary                  | 21 |  |  |  |  |  |

| 4. | Con                                      | nmands                                     | 22 |  |  |  |  |  |

|    | 4.a.                                     | Init Commands                              | 22 |  |  |  |  |  |

|    | 4.b.                                     | RUN Command                                | 23 |  |  |  |  |  |

|    | 4.c.                                     | HOST_ACK Command                           | 23 |  |  |  |  |  |

|    | 4.d.                                     | HOST_START Command                         | 24 |  |  |  |  |  |

| 5. | 5. Service signals polarity selection 25 |                                            |    |  |  |  |  |  |

| 6. | Data Format                              |                                            |    |  |  |  |  |  |

| 7. | . Data Encapsulation                     |                                            |    |  |  |  |  |  |

| 8. | . Data collecting through PCI Bus        |                                            |    |  |  |  |  |  |

| 9. | Technical Characteristics                |                                            |    |  |  |  |  |  |

| 10.   | Data collecting rates           | 34 |

|-------|---------------------------------|----|

| 10.a. | . the 3 data collecting methods | 34 |

| 10.b. | . maximum rate without losses   | 36 |

| 11.   | TDC-V4 installation             | 39 |

| 11.a. | . required configuration        | 39 |

| 11.b. | . installation                  | 39 |

| 12.   | DLL Functions                   | 40 |

| 12.a. | . required files                | 40 |

| 12.b. | . functions                     | 40 |

| 13.   | Program example                 | 42 |

| 14.   | TDC-V4 registers summary        | 44 |

# **1. Preliminary**

- TDC-V4 board plugs into a free slot of a 32 or 64 bit PCI Bus.

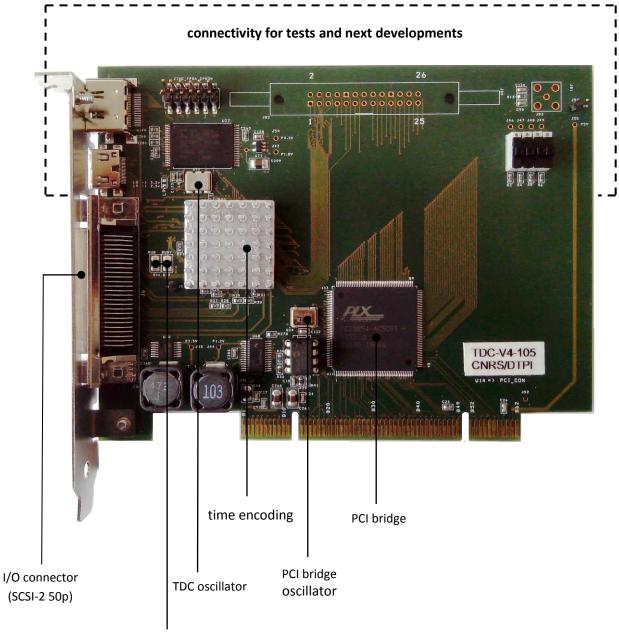

- TDC-V4 operation is guaranteed with an air temperature around the board less than 60°C. If the operating environment does not allow this constraint to be followed, it is possible to set a fan onto the dissipating component (time encoding chip with heat sink, see figure chapter 2.a); a 5.0V supply connector is available for this purpose. Other solution is to restrict the number of time encoding channels to 10 (TDC-V4-10 option : 1 Start Channel + 8 Stop Channels + 1 Additional Channel).

### • Caution :

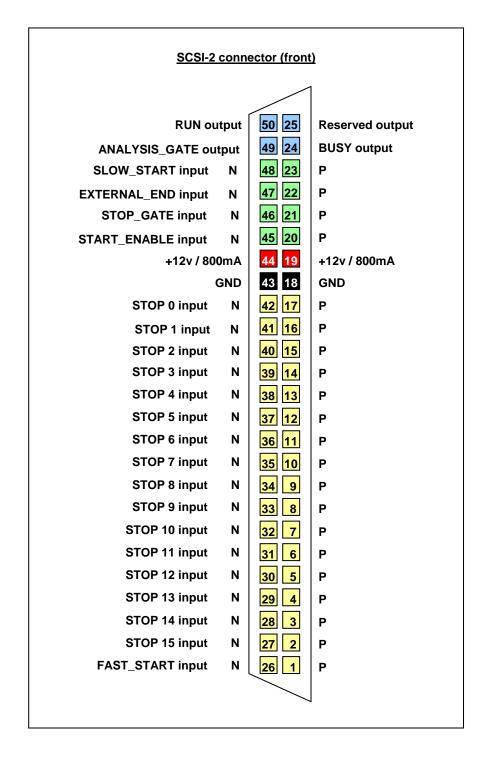

Assignment of SCSI-2 connector pins is characteristic of TDC-V4 board ; the board must not be plugged into a SCSI bus. Particularly, SCSI-2 connector presents two pins delivering +12v / 800mA CC power in order to supply ISIBox Interface (see chapter 2.c and ISIBox User Manual).

- When inserting TDC-V4 board into a PCI slot, it is imperative that computer power is turned off.

- From data collecting point of view, TDC-V4 board is upwards compatible with the ISITime01 TDC family.

- The following graphical conventions are used in this document :

- blue characters for Input/Output signals, for instance : FAST\_START; BUSY

- red characters for modes of function, for instance : STATIC\_STOP\_ENABLE; EBE\_HOST\_ACK

- green characters for commands, for instance : RUN; HOST\_START

- black characters for inner machine states, for instance : Busy

- The quantified characteristics presented in this document are according to TDC-V4 version operating 120 ps step.

- If ISIBox is used as TDC-V4 Interface, mechanical and electrical standards of the Input/Output signals are described in the ISIBox User Manual.

# 2. TDC-V4 board architecture

# 2.a. location of the main electronic components

RUN and BUSY LEDs

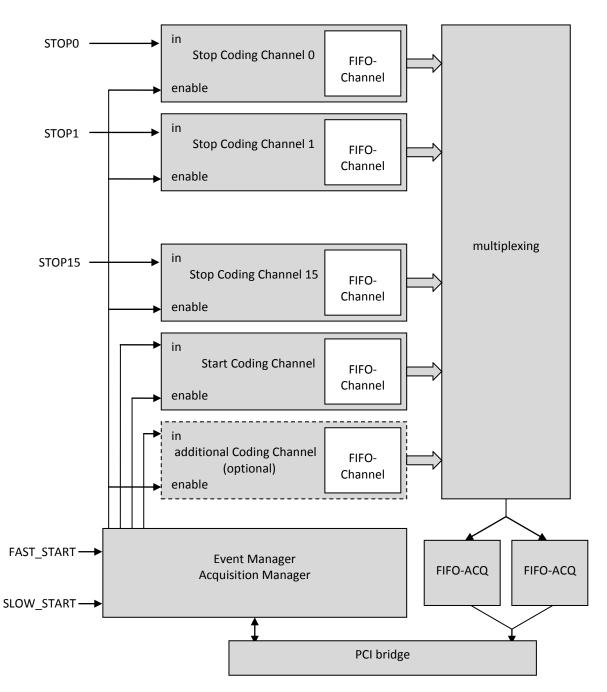

- FIFO-Channel : single buffer ; memory depth : 512 Time Encoding words

- buffers encoding words from a same Event

- a new Event cannot be accepted as long as the FIFO-Channel is not emptied of the Encoding words of the previous Event. ; therefore several Events cannot coexist in a FIFO-Channel.

2 x FIFO-ACQ : - double toggle buffering ; each memory depth : 509 words (32 bits)

- in Event By Event Mode (EBE\_HOST\_ACK, EBE\_TDC\_AUTO et EBE\_EXT\_END), stores Encoding or Service words from a same Event

- in Accumulation Mode (ACC\_TDC\_AUTO), several Events may coexist in a FIFO-ACQ buffer.

### 2.c. Inputs/Outputs (SCSI-2 50p connector)

# **3.** Functions Modes

### 3.a. Event definition

An Event concerns all the information (Coding Words and Service Words) in relation to a single physical action. Then, an Event may present a small number of words (for instance : locating of a few particles after interaction), a large number of words (for instance : time of flight mass spectrometry) or a very large number of words (for instance : "cold atoms" experiments).

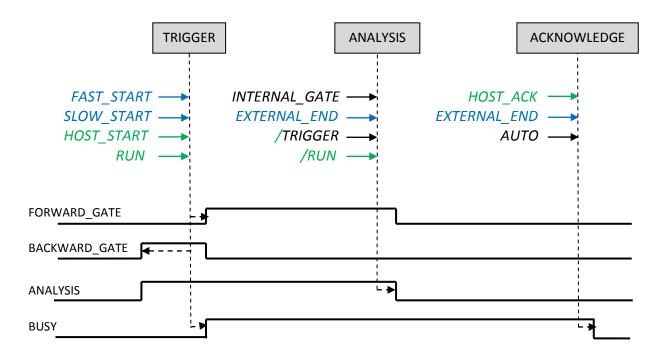

On a logical point of view, an Event is specified by :

- a Trigger signal (TRIGGER)

- > an Analysis duration (ANALYSIS)

- > an Acknowledgment signal (ACKNOWLEDGE)

- > an Acquisition Mode.

Between TRIGGER and ACKNOWLEDGE signals, TDC-V4 is in the Busy state: it cannot collect a new Event. The Busy state = 1 is displayed by a LED on the printed circuit and on the front panel of ISIBox Interface.

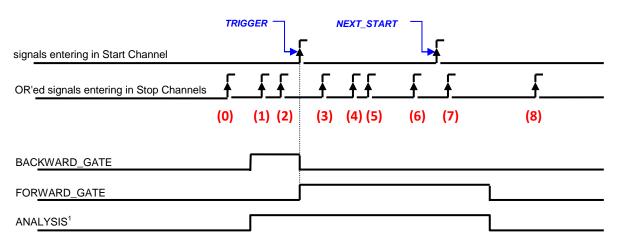

Event processing is represented by the following chronogram.

### 3.b. Acquisition Modes

Each Coding Channel has a single buffer with 512 words depth FIFO-Channel memory and all FIFOs are empty at the trigger time of a new Event. So, except for Events presenting very large Stop rate, a Channel may not sustain losses due to the Stop rate on another channel.

Output data from FIFO-Channels of the Start and Stop Coding Channels are multiplexed and stored into one of the two FIFO-ACQ output buffers which operate in toggle buffering mode, as signals are encoded as soon as Analysis Duration begins (see chapter 2.b : logical architecture).

The multiplexing mechanism gives an equal access probability for all the Channels ; only the first encoding on the Start Coding Channel has priority. This mechanism ensures that a Channel with a large Stop rate does not result in losses on a Channel with a low Stop rate. In the FIFO-ACQ output buffers, chronological order is for the encoding words coming from a same Channel ; it may be not maintained among the encoding words coming from separate Channels.

Whichever the selected data collecting mode (see below), the quantity of data making up an Event is unlimited : the acquisition software is called each time a FIFO-ACQ output buffer has data to output and is informed of the quantity of relevant data ( $\leq$  509 words of 32 bits).

After the last word related to an Event (that is to say the EOE Service Word) is stored in one of the two FIFO-ACQ output buffers, TDC-V4 proposes two main data collecting modes :

- Event by Event collecting Mode

- Accumulation collecting Mode

#### Event by Event collecting Mode

The acquisition software is informed that a data table is ready for reading and is informed of the quantity of the available relevant data ( $\leq$  509 words of 32 bits). TDC-V4 waits for Event Acknowledgment (see chapter 3.f : Acknowledgment Modes) before accepting a new Trigger.

Due to the acquisition system latency, this regulating mode is not very rate effective and is all the less effective because the size of the Event is small (see chapter 10 : data collecting mean rate). Nevertheless, this regulating mode must be used if TDC-V4 is correlated with other encoding devices, because all the other data sources making up an Event must be collected by the acquisition software before TDC-V4 is allowed to encode a new Event.

#### Accumulation collecting Mode

TDC-V4 self-acknowledges the Event in progress and is ready to accept a new Trigger. Then, TDC-V4 accumulates the data in succession into FIFO-ACQ output buffers the data related to the successive Events.

This regulating mode is more effective from mean rate point of view and is all the more effective because the size of the Event is small (see chapter 10 : data collecting mean rate). It is suitable for setups which have the TDC-V4 as the only data source.

#### Particular Accumulation collecting Mode : Continuing Analysis

In this configuration, TDC-V4 no longer filters signals by means of Trigger, Analysis Duration and Acknowledgment : all the signals occurring at the input of the validated Start and Stop Channels are encoded from a single Trigger instant and during the entire time the TDC-V4 remains in state Run = ON.

For instance, if Trigger is selected with TRIGGER\_SOURCE = RUN + HOST\_START (see chapter 3.c : Trigger Modes), the whole Run is logically considered as an unique Event with an infinite Analysis Duration, all the signals are encoded during duration of the Run and all the encoding results are stored in succession in the FIFO-ACQ output buffers.

<u>This collecting Mode is the more effective from rate point of view</u> (see chapter 10 : data collecting rate) because filtering of the data and Event building are assigned to the acquisition software.

This collecting Mode is chosen by selecting FORWARD\_MODE = EXTERNAL\_GATE with no signal present in the EXTERNAL\_END input.

### 3.c. Trigger Modes

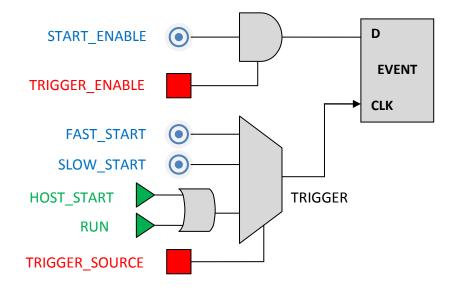

An Event can be triggered from 4 sources :

- either of the FAST\_START or SLOW\_START input signals; if the ISIBox Interface is used, FAST\_START is a NIM signal and SLOW\_START is a TTL signal

- HOST\_START command ; this Trigger Mode may be used for tests or in order to measure physical backward noise by random sampling

- RUN command ; this Trigger Mode may be used to trigger the Continuing Analysis collecting Mode mentioned above without the necessity to generate a signal neither by hardware or by software.

Moreover, Trigger can be validated or inhibited by the START\_ENABLE input signal.

Trigger sources are represented on the following figure :

Trigger Modes are controlled by the following registers :

| name           | PCI       |                       | data           |                            |

|----------------|-----------|-----------------------|----------------|----------------------------|

|                | address   |                       |                |                            |

| TRIGGER_SOURCE | 240 0000h | 2 <sup>1</sup>        | 2 <sup>0</sup> | source                     |

|                |           | 0                     | 0              | reserved                   |

|                |           | 0                     | 1              | FAST_START                 |

|                |           | 1                     | 0              | SLOW_START                 |

|                |           | 1                     | 1              | RUN + HOST_START           |

| TRIGGER_ENABLE | 220 0000h | <b>2</b> <sup>5</sup> | 2 <sup>4</sup> | enabling                   |

|                |           | 0                     | 1              | START_ENABLE as Enable On  |

|                |           | 0                     | 0              | START_ENABLE as Enable Off |

### 3.d. Analysis Durations

### > FORWARD ANALYSIS

Once the Event is triggered, signals entering into Coding Channels are encoded during a duration beginning immediately after the trigger instant and lasting according to one among the 4 following Forward Modes :

- a preset time inside TDC-V4 (INTERNAL\_GATE)

- the EXTERNAL\_END input (EXTERNAL\_GATE)

- the first of the two signals : EXTERNAL\_END input or preset time inside TDC-V4 (EXTERNAL\_GATE / WATCHDOG)

- the duration of TRIGGER signal itself

The last Analysis Duration Mode is the easiest to adjust precisely the analysis duration : for instance, select FAST\_START as trigger source and adjust the duration of the FAST\_START input signal.

An infinite FORWARD Duration is configured by selecting EXTERNAL\_GATE mode and suppressing any signal onto EXTERNAL\_END input. Moreover, trigger an infinite duration may be got without input signal by selecting TRIGGER\_SOURCE = RUN + HOST\_START (see chapter 3.c).

The FORWARD\_MODE, and the FORWARD\_DURATION if INTERNAL\_GATE is selected, are controlled by the following registers :

| name             | PCI       |                | data           |          |                 |

|------------------|-----------|----------------|----------------|----------|-----------------|

|                  | address   | -6             | -5             |          |                 |

| FORWARD_MODE     | 1C0 0000h | 2 <sup>6</sup> | 2 <sup>5</sup> |          | source          |

|                  |           | 0              | 0              | TRIGGER  |                 |

|                  |           | 0              | 1              | INTERNAL |                 |

|                  |           | 1              | 0              | EXTERNAL | —               |

|                  |           | 1              | 1              |          | GATE / WATCHDOG |

| FORWARD_DURATION | 1C0 0000h |                | $2^4 2^3 2^4$  |          | duration        |

|                  |           |                | 0              |          | 180 ns          |

|                  |           |                | 1              |          | 260 ns          |

|                  |           |                | 2              |          | 340 ns          |

|                  |           |                | 3              |          | 500 ns          |

|                  |           |                | 4              |          | 660 ns          |

|                  |           |                | 5              |          | 980 ns          |

|                  |           |                | 6              |          | 1.3 µs          |

|                  |           |                | 7              |          | 1.9 µs          |

|                  |           |                | 8              |          | 2.5 µs          |

|                  |           | 9              |                |          | 3.8 µs          |

|                  |           | 10             |                |          | 5.1 µs          |

|                  |           |                | 11             |          | 7.6 µs          |

|                  |           |                | 12             |          | 10 µs           |

|                  |           |                | 13             |          | 15 µs           |

|                  |           |                | 14             |          | 20 µs           |

|                  |           |                | 15             |          | 30 µs           |

|                  |           |                | 10             |          | 41 µs           |

|                  |           |                | 17             |          | 61 µs           |

|                  |           | 18             |                |          | 82 µs           |

|                  |           | 19             |                |          | 120 µs          |

|                  |           | 20             |                |          | 160 µs          |

|                  |           |                | 21             |          | 240 µs          |

|                  |           |                | 22             |          | 320 µs          |

|                  |           | 23             |                |          | 490 µs          |

|                  |           |                | 24             |          | 650 µs          |

|                  |           | 25             |                |          | 980 µs          |

|                  |           | 26             |                |          | 1.3 ms          |

|                  |           | 27             |                |          | 1.9 ms          |

|                  |           | 28<br>29       |                |          | 2.6 ms          |

|                  |           |                |                |          | 3.9 ms          |

|                  |           |                | 30             |          | 5.2 ms          |

|                  |           |                | 32             | L        | 7.8 ms          |

### > BACKWARD ANALYSIS

TDC-V4 may encode Stop signals during a **BACKWARD\_DURATION** before the trigger time. This Mode avoids having to delay the Stop input signals occurring before the signal used to trigger the event.

| name              | PCI       | da                        | ita      |

|-------------------|-----------|---------------------------|----------|

|                   | address   |                           |          |

| BACKWARD_MODE     | 180 0000h | 2 <sup>5</sup>            | enabling |

|                   |           | 0                         | OFF      |

|                   |           | 1                         | ON       |

| BACKWARD_DURATION | 180 0000h | $2^{3} 2^{2} 2^{1} 2^{0}$ | duration |

|                   |           | 0                         | 0 ns     |

|                   |           | 1                         | 0 ns     |

|                   |           | 2                         | 120 ns   |

|                   |           | 3                         | 240 ns   |

|                   |           | 4                         | 360 ns   |

|                   |           | 5                         | 610 ns   |

|                   |           | 6                         | 860 ns   |

|                   |           | 7                         | 1.3 µs   |

|                   |           | 8                         | 1.8 µs   |

|                   |           | 9                         | 2.8 µs   |

|                   |           | 10                        | 3.8 µs   |

|                   |           | 11                        | 5.7 µs   |

|                   |           | 12                        | 7.7 µs   |

|                   |           | 13                        | 11.6 µs  |

BACKWARD Mode and its Analysis Duration are controlled by the following registers :

Notes :

If BACKWARD\_MODE is disabled, TDC-V4 presents a short dead time between the Event Trigger time and the time when the Stop Channels can encode (see Start Latency Time chapter 9 : Technical Characteristics).

If BACKWARD\_MODE is enabled and BACKWARD\_DURATION = 0 ns, the Start Latency Time = 0 ns.

BACKWARD\_MODE does not operate with the Coding Start Channel.

### 3.e. Coding Modes

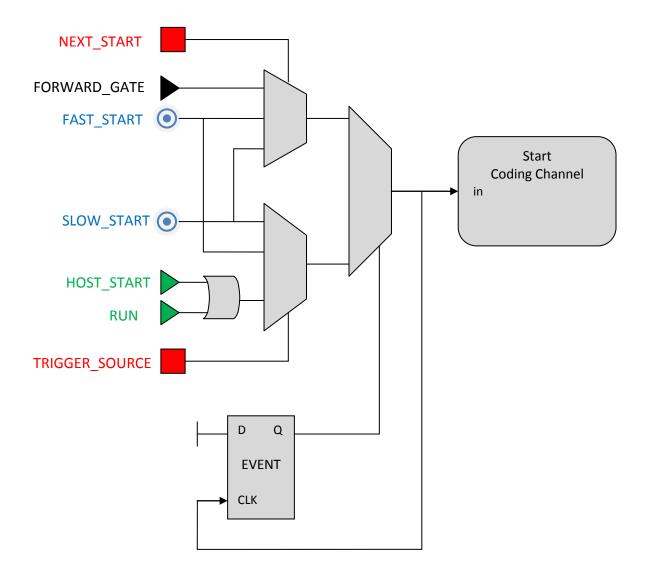

#### > Start Coding Channel: NEXT\_START mode

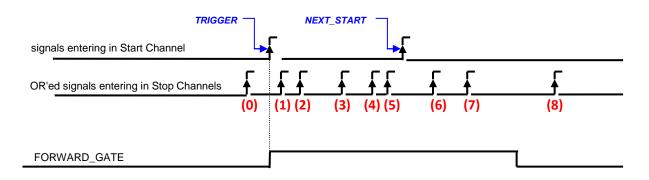

The Start Coding Channel encodes the Event Trigger time. During data encapsulation, the Encoding Word delivered by this Channel is automatically placed at the beginning of the table of data relative to the Event, whether Backward Mode is used or not (see chapter 7 : Data Encapsulation).

Data Encapsulation necessarily ends the table of data relative to an Event with the Service Word EOE ; then, Coding Channel Start may, without chance of making a mistake during Event Building, encode signals occurring after the trigger time. We call these Next Starts signals.

In NEXT\_START mode, TDC-V4 permits to select as Next Start one of the 3 following signals (see diagram on next page) :

- FAST\_START

- SLOW\_START

- FORWARD\_GATE

In this way, if Interface ISIBox is used, TDC-V4 can operate the 4 following set up :

| Trigger<br>signal | next signals | note                                    |

|-------------------|--------------|-----------------------------------------|

| FAST_START        | FAST_START   | Event pile-up detection                 |

| NIM               | NIM          |                                         |

| FAST_START        | SLOW_START   | Extra Stop encoding channel (TTL input) |

| NIM               | TTL          |                                         |

| SLOW_START        | FAST_START   | Extra Stop encoding channel (NIM input) |

| TTL               | NIM          |                                         |

| SLOW_START        | SLOW_START   | Event pile-up detection                 |

| TTL               | TTL          |                                         |

FORWARD\_GATE source selection of the Next Starts permits to control the actual value of the Analysis Duration, particularly if this duration is variable (EXTERNAL\_GATE mode).

NEXT\_START mode is controlled by the following register :

| name       | PCI<br>address | data           |                       |                   |

|------------|----------------|----------------|-----------------------|-------------------|

| NEXT_START | 220 0000h      | 2 <sup>1</sup> | <b>2</b> <sup>0</sup> | Next Start source |

|            |                | 0              | 0                     | OFF               |

|            |                | 0 1 FAST_START |                       | FAST_START        |

|            |                | 1              | 0                     | SLOW_START        |

|            |                | 1              | 1                     | FORWARD_GATE      |

### Operating in NEXT START mode

### Start Coding Channel: EVENT\_LABELLING

The state of the START\_ENABLE input signal at the Trigger instant can be stored and reported into the Start Coding Word (bit EL; see chapter 6 : Data Format).

This function is controlled by the following register :

| name            | PCI       | data                         |                |                           |

|-----------------|-----------|------------------------------|----------------|---------------------------|

|                 | address   |                              |                |                           |

| EVENT_LABELLING | 220 0000h | <b>2</b> <sup>5</sup>        | 2 <sup>4</sup> | enabling                  |

|                 |           | 1 1 START_ENABLE as Label On |                | START_ENABLE as Label On  |

|                 |           | 1                            | 0              | START_ENABLE as Label Off |

### > Additional Coding Channel (optional)

This optional Channel encodes either of the two following input signals :

- SLOW\_START

- EXTERNAL\_END

If either SLOW\_START or EXTERNAL\_END is not used (Trigger by SLOW\_START ; Analysis Duration by EXTERNAL\_END), the Additional Coding Channel permits to extend the number of Coding Channels to 17 and, if Interface ISIBox is used, to encode a TTL input signal.

The Additional Coding Channel does not benefit from static or dynamic enabling capabilities (see next paragraph).

Input signal selection is controlled by the following register :

| name          | PCI     | data                        |              |  |

|---------------|---------|-----------------------------|--------------|--|

|               | address |                             |              |  |

| EXTRA_CHANNEL | NA      | 2 <sup>0</sup> input signal |              |  |

|               |         | 0 SLOW_START                |              |  |

|               |         | 1                           | EXTERNAL_END |  |

### > Stop Coding Channels: enabling

Coding Channels can be enabled or disabled :

- <u>statically</u> for each Channel

- <u>dynamically</u> for the whole 16 Channels by means of the STOP\_GATE input signal

Enabling of the Stop Coding Channels is controlled by the following registers :

| name               | PCI<br>address | data           |                              |  |

|--------------------|----------------|----------------|------------------------------|--|

| STATIC_STOP_ENABLE | 120 0000h      | 2 <sup>i</sup> | static enabling of i channel |  |

|                    |                | 0              | OFF                          |  |

|                    |                | 1              | ON                           |  |

| DYNAM_STOP_ENABLE  | 220 0000h      | 2 <sup>3</sup> | enabling by STOP_GATE        |  |

|                    |                | 0              | OFF                          |  |

|                    |                | 1              | ON                           |  |

#### Stop Coding Channels: Overflow

TDC-V4 empties the FIFO-Channel memory of each Channel as soon as Forward Analysis begins. If the rate of the experiment is larger than the rate of the data collecting system, the FIFO-Channel of a Channel may overflow.

In this case, the FIFO-Channel of this Channel becomes "Full" and the first Coding Word which will be delivered by the Channel is stamped in his Label Field by means of the bit OF (see chapter 6 : Data format).

### > Service Channel Range Extension REXT (optional)

TDC-V4 delivers Coding Words and Service Words, 32 bits wide. These Words are composed with 2 fields (see chapter 6 : Data format) :

- DATA field, 26 bits wide

- <u>LABEL field</u>, 6 bits wide.

The DATA field extends the maximum range of the Coding Channels to  $2^{26} \times 120 \text{ ps} = 7.8 \text{ ms.}$

Implementation of the unique Service Channel Range Extension permits to extend beyond 7.8 ms the time range of all the 32 bits wide Coding Channels. The DATA extension beyond 26 bits has to be processed by the acquisition software.

The Service Channel Range Extension is not provided with a FIFO-Channel memory.

### Stop Coding Channels: RESOLUTION/DNL optimization

TDC-V4 provides a mechanism in order to optimize either the Resolution figure (at the expense of the DNL characteristics) or the DNL characteristics (at the expense of the Resolution figure) ; this optimization is valid overall for all the Coding Channels (with or without Range Extension).

| name         | PCI       | data                                    |            |  |

|--------------|-----------|-----------------------------------------|------------|--|

|              | address   |                                         |            |  |

| OPTIMIZATION | 220 0000h | 2 <sup>2</sup> Optimized characteristic |            |  |

|              |           | 0                                       | RESOLUTION |  |

|              |           | 1                                       | DNL        |  |

This optimization is controlled by the following register :

Note 1 : Differential Non Linearity (quantifies the actual bins width inequality)

### 3.f. Acknowledgment Modes

Possibilities of Event Acknowledgment according to the suitable Acquisition Mode for the experiment are presented on the following table :

| Acquisition<br>Mode | Acknowledgment<br>Mode |                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | EBE_HOST_ACK           | TDC-V4 supplies to the acquisition software<br>processor only the data relative to one Event and<br>enables a new Trigger after it is acknowledged by<br>the acquisition software by means of the<br>command HOST_ACK.                                                                                                                                                                                  |

| Event by Event      | EBE_EXT_END            | TDC-V4 supplies to the acquisition software only<br>the data relative to one Event and enables a new<br>Trigger after it is acknowledged by means of the<br>command EXTERNAL_END.                                                                                                                                                                                                                       |

|                     | EBE_TDC_AUTO           | TDC-V4 supplies to the acquisition software only<br>the data relative to one Event and enables a new<br>Trigger as soon as all the data relative to this Event<br>are stored into FIFO-ACQ output buffers. <i>This</i><br><i>Acknowledgment Mode involves that the user</i><br><i>controls the Trigger signal in order to ensure the</i><br><i>correlation of all data sources making up the Event.</i> |

| Accumulation        | ACC_TDC_AUTO           | TDC-V4 piles up in succession into FIFO-ACQ output buffer the data related to the successive Events. Each Event is acknowledged automatically as soon as all the data relative to an Event are stored into FIFO-ACQ output buffers.                                                                                                                                                                     |

Acknowledgment Mode selection is controlled by the following register :

| name     | PCI<br>address | data                  |                       |                        |

|----------|----------------|-----------------------|-----------------------|------------------------|

| ACK_MODE | 260 0000h      | <b>2</b> <sup>1</sup> | <b>2</b> <sup>0</sup> | mode                   |

|          |                | 0                     | 0                     | ACC_TDC_AUTO           |

|          |                | 0                     | 1                     | EBE_TDC_AUTO           |

|          |                | 1                     | 0                     | EBE_EXT_END (optional) |

|          |                | 1                     | 1                     | EBE_HOST_ACK           |

# 3.g. Modes of Function summary

|                      | default                                                                                                                                                                                                                     | values |                                  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------|

| Trigger Modes        | <ul> <li>TRIGGER SOURCE<br/>FAST_START<br/>SLOW_START<br/>RUN + HOST_START</li> <li>TRIGGER ENABLE<br/>START_ENABLE as Enable</li> </ul>                                                                                    | 3-с    | FAST_START<br>OFF                |

| Analysis Duration    | <ul> <li>FORWARD ANALYSIS         <ul> <li>INTERNAL_GATE / duration table</li> <li>EXTERNAL_GATE</li> <li>EXTERNAL_GATE / WATCHDOG</li> <li>TRIGGER_GATE</li> </ul> </li> <li>BACKWARD ANALYSIS / duration table</li> </ul> | 3-d    | INTERNAL<br>(180ns)<br>OFF (0ns) |

|                      | Start Coding Channel<br>• NEXT_START<br>FAST_START<br>SLOW_START<br>FORWARD_GATE<br>• EVENT_LABELLING<br>START_ENABLE as Label                                                                                              | 3-е    | OFF                              |

| Coding Modes         | <u>Additional Coding Channel</u> (optional)<br>• INPUT<br>SLOW_START<br>EXTERNAL_END                                                                                                                                        |        |                                  |

|                      | <u>Stop Coding Channels</u><br>• STATIC_STOP_ENABLE<br>• DYNAM_STOP_ENABLE<br><u>Service Channel Range Extension</u> (optional)                                                                                             |        | all enabled<br>OFF               |

|                      | Coding Channel Stop Overflow<br>RESOLUTION/DNL Optimization                                                                                                                                                                 |        | RESOLUTION                       |

| Acknowledgment Modes | <u>Data collecting</u><br>EBE_HOST_ACK<br>EBE_EXT_END (optional)<br>EBE_TDC_AUTO<br>ACC_TDC_AUTO                                                                                                                            | 3-f    | ACC_TDC_AUTO                     |

<u>Note</u> :

Modes configuration registers access is write only.

# 4. Commands

### 4.a. Init Commands

### Function Modes Initialization

The Command is controlled by the following register :

| name      | PCI<br>address | data                  |         |

|-----------|----------------|-----------------------|---------|

| INIT_CONF | 140 0000h      | <b>2</b> <sup>0</sup> | command |

|           |                | 0                     | OFF     |

|           |                | 1                     | ON      |

INIT\_CONF = ON Command must be followed by INIT\_CONF = OFF Command.

Be careful with this Command : after this Command executed, Function Modes get their default values as described chapter 3.g and may not to correspond to the one displayed by the Configuration utility program.

### > TDC-V4 logical state Initialization

The Command is controlled by the following register :

| name     | PCI       | data                  |         |

|----------|-----------|-----------------------|---------|

|          | address   |                       |         |

| INIT_TDC | 160 0000h | <b>2</b> <sup>0</sup> | command |

|          |           | 0                     | ON      |

|          |           | 1                     | OFF     |

INIT\_TDC = ON Command must be followed by INIT\_TDC = OFF Command. TDC-V4 logical state is automatically initialized while TDC-V4 powering on.

### 4.b. RUN Command

RUN Command carries out several functions :

- in any case, RUN = ON enables Event Trigger

- in the TRIGGER\_SOURCE = RUN + HOST\_START case (see chapter 3.c: Trigger Modes), RUN = ON triggers an Event processing

- in the infinite Forward Duration case (see chapter 3.d: Analysis Duration), RUN = OFF ends the Analysis Duration

- in any case RUN = OFF

- disables Event Trigger

- transfers to the acquisition software, if data collecting is not stopped, all the data present in TDC-V4

- closes the last data table with EOR Service Word (see chapter 6 : Data Format).

The Command is controlled by the following register :

| name | PCI       | data           |         |

|------|-----------|----------------|---------|

|      | address   |                |         |

| RUN  | 1A0 0000h | 2 <sup>0</sup> | command |

|      |           | 0              | OFF     |

|      |           | 1              | ON      |

RUN = ON state is displayed by means of a LED on the TDC-V4 printed circuit board as well as on the ISIBox Interface front panel.

### 4.c. HOST\_ACK Command

HOST\_ACK Command is used by EBE\_HOST\_ACK Acknowledgment Mode (see chapter 3.f: Acknowledgment Modes) in order to regulate the Event By Event throughput.

The Command is controlled by the following register :

| name     | PCI<br>address | data           |         |

|----------|----------------|----------------|---------|

| HOST_ACK | 2C0 0000h      | 2 <sup>0</sup> | command |

|          |                | 0              | OFF     |

|          |                | 1              | ON      |

HOST\_ACK = ON Command must be followed by HOST\_ACK = OFF Command.

### 4.d. HOST\_START Command

HOST\_START command is used by TRIGGER\_SOURCE = RUN + HOST\_START Trigger Mode (see chapter 3.c : Trigger modes).

The Command is controlled by the following register :

| name       | PCI       | data                  |         |

|------------|-----------|-----------------------|---------|

|            | address   |                       |         |

| HOST_START | 2E0 0000h | <b>2</b> <sup>0</sup> | command |

|            |           | 0                     | OFF     |

|            |           | 1                     | ON      |

HOST\_START = ON Command must be followed by HOST\_START = OFF Command.

<u>Note</u>: Command registers access is write only.

# **5. Service signals polarity selection**

Selection of the polarity of each of the START\_ENABLE, STOP\_GATE, EXTERNAL\_END and SLOW\_START input signals as well as of each of the ANALYSIS\_GATE and BUSY output signals is controlled by the following register :

| name     | PCI<br>address | data                                                                                               |

|----------|----------------|----------------------------------------------------------------------------------------------------|

| POLARITY | 280 0000h      | 2 <sup>5</sup> 2 <sup>4</sup> 2 <sup>3</sup> 2 <sup>2</sup> 2 <sup>1</sup> 2 <sup>0</sup> polarity |

|          |                | x     x     x     x     0       START_ENABLE input: active low                                     |

|          |                | x x x x x 1 START_ENABLE input: active high                                                        |

|          |                | x x x x 0 x STOP_GATE input: active low                                                            |

|          |                | x x x x 1 x STOP_GATE input: active high                                                           |

|          |                | x x x 0 x x EXTERNAL_END input: active low                                                         |

|          |                | x x x 1 x x EXTERNAL_END input: active high                                                        |

|          |                | x x 0 x x x SLOW_START input: active low                                                           |

|          |                | x x 1 x x x SLOW_START input: active high                                                          |

|          |                | x 0 x x x x BUSY output: active low                                                                |

|          |                | x 1 x x x x BUSY output: active high                                                               |

|          |                | 0 x x x x x ANALYSIS_GATE output: active low                                                       |

|          |                | 1 x x x x x ANALYSIS_GATE <i>output: active high</i>                                               |

### <u>Note :</u>

If ISIBox Interface is used, the state of Busy LED in front panel depends on the selected polarity for BUSY signal (Lemo00 in front panel) :

- if BUSY signal is active high, the LED is ON while TDC-V4 is in Busy state

- if BUSY signal is active low, the LED is OFF while TDC-V4 is in Busy state.

<u>Note</u> :

Polarity Selection registers access is write only.

Polarity Selection default values are in Active high state.

# 6. Data Format

TDC-V4 delivers Coding Words and Service Words. The 32 bits wide Word decomposes into 2 fields :

- 26 bits wide DATA field

- 6 bits wide <u>LABEL field</u>.

The 6 bits wide LABEL field permits 64 various Labels, thus to distinguish 64 data sources. Among these 64 Labels, 50 Labels are allotted and are listed on the table next page :

- *bold type Labels* are allotted to data source types developed in the TDC-V4 version described in this User Manual

- *dimmed Labels* are allotted to data source types which may be developed in accordance with the user's needs

The last 14 Labels are available for exotic data sources as Counting Scale, Rate meter, ADC, QDC,  $\dots$ .

| LABEL                                                                                           | FUNCTION                                                                                                                                                                                                                                                                | DATA                                                          |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 2 <sup>31</sup> 2 <sup>30</sup> 2 <sup>29</sup> 2 <sup>28</sup> 2 <sup>27</sup> 2 <sup>26</sup> |                                                                                                                                                                                                                                                                         | 2 <sup>25</sup> 2 <sup>24</sup> 2 <sup>1</sup> 2 <sup>0</sup> |

| 0 n n n n m                                                                                     | <ul> <li><u>TDC 16 Stop Channels / 1 word encoding with mark</u><br/>nnnn = Channel number<br/>m = OF (OverFlow FIFO-Channel)</li> <li><u>TDC 16 Stop Channels / 2 words / duration</u><br/>nnnn = Channel number<br/>m = 0 rising edge ; m = 1 falling edge</li> </ul> | absolute time                                                 |

|                                                                                                 | - <u>TDC 16 Stop Channels / 2 words / high resolution</u><br>nnnn = Channel number<br>m = 1 MSB's ; m = 0 LSB's                                                                                                                                                         | absolute time                                                 |

| 0 n n n n n                                                                                     | <ul> <li><u>TDC 32 Stop Channels / 1 word encoding</u></li> <li>nnnnn = Channel number</li> </ul>                                                                                                                                                                       | absolute time                                                 |

| 10000EL                                                                                         | <ul> <li><u>Start Channel / 1 word encoding with mark</u></li> <li>EL = START_ENABLE input as Label (unless EL = 0)</li> </ul>                                                                                                                                          | absolute time                                                 |

| 100101                                                                                          | - Additional Channel / 1 word encoding                                                                                                                                                                                                                                  | absolute time                                                 |

| 10001EL                                                                                         | - <u>Start Channel / 2 words encoding with mark /</u> MSB's<br>EL = START_ ENABLE input as label (unless EL = 0)                                                                                                                                                        | absolute time                                                 |

| 100100                                                                                          | - <u>Start Channel / 2 words encoding</u> / LSB's absolute time                                                                                                                                                                                                         |                                                               |

| 10011m                                                                                          | - <u>Additional Channel / 2 word encoding</u><br>m = 1 MSB's; m = 0 LSB's absolute time                                                                                                                                                                                 |                                                               |

| 11100m                                                                                          | $-\frac{REXT (Range Extension)}{m = 0 \ 1^{st} \text{ semi-period 7.8 ms}} $ (count)*<br>m = 1 2 <sup>nd</sup> semi-period 7.8 ms                                                                                                                                       |                                                               |

| 1 1 0 0 0 0                                                                                     | - <u>EOE (End Of Event) / 1 word</u>                                                                                                                                                                                                                                    | free                                                          |

| 11001m                                                                                          | - <u>EOE-N (End Of Event / Event Number) / 2 words</u><br>m = 1 MSB's<br>m = 0 LSB's                                                                                                                                                                                    | event number                                                  |

| 11010m                                                                                          | - <u>EOE-T (End Of Event / Event Time) / 2 words</u><br>m = 1 MSB's<br>m = 0 LSB's                                                                                                                                                                                      | time flag                                                     |

| 1 1 0 1 1 0                                                                                     | - <u>SOR (Start Of Run)</u> (run number)                                                                                                                                                                                                                                |                                                               |

| 1 1 0 0 0 1                                                                                     | - <u>EOR (End Of Run)</u>                                                                                                                                                                                                                                               | (run number)*                                                 |

| 1 1 0 1 1 0                                                                                     | - <u>EOS (End Of Source)</u>                                                                                                                                                                                                                                            | source number                                                 |

\* to be specified

Coding Channel

Service Channel

# 7. Data Encapsulation

Data encapsulation is independent of any Function Mode.

Data relatives to an Event and delivered by Stop Channels, Start Channel (if NEXT\_START mode is selected), Additional Channel (if the option is implemented) and Range Extension Service Channel (if the option is implemented) are bulked into an unique table (which may be shared between consecutive buffers according to the Event size and the Acquisition Mode) and are enclosed with the two following words :

- <u>at the head of the table</u> : the Start Channel Word encoding the Trigger instant

- <u>at the rear of the table</u> : EOE (End Of Event) Service Word.

The illustration below presents an example of Data Encapsulation :

| START_WORD     |

|----------------|

| STOP_WORD (1)  |

| STOP_WORD (2)  |

| STOP_WORD (3)  |

| STOP_WORD (4)  |

| STOP_WORD (5)  |

| START_WORD (*) |

| STOP_WORD (6)  |

| STOP_WORD (7)  |

| EOE_WORD       |

(\*) if NEXT\_START mode is selected

#### <u>Notes</u> :

- Chronological order of encodings of the signals entering a same Channel is restored after encapsulation.

- Chronological order of encodings of the signals entering different Channels is not maintained after encapsulation.

- Chronological order of encodings of the signals entering Start Channel with NEXT\_START mode selected is restored after encapsulation. The first encoding word delivered by Start Channel is distinguished from the following ones because it is at the beginning of the Run or because it is directly preceded with EOE Service Word.

- Illustration below shows that Data Encapsulation is unchanged if BACKWARD\_MODE mode is selected :

| START_WORD                 |

|----------------------------|

| STOP_WORD (1)              |

| STOP_WORD (2)              |

| STOP_WORD (3)              |

| STOP_WORD (4)              |

| STOP_WORD <mark>(5)</mark> |

| STOP_WORD (6)              |

| START_WORD <sup>2</sup>    |

| STOP_WORD (7)              |

| EOE_WORD                   |

<u>Note 1</u> : <u>ANALYSIS\_GATE</u> output signal is high during FORWARD\_GATE <u>Note 2</u> : if <u>NEXT\_START</u> mode is selected

• After RUN = OFF Command, EOR Service Word is delivered to the acquisition software after the last data table of the last Event processed by TDC-V4.

# 8. Data collecting through PCI Bus

Collecting of the data delivered by TDC-V4 operates by means of the 3 following registers (the PCI address values are different with TDC-V4 version compatible with Narval acquisition software) :

• SEMAPHORE register (read and write)

| name      | PCI     | data                                                               |

|-----------|---------|--------------------------------------------------------------------|

|           | address |                                                                    |

| SEMAPHORE | 2AFC04h | $2^{31}$ $2^{16}$ $2^{15}$ $2^{4}$ $2^{3}$ $2^{2}$ $2^{1}$ $2^{0}$ |

|           |         | X X 0 0 0 1 0 0 available buffer : no                              |

|           |         | n n 0 0 0 1 1 0 <i>available buffer</i> : yes                      |

|           |         | n n : Size                                                         |

Reset of SEMAPHORE register is made by writing 4h.

• SIZE (read only)

| name | PCI     | data                               |            |

|------|---------|------------------------------------|------------|

|      | address |                                    |            |

| SIZE | 2AFC08h | $2^{31}$ $2^{16}$ $2^{15}$ $2^{0}$ |            |

|      |         | 00 n n                             | n n : Size |

• DATA (read only)

| name | PCI<br>address | data             |            |

|------|----------------|------------------|------------|

| DATA | 2AFC18h        | $2^{31}$ $2^{0}$ |            |

|      |                | d d              | d d : Data |

The 2 FIFO-ACQ output buffers of TDC-V4 operate as double buffering. When a buffer is said available ?

- If Event By Event Acquisition Mode is selected (EBE\_HOST\_ACK, EBE\_EXT\_END or EBE\_TDC\_AUTO), a buffer is available if :

- the FIFO memory in progress is full (509 words)

- or EOE (End of Event) Service Word is stored

- or EOR (End of Run) Service Word is stored.

- If Accumulation Acquisition Mode is selected (ACC\_TDC\_AUTO), <u>a buffer is</u> <u>available</u> if:

- the FIFO memory in progress is full (509 words)

- or EOR (End of Run) Service Word is stored.

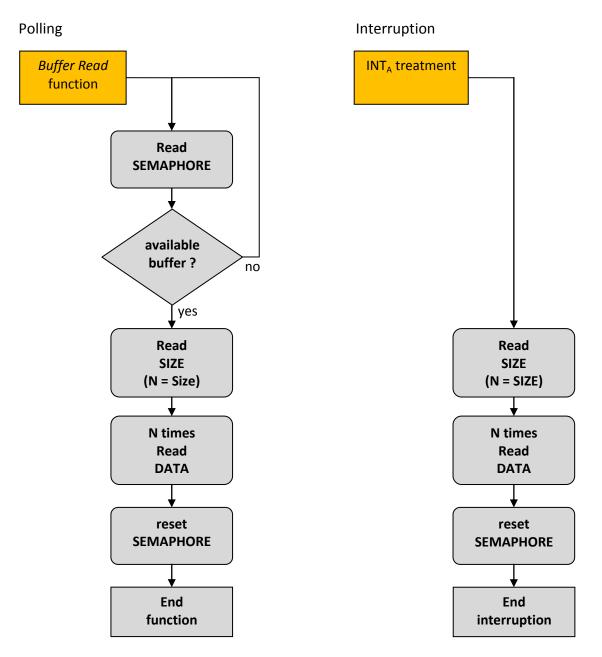

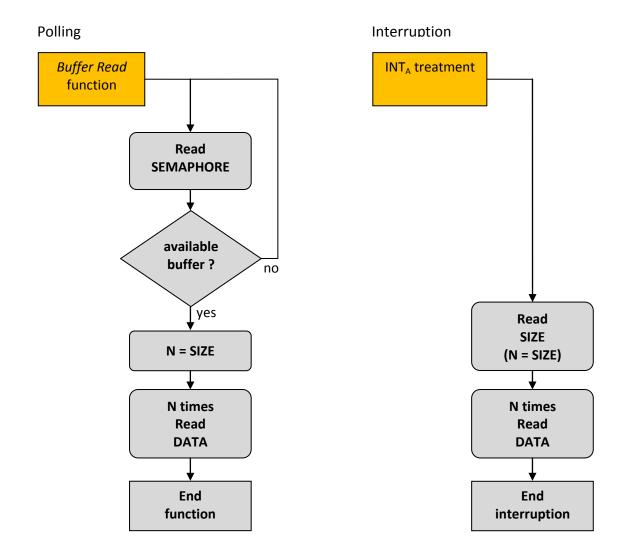

The acquisition software accesses to SEMAPHORE, i.e. to the information "buffer is available", can be done by means of :

- interrogation of the content of SEMAPHORE register (polling)

- treatment of hardware interruption (INT<sub>A</sub> Interruption line of PCI Bus)

For either these 2 access modes (Polling or Interruption), TDC-V4 is compatible with 2 possible data collecting protocols :

- Standard Protocol, the most often used with previous TDC versions

- Simplified Protocol, allowing rate increasing in Event By Event Acquisition Mode.

#### **Standard Protocol**

#### **Simplified Protocol**

By Polling access, the Simplified Protocol suppresses :

- the reading of SIZE register (the protocol uses the SIZE field of SEMAPHORE register)

- > the Reset by writing into SEMAPHORE register.

By Interruption access, this protocol suppresses:

the Reset by writing into SEMAPHORE register.

# 9. Technical Characteristics

|                                           |                             | with ISIBox rack  |

|-------------------------------------------|-----------------------------|-------------------|

| time bin                                  | 120 ps                      |                   |

| resolution (σ)                            | 60 ps                       |                   |

| double hit resolution (max)               |                             |                   |

| <ul> <li>isolated</li> </ul>              | 2.5 ns                      |                   |

| <ul> <li>in burst (max)</li> </ul>        | 5 ns                        |                   |

| <ul> <li>in burst (mean)</li> </ul>       | 4 ns                        |                   |

| latency after Trigger                     |                             |                   |

| <ul> <li>without backward mode</li> </ul> | 4 ns                        |                   |

| <ul> <li>with backward mode</li> </ul>    | 0 ns                        |                   |

| INL                                       | 0 %                         |                   |

| DNL                                       | 4 %                         |                   |

| range                                     |                             |                   |

| <ul> <li>without REXT</li> </ul>          | 7.8 ms                      |                   |

| <ul> <li>with REXT (optional)</li> </ul>  | boundless                   |                   |

| input buffer per channel                  | 512 words                   |                   |

| output buffer                             | 2 x 509 words               |                   |

| time encoding channels                    |                             |                   |

| • Start                                   | 1                           |                   |

| • Stop                                    | 16                          | NIM / ECL         |

| <ul> <li>Additional (optional)</li> </ul> | 1                           |                   |

| SCSI input/output level                   | LVDS                        |                   |

|                                           | RUN                         | TTL and displayed |

| monitoring outputs                        | BUSY                        | TTL and displayed |

|                                           | FORWARD_GATE                | TTL               |

|                                           | TRIGGER_ EN. / EVENT_LABEL. | TTL               |

| control inputs                            | STOP_GATE                   | TTL               |

|                                           | EXTERNAL_END                | TTL               |

|                                           | FAST_START                  | NIM               |

| trigger sources                           | SLOW_START                  | TTL               |

|                                           | HOST                        |                   |

|                                           | INTERNAL                    |                   |

| analysis gate                             | EXTERNAL                    |                   |

|                                           | BACKWARD                    |                   |

|                                           | boundless                   |                   |

| acquisition modes                         | EVENT BY EVENT              |                   |

|                                           | ACCUMULATION                |                   |

| PCI handshake                             | POLLING                     |                   |

|                                           | INTERRUPTION                |                   |

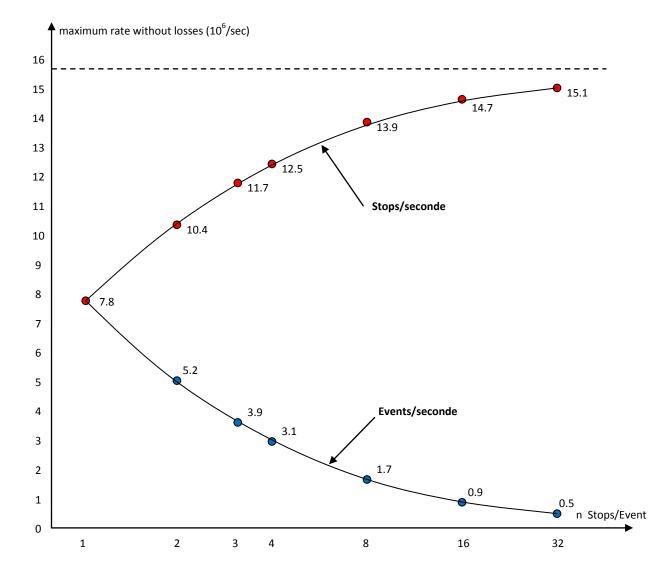

# 10. Data collecting rates

Data collecting rate depends on many parameters : power, architecture and operating system of the acquisition computer, data processing software, Event rhythm (periodic, Poisson), Event feature (fixed size, variable size, Analysis Duration), data losses, etc.

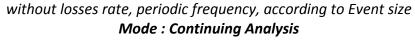

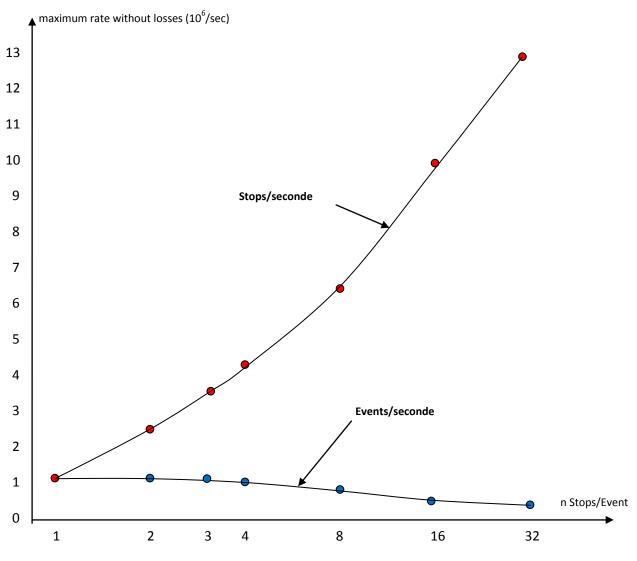

Moreover, data collecting rate depends strongly on selected Acquisition mode and Acknowledgment Mode (see chapters 3.b and 3.f). This chapter clarifies the 3 modes (<u>Continuing Analysis</u>; <u>Accumulation</u>; <u>Event By Event</u>) and presents the measured rate performances.

### 10.a. the 3 data collecting methods

#### Continuing Analysis

With this method, all the enabled signals are encoded since TDC-V4 is triggered (only one Trigger signal is sufficient) (see chapter 3.c) up to the Run reset. Resulting data are piled up continuously into double buffering FIFOs.

Continuously Analysis Mode is chosen by selecting EXTERNAL\_GATE as Analysis Duration and by suppressing any signal on the EXTERNAL\_END input: so, TDC-V4 runs with an infinite Analysis Duration (see chapter 3.d).

Thus, the whole Run is considered as a unique Event, either Event By Event Mode or Accumulation Mode may be equally selected (see chapter 3.f). In the same way, it does not make sense to select BACKWARD\_MODE.

If all the signals entering the Start Coding Channel, NEXT\_START mode must be selected (see chapter 3.e).

Data flow is framed by the Start Coding Word at the Run beginning and the EOE + EOR Service Words at the end. Except the last buffer of the Run, all buffers contain 509 Words 32 bits wide.

<u>Continuing Analysis Mode is the most efficient one from a rate point of view</u>. TDC-V4 operates no filtering on the input signals and no Event building ; these operations have to be processed by the acquisition software.

#### > Accumulation

With this method, each Trigger induces a Forward Analysis Gate with finite Duration (180 ns minimum, 7.8 ms maximum) and TDC-V4 accumulates the encodings relative to successive Events into the output buffer.

For each Event, TDC-V4 gathers encodings occurring during the Backward Analysis Gate (if BACKWARD\_MODE is selected, see chapter 3.d) and during the Forward Analysis Gate. TDC-V4 frames Stop Channels encodings (and Start Channel encodings if NEXT\_START is selected, see chapter 3.e) with Start Coding Word at the beginning of the Event table and with EOE Service Word at the end of the Event table.

In Accumulation Mode, the data processing software is simpler than in Continuing Analysis Mode but collecting rate is decreased.

Except the last buffer of the Run, all buffers contain 509 Words 32 bits wide.

#### > Event By Event

With this method, each Trigger induces a Forward Analysis Gate with finite Duration (180 ns minimum, 7.8 ms maximum), TDC-V4 gathers encodings occurring during the Backward Analysis Gate (if BACKWARD\_MODE is selected, see chapter 3.d) and during the Forward Analysis Gate and waits for Acknowledgment before enabling a new Trigger. Only in EBE\_TDC\_AUTO mode (see chapter 3.f), TDC-V4 is self-acknowledged.

TDC-V4 frames Stop Channels encodings (and Start Channel encodings if NEXT\_START is selected, see chapter 3.e) with Start Coding Word at the beginning of the Event table and with EOE Service Word at the end of the Event table.

The size of the buffers read by the acquisition software is variable, between 2 and 509 words 32 bits wide.

Event By Event Mode must be used if TDC-V4 has to be correlated with other data sources. This Mode is the least efficient from rate point of view, especially since the mean number of Stops per Event is small.

### 10.b. maximum rate without losses

The conditions of the measurement are as it follows :

- <u>central unit</u> : multi-cores PC

- operating system : Windows XP

- data processing : none

- Event rhythm : periodic

- <u>Event size</u> : fixed : 1 Start + n Stops

- losses ratio : 0%

#### Continuing Analysis data collecting

#### > <u>ACCUMULATION</u> data collecting

without losses rate, periodic frequency, according to Event size Acknowledgment Mode : ACC\_TDC\_AUTO INTERNAL\_GATE : 180 ns

| mean number of<br>Stops per Event | without losses rate<br>MegaEvents/sec | without losses rate<br>MegaStops/sec |

|-----------------------------------|---------------------------------------|--------------------------------------|

| 1                                 | 1.25                                  | 1.25                                 |

| 2                                 | 1.25                                  | 2.5                                  |

| 3                                 | 1.25                                  | 3.75                                 |

| 4                                 | 1.1                                   | 4.4                                  |

| 8                                 | 0.8                                   | 6.4                                  |

| 16                                | 0.6                                   | 10.0                                 |

| 32                                | 0.4                                   | 12.8                                 |

#### > <u>Event By Event</u> data collecting

without losses rate, periodic frequency, according to Event size Acknowledgment Mode : EBE\_HOST\_ACK or EBE\_TDC\_AUTO INTERNAL\_GATE : 180 ns

| mean number of<br>Stops per Event | without losses rate<br>KiloEvents/sec | without losses rate<br>KiloStops/sec |

|-----------------------------------|---------------------------------------|--------------------------------------|

| 1                                 | 91.3                                  | 91.3                                 |

| 2                                 | 90.5                                  | 181                                  |

| 3                                 | 89.7                                  | 269                                  |

| 4                                 | 88.9                                  | 356                                  |

| 8                                 | 85.8                                  | 687                                  |

| 16                                | 80.3                                  | 1285                                 |

| 32                                | 71.2                                  | 2280                                 |

# 11. TDC-V4 installation

### 11.a. required configuration

Installation of TDC-V4 board as well as associated Driver and DLL needs a PC type computer with the following minimum characteristics :

- Processor : compatible Pentium<sup>®</sup> 1 GHz

- RAM memory: 256 Mo

- Hard disk : 10 Mo free

- One free slot PCI 32 bits or 64 bits wide with a 3.3V supply (PCI certification)

- Operating System : Windows

### 11.b. installation

Installation of the board into the PC :

- Turn off the computer and unplug the supplied cable

- Remove the PC cover

- Choice a free PCI slot (white color slots) ; if a filling bracket shuts the slot on the PC rear panel, remove it

- Insert the TDC-V4 board all the way in, holding the board edges firmly

- Check that the board is well straight and hold the TDC-V4 bracket with the supplied screw

- Replace the computer cover and the supplied cable.

### Installation of the driver (Windows XP) :

- Start the computer

- If the Found new hardware wizard window appears, click Cancel

- Install the driver by launching the *drv\_install.exe* program contained in the *Installation Driver* folder of the supplied Package TDC-V4, then follow the instructions.

#### Checking that TDC-V4 is recognized by Operating System :

- Click Start, then Control panel, System, and finally Device manager

- Double click Jungo (driver supplier), then ITO01 (TDC-V4 card name).

*Properties* window opens and a message displays the device state. Check that *This device is* working properly message is displayed.  $\triangle$  icon next to *IT001* informs that TDC-V4 board is not properly installed.

# **12. DLL Functions**

This chapter helps to use DLL Functions supplied with TDC-V4 board for C/C++ software. This DLL was developed by ISITech company and TDC-V4 is compatible with it. An optimized DLL will be developed later.

### 12.a. required files

For C/C++ software, the following files enclosed in the *DLL* folder of the TDC-V4 Package, must be included into the program :

- *isitime dll.dll* : DLL file

- *import\_dll.h* : header file

- *isitime\_dll.lib* : resource file

### 12.b. functions

<u>Driver opening</u>:

Void OuvertureDriver(char \*flag, unsigned long vID, unsigned long dID, int mc)

To be used during each program launching. This function needs the following parameters :

- flag returns the value 20 if the function is successful

- **vID** = 0x10B5

- **dID** = 0x5406

- mc = -1

- Driver closing : Void FermetureDriver()

To be used during each program exit.

Writing into a register : Bool Data\_Ecriture(int \*buffer, int taille, unsigned long adresse, int mode)

To be used to write into the Mode and Command registers :

- **buffer** : data word (32 bits wide)

- size = 1

- address : report to summary chapter 14

- mode = 6

<u>Reading from a register</u>:

Bool Data\_Lecture(int \*buffer, int taille, unsigned long adresse, int mode)

To be used to read one among the 3 registers DATA, SEMAPHORE and SIZE :

- buffer : data word (32 bits wide)

- size : number of words to read

- address : report to summary chapter 14

- mode = 3 for DATA register; 0 for the other registers

- Data reading from the FIFO-ACQ output buffers: int Read\_dsp\_bis(int \*data\_buffer, int \*size)

To be used to read the data buffer available in the TDC-V4 output buffers with the standard protocol. This integrated function manages :

- ✓ reading from SEMAPHORE register

- ✓ test of data availability :

- if data are not available : the function returns 0

- if data are available : the function reads size from TDC-V4 SIZE register, reads the suitable number of data from the TDC-V4 output buffers, resets the SEMAPHORE register, returns 6 and assigns the following contents :

- data\_buffer : read data (32 bits wide table)

- size : number of read words ( $\leq$  509)

# 13. Program example

The following example clarifies the chronological architecture to be respected by any acquisition software (standard protocol).

### 1. Driver opening

Use OuvertureDriver function

Syntax example :

char flag = 0;

OuvertureDriver(&flag, 0x10B5, 0x5406, -1);

### 2. Initialization (not necessary before a Run launching)

Use Data\_Ecriture function

Syntax example :

#define INIT\_TDC 0x1600000

int register\_val = 0;

Data\_Ecriture(&register\_val, 1, INIT\_TDC, 6); // Reset TDC asserted

register\_val = 1;

Data\_Ecriture(&register\_val, 1, INIT\_TDC, 6); // Reset TDC de-asserted

Caution : Reset TDC must be a pulse ; de-assertion must follow assertion.

### 3. Configuration (may be operated at any time)

Use Data\_Ecriture function

Syntax example : static enabling of Stop1 and Stop3 Channels, static disabling of the other Stop Channels (keeps the other registers to their default values) :

#define STATIC\_STOP\_ENABLE 0x1200000

register\_val = 0xA; // binary: 1010

Data\_Ecriture(&register\_val, 1, STATIC\_STOP\_ENABLE, 6);

### 4. Run launching

Use Data\_Ecriture function Syntax example :

#define RUN 0x1A00000

register\_val = 1;

Data Ecriture(&register val, 1, RUN, 6);

### 5. Data collecting (standard protocol)

Use Read\_dsp\_bis function Syntax example :

int size, data\_buffer[509], status = 0;

// Acquisition loop during the wanted duration

while(status == 0) // Data available polling test

{

status = Read\_dsp\_bis(data\_buffer, &size)

}

### 6. <u>Run ending</u>

Use Data\_Ecriture function Syntax example :

> register\_val = 0; Data\_Ecriture(&register\_val, 1, RUN, 6);

### 7. Data collecting ending

In order to be sure that all the encodings remaining in the TDC-V4 buffers after the Run ending are read, data collecting should continue until the EOR Service word is detected.

### 8. Driver closing

Use FermetureDriver function Syntax example :

FermetureDriver();

A functional example of C++ program is available in the *Example program* folder of the TDC-V4 package.

# 14. TDC-V4 registers summary

| name               | address   | page             |

|--------------------|-----------|------------------|

|                    | CONFIGUI  | RATION REGISTERS |

| TRIGGER_SOURCE     | 240 0000h | 12               |

| TRIGGER_ENABLE     | 220 0000h | 12               |

| FORWARD_MODE       | 1C0 0000h | 14               |

| FORWARD_DURATION   | 1C0 0000h | 14               |

| BACKWARD_MODE      | 180 0000h | 15               |

| BACKWARD_DURATION  | 180 0000h | 15               |

| NEXT_START         | 220 0000h | 16               |

| EVENT_LABELLING    | 220 0000h | 17               |

| EXTRA_CHANNEL      | NA        | 18               |

| STATIC_STOP_ENABLE | 120 0000h | 18               |

| DYNAM_STOP_ENABLE  | 220 0000h | 18               |

| OPTIMIZATION       | 220 0000h | 19               |

| ACK_MODE           | 260 0000h | 20               |

| INIT_CONF          | 140 0000h | 22               |

| INIT_TDC           | 160 0000h | 22               |

| RUN                | 1A0 0000h | 23               |

| HOST_ACK           | 2C0 0000h | 23               |

| HOST_START         | 2E0 0000h | 24               |

| POLARITY           | 280 0000h | 25               |

| COMMAND REGISTERS  |           |                  |

| SEMAPHORE          | 2AFC04h   | 30               |

| SIZE               | 2AFC08h   | 30               |

| DATA               | 2AFC18h   | 30               |