A PUBLICATION OF MENTOR GRAPHICS NOV 2010—VOLUME 6, ISSUE 3

"Survey Says"...page 6 Chief Verification Scientist Harry Foster introduces our newest Verification Academy module, Verification Planning, and shares results from a poll conducted through our Verification Academy program....more

# THE HOT SPOT

Firmware Verification Using SystemVerilog OVM page 8 ...implementing a new OVM environment from scratch, replacing a previous e-based environment. more

SystemVerilog Configurable Coverage Model in an OVM Setup page 14 ...an elegant way to handle SystemVerilog's limited flexibility in covergroups. more

Advanced Techniques for AXI Bus Fabric Verification page 25 ...introducing the concept of a virtual fabric that helps you tackle the challenges of complexity and schedule pressure. more

#### Converting Module-Based Verification Environments to Class-Based Using SystemVerilog OOP page 34

...wrap your existing code with a class-based layer, taking advantage of the reusability and modularity of OOP code while maintaining backward compatibility with your existing environment. more

#### Verifying a CoFluent SystemC IP Model from a SystemVerilog UVM Testbench in Questa page 38

...use an OVM testbench to verify SystemC IP, with Cofluent Studio—a graphical modeling and simulation environment that can generate SystemC TLM code automatically. **more**

### What You Need to Know About Dead-Code and X-Semantic Checks.

**page 44**...introducing a variety of ways to adopt formal verification without writing properties or assertions. **more**

# New Methodologies: They Don't Have to Be Scary.

By Tom Fitzpatrick, Editor and Verification Technologist

My daughter recently celebrated her 10th birthday. We've always had her birthday parties at our house, but this year was different for two reasons. First, now that Megan has reached "double-digits," we let her have a sleepover party, which meant there were six nine- and ten-year-old girls sleeping in our basement that night. Second, since Megan's birthday is right

around Halloween, she decided to make that the theme of the party. My wife had a great time getting all the decorations and games together for the party, and on the big night our guests

were treated to everything from light-up ghosts to tombstones on the front lawn, cobwebs on the ceilings and even a giant spider hanging from the kitchen ceiling. But the biggest surprise of all was Megan's costume.

Having spent most of the previous Halloweens as a princess of some sort or other, Megan decided that this year would be different. She wanted to be a vampire! My wife used her theatrical makeup experience to good use, painting Megan's face white and including some "blood" dripping from her mouth. With her beautiful auburn hair hidden under a black wig, Megan didn't look like my little girl at all. But, of course, it was still her underneath. *"It all comes down to building on the familiar while pushing the boundaries a bit and stepping a little outside your comfort zone."*

—Tom Fitzpatrick

I'm sure by now you're wondering what this has to do with *Verification Horizons*. Megan's party reinforced the idea that, when you step outside your comfort zone, sometimes you can achieve better results than you might have imagined. But there are still some important things to remember. We were able to build on past experience to take typical party games and add a spooky flair to them so that they would both fit the theme of the party and also be great fun for the girls, and we even thought up a couple of new games, too. Big brother David helped keep everything on schedule so we could fit everything in (including presents and cake!) and we even managed to get the girls to bed at a reasonable time (for a girls' sleepover, anyway). And lastly, we were able to adapt as the night wore on so that, even though we didn't do everything we had originally planned, we got the important things done and everyone had fun.

Let's see...planning, building on experience, adding new features, tracking progress, managing schedules, achieving results. My daughter's party was an engineering project!

In this issue, we're going to show you how all of these ideas fit into adopting a new verification methodology, or improving your current methodology.

Our first article, from our good friend and colleague Harry Foster, "The Survey Says," introduces our newest Verification Academy module, Verification Planning. It also shares the first round of results from a poll conducted through our Verification Academy program. This article sets the stage for the discussions to follow by letting you see how you compare to your colleagues who have visited the academy.

Our feature article, "Firmware Verification Using SystemVerilog OVM," comes from our friends at Infineon in Singapore, who worked closely with some of my Mentor Graphics colleagues to implement a layered OVM-based methodology to verify a power train microcontroller. Interestingly, they chose to implement their new OVM environment from scratch to replace their previous e-based environment. As you'll see, they were able to take advantage of OVM's ability to provide structure to the environment, as well as flexibility in reusing the structure for a variety of tests. This will now form the basis for additional projects moving forward.

Our next article was written by our friends at Applied Micro, who share their thoughts on reusability in "SystemVerilog Configurable Coverage Model in an OVM Setup." This shows a clever bit of coding in which the covergroups are written in terms of configurable parameters that can be controlled using the OVM set/get\_config mechanism to let you modify the covergroups on a per-test basis. It even shows how to use a similar approach to configure cover properties as well. I've heard many SystemVerilog users complain to various degrees about the lack of flexibility in covergroups, and this article shows how to handle it quite well.

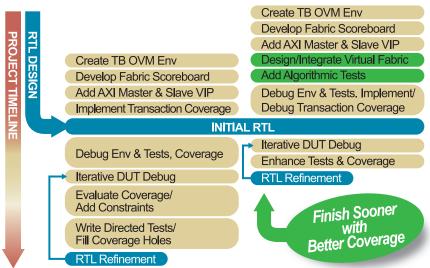

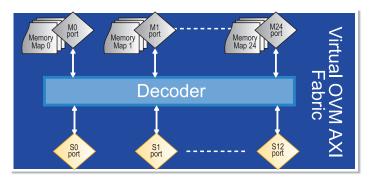

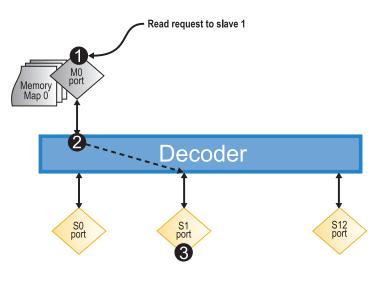

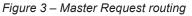

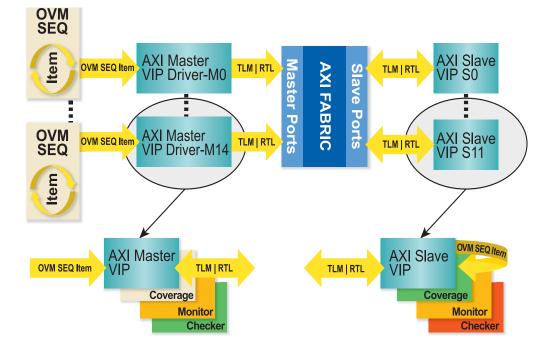

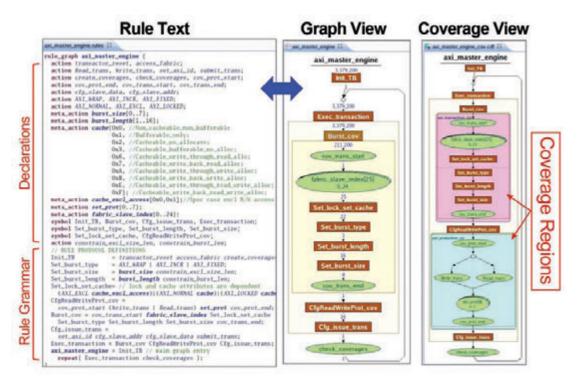

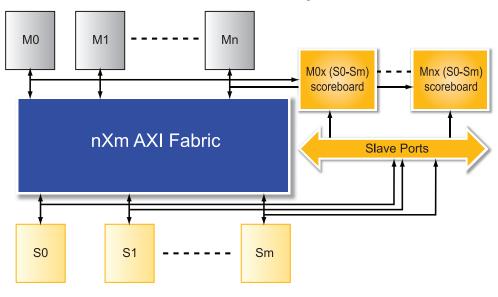

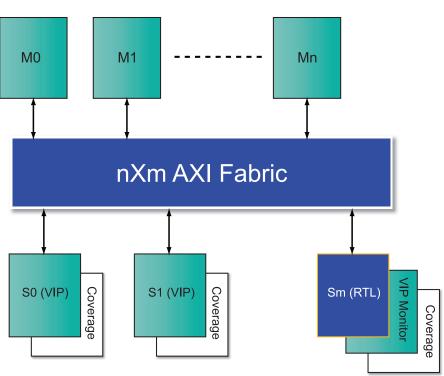

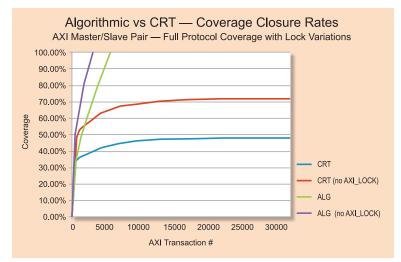

In "Advanced Techniques for AXI Bus Fabric Verification," the authors introduce the concept of a virtual fabric that helps you tackle the challenges of complexity and schedule pressure. Using a combination of a virtual model of the fabric along with Mentor's unique algorithmic stimulus generation techniques, you'll be able to implement and debug most of your environment while the RTL is still being designed. The article discusses how these techniques were applied to an actual project, so you'll see the issues and benefits they encountered.

We realize that many of you are still testing the waters a bit when it comes to Object-Oriented Programming and adopting new methodologies like OVM. In the spirit of "walk before you run," we next present an article from one of my colleagues in India, which discusses "Converting Module-Based Verification Environments to Class-Based Using SystemVerilog OOP." Rather than abandoning what may be a substantial amount of module-based Verilog or SystemVerilog code, this article will show you how to wrap your existing code with a class-based layer to begin to take advantage of the reusability and modularity of OOP code while maintaining backward compatibility with your existing environment. From there, it's a straightforward step to fully adopt something like OVM.

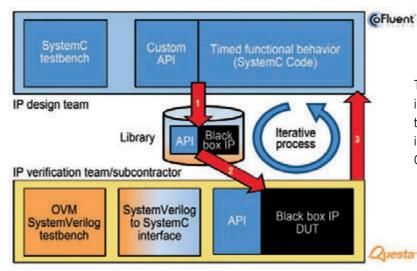

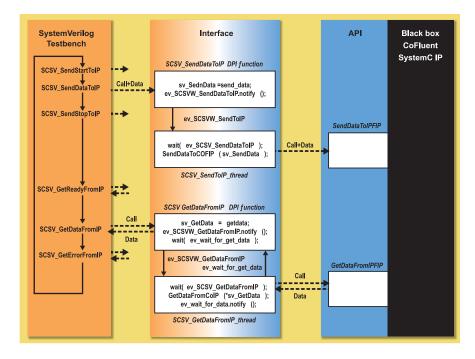

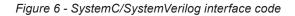

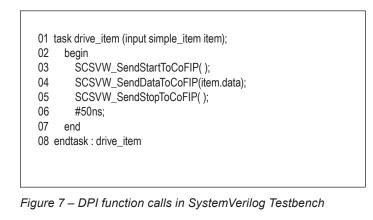

In our Partners' Corner this issue, we present "Verifying a CoFluent SystemC IP Model from a SystemVerilog UVM Testbench in Mentor Graphics Questa" from our friends at CoFluent Design. This article shows you how to use an OVM testbench to verify SystemC IP. Cofluent Studio provides a graphical modeling and simulation environment that lets you generate SystemC TLM code automatically. As you'll see, it can also generate the Questa DPI code and custom C++ code needed to seamlessly integrate that TLM code into your OVM environment, which can itself be partially reused as the design is refined to RTL.

And last but not least, we have an article from my formal verification colleagues, Ping Yeung and Erich Marschner, on "What You Need to Know About Dead-Code and X-Semantic Checks." In this article, you'll be introduced to some ways of adopting formal verification without having to write properties or assertions. Dead-Code and X-Semantic checks are two of the areas where our new automatic formal checking can be used to augment dynamic simulation. I think you'll see that being able to add this new technology on top of your existing methodology will prove extremely useful.

As you can see, we spend a lot of time here at Mentor trying to make it easier for you to adopt all this cool technology we're developing. It all comes down to building on the familiar while pushing the boundaries a bit and stepping a little outside your comfort zone. Don't be afraid. What may look like a giant spider at first may turn out to be just a balloon. I hope you enjoy this issue of *Verification Horizons*.

Getting back to Megan's party, I'm sure you parents out there can sympathize with my difficulty in understanding how it could be that we're celebrating her tenth birthday when she was just born not too long ago. I guess time really does fly when you're having fun.

Respectfully submitted, Tom Fitzpatrick Editor, Verification Horizons

# TABLE OF CONTENTS

# Page 6...Survey Says: Verification Planning

by Harry Foster, Chief Verification Scientist Design Verification Technology, Mentor Graphics Corporation

# Page 8...Firmware Verification Using SystemVerilog OVM

by Ranga Kadambi, Eric Eu, and Sudheer Arey, Infineon Singapore Mark Glasser and Christoph Suehnel, Mentor Graphics Corporation

# Page 14...A SystemVerilog Configurable Coverage Model in an OVM setup

by Parag Goel, Sr. Design Engineer and Sakshi Bajaj, Design Engineer II, Applied Micro with Pushkar Naik, Sr. Staff Design Engineer, Applied Micro and Ashish Kumar, Lead Application Engineer, Mentor Graphics Corporation

# Page 25...Advanced Techniques for AXI Bus Fabric Verification

by Alain Gonier and Jay O'Donnell, Mentor Graphics Corporation

# Page 34...Converting Module-Based Verification Environments to Class-Based Using SystemVerilog OOP

by Amit Tanwar, Mentor Graphics Corporation

Δ

# Partners' Corner Page 38...Verifying a CoFluent SystemC IP Model from a SystemVerilog UVM Testbench in Mentor Graphics Questa

by Laurent Isenegger, Jérôme Lemaitre and Wander Oliveira Cesário, CoFluent Design

# Page 44...What you need to know about dead-code and x-semantic checks

by Ping Yeung and Erich Marschner, Mentor Graphics Corporation

Verification Horizons is a publication of Mentor Graphics Corporation, all rights reserved.

Editor: Tom Fitzpatrick Program Manager: Rebecca Granquist

Wilsonville Worldwide Headquarters 8005 SW Boeckman Rd. Wilsonville, OR 97070-7777 Phone: 503-685-7000

To subscribe visit: www.mentor.com/horizons

To view our blog visit: VERIFICATIONHORIZONSBLOG.COM

# **Survey Says: Verification Planning**

by Harry Foster, Chief Verification Scientist Design Verification Technology, Mentor Graphics Corporation

As the saying goes: Those who fail to plan, plan to fail. With that said. I am excited to announce a new module focused on Verification Planning, which has been one of the Verification Academy's mostrequested subjects for new content. The new Verification Planning module is delivered by our subject matter expert, who literally wrote the book on the subject, Peet James. The goal of verification planning and management is to architect an overall verification approach, and then to document that approach in a family of useful, easily extracted, maintainable verification documents that will strategically guide the overall verification effort so that the most amount of verification is accomplished in the allotted time. The aim of this module is to define terms, logically divide up the verification effort, and lay the foundation for actual verification planning and management on a real project. I think you will really enjoy and be enlightened by Peet's treatment of the subject, and hopefully, you can apply many of the techniques that he presents to your own projects.

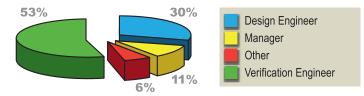

Speaking of applying Verification Academy techniques—we just conducted a large survey about the academy and found some interesting results that I would like to share with you. First, Figure 1 shows who is viewing the Verification Academy content by job title.

Figure 1: Verification Academy viewers by job title

It's not too surprising that a majority of the viewers are verification engineers, with a ratio of about 3.5 verification engineers for every 2 designers.

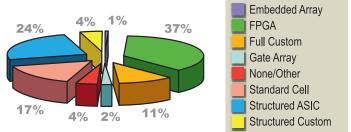

In addition to who is viewing the Verification Academy, we were interested in learning the viewer's type of targeted design implementation to get a better understanding of our viewers' needs. Figure 2 shows who is viewing the Verification Academy by their type of targeted design implementation.

Figure 2: Verification Academy viewers by targeted design implementation

We are obviously seeing a growing number of FPGA engineers interested in advanced functional verification. Today's complex SoCbase FPGA designs are not your mom and pop variety of FPGA designs. More advanced verification skills are required to ultimately meet both quality and schedule goals.

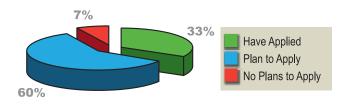

Another question we wanted to answer through our survey is whether the Verification Academy has been useful. One way to answer this is to see how many viewers had actually applied or plan to apply the knowledge they learned in the Verification Academy on their own projects. The survey results are shown in Figure 3.

Figure 3: Verification Academy viewers who have applied knowledge on projects

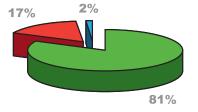

We also wanted to determine through the survey if the content presented in the Verification Academy was at an appropriate level of detail. The survey results are shown in Figure 4.

Figure 4: Verification Academy content level of detail

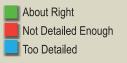

Finally, we wanted to determine through the survey which additional topic in advanced functional verification should be covered in the Verification Academy. Figure 5 presents the results.

Your feedback is important to us, and we are very excited that our new Verification Planning module was one of the top requests from the Verification Academy survey participants.

I would like to encourage you to check out all our new and existing content at the Verification Academy by visiting www. verificationacademy.com.

Figure 5: Verification Academy new subject content request

# Firmware Verification Using SystemVerilog OVM

by Ranga Kadambi, Eric Eu, and Sudheer Arey, Infineon Singapore Mark Glasser and Christoph Suehnel, Mentor Graphics

### INTRODUCTION

Semiconductor design is changing rapidly, which in turn forces continual evolution of verification methodologies and languages. This change is happening across the board, affecting not only expensive chips bound for big-iron servers but also more modestly priced processors built for specific applications.

Consider the case of embedded microcontrollers. These integrated blocks of processing capability, memory and programmable peripherals are found in a range of products, from power tools to toys. Their reach is in part due to their plunging cost. Today, 8-bit microcontrollers, which account for the majority of all CPUs sold in the world, sell for as little as \$0.25 each. Consider that in the early 1970s, Intel's 8008, the world's first 8-bit processor, sold for \$120, an amount roughly equal to \$520 today.

Microcontrollers of course are niche devices, usually built for a small handful of tasks. An engine microcontroller, for example, might take input from various sensors and adjust fuel mix and spark plug timing. However, the specificity of these chips does not equate to simplicity in their design. High-end 32-bit Infineon microcontrollers bound for various automotive applications have as many as 70 distinct IP blocks that must be integrated and verified. And as it turns out, the hardware challenges are only the half of it.

Like all microcontrollers, those designed by Infineon rely heavily on firmware. The firmware is critical, and not just the higher-level code that is closest to the application itself and that usually resides in flash memory. The lower level boot read only memory (ROM) code executes an increasing number of background processing tasks, including bootstrap loading, memory checking and so on. As is true of the hardware, the firmware itself is increasingly complex. Just a few years back the firmware for Infineon's automotive chips – the Munich, Germany-based company is the No. 1 chip supplier to the automotive industry – amounted to just a few hundred lines of code. Today the firmware file is 16 kilobytes, and growing larger with each release.

For those writing the firmware, the challenge is a bit like building a plane while flying it. Namely, they are writing software for early-stage hardware that is nowhere near stable. How do you verify something when everything – the individual IP blocks, the overall design, even the firmware code itself – is still a work-in-progress? That was the

challenge in a recent pilot project to design and verify a power train microcontroller at Infineon in Singapore.

The solution was a layered methodology. The first layer is a standard Open Verification Methology (OVM) testbench used to drive input interfaces via constrained-random pattern generation, observe outputs, measure functional coverage and compare the results against expected values, a process known as scoreboarding. (OVM is a joint development initiative between Mentor Graphics and Cadence Design Systems to provide the first open, interoperable, SystemVerilog verification methodology in the industry.) A second layer implements a well-defined structure for observing (using the SystemVerilog *bind* construct) and driving internal nodes in the VHDL design (using SignalSpy<sup>™</sup>, a technology within the Mentor Graphics Questa<sup>®</sup> Solution). We believe this combined approach will be more widely used in the future.

### FIRMWARE VERIFICATION METHODOLOGY

When building our new testbenches with OVM, our goal was to use the same firmware verification methodology we used in e, a verification language developed by Cadence and approved in IEEE Standard 1647. We chose to start from scratch rather than migrate portions of the e testbench to SystemVerilog because we did not have an e Reuse Methodology (eRM)-compliant testbench. Additionally, it would not be easy to migrate from e to OVM because of fundamental language differences. This also gave us the opportunity to make all of the OVM verification components (OVC) more structured, a contrast to our former e environment.

Building an OVM testbench from scratch certainly takes a bit of effort. For example, we needed to make our firmware verification methodology fit the OVM technology and guidelines. Then, of course, we had to build it. As the project progressed we definitely became convinced that the OVM methodology and technology were quite impressive and worth the initial effort to ramp up.

This effort to learn OVM took place against a backdrop of increasing time and resources required to verify firmware in general. Five years ago, verification of automotive Infineon microcontrollers took no more than four man-months. Today we spend twice as long, largely due to mounting complexity.

Even seemingly simple tasks can be confounding. Take, as a hypothetical case, firmware written to toggle a particular port. It should be straightforward enough to verify the code and check the ports that are toggled. But what happens when there are additional conditions, as is inevitably the case? Perhaps the firmware reads the counter value from another address and is coded to toggle every set number of cycles. And maybe there's input from another pin that tells the code whether the counter should be reset or just stopped with each toggle. Verifying all this functionality at the design stage is flat out difficult, especially with unverified underlying hardware.

# **DESIGN DESCRIPTION**

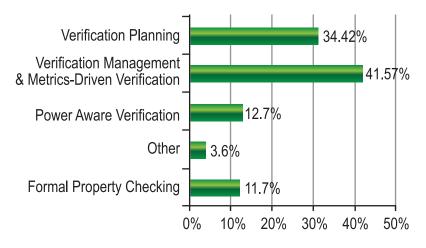

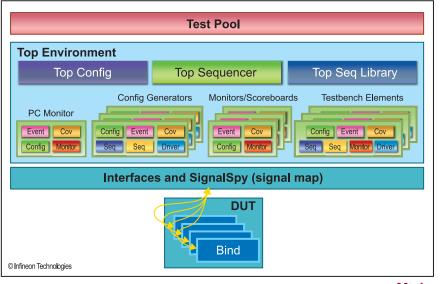

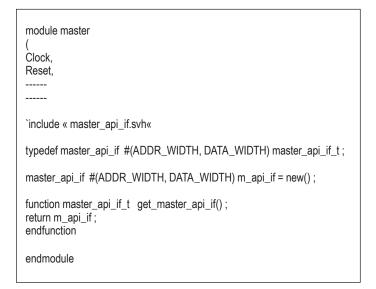

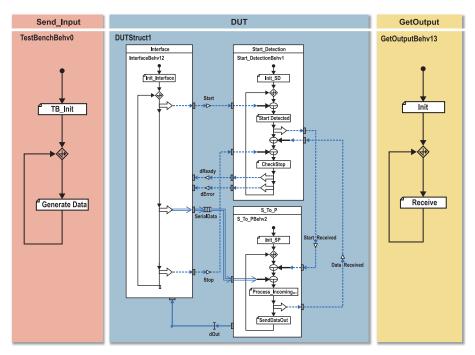

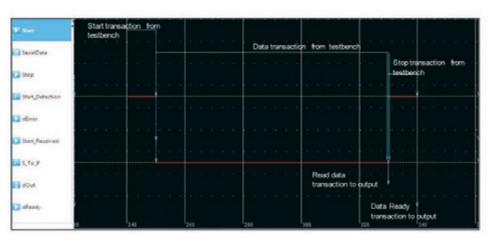

The design under test (DUT) is mainly coded in VHDL with some IP blocks coded in Verilog. The DUT is instantiated by a VHDL top-level testbench used for SoC verification (see Figure 1). The SystemVerilog/ OVM top-level is instantiated under this VHDL top-level.

Figure 1. VHDL top-level testbench.

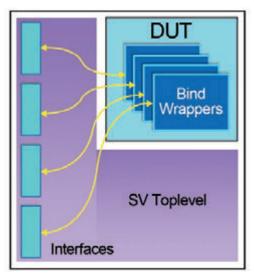

# OVM TEST ENVIRONMENT

The first layer test environment (see Code Sample 1 and Figure 2) consists of an interface layer for observing and driving signals into the DUT. Firmware verification differs from the conventional bus functional model (BFM) because we are mostly interested in whitebox testing. Instead of a BFM model, we used a signal map. The signal map is a collection of internal signals that are relevant to our verification goals. The signal map implements methods for observing and driving internal signals. In this project, we used the SystemVerilog bind construct to observe the internal VHDL signals and the Mentor Graphics Questa SignalSpy technology for driving them.

endmodule

#### Code Sample 1

The second layer consists of the OVCs (see Code Sample 2). We are using a proprietary OVC template and guidelines to develop these verification components. The OVCs are configurable using parameters and/or macros. TLM analysis ports and TLM analysis fifos are used for the OVC interconnections. TLM analysis ports provide simple and powerful transaction-based communication because of their ease of implementation, support of multiple connections, and execution in the delta cycle.

Figure 2: The OVM test environment.

#### // example of an OVC class clkgen\_agent extends ovm\_agent; else protected ovm\_active\_passive\_enum is\_active = OVM\_ACTIVE; end // TLM connections to other OVCs ovm\_analysis\_port #(clkgen\_item) aport; // TLM output to other OVCs ovm\_analysis\_export #(bootgen\_item) bootgen\_export; end // TLM input from other OVCs // signal maps ports if ports\_vif; cpu\_if cpu\_vif; else // global event pool ovm\_event\_pool eventPool; end // components cfg; clkgen config clkgen\_driver driver; end clkgen\_sequencer sequencer; clkgen\_monitor monitor; clkgen\_coverage coverage; `ovm\_component\_utils\_begin(clkgen\_agent) ovm\_field\_enum (ovm\_active\_passive\_enum, is\_active, OVM\_ALL\_ON) this); `ovm\_field\_object(cfg, OVM\_ALL\_ON) 'ovm component utils end function new (string name, ovm\_component parent); end super.new(name, parent); aport = new("aport", this); endfunction bootgen\_export = new("bootgen\_export", this); endfunction function void connect(); function void build(); ovm\_object obj; super.build(); monitor.cfg // check if cfg has been created externally if (cfg == null) begin // fallback if cfg is not created outside `ovm\_info(get\_type\_name(), "Configuration" object not initialised from outside. Generating one internally", OVM\_LOW) cfg = clkgen\_config::type\_id::create("cfg", this); assert(cfg.randomize()); end seq\_item\_export); driver.dport.connect(coverage.analysis\_export);

// get signal map if (get\_config\_object("ports\_vif", obj, 0)) begin assert(\$cast(ports\_vif, obj)) `ovm\_error(get\_type\_name(), "Wrong virtual interface type!") else begin `ovm\_error(get\_type\_name(), "Virtual interface not available!") // get signal map if (get\_config\_object("cpu\_vif", obj, 0)) begin assert(\$cast(cpu\_vif, obj)) `ovm\_error(get\_type\_name(), "Wrong virtual interface type!") else begin `ovm\_error(get\_type\_name(), "Virtual interface not available!") // get global event pool eventPool = ovm\_event\_pool::get\_global\_pool(); monitor = clkgen\_monitor::type\_id::create("monitor", this); coverage = clkgen\_coverage::type\_id::create("coverage", if (is\_active == OVM\_ACTIVE) begin driver = clkgen\_driver::type\_id::create("driver",this); sequencer = clkgen\_sequencer::type\_id:: create("sequencer", this); super.connect(); // connect monitor resources = cfg;monitor.cpu vif = cpu\_vif; monitor.eventPool = eventPool; if (is\_active == OVM\_ACTIVE) begin // connect driver resources driver.cfg = cfg; driver.ports\_vif = ports\_vif; driver.eventPool = eventPool; driver.seq\_item\_port.connect(sequencer.

// connect driver TLM to coverage

```

driver.dport.connect(this.aport);

// connect driver TLM to agent

sequencer.cfg = cfg;

end

endfunction

endclass

```

#### Code Sample 2

OVCs are critical in helping us to deal with large numbers of IP blocks. We can more or less map each such block to a corresponding OVC, and together these OVCs interact and cross check at a high level in such a way as to hide the lion's share of the complexity. If a future Infineon product incorporates a new or replacement block, we simply need to add or swap out one OVC. Given the modular nature of OVC, and of SystemVerilog in general, we can leave the rest of the stitched together design mostly as is. This is a boon to the design team and unusual in an era in which complexity often hides interdependence. Tugging on one loose thread can often cause an entire digital fabric to unravel.

In general, in our firmware verification testbench we have four types of OVCs: PC monitor, config generator, monitor/scoreboard,

and compare signals in the DUT against the stimulus generated by the generator OVC in response to events triggered by the PC monitor (see Figure 3). The monitor OVC contains the required functional coverage points. It will be sampled by the covergroup only if all the conditions and checks for a coverage point are met. The testbench element OVC is usually a communication component that interacts with the DUT on the port interfaces. Examples include the JTAG module and bootstrap loaders. This OVC performs a specific task using the actual protocol of the communication component.

The third layer is the top-level OVM environment and configuration layer. The top-level environment instantiates all the OVCs and creates the TLM connections. The top config block configures the sub-configs in each of the OVCs for a specific DUT. A virtual top sequencer controls the config generators, the OVC's sequencer, and the testbench element OVC's sequencer. The top sequencer library contains complex sequences involving two or more of the OVCs, such as pipelined sequences whereby the output of one generator OVC is needed by another generator OVC.

The fourth layer contains the OVM test pool. Each test specifies a particular scenario to run in the testbench. The test pool configures the environment by using the factory override methods.

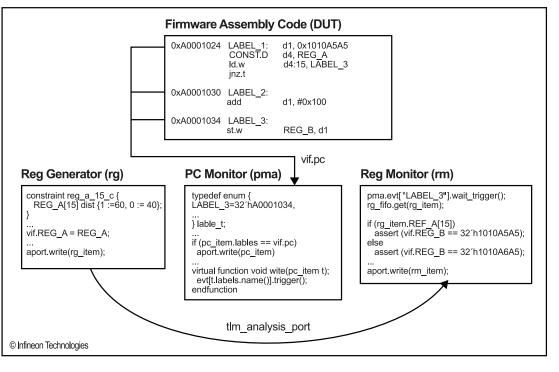

Figure 3: An example of event (PC) based assertions in firmware verification.

The PC (program counter) monitor is the main OVC. It is responsible for monitoring the PC, decoding the PC, and triggering an ovm event when the PC matches a label in the firmware code. In addition, it will collect PC data for code and branch coverage. All other OVCs in the testbench need an object handle to this PC monitor class. The config generator OVC creates the constrained-random stimulus and feeds it into the DUT that will influence the behavior of the firmware execution. The chief function of the monitor/ scoreboard OVC is to observe

and testbench element.

### FIRMWARE VERIFICATION RESULTS

Our verification focus in this project is the firmware, which is assembly ROM code in the microcontroller. The firmware code contains the very first instructions that will be executed by the microcontroller upon boot up. A proper execution of the firmware upon power-on must be ensured to bring the microcontroller to a functional state. Any bug in the firmware that causes the startup to fail will render the device unusable. Since the firmware code is hard-coded, a respin of the chip would be necessary, driving up the cost of development significantly.

We found 12 firmware bugs and five hardware bugs using the OVM for firmware verification. Common firmware bugs were the result of the implementation not meeting specification (these were detected by assertions) or implementations that did not cover all possible scenarios in the firmware (detected by random stimulus generation and coverage). Firmware verification quite often also detects hardware bugs (through assertions) caused by registers that are not writable or readable because either their protections are not set correctly in the RTL or their top-level connections are incorrect. Most significantly, we hit verification targets related to functional coverage and code branch coverage. The latter is a methodology in which we execute both trunk and branch blocks of code, a technique that helps to deal with multiple revisions, a fact of life in all software development.

### EXPERIENCES AND LESSONS LEARNED

We were able to pursue our goal of constructive, meaningful innovation in the sense that this was a successful pilot project using OVM and SystemVerilog for firmware verification. The success during the pilot convinced us that for subsequent projects we could reuse most of our firmware test environment, especially the OVM portion.

OVM provides comprehensive guidelines for building a complete verification environment. OVM extends tested and proven coveragedriven, constrained-random verification with practical resources in the OVM class libraries. OVM facilitates reuse and configuration by using the OVM factory method, and the TLM provides a standard and simple data transaction between verification components. Another useful feature was OVM Event, which helps to monitor the core program counter so we can know at which stage the core is actually getting the instruction in the firmware. Essentially we can trigger the feature at a particular stage of the firmware's execution. OVM Event propagates to all OVCs, which do various assertions and checks on signals and monitors. All told these OVM features enabled a reusable and modular approach to design verification. The OVM methodology and technology were quite impressive and worth the initial ramp up. In the past for a project of this scale, Infineon would generally spends perhaps six to nine man-months on the firmware, though for this pilot we put in 10 man-months. One reason is that compared to AOP, OOP does sometimes require more lines of code. However, the extra lines of code required by OOP enabled us to reach our primary goal of a more structured approach. Importantly, our OVM infrastructure was well structured, a contrast to our former e environment. Furthermore, the compile issues inherent to AOP required an effort greater than that required to write the extra lines of OOP code. On subsequent projects, the amount of effort and workarounds associated with the OVM should also decline.

The main challenges we came across were in the first layer of the verification architecture: implementing the bind mechanism to connect to internal nodes of the VHDL design and feeding back these connections into the OVM testbench. The objective was to provide a complete language-based interface for observation and forcing of internal nodes. So far, this objective was reached only with respect to observation.

We resolved the control issue by using SignalSpy, a Questa utility that provides access to internal design nodes to drive signals. However, it is not a language-based approach. The employment of the force functionality in SignalSpy conformed to OVM guidelines without generating serious issues.

To avoid changing existing force files to accommodate testbench development (required by the standard Infineon OVM testbench architecture), the top-level testbench had to be VHDL. OVM does not require a SystemVerilog top-level module. Therefore, this could be easily managed. The implementation of testbench elements for the design (JTAG, etc.) involved separate tasks and was performed following the OVM guidelines.

### FUTURE IMPROVEMENTS

The main challenge of this project was the implementation of the signal map layer. The use of the SystemVerilog bind construct was not suitable for whitebox verification because the construct is not reusable if the design changes. Furthermore, SystemVerilog bind has its limitation with VHDL designs.

For future improvements, we would like to explore the possibility of replacing the signal map with an OVM register package to access the internal registers of the DUT, and we are aware that a register package will be provided in the near future by the OVM organization. Once available, this will solve the controllability issue.

SystemVerilog should be extended to improve the driving of internal signals in VHDL designs. VHDL users will drive this demand to improve the functionality of SystemVerilog for VHDL designs. This is not an issue for Verilog portions of a design or IP.

Based on this pilot project, we recommend the following enhancements to SystemVerilog:

- 1. Deliver improved documentation for the SystemVerilog bind construct to make its employment easier and more powerful.

- 2. Provide a language-based approach to access internal nodes in VHDL designs for observation and forcing.

# A SystemVerilog Configurable Coverage Model in an OVM setup

by Parag Goel, Sr. Design Engineer and Sakshi Bajaj, Design Engineer II, Applied Micro with Pushkar Naik, Sr. Staff Design Engineer, Applied Micro and Ashish Kumar, Lead Application Engineer, Mentor Graphics Corporation

With the advent of a new era in verification technology based on an advanced HVL like SystemVerilog, the concept of random stimulus based verification was born, to verify today's multi-million gate designs.

In concept, every verification engineer fancies the idea of random stimuli driven verification, but as is rightly said – "Everything comes with a cost" and the cost here is a big concern that haunts the life of every verification engineer:

- How do I close my verification?

- When can I say I am done?

To answer such questions, SystemVerilog as a language came up with the concept of Functional Coverage that is much more accurate of a measure compared to the traditional Code Coverage techniques. We concentrate mainly on this SV feature in our write-up, adding one more dimension to it - configurability.

Methodology like OVM has brought in the concept of reusability of Environment/Agent (mainly consisting of Driver/ Monitor/ Sequencer) across projects. But, on the other hand, a user tends to create a coverage model that is usually coupled very tightly to the specifications of the given project. In the process, he/she ends up writing a separate coverage model for every project, compromising the reusability aspect and violating the Methodology mantra! Keeping above limitation in view, we would like to present the user with one possible solution – Configurable and Reusable Coverage Model, sighting AMBA AXI protocol as the case study for discussion.

The paper is sub-divided in the following major sections:

- 1. Overview

- a. Why configurable coverage model???

- b. SystemVerilog coverage constructs Key to configurability

- 2. Basic coverage setup

- a. Overview of the AXI setup agents/connections/passing configuration

- b. Classification of the coverage model AXI as an example

- c. Requirements of configurable model

- In depth analysis of the coverage model (coding practices/ constructs used)

- a. Transaction Coverage

- b. Error Coverage

- c. Protocol Coverage (AXI Handshake coverage) / Flow Coverage

- 4. Limitations faced

- 5. Concluding Remarks

### OVERVIEW Why configurable coverage model???

"To minimize wasted effort, coverage is used as a guide for directing verification resources by identifying tested and untested portions of the design."

IEEE Standard for SystemVerilog (IEEE Std 1800-2009)

This quote from LRM [2], explains the intent of functional coverage. But the crux of this paper lies in the configurability of any given coverage model. Configurability is the key to re-usability for any setup.

All our current day methodologies have brought in the concept of reusability of the agents such as BFM's and Monitors across projects. In the same project, an engineer also creates a coverage model in order to provide the management with a picture of the verification activity status. However it's as per the given project specifications. Thus an engineer ends up having to write a separate coverage model per project while re-using the rest.

However, verification environments created from reusability perspective need to be meticulously designed to take care of coverage model reusability as well! So our main focus is on the coverage model that could be configured and re-used.

AMBA – AXI is one of the most commonly used protocols in industry for communication among the SOC peripherals. Thus we chose this protocol for our case study.

### SystemVerilog Coverage constructs – Key to configurability

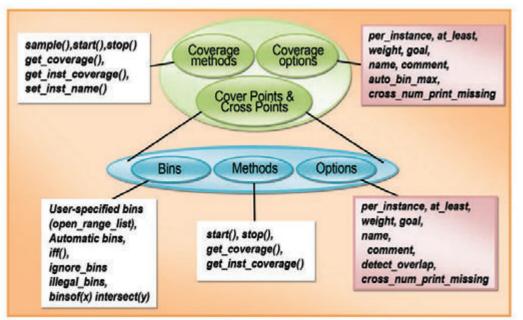

SystemVerilog provides a very fast and convenient method to describe the functional coverage for any given setup with the help of pre-defined constructs. A brief overview shall be a good starting point.

A covergroup is user-defined type like a class, which defines a

coverage model. Composed of a number of sub-elements including the following...

- Coverpoint Describes a particular type of coverage event, how it will be counted as well as one or more bins to organize the count

- **Cross** Defines a new coverage event by "combining" two or more existing coverpoints or variables

- Bin- A coverage event counting mechanism, automatically or userdefined

- **Options** Certain built-in options that helps to gain better controllability over the collection of coverage numbers.

Figure-1 below depicts a brief overview. The main highlight of the paper lies in the wise usage of the coverage/coverpoint/cross point *"OPTIONS", "METHODS"* and *"BINS"* provided in the language. The following outlines a few important aspects.

Firstly, the important coverage options:

- 1. *per\_instance:* Each instance contributes to the overall information for the *covergroup* type. When true, coverage information for this *covergroup* instance is tracked well.

- at\_least: Minimum number of hits for each *bin*. A *bin* with a hit count less than this number is not considered covered.

Say for example, if we want a particular *coverpoint/bin* to be hit a minimum of 5 times before user gains a confidence on the same, user should specify *option.at\_least=5*

- weight: If set at the covergroup level, it specifies the weight of this covergroup for computing the overall coverage. If set at coverpoint (or cross) level, it specifies the weight of a coverpoint (or cross) for computing the coverage

- 4. *goal:* Specifies the target goal for a *covergroup*. If the userspecified goal, say 50% for that given coverpoint/bin, then this shall account towards 100% coverage calculation.

- 5. *auto\_bin\_max:* Maximum number of automatically created *bins* when no *bins* are explicitly defined for a coverpoint.

All the options can be specified for instance-specific or type specific coverage calculation. *But language restricts that type\_option must be a constant parameter and does not allow variable for the same.* The only configurations provided are goal, weight, strobe and comment.

There is a key difference between type and instance coverage. The instance coverage would give us coverage of each individual instance created while type coverage is a sum of all instances. Type coverage has many limitations which are described in later part of the paper.

Coverage methods are what we would discuss next.

- 1. *sample()*: Controls the triggering of a covergroup.

- 2. get\_coverage(): Calculates type coverage number (0-100)

- 3. *get\_inst\_coverage()*: Calculates the coverage number (0-100) of a specific instance on which it is invoked.

Since these methods can be called procedurally at any point of time, gives the user an additional flexibility to control the collection of coverage for a defined *covergroup* as well as get the coverage numbers in any of the agents in your OVM setup say, a score-board etc.

Now let's look into a little detail of bins:

[**open\_range\_list**] specification - one of the important features in the bin definition that enables the user to control the number of bins created in case the user has explicitly defined the bins, since the

option *auto\_bin\_max* doesn't work in this case.

Another point that we have utilized is the order of precedence that the language imposes on the *illegal/ ignore/normal bin* definition. The priority order is as:

1. *illegal\_bins:* doesn't account towards overall coverage, issues an error

Figure 1 : SystemVerilog Coverage Constructs - Overview

#### 2. ignore\_bins: doesn't account towards overall coverage

3. **bins:** are user-defined/automatically created collectors which count towards the overall coverage numbers.

"The **default** specification is associated with each of the above bins. It defines a bin that is associated with none of the defined value bins. The default bin catches the values of the coverage point that do not lie within any of the defined bins. However, the coverage calculation for a coverage point shall not take into account the coverage captured by the default bin. The default bin is also excluded from cross coverage."

### **BASIC COVERAGE SET-UP**

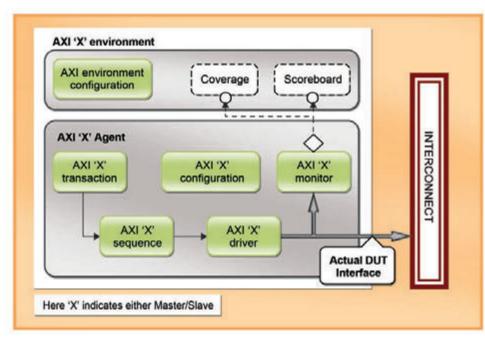

#### Overview of the AXI setup

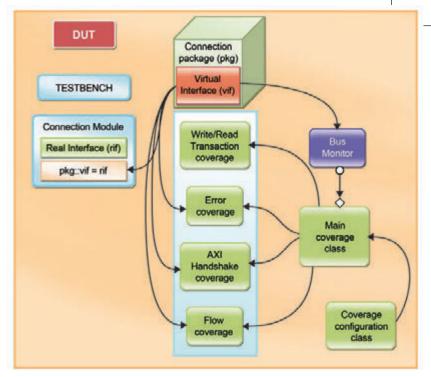

As shown in Figure 2, we have built our coverage model in an OVMbased setup. Utilization of OVM's TLM communication to build the hierarchy run-time helps a user in the placement of the components as required and also provides ease-of-communication amongst the components. As evident, all the regular components of the VIP are placed inside an *agent* wrapper. For the visibility of the collected *transaction* we utilize *analysis port-export* connection to establish a link between the *bus monitor* and the *score-board* as well as the *coverage collector*. The main reason for this structure is that both these components are coded by a user as per project specific requirements. But later, with the introduction of the generic coverage model, we were able to shift this coverage collector inside the agent itself. Still it follows the same TLM connection along with an **enable/disable switch attached to its connection** in the *connect()* phase of OVM. This is the **first level of control** for the coverage model, as we don't start focusing on the coverage numbers right from the start of the project, hence we need to keep it disabled until we gain first cut confidence on the design as well as the verification environment setup.

#### Classification of the coverage model – AXI Protocol as an example

As we rely mainly on our coverage definition for verification closure, so a comprehensive coverage model definition is required. Towards this end, a modular coverage model divided into 4 sections as shown below would yield great results.

But this modular coverage classification can still be considered generic in the sense that every protocol can be categorized under these same 4 sections.

- Transaction coverage: coverage definition on the user-controlled parameters usually defined in the transaction class & controlled through sequences.

- Error coverage: coverage definition on the pre-defined error injection scenarios

• **Protocol coverage:** (AXI Handshake coverage) this is protocol specific. In the case of AXI, it is mainly for coverage on the handshake signals i.e. READY & VALID on all the 5 channels.

• *Flow coverage:* This is again protocol specific and for AXI it covers various features like, *outstanding, inter-leaving, write data before write address* etc...

Consolidating all the above 4 models in a modular & easily controllable fashion was the next task. The figure below describes how it was done in an OVM setup.

Following are the basic requirements to model these 4 coverage models:

1. Interface

2. Transaction collected

3. Configuration class

Figure 2 : Overview of the AXI setup

Let's see how we get each one of them in detail. As depicted in Figure 3, for getting the transactions collected by bus monitor into the Main coverage class, we established a basic port-export TLM connection with the Main coverage class. This transaction is in turn passed to the Write/Read Transaction coverage model class, again via a TLM communication channel.

For coverage models other than transaction coverage model, an interface connection is required such that it is shared across the Bus monitor as well as the individual coverage models. This was achieved via connection package as shown in Figure 3. For more details refer [1]

Lastly, a very crucial input required is the configuration class, which in our case is specific for coverage definition only. This configuration class is passed and utilized via set\_config\_\*/get\_config\_\* configuration utility of OVM. The configuration is set by the user in the main coverage class and from there it is passed via the same utility further below to the respective coverage models as depicted in Figure 3.

Figure 3 : Coverage Model – OVM setup

Note: As per the SV LRM, since the covergroup(s) can be created only in the class constructor, we should have the configuration object available from the user in the class constructor itself, despite the fact that we use OVM set/get configuration methods usually in the build() phase of an OVM setup. We shall talk more about this in the later section of the paper.

| function void <b>build</b> ();                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| super.build();                                                                                                                                                                      |

| if(cov_cfg.disable_transaction_coverage == 0) begin //{                                                                                                                             |

| axi_trans_cov = axi_transaction_coverage# (ADDR_WIDTH)                                                                                                                              |

| ::type_id::create("axi_trans_cov", this);                                                                                                                                           |

| end //}                                                                                                                                                                             |

| if(cov_cfg.disable_error_coverage == 0) begin //{                                                                                                                                   |

| axi_error_cov = axi_error_coverage# (ADDR_WIDTH)                                                                                                                                    |

| ::type_id::create("axi_error_cov", this);                                                                                                                                           |

| end //}                                                                                                                                                                             |

| <pre>if(cov_cfg.disable_axi_handshake_coverage == 0) begin //{     axi_handshake_cov = axi_handshake_coverage# (ADDR_WIDTH)     ::type_id::create("axi_handshake_cov", this);</pre> |

| end //}                                                                                                                                                                             |

| if(cov_cfg.disable_flow_coverage == 0) begin //{                                                                                                                                    |

| axi_flow_cov = axi_flow_coverage# (ADDR_WIDTH)                                                                                                                                      |

| ::type_id::create("axi_flow_cov", this);                                                                                                                                            |

| end //}                                                                                                                                                                             |

| endfunction                                                                                                                                                                         |

|                                                                                                                                                                                     |

|                                                                                                                                                                                     |

. . . . . . . . .

Listing 1 : Code depicting coverage model classes controlled via user controlled configuration class

The main **coverage class** is a class that serves as a basic control point for the remaining coverage models. Listing 1 depicts the first level of configurability based on whether the user wishes to enable/disable a coverage model as a whole, in the *build()* phase of the OVM.

### Requirements of configurable model

Let us first summarize very basic requirements necessary for re-usability.

- Turn ON/OFF each coverage model defined, on an individual basis. For example, user may not always want the error coverage to be ON, until he/she performs error testing. So, by default, we generally keep it disabled and enable only when required.

- Turn ON/OFF coverage for each *covergroup* defined. Every *covergroup* should be created only if a user wishes to do so. So this configuration control is used in the class constructor itself to restrict the creation of the *covergroup* altogether. Also, the same control needs to be applied at the sampling of a *covergroup*.

- User must be able to set the limits on the individual field being covered in the coverage model within a legal set of values. Say for example, transaction field like, *Burst Length* - user should be

able to guide the model on what are the limits on the field that one wishes to get coverage on within a legal set of values ranging from 1-16 as per AXI spec. So providing lower and upper limits for transaction parameters like burst *size, burst length, address* etc. makes it re-usable.

- o option.weight can be exploited for this purpose. Thus, weight of only those *coverpoints* can be set to 1 which are legal and within user defined limits

- User should be able to control the number of bins to be created and the limits within which they should be created, for example in fields like address. auto\_bin\_max option can be exploited to achieve this, in case user doesn't specify the bins explicitly. This can also be achieved by specifying the number of bins to be created as parameter to the bins construct, which works when there are user defined bins. So a legitimate choice needs to be made from above options.

- User must be able to control the number of hits for which a bin can be considered as covered. *option.atleast* can be used for this purpose and the input to this can be a user defined parameter

- User should also have the control to specify his coverage goal,

i.e. when the coverage collector should show the covergroup

"covered" even though the coverage is not 100%. This can be achieved by using option.goal, where goal is again a user defined parameter. This is useful in various applications as illustrated in the later part of this paper.

# IN DEPTH ANALYSIS OF THE COVERAGE MODEL

#### Transaction Coverage

*Transaction class* in terms of methodology is a class that contains all the randomizable properties contributing towards complete testing of a given design. But unless all the possible values of every individual parameter as well as set of combinations of each one of them, is applied to the design, gaining confidence on our testing is difficult. However, even after one has created several random test cases, how can one be sure that the verification is complete and that he has covered all possible scenarios? Thus it is of utmost importance to building a coverage model that will let the verification engineer know quantitatively how much he/she has been able to achieve.

In order to get a better understanding of this coverage model, let us consider an example from AXI. There are several parameters in AXI which should be tested and checked for corner case hit. Some of them are mentioned in the Listing 2.

Burst Length, Burst Size, Burst Type, Access Type, Response Type, Address .....

#### Listing 2 : AXI Transaction parameters

Although it is essential to check corner case hits from protocol specification perspective, but at the same time, it's very important that exact hits relevant to one's project specification get checked. For example, AXI spec does provide limits for parameter *Burst Length* from 1 to 16, but it is important to check for the values relevant to ones project specification and not as per AXI specification (assuming project specifies a subset of values supported by AXI). This is where configurability takes the lead. Not having a configurable coverage model might give us false numbers which are of no use to the specific project.

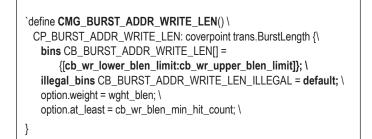

Also we need to ensure that duplication of code can be avoided while coding the same *coverpoint* across various *covergroup(s)* (i.e. individual *covergroup* for a given property and while defining it's *cross points*). Here in the example below we have taken BurstLength from AXI to illustrate the same Macro for burst length and burst size has been shown in Listing 3 & Listing 4.

Listing 3 : Macro definition for covergroup – Burst length. Here legal bins are defined within user configured limits, rest all are treated as illegal. Weight i.e. enable/disable & hit-count are also set by the user.

`define CMP\_BURST\_ADDR\_WRITE\_SIZE() \

CP\_BURST\_ADDR\_WRITE\_SIZE : coverpoint trans.BurstSize { \

bins CB\_BURST\_ADDR\_WRITE\_SIZE[] =

{1,2,4,8,16,32,64,128,256,512,1024} ; \

illegal\_bins CB\_BURST\_SIZE\_ILLEGAL\_OUTSIDE\_LIMITS =

{[\$:(cb\_wr\_lower\_bsize\_limit+1)],

[(cb\_wr\_lower\_bsize\_limit+1)],

[(cb\_wr\_upper\_bsize\_limit+1):\$]]; \

illegal\_bins CB\_BURST\_ADDR\_WRITE\_SIZE\_ILLEGAL= default; \

option.weight = wt\_bsize; \

option.at\_least = cb\_wr\_bsize\_min\_hit\_count; \

}

Listing 4 : Macro definition for covergroup – Burst Size

The SystemVerilog feature that has been exploited in *Burst Size covergroup* is that **illegal bins take precedence over bins**. Thus, the approach used was:

- Include all the legal values of Burst Size as per AXI spec in bins

- Include the values which are outside user defined limits in *illegal\_bins*.

- By default, the rest of all values are treated as illegal.

Since *illegal\_bins* have greater precedence so the values of *Burst* Size which are common to both *illegal\_bins* and *bins* are considered as part of *illegal\_bins* thus giving us *bins/coverage* as per the user configuration.

We have also provided user configurable **minimum hit count** i.e. number of hits required to consider a *bin/ covergroup* to be hit.

While defining *covergroup(s)*, it is essential to pass configuration parameters as an argument to that group. Note that the *covergroup* has to be created in class constructor where the configuration parameters are passed to the *new()* function of the *covergroup* and this *covergroup* is triggered using in-built *sample()* function in the *run()* phase of OVM. The Listing 5 illustrates the same.

covergroup CG\_BURST\_ADDR\_WRITE\_LEN (int cb\_wr\_lower\_blen\_limit,......); option.per\_instance = 1; `CMG\_BURST\_ADDR\_WRITE\_LEN endgroup : CG\_BURST\_ADDR\_WRITE\_LEN

function **new**(string name, ovm\_component parent); cb\_wr\_lower\_blen\_limit = cov\_cfg.wr\_lower\_blen\_limit; if(cov\_cfg.cg\_disable\_wr\_blen\_cov == 0)

CG\_BURST\_ADDR\_WRITE\_LEN =

new(cb\_wr\_lower\_blen\_limit,....);

endfunction : new

task run;

if(cov\_cfg.cg\_disable\_wr\_blen\_cov == 0)

CG\_BURST\_ADDR\_WRITE\_LEN.sample();

endtask

Listing 5 : Covergroup definition and creation of covergroup based on enable/disable with the configurable parameters passed and sample() function call in run() phase.

verification HORIZONS

Coverage on parameters like *address* is also essential. However, for large *address* ranges, forming individual *bin* for each *address* might not be desirable or feasible. In such cases each bin can cover a range of addresses instead. Although the language has provided *auto\_bin\_max* construct for this, but it again has its own limitations, and this is where configurability comes in handy. For example, what if a user wants to define *address* range within which he/she wishes to measure coverage? The option *auto\_bin\_max* creates specified number of *bins* only if no *bins* have been defined explicitly and thus is not useful in this case. Listing 6 shows how the scenario can be created and achieved.

```

covergroup CG_WRITE_ADDR_COV(int cb_wr_addr_num_bins.....);

option.per_instance = 1;

CP_WRITE_ADDR_COV : coverpoint trans.Address {

bins CB_WRITE_ADDR_COV[cb_wr_addr_num_bins] =

{[cb_wr_lower_addr_limit : cb_wr_upper_addr_limit]];

option.at_least = cb_wr_addr_hit_count;

}

endgroup : CG_WRITE_ADDR_COV

```

Listing 6 : Covergroup definition with the [open\_range\_list] for the coverage of parameters like Address ranges

The number of *bins* that need to be created can be passed as a parameter to the *bin*. Thus now the entire *address* range is divided such that, first the number of *bins* configured by the user gets created, with each *bin* carrying an *address* range as specified by the user per bin. Number of hits per bin as desired by user, can also be controlled by using *option.atleast* (Listing 6).

**Cross Coverage:** Once individual coverage on each parameter has been checked, sometimes it's also important for a verification engineer to check *cross coverage*. In fact, there are some parameters which should be checked for coverage only w.r.t. other parameters. Sighting an AXI example to explain this, if user wants to check coverage on *Burst Length*, one cannot deduce useful coverage numbers unless it is measured w.r.t. to the *Burst Size*. This would help in giving the correct idea of the *narrow/aligned/unaligned transfers* taking place in the simulation. *Cross coverage* becomes essential in such cases.

Again, although *cross coverage* is important, but 100% coverage goal might not be desirable always for same. Let us consider *cross coverage* between two AXI parameters namely, *Burst Length* and *Burst Size*. Here, usually the requirement is to check that for each value of *Burst Size* all values of *Burst Lengths* have been hit and vice versa. However, if user knows that not all combination scenarios are valid as per his project specification, then he should be able to check for only required combinations of this cross coverage, ignoring the rest. For example, say for *Burst Length* > 1, the project specification requires *Burst Size* to be fixed to 16, then the user knows that rest of the values of *Burst Size* will never hit. In such a case, user should have the power to redefine his goals, so that he/she knows when to consider the RTL as covered. This flexibility is achieved by providing user configurable *goal* for *cross coverage*. The Listing 7 shows an example of *cross coverage* between *Burst Size* and *Burst Length*.

covergroup CG\_BURST\_WRSIZE\_CROSS\_LEN

(int cg\_wr\_size\_cross\_len\_target\_cov,....); option.per\_instance = 1; option.goal = cg\_wr\_size\_cross\_len\_target\_cov; type\_option.weight = 0; type\_option.goal = 0;

`CMP\_BURST\_ADDR\_WRITE\_SIZE `CMP\_BURST\_ADDR\_WRITE\_LEN CP\_BURST\_WRSIZE\_CROSS\_LEN: cross CP\_BURST\_ADDR\_WRITE\_SIZE , CP\_BURST\_ADDR\_WRITE\_LEN{ option.at\_least = cb\_wr\_bsize\_min\_hit\_count ;} endgroup : CG\_BURST\_ADDR\_WRITE\_SIZE\_CROSS\_LEN

Listing 7 : Example depicting the cross coverage between Burst Size & Burst length parameters (using macros in Listing 3 & 4). Here we have type\_option.weight = 0 as we are just focusing on the instance coverage rather than type coverage. The key features exploited in above coverage are as follows:

- Definition of cross coverpoints has been given in separate covergroup. This is useful in case user does not wish to measure cross coverage, then on the basis of disable, the covergroup will not be created thus making things simpler since the group does not appear in the report.

- Although the cross covergroups were defined separately, it was made sure that unnecessary code repetition is avoided by using SystemVerilog macros throughout.

- User configurable *goal* was also provided. This is done by using *"option.goal"*

- User configurable *hit count* was provided so that the user can decide how many *hits* of *Burst Size* are required for each *Burst Length* to consider a *bin* hit. This is done by providing configurable "option.atleast"

#### Error Coverage

Negative scenario testing is one of the stressed domains these days (especially for the complex protocols) to get a confidence on the behavior of the design. But again with this comes one big question - **Have I done enough error testing?**

So building a generic coverage model that can be used on a given setup to help the verification engineer know how much error testing he/ she has stressed upon as per given design specification, will help in closing negative testing quickly.

As is the case of AXI in our current study, we can introduce a widerange of error scenarios and test if the DUT responds correctly or not. A few possible error scenarios in AXI are listed in Listing 8 for your reference.

Note that each **error scenario** is attached to a **unique message ID** for coverage collection and report generation using OVM reporting mechanism. More about this is discussed below.

1. Corrupt the WLAST signal

- (AXI\_LAST\_WRITE\_TRANSFER\_SHOULD\_HAVE\_LAST\_BIT\_SET)

- Send a request originally for Y bytes while in the Data phase send only Y+1 beats.(AXI\_WLAST\_ASSERTED\_AFTER\_COMPLETE\_BEATS)

- 3. Drop a Write transfer in a Write transaction (Y beats) i.e. transfer Y-1 beat. (AXI\_WLAST\_ASSERTED\_BEFORE\_COMPLETE\_BEATS)

4. Corrupt the Write Response

a. SLVERR –(AXI\_WRITE\_RESPONSE\_SLVERR)

b. DECERR- (AXI\_WRITE\_RESPONSE\_DECERR)

5. Corrupt the Id field (AXI\_WRITE\_RESPONSE\_ID\_CORRUPTED)

However, all the scenarios may not be applicable to all the modules/ projects, so configurability is required to enable only the required set of *coverpoints*. Described below is an approach to deal with this requirement.

Here, we utilized the unique **Message ID** as a tool. Functional *coverpoints* were written on the unique message ID representing the error-scenarios being covered. However, the following assumption was made while developing this coverage model:

→ Every error scenario emits one unique message ID, although there may be more message ID's getting emitted from some other checks simultaneously, that might get triggered owing to a given scenario. These error message Id's were issued in the report log using immediate assertions with the help of OVM reporting functions like ovm\_report\_error, ovm\_report\_fatal etc...

Listing 9 explains the reporting facility of OVM used to achieve this.

ovm\_report\_global\_server glbl\_serv; ovm\_report\_server srve; function void build(); super.build(); srve = glbl\_serv.get\_server(); endfunction

Listing 9 : OVM global/report server to get a handle of server in the component class

As depicted, the **global report server** in OVM is used to get handle to the **ovm\_report\_server**, which in turn is used to access the methods of the **report server class**.

Using this handle, report server function *get\_id\_count(<string>)* is called, which takes a string i.e. the message ID as an argument and returns the incremented value of count variable that can be used in covergroup to indicate **hits** have happened, as depicted in Listing 10.

```

`define NUM_ID 10

reg [31:0][`NUM_ID:0] count;

task get_error_id();

while(1) begin

@(clk);

count[0] = srve.get_id_count("AXI_WRITE_ID_CORRUPTED");

......

count[n] = srve.get_id_count(<"Msg_ld_n">);

end

endtask

```

| task run();     |

|-----------------|

| fork            |

| get_error_id(); |

| join_none       |

| endtask         |

Listing 10 : Collecting the count of Message ID's in count variable. Task forked in the run() phase.

Now, using the *get\_config\_\**/set\_config\_\* utility of OVM, we get the object of configuration class, which basically contains the *enable*/ *disable* control for each covergroup. Using the strategy defined earlier in Listing 5, each *covergroup* is created in the class *constructor* on the basis of configuration, as set by the user.

With the code infrastructure in Listing 10, the count variable is passed to the covergroup for coverage definition. The overall definition of covergroup is depicted in Listing 11.

Note: We have used the 2-D **packed array** to collect the count of any given message ID, due to the fact that covergroup **doesn't allow unpacked arrays** to be passed as an argument.

class axi\_vip\_error\_coverage extends ovm\_component; `ovm\_component\_utils(axi\_vip\_error\_coverage)

axi\_vip\_coverage\_cfg cov\_cfg;

covergroup CG\_WR\_ID\_CORRUPTION (ref reg [31:0][17:0] count)@(clk); option.per\_instance = 1; CP\_AXI\_WRITE\_ID\_CORRUPTED: coverpoint count [0] {bins CB\_AXI\_WRITE\_ID\_CORRUPTED = {[1:\$]}; } endgroup : CG\_WR\_RESP\_ID\_CORRUPTION

function new (string name, ovm\_component parent);

ovm\_object obj;

super.new(name, parent);

assert(get\_config\_object("cov\_cfg", obj)); \$cast(cov\_cfg , obj);

```

if(cov_cfg.cg_disable_wr_resp_id_corrupt_cov == 0)

CG_WR_RESP_ID_CORRUPTION = new (count);

```

endfunction : new endclass : axi\_vip\_error\_coverage

Listing 11 : Covergroup using 2-D packed array variable for coverage on the individual message ID's

# Protocol Coverage (AXI handshake coverage)/ Flow Coverage

Protocol and flow coverage are mainly pertaining to the interface signals, on which various combination of their respective occurrence are possible, all of which are legal. Although all these combinations achieve the same functionality, a user may wish to know whether all the combinations have been really covered or not.

The reason why protocol and flow coverage were separated in two categories is that we focused on the scenarios defined by the **Standard AXI specs** as a part of **protocol coverage**, whereas

flow control describes coverage on user created scenarios. For coding both these aspects of coverage, a similar approach was used i.e. Assertion – based Functional Coverage, thus conceptually both will be discussed under a single head.

Again, in our AXI example, three combinations are possible with handshake signals (*READY/VALID*), on all the 5 respective channels, as per the AXI spec. Thus we need to ensure that we have covered all these combinations for all the 5 channels. There could be other similar combinations possible related to the interface pins that can be included under this type of coverage.

Assertion based coverage was used for this purpose since it fit the bill well for interface signals monitoring. SystemVerilog provides a construct called *cover property* for this specific requirement. A brief on *cover property* is discussed below.

SystemVerilog *property* helps us keep track of events occurring on interface signals. A *property* can be invoked in two ways:

- Assert property These are statements that assert the specified properties for its success/failure. Each assert property statement sets a flag in its action block if it fails.

- Cover Property- this is used to measure assertion *based coverage*. It has analogy to *bins*. In a *covergroup*, the way every *hit* in the *bin* increments its count by 1, so is the case with *Cover Property*. Every time the *property* is true, the count increments by 1 indicating a *hit*.

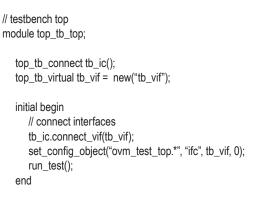

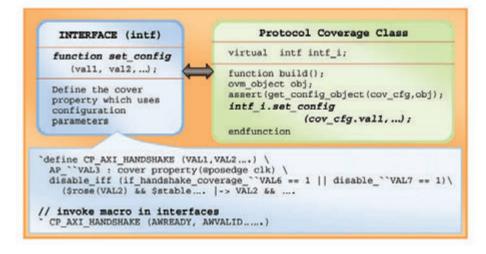

However, one of the major **limitations** of property is that it can **be declared and called only inside an interface or a module** container while configurability demands use of classes. Thus, it was very important to develop a relation between the two i.e. to pass configuration to the *interface* for it to be used by *cover property*. The schematic following depicts how we dealt with this limitation.

Figure 4 : Interface explored to write cover-property and class to exercise control over the properties

Figure 4 above shows a coverage class, which has a virtual interface. The connection of *virtual interface* to *real interface* is done in *build()* phase of this class. This class also takes all the configuration parameters from the *main coverage class*. On the other hand, we have *interface*, which has *cover property*. This interface also has a *set\_config* function (user defined), which as the name suggests, gets called from the class to set the configuration, as shown in Figure 4. Once set, these configuration parameters are used to control the behavior of the *cover property* defined in the *interface* as per user.

In order to avoid code repetition, a macro has been defined for the cover property so that it can be called for all the 5 channels in both master and slave interface, multiple times. Cover property has a *disable\_iff* construct for **conditional coverage**, but even if the condition is true and the property is disabled, only the hits to the property are made 0, while it still contributes to overall coverage.

In a cover property we don't have the concept of user-defined bins; Listing 12 specifies the command while Listing 13 is an example text report from the simulator – Mentor Graphics Questa.

vcover report -detail -cvg -directive -comments -file fcov.txt coverage.ucdb where,

-directive - is used to capture assertion based coverage.

Listing 12 : Command to view coverage in text format in Mentor Questa

| Name       | Design<br>Unit | Design<br>Unit Type                                                                             | Lang          | File (Line)     | Count     | Status |

|------------|----------------|-------------------------------------------------------------------------------------------------|---------------|-----------------|-----------|--------|

| /top/maste | er_conn/axi_vi | p_master_if_in                                                                                  | st[0]/AP_AW   | READY_BEFOR     | RE_AWVALI | D      |

| axi_v      | ip_master_if V | erilog SVA <pa< td=""><td>ath_to_file&gt;(</td><td>267) 18 Covered</td><td></td><td></td></pa<> | ath_to_file>( | 267) 18 Covered |           |        |

| /top/maste | er_conn/axi_vi | p_master_if_in                                                                                  | st[0]/AP_AW   | VALID_BEFOR     | E_AWREAD  | Y      |

|            | -              | erilog SVA <pa< td=""><td></td><td></td><td>-</td><td></td></pa<>                               |               |                 | -         |        |

Listing 13 : Assertion based coverage report as depicted in the text format - Questa

## LIMITATIONS

- SystemVerilog does not allow use of procedural statements and operators within a covergroup.

- The "*iff*" construct can be used for conditional dumping which can be used in *coverpoint* or *bin*. But this construct has limited functionality and only disables *coverpoint/bin* in *cross coverage* calculation thus providing limited functionality as explained below.

- o When used with *coverpoint* expression, the weight of each *coverpoint* has to be set explicitly based on whether the condition in *iff* construct is true or not. This is because the *iff* construct does not disable coverpoint in total coverage calculation even if the condition is false.

- o When used in *bins*, the *iff* construct does not disable actual dumping in *bin*. Talking about priority, *illegal\_bins* have highest priority, *bins* have least, meaning if an element is common to both *illegal\_bins* and *bins*, then it is dumped in illegal\_bins. However, conditional dumping is not possible here i.e. even if the condition in *iff* construct related to *illegal\_bins* is false, the element is still considered to be part of *illegal\_bins* and not *bins*. Thus conditional dumping in *illegal\_bins* is not possible.

- auto\_bin\_max option can be used only if no bins have been defined explicitly for a *coverpoint*. When the *bins* are explicitly defined by a user, a configurable [open\_range\_list] specification is needed in cases where user wishes to restrict the number of bins..

- Covergroups do not take unpacked arrays as an argument.

- A covergroup has to be created within the class constructor. Thus, the configuration to be passed to the group must be available in the class constructor only. So user has to get the **configuration** in **class constructor only** and OVM phases cannot be exploited much here. It should also be noted here that as per common coding practice, we always set and get configuration in build,

# verification HORIZONS

but due to this limitation everything has to be done in class constructor.

- As a matter of fact, SystemVerilog provides 2 types of coverage numbers, namely

- o Type Coverage gives the overall coverage which is sum of all the instances

- o Instance Coverage gives the coverage of individual instances

Thus, if a user creates a single instance, then the above two coverage numbers should ideally match. However, this is not the case always. The following example from AXI elaborates more on this. Our design supported a *Burst Type of INCR* type while the AXI spec. specifies this *INCR*, *FIXED*, *WRAP* as the legal set of values. So Type coverage would say 33.33% even if we covered *INCR Burst Type* as per our specification, while the instance coverage would report 100%.

This is because of SystemVerilog limitation. *type\_option* cannot have **weights** as a parameter, it has to be a **constant**. Also, there are many options which are available for *instance coverage* but not for *type coverage viz. at\_least, auto\_bin\_max* etc. This leads to an unavoidable mismatch between type and instance coverage even if user has a single instance.

- Assertion based coverage was used for AXI handshake coverage. One of the limitations faced was incorporating the concept of configurability. This is because *cover property* cannot be defined inside a *class*. Thus, when we get the *configuration* inside the *class*, we had to find a method to export this configuration to *interface* where *cover property* could be defined.

- Also, there is no way to exclude a property from overall coverage calculation. Although SystemVerilog provides with "disable\_iff" construct for conditional coverage, it still takes it into account the disabled property while calculating total coverage. Hence the final coverage number would be lower than actual

- The user-defined configurable covergroup parameters have to be passed to the covergroup while creating its instance. Any class instantiating this covergroup, shall do so within its own constructor (Refer to Listing 5). Thus, all the configuration parameters should be ready in the instantiating class's constructor itself. This poses a big limitation to develop configurable model since the configuration has to be made available in class constructor itself while the rest of the OVM test bench code is usually spread across various OVM phases following the new() constructor. So what if a user wants to decide on the configuration parameters at a later stage during the simulation?

- o **Solution:** SystemVerilog 2009 provides a solution to this limitation by providing a method to override the built-in sample function. In this method, the pre-defined *sample()* method is overridden with a triggering function that accepts arguments and facilitates sampling of coverage data from contexts other than the scope enclosing the *covergroup* definition. For example, an overridden *sample* method can be called with different arguments to pass directly to a *covergroup*, the data to be sampled. These arguments can come from either an automatic task or function, or from a particular instance of a process, or from a sequence or a property of a concurrent assertion. Listing 14 describes how this can be achieved.

- Limitation to above solution: Although the latest version of SystemVerilog (2009) has provided this feature but it is still not supported by EDA tools and hence is not much use at this time.

covergroup p\_cg with function sample(bit a,int x); coverpoint x; cross x.a;

endgroup : p\_cg

p\_cg **cg1** = new;

```

property p1;

int x;

@(posedge clk) (a, x = b) ##1 (c, cg1.sample(a,x));

endproperty :p1

c1: cover property (p1);

```

```

function automatic void F(int j);

bit d;

....

cg1.sample(d,j);

endfunction

```

Listing 14 : Example usage of new sample() function. Here a covergroup is defined and created. Also, it depicts the 2 methods of overriding the sample() function i.e. overriding sample() method from within a property and pass them as arguments and also overriding the parameters within a function and pass them as arguments.

### SUGGESTIONS

Some basic coding practices that a user should follow while coding these coverage models, which will help in ease of use as well as less maintenance in the long-term: