# The IDT79R3071<sup>™</sup>, IDT 79R3081<sup>™</sup> RISController<sup>™</sup> Hardware User's Manual

**Revision 2.0**

April 4, 1994

## ABOUT THIS MANUAL

This manual provides a qualitative description of the operation of the IDT 79R3071 and IDT 79R3081, members of the IDT R30xx family of integrated RISControllers.

A quantitative description of the processor electrical interface is provided in the data sheets for these products. Also included in the data sheets are the mechanical descriptions of the parts, including packaging and pin-out.

Additional information on development tools, complementary support chips, and the use of this product in various applications, is provided in separate data sheets, applications notes, software reference manuals, and IDT Advantage Program Guide.

Additional information on other family members can be found in the documentation for those devices.

Any of this information is readily available from your local IDT sales representative.

### **CONTENTSOVER VIEW**

**Chapter 1** contains an overview description of the R3071/R3081 integrated RISControllers, including a brief discussion of development tools and a family overview.

Chapter 2 describes the instruction set architecture of the R3071/R3081.

**Chapter 3** describes the instruction set architecture of the on-chip hardware floating point unit of the R3071/R3081.

Chapter 4 describes the on-chip caches of the R3071/R3081.

**Chapter 5** discusses the memory management capabilities of the R3071/R3081.

**Chapter 6** describes the exception interface and handling capabilities of the processors.

Chapter 7 provides an overview of the bus interface of the R3071/R3081, including signal description and transaction priority model.

**Chapter 8** describes the read interface of the R3071/R3081.

**Chapter 9** describes the write interface of the R3071/R3081.

**Chapter 10** describes the DMA Arbiter interface and cache coherency mechanisms of the devices.

Chapter 11 describes the reset, mode initialization, and clocking of the processors.

**Chapter 12** describes various debug features of the processors.

$\label{eq:Appendix A describes design considerations for systems which may interchange among the R3041, R3051, R3052, R3071, and R3081 processors.$

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

- Life support devices or systems are devices or systems which (a) are intended for surgical implant into

the body or (b) support or sustain life and whose failure to perform, when properly used in accordance

with instructions for use provided in the labeling, can be reasonably expected to result in a significant

injury to the user.

- A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

The IDT logo is a registered trademark and RISController, R3051, R3041, R3071, R3081 and RISChipset are trademarks of Integrated Device Technology, Inc.

MIPS is a registered trademarks of MIPS Computer Systems, Inc.

UNIX is a registered trademark of AT&T.

MC680x0 and iAPXx86 are registered trademarks of Motorola Corporation and Intel Corporation, respectively.

# TABLE OF CONTENTS

| Family Overview                                                                | 1-1        |

|--------------------------------------------------------------------------------|------------|

| Introduction                                                                   | 1-1        |

| Features                                                                       | 1-1        |

| Device Overview                                                                | 1-2        |

| CPU Core                                                                       | 1-3        |

| System Control Co-Processor                                                    | 1-4        |

| Floating Point Co-Processor                                                    | 1-4        |

| Clock Generator Unit                                                           | 1-4        |

| Instruction Cache                                                              | 1-4        |

| Data Cache                                                                     | 1-5        |

| Bus Interface Unit                                                             | 1-5        |

| System Usage                                                                   | 1-6        |

| Development Support                                                            | 1-8        |

| Performance Overview                                                           | 1-10       |

| Family Instruction Set Architecture                                            | 2-1        |

| Introduction                                                                   | 2-1        |

| R3051 Family Processor Features Overview                                       | 2-1        |

| CPU Registers Overview                                                         | 2-1        |

| Instruction Set Overview                                                       | 2-2        |

| Programming Model                                                              | 2-4        |

| Data Formats and Addressing                                                    | 2-4        |

| CPU General Registers                                                          | 2-6        |

| CPO Special Registers                                                          | 2-6        |

| Operating Modes                                                                | 2-7        |

| Pipeline Architecture                                                          | 2-7        |

| Pipeline Hazards                                                               | 2-8        |

| Instruction Set Summary                                                        | 2-10       |

| Instruction Formats                                                            | 2-10       |

| Instruction Notational Conventions                                             | 2-10       |

| Load and Store Instructions                                                    | 2-10       |

| Computational Instructions                                                     | 2-13       |

| Jump and Branch Instructions                                                   | 2-15       |

| Special Instructions                                                           | 2-16       |

| Co-processor Instructions                                                      | 2-17       |

| System Control Co-processor Instructions                                       | 2-18       |

| Opcode Encoding                                                                | 2-18       |

| R3081 Floating Point Accelerator                                               | 3-1        |

| Introduction                                                                   | 3-1        |

| FPA Features                                                                   | 3-1        |

| FPA Programming Model                                                          | 3-2        |

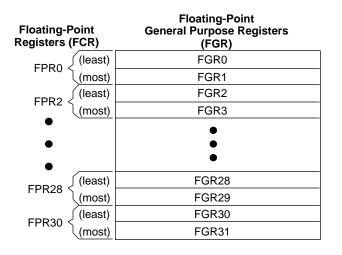

| Floating-Point General Registers                                               | 3-2        |

| Floating-Point Registers                                                       | 3-2        |

| Floating-Point Registers                                                       | 3-3        |

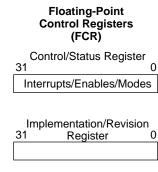

| Control/Status Register (Read and Write)                                       | 3-3        |

| Control/Status Register Condition Bit                                          | 3-3        |

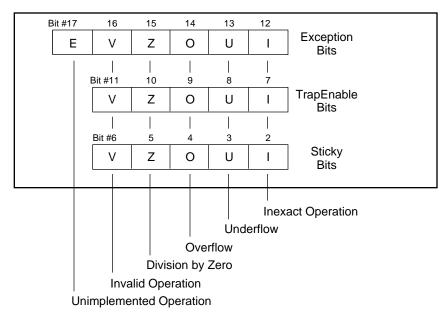

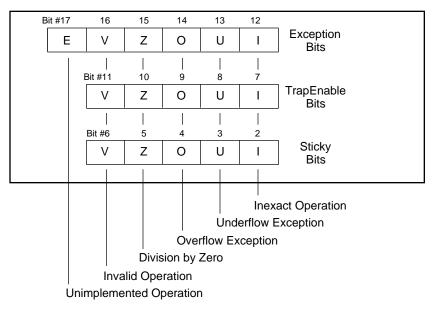

| Control/Status Register Exception Bits                                         | 3-4        |

| Control/Status Register Exception Bits                                         | 3-4        |

| Control/Status Register Exception Bits Control/Status Register TrapEnable Bits | 3-5        |

| Control/Status Register Rounding Mode Control Bits                             | 3-5        |

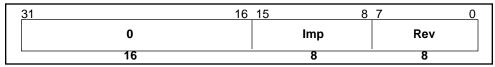

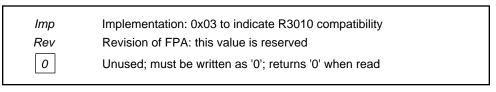

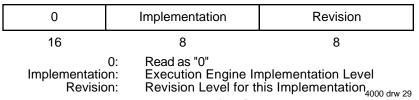

| Implementation and Revision Register (Read Only)                               | 3-5<br>3-5 |

| mipicincitation and iterision itegister (iteau Ulliv)                          | J-J        |

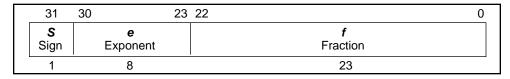

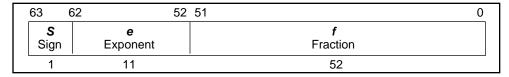

| Floating-Point Formats                    | 3-6  |

|-------------------------------------------|------|

| Number Definitions                        | 3-7  |

| Normalized Numbers                        | 3-7  |

| Denormalized Numbers                      | 3-7  |

| Infinity                                  | 3-7  |

| Zero                                      | 3-7  |

| Co-Processor Operation                    | 3-8  |

| Load, Store and Move Operations           | 3-8  |

| Floating-Point Operations                 | 3-8  |

| Exceptions                                | 3-8  |

| Instruction Set Overview                  | 3-8  |

| Instruction Set Summary                   | 3-10 |

| Load, Store and Move Operations           | 3-10 |

| Floating-Point Computational Instructions | 3-10 |

| Floating-Point Relational Instructions    | 3-13 |

| Branch On FPA Condition Instructions      | 3-14 |

| FPA Opcode Encoding                       | 3-15 |

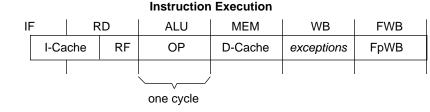

| The Instruction Pipeline                  | 3-16 |

| Instruction Execution Times               | 3-18 |

| Overlapping FPA Instructions              | 3-19 |

| R3081 Cache Architecture                  | 4-1  |

| Introduction                              | 4-1  |

| Fundamentals of Cache Operation           | 4-1  |

| R3081 Cache Organization                  | 4-2  |

| Basic Cache Operation                     | 4-2  |

| Memory Address to Cache Location Mapping  | 4-2  |

| Cache Addressing                          | 4-3  |

| Write Policy                              | 4-3  |

| Partial Word Writes                       | 4-3  |

| Instruction Cache Line Size               | 4-3  |

| Data Cache Line Size                      | 4-4  |

| Cache Configurability                     | 4-5  |

| Cache Construction Summary                | 4-5  |

| Cache Operation                           | 4-6  |

| Basic Cache Fetch Operation               | 4-6  |

| Cache Miss Processing                     | 4-6  |

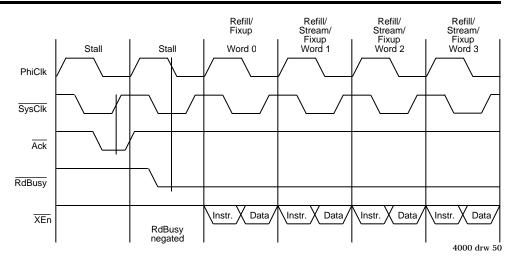

| Instruction Streaming                     | 4-7  |

| Cacheable References                      | 4-7  |

| Software Directed Cache Operations        | 4-7  |

| Cache Sizing                              | 4-8  |

| Cache Flushing                            | 4-8  |

| Forcing Data Into Caches                  | 4-9  |

| Summary                                   | 4-9  |

| Memory Management                         | 5-1  |

| Introduction                              | 5-1  |

| Virtual Memory In the R3051 Family        | 5-1  |

| Privilege States                          | 5-2  |

| User Mode Virtual Addressing              | 5-2  |

| Kernel Mode Virtual Addressing            | 5-2  |

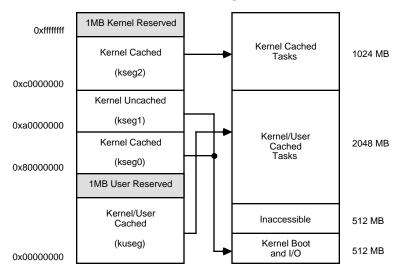

| Base Versions Address Translation         | 5-3  |

| Extended Versions Address Translation     | 5-5  |

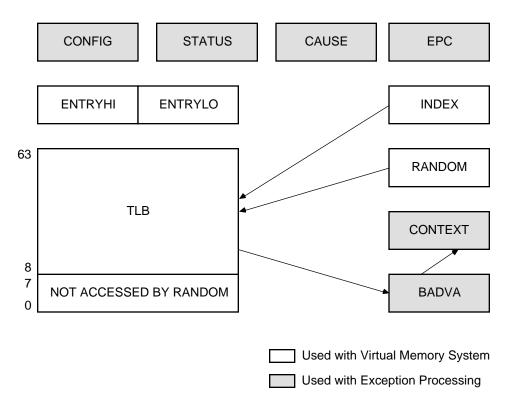

| TLB Entries                               | 5-6  |

| EntryHi and EntryLo Registers             | 5-6  |

| Virtual Address Translation               | 5-7  |

| The Index Register                        | 5-8  |

| The Random Register                       | 5-9  |

| TLB Instructions                          | 5-9  |

| TLB Shutdown                              | 5-10 |

| Summary                                           | 5-10 |

|---------------------------------------------------|------|

| Exception Handling                                | 6-1  |

| Introduction                                      | 6-1  |

| R3051 Family Exception Model                      | 6-1  |

| Precise vs. Imprecise Exceptions                  | 6-2  |

| Exception Processing                              | 6-3  |

| Exception Handling Registers                      | 6-3  |

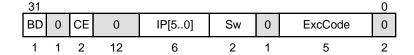

| The Cause Register                                | 6-4  |

| The EPC Register                                  | 6-5  |

| Bad VAddr Register                                | 6-5  |

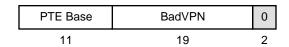

| Context Register                                  | 6-5  |

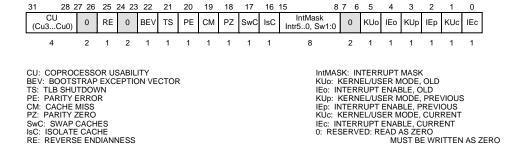

| The Status Register                               | 6-6  |

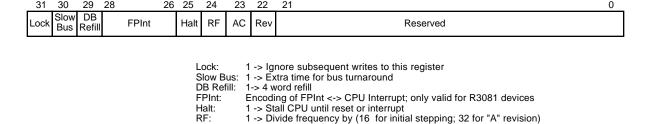

| The Config Register                               | 6-8  |

| Lock:                                             | 6-8  |

| Slow Bus                                          | 6-8  |

| FPInt:                                            | 6-9  |

| DB Refill:                                        | 6-9  |

| RF:                                               | 6-9  |

| Halt:                                             | 6-9  |

| Alt Cache:                                        | 6-10 |

| Reserved:                                         | 6-10 |

| PrId Register                                     | 6-10 |

| Exception Vector Locations                        | 6-10 |

| •                                                 | 6-10 |

| Exception Prioritization                          | 6-11 |

| Exception Latency                                 | 6-12 |

| Interrupts in the R3051 Family                    |      |

| Using The BrCond Inputs                           | 6-14 |

| Interrupt Handling                                | 6-14 |

| Interrupt Servicing                               | 6-15 |

| Basic Software Techniques for Handling Interrupts | 6-15 |

| Preserving Context                                | 6-16 |

| Determining the Cause of the Exception            | 6-17 |

| Return From Exceptions                            | 6-18 |

| Special Techniques for Interrupt Handling         | 6-19 |

| Interrupt Masking                                 | 6-19 |

| Using the BrCond for Fast Response                | 6-19 |

| Nested Interrupts                                 | 6-21 |

| Catastrophic Exceptions                           | 6-22 |

| Handling Specific Exceptions                      | 6-23 |

| Address Error Exception                           | 6-23 |

| Breakpoint Exception                              | 6-24 |

| Bus Error Exception                               | 6-25 |

| Co-processor-Unusable Exception                   | 6-26 |

| Interrupt Exception                               | 6-27 |

| Overflow Exception                                | 6-28 |

| Reserved Instruction Exception                    | 6-29 |

| Reset Exception                                   | 6-30 |

| System Call Exception                             | 6-31 |

| TLB Miss Exceptions                               | 6-32 |

| TLB Miss Exception                                | 6-33 |

| TLB Modified Exception                            | 6-34 |

| UTLB Miss Exception                               | 6-35 |

| Floating-Point Exceptions                         | 6-36 |

| Exception Trap Processing                         | 6-37 |

| Inexact Exception                                 | 6-39 |

| Invalid Operation Exception (V)                   | 6-39 |

| Division-By-Zero Exception                        | 6-40 |

| Underflow Exception                               | 6-40 |

| Unimplemented Operation Exception (E)                                    | 6-40         |

|--------------------------------------------------------------------------|--------------|

| Saving and Restoring State                                               | 6-41         |

| Interface Overview                                                       | 7-1          |

| Multiple Operations                                                      | 7-2          |

| Execution Engine Fundamentals                                            | 7-4          |

| Execution Core Cycles                                                    | 7-4          |

| Cycles                                                                   | 7-4          |

| Run Cycles                                                               | 7-4          |

| Stall Cycles                                                             | 7-4          |

| Multiple Stalls                                                          | 7-5          |

| Pin Description                                                          | 7-6          |

| Read Interface                                                           | 8-1          |

| Introduction Types of Read Transactions                                  | 8-1          |

| Types of Read Transactions                                               | 8-1<br>8-2   |

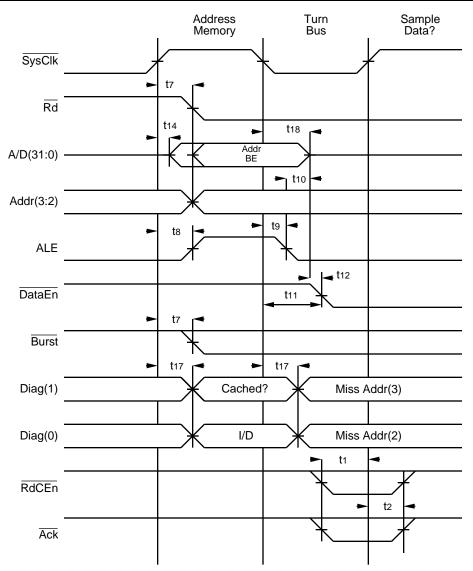

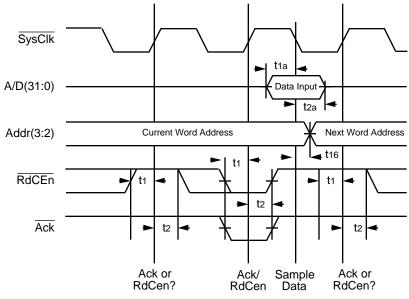

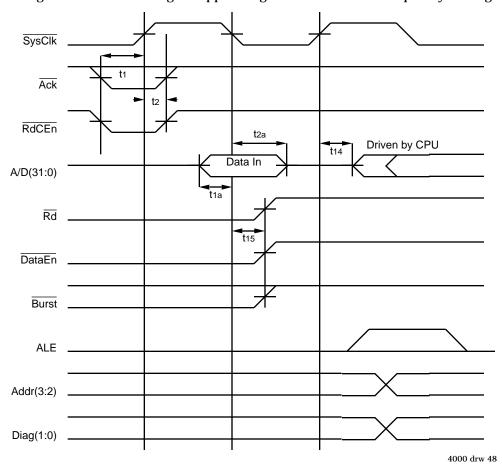

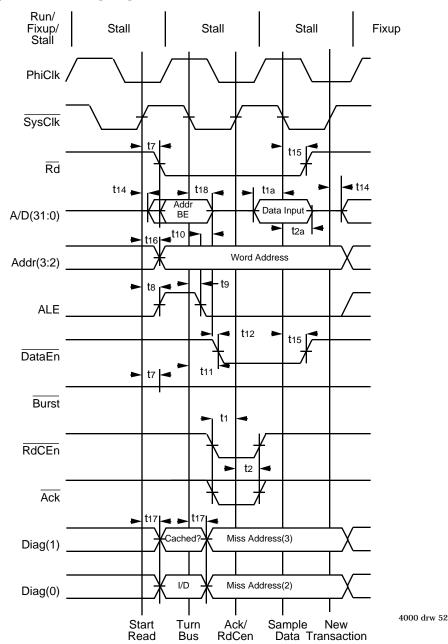

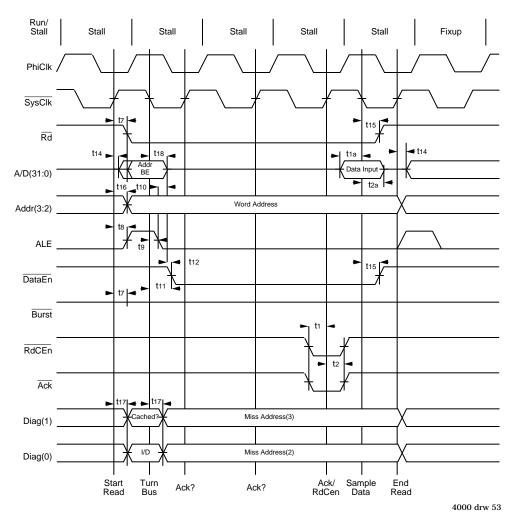

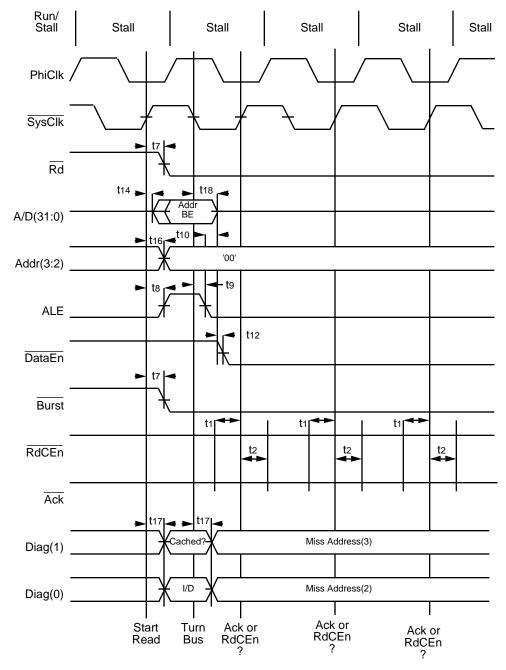

| Read Interface Signals Read Interface Timing Overview                    | 8-2<br>8-4   |

| Initiation of Read Request                                               | 8-4          |

| Memory Addressing                                                        | 8-6          |

| Bus Turn Around                                                          | 8-6          |

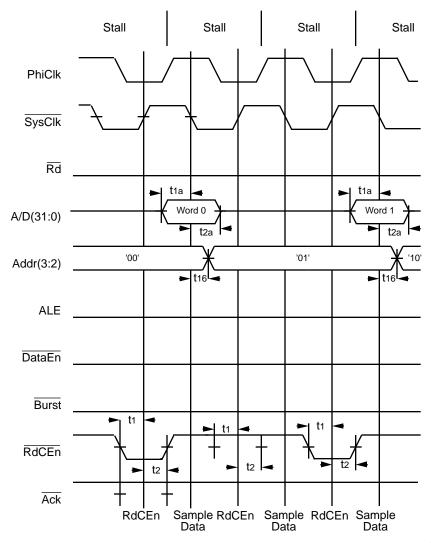

| Bringing Data into the Processor                                         | 8-7          |

| Terminating the Read                                                     | 8-8          |

| Latency Between Processor Operations                                     | 8-9          |

| Processor Internal Activity                                              | 8-11         |

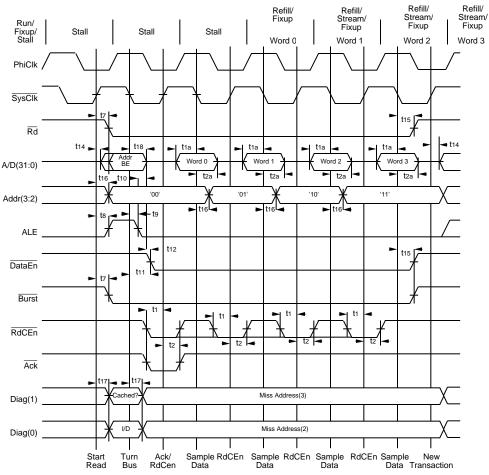

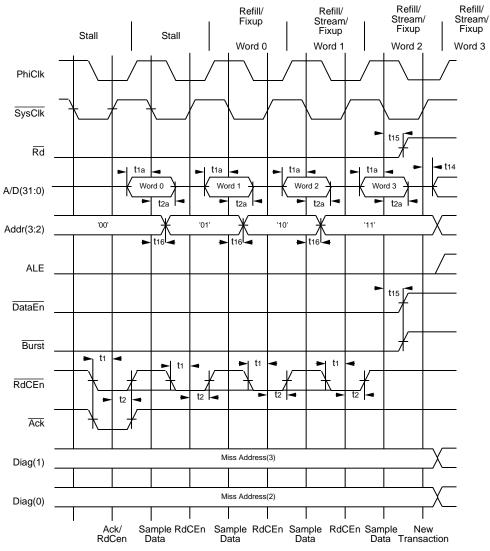

| Read Timing Diagrams                                                     | 8-13         |

| Single Word Reads                                                        | 8-13         |

| Block Reads                                                              | 8-15         |

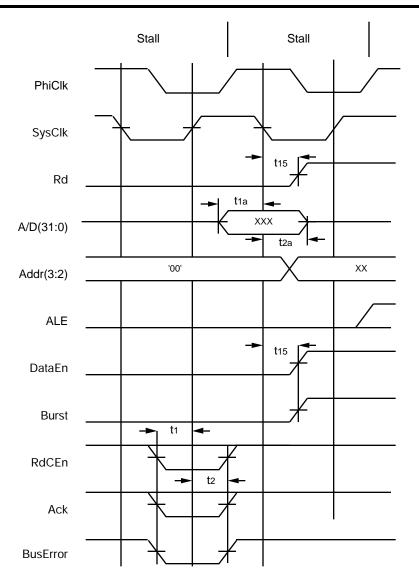

| Bus Error Operation                                                      | 8-20         |

| Write Interface                                                          | 9-1          |

| Introduction                                                             | 9-1          |

| Importance of Writes in R3081 Systems                                    | 9-1          |

| Types of Write Transactions                                              | 9-2          |

| Partial Word Writes                                                      | 9-2          |

| Write Interface Signals Write Interface Timing Overview                  | 9-3<br>9-5   |

| Initiating the write                                                     | 9-5<br>9-5   |

| Memory Addressing                                                        | 9-6          |

| Data Phase                                                               | 9-7          |

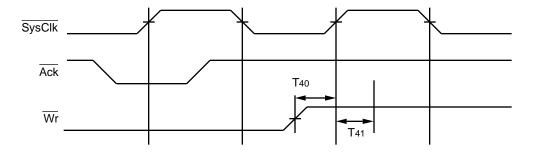

| Terminating the Write                                                    | 9-8          |

| Latency Between Processor Operations                                     | 9-8          |

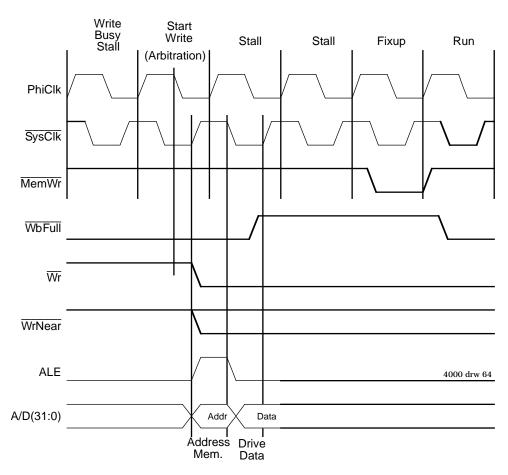

| Write buffer Full Operation                                              | 9-9          |

| Write Timing Diagrams                                                    | 9-10         |

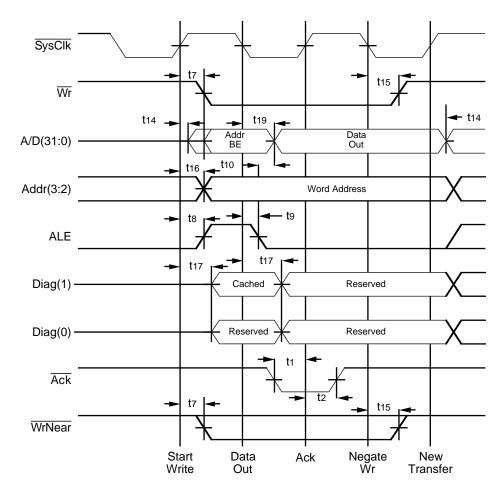

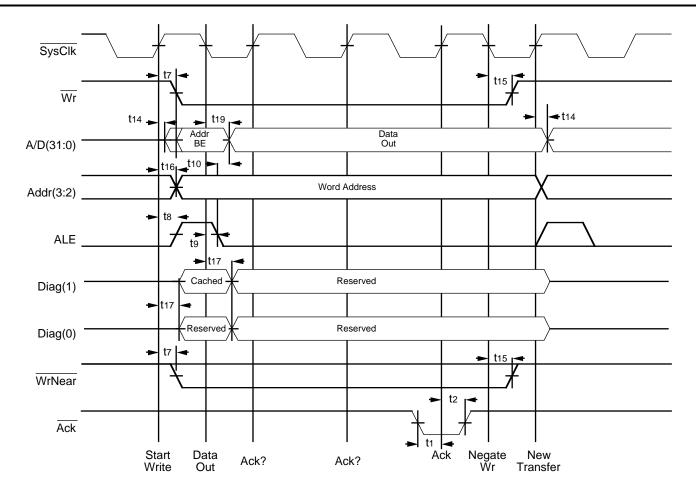

| Basic Write                                                              | 9-10         |

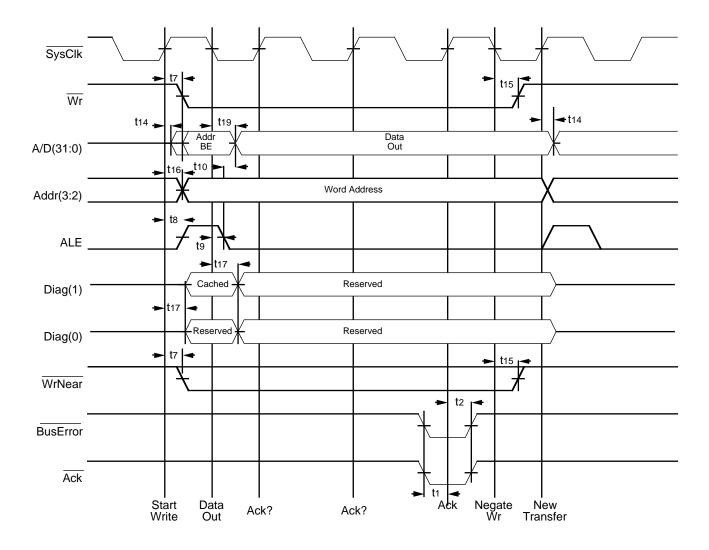

| Bus Error Operation                                                      | 9-12         |

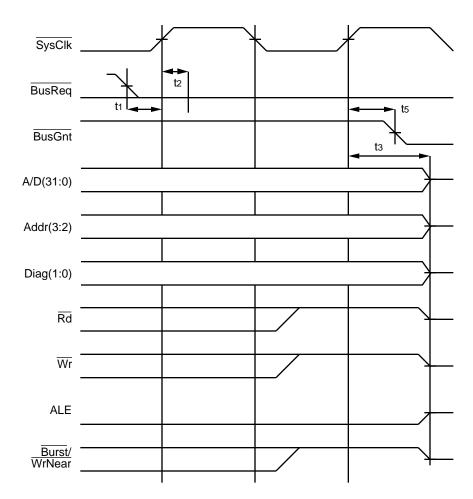

| DMA Interface and Cache Coherency                                        | 10-1         |

| Introduction                                                             | 10-1         |

| Interface Overview                                                       | 10-1         |

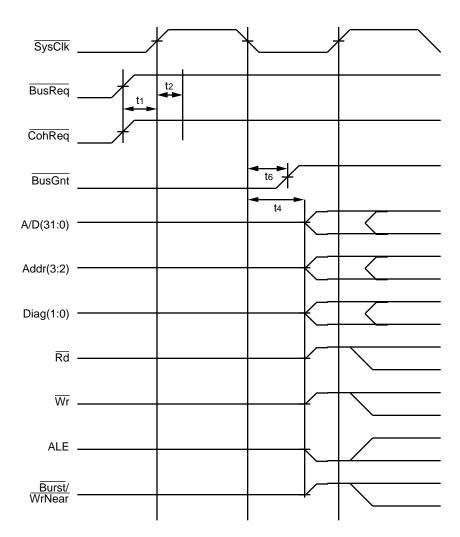

| DMA Arbiter Interface Signals                                            | 10-2         |

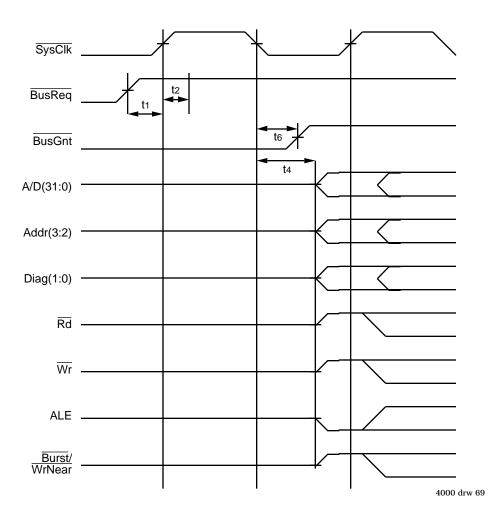

| Non-Coherent DMA Arbitration Timing Diagrams                             | 10-3         |

| Initiation of DMA Mastership<br>Relinquishing Mastership Back to the CPU | 10-3<br>10-4 |

| Hardware-Based Cache Coherency                                           | 10-4         |

| Cache Coherency Interface Signals                                        | 10-3         |

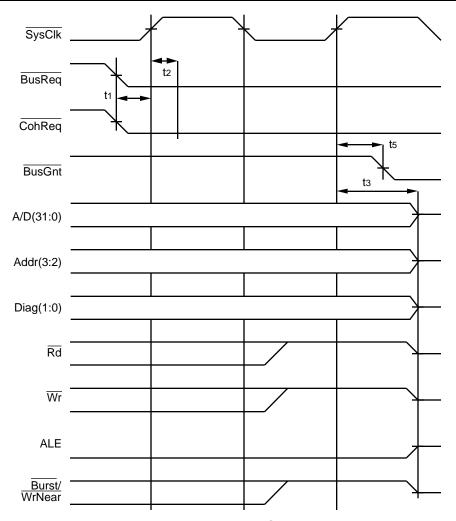

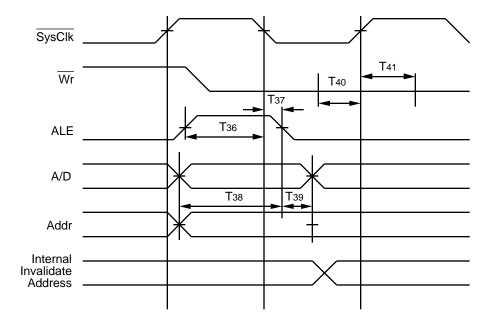

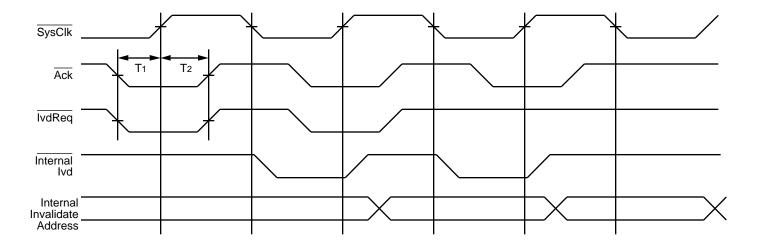

| Cache Coherency Operations Timing                                        | 10-7         |

| Initiating Coherent DMA                                                  | 10-7         |

| Capturing Write Target Address                                           | 10-9         |

| Invalidating the Data Cache Word                                         | 10-10        |

| Ending the Current Write                                                 | 10-11        |

| Terminating the Coherent DMA                                             | 10-12        |

|                                                                          |              |

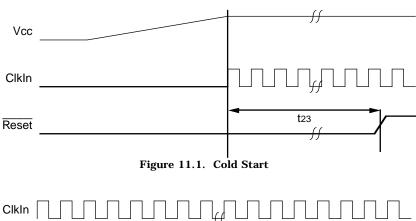

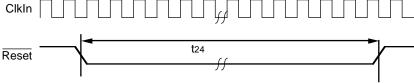

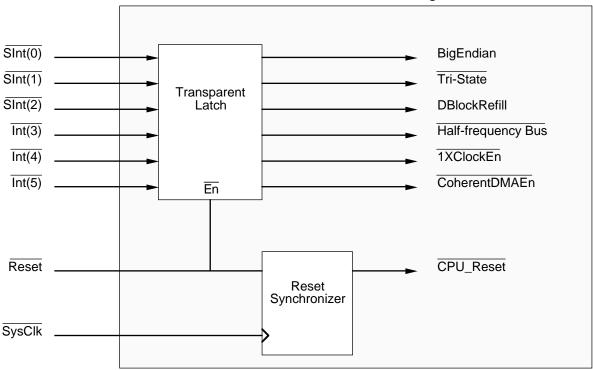

| Reset Initialization and Input Clocking                   | 11-1         |

|-----------------------------------------------------------|--------------|

| Introduction                                              | 11-1         |

| Reset Timing                                              | 11-1         |

| Mode Selectable Features                                  | 11-1         |

| CoherentDMAEn                                             | 11-1         |

| 1xClockEn                                                 | 11-1         |

| Half-Frequency Bus                                        | 11-2         |

| DBlockRefill                                              | 11-2         |

| Tri-State                                                 | 11-2         |

| BigEndian                                                 | 11-2         |

| R3000A Equivilant Modes<br>Reset Behavior                 | 11-2         |

|                                                           | 11-3         |

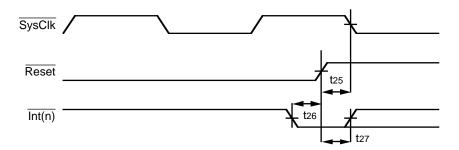

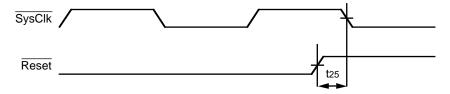

| Boot Software Requirements Detailed Reset Timing Diagrams | 11-3<br>11-4 |

| Reset Pulse Width                                         | 11-4         |

| Mode Initialization Timing Requirements                   | 11-4         |

| Reset Setup Time Requirements                             | 11-6         |

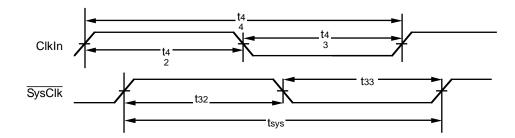

| ClkIn Requirements                                        | 11-6         |

| Debug Mode Features                                       | 12-1         |

| Introduction                                              | 12-1         |

| Overview of Features                                      | 12-1         |

| Debug Mode Activation                                     | 12-1         |

| Address Display                                           | 12-2         |

| Run Status Display                                        | 12-2         |

| Forcing Cache Misses                                      | 12-4         |

| Compatibility Among R3051 Family Devices                  | A-1          |

| Introduction                                              | A-1          |

| Software Considerations                                   | A-1          |

| Hardware Considerations                                   | A-2          |

| R3041 Unique Features                                     | A-2          |

| R3081 Unique Features                                     | A-3          |

| Pin Description Differences                               | A-3          |

| Reset Mode Selection                                      | A-4          |

| Reserved No-Connect Pins                                  | A-5          |

| DIAG Pins                                                 | A-5          |

| BrCond(1:0), SBrCond(3:2)                                 | A-5          |

| Slow Bus Turn Around Mode                                 | A-6          |

| The R3081 FPA Interrupt                                   | A-6          |

| Half-Frequency Bus Mode                                   | A-6          |

| Reduced Frequency/Halt Capability                         | A-6          |

| DMA Issues                                                | A-6          |

| Debug Features                                            | A-7          |

| WrNear Page Size                                          | A-7          |

| Hardware Compatibility Summary                            | A-7          |

| Summary                                                   | A-8          |

| List of Figures                                           |              |

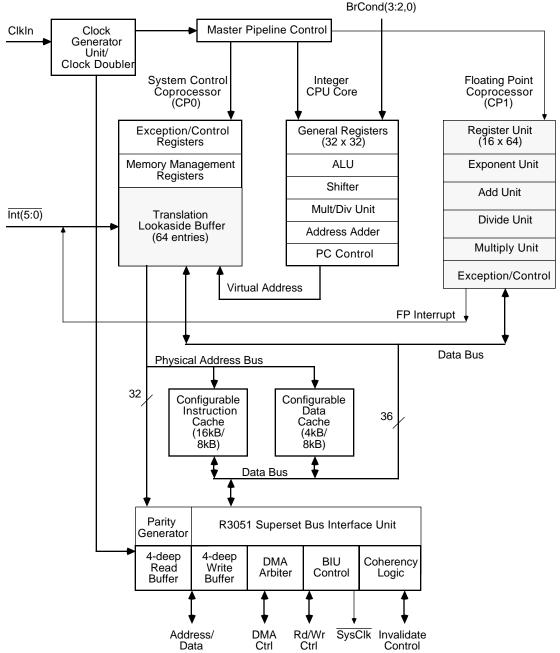

| 1.1. Block Diagram                                        | 1-3          |

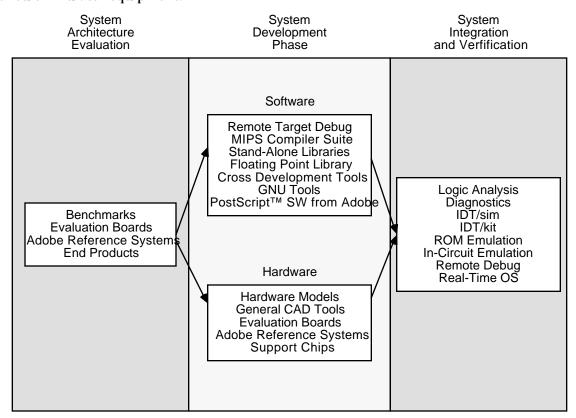

| 1.2. System Diagram                                       | 1-7          |

| 1.3. Development Support                                  | 1-9          |

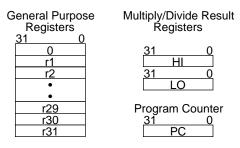

| 2.1. CPU Registers                                        | 2-1          |

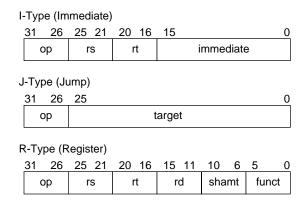

| 2.2. Instruction Encoding                                 | 2-2          |

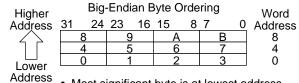

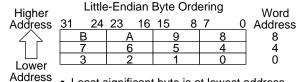

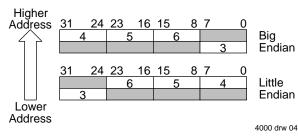

| 2.3. Byte Ordering Conventions                            | 2-5          |

| 2.4. Unaligned Words                                      | 2-5          |

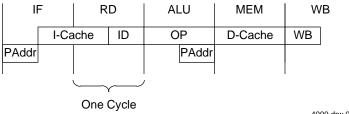

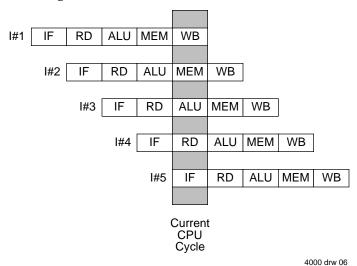

| 2.5. 5-Stage Pipeline                                     | 2-7          |

| 2.6. 5-Instructions per Clock Cycle                       | 2-8          |

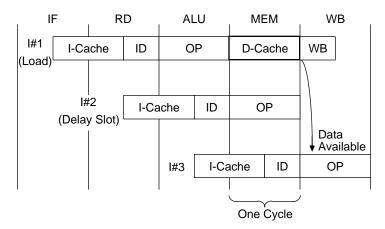

| 2.7. Load Delay                                           | 2-9          |

| 0.0 Possed Deles                                                  | 0.0  |

|-------------------------------------------------------------------|------|

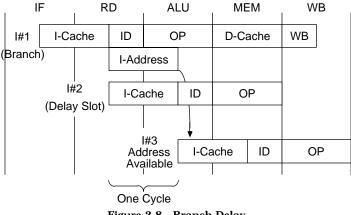

| 2.8. Branch Delay                                                 | 2-9  |

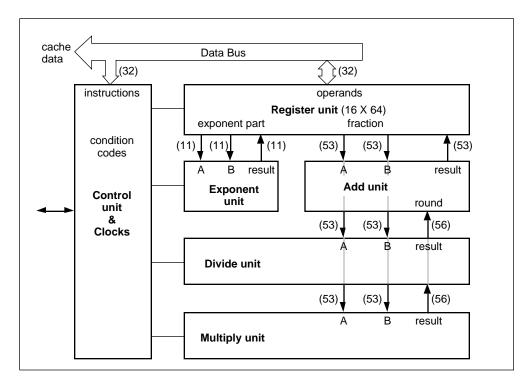

| 3.1. On-Chip FPA Functional Block Diagram                         | 3-1  |

| 3.2. FPA Registers                                                | 3-2  |

| 3.3. Control/Status Register Bit Assignments                      | 3-3  |

| 3.4. Control/Status Register Exception/Sticky/Trap Enable Bits    | 3-4  |

| 3.5. Implementation/Revision Register                             | 3-5  |

| 3.6. Single Precision Floating Point Format                       | 3-6  |

| 3.7. Double Precision Floating Point Format                       | 3-6  |

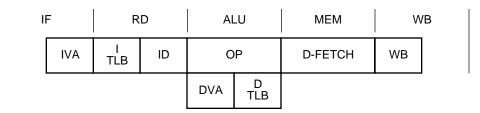

| 3.8. FPA Instruction Execution Sequence                           | 3-16 |

| 3.9. FPA Instruction Pipeline                                     | 3-17 |

| 3.10. An FPA Pipeline Stall                                       | 3-17 |

| 3.11. FPA Instruction Execution Times                             | 3-18 |

| 3.12. Overlapping FPA Instructions                                | 3-19 |

| 3.13. Overlapped Instructions in FPA Pipeline                     | 3-20 |

| 4.1. Cache Line Selection                                         | 4-2  |

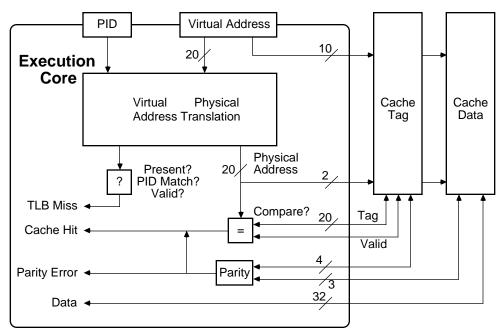

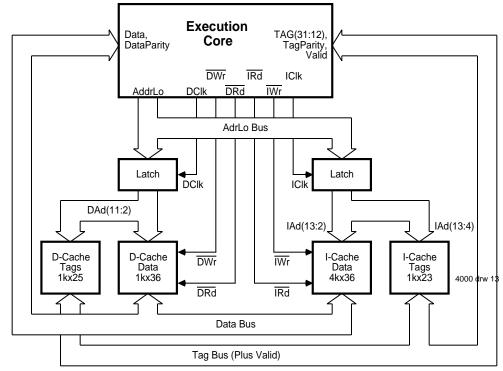

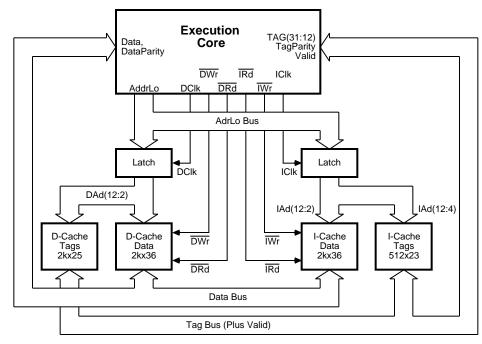

| 4.2. R3081 Execution Core and Cache Interface                     | 4-4  |

| 4.3. R3081 Execution Core and Cache Interface                     | 4-5  |

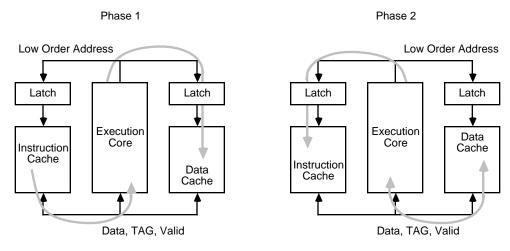

| 4.4. Phased Access of Instruction and Data Caches                 | 4-6  |

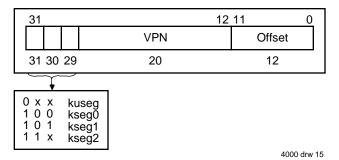

| 5.1. Virtual Address Format                                       | 5-1  |

| 5.2. Virtual to Physical Address Translation in Base Versions     | 5-2  |

| 5.3. Virtual to Physical Address Mapping of Extended Archit.      | 5-4  |

| 5.4. The System Co-Processor Registers                            | 5-5  |

| 5.5. Format of a TLB Entry                                        | 5-6  |

| 5.6. The TLB EntryLo and EntryHi Registers                        | 5-6  |

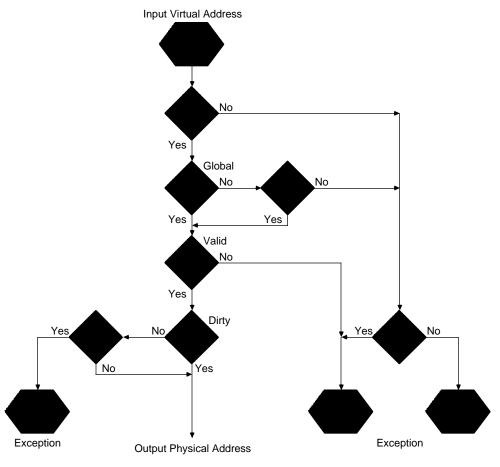

| 5.7. TLB Address Translation                                      | 5-7  |

| 5.8. Virtual to Physical TLB Translation                          | 5-8  |

| 5.9. The Index Register                                           | 5-9  |

| 5.10. The Random Register                                         | 5-9  |

| 6.1. The CPO Execution Handling Registers                         | 6-3  |

| 6.2. The Cause Register                                           | 6-4  |

| 6.3. Context Register                                             | 6-5  |

| 6.4. The Status Register                                          | 6-6  |

| 6.5. R3081 Config Register                                        | 6-8  |

| 6.6. Format of Prid Register                                      | 6-10 |

| 6.7. Pipelining in the R3051 Family                               | 6-11 |

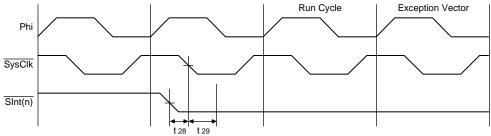

| 6.8. Synchronized Interrupt Operation                             | 6-13 |

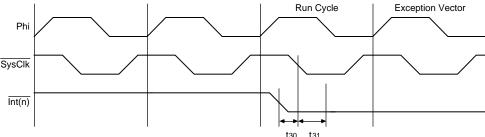

| 6.9. Direxct Interrupt Operation                                  | 6-13 |

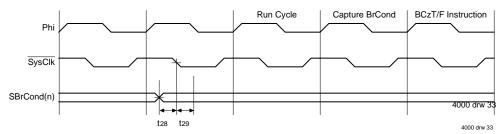

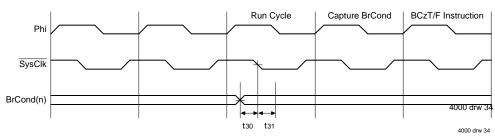

| 6.10. Synchronized BrCond Inputs                                  | 6-14 |

| 6.11. Direct BrCond Inputs                                        | 6-14 |

| 6.12. Kernal and Interrupt Status Being Saved on Interrupts       | 6-15 |

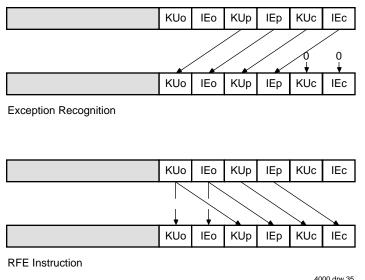

| 6.13. Code Sequence to Initialize Exception Vectors               | 6-16 |

| 6.14. Preserving Processor Context                                | 6-17 |

| 6.15. Exception Cause Decoding                                    | 6-17 |

| 6.16. Exception Service Branch Table                              | 6-18 |

| 6.17. Returning from Exception                                    | 6-18 |

| 6.18. Polling System Using BrCond                                 | 6-20 |

| 6.19. Using BrCond for Fast Interrupt Decoding                    | 6-21 |

| 6.20. TLB Miss Exceptions                                         | 6-32 |

| 6.21. User TLB Refill Code                                        | 6-35 |

| 6.22. FPA Control/Status Register                                 | 6-36 |

| 8.1(a). CPU Latency to Start of Read (Full Frequency Mode)        | 8-4  |

| 8.1(b). CPU Latency to start of Read (Half Frequency Mode)        | 8-5  |

| 8.2. Start of Bus Read Operation                                  | 8-7  |

| 8.3. Data Sampling on R3051/52                                    | 8-8  |

| 8.4. Read Cycle Termination                                       | 8-9  |

| 8.5. Use of DataEn as Output Enable Control                       | 8-10 |

| 8.6(a). Internal Processor States on Burst Read (Full Freq. Mode) | 8-11 |

| 8.6(b). Internal Processor States on Burst Read (Half Freq. Mode) | 8-11 |

|                                                                   |      |

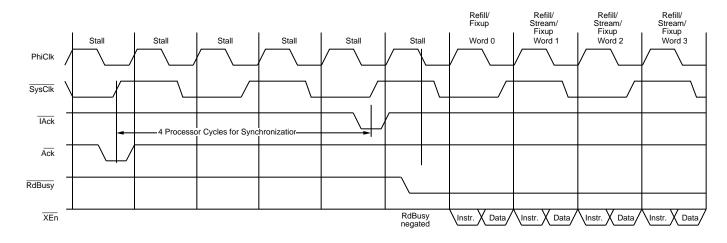

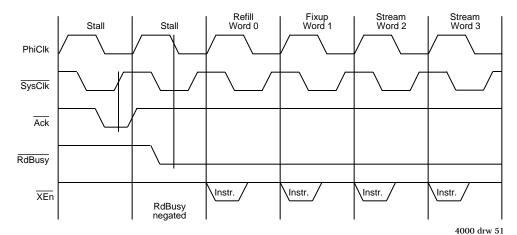

|    | 8.7. Instruction Streaming Example (Full Freq. Mode)             | 8-12  |

|----|------------------------------------------------------------------|-------|

|    | 8.8. Single Word Read Without Bus Wait Cycles                    | 8-13  |

|    | 8.9. Single Word Read With Bus Wait Cycles                       | 8-14  |

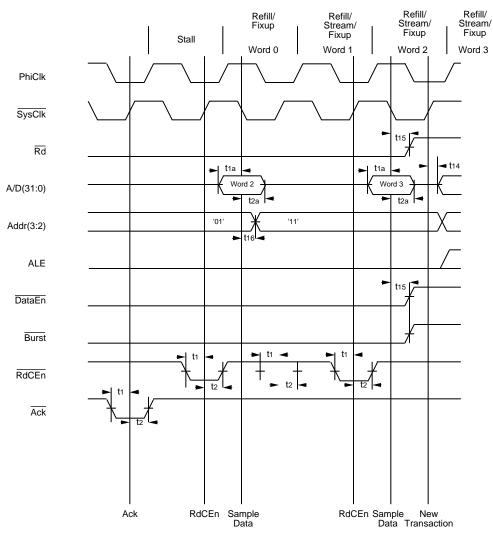

|    | 8.10. Burst Read With No Wait Cycle                              | 8-15  |

|    | 8.11(a). Start of Burst Read with Initial Wait Cycles            | 8-16  |

|    | 8.11(b). End of Burst Read                                       | 8-17  |

|    | 8.12(a). First Two Words of "Throttled" Quad Word Read           | 8-18  |

|    | 8.12(b). End of Throttled Quad Word Read                         | 8-19  |

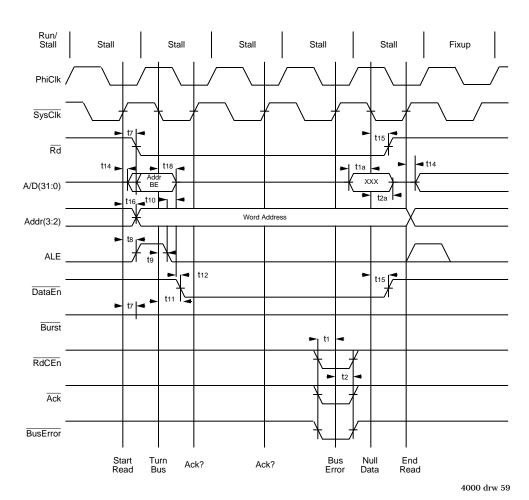

|    | 8.13. Single Word Read Terminated by Bus Error                   | 8-20  |

|    | 8.14. Block Read Terminated by Bus Error                         | 8-21  |

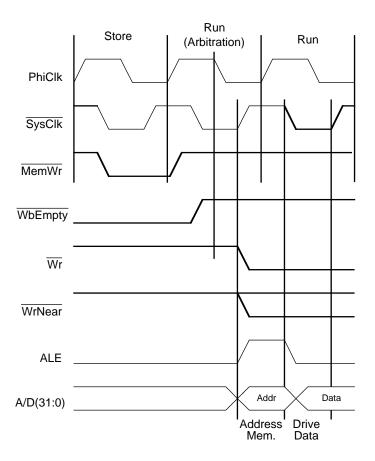

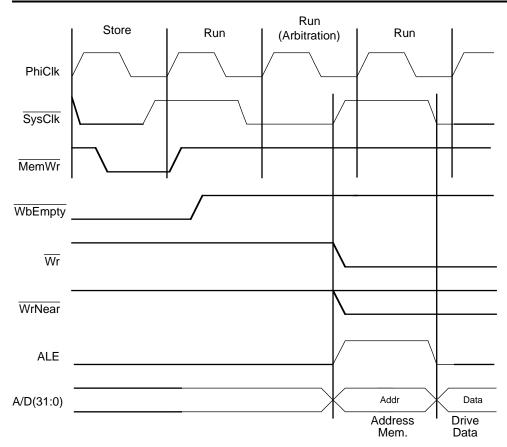

|    | 9.1(a). Start of Write Operation—BIU Arbitration                 | 9-5   |

|    | 9.1(b). Start of Write Arbitration—Half-frequency Mode           | 9-6   |

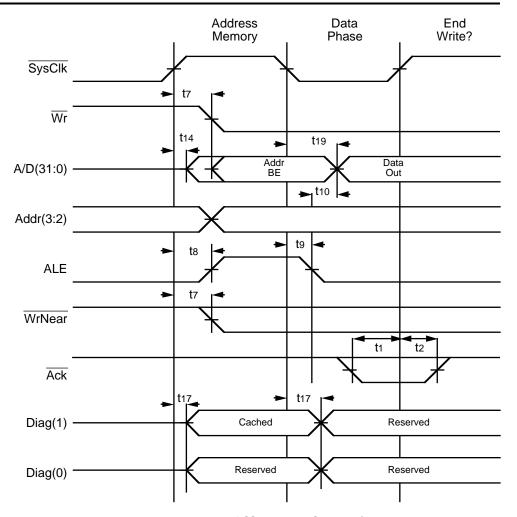

|    | 9.2. Memory addressing and Start of Write                        | 9-7   |

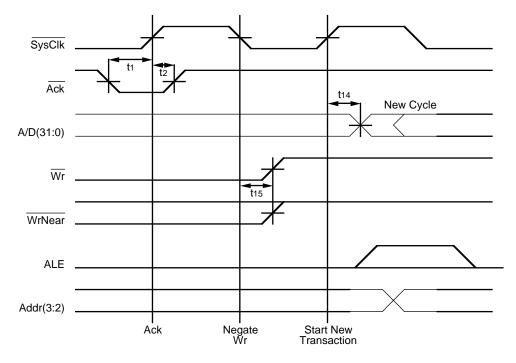

|    | 9.3. End of Write                                                | 9-8   |

|    | 9.4. Write Buffer Full Operation                                 | 9-9   |

|    | 9.5. Bus Write with No Wait Cycles                               | 9-10  |

|    | 9.6. Write with Bus Wait Cycles                                  | 9-11  |

|    | 9.7. Bus Error on Write                                          | 9-12  |

|    | 10.1. Bus Grant and Start off DMA Transaction                    | 10-3  |

|    | 10.2. Regaining Bus Mastership                                   | 10-4  |

|    | 10.3. Requesting Coherent DMA                                    | 10-8  |

|    | 10.4. Capturing Write Target Address During Coherent DMA         | 10-9  |

|    | 10.5. Invalidating Current Data Cache Word and Incrementing      |       |

|    | Invalidate Address                                               | 10-10 |

|    | 10.6. Terminating a Coherent Write Sequence                      | 10-11 |

|    | 10.7. Terminating Coherent DMA                                   | 10-12 |

|    | 11.1. Cold Start                                                 | 11-4  |

|    | 11.2. Warm Reset                                                 | 11-4  |

|    | 11.3. R3081 Internal Mode Vector Logic                           | 11-5  |

|    | 11.4. Mode Vector Timing                                         | 11-5  |

|    | 11.5. Reset Timing                                               | 11-6  |

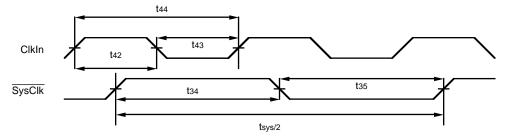

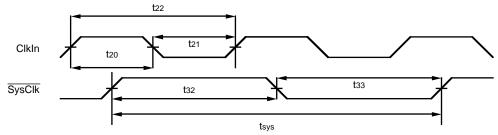

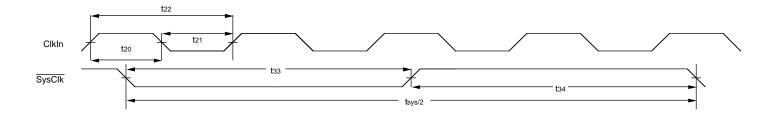

|    | 11.6(a). R3081 Family Clocking (1x ClkIn, Full Frequency)        | 11-6  |

|    | 11.6(b). R3081 Family Clocking (1x ClkIn, Half Frequency)        | 11-6  |

|    | 11.6(c). R3081 Family Clocking (2x ClkIn, Full Frequency)        | 11-7  |

|    | 11.6(d). R3081 Family Clocking (2x ClkIn, Half Frequency)        | 11-7  |

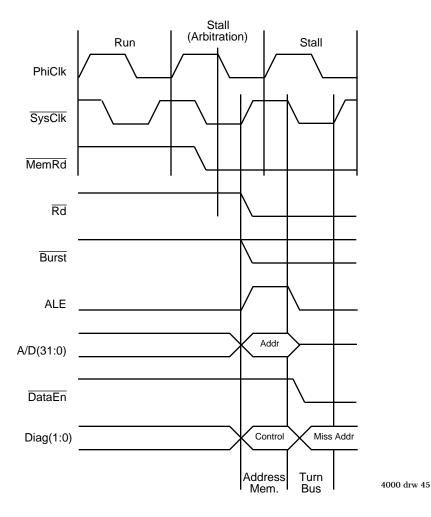

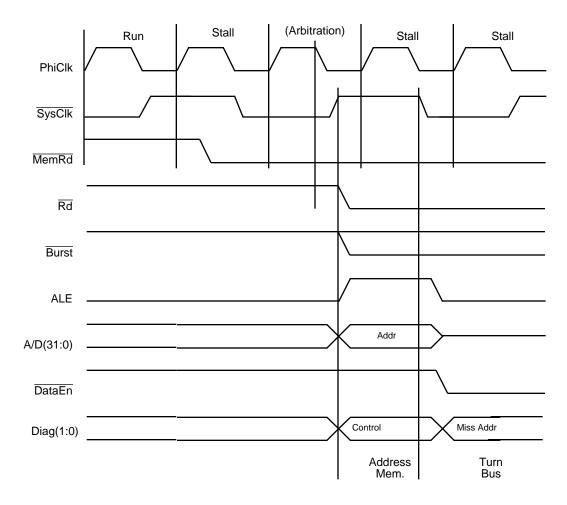

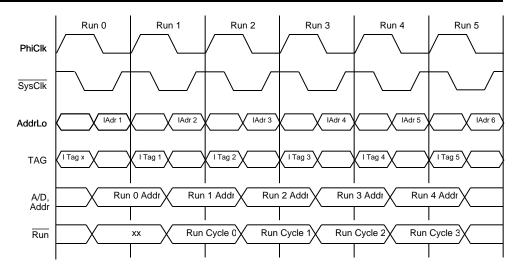

|    | 12.1(a). R3051 Debug Mode Instruction Address Display            | 12-3  |

|    | 12.1(b). R3051 Debug Mode Instruction Address Display            | 12-3  |

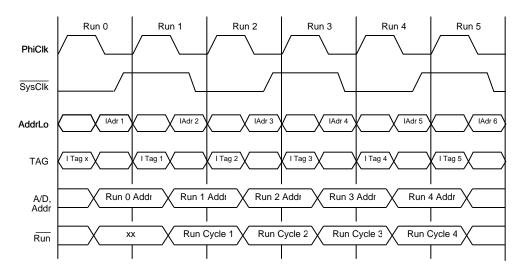

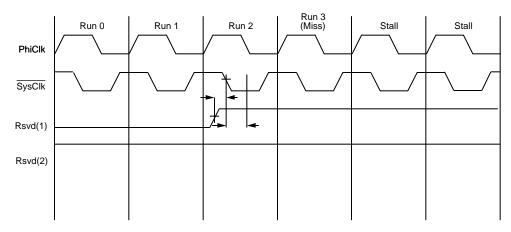

|    | 12.1(c). Instruction Cache Miss Sequence in Address Display Mode |       |

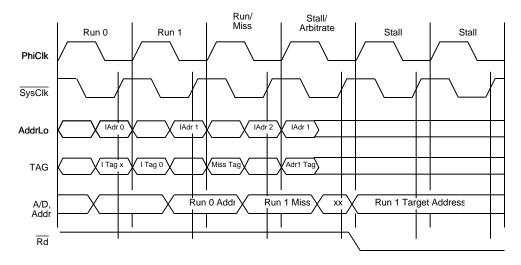

|    | 12.3. Forcing an Instruction Cache Miss in Debug Mode            | 12-4  |

|    |                                                                  |       |

| Li | sting of Tables                                                  |       |

|    | 1.1. Pin-, Socket-, and Software-Compatible R3051 Family         | 1-2   |

|    | 2.1. Instruction Set Mnemonics                                   | 2-4   |

|    | 2.2. CPO Registers                                               | 2-6   |

|    | 2.3. Byte Addressing in Load/Store Operations                    | 2-11  |

|    | 2.4. Load and Store Instructions                                 | 2-12  |

|    | 2.5(a). ALU Immediate Operations                                 | 2-13  |

|    | 2.5(b). Three Operand Register-Type Operations                   | 2-14  |

|    | 2.5(c). Shift Operations                                         | 2-14  |

|    | 2.5(d). Multiply and Divide Operations                           | 2-15  |

|    | 2.6(a). Jump Instructions                                        | 2-16  |

|    | 2.6(b). Branch Instructions                                      | 2-16  |

|    | 2.7. Special Instructions                                        | 2-17  |

|    | 2.8. Co-Processor Operations                                     | 2-17  |

|    | 2.9. System Control Co-Processor (CPO) Operations                | 2-18  |

|    | 2.10. OpCode Encoding                                            | 2-19  |

|    | 3.1. Floating Point General Registers                            | 3-3   |

|    | 3.2. Rounding Mode Bit Decoding                                  | 3-5   |

|    |                                                                  |       |

| 3.3. Equations for Calculating Values in Floating-Point Format   | 3-6  |

|------------------------------------------------------------------|------|

| 3.4. Floating Point Parameter Values                             | 3-7  |

| 3.5. Floating Point Instruction Summary                          | 3-9  |

| 3.6. Floating Point Load, Store, and Move Instruction Summary    | 3-11 |

| 3.7. Floating Point Computational Instruction Summary            | 3-12 |

| 3.8. Relationship Mnemonic Definitions                           | 3-13 |

| 3.9. Floating Point Relational Operators                         | 3-14 |

| 3.10. Branch on FPA Condition Instructions                       | 3-14 |

| 3.11. FPA OpCode Encoding                                        | 3-15 |

| 5.1. Virtual and Physical Address Relationships in Base Versions | 5-4  |

| 5.2. TLB Instructions                                            | 5-9  |

| 6.1. R3051 Family Exceptions                                     | 6-2  |

| 6.2. Co-Processor O Register addressing                          | 6-4  |

| 6.3. Cause Register Exception Codes                              | 6-5  |

| 6.4. Encoding of FPInt Field of Config Register                  | 6-9  |

| 6.5. Exception Vectors When BEV = 0                              | 6-10 |

| 6.6. Exception Vectors When BEV = 1                              | 6-10 |

| 6.7. Exception Priority                                          | 6-12 |

| 6.8. FPA Exception Causing Codes                                 | 6-37 |

| 6.9. FPA Exception Causing Conditions                            | 6-38 |

| 11.1. R3081 Mode Selectable Features                             | 11-1 |

| A.1. CPO Registers in the R3051 Family                           | A-1  |

| A.2. Pin Considerations Among R3051 Family Members               | A-3  |

| A.3. Reset Mode Vectors of R3041, R3051/52, and R3081            | A-4  |

| A.4. Rsvd Pins of R3041, 3051/52, and R3081                      | A-5  |

| A.5. Summary of Hardware Design Considerations                   | A-7  |

# R3071/R3081 OVERVIEW

#### INTRODUCTION

The IDT R30xx family is a series of high-performance 32-bit microprocessors featuring a high-level of integration, and targeted to high-performance but cost sensitive processing applications. The R30xx family is designed to bring the high-performance inherent in the MIPS RISC architecture into low-cost, simplified, power sensitive applications.

Thus, functional units have been integrated onto the CPU core in order to reduce the total system cost, rather than to increase the inherent performance of the integer engine. Nevertheless, the R30xx family is able to offer over 40 MIPS of integer performance at 50 MHz without requiring external SRAM or caches.

The R3071 and R3081 extend the capabilities of the R30xx family by integrating additional resources into the same pin-out. The R3071 and R3081 thus extend the range of applications addressed by the R30xx family, and allow designers to implement a single, base system and software set capable of accepting a wide variety of CPUs, according to the price performance goals of the end system.

This manual describes the 79R3071, 79R3071E, 79R3081 and 79R3081E devices; the 79R3041, and 79R3051/52 (and their "E" variants), are described in separate manuals. Appendix A describes design considerations for those wishing to interchange various R3051 family CPUs in a given design.

#### **FEATURES**

- Instruction set compatible with IDT 79R3000A RISC CPU

- · High level of integration minimizes system cost

- Over 40 MIPS at 50 MHz

- · Low cost 84-pin packaging

- · Large on-chip instruction and data caches with user configurability

- · Parity protection over on-chip caches

- R3081 includes on-chip R3010A compatible Floating Point Accelerator

- Flexible bus interface allows simple, low cost designs.

- Optional half-frequency bus mode allows high-execution rate with low cost, low-speed system interface

- 1X clock input with 45-55% duty cycle tolerance

- R3081 offers optional R3051 compatible 2x clock input for 20-40MHz

- R3081 features 20 through 50 MHz operation

- R3071 features 33 through 50MHz Operation

- Superset Pin- and Software- compatible with R3041, R3051, R3052

- Multiplexed bus interface with support for low cost, low speed memory systems with a high-speed CPU

- · On-chip 4-deep write buffer eliminates memory write stalls

- On-chip 4-deep read buffer supports burst or simple block reads

- · On-chip DMA arbiter

- Hardware-based Cache Coherency Support

- Dynamic power management capability through the ability to reduce operation frequency under software control.

#### NOTES:

At 50MHz, only 1/2 frequency bus is available

For the R3071 at all frequencies, and for the R3081 at 50 MHz, only 1x input clock mode is available

#### **DEVICE OVERVIEW**

The R30xx family offers a wide range of functionality in a pin-compatible interface. The R30xx family allows the system designer to implement a single base system, and utilize interface-compatible processors of various complexity to achieve the price-performance goals of the particular end system.

Differences among the various family members pertain to the on-chip resources of the processor, as illustrated in Table 1.1.

| Device | Instr.<br>Name | Data<br>Cache | Freq.<br>Cache | MMU<br>(MHz) | Floating<br>Option | Bus<br>Point Options                   |

|--------|----------------|---------------|----------------|--------------|--------------------|----------------------------------------|

| D0041  |                |               |                | ` ′          | -                  | •                                      |

| R3041  | 2kB            | 512B          | 16-25          | No           | Software           | 8-, 16-, and 32-bit port width support |

|        |                |               |                |              | Emulation          | Programmable timing support            |

| R3051  | 4kB            | 2kB           | 20-40          | "E"          | Software           | 32-bit Mux'ed Address/Data             |

|        |                |               |                | Version      | Emulation          |                                        |

| R3052  | 8kB            | 2kB           | 20-40          | "E"          | Software           | 32-bit Mux'ed Address/Data             |

|        |                |               |                | Version      | Emulation          |                                        |

| R3071  | 16kB           | 4kB           | 33-50          | "E"          | Software           | 1/2 frequency bus option               |

|        | 0r 8kB         | or 8kB        |                | Version      | Emulation          |                                        |

| R3081  | 16kB           | 4kB           | 20-50          | "E"          | On-chip            | 1/2 frequency bus option               |

|        | 0r 8kB         | or 8kB        |                | Version      | Hardware           |                                        |

Table 1.1. Pin-, Socket-, and Software- Compatible R3051 Family

#### Current family members include:

- The R3041, which incorporates 2kB of instruction cache, 512B of data cache, and a flexible system interface suited to low cost memory systems. The R3041 does not feature an on-chip MMU, but is fully address map compatible with the base versions of the R3051 family.

- The R3052E, which incorporates an 8kB instruction cache, a 2kB data cache, and full function memory management unit (MMU) including 64entry fully associative Translation Lookaside Buffer (TLB).

- The R3052, which also incorporates an 8kB instruction cache and 2kB data cache, but does not include the TLB, and instead uses a simpler virtual to physical address mapping.

- The R3051E, which incorporates 4kB of instruction cache and 2kB of data cache, along with the full function MMU/TLB of the R3000A.

- The R3051, which incorporates 4kB of instruction cache and 2kB of data cache, but omits the TLB, and instead uses a simpler virtual to physical address mapping.

- The R3071E, which incorporates a 16kB instruction cache, a 4kB data cache, and full function memory management unit (MMU) including 64-entry fully associative Translation Lookaside Buffer (TLB). The cache on the R3081E is user configurable to 8kB I-Cache and 8kB D-Cache.

- The R3071, which incorporates a 16kB instruction cache, a 4kB data cache, but uses the simpler memory mapping of the R3051/52, and thus omits the TLB. The cache on the R3081 is user configurable to 8kB I-Cache and 8kB D-Cache.

- The R3081E, which incorporates a 16kB instruction cache, a 4kB data cache, and full function memory management unit (MMU) including 64-entry fully associative Translation Lookaside Buffer (TLB). The cache on the R3081E is user configurable to 8kB I- Cache and 8kB D-Cache. The R3081E also includes an on-chip floating-point accelerator.

- The R3081, which incorporates a 16kB instruction cache, a 4kB data cache, but uses the simpler memory mapping of the R3051/52, and thus omits the TLB. The cache on the R3081 is user configurable to 8kB I-Cache and 8kB D-Cache. The R3081 also includes an on-chip floatingpoint accelerator.

Figure 1.1. Block Diagram

Figure 1.1 shows a block level representation of the functional units within the R3081E. The R3081E could be viewed as the embodiment of a discrete solution built around the R3000A and R3010A. However, by integrating this functionality on a single chip, dramatic cost and power reductions are achieved.

Non-E versions differ from the block diagram shown in that they omit the TLB structure. R3071 devices differ from the block diagram in that they omit the floating-point accelerator unit.

An overview of these blocks is presented here, with detailed information on each block found in subsequent chapters.

#### **CPU Core**

The CPU core is a full 32-bit RISC integer execution engine, capable of sustaining close to single cycle execution rate. The CPU core contains a five stage pipeline, and 32 orthogonal 32-bit registers. The R3071 and R3081 use the same basic integer execution core as the entire R30xx family, which is the R3000A implementation of the MIPS instruction set. Thus, the R3071 and R3081 families are binary compatible with the R3051, R3052, R3000A, R3001, and R3500 CPUs. In addition, the R4000 family (including the R4600 Orion family) represents an upwardly software compatible migration path to still higher levels of performance.

#### **System Control Co-Processor**

The R3071 and R3081 families also integrate on-chip the System Control Co-processor, CPO. CPO manages both the exception handling capability of the CPU, as well as the virtual to physical address mapping. These topics are discussed in subsequent chapters.

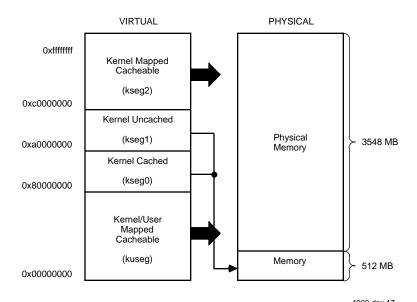

As with the R3051 and R3052, the R3071 and R3081 families offer two versions of memory management and virtual to physical address mapping: the extended architecture versions, the R3051E, R3052E, R3071E, and R3081E, incorporate the same MMU as the R3000A and R3001. These versions contain a fully associative 64-entry TLB which maps 4kB virtual pages into the physical address space. The virtual to physical mapping thus includes kernel segments which are hard-mapped to physical addresses, and kernel and user segments which are mapped page by page by the TLB into anywhere in the 4GB physical address space. In this TLB, 8 pages can be "locked" by the kernel to insure deterministic response in real-time applications.

R30xx family base versions (the R3041, R3051, R3052, R3071, and R3081) remove the TLB and institute a fixed address mapping for the various segments of the virtual address space. These devices still support distinct kernel and user mode operation, but do not require page management software, leading to a simpler software model.

#### **Floating Point Co-Processor**

The R3081 devices also integrate an R3010A compatible floating point accelerator. The R3010A is a high performance floating point co-processor (co-processor 1 to the CPU) providing separate add, multiply, and divide functional units for single and double precision floating point arithmetic. The floating point accelerator features low latency operations, and autonomous functional units which allow differing types of floating point operations to function concurrently with integer operations. The R3010A appears to the software programmer as a simple extension of the integer execution unit, with 16 dedicated 64-bit floating point registers (software references these as 32 32-bit registers when performing loads or stores).

The primary difference between the R3071 family and the R3081 family is that the R3081 devices include the FPA, while the R3071 devices do not.

#### Clock Generator Unit

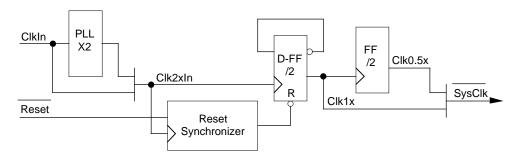

The R3071 and R3081 family CPUs are driven from a single input clock.

For the R3081, this input clock can either be at twice the execution rate (2x clock mode, provided for R3051 input clocking compatibility) or exactly at the execution rate (1x clock mode). For the R3071, only the 1x clock mode is available.

On-chip, the clock generator unit is responsible for managing the interaction of the CPU core, caches, and bus interface. The R3071 and R3081 include an on-chip clock doubler to provide higher frequency signals to the internal execution core.

#### **Instruction Cache**

The R3071 and R3081 implement a 16kB Instruction Cache. The system designer may choose to repartition the on-chip caches, so that the instruction cache is reduced to 8kB but the data cache is increased to 8kB. The instruction cache is organized with a line size of 16 bytes (four 32-bit entries). This large cache achieves hit rates in excess of 98% in most applications, and substantially contributes to the performance inherent in the R3071/R3081. The cache is implemented as a direct mapped cache, and is capable of caching instructions from anywhere within the 4GB physical address space. The cache is implemented using physical addresses and physical tags (rather than virtual addresses or tags), and thus does not require flushing on context switch.

The on-chip instruction cache is parity protected over both the instruction word and tag fields. The read buffer will generate proper parity into the cache during cache refills; on cache references, the parity will be checked. If a parity error is detected, a cache miss will be processed.

#### **Data Cache**

The R3071/R3081 incorporate an on-chip data cache of 4kB, organized as a line size of 4 bytes (one word). The R3071 and R3081 allow the system software to reconfigure the on-chip cache from the default 16kB I-Cache/4kB D-Cache to 8kB of Instruction and 8kB of Data caches.

The relatively large data cache achieves hit rates in excess of 95% in most applications, and contributes substantially to the performance inherent in the R3071/R3081. As with the instruction cache, the data cache is implemented as a direct mapped physical address cache. The cache is capable of mapping any word within the 4GB physical address space.

The data cache is implemented as a write through cache, to insure that main memory is always consistent with the internal cache. In order to minimize processor stalls due to data write operations, the bus interface unit incorporates a 4-deep write buffer which captures address and data at the processor execution rate, allowing it to be retired to main memory at a much slower rate without impacting system performance. Further, support has been provided to allow hardware based data cache coherency in a multi-master environment, such as one utilizing DMA from I/O to memory.

The on-chip data cache is parity protected over both the data and tag fields. The read buffer will generate proper parity into the cache during cache refills; on cache references, the parity will be checked. If a parity error is detected, a cache miss will be processed.

#### **Bus Interface Unit**

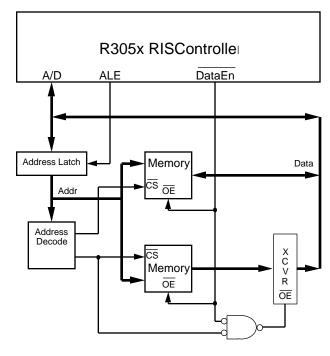

The R3071/R3081 uses the large internal caches to provide the majority of the bandwidth requirements of the execution engine, and thus can utilize a simple bus interface connected to slower memory devices.

The R30xx family bus interface utilizes a 32-bit address and data bus multiplexed onto a single set of pins. The bus interface unit also provides an ALE (Address Latch Enable) output signal to de-multiplex the A/D bus, and simple handshake signals to process CPU read and write requests. In addition to the read and write interface, the R30xx family incorporates a DMA arbiter, to allow an external master to control the external bus. The R3071 and R3081 can be used in a multi-master system using hardware-based cache coherency.

The R3071/R3081 incorporate a 4-deep write buffer to decouple the speed of the execution engine from the speed of the memory system. The write buffers capture and FIFO processor address and data information in store operations, and present it to the bus interface as write transactions at the rate the memory system can accommodate.

The R3071/R3081 read interface performs both single word reads and quad word reads. Single word reads work with a simple handshake, and quad word reads can either utilize the simple handshake (in lower performance, simple systems) or utilize a tighter timing mode when the memory system can burst data at the processor clock rate. Thus, the system designer can choose to utilize page or nibble mode DRAMs (and possibly use interleaving, if desired, in high-performance systems), or use simpler techniques to reduce complexity. During cache refills, the bus interface unit generates parity over the incoming data values, and places the parity in the on-chip caches.

In order to accommodate slower quad word reads, the R3071/R3081 incorporate a 4-deep read buffer FIFO, so that the external interface can queue up data within the processor before releasing it to perform a burst fill of the internal caches.

The R3071 and R3081 are R3051 superset compatible in their bus interface. Specifically, the R3071/R3081 have additional support to simplify the design of very high frequency systems. This support includes the ability to run the bus interface at one-half the processor execution rate, as well as the ability to slow the transitions between reads and writes to provide extra buffer disable time for the memory interface.

#### **SYSTEM USAGE**

The IDT R30xx family bus interface has been specifically designed to allow a wide variety of memory systems. Low cost systems can use slow speed memories and simple controllers, while other designers may choose to incorporate higher frequencies, faster memories, and techniques such as DMA to achieve maximum performance. The R3071 and R3081 include specific support for high perfromance systems, including the ability to perform hardware based cache coherency in multi-master systems.

A typical system implementation using off-the-shelf logic devices contains simple transparent latches to de-multiplex the R30xx address and data busses from the A/D bus; the data path between the memory system elements and the R30xx family A/D bus is managed by simple octal transceivers; a small set of simple PALs is used to control the various data path elements, and to control the handshake between the memory devices and the R30xx.

Depending on the cost vs. performance tradeoffs appropriate to a given application, the system design engineer could include true burst support from the DRAM to provide for high-performance cache miss processing, or utilize a simpler, lower performance memory system to reduce cost and simplify the design. Similarly, the system designer could choose to implement techniques such as DMA to further improve system performance.

#### DEVELOPMENT SUPPORT

The IDT R30xx family is supported by a rich set of development tools, ranging from system simulation tools through PROM monitor and debug support, applications software and utility libraries, logic analysis tools, sub-system modules, and shrink wrap operating systems. IDT's development support program, called "AdvantageIDT", insures the availability of all the tools required to rapidly bring an R30xx-based system rapidly to market.

The R3071 and R3081 are pin and software compatible with many other family members, allowing the system designer to use a single toolchain and methodology for multiple system development efforts.

Figure 1.2 is an overview of the system development process typically used when developing R30xx family applications. The R30xx family is supported in all phases of project development. These tools allow timely, parallel development of hardware and software for R30xx family based applications, and include tools such as:

- Optimizing compilers from MIPS, the acknowledged leader in optimizing compiler technology. The compilers are available in both native and cross environments.

- Cross development tools, available in a variety of development environments and from a number of vendors.

- The high-performance IDT floating point library software, including transcendental functions and IEEE compliant exception handlers.

- IDT Evaluation systems, which includes RAM, EPROM, I/O, and the IDT PROM Monitor.

- IDT Adobe Reference Printer systems, which directly drive low-cost print engines, and run PostScript $^{TM}$  software from Adobe.

- IDT/sim, which implements a full prom monitor (diagnostics, remote debug support, peek/poke, etc.).

- IDT/kit, which implements a run-time support package for R3051 family systems.

- In-circuit Emulator equipment.

Figure 1.2. Development Support

#### **PERFORMANCE OVERVIEW**

The R3071/R3081 achieves a very high-level of performance. This performance is based on:

- An efficient execution engine. The CPU performs ALU operations and store operations in single cycle, and has an effective load time of 1.3 cycles, and branch execution rate of 1.5 cycles (based on the ability of the compilers to avoid software interlocks). Thus, the execution engine achieves over 40 MIPS performance when operating out of cache.

- A full featured floating point accelerator/co-processor. The R3081 incorporates the R3010A floating point accelerator on-chip, with independent ALUs for floating point add, multiply, and divide. The floating point unit is fully hardware interlocked, and features overlapped operation and precise exceptions. The FPA allows floating point adds, multiplies, and divides to occur concurrently with each other, as well as concurrently with integer operations.

- Large on-chip caches. The R3071/R3081 contain caches which are substantially larger than those on the majority of today's microprocessors. These large caches minimize the number of bus transactions required, and allow the R30xx family to achieve actual sustained performance very close to its peak execution rate. The R3071/R3081 double the cache available on the R3052, making it a suitable engine for many high-performance applications, including color printing systems and internetworking devices.

- Autonomous multiply and divide operations. The R30xx family features an on-chip integer multiplier/divide unit which is separate from the main ALU. This allows the CPU to perform multiply or divide operations in parallel with other integer operations, using a single multiply or divide instruction rather than "step" operations.

- Integrated write buffer. The R3071/R3081 feature a four deep write buffer, which captures store target addresses and data at the processor execution rate and retires it to main memory at the slower main memory access rate. Use of on-chip write buffers eliminates the need for the processor to stall when performing store operations.

- Burst read support. The R3071/R3081 enable the system designer to utilize page mode or nibble mode RAMs when performing read operations to minimize the main memory read penalty and increase the effective cache hit rates.

The performance differences amongst the various family members depend on the application software and the design of the memory system. Since the R3041, R3051, R3052, R3071, and R3081 are all pin and software compatible, the system designer has maximum freedom in trading between performance and cost. A system can be designed, and later the appropriate CPU inserted into the board, depending on the desired system performance.

# FAMILY INSTRUCTION SET ARCHITECTURE

#### INTRODUCTION

The IDT R30xx family contains the same basic execution core as the IDT/MIPS R3000A. In addition to being able to run software written for either of this processor family, this enables the R30xx family to achieve dramatic levels of performance, based on the efficiency of the execution engine. The R3071 and R3081 include the same integer execution unit as all members of the R30xx family, and thus is fully binary compatible with applications for that processor. The floating point accelerator included in the R3081 acts as an extension to the CPU, and is described in chapter 3.

This chapter gives an overview of the MIPS architecture implemented in the R30xx family, and discusses the programmers' model for this device. Further detail is available in the book "R30xx Family Software Reference Manual", available from IDT.

#### R30XX FAMILY PROCESSOR FEATURES OVERVIEW

The R30xx family has many of the same attributes of the IDT R3000A, at a higher level of integration geared to lower system cost. These features include:

- Full 32-bit Operation. The R30xx family contains thirty-two 32-bit integer registers, and all instructions and addresses are 32 bits.

- **Efficient Pipelining.** The CPU utilizes a 5-stage pipeline design to achieve an execution rate approaching one instruction per cycle. Pipeline stalls, hazards, and exceptional events are handled precisely and efficiently.

- Large On-Chip Instruction and Data Caches. The R30xx family utilizes large on-chip caches to provide high-bandwidth to the execution engine. The large size of the caches insures high hit rates, minimizing stalls due to cache miss processing and dramatically contributing to overall performance. Both the instruction and data cache can be accessed during a single CPU cycle.

- On-chip Memory Management. The IDT Extended Architecture versions of the R305xx family (the R3051E, R3052E, R3071E, and R3081E) utilize the same memory management scheme as the R3000A, providing a 64-entry fully-associative TLB to provide fast virtual to physical address translation of the 4GB address space. The base versions of the family (the R3041, R3051, R3052, R3071, and R3081) do not utilize the TLB, but perform fixed segment-based mapping of the virtual space to physical addresses.

#### CPU REGISTERS OVERVIEW

The IDT R30xx family CPU engine provides 32 general purpose 32-bit registers, a 32-bit Program Counter, and two dedicated 32-bit registers which hold the result of an integer multiply or divide operation. The CPU registers, illustrated in Figure 2.1, are discussed later in this chapter.

Figure 2.1. CPU Registers

Note that the MIPS architecture does not use a traditional Program Status Word (PSW) register. The functions normally provided by such a register are instead provided through the use of "Set" instructions and conditional branches. By avoiding the use of traditional condition codes, the architecture can be more finely pipelined. This, coupled with the fine granularity of the instruction set, allows the compilers to achieve dramatically higher levels of optimizations than for traditional architectures.

Overflow and exceptional conditions are then handled through the use of the on-chip *Status* and *Cause* registers, which reside on-chip as part of the System Control Co-Processor (Co-Processor 0). These registers contain information about the run-time state of the machine, and any exceptional conditions it has encountered.

#### INSTRUCTION SET OVERVIEW

All instructions are 32-bits long, and there are only three basic instruction formats. This approach dramatically simplifies instruction decoding, permitting higher frequency operation. More complicated (but less frequently used) operations and addressing modes are synthesized by the assembler, using sequences of the basic instruction set. This approach enables object code optimizations at a finer level of resolution than achievable in micro-coded CPU architectures.

Figure 2.2 shows the instruction set encoding used by the MIPS architecture. This approach simplifies instruction decoding in the CPU.

The instruction set can be divided into the following basic groups:

- Load/Store instructions move data between memory and the general registers. They are all encoded as "I-Type" instructions, and the only addressing mode implemented is base register plus signed, immediate offset. This directly enables the use of three distinct addressing modes: register plus offset; register direct; and immediate.

- Computational instructions perform arithmetic, logical, and shift operations on values in registers. They are encoded as either "R-Type" instructions, when both source operands as well as the result are general registers, and "I-Type", when one of the source operands is a 16-bit immediate value. Computational instructions use a three address format, so that operations don't needlessly interfere with the contents of source registers.

- Jump and Branch instructions change the control flow of a program. A

Jump instruction can be encoded as a "J-Type" instruction, in which case

| where:    |                                                          |

|-----------|----------------------------------------------------------|

| ор        | is a 6-bit operation code                                |

| rs        | is a five bit source register specifier                  |

| rt        | is a 5-bit target register or branch condition           |

| immediate | is a 16-bit immediate, or branch or address displacement |

| target    | is a 26-bit jump target address                          |

| rd        | is a 5-bit destination register specifier                |

| shamt     | is a 5-bit shift amount                                  |

| funct     | is a 6-bit function field                                |

Figure 2.2. Instruction Encoding

4000 drw 02

the Jump target address is a paged absolute address formed by combining the 26-bit immediate value with four bits of the Program Counter. This form is used for subroutine calls.

Alternately, Jumps can be encoded using the "R-Type" format, in which case the target address is a 32-bit value contained in one of the general registers. This form is typically used for returns and dispatches.

Branch operations are encoded as "I-Type" instructions. The target address is formed from a 16-bit displacement relative to the Program Counter.

The Jump and Link instructions save a return address in Register r31. These are typically used as subroutine calls, where the subroutine return address is stored into r31 during the call operation.

Co-Processor instructions perform operations on the co-processor set.

Co-ProcessorLoads and Stores are always encoded as "I-Type" instructions;

co-processor operational instructions have co-processor dependent formats.

In the R30xx family, the System Control Co-Processor (CP0) contains registers which are used in memory management and exception handling. In the R3081, the floating point accelerator also resides on-chip, and operates as Co-Processor 1 (CP1)

Additionally, the R30xx family implements BrCond inputs. Software can use the Branch on Co-Processor Condition instructions to test the state of these external inputs, and thus they may be used like general purpose input ports. In the R3071 and R3081, BrCond(1) is not available externally; in the R3081, it is used internally for the floating-point condition flag, used on floating-point conditional instructions.

Special instructions perform a variety of tasks, including movement of data between special and general registers, system calls, and breakpoint operations. They are always encoded as "R-Type" instructions.

| OP            | Description                                                     | OP         | Description                                         |

|---------------|-----------------------------------------------------------------|------------|-----------------------------------------------------|

|               | Load/Store Instructions                                         |            | Multiply/Divide Instructions                        |

| LB            | Load Byte                                                       | MULT       | Multiply                                            |

| LBU           | Load Byte Unsigned                                              | MULTU      | Multiply Unsigned                                   |

| LH            | Load Halfword                                                   | DIV        | Divide                                              |

| LHU           | Load Halfword Unsigned                                          | DIVU       | Divide Unsigned                                     |

| LW            | Load Word                                                       |            |                                                     |

| LWL           | Load Word Left                                                  | MFHI       | Move From HI                                        |

| LWR           | Load Word Right                                                 | MTHI       | Move To HI                                          |

| SB            | Store Byte                                                      | MFLO       | Move From LO                                        |

| SH            | Store Halfword                                                  | MTLO       | Move To LO                                          |

| SW            | Store Word                                                      |            |                                                     |

| SWL           | Store Word Left                                                 | -          | Jump and Branch Instructions                        |

| SWR           | Store Word Right                                                | J<br>JAL   | Jump                                                |

|               | Anialana ati a Taratana ati ana                                 |            | Jump and Link                                       |

|               | Arithmetic Instructions (ALU Immediate)                         | JR<br>JALR | Jump to Register<br>Jump and Link Register          |

| ADDI          | ,                                                               |            |                                                     |

| ADDI<br>ADDIU | Add Immediate Add Immediate Unsigned                            | BEQ<br>BNE | Branch on Equal                                     |

| SLTI          | Set on Less Than Immediate                                      | BLEZ       | Branch on Not Equal<br>Branch on Less than or Equal |

| SLTIU         | Set on Less Than Immediate Set on Less Than Immediate           | BLEZ       | to Zero                                             |

| SLIIO         | Unsigned                                                        | BGTZ       | Branch on Greater Than Zero                         |

| ANDI          | AND Immediate                                                   | BLTZ       | Branch on Less Than Zero                            |

| ORI           | OR Immediate                                                    | BGEZ       | Branch on Greater Than or                           |

| XORI          | Exclusive OR Immediate                                          | DGLL       | Equal to Zero                                       |

| LUI           | Load Upper Immediate                                            | BLTZAL     | Branch on Less Than Zero and                        |

|               |                                                                 |            | Link                                                |

|               |                                                                 | BGEZAL     | Branch on Greater Than or Equal                     |

|               | Arithmetic Instructions                                         |            | to Zero and Link                                    |

|               | (3-operand, register-type)                                      |            |                                                     |

| ADD           | Add                                                             |            | Special Instructions                                |

| ADDU          | Add Unsigned                                                    | SYSCALL    | System Call                                         |

| SUB           | Subtract                                                        | BREAK      | Break                                               |

| SUBU          | Subtract Unsigned                                               |            |                                                     |

| SLT           | Set on Less Than                                                |            | Coprocessor Instructions                            |

| SLTU          | Set on Less Than Unsigned                                       | LWCz       | Load Word from Coprocessor                          |

| AND           | AND                                                             | SWCz       | Store Word to Coprocessor                           |

| OR            | OR                                                              | MTCz       | Move To Coprocessor                                 |

| XOR           | Exclusive OR                                                    | MFCz       | Move From Coprocessor                               |

| NOR           | NOR                                                             | CTCz       | Move Control To Coprocessor                         |

|               | Clarge Total Carlo                                              | CFCz       | Move Control From Coprocessor                       |

| CII           | Shift Instructions                                              | COPz       | Coprocessor Operation                               |

| SLL           | Shift Left Logical                                              | BCzT       | Branch on Coprocessor z True                        |

| SRL           | Shift Right Logical                                             | BCzF       | Branch on Coprocessor z False                       |

| SRA<br>SLLV   | Shift Right Arithmetic                                          |            | System Control Convessors                           |

|               | Shift Left Logical Variable                                     |            | System Control Coprocessor                          |

| SRLV<br>SRAV  | Shift Right Logical Variable<br>Shift Right Arithmetic Variable | MTC0       | (CP0) Instructions Move To CP0                      |

| SICAV         | Sint Mgnt Arthinetic variable                                   | MFC0       | Move From CP0                                       |

|               |                                                                 | TLBR       | Read indexed TLB entry                              |

|               |                                                                 | TLBWI      | Write indexed TLB entry                             |

|               |                                                                 | TLBWR      | Write Random TLB entry                              |

|               |                                                                 | TLBVIK     | Probe TLB for matching entry                        |

|               |                                                                 | RFE        | Restore From Exception                              |

|               | ļ                                                               |            | 4000 tbl 0                                          |

4000 tbl 01

**Table 2.1. Instruction Set Mnemonics**

Table 2.1 lists the instruction set mnemonics of the R30xx family. More detail on these operations is presented later in this chapter. For further detail, consult "R30xx Software Reference Manual", available from IDT.

#### **PROGRAMMING MODEL**

This section describes the organization of data in the general registers and in memory, and discusses the set of general registers available. A summary description of all of the CPU registers is presented. The Floating Point Registers in the R3081 are discussed in Chapter 3.

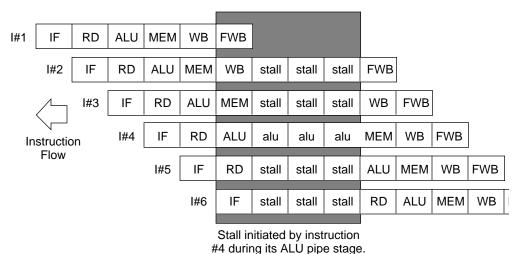

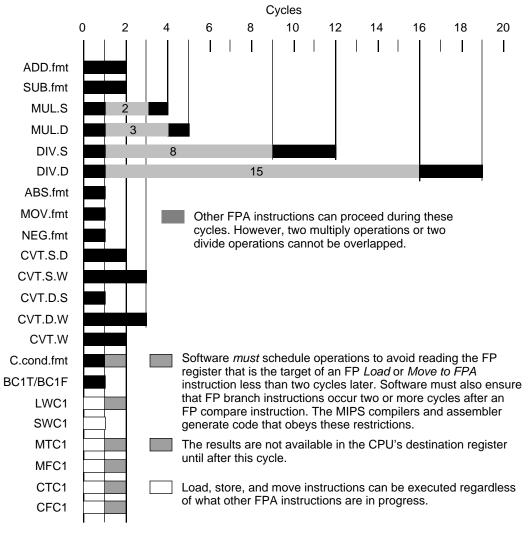

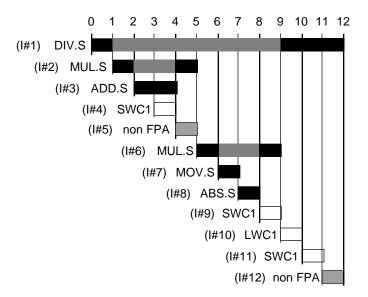

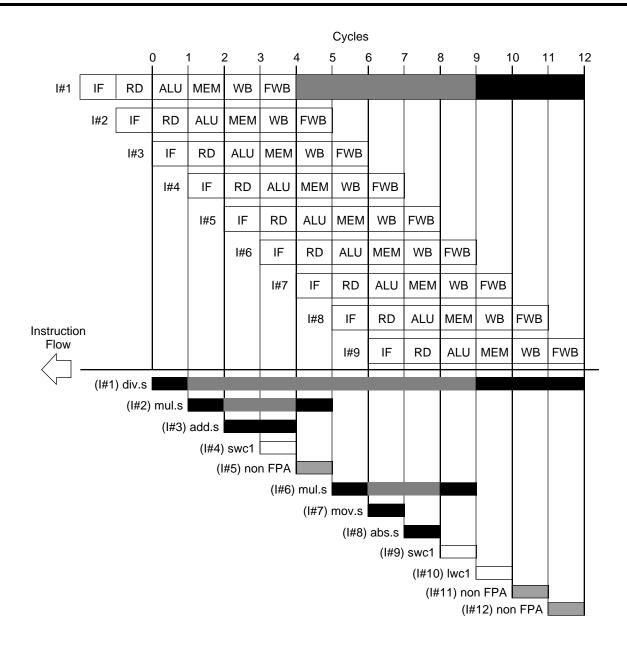

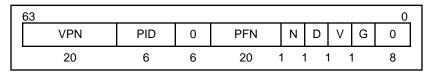

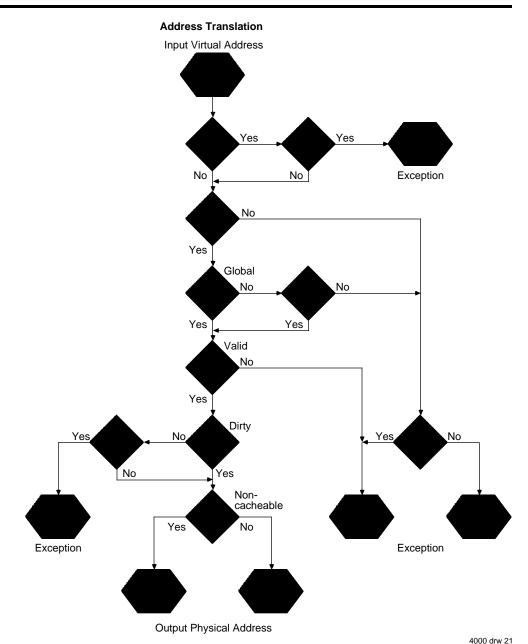

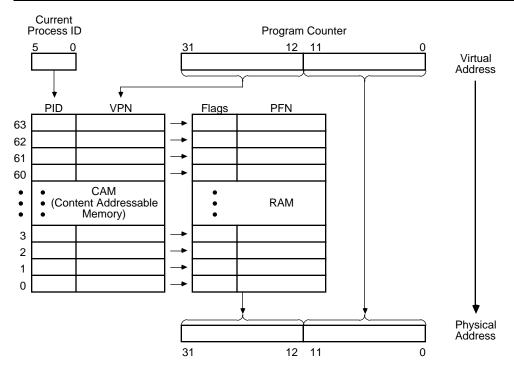

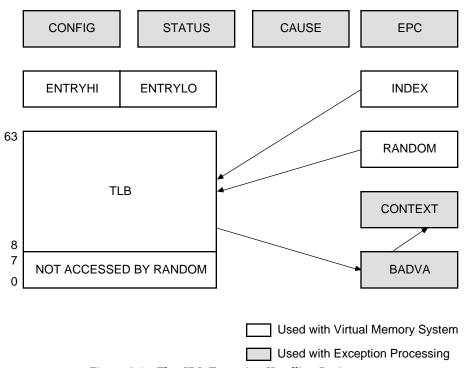

#### **Data Formats and Addressing**