# ML300 Reference Design

**User Guide**

UG057 (v1.1) March 18, 2004

"Xilinx" and the Xilinx logo shown above are registered trademarks of Xilinx, Inc. Any rights not expressly granted herein are reserved. CoolRunner, RocketChips, Rocket IP, Spartan, StateBENCH, StateCAD, Virtex, XACT, XC2064, XC3090, XC4005, and XC5210 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

ACE Controller, ACE Flash, A.K.A. Speed, Alliance Series, AllianceCORE, Bencher, ChipScope, Configurable Logic Cell, CORE Generator, CoreLINX, Dual Block, EZTag, Fast CLK, Fast CONNECT, Fast FLASH, FastMap, Fast Zero Power, Foundation, Gigabit Speeds...and Beyond!, HardWire, HDL Bencher, IRL, J Drive, JBits, LCA, LogiBLOX, Logic Cell, LogicORE, LogicProfessor, MicroBlaze, MicroVia, MultiLINX, NanoBlaze, PicoBlaze, PLUSASM, PowerGuide, PowerMaze, QPro, Real-PCI, RocketIO, SelectIO, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, SMARTswitch, System ACE, Testbench In A Minute, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex-II Pro, Virtex-II EasyPath, Wave Table, WebFITTER, WebPACK, WebPOWERED, XABEL, XACT-Floorplanner, XACT-Performance, XACTstep Advanced, XACTstep Foundry, XAM, XAPP, X-BLOX +, XC designated products, XChecker, XDM, XEPLD, Xilinx Foundation Series, Xilinx XDTV, Xinfo, XSI, XtremeDSP and ZERO+ are trademarks of Xilinx, Inc.

The Programmable Logic Company is a service mark of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx provides any design, code, or information shown or described herein "as is." By providing the design, code, or information as one possible implementation of a feature, application, or standard, Xilinx makes no representation that such implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of any such implementation, including but not limited to any warranties or representations that the implementation is free from claims of infringement, as well as any implied warranties of merchantability or fitness for a particular purpose. Xilinx, Inc. devices and products are protected under U.S. Patents. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

The contents of this manual are owned and copyrighted by Xilinx. Copyright 1994-2004 Xilinx, Inc. All Rights Reserved. Except as stated herein, none of the material may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of any material contained in this manual may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

# ML300 Reference Design UG057 (v1.1) March 18, 2004

The following table shows the revision history for this document..

|          | Version | Revision                |

|----------|---------|-------------------------|

| 01/12/04 | 1.0     | Initial Xilinx release. |

| 03/18/04 | 1.1     | Updates for EDK 6.2i.   |

|          |         |                         |

|          |         |                         |

# Table of Contents

| Preface: About This Guide                                                                                                                                                                                                                                                                                                  |           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Guide Contents                                                                                                                                                                                                                                                                                                             |           |

| Additional Resources                                                                                                                                                                                                                                                                                                       |           |

| Conventions                                                                                                                                                                                                                                                                                                                |           |

| Typographical                                                                                                                                                                                                                                                                                                              |           |

| Online Document                                                                                                                                                                                                                                                                                                            |           |

| Chapter 1: Introduction to ML300 Embedded PPC405 System                                                                                                                                                                                                                                                                    | Reference |

| Introduction                                                                                                                                                                                                                                                                                                               | 15        |

| Requirements                                                                                                                                                                                                                                                                                                               |           |

| V2PDK Users and New EDK Users                                                                                                                                                                                                                                                                                              | 15        |

| CoreConnect                                                                                                                                                                                                                                                                                                                | 16        |

| Reference System Information                                                                                                                                                                                                                                                                                               |           |

| Further Reading                                                                                                                                                                                                                                                                                                            |           |

| Resources for EDK Users (Including New Users)                                                                                                                                                                                                                                                                              |           |

| Documentation Provided by Xilinx                                                                                                                                                                                                                                                                                           | 17        |

| IBM ® CoreConnect™ Documentation                                                                                                                                                                                                                                                                                           |           |

| IBM CoreConnect Bus Architecture Specifications  IBM CoreConnect Toolkit Documentation                                                                                                                                                                                                                                     |           |

| Chapter 2: ML300 Embedded PPC405 Reference Syste                                                                                                                                                                                                                                                                           |           |

|                                                                                                                                                                                                                                                                                                                            |           |

|                                                                                                                                                                                                                                                                                                                            | 10        |

| Hardware                                                                                                                                                                                                                                                                                                                   |           |

| Overview                                                                                                                                                                                                                                                                                                                   | 19        |

| Overview                                                                                                                                                                                                                                                                                                                   |           |

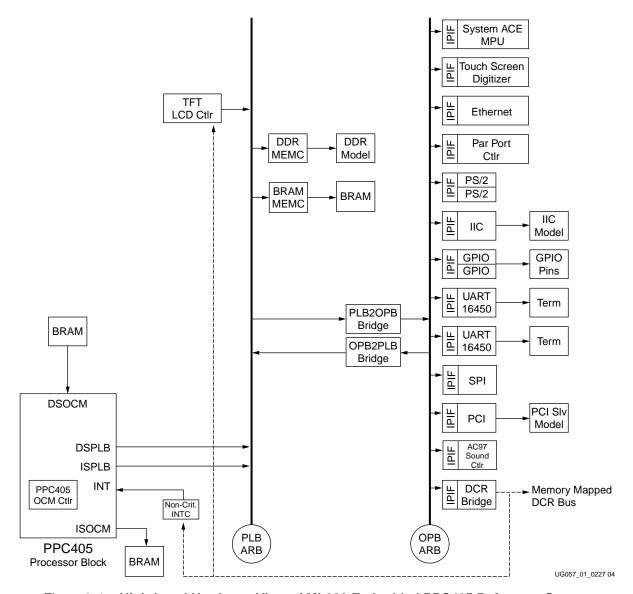

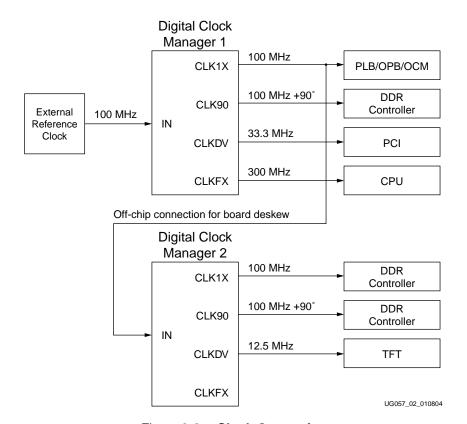

| Overview . Processor Local Bus (PLB) On-Chip Peripheral Bus (OPB) Device Control Registers (DCR) Other Devices Interrupts Clock/Reset Distribution                                                                                                                                                                         |           |

| Overview Processor Local Bus (PLB) On-Chip Peripheral Bus (OPB) Device Control Registers (DCR) Other Devices Interrupts Clock/Reset Distribution CPU Debug via JTAG IP Version and Source  Simulation and Verification                                                                                                     |           |

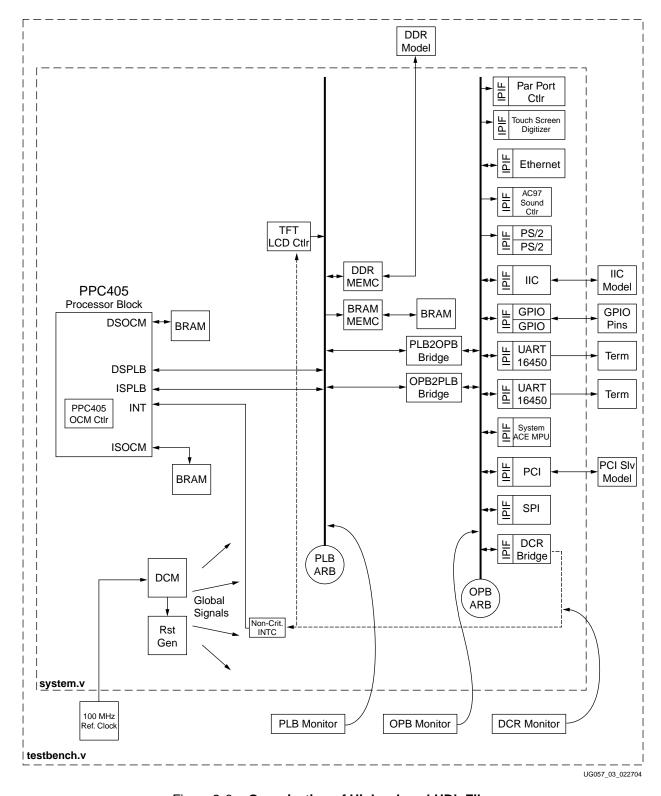

| Overview Processor Local Bus (PLB) On-Chip Peripheral Bus (OPB) Device Control Registers (DCR) Other Devices Interrupts Clock/Reset Distribution CPU Debug via JTAG IP Version and Source  Simulation and Verification Simulation Overview                                                                                 |           |

| Overview Processor Local Bus (PLB) On-Chip Peripheral Bus (OPB) Device Control Registers (DCR) Other Devices Interrupts Clock/Reset Distribution CPU Debug via JTAG IP Version and Source  Simulation and Verification Simulation Overview SWIFT and BFM CPU Models                                                        |           |

| Overview Processor Local Bus (PLB) On-Chip Peripheral Bus (OPB) Device Control Registers (DCR) Other Devices Interrupts Clock/Reset Distribution CPU Debug via JTAG IP Version and Source  Simulation and Verification Simulation Overview SWIFT and BFM CPU Models Behavioral Models                                      |           |

| Overview Processor Local Bus (PLB) On-Chip Peripheral Bus (OPB) Device Control Registers (DCR) Other Devices Interrupts Clock/Reset Distribution CPU Debug via JTAG IP Version and Source  Simulation and Verification Simulation Overview SWIFT and BFM CPU Models Behavioral Models Design Flow Environment.             |           |

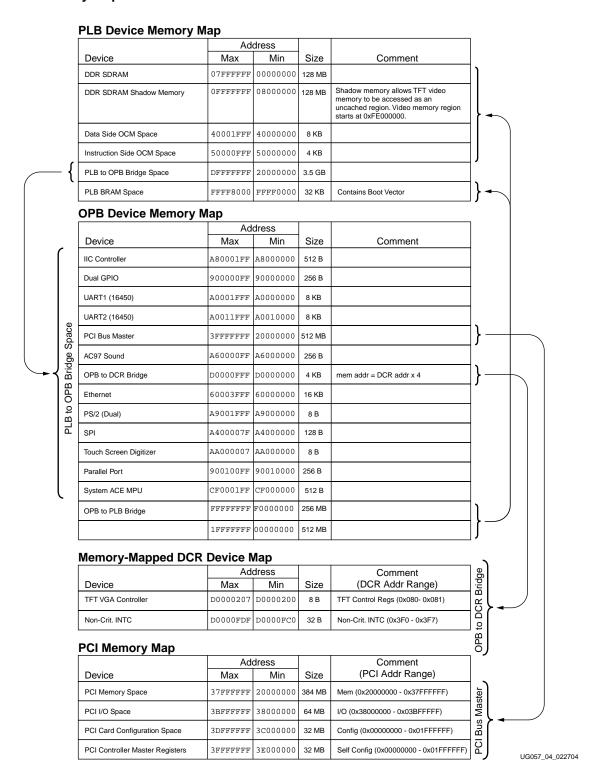

| Overview Processor Local Bus (PLB) On-Chip Peripheral Bus (OPB) Device Control Registers (DCR) Other Devices Interrupts Clock/Reset Distribution CPU Debug via JTAG IP Version and Source  Simulation and Verification Simulation Overview SWIFT and BFM CPU Models Behavioral Models Design Flow Environment.  Memory Map |           |

| Overview Processor Local Bus (PLB) On-Chip Peripheral Bus (OPB) Device Control Registers (DCR) Other Devices Interrupts Clock/Reset Distribution CPU Debug via JTAG IP Version and Source  Simulation and Verification Simulation Overview SWIFT and BFM CPU Models Behavioral Models Design Flow Environment.             |           |

| Other Modifications                                        |    |

|------------------------------------------------------------|----|

| Behavioral Models/Testbenches                              |    |

| Directory and File Listings                                | 34 |

|                                                            |    |

| Chapter 3: EDK Tutorial and Demonstration                  |    |

| Introduction                                               | 37 |

| Instructions for Invoking the EDK tools                    |    |

| Launching Xilinx Platform Studio (XPS)                     |    |

| Instructions for Selecting Software Application            | 38 |

| Instructions for Running Functional Simulations            | 38 |

| Instructions for Building / Implementing Design            | 41 |

| Instructions for Downloading Design                        |    |

| Download Using Parallel Cable IV (iMPACT Program)          | 41 |

| Download Using System ACE                                  |    |

| Software                                                   |    |

| Building the Software Demo Applications                    |    |

| Building the Linux BSP                                     | 45 |

|                                                            |    |

| Chapter 4: Introduction to Hardware Reference IP           |    |

| Introduction                                               | 47 |

| Hardware Reference IP Source Format and Size               | 47 |

| Further Reading                                            | 48 |

| Resources for EDK Users (Including New Users)              |    |

| Documentation Provided by Xilinx                           |    |

| IBM CoreConnect Documentation                              |    |

| IBM CoreConnect Toolkit Documentation                      |    |

|                                                            |    |

| Chapter 5: Using IPIF to Build IP                          |    |

| Abstract                                                   | 51 |

| Introduction                                               |    |

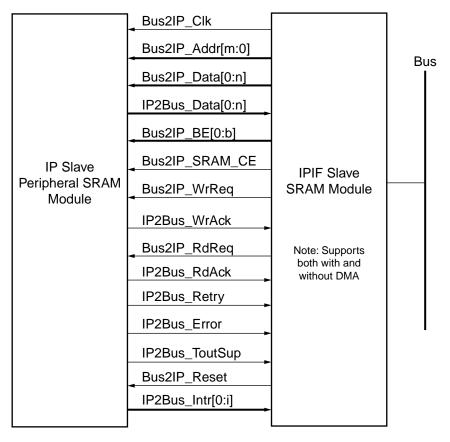

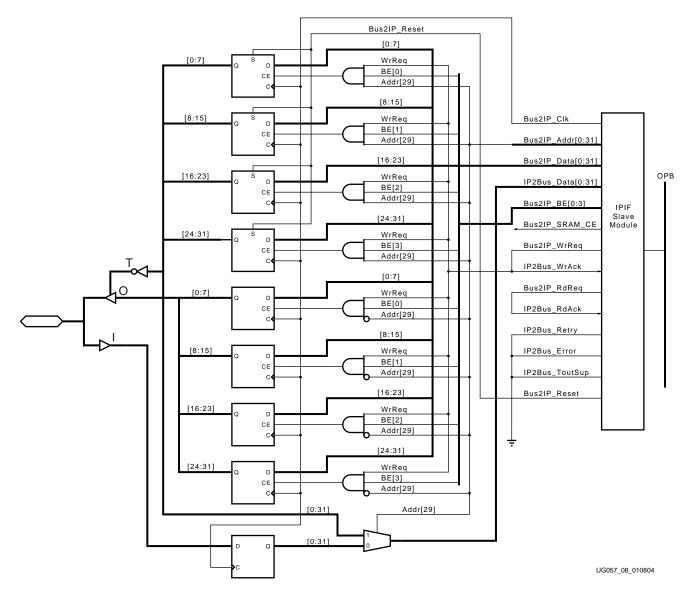

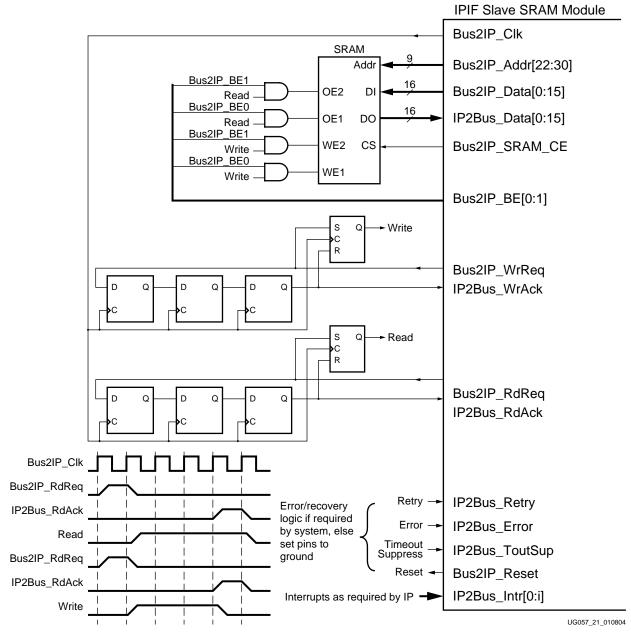

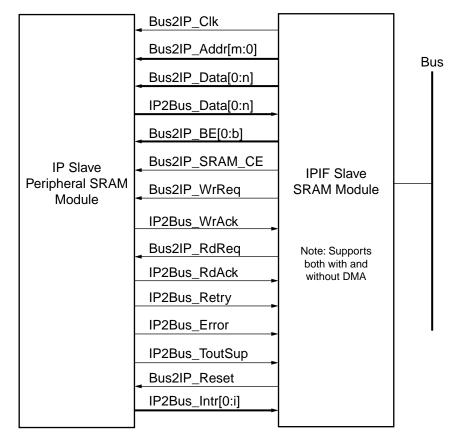

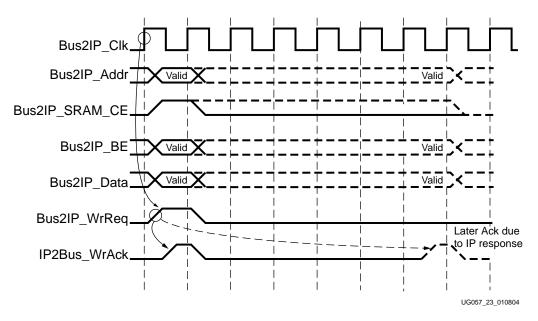

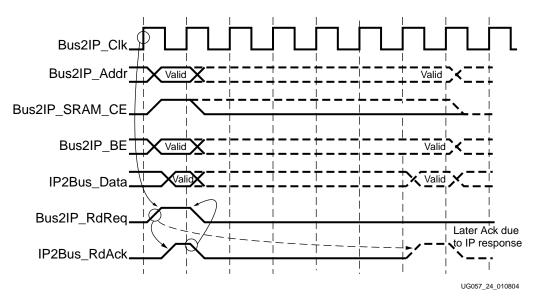

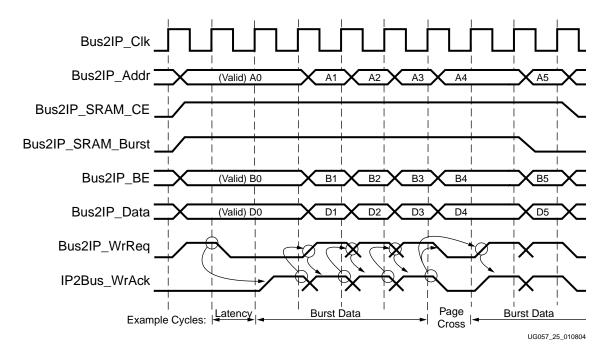

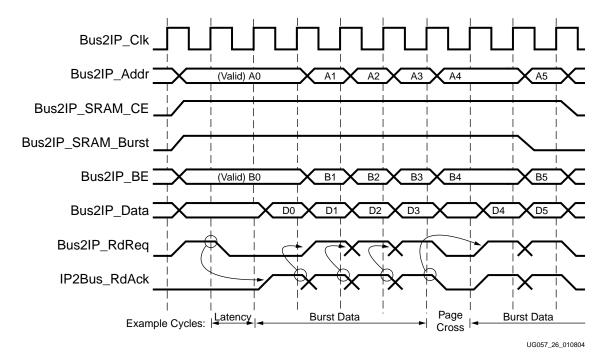

| SRAM Protocol Overview of IPIF                             |    |

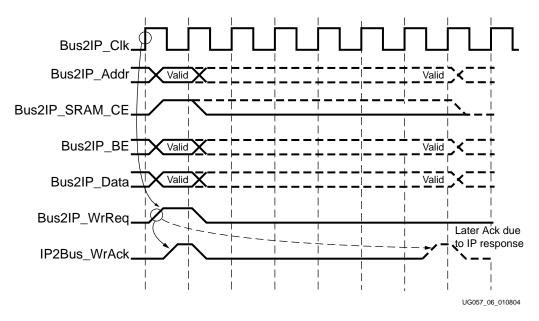

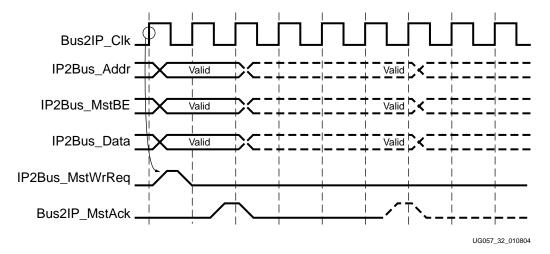

| Basic Write Transactions                                   |    |

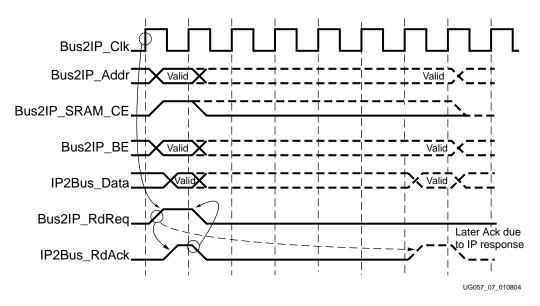

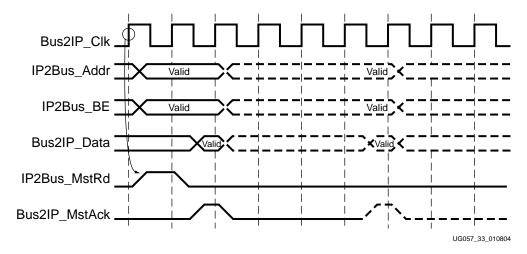

| Basic Read Transactions                                    |    |

| IPIF Status and Control Signals                            | 54 |

| Using IPIF to Create a GPIO Peripheral from Scratch        | 55 |

| Using IPIF to Connect a Pre-existent Peripheral to the Bus | 57 |

| Conclusion                                                 | 57 |

|                                                            |    |

| Chapter 6: IPIF Specification                              |    |

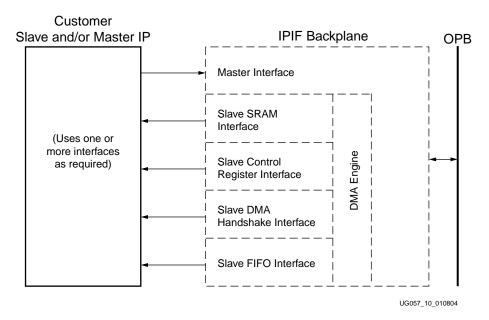

| Overview                                                   | 59 |

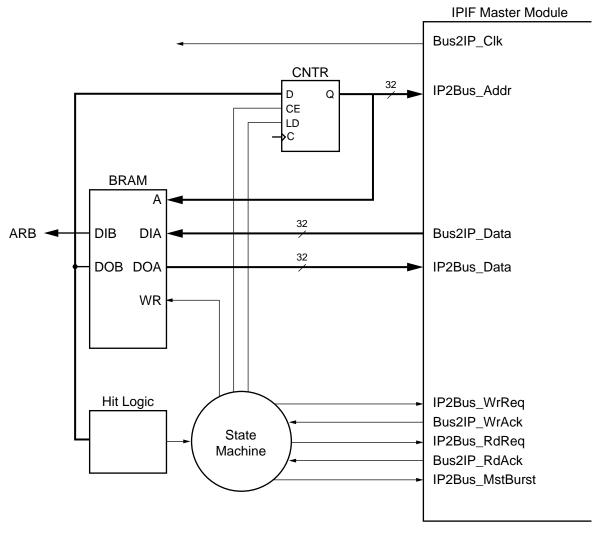

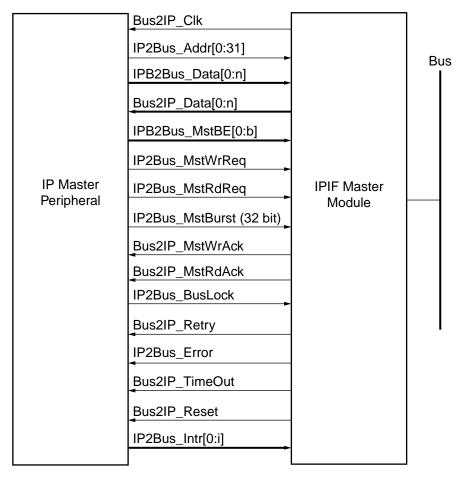

| IPIF Master Module Overview                                |    |

| IPIF Slave Modules Overview                                |    |

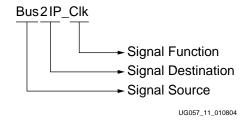

| Signal Conventions                                         |    |

| Bus Numbering and Bit Ordering                             |    |

| Parameter Indexing Versus Parameter Numbering              | 62 |

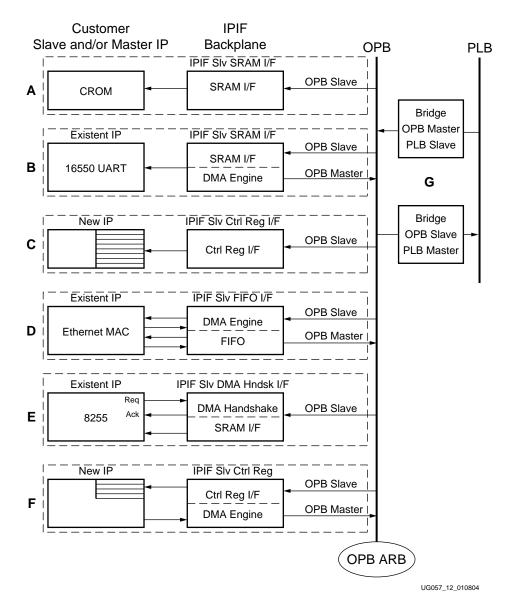

| IPIF Modules in an Example OPB System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| A: Slave SRAM to CROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <br>. 63  |

| B: Slave SRAM to UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <br>. 63  |

| C: Slave Control Register to New IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <br>. 64  |

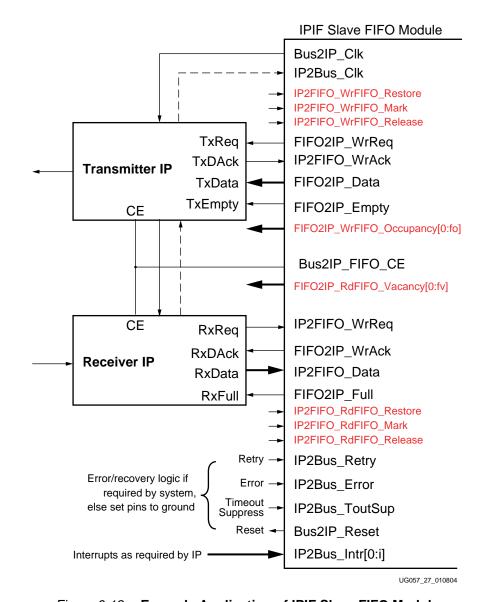

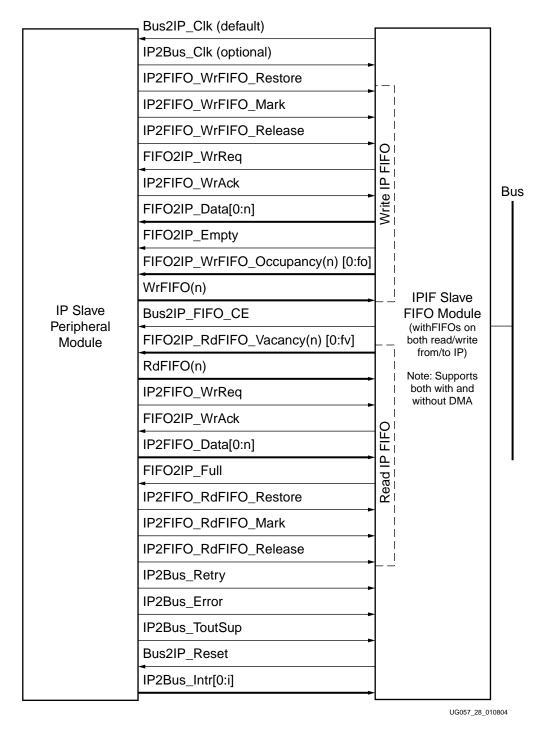

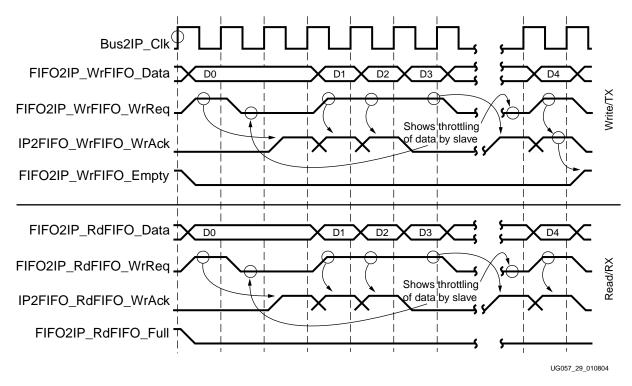

| D: Slave FIFO and DMA Engine to Ethernet MAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

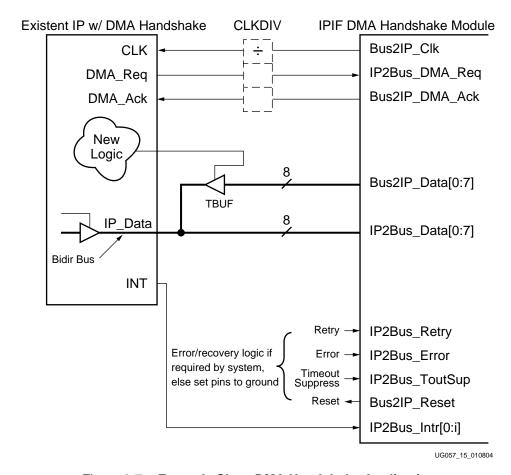

| E: Slave DMA Handshake to 8255                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |

| F: Master with Slave Control Register and DMA Engine to New IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |

| G: Bus-to-Bus Bridges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| Design Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |

| DMA Engine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

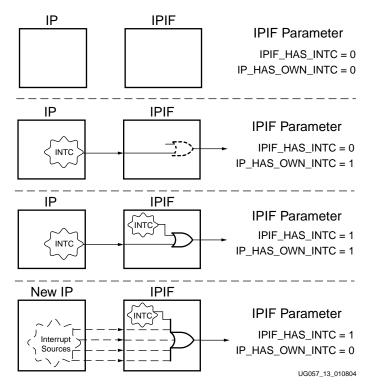

| Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

| Bus Arbiter and Bridges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |

| Data Bus Width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |

| Retry, Error, and Timeout Suppress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <br>67    |

| IPIF Module Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <br>. 67  |

| Slave DMA Handshake Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 67        |

| Example Slave DMA Handshake Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |

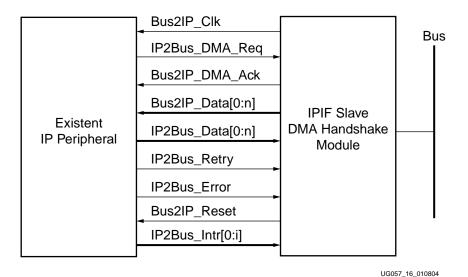

| Generic Slave DMA Handshake Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

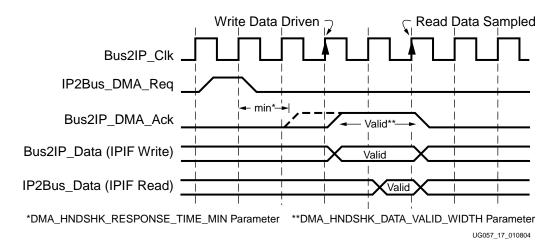

| Slave DMA Handshake Signal Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |

| Slave DMA Handshake Signal List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| Slave DMA Handshake Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |

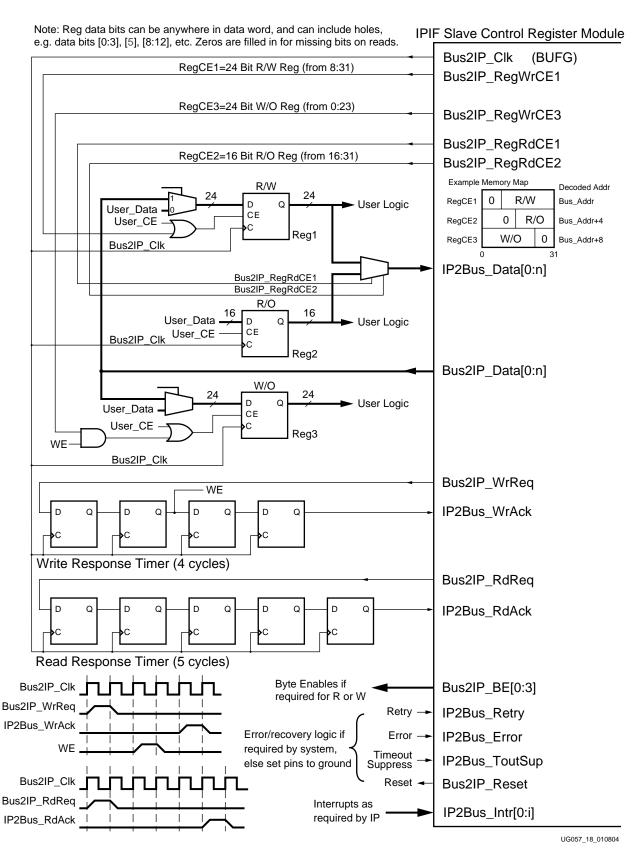

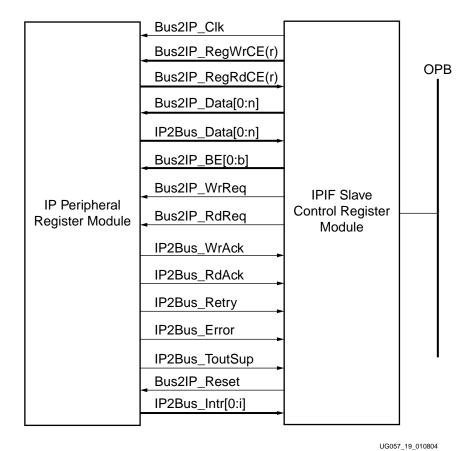

| Slave Control Register Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |

| Example Slave Control Register Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

| Generic Slave Control Register Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <br>. 76  |

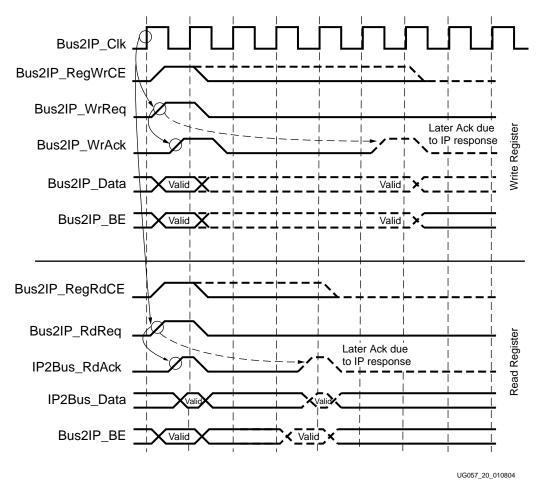

| Slave Control Register Signal Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <br>78    |

| Slave Control Register Signal List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <br>79    |