# **LS-22-SE**

# Hardware User's Manual

# Spectral & Oscilloscope Display PCI Card

| Document: | U0220201    |

|-----------|-------------|

| Author:   | D. Spielman |

| Date:     | 8/09/2006   |

| Release:  | Rev-1       |

Lumistar, Inc.

2701 Loker Ave. West, Suite 230

Carlsbad, CA 92010

(760) 431-2181

www.lumi-star.com

This document is the intellectual property of Lumistar, Inc. The document contains proprietary and confidential information. Reproduction, disclosure, or distribution of this document is prohibited without the explicit written consent of Lumistar, Inc.

This document is provided as is, with no warranties of any kind. Lumistar, Inc. disclaims and excludes all other warranties and product liability, expressed or implied, including but not limited to any implied warranties of merchantability or fitness for a particular purpose or use, liability for negligence in manufacture or shipment of product, liability for injury to persons or property, or for any incidental, consequential, punitive or exemplary damages. In no event, will Lumistar, Inc., be liable for any lost revenue or profits, or other indirect, incidental and consequential damages even if Lumistar, Inc. has been advised of such possibilities, as a result of this document or the usage of items described within. The entire liability of Lumistar, Inc. shall be limited to the amount paid for this document and its contents.

#### RESTRICTED RIGHTS LEGEND

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the rights in Technical Data and Computer Software clause in DFARS 252.227-7013. Lumistar, Inc. and its logo are trademarks of Lumistar, Inc. All other brand names and product names contained in this document are trademarks, registered trademarks, or trade names of their respective holders.

© 2006 Lumistar, Inc. All rights reserved.

Lumistar, Inc. 2701 Loker Avenue West Suite 230 Carlsbad, CA 92010 (760) 431-2181 (760) 431-2665 Fax www.lumi-star.com

### **TABLE OF CONTENTS**

| 2.1       INPUT CHANNELS.       11         2.2       SPECTRUM ANALYZER FUNCTIONALITY       11         2.3       OSCILLOSCOPE FUNCTIONALITY       12         2.4       FPGA FUNCTIONALITY       12         2.5       PCI INTERFACE.       13         3       INSTALLATION AND CONIGURATION.       14         3.1       PRODUCT OUTLINE DIAGRAMS.       14         3.2       ADDRESSING.       14         3.3       PHYSICAL INSTALLATION       14         3.4       INDICATORS.       15         3.5       SHUNT PATCHES.       15         3.6       INTERFACES.       18         3.6.1       70 MHz IF Inputs.       18         3.6.2       Baseband I/O Inputs.       18         3.7       SPECIAL I/O       19         3.8       LS-22V3 INTERFACE CABLE ASSEMBLY.       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE.       21         4.1       The SPECTRAL DISPLAY.       23         4.1.1       Marker Mode.       24         4.1.2       Pause Mode.       27         4.1.3       Bandwidth (BW) Averaging.       28         4.1.4       Spike Rejection.       28                                                | 1 | INTRO | ODUCTION         | 6  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|------------------|----|

| 1.2       MANUAL FORMAT AND CONVENTIONS       7         2       THEORY OF OPERATION       11         2.1       INPUT CHANNELS       11         2.2       SPECTRUM ANALYZER FUNCTIONALITY       12         2.4       FPGA FUNCTIONALITY       12         2.5       PCI INTERFACE       13         3       INSTALLATION AND CONIGURATION       14         3.1       PRODUCT OUTLINE DIAGRAMS       14         3.2       ADDRESSING       14         3.4       INDICATORS       15         3.5       SHUNT PATCHES       15         3.6       INTERFACES       15         3.6       INTERFACES       18         3.6.1       70 MHz IF Inputs       18         3.6.2       Baseband I/O Inputs       18         3.7       SPECIAL I/O       19         3.8       LS-22V3 INTERFACE CABLE ASSEMBLY       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1       THE SPECTRAL DISPLAY       23         4.1.1       Marker Mode       24         4.1.2       Pause Mode       24         4.1.3       Bandwidth (BW) Averaging       28         4.1.4 </th <th></th> <th>1.1 G</th> <th>ENERAL</th> <th> 6</th>  |   | 1.1 G | ENERAL           | 6  |

| 2.1       INPUT CHANNELS.       11         2.2       SPECTRUM ANALYZER FUNCTIONALITY       11         2.3       OSCILLOSCOPE FUNCTIONALITY       12         2.4       FPGA FUNCTIONALITY       12         2.5       PCI INTERFACE.       13         3       INSTALLATION AND CONIGURATION       14         3.1       PRODUCT OUTLINE DIAGRAMS.       14         3.2       ADDRESSING.       14         3.3       PHYSICAL INSTALLATION       14         3.4       INDICATORS       15         3.5       SHUNT PATCHES       15         3.6       INTERFACES       15         3.6       INTERFACES       18         3.6.1       70 MHz IF Inputs       18         3.6.2       Baseband I/O Inputs       18         3.7       SPECIAL I/O       19         3.8       LS-22V3 INTERFACE CABLE ASSEMBLY       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1       I Marker Mode       24         4.1.1       Marker Mode       27         4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.1                                                          |   |       |                  |    |

| 2.1       INPUT CHANNELS.       11         2.2       SPECTRUM ANALYZER FUNCTIONALITY       11         2.3       OSCILLOSCOPE FUNCTIONALITY       12         2.4       FPGA FUNCTIONALITY       12         2.5       PCI INTERFACE.       13         3       INSTALLATION AND CONIGURATION       14         3.1       PRODUCT OUTLINE DIAGRAMS.       14         3.2       ADDRESSING.       14         3.3       PHYSICAL INSTALLATION       14         3.4       INDICATORS       15         3.5       SHUNT PATCHES       15         3.6       INTERFACES       15         3.6       INTERFACES       18         3.6.1       70 MHz IF Inputs       18         3.6.2       Baseband I/O Inputs       18         3.7       SPECIAL I/O       19         3.8       LS-22V3 INTERFACE CABLE ASSEMBLY       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1       I Marker Mode       24         4.1.1       Marker Mode       27         4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.1                                                          | 2 | THEC  | DRY OF OPERATION | 11 |

| 2.2       SPECTRUM ANALYZER FUNCTIONALITY       11         2.3       OSCILLOSCOPE FUNCTIONALITY       12         2.4       FPGA FUNCTIONALITY       12         2.5       PCI INTERFACE       13         3       INSTALLATION AND CONIGURATION       14         3.1       PRODUCT OUTLINE DIAGRAMS       14         3.2       ADDRESSING       14         3.3       PHYSICAL INSTALLATION       14         3.4       INDICATORS       15         3.5       SHUNT PATCHES       15         3.6       INTERFACES       15         3.6       INTERFACES       18         3.6.1       70 MHz IF Inputs       18         3.6.2       Baseband I/O Inputs       18         3.7       SPECIAL I/O       19         3.8       LS-22V3 INTERFACE CABLE ASSEMBLY       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1       THE SPECTRAL DISPLAY       23         4.1.1       Marker Mode       24         4.1.2       Pause Mode       27         4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.                                                          |   |       |                  |    |

| 2.3       OSCILLOSCOPE FUNCTIONALITY       12         2.4       FPGA FUNCTIONALITY       12         2.5       PCI INTERFACE       13         3       INSTALLATION AND CONIGURATION       14         3.1       PRODUCT OUTLINE DIAGRAMS       14         3.2       ADDRESSING       14         3.3       PHYSICAL INSTALLATION       14         3.4       INDICATORS       15         3.5       SHUNT PATCHES       15         3.6       INTERFACES       18         3.6.1       70 MHz IF Inputs       18         3.7       SPECIAL I/O       19         3.8       LS-22V3 INTERFACE CABLE ASSEMBLY       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1       THE SPECTRAL DISPLAY       23         4.1.1       Marker Mode       24         4.1.2       Pause Mode       27         4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.1.5       Analyzer Span       29         4.1.6       Analyzer Relative Frequency       30         4.2       THE TIME-DOMAIN DISPLAY       31         <                                                      |   |       |                  |    |

| 2.4       FPGA FUNCTIONALITY       12         2.5       PCI INTERFACE       13         3       INSTALLATION AND CONIGURATION       14         3.1       PRODUCT OUTLINE DIAGRAMS       14         3.2       ADDRESSING       14         3.3       PHYSICAL INSTALLATION       14         3.4       INDICATORS       15         3.5       SHUNT PATCHES       15         3.6       INTERFACES       18         3.6.1       70 MHz IF Inputs       18         3.6.2       Baseband I/O Inputs       18         3.7       SPECIAL I/O       19         3.8       LS-22V3 INTERFACE CABLE ASSEMBLY       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1       THE SPECTRAL DISPLAY       23         4.1.1       Marker Mode       24         4.1.2       Pause Mode       24         4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.1.5       Analyzer Span       29         4.1.6       Analyzer Frequency Mode       29         4.1.7       Analyzer Relative Frequency       30                                                                   |   |       |                  |    |

| 2.5       PCI INTERFACE       13         3       INSTALLATION AND CONIGURATION       14         3.1       PRODUCT OUTLINE DIAGRAMS       14         3.2       ADDRESSING       14         3.3       PHYSICAL INSTALLATION       14         3.4       INDICATORS       15         3.5       SHUNT PATCHES       15         3.6       INTERFACES       18         3.6.1       70 MHz IF Inputs       18         3.6.2       Baseband I/O Inputs       18         3.7       SPECIAL I/O       19         3.8       LS-22V3 INTERFACE CABLE ASSEMBLY       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1       THE SPECTRAL DISPLAY       23         4.1.1       Marker Mode       24         4.1.2       Pause Mode       27         4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.1.5       Analyzer Span       29         4.1.6       Analyzer Relative Frequency Mode       29         4.1.7       Analyzer Relative Frequency       30         4.2.1       Cursor Controls       32                                                           |   |       |                  |    |

| 3 INSTALLATION AND CONIGURATION       14         3.1 PRODUCT OUTLINE DIAGRAMS       14         3.2 ADDRESSING       14         3.3 PHYSICAL INSTALLATION       14         3.4 INDICATORS       15         3.5 SHUNT PATCHES       15         3.6 INTERFACES       18         3.6.1 70 MHz IF Inputs       18         3.6.2 Baseband I/O Inputs       18         3.7 SPECIAL I/O       19         3.8 LS-22V3 INTERFACE CABLE ASSEMBLY       20         4 OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1 THE SPECTRAL DISPLAY       23         4.1.1 Marker Mode       24         4.1.2 Pause Mode       27         4.1.3 Bandwidth (BW) Averaging       28         4.1.4 Spike Rejection       28         4.1.5 Analyzer Span       29         4.1.6 Analyzer Relative Frequency Mode       29         4.1.7 Analyzer Relative Frequency       30         4.2 THE TIME-DOMAIN DISPLAY       31         4.2.1 Cursor Controls       32         4.2.2 Pause Mode       34         4.2.3 Persistence Control       35         4.2.4 Oscilloscope Timebase Control       35         4.2.5 Oscilloscope Tingger Mode       35  |   |       |                  |    |

| 3.1       PRODUCT OUTLINE DIAGRAMS       14         3.2       ADDRESSING       14         3.3       PHYSICAL INSTALLATION       14         3.4       INDICATORS       15         3.5       SHUNT PATCHES       15         3.6       INTERFACES       18         3.6.1       70 MHz IF Inputs       18         3.6.2       Baseband I/O Inputs       18         3.7       SPECIAL I/O       19         3.8       LS-22V3 INTERFACE CABLE ASSEMBLY       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1       THE SPECTRAL DISPLAY       23         4.1.1       Marker Mode       24         4.1.2       Pause Mode       24         4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.1.5       Analyzer Span       29         4.1.6       Analyzer Frequency Mode       29         4.1.7       Analyzer Relative Frequency       30         4.2       THE TIME-DOMAIN DISPLAY       31         4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3<                                                          | 3 |       |                  |    |

| 3.2       ADDRESSING       14         3.3       PHYSICAL INSTALLATION       14         3.4       INDICATORS       15         3.5       SHUNT PATCHES       15         3.6       INTERFACES       18         3.6.1       70 MHz IF Inputs       18         3.6.2       Baseband I/O Inputs       18         3.7       SPECIAL I/O       19         3.8       LS-22V3 INTERFACE CABLE ASSEMBLY       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1       THE SPECTRAL DISPLAY       23         4.1.1       Marker Mode       24         4.1.2       Pause Mode       27         4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.1.5       Analyzer Span       29         4.1.6       Analyzer Frequency Mode       29         4.1.7       Analyzer Relative Frequency       30         4.2       THE TIME-DOMAIN DISPLAY       31         4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3       Persistence Control       34         4.2.4 <td>J</td> <td></td> <td></td> <td></td>                     | J |       |                  |    |

| 3.3       PHYSICAL INSTALLATION       14         3.4       INDICATORS       15         3.5       SHUNT PATCHES       15         3.6       INTERFACES       18         3.6.1       70 MHz IF Inputs       18         3.6.2       Baseband I/O Inputs       18         3.7       SPECIAL I/O       19         3.8       LS-22V3 INTERFACE CABLE ASSEMBLY       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1       The SPECTRAL DISPLAY       23         4.1.1       Marker Mode       24         4.1.2       Pause Mode       24         4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.1.5       Analyzer Span       29         4.1.6       Analyzer Frequency Mode       29         4.1.7       Analyzer Relative Frequency       30         4.2       The Time-Domain Display       31         4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3       Persistence Control       34         4.2.4       Oscilloscope Timebase Control       35 <tr< td=""><td></td><td></td><td></td><td></td></tr<> |   |       |                  |    |

| 3.4       INDICATORS       15         3.5       SHUNT PATCHES       15         3.6       INTERFACES       18         3.6.1       70 MHz IF Inputs       18         3.6.2       Baseband I/O Inputs       18         3.7       SPECIAL I/O       19         3.8       LS-22V3 INTERFACE CABLE ASSEMBLY       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1       THE SPECTRAL DISPLAY       23         4.1.1       Marker Mode       24         4.1.2       Pause Mode       27         4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.1.5       Analyzer Span       29         4.1.6       Analyzer Frequency Mode       29         4.1.7       Analyzer Relative Frequency       30         4.2       The TIME-DOMAIN DISPLAY       31         4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3       Persistence Control       35         4.2.4       Oscilloscope Tinebase Control       35         4.2.5       Oscilloscope Trigger Source       36                                               |   |       |                  |    |

| 3.5       SHUNT PATCHES       15         3.6       INTERFACES       18         3.6.1       70 MHz IF Inputs       18         3.6.2       Baseband I/O Inputs       18         3.7       SPECIAL I/O       19         3.8       LS-22V3 INTERFACE CABLE ASSEMBLY       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1       THE SPECTRAL DISPLAY       23         4.1.1       Marker Mode       24         4.1.2       Pause Mode       24         4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.1.5       Analyzer Span       29         4.1.6       Analyzer Span       29         4.1.7       Analyzer Relative Frequency       30         4.2       THE TIME-DOMAIN DISPLAY       31         4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3       Persistence Control       34         4.2.4       Oscilloscope Timebase Control       35         4.2.5       Oscilloscope Trigger Mode       35         4.2.6       Oscilloscope Trigger Source       36                                        |   |       |                  |    |

| 3.6       INTERFACES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |       |                  |    |

| 3.6.1       70 MHz IF Inputs       18         3.6.2       Baseband I/O Inputs       18         3.7       SPECIAL I/O       19         3.8       LS-22V3 INTERFACE CABLE ASSEMBLY       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1       THE SPECTRAL DISPLAY       23         4.1.1       Marker Mode       24         4.1.2       Pause Mode       27         4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.1.5       Analyzer Span       29         4.1.6       Analyzer Frequency Mode       29         4.1.7       Analyzer Relative Frequency       30         4.2       THE TIME-DOMAIN DISPLAY       31         4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3       Persistence Control       34         4.2.4       Oscilloscope Timebase Control       35         4.2.5       Oscilloscope Trigger Mode       35         4.2.6       Oscilloscope Trigger Source       36         4.2.7       Oscilloscope Trigger Slope       36         4.2.8       Oscillosc                       |   |       |                  |    |

| 3.6.2       Baseband I/O Inputs       18         3.7       SPECIAL I/O       19         3.8       LS-22V3 INTERFACE CABLE ASSEMBLY       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1       THE SPECTRAL DISPLAY       23         4.1.1       Marker Mode       24         4.1.2       Pause Mode       27         4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.1.5       Analyzer Span       29         4.1.6       Analyzer Frequency Mode       29         4.1.7       Analyzer Relative Frequency       30         4.2       THE TIME-DOMAIN DISPLAY       31         4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3       Persistence Control       34         4.2.4       Oscilloscope Timebase Control       35         4.2.5       Oscilloscope Timebase Control       35         4.2.6       Oscilloscope Trigger Source       36         4.2.7       Oscilloscope Trigger Source       36         4.2.8       Oscilloscope Samples       36         4.3       MO                       |   |       |                  |    |

| 3.7       SPECIAL I/O.       19         3.8       LS-22V3 INTERFACE CABLE ASSEMBLY.       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE.       21         4.1       THE SPECTRAL DISPLAY.       23         4.1.1       Marker Mode.       24         4.1.2       Pause Mode.       27         4.1.3       Bandwidth (BW) Averaging.       28         4.1.4       Spike Rejection.       28         4.1.5       Analyzer Span.       29         4.1.6       Analyzer Frequency Mode.       29         4.1.7       Analyzer Relative Frequency.       30         4.2       THE TIME-DOMAIN DISPLAY       31         4.2.1       Cursor Controls.       32         4.2.2       Pause Mode.       34         4.2.3       Persistence Control.       34         4.2.4       Oscilloscope Tinebase Control.       35         4.2.5       Oscilloscope Trigger Mode.       35         4.2.6       Oscilloscope Trigger Source.       36         4.2.7       Oscilloscope Trigger Source.       36         4.2.8       Oscilloscope Samples.       36         4.3       Modifying the Spectral and Time-Domain Controls       37   |   |       | <u> •</u>        |    |

| 3.8       LS-22V3 Interface Cable Assembly       20         4       OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1       The Spectral Display       23         4.1.1       Marker Mode       24         4.1.2       Pause Mode       27         4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.1.5       Analyzer Span       29         4.1.6       Analyzer Frequency Mode       29         4.1.7       Analyzer Relative Frequency       30         4.2       The Time-Domain Display       31         4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3       Persistence Control       34         4.2.4       Oscilloscope Timebase Control       35         4.2.5       Oscilloscope Trigger Mode       35         4.2.6       Oscilloscope Trigger Source       36         4.2.7       Oscilloscope Trigger Slope       36         4.2.8       Oscilloscope Samples       36         4.3       Modifying the Spectral and Time-Domain Controls       37                                                              |   |       | - was a war      |    |

| 4 OPERATION OF THE LS-22-SE WITH THE LDPS SOFTWARE       21         4.1 THE SPECTRAL DISPLAY       23         4.1.1 Marker Mode       24         4.1.2 Pause Mode       27         4.1.3 Bandwidth (BW) Averaging       28         4.1.4 Spike Rejection       28         4.1.5 Analyzer Span       29         4.1.6 Analyzer Frequency Mode       29         4.1.7 Analyzer Relative Frequency       30         4.2 THE TIME-DOMAIN DISPLAY       31         4.2.1 Cursor Controls       32         4.2.2 Pause Mode       34         4.2.3 Persistence Control       34         4.2.4 Oscilloscope Timebase Control       35         4.2.5 Oscilloscope Trigger Mode       35         4.2.6 Oscilloscope Trigger Source       36         4.2.7 Oscilloscope Trigger Slope       36         4.2.8 Oscilloscope Samples       36         4.3 MODIFYING THE SPECTRAL AND TIME-DOMAIN CONTROLS       37                                                                                                                                                                                                                                            |   |       |                  |    |

| 4.1       The Spectral Display       23         4.1.1       Marker Mode       24         4.1.2       Pause Mode       27         4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.1.5       Analyzer Span       29         4.1.6       Analyzer Frequency Mode       29         4.1.7       Analyzer Relative Frequency       30         4.2       The Time-Domain Display       31         4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3       Persistence Control       34         4.2.4       Oscilloscope Timebase Control       35         4.2.5       Oscilloscope Trigger Mode       35         4.2.6       Oscilloscope Trigger Source       36         4.2.7       Oscilloscope Trigger Slope       36         4.2.8       Oscilloscope Samples       36         4.3       Modifying the Spectral and Time-Domain Controls       37                                                                                                                                                                                                    | 1 |       |                  |    |

| 4.1.1       Marker Mode       24         4.1.2       Pause Mode       27         4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.1.5       Analyzer Span       29         4.1.6       Analyzer Frequency Mode       29         4.1.7       Analyzer Relative Frequency       30         4.2       The Time-Domain Display       31         4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3       Persistence Control       34         4.2.4       Oscilloscope Timebase Control       35         4.2.5       Oscilloscope Trigger Mode       35         4.2.6       Oscilloscope Trigger Source       36         4.2.7       Oscilloscope Trigger Slope       36         4.2.8       Oscilloscope Samples       36         4.3       Modifying the Spectral and Time-Domain Controls       37                                                                                                                                                                                                                                                    | • |       |                  |    |

| 4.1.2       Pause Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |       |                  |    |

| 4.1.3       Bandwidth (BW) Averaging       28         4.1.4       Spike Rejection       28         4.1.5       Analyzer Span       29         4.1.6       Analyzer Frequency Mode       29         4.1.7       Analyzer Relative Frequency       30         4.2       THE TIME-DOMAIN DISPLAY       31         4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3       Persistence Control       34         4.2.4       Oscilloscope Timebase Control       35         4.2.5       Oscilloscope Trigger Mode       35         4.2.6       Oscilloscope Trigger Source       36         4.2.7       Oscilloscope Trigger Slope       36         4.2.8       Oscilloscope Samples       36         4.2.8       Oscilloscope Samples       36         4.3       MODIFYING THE SPECTRAL AND TIME-DOMAIN CONTROLS       37                                                                                                                                                                                                                                                                                   |   |       |                  |    |

| 4.1.4       Spike Rejection       28         4.1.5       Analyzer Span       29         4.1.6       Analyzer Frequency Mode       29         4.1.7       Analyzer Relative Frequency       30         4.2       The Time-Domain Display       31         4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3       Persistence Control       34         4.2.4       Oscilloscope Timebase Control       35         4.2.5       Oscilloscope Trigger Mode       35         4.2.6       Oscilloscope Trigger Source       36         4.2.7       Oscilloscope Trigger Slope       36         4.2.8       Oscilloscope Samples       36         4.2.8       Oscilloscope Samples       36         4.3       Modifying the Spectral and Time-Domain Controls       37                                                                                                                                                                                                                                                                                                                                         |   |       |                  |    |

| 4.1.5       Analyzer Span       29         4.1.6       Analyzer Frequency Mode       29         4.1.7       Analyzer Relative Frequency       30         4.2       THE TIME-DOMAIN DISPLAY       31         4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3       Persistence Control       34         4.2.4       Oscilloscope Timebase Control       35         4.2.5       Oscilloscope Trigger Mode       35         4.2.6       Oscilloscope Trigger Source       36         4.2.7       Oscilloscope Trigger Slope       36         4.2.8       Oscilloscope Samples       36         4.3       MODIFYING THE SPECTRAL AND TIME-DOMAIN CONTROLS       37                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |       |                  |    |

| 4.1.6       Analyzer Frequency Mode       29         4.1.7       Analyzer Relative Frequency       30         4.2       The Time-Domain Display       31         4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3       Persistence Control       34         4.2.4       Oscilloscope Timebase Control       35         4.2.5       Oscilloscope Trigger Mode       35         4.2.6       Oscilloscope Trigger Source       36         4.2.7       Oscilloscope Trigger Slope       36         4.2.8       Oscilloscope Samples       36         4.3       Modifying the Spectral and Time-Domain Controls       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |       |                  |    |

| 4.1.7       Analyzer Relative Frequency       30         4.2       THE TIME-DOMAIN DISPLAY       31         4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3       Persistence Control       34         4.2.4       Oscilloscope Timebase Control       35         4.2.5       Oscilloscope Trigger Mode       35         4.2.6       Oscilloscope Trigger Source       36         4.2.7       Oscilloscope Trigger Slope       36         4.2.8       Oscilloscope Samples       36         4.3       Modifying the Spectral and Time-Domain Controls       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |       |                  |    |

| 4.2       The Time-Domain Display       31         4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3       Persistence Control       34         4.2.4       Oscilloscope Timebase Control       35         4.2.5       Oscilloscope Trigger Mode       35         4.2.6       Oscilloscope Trigger Source       36         4.2.7       Oscilloscope Trigger Slope       36         4.2.8       Oscilloscope Samples       36         4.3       Modifying the Spectral and Time-Domain Controls       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |       |                  |    |

| 4.2.1       Cursor Controls       32         4.2.2       Pause Mode       34         4.2.3       Persistence Control       34         4.2.4       Oscilloscope Timebase Control       35         4.2.5       Oscilloscope Trigger Mode       35         4.2.6       Oscilloscope Trigger Source       36         4.2.7       Oscilloscope Trigger Slope       36         4.2.8       Oscilloscope Samples       36         4.3       Modifying the Spectral and Time-Domain Controls       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |       |                  |    |

| 4.2.2       Pause Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |       |                  |    |

| 4.2.3Persistence Control344.2.4Oscilloscope Timebase Control354.2.5Oscilloscope Trigger Mode354.2.6Oscilloscope Trigger Source364.2.7Oscilloscope Trigger Slope364.2.8Oscilloscope Samples364.3Modifying the Spectral and Time-Domain Controls37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |       |                  |    |

| 4.2.4Oscilloscope Timebase Control354.2.5Oscilloscope Trigger Mode354.2.6Oscilloscope Trigger Source364.2.7Oscilloscope Trigger Slope364.2.8Oscilloscope Samples364.3Modifying the Spectral and Time-Domain Controls37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |       |                  |    |

| 4.2.5Oscilloscope Trigger Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |       |                  |    |

| 4.2.6Oscilloscope Trigger Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |       | 1                |    |

| 4.2.7Oscilloscope Trigger Slope364.2.8Oscilloscope Samples364.3Modifying the Spectral and Time-Domain Controls37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |       | 1 00             |    |

| 4.2.8 Oscilloscope Samples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |       | 1 00             |    |

| 4.3 MODIFYING THE SPECTRAL AND TIME-DOMAIN CONTROLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |       | 1 66 1           |    |

| 5 PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |       |                  |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5 | PROG  | GRAMMING         | 39 |

### LS-22-SE User's Manual

| 5.1 Gi  | ENERAL                         | 39 |

|---------|--------------------------------|----|

| 5.1.1   | PCI Systems                    | 39 |

| 5.2 I/C | O CHANNELS                     |    |

| 5.3 PF  | OGRAMMING DETAILS              | 41 |

| 5.3.1   | Initialization                 | 41 |

| 5.3.2   | Board Identifier               | 41 |

| 5.3.3   | Board ID Register              |    |

| 5.3.4   | EEPROM Access                  |    |

| 5.3.5   | Command Register               |    |

| 5.3.6   | Auxiliary Command Register     |    |

| 5.3.7   | Timebase Register              |    |

| 5.3.8   | Acquisition Memory             | 44 |

| 5.3.9   | Bit Synchronizer Daughterboard | 44 |

## List of Tables Table 5-1 Write Register Summary 41 Table 5-2 Read Register Summary 42 **List of Figures**

#### 1 INTRODUCTION

#### 1.1 General

This document is the Hardware User's Manual for the Lumistar LS-22-SE Spectral & Oscilloscope Display PCI Card. The intent of this document is to provide physical, functional, and operational information for the end user including hardware configuration, interconnection and software interfaces for the device.

Table 1-1 on page 7 contains a detailed model number construction for the LS-22-SE series. This document applies to all model combinations indicated in the table. Optionally, the Lumistar **LS-40-DB10** or **LS-40-DB20** Bit Sync Daughterboard may also be installed on the LS-22-SE Series. Consult the factory for a copy of the LS-40 documentation. Hardware related setup and

interface information can be found in the LS-40 Series User's Manual (Doc. No. U4000201).

The Lumistar LS-22-SE series Spectral & Oscilloscope Display PCI Card is designed to allow spectral and eye pattern displays when used in concert with receivers and diversity combiners.

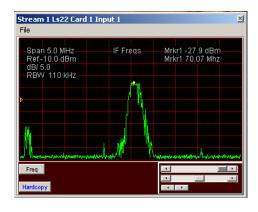

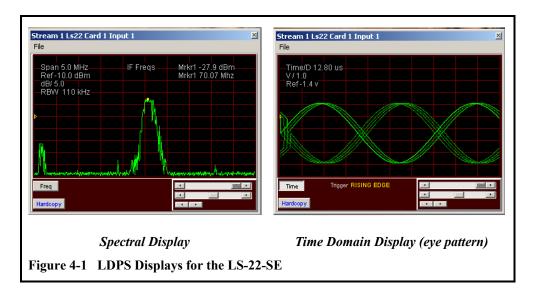

Spectral Display

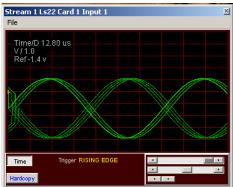

Time Domain Display (eye pattern)

There are three variants in the LS-22-SE series, with single, dual, and triple channel versions available. The LS-22-SE is a single channel instrument that supports the display of spectral and oscilloscope information using the Lumistar Data Processing System (LDPS) software (shown above). The single channel LS-22-SE variant only supports the selection of one type of display at a time (spectrum or time domain). The simultaneous display of both spectral and eye pattern is achievable with the dual channel LS-22-2SE. The simultaneous display of three input channels (in any combination) is supported by the LS-22-3SE.

### LS-22-SE series key features:

- A spectral display with up to 20 MHz Bandwidth accepts 70 MHz IF inputs from the LS-25P-2 Receiver or LS-23-P Pre-Detection Combiner and displays up to 3 spectrums depending on the model selected.

- An Oscilloscope with a sampling rate of 40 MSPS- accepts and selects one of 3 input channels of analog information such as baseband data, bit synchronized data, or AM waveform displays.

- Accepts the LS-40-DB Bit Synchronizer Daughterboard to output data & clock.

- A PCI board with 7.525 inch length.

- Uses the LDPS Software allowing setup, control, and display of LS-25 Series of Receivers and LS-23 series of Diversity Combiners.

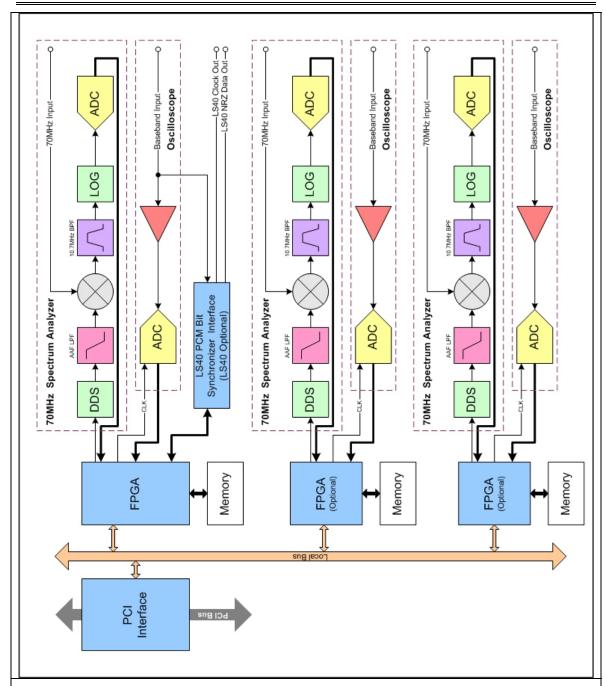

Table 1-2 on page 9 provides specifications for electrical, mechanical, and operational characteristics of the LS-22-SE series product line. A block diagram of the product design is shown in Figure 1-1 on page 10.

| Table 1-1 Applicable Models |                             |  |  |  |  |

|-----------------------------|-----------------------------|--|--|--|--|

| Without Bit Synchronizer    | LS-22-SE (Single Display)   |  |  |  |  |

|                             | LS-22-2SE (Dual Display)    |  |  |  |  |

|                             | LS-22-3SE (Triple Display)  |  |  |  |  |

| With Bit Synchronizer       | LS-22-SEB (Single Display)  |  |  |  |  |

|                             | LS-22-2SEB (Dual Display)   |  |  |  |  |

|                             | LS-22-3SEB (Triple Display) |  |  |  |  |

#### 1.2 Manual Format And Conventions

This manual contains the following sections:

- Chapter 1 provides a brief product overview and technical specifications

- Chapter 2 provides the theory of operation

- Chapter 3 provides installation and configuration instructions

- Chapter 4 provides info on the LS-22-SE LDPS software

- Chapter 5 provides programming information

Throughout this document, several document flags will be utilized to emphasis warnings or other important data. These flags come in three different formats: Warnings, Cautions, and Information. Examples of these flags appear below.

### Warning:

(Details of critical information which prevents loss of functionality)

#### Caution:

Details of operational or functional cautionary advisories

#### Information:

(Details of emphasised operational information)

| Table 1-2 Speci  | ifications for the L   | S-22-SE Series                                                      |

|------------------|------------------------|---------------------------------------------------------------------|

| Mechanical       |                        |                                                                     |

| 111001111111111  | Envelope Dimensions    | 7.5"(L) x 3.9"(W) x 0.74"(H)                                        |

|                  | Form Factor            | PCI board – 7.5 inch long                                           |

|                  | Weight                 | $\sim 6 \text{ oz.}$                                                |

|                  | Daughterboard          | Accepts LS-40-DB Bit Synchronizer                                   |

| Electrical       | Daughteroouru          | recepts Lo 10 DD Dit Synchronizer                                   |

|                  | Individual power       | +5  V = 680 ma                                                      |

|                  | requirements           |                                                                     |

|                  | Current Required (typ) | +12  V = 25 ma                                                      |

|                  | (·JF)                  | -12  V = 10 ma                                                      |

|                  | Total Power            | < 3.8 Watts                                                         |

| Performance      |                        |                                                                     |

| Spectral Display | Display Bandwidth      | Up to 20 MHz                                                        |

| Inputs:          | -r                     |                                                                     |

|                  | Number of Channels     | Up to 3 depending on the model chosen                               |

|                  | Input Frequency        | 70 MHz IF                                                           |

|                  | Input Signal Level     | -20 dBm Nominal                                                     |

| Oscilloscope     | Oscilloscope           | 40 MHz sampling rate                                                |

| Display Inputs:  | Bandwidth              | Approx. 8 MHz                                                       |

| Display inpats.  | Number of Channels     | Up to 3 depending on the model chosen                               |

|                  | Baseband PCM Inputs    | Baseband PCM inputs can be simultaneously applied to the scope      |

|                  | Buscound I Civi Inputs | and optional bit synchronizer.                                      |

|                  | Other Analog Inputs    | Oscope can also monitor: Bit Synchronizer output, AM Output from    |

|                  | Other Analog inputs    | LS-25, AGC Output from LS-25, etc                                   |

|                  | Input Signal Level     | 4 Volts p-p for full-scale                                          |

| Bit Synchronizer | NRZ-L Data and         | TTL Level                                                           |

| Outputs:         | Clock                  |                                                                     |

|                  | Tape Output            | PCM Code selectable bi-polar output for Instrumentation tape        |

|                  |                        | recorder                                                            |

|                  | Test Output            | Pseudo-random test pattern can be enabled from the bit synchronizer |

|                  |                        | with 2 <sup>15</sup> -1 PRN sequence. This output is bi-polar.      |

| Other Inputs &   | Status                 | A TTL-compatible status line is provided                            |

| Outputs:         |                        |                                                                     |

|                  | Aux Status Triggers    | Used for external trigger input for the oscilloscope display        |

|                  | (up to 3)              |                                                                     |

|                  | Auxiliary Bit Sync     | Used when bit sync is not associated with scope                     |

|                  | Input                  |                                                                     |

| Connectors       |                        |                                                                     |

|                  | IF Input Connections   | Three (3) SMA Type                                                  |

|                  | Other I/O              | D-Series Connector with 26 female contacts.                         |

|                  | Breakout Cable         | Cable assembly to BNC included                                      |

| Environmental    | •                      |                                                                     |

|                  | Operating              | 0° to +50° C                                                        |

|                  | Temperature            |                                                                     |

|                  | Non-Operating Temp     | -25° to +70° C                                                      |

|                  | Operating Humidity     | 0 to 90% (Non-condensing)                                           |

|                  | Non-Operating          | Protect from moisture and contamination                             |

|                  | Humidity               | Trees from more and contamination                                   |

Figure 1-1 Block Diagram of the LS-22-SE Series Display Card

### 2 THEORY OF OPERATION

This section of the document discusses the theory of operation of the LS-22-SE Spectral & Oscilloscope Display PCI Card from a functional perspective. The discussion will focus on the main functions the board performs and will include:

- Spectrum Analyzer

- Oscilloscope

- FPGA

- PCI Interface

- Input Channels

The functional block diagram for the LS-22-SE is shown in Figure 1-1 on page 10.

### 2.1 Input Channels

The LS-22-SE is populated with either, one, two, or three "channels." Each channel implements either a spectral display centered at 70MHz or a digital oscilloscope. For each channel, a Xilinx FPGA controls these functions and interfaces them to the local address and data bus of a PLX Technologies PCI9080 PCI interface chip. The 9080 is the primary interface between the LS-22-SE and the computer system it is installed in. The first channel is always populated and performs some additional functions not found in the other two channels (LS-40 interface for example).

#### 2.2 Spectrum Analyzer Functionality

To obtain a spectral plot, a Numerically Controlled Oscillator (NCO) is initially programmed to run at a frequency that is equal to 59.3 MHz, minus one half of the sweep range. The NCO output has many extraneous frequencies that are knocked down by a passive LC filter. The filtered signal drives the IF input of a mixer. The other input of the mixer is a 70MHz (nominal) IF output from a receiver or combiner and is brought in and amplified prior to mixing. The mixer output is buffered and then passed through two, 10.7 MHz ceramic bandpass filters. The 10.7 MHz result is monitored by a LOGAmp. The leveled output of the LOGAmp is not used but its VLOG output is conditioned and sampled by a LTC1199, 10-Bit, 500ksps A/D converter.

During the acquisition of the spectral samples, the controlling application issues commands that initializes the NCO to begin running at the bottom frequency of the sweep range. The ceramic bandpass filters create a "window" about 150 kHz wide at this point. The A/D converter samples the LOGAmp output, and the NCO is then stepped up 1/128 of the sweep range (moving the window). The A/D samples again, and so on until 128 consecutive samples have been taken. As the samples are taken the results are stored away in RAM. A status register sets a flag when the last sample has been taken. The controlling application can then issue an address reset command and reads the RAM contents out by sequential two-byte reads of the I/O space. It should be noted that the spectrum analyzer data is logarithmic and unipolar and is represented in offset-binary format.

### 2.3 Oscilloscope Functionality

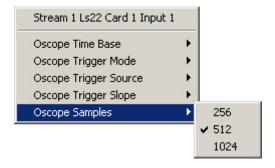

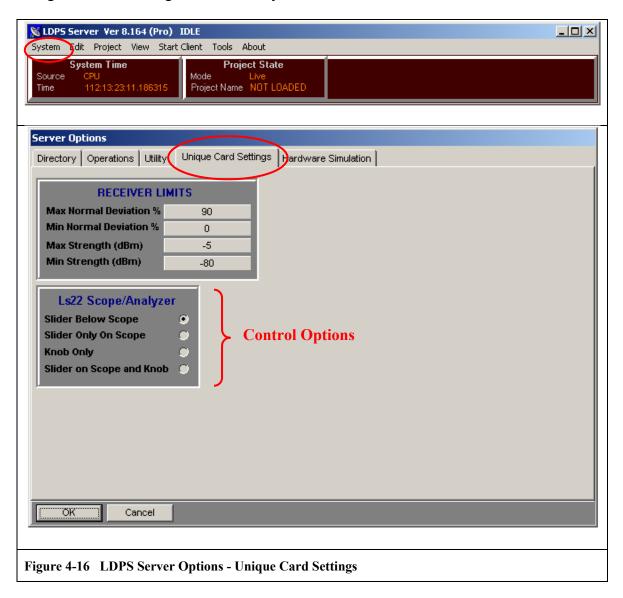

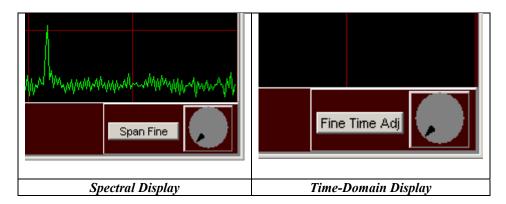

The baseband input signal(s) of the LS-22-SE are first buffered and level-shifted to establish them within the range of an AD9050, 10-Bit, 40-MSPS high-speed flash A/D. The A/D clock is provided by the FPGA. The A/D samples are latched into a register and connected directly to the RAM. To initiate a sample, the controlling application issues an I/O command to arm the scope. The scope control logic in the FPGA is set to trigger on either a zero-crossing at the input, or on an externally-supplied trigger pulse. The scope logic can also free-run and trigger immediately. When the scope triggers, 256, 512, or 1024 samples are taken at the A/D clock rate. At slower sample rates, the A/D is "over-clocked" and the output decimated (most of the data thrown away). As with the spectrum analyzer, a done-status indicates the sampling is complete and the data can be read out sequentially.

#### 2.4 FPGA Functionality

On the LS-22-SE, most of the logic associated with a "channel" is implemented in a Xilinx FPGA. The Xilinx part is a programmable "soft" device, and is initialized from a serial EEPROM. At system reset time, this EEPROM is sequentially read from and the Xilinx part is configured. If additional channels are populated, each of them will have their own FPGA but will be programmed in parallel with data from the EEPROM.

The FPGA provides data and timing signals to the spectrum analyzer and scope functions for each channel. In the case of the channel 0 FPGA, it also controls the timing of the data bus and address bus connected to the PCI9080 PCI interface chip.

A second EEPROM is associated with channel 0. This EEPROM is organized into 16-bit words and in this application is pre-initialized to provide the following: First, a null-bound ASCII string up to 15 bytes long is pre-stored in this EEPROM (specifically, "LS22SE") and is read out immediately after the FPGA is initialized. This string is stored in a small RAM inside the FPGA and can be sequentially read through I/O port 0xn0. For channel 0, this can be used to confirm the board is indeed an LS-22-SE. For the other channels, it can be used to determine their presence. Second, the spectrum analyzer has four sweep widths defined. The sweep function is implemented by an NCO. The starting NCO frequency, and the "increment" for each sweep are stored in the EEPROM as 32-bit constants. This enables the FPGA to operate the analyzer sweep function without processor mothering.

Third, the channel 0 FPGA uniquely drives the board ID function. This is implemented by four chip LEDs mounted along the top edge of the board. These indicators have two purposes. As the LS-22-SE has no real power-up diagnostics, the LED indicators are physically connected in such way that during system reset, and until the FPGA(s) initialize, they flash on and go out in unison. If they don't come on, or come on and stay on, the board is most definitely broken. In normal operation, after all the lights have gone

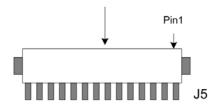

out, the controlling application that runs the board can program the lights on each LS-22-SE board to have a unique pattern. This is often beneficial. The nature of PCI is such that if multiple instances of the same board are plugged into the same bus, there will be no visible way to tell one board from another. Finally, the channel 0's FPGA uniquely has eight bidirectional lines (open drains with pull-ups) that go to an "XD" molex connector, designated J5, whose pads are along the top board edge. They connect to an I/O port for factory test purposes.

#### 2.5 PCI Interface

The PCI interface for the LS-22-SE is a PLX Technologies PCI9080. The PCI interface is set up to map, aside from the 9080's own registers, 64 bytes of PCI I/O space. No memory space is mapped. While there are memories on board, each is mapped to one two-byte area in I/O space. This I/O space is divided as follows:

0x00....0x0F: Channel-0 I/O Reads/Writes. 0x10....0x1F: Channel-1 I/O Reads/Writes. 0x20....0x2F: Channel-2 I/O Reads/Writes.

0x30....0x3F: Reads from this space return meaningless data. Writes to this space are considered broadcasts and write to like registers in all channels at once.

#### 3 INSTALLATION AND CONIGURATION

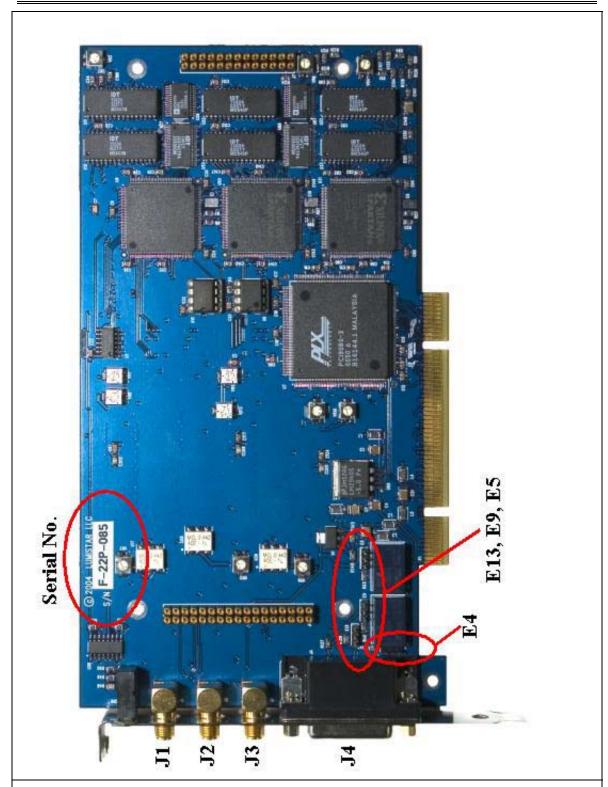

Chapter 3 provides installation and configuration information. This chapter will locate serial numbers and product configuration information, familiarize the user with the layout of the board, and provide information on the proper installation and interconnection of the hardware.

### 3.1 Product Outline Diagrams

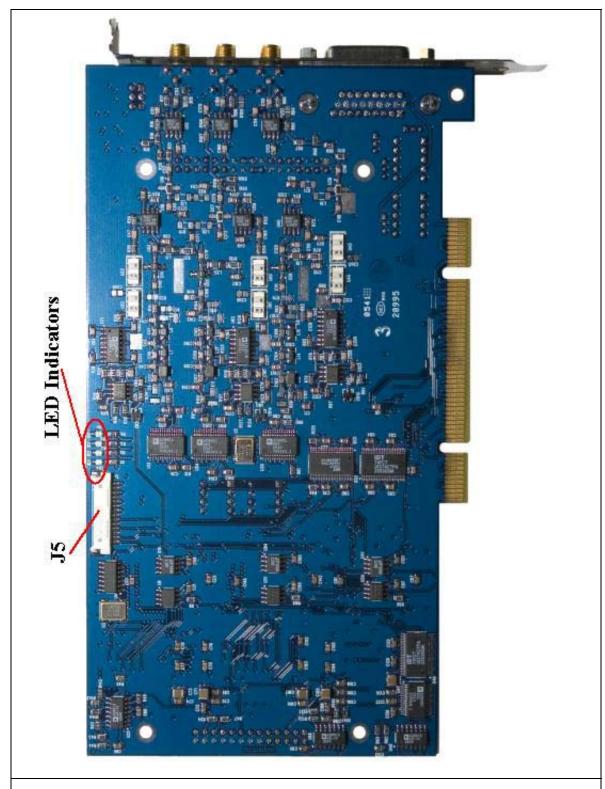

Figure 3-1 on page 16 and Figure 3-2 on page 17 contain photographs of the top and bottom sides of the LS-22-SE Spectral & Oscilloscope Display Card. Connector locations and switch positions are indicated. The model number, serial number, revision information and product options are denoted as shown right and as indicated in Figure 3-1.

#### 3.2 Addressing

The LS-22-SE Spectral & Oscilloscope Display Card is designed around the Peripheral Component Interconnect (PCI) specification. PCI is an interconnection system between a microprocessor and attached devices in which expansion slots are spaced closely for high-speed operation. Using PCI, a computer can support both new PCI cards while continuing to support Industry Standard Architecture (ISA) expansion cards, an older standard. One characteristic of the PCI architecture is that the cards do not have fixed address assignments, and as such, the LS-22-SE card has no address switches or jumpers to set.

#### 3.3 Physical Installation

To install the LS-22-SE in the target computer system, the following procedure should be followed:

1. Perform a normal system shutdown of the PC system and remove the primary power plug.

#### Warning:

Installation of display card in a powered platform will cause immediate damage to the interface hardware. Ensure that power is removed from the system prior to hardware installation.

2. Install the LS-22-SE in an unobstructed PC slot ensuring that the card is properly seated in the interface bus socket. PCs vary in their mechanical configurations so it may be necessary to remove additional PC hardware to properly install the LS-22-SE.

3. Install a screw in the mounting panel to secure the unit. Some platforms also have a vertical hold down which can be adjusted to provide additional mechanical stability.

#### 3.4 Indicators

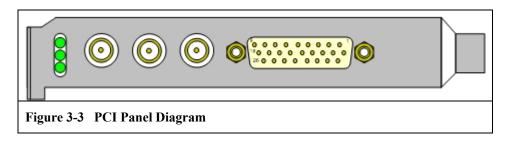

The LS-22-SE has four chip LED indicators shown right that are located along the top edge of the card (see Figure 3-2 on page 17). These LEDs are board identification indicators that are connected to a static register and are intended for use by device drivers in environments where multiple cards are present to identify each of the cards. Additionally, there are three LED

indicators on the PCI panel (see Figure 3-3 on page 18). These have meaning only when the optional LS-40-DB Bit Synchronizer Daughterboard is installed. From left to right, these indicators are defined as bit synchronizer signal present, bit synchronizer lock, and bit synchronizer signal quality. Refer to the LS-40 PCM Bit Synchronizer Technical Manual for interpreting these indicators (Doc. No. U4000201).

#### 3.5 Shunt Patches

As shown in Figure 3-1 on page 16, located near the lower left-hand corner of the card are four, 3-pin patch arrays. Each patch array allows for a 2mm shunt patch. For orientation purposes, glance at the back-side of the card and make note of the location of pin 1 for each patch. Pin 1 is indicated by means of a *square* pad. The four patch arrays are designated; E5, E4, E13, and E9 and perform the following function:

- E5: Shunt Pins 1 and 2 to terminate the auxiliary bit synchronizer input with 75 ohms to ground. When this option is used, the termination jumper JP2 on the LS-40 module must be removed. To use the LS-40 JP2 termination option instead, shunt pins 2 and 3 on E5.

- E4: Shunt Pins 1 and 2 to terminate the Baseband In-1 with 75 ohms to ground. Pin 3 is for factory use.

- E13: Shunt Pins 1 and 2 to terminate the Baseband In-2 with 75 ohms to ground. Pin 3 is for factory use.

- E9: Shunt Pins 1 and 2 to terminate the Baseband In-3 with 75 ohms to ground. Pin 3 is for factory use.

Figure 3-1 LS-22-SE PCI Card (Component Side)

Figure 3-2 LS-22-SE PCI Card (Solder Side)

#### 3.6 Interfaces

The LS-22-SE Spectral & Oscilloscope Display Card is configured at the factory with one, two, or three input channels (see Figure 3-3 below). Both a 70 MHz IF and baseband I/O are provided for each of the configured channels. These interfaces are described in the following paragraphs.

#### **3.6.1 70 MHz IF Inputs**

Each of the configured channels has a 70MHz IF input that employs an SMA Connector. As shown in Figure 3-3 below, from the top down these inputs are designated J1, J2, and J3 and are the IF inputs for spectral display channels 1 through 3 respectively. The nominal input signal level is -20 dBm.

### 3.6.2 Baseband I/O Inputs

The subminiature 26-pin connector designated J4 shown in Figure 3-3 above provides the baseband I/O for the LS-22-SE. The pin outs for the J4 connector are shown in Table 3-1 on page 19.

The Baseband In signal (1, 2, and 3) is the input for the oscilloscope displays. Any of these baseband inputs may also be selected as an input for the optional daughterboard bit synchronizer module. The signal level at each input is fixed at approximately 4 Volts p-p for full-scale oscilloscope deflection.

The Status line (1, 2, and 3) is a TTL-compatible status signal. This pin is connected to an open-drain output driver with weak pull-up, and may thus also be used as a status output.

The Aux Status/Trigger input (1, 2, and 3) is a TTL-compatible signal that may be sensed by any software application, or used as an external trigger input for the oscilloscope display.

The Aux Bit Sync Input may be selected as a separate bit synchronizer input that is not associated with any of the baseband inputs.

The Bit Sync NRZ-L and Clock signals are TTL-compatible outputs. The Bit Sync Tape and Test outputs are bipolar signals, intended for compatibility with instrumentation recorders. When enabled via software on the optional daughterboard Bit Synchronizer, the Test output is a 2<sup>15</sup>-1 bit pseudo-random test pattern at the bit synchronizer programmed bit rate.

| Table 3-1 J4 I/O Connector Pin-out |                        |     |        |     |                    |  |  |  |

|------------------------------------|------------------------|-----|--------|-----|--------------------|--|--|--|

| Pin                                | Signal                 | Pin | Signal | Pin | Signal             |  |  |  |

| 1                                  | Baseband In 1          | 10  | Ground | 19  | Aux Bit Sync Input |  |  |  |

| 2                                  | 2 Aux Status/Trigger 1 |     | Ground | 20  | Status 1           |  |  |  |

| 3                                  | Not Used               | 12  | Ground | 21  | Bit Sync NRZ-L Out |  |  |  |

| 4                                  | Baseband In 2          | 13  | Ground | 22  | Bit Sync Clock Out |  |  |  |

| 5                                  | Aux Status/Trigger 2   | 14  | Ground | 23  | Status 2           |  |  |  |

| 6                                  | Not Used               | 15  | Ground | 24  | Bit Sync Tape Out  |  |  |  |

| 7                                  | Baseband In 3          | 16  | Ground | 25  | Bit Sync Test Out  |  |  |  |

| 8                                  | Aux Status/Trigger 3   | 17  | Ground | 26  | Status 3           |  |  |  |

| 9                                  | Not Used               | 18  | Ground | _   | _                  |  |  |  |

### 3.7 Special I/O

The 14-pin Molex 53780-series connector designated J5 shown in Figure 3-2 on page 17 is located along the top board edge. This is connected to a pseudo-bidirectional I/O port associated with channel 1. The signals here are open drains with weak pull-ups. The connector pin-out is shown in Table 3-2. At present there is no defined usage for this firmware definable input/output.

Function: Accessory Interfaces (See Table Below) Panel Connector: 53780-1400 (Molex) Mating Connector: 51146-1400 (Molex)

| Table 3-2 J5 Special I/O Pin-out |        |     |        |  |  |  |  |  |

|----------------------------------|--------|-----|--------|--|--|--|--|--|

| Pin                              | Signal | Pin | Signal |  |  |  |  |  |

| 1                                | Bit 0  | 8   | Ground |  |  |  |  |  |

| 2                                | Ground | 9   | Bit 4  |  |  |  |  |  |

| 3                                | Bit 1  | 10  | Ground |  |  |  |  |  |

| 4                                | Ground | 11  | Bit 5  |  |  |  |  |  |

| 5                                | Bit 2  | 12  | Ground |  |  |  |  |  |

| 6                                | Ground | 13  | Bit 6  |  |  |  |  |  |

| 7                                | Bit 3  | 14  | Bit 7  |  |  |  |  |  |

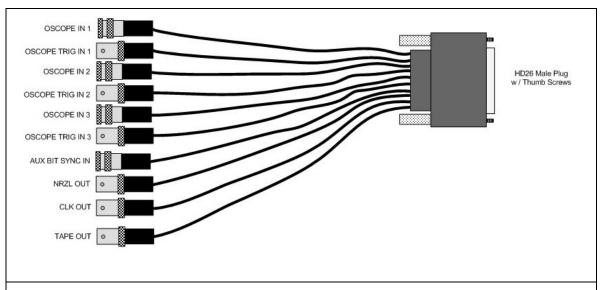

### 3.8 LS-22V3 Interface Cable Assembly

The LS-22-SE Spectral & Oscilloscope Display PCI Card is supplied with a supplementary interface cable assembly shown in Figure 3-4 below. The 26-pin connector is designed to interface with the J4 connector shown in Figure 3-1 on page 16. The specific connector pins of J4 that are used, the signal names, signal types and connector types are documented in Table 3-3 below. The complete pin-out for J4 is shown in Table 3-1 on page 19.

Figure 3-4 LS-22V3 Interface Cable Assembly

| D-Style<br>Connector Pin/ |                  |              |                        |

|---------------------------|------------------|--------------|------------------------|

| Contact No.               | Label Text/Color | Pigtail Type | Signal Details         |

| 1                         | OSCOPE IN1       | BNC-M        | +/- 4V Input Range     |

| 2                         | OSCOPE TRIG IN1  | BNC-F        | TTL Input              |

| 4                         | OSCOPE IN2       | BNC-M        | +/-4V Input Range      |

| 5                         | OSCOPE TRIG IN2  | BNC-F        | TTL Input              |

| 7                         | OSCOPE IN3       | BNC-M        | +/-4V Input Range      |

| 8                         | OSCOPE TRIG IN3  | BNC-F        | TTL Input              |

| 19                        | BIT SYNC IN      | BNC-M        | LS-40 PCM Input Levels |

| 21                        | NRZL OUT         | BNC-F        | RS-422/TTL Output      |

| 22                        | CLK OUT          | BNC-F        | RS-422/TTL Output      |

| 24                        | TAPE OUT         | BNC-F        | RS-422/TTL Output      |

| 10-18                     | (N/A)            | (N/A)        | Ground                 |

### 4 Operation of The LS-22-SE With The LDPS Software

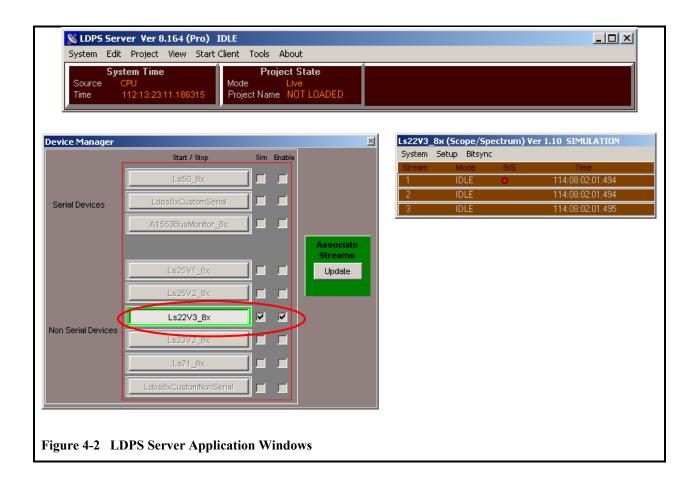

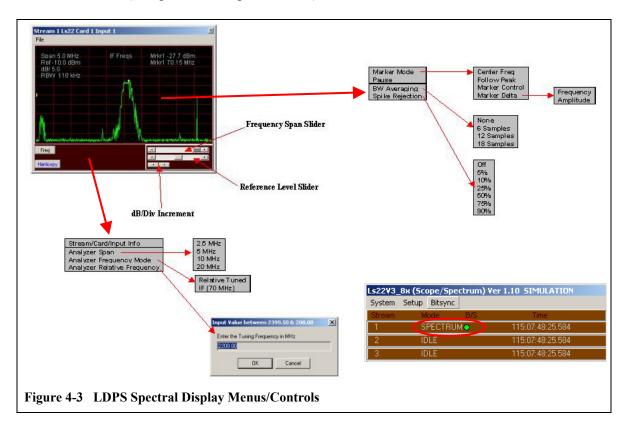

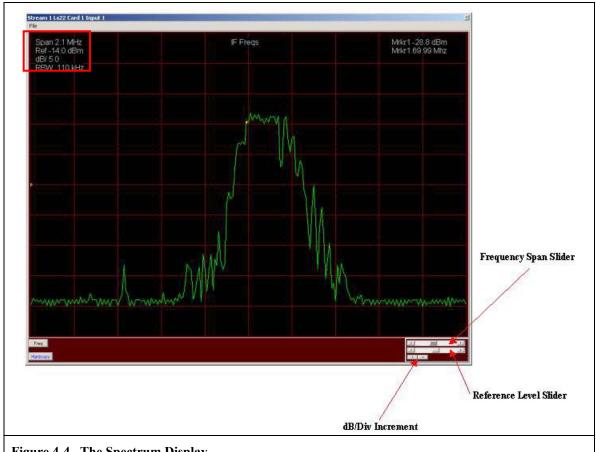

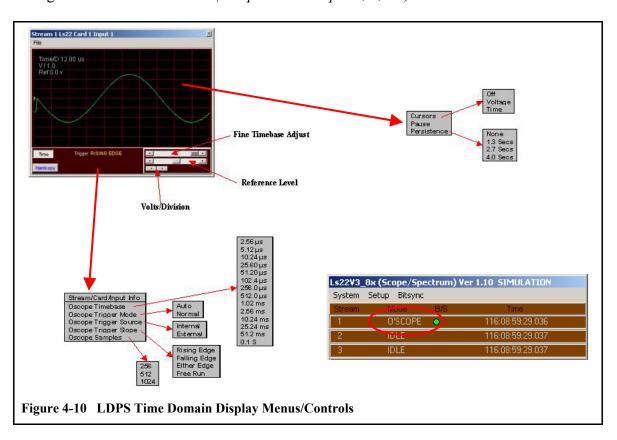

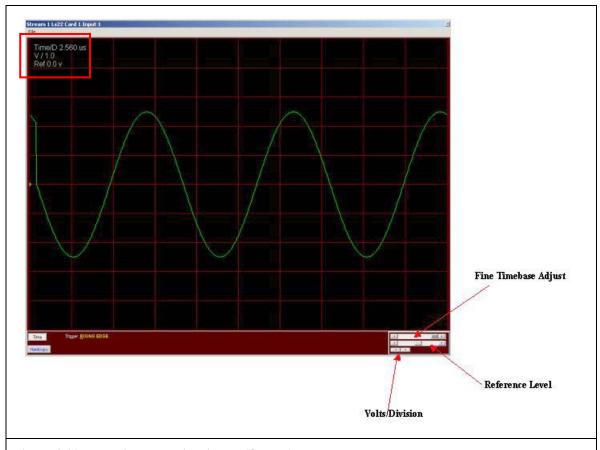

The LS-22-SE is a single/multi-channel instrument that supports the display of spectral and time domain information using the Lumistar Data Processing System (LDPS) software (shown below).

The LDPS is composed of two major application programs - the Server and the Client. The Server program is used to acquire data from various sources (such as the LS-22-SE). The server formats the data into a normalized format, archives it, and then pass the data on to the client application for further processing and/or display. The Client is mainly a data processing and presentation program, with hooks to allow new display and processing routines to be added by the user. The server and client applications can run together on the same computing platform, or on different platforms interconnected via a Local Area Network (LAN). This user's manual will focus primarily on the server side application.

To initially configure the LS-22-SE, perform the following steps:

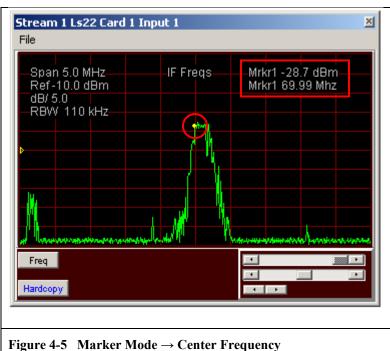

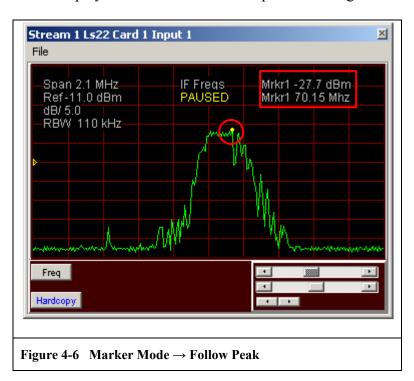

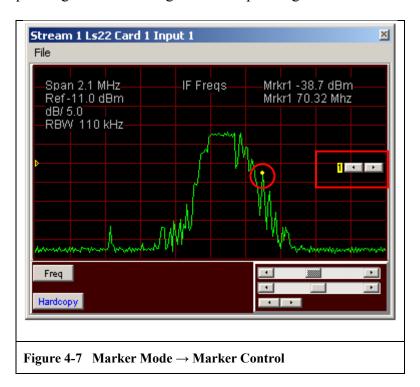

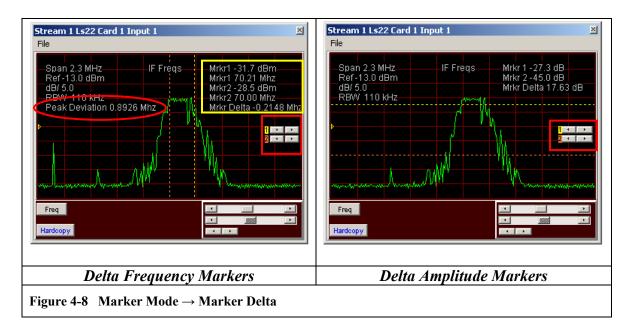

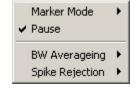

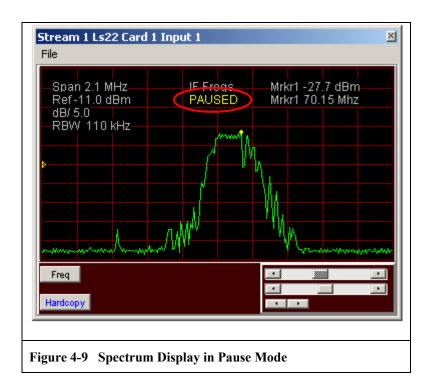

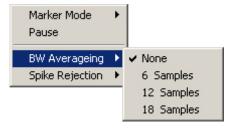

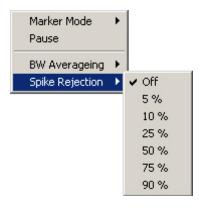

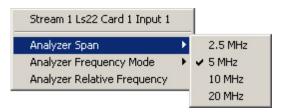

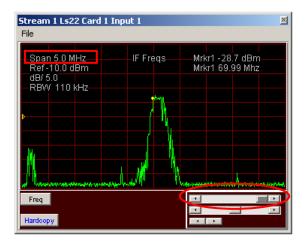

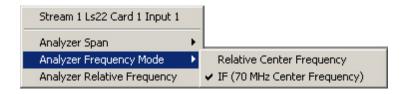

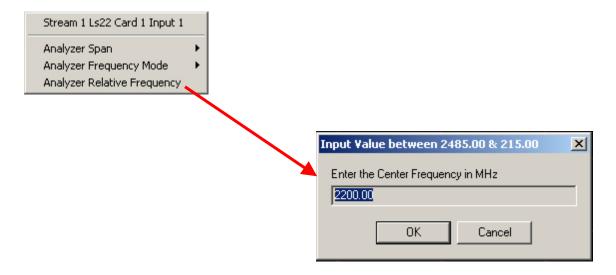

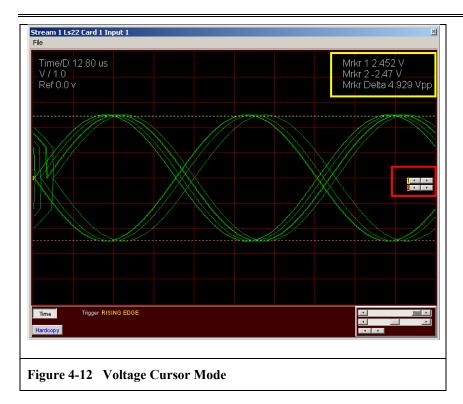

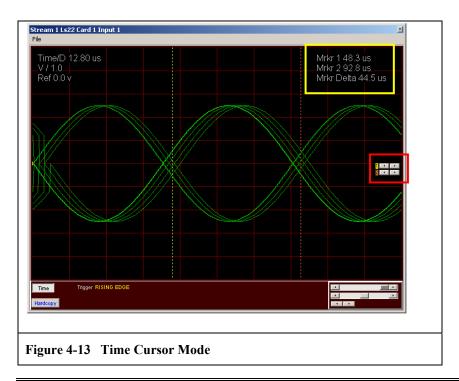

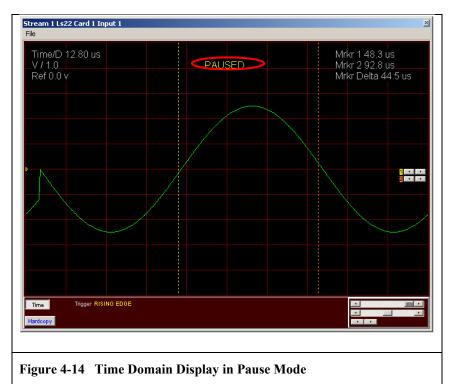

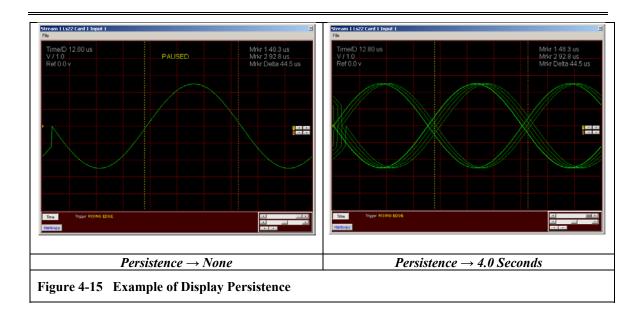

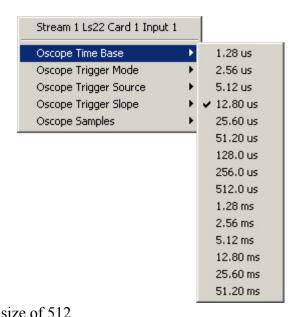

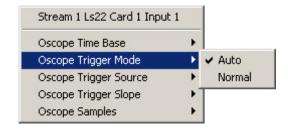

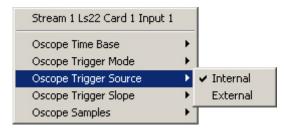

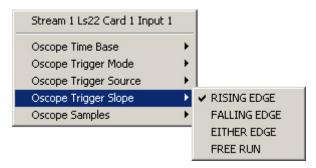

- 1. Run the LDPS server program and from the System menu shown below, select "Devices" and then "Manage" (System→ Devices→ Manage)