# QUANTUM

Intel PXA270 XScale RISC based SODIMM Single Board Computer

**Technical Manual**

#### Disclaimer

The information in this manual has been carefully checked and is believed to be accurate. Eurotech Ltd assumes no responsibility for any infringements of patents or other rights of third parties, which may result from its use.

Eurotech Ltd assumes no responsibility for any inaccuracies that may be contained in this document. Eurotech Ltd makes no commitment to update or keep current the information contained in this manual.

Eurotech Ltd reserves the right to make improvements to this document and/or product at any time and without notice.

#### Warranty

This product is supplied with a 3 year limited warranty. The product warranty covers failure of any Eurotech Ltd manufactured product caused by manufacturing defects. The warranty on all third party manufactured products utilised by Eurotech Ltd is limited to 1 year. Eurotech Ltd will make all reasonable effort to repair the product or replace it with an identical variant. Eurotech Ltd reserves the right to replace the returned product with an alternative variant or an equivalent fit, form and functional product. Delivery charges will apply to all returned products. Please check www.eurotech-ltd.co.uk for information about Product Return Forms.

#### Trademarks

ARM and StrongARM are registered trademarks of ARM Ltd.

Intel and XScale are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

CompactFlash is the registered trademark of SanDisk Corp.

Bluetooth is a registered trademark of Bluetooth SIG, Inc.

All other trademarks recognised.

#### **Revision History**

| Manual  | PCB        | Date                         | Comments                                    |

|---------|------------|------------------------------|---------------------------------------------|

| Issue A | V0 Issue 2 | 1 <sup>st</sup> October 2007 | First full release for QUANTUM Version 0I2. |

© 2007 Eurotech Ltd. For contact details, see page <u>55</u>.

ISO 9001 FM12961

## Contents

| Product handling and environmental compliance                     | 5  |

|-------------------------------------------------------------------|----|

| Introduction                                                      | 6  |

| QUANTUM 'at a glance'                                             | 7  |

| QUANTUM features                                                  |    |

| QUANTUM support products                                          |    |

| About this manual                                                 |    |

| Conventions                                                       |    |

| Getting started                                                   | 12 |

| Detailed hardware description                                     | 13 |

| QUANTUM block diagram                                             |    |

| QUANTUM address map                                               |    |

| PXA270 GPIO pin assignments                                       |    |

| Interrupt assignments                                             |    |

| PXA270 processor                                                  |    |

| Real Time Clock (RTC)                                             |    |

| Watchdog timer<br>Memory                                          |    |

| Bus extension interfaces                                          |    |

| Flat panel display                                                |    |

| Secure Digital Input/Output (SDIO)                                |    |

| Audio                                                             |    |

| Touchscreen controller                                            | 33 |

| USB ports                                                         | 34 |

| Serial UART ports                                                 | 35 |

| Synchronous Serial Protocol (SSP) ports                           |    |

| I <sup>2</sup> C bus                                              |    |

| Pulse-Width Modulation (PWM)                                      |    |

| Atmel Trusted Platform Module (TPM)                               |    |

| General purpose I/O                                               |    |

| JTAG and debug access                                             |    |

| Power and power management                                        |    |

| Power supplies                                                    |    |

| Processor power management<br>Peripheral devices power management |    |

| Add-on modules power management                                   |    |

| Jumpers and connectors                                            |    |

| Jumpers and connectors                                            |    |

| Connectors                                                        |    |

| Appendix A – Contacting Eurotech Ltd                              |    |

| Appendix R – Specification                                        |    |

|                                                                   |    |

| Appendix C – QUANTUM mechanical diagram                           |    |

| Appendix D – QUANTUM Ethernet module                              |    |

| Appendix E - Reference information                                |    |

| Appendix F - Acronyms and abbreviations                           | 63 |

| Appendix G – RoHS-6 compliance - Materials Declaration Form | 65 |

|-------------------------------------------------------------|----|

| Index                                                       | 66 |

## Product handling and environmental compliance

#### Anti-static handling

This board contains CMOS devices that could be damaged in the event of static electricity being discharged through them. At all times, please observe anti-static precautions when handling the board. This includes storing the board in appropriate anti-static packaging and wearing a wrist strap when handling the board.

#### Packaging

Please ensure that should a board need to be returned to Eurotech Ltd, it is adequately packed, preferably in the original packing material.

#### Electromagnetic compatibility (EMC)

The QUANTUM is classified as a component with regard to the European Community EMC regulations and it is the user's responsibility to ensure that systems using the board are compliant with the appropriate EMC standards.

## 💫 RoHS compliance

The European RoHS Directive (Restriction on the use of certain Hazardous Substances – Directive 2002/95/EC) limits the amount of six specific substances within the composition of the product. The QUANTUM and associated accessory products are available as RoHS-6 compliant options and are identified by a -R6 suffix in the product order code. A full RoHS Compliance Materials Declaration Form is included in <u>Appendix G – RoHS-6 compliance - Materials Declaration Form</u>, page <u>21</u>. Further information about RoHS compliance is available on the Eurotech Ltd web site at <u>www.eurotech-ltd.co.uk</u>.

## Introduction

The QUANTUM is an ultra low-power, low-cost single board computer, based on the Intel PXA270 XScale<sup>®</sup> processor. The PXA270 is an implementation of the Intel XScale micro-architecture combined with a comprehensive set of integrated peripherals, including a flat panel graphics controller, interrupt controller, Real Time Clock and various serial interfaces. The QUANTUM board is based on the standard SO-DIMM form factor module. The QUANTUM board offers a wide range of features, making it ideal for power-sensitive embedded communications, asset monitoring solutions and compact MMI solutions.

The board is available in the following seven variants (the standard variant is QUANTUM 520-M64-F32-04, others are available on request):

| QUANTUM 312-M64-F1-01  | 312MHz PXA270, 64MB SDRAM, 1MB Flash.<br>No AC'97 on-board, no external RTC on-board.  |

|------------------------|----------------------------------------------------------------------------------------|

| QUANTUM 520-M64-F64-02 | 520MHz PXA270, 64MB SDRAM, 64MB Flash.<br>No AC'97 on board, external RTC on-board.    |

| QUANTUM 312-M64-F32-03 | 312MHz PXA270, 64MB SDRAM, 32MB Flash.<br>No AC'97 on-board, external RTC on-board.    |

| QUANTUM 520-M64-F32-04 | 520MHz PXA270, 64MB SDRAM, 32MB Flash.<br>AC'97 on-board, external RTC on-board.       |

| QUANTUM 312-M64-F32-05 | 312MHz PXA270, 64MB SDRAM, 32MB Flash.<br>AC'97 on-board, external RTC on-board.       |

| QUANTUM 520-M64-F64-06 | 520MHz PXA270, 64MB SDRAM, 64MB Flash.<br>No AC'97 on-board, no external RTC on-board. |

| QUANTUM 520-M64-F1-07  | 520MHz PXA270, 64MB SDRAM, 1MB Flash.<br>No AC'97 on-board, no external RTC on-board.  |

An industrial temperature version is available on request. The QUANTUM board is fully RoHS-6 compliant.

For alternative board configurations, please contact Eurotech Ltd (see <u>Appendix A –</u> <u>Contacting Eurotech Ltd</u>, page <u>55</u>, for contact details).

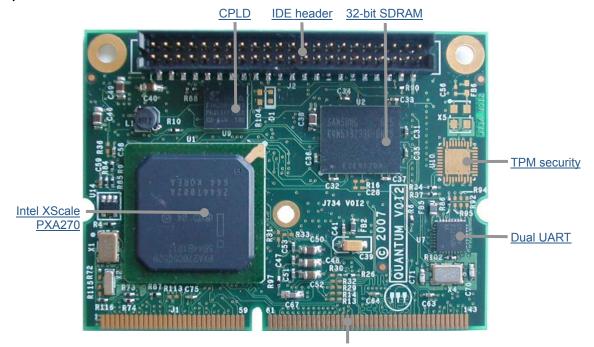

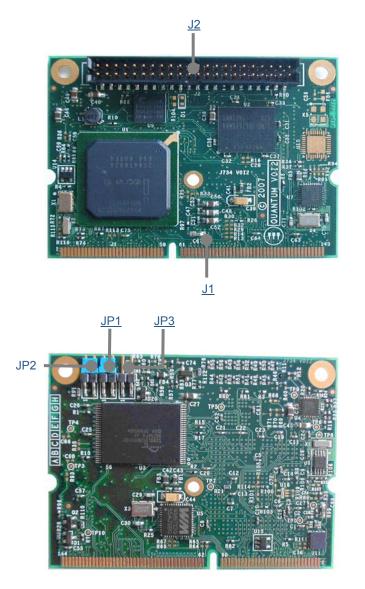

## QUANTUM 'at a glance'

### Top view

SO-DIMM interface

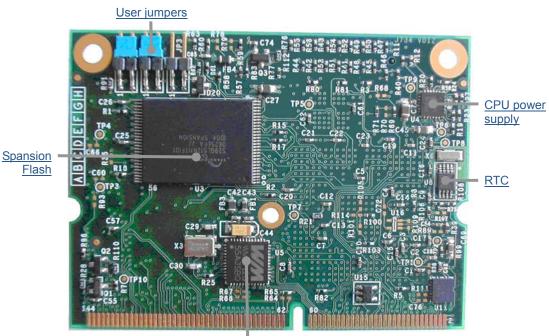

Bottom view

AC'97 audio codec

## **QUANTUM** features

| Processor                   | Intel PXA270 312/416/520MHz XScale <sup>®</sup> Processor 520MHz as standard                                                                                                                                                         |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System memory               | Fixed on-board<br>Up to 64MB SDRAM (32-bit wide SDRAM data bus)                                                                                                                                                                      |

| Silicon disk                | Fixed on-board memory<br>1/16/32/64MB on-board Flash                                                                                                                                                                                 |

| 5 serial ports              | <ul> <li>Three UART serial ports:</li> <li>FFUART</li> <li>BTUART</li> <li>Standard UART</li> <li>Dual extra high-speed full function UART:</li> <li>16C2552 compatible UART</li> <li>RS485 half-duplex direction control</li> </ul> |

| USB support                 | USB 1.1 host/client controller port supporting 12Mb/s and 1.5Mb/s speeds<br>USB 1.1 host controller port supporting 12Mb/s and 1.5Mb/s speeds                                                                                        |

| Extension interfaces        | IDE/bus extension on-board interface (for 3.3V devices only)<br>MMC/SD/SDIO interface<br>I <sup>2</sup> C bus<br>CompactFlash interface bus<br>Two synchronous serial ports (SSP)                                                    |

| Video                       | 16-bit flat panel interface (for STN and TFT displays)                                                                                                                                                                               |

| Audio codec and touchscreen | AC'97 compatible codec<br>Line In, Line Out, Microphone In<br>Touchscreen support – 4-wire analogue resistive                                                                                                                        |

| RTC                         | Battery-backed RTC device**                                                                                                                                                                                                          |

| ТРМ                         | Atmel Trusted Platform module device, TCG v1.2 compatible (optional)                                                                                                                                                                 |

| GPIO                        | Up to seventy eight (depends on used interfaces)                                                                                                                                                                                     |

| PWM                         | Two (Four optionally) x PWM output                                                                                                                                                                                                   |

| Test support                | JTAG interface                                                                                                                                                                                                                       |

| Power requirements          | 3.3V/0.7A maximum                                                                                                                                                                                                                    |

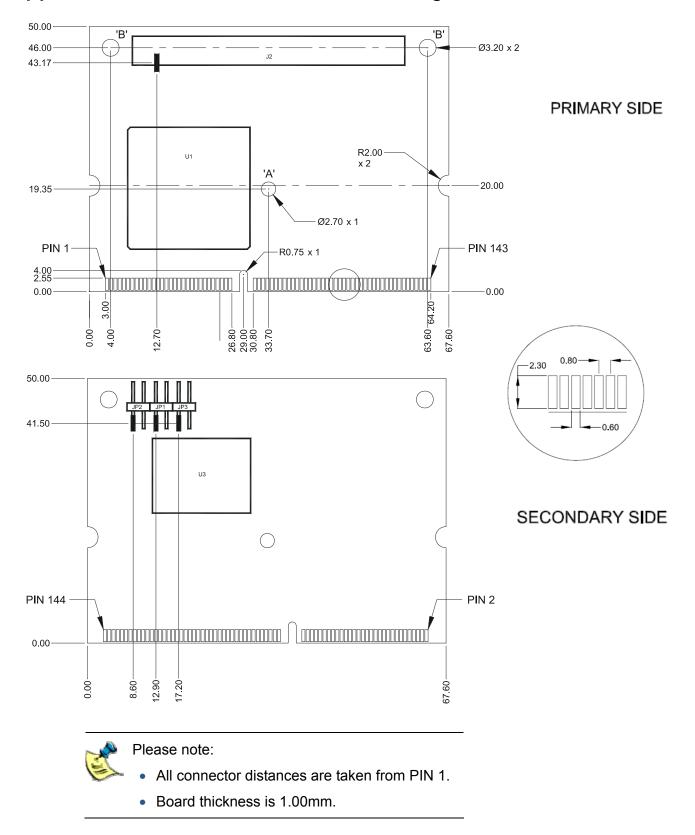

| Mechanical    | SO-DIMM factor, 67.6mm x 50mm                                                                                                                         |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Environmental | <ul> <li>Operating temperature:</li> <li>Industrial: -40 to +85°C**</li> <li>Commercial: -20 to +70°C**</li> <li>RoHS Directive: Compliant</li> </ul> |

|               |                                                                                                                                                       |

\*\* The battery is not a part of the board, it should be connected to the dedicated SO-DIMM pin

## **QUANTUM support products**

The QUANTUM is supported by the following products:

#### QUANTUM Base Board

The QUANTUM Base Board (V2 – J764 V1I1) is offered as part of the QUANTUM development kit and enables the following QUANTUM peripheral connectivity:

- CompactFlash card socket (on-board WLAN module optionally).

- MMC/SD (miniSD) card socket.

- FFUART, BTUART and IRUART serial ports (on-board Bluetooth<sup>®</sup> module on BTUART optionally).

- Two Ext UART serial ports.

- Four standard USB host ports (for standard client devices, i.e. mouse, keyboard, USB flash disk, etc).

- B or mini B-format USB connector (these two connectors have a parallel connection, allowing the QUANTUM module to be connected in client mode to a USB host).

- Three analogue audio jack plugs (stereo Line In, stereo Line Out and Microphone In) provided by QUANTUM WM9712 AC'97 codec.

- Hitachi 3.8" TX09D50VM1CCA LCD connector, universal 2x17 pin header for other LCDs and a 5-pin header for a touchpanel.

- Two 10 pin headers for SPI1, SPI2, I2C, RS485, PWM outputs and GPIO.

- Two 22 pin bus expansion headers, providing:

- IDE interface, or

- 16-bit expansion bus, for the addition of add-on modules.

- VGA and composite Video-Out provided by Focus FS453 data video encoder.

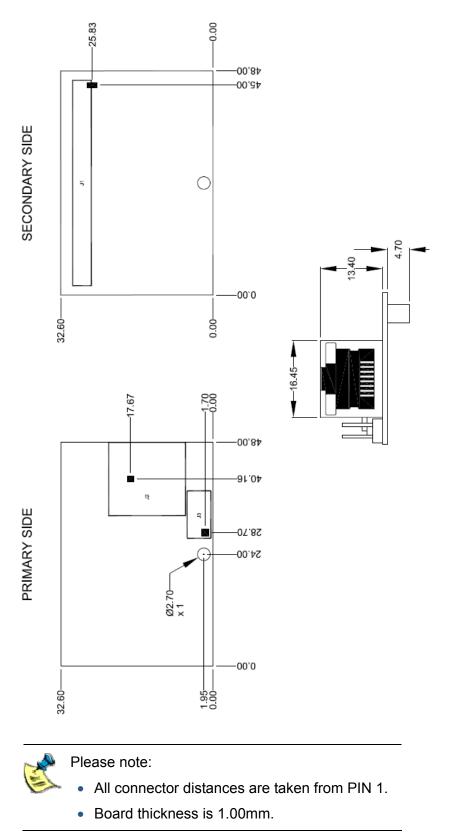

#### QUANTUM Ethernet module

QUANTUM Ethernet module is a DoM (Disk-on-Module) form factor board which extends the QUANTUM module by Ethernet connectivity. The module includes the magnetics and a standard RJ-45 Ethernet port connector. This can be particularly beneficial for Windows CE installation, commissioning and application download. This module could be used by customers during their own commissioning processes. The Ethernet port can be connected via a standard RJ45 or alternatively, a low-profile header. More information about the Ethernet Davicom DM9000A device can be found at <a href="https://www.davicom.com.tw/eng/products/dm9000a.htm">www.davicom.com.tw/eng/products/dm9000a.htm</a>.

## About this manual

This manual describes the operation and use of the QUANTUM module. It is designed to be a reference and user manual and includes information about all aspects of the board.

## Conventions

#### Symbols

The following symbols are used in this guide:

Symbol Explanation

Note - information that requires your attention.

Tip - a handy hint that may provide a useful alternative or save time.

Caution – proceeding with a course of action may damage your equipment or result in loss of data.

Jumper is fitted.

Jumper is not fitted.

## Getting started

A *QUANTUM Quickstart Manual* is provided with each development kit to help you set up and start using the QUANTUM board. Please read this manual and follow the steps explaining how to set up the board and get it up and running.

Once you have done this, you can then start adding further peripherals and begin development.

## **Detailed hardware description**

This section provides a detailed description of the functionality provided by the QUANTUM. This information may be required during development, when adding peripherals or when using the embedded features.

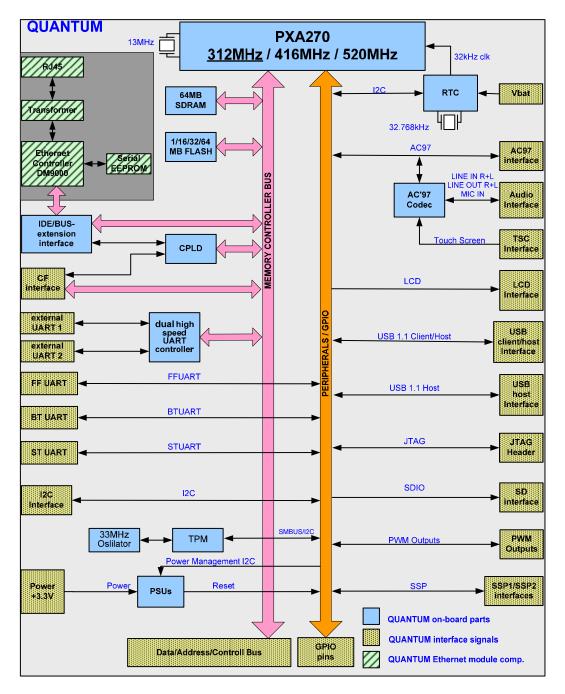

## QUANTUM block diagram

The following diagram shows the functional organisation of the QUANTUM module:

## QUANTUM address map

| PXA270 chip select | Physical address        | Bus width | Description                              |

|--------------------|-------------------------|-----------|------------------------------------------|

| CS0#               | 0x00000000 – 0x03FFFFE  | 16-bit    | FLASH memory (U3)                        |

| CS1#               | 0x04000000 – 0x0400000E | 16-bit    | Dual UART – Ext UART 2                   |

| CS1#               | 0x04000010 - 0x0400001E | 16-bit    | Dual UART – Ext UART 1                   |

| CS1#               | 0x04000020 – 0x07FFFFE  | -         | Reserved                                 |

| CS2#               | 0x08000000 – 0x0BFFFFE  | 16-bit    | SO-DIMM bus expansion                    |

| CS3#               | 0x0C000000 – 0x0FFFFFF  | -         | Reserved                                 |

| CS4#               | 0x10000000 – 0x101FFFFE | 16-bit    | Ethernet on DoM interface                |

| CS4#               | 0x10200000 – 0x103FFFFE | 16-bit    | SO-DIMM bus expansion                    |

| CS4#               | 0x10400000 – 0x13FFFFFF | -         | Reserved                                 |

| CS5#               | 0x14000000 – 0x17FFFFFE | 16-bit    | DoM interface - IDE device               |

| -                  | 0x18000000 – 0x1FFFFFFF | -         | Reserved                                 |

| -                  | 0x20000000 – 0x2FFFFFFE | 16-bit    | CompactFlash                             |

| -                  | 0x30000000 – 0x3FFFFFE  | 16-bit    | Reserved (CompactFlash 2)                |

| -                  | 0x40000000 – 0x43FFFFFC | 32-bit    | PXA270 peripherals <sup>1</sup>          |

| -                  | 0x44000000 – 0x47FFFFFC | 32-bit    | LCD control registers <sup>1</sup>       |

| -                  | 0x48000000 – 0x4BFFFFFC | 32-bit    | Memory controller registers <sup>1</sup> |

| -                  | 0x4C000000 – 0x4FFFFFC  | 32-bit    | USB host registers <sup>1</sup>          |

| -                  | 0x50000000 – 0x53FFFFFC | 32-bit    | Capture interface registers <sup>1</sup> |

| -                  | 0x54000000 – 0x57FFFFFC | 32-bit    | Reserved                                 |

| -                  | 0x58000000 – 0x5BFFFFFC | 32-bit    | Internal memory control <sup>1</sup>     |

| -                  | 0x5C000000 – 0x5C00FFFC | 32-bit    | Internal SRAM bank 0                     |

| -                  | 0x5C010000 – 0x5C01FFFC | 32-bit    | Internal SRAM bank 1                     |

| -                  | 0x5C020000 – 0x5C02FFFC | 32-bit    | Internal SRAM bank 2                     |

| -                  | 0x5C030000 – 0x5C03FFFC | 32-bit    | Internal SRAM bank 3                     |

| -                  | 0x5C040000 – 0X7FFFFFFF | -         | Reserved                                 |

| SDCS0#             | 0xA0000000 – 0xA3FFFFFC | 32-bit    | SDRAM (U2)                               |

| SDCS1#             | 0xA4000000 – 0xA7FFFFC  | 32-bit    | Reserved                                 |

<sup>1</sup> Details of the internal registers are in the *Intel<sup>®</sup> developer's manual* (available on the development kit CD).

## PXA270 GPIO pin assignments

The following table summarises the use of the 118 PXA270 GPIO pins, their direction, alternate functions and active levels:

Key:

- No: GPIO number.

- AF: Alternate Function number.

- Dir: Pin direction.

Active: Function active level or edge.

| GP<br>No | Pio<br>Af | Signal name | Dir    | Active | Function                                         | Wake-up<br>source | See section                                                  |

|----------|-----------|-------------|--------|--------|--------------------------------------------------|-------------------|--------------------------------------------------------------|

| 0        | 0         | AC97_IRQ    | Input  |        | On-board AC'97 interrupt                         | ~                 | <u>Audio power</u><br><u>management,</u><br>page <u>46</u> . |

| 1        | 0         | GPIO1       | Input  | Ţ      | GPIO/deep sleep WakeUp                           | ✓                 | <u>General</u><br><u>purpose I/O,</u><br>page <u>38</u> .    |

| 3        | 0         | PWR_SCL     | Output |        | PXA270 power manager I <sup>2</sup> C            |                   | <u>l<sup>2</sup>C bus,</u>                                   |

| 4        | 0         | PWR_SDA     | I/O    |        |                                                  |                   | page <u>36</u> .                                             |

| 5        | N/A       | PWR_CAP0    | Power  |        |                                                  |                   |                                                              |

| 6        | N⁄A       | PWR_CAP1    | Power  |        | Dedicated function - to achieve low power during |                   | _                                                            |

| 7        | N⁄A       | PWR_CAP2    | Power  |        | sleep                                            |                   |                                                              |

| 8        | N⁄A       | PWR_CAP3    | Power  |        |                                                  |                   |                                                              |

| 9        | 0         | CLK_PIO     | Input  | -      | N.C.                                             | $\checkmark$      | -                                                            |

| 10       | 0         | UART2_INT   | Input  | High   | Ext UART2 interrupt                              | ~                 | External<br>interrupts,<br>page <u>21</u> .                  |

| 11       | 0         | UART1_INT   | Input  | High   | Ext UART1 interrupt                              | ✓                 | <u>External</u><br>interrupts,<br>page <u>21</u> .           |

| 12       | 0         | IDE_INT     | Input  | Ţ      | DoM interface interrupt                          | √                 | External<br>interrupts,<br>page <u>21</u> .                  |

| 13       | 0         | CLK_EXT     | Input  | N/A    | N.C.                                             | ✓                 | -                                                            |

| GP<br>No | Pio<br>Af | Signal name   | Dir    | Active   | Function                          | Wake-up<br>source | See section                                                                          |

|----------|-----------|---------------|--------|----------|-----------------------------------|-------------------|--------------------------------------------------------------------------------------|

| 14       | 0         | IRQ_CF#       | Input  | <b>_</b> | CF slot interrupt                 | ~                 | <u>External</u><br>interrupts,<br>page <u>21</u> .                                   |

| 15       | 2         | CS1/CS_UART   | Output | Low      | Chip select 1 – dual UART         | $\checkmark$      | <u>Serial UART</u><br>ports, page <u>35</u> .                                        |

| 16       | 2         | PWM0          | Output | N/A      | PWM0 output                       | 1                 | Pulse-Width<br>Modulation                                                            |

| 17       | 2         | PWM1          | Output | N/A      | PWM1 output                       | $\checkmark$      | <u>(PWM)</u> , page<br><u>37</u> .                                                   |

| 18       | 1         | SA_RDY/GPIO18 | Input  | Low      | RDY for bus expansion             |                   | Disk-on-Module/<br>IDE interface,<br>page <u>26</u> .                                |

| 19       | 0         | MMC/CF_EN     | Output | Low      | MMC/CF power enable               |                   | <u>CompactFlash,</u><br>page <u>28</u> .                                             |

| 20       | 0         | GPIO001       | I/O    | N/A      | Programmable GPIO                 |                   | Disk-on-Module/<br>IDE interface,                                                    |

| 21       | 0         | GPIO002       | I/O    | N/A      | Programmable GPIO                 |                   | page <u>26</u> .                                                                     |

| 22       | 0         | 33MHz_EN      | Output | Low      | Enables 33MHz oscillation for TPM |                   | <u>Atmel Trusted</u><br><u>Platform</u><br><u>Module (TPM)</u> ,<br>page <u>37</u> . |

| 23       | 0/2       | SSP_CLK       | Output | N/A      | GPIO/SSP clock                    |                   |                                                                                      |

| 24       | 0/2       | SSP_FRM       | Output | N/A      | GPIO/SSP frame                    |                   | Synchronous                                                                          |

| 25       | 0/2       | SSP_TXD       | Output | N/A      | GPIO/SSP transmit data            |                   | <u>Serial Protocol</u><br>(SSP) ports,                                               |

| 26       | 0/1       | SSP_RXD       | Input  | N/A      | GPIO/SSP received data            |                   | page <u>36</u> .                                                                     |

| 27       | 0/1       | SSP_EXTCLK    | Inout  | N/A      | GPIO/SSP external clock           |                   |                                                                                      |

| 28       | 1         | AC97_BITCLK   | Input  |          | AC'97 BIT CLOCK                   |                   |                                                                                      |

| 29       | 1         | AC97_DIN      | Input  | N/A      | AC'97 DATA IN                     |                   | Audio page 22                                                                        |

| 30       | 2         | AC97_DOUT     | Output | N/A      | AC'97 DATA OUT                    |                   | <u>Audio</u> , page <u>32</u> .                                                      |

| 31       | 2         | AC97_SYNC     | Output |          | AC'97 SYNC                        | $\checkmark$      |                                                                                      |

| 32       | 2         | MMCLK         | Output | N/A      | MMC/SD/SDIO clock                 |                   | Secure Digital<br>Input/Output<br>(SDIO), page<br>32.                                |

| GPI<br>No |   | Signal name | Dir    | Active | Function                         | Wake-up<br>source | See section                                                    |

|-----------|---|-------------|--------|--------|----------------------------------|-------------------|----------------------------------------------------------------|

| 33        | 2 | CS5/CS_IDE  | Output | Low    | Chip select 5 – DoM<br>interface |                   | Complex<br>Programmable<br>Logic Device<br>(CPLD), page<br>26. |

| 34        | 1 | FFRXD       | Input  | N/A    | FFUART receive data              | $\checkmark$      |                                                                |

| 35        | 1 | FFCTS       | Input  | N/A    | FFUART clear to send             | $\checkmark$      |                                                                |

| 36        | 1 | FFDCD       | Input  | N/A    | FFUART data carrier detect       | $\checkmark$      |                                                                |

| 37        | 1 | FFDSR       | Input  | N/A    | FFUART data sender ready         | $\checkmark$      | Serial UART                                                    |

| 38        | 1 | FFRI        | Input  | N/A    | FFUATR ring indicator            | $\checkmark$      | ports, page <u>35</u> .                                        |

| 39        | 2 | FFTXD       | Output | N/A    | FFUART transmit data             | $\checkmark$      |                                                                |

| 40        | 2 | FFDTR       | Output | N/A    | FFUART data terminal ready       | ✓                 |                                                                |

| 41        | 2 | FFRTS       | Output | N/A    | FFUART request to send           |                   |                                                                |

| 42        | 1 | BTRXD       | Input  | N/A    | BTUART receive data              |                   |                                                                |

| 43        | 2 | BTTXD       | Output | N/A    | BTUART transmit data             |                   | Serial UART                                                    |

| 44        | 1 | BTCTS       | Input  | N/A    | BTUART clear to send             |                   | ports, page <u>35</u> .                                        |

| 45        | 2 | BTRTS       | Output | N/A    | BTUART request to send           |                   |                                                                |

| 46        | 2 | STDRXD/PWM2 | Input  | N/A    | STUART receive data              |                   | Serial UART                                                    |

| 47        | 1 | STDTXD/PWM3 | Output | N/A    | STUART transmit data             |                   | ports, page <u>35</u> .                                        |

| 48        | 2 | CF_POE#     | Output | Low    | Card bus output enable           |                   |                                                                |

| 49        | 2 | CF_PWE#     | Output | Low    | Card bus write enable            |                   | CompactFlash,                                                  |

| 50        | 2 | CF_PIOR#    | Output | Low    | Card bus I/O read                |                   | page <u>28</u> .                                               |

| 51        | 2 | CF_PIOW#    | Output | Low    | Card bus I/O write               |                   |                                                                |

| 52        | 0 | N.C.        | Input  | N/A    | N.C.                             |                   | -                                                              |

| 53        | 0 | GPIO003     | I/O    | N/A    | Programmable GPIO                | ✓                 | Disk-on-Module/<br>IDE interface,<br>page <u>26</u> .          |

| 54        | 2 | CF_PCE2#    | Output | Low    | Card bus high byte enable        |                   |                                                                |

| 55        | 2 | CF_PREG#    | Output | Low    | Card bus register space select   |                   | CompactFlash,                                                  |

| 56        | 1 | CF_WAIT#    | Input  | Low    | Card bus WAIT#                   |                   | page <u>28</u> .                                               |

| 57        | 1 | CF_PIOCS16# | Input  | Low    | Card bus IOIS16#                 |                   |                                                                |

|           |   |             |        |        |                                  |                   |                                                                |

| GPIO<br>No AF | Signal name | Dir    | Active | Function               | Wake-up<br>source | See section                                                    |

|---------------|-------------|--------|--------|------------------------|-------------------|----------------------------------------------------------------|

| 58 2          | LCD_D0      | Output | N/A    | LCD data bit 0         |                   |                                                                |

| 59 2          | LCD_D1      | Output | N/A    | LCD data bit 1         |                   |                                                                |

| 60 2          | LCD_D2      | Output | N/A    | LCD data bit 2         |                   |                                                                |

| 61 2          | LCD_D3      | Output | N/A    | LCD data bit 3         |                   |                                                                |

| 62 2          | LCD_D4      | Output | N/A    | LCD data bit 4         |                   |                                                                |

| 63 2          | LCD_D5      | Output | N/A    | LCD data bit 5         |                   |                                                                |

| 64 2          | LCD_D6      | Output | N/A    | LCD data bit 6         |                   |                                                                |

| 65 2          | LCD_D7      | Output | N/A    | LCD data bit 7         |                   |                                                                |

| 66 2          | LCD_D8      | Output | N/A    | LCD data bit 8         |                   |                                                                |

| 67 2          | LCD_D9      | Output | N/A    | LCD data bit 9         |                   | <u>Flat panel</u><br><u>display</u> , page <u>29</u>           |

| 68 2          | LCD_D10     | Output | N/A    | LCD data bit 10        |                   |                                                                |

| 69 2          | LCD_D11     | Output | N/A    | LCD data bit 11        |                   |                                                                |

| 70 2          | LCD_D12     | Output | N/A    | LCD data bit 12        |                   |                                                                |

| 71 2          | LCD_D13     | Output | N/A    | LCD data bit 13        |                   |                                                                |

| 72 2          | LCD_D14     | Output | N/A    | LCD data bit 14        |                   |                                                                |

| 73 2          | LCD_D15     | Output | N/A    | LCD data bit 15        |                   |                                                                |

| 74 2          | LCD_FCLK    | Output | N/A    | LCD frame clock        |                   |                                                                |

| 75 2          | LCD_LCLK    | Output | N/A    | LCD line clock         |                   |                                                                |

| 76 2          | LCD_PCLK    | Output | N/A    | LCD pixel clock        |                   |                                                                |

| 77 2          | LCD_BIAS    | Output | N/A    | LCD bias               |                   |                                                                |

| 78 2          | CS2/GPIO78  | Output | Low    | Chip select 2          |                   | Complex<br>Programmable<br>Logic Device<br>(CPLD), page<br>26. |

| 79 1          | CF_PSKTSEL  | Output | Low    | Card bus socket select |                   | <u>CompactFlash,</u><br>page <u>28</u> .                       |

| GP<br>No | Pio<br>Af | Signal name | Dir    | Active | Function                                  | Wake-up<br>source | See section                                                            |

|----------|-----------|-------------|--------|--------|-------------------------------------------|-------------------|------------------------------------------------------------------------|

| 80       | 2         | CS4/GPIO80  | Output | Low    | Chip select 4                             |                   | Complex<br>Programmable<br>Logic Device<br>(CPLD),<br>page <u>26</u> . |

| 81       | 0(1)      | SSP3_TXD    | Output | N/A    | SSP transmit data                         |                   |                                                                        |

| 82       | 0(1)      | SSP3_RXD    | Input  | N/A    | SSP receive data                          |                   | <u>Synchronous</u><br>Serial Protocol                                  |

| 83       | 0(1)      | SSP3_FRM    | Output | Low    | SSP chip select                           | $\checkmark$      | <u>(SSP) ports,</u><br>page <u>36</u> .                                |

| 84       | 0(1)      | SSP3_CLK    | Output | N/A    | SSP clock                                 |                   |                                                                        |

| 85       | 1         | CF_PCE1#    | Output | Low    | Card bus low byte enable                  |                   | <u>CompactFlash,</u><br>page <u>28</u> .                               |

| 86       | 0         | MMC_WP      | Input  | High   | MMC write protect                         |                   | Secure Digital<br>Input/Output<br>(SDIO), page <u>32</u> .             |

| 87       | 0         | CF_CD1#     | Input  | Low    | CF card detect 1                          |                   | <u>CompactFlash,</u><br>page <u>28</u> .                               |

| 88       | 0/1       | USB_OC1#    | Input  | Ţ      | GPIO/USB port 1 over<br>current detection |                   | USB ports,                                                             |

| 89       | 0/2       | USB_PWE1    | Output | High   | GPIO/USB port 1 power enable              |                   | page <u>34</u> .                                                       |

| 90       | 0         | CF_RST      | Output | Low    | CF card RESET                             | ✓                 | CompactFlash,                                                          |

| 91       | 0         | CF_CD2#     | Input  | Low    | CF card detect 2                          | $\checkmark$      | page <u>28</u> .                                                       |

| 92       | 1         | MMDAT0      | Bidir. | N/A    | MMC/SD/SDIO data 0                        |                   | Secure Digital<br>Input/Output<br>(SDIO), page<br>32.                  |

| 93       | 0         | N.C.        | Input  | N/A    | N.C.                                      | $\checkmark$      | _                                                                      |

| 94       | 0         | N.C.        | Input  | N/A    | N.C.                                      | $\checkmark$      |                                                                        |

| 95       | 0         | MMC_DET     | Input  | High   | MMC/SD/SDIO card detect                   | ~                 | Secure Digital<br>Input/Output<br>(SDIO), page<br>32.                  |

| 96       | 0         | N.C.        | Input  | N/A    | N.C.                                      | ✓                 | -                                                                      |

| _        |           |             |        |        |                                           |                   |                                                                        |

| GP<br>No |   | Signal name | Dir    | Active | Function                    | Wake-up<br>source | See section                          |

|----------|---|-------------|--------|--------|-----------------------------|-------------------|--------------------------------------|

| 97       | 0 | JP1         | Input  | Low    | JP1 – flashing enable       | √                 | <u>Jumpers</u> , page<br><u>48</u> . |

| 98       | 0 | N.C.        | Input  | N/A    | N.C.                        | $\checkmark$      |                                      |

| 99       | 0 | GPIO10      | Input  | N/A    | Programmable GPIO           | $\checkmark$      |                                      |

| 100      | 0 | PWR_IDE     | Output | Low    | Enable DoM interface power  | $\checkmark$      |                                      |

| 101      | 0 | WD_EN       | Output | High   | WATCHDOG function enable    | • ✓               | -                                    |

| 102      | 0 | N.C.        | Input  | N/A    | N.C.                        | $\checkmark$      |                                      |

| 103      | 0 | WD_IN       | Output | N/A    | WATCHDOG refresh            |                   |                                      |

| 104      | 0 | N.C.        | Input  | N/A    | N.C.                        |                   |                                      |

| 105      | 0 | JMP_JP2     | Input  | N/A    | JP2 status                  |                   | <u>Jumpers</u> , page<br><u>48</u> . |

| 106      | 0 | N.C.        | Input  | N/A    | N.C.                        |                   |                                      |

| 107      | 0 | N.C.        | Input  | N/A    | N.C.                        |                   | -                                    |

| 108      | 0 | N.C.        | Input  | N/A    | N.C.                        |                   |                                      |

| 109      | 1 | MMDAT1      | I/O    | N/A    | MMC/SD/SDIO data 1          |                   |                                      |

| 110      | 1 | MMDAT2      | I/O    | N/A    | MMC/SD/SDIO data 2          |                   | Secure Digital<br>Input/Output       |

| 111      | 1 | MMDAT3      | I/O    | N/A    | MMC/SD/SDIO data 3          |                   | (SDIO), page<br><u>32</u>            |

| 112      | 1 | MMCMD       | I/O    | N/A    | MMC/SD/SDIO command         |                   |                                      |

| 113      | 2 | AC97_RST#   | Output | Low    | AC'97 reset                 | $\checkmark$      | Audio, page <u>32</u> .              |

| 114      | 0 | GPIO22      | Input  | N/A    | Programmable GPIO           |                   | -                                    |

| 115      | 0 | GPIO12      | Output | N/A    | Programmable GPIO           |                   | -                                    |

| 116      | 0 | USB_DET     | Input  | Low    | USB client device detection | $\checkmark$      | <u>USB</u> , page <u>34</u> .        |

| 117      | 1 | I2C_SCL     | Output | N/A    | l <sup>2</sup> C clock      |                   | l <sup>2</sup> C bus, page           |

| 118      | 1 | I2C _SDA    | I/O    | N/A    | l <sup>2</sup> C data       |                   | <u>36</u> .                          |

|          |   |             |        |        |                             |                   |                                      |

For details of pin states during sleep modes and reset, see the Pin Usage table in the Intel<sup>®</sup> PXA27x Processor Family Electrical, Mechanical, and Thermal Specification.

## Interrupt assignments

#### Internal interrupts

For details on the PXA270 interrupt controller and internal peripheral interrupts please see the *Intel<sup>®</sup> PXA270 developer's manual* on the development kit CD.

#### External interrupts

The following table lists the PXA270 signal pins used for external interrupts.

| PXA270 pin | Signal name | Peripheral                                              | Active     |

|------------|-------------|---------------------------------------------------------|------------|

| GPIO0      | AC97_IRQ    | On-board audio*                                         | _ <b>f</b> |

|            | RTC_IRQ     | On-board RTC*                                           | <b>_</b>   |

|            | DIMM_GPIO   | SO-DIMM socket*                                         | TBD        |

| GPIO1      | GPIO1       | Vdd_fault monostable                                    | <b>~</b> _ |

| GPIO10     | UART2_INT   | UART expander                                           |            |

| GPIO11     | UART1_INT   | UART expander                                           |            |

| GPIO12     | IDE_INT     | DoM interface**                                         | <b>_</b>   |

| GPIO14     | IRQ_CF#     | CF interface                                            | <b>_</b>   |

| GPIO87     | CF_CD1#     | Card detect 1***                                        | <b>_</b>   |

| GPIO91     | CF_CD2#     | Card detect 2***                                        | <b>_</b>   |

| GPIO95     | MMC_DET     | Indicates insertion/ejection of MMC/SD card****         |            |

| GPIO99     | GPIO10      | Universal GPIO                                          |            |

| GPIO116    | USB_DET     | Indicates connected/disconnected USB client device***** |            |

| GPIO20     | GPIO001     | Universal GPIO on IDE interface                         | TBD        |

\* GPIO0: Only one of three possible GPIO pin assignments is applicable, AC97\_IRQ is the default functionality (others are available using factory fitted resistors).

\*\* IDE\_INT: This interrupt is connected to 44 pin IDE header. When Disk-on-Module is used, it is an interrupt from the IDE interface. If the QUANTUM Ethernet module is used, this represents an interrupt from the Ethernet chip.

- \*\*\* CF\_CD1#, CF\_CD2#: If only one CF socket is active, the logical expression CF\_CD1# or CF\_CD2# indicates card insertion. If two sockets are active (e.g. IPS-100), CF\_CD1# can indicate Card 1 insertion and CF\_CD2# can indicate Card 2 insertion (log 0 – card is inserted).

- \*\*\*\* MMC\_DET: Log 1 indicates MMC/SD card insertion.

\*\*\*\*\* USB\_DET: Log 1 indicates connection of a USB client device.

### PXA270 processor

The QUANTUM board is based on an Intel<sup>®</sup> PXA270 XScale<sup>®</sup> processor, information on which can be found on the development kit CD.

The PXA270 processor is an integrated system-on-a-chip microprocessor for high-performance, low-power, portable, handheld and handset devices. It incorporates Intel XScale technology, with on-the-fly voltage, frequency scaling and sophisticated power management.

The PXA270 processor complies with the ARM Architecture V5TE instruction set (excluding floating point instructions) and follows the ARM programmer's model. The PXA270 processor also supports Intel Wireless MMX<sup>™</sup> integer instructions in applications such as those that accelerate audio and video processing.

The features of PXA270 processor include:

- Intel XScale core.

- Power management.

- Internal memory 256KB of on-chip RAM.

- Interrupt controller.

- Operating system timers.

- Pulse-Width Modulation unit (PWM).

- Real Time Clock (RTC)

- General Purpose I/O (GPIO).

- Memory controller.

- DMA controller.

- Serial ports:

- Three UARTs.

- Fast Infrared port.

- I<sup>2</sup>C bus port.

- AC'97 codec interface.

- I<sup>2</sup>S codec interface.

- USB host controller (two ports).

- USB client controller.

- Three Synchronous Serial Ports (SSP).

- LCD panel controller.

- Multimedia Card (MMC), SD memory card and SDIO card controller.

- Memory stick host controller.

- Mobile Scalable Link (MSL) interface.

- Keypad interface.

- Universal Subscriber Identity Module (USIM) interface.

- Quick capture camera interface.

- JTAG interface.

- 356 pin VF-BGA packaging.

The design supports 520, 416 and 312MHz speed variants of the Intel PXA270 processor. The standard variant of the QUANTUM board is fitted with a 312MHz version of the Intel<sup>®</sup> PXA270. A 13MHz external crystal is used to run the PXA270 processor; all other clocks are generated internally in the processor.

The Intel PXA270 processor family provides multimedia performance, low power capabilities, and rich peripheral integration. Designed for wireless clients, it incorporates the latest Intel advances in mobile technology over its predecessor, the Intel PXA255 processor. The Intel PXA270 processor features scalability by operating from 104MHz up to 520MHz, providing enough performance for the most demanding control and monitoring applications.

PXA270 is the first Intel Personal Internet Client Architecture (PCA) processor to include Intel Wireless MMX<sup>™</sup> technology, enabling high performance, low-power multimedia acceleration with a general purpose instruction set. Intel Quick Capture technology provides flexible and powerful camera interfacing for capturing digital images and video. Power consumption is also a critical component. Wireless Intel SpeedStep<sup>®</sup> technology provides these new capabilities in low-power operation.

The processor requires a number of power supply rails. All voltage levels are generated on-board from either the DC/DC PSU or from the single +3.3V power input. The QUANTUM uses specialised power management IC that supports Intel SpeedStep technology.

The PXA270 processor is a low-power device and does not require a heat sink for operating temperatures up to 85°C.

## Real Time Clock (RTC)

The QUANTUM uses an external RTC (Intersil ISL1208) to store the date and time and provide power management events. The RTC is connected to the  $I^2C$  bus of the PXA270 processor and is accessible through  $I^2C$  bus address 0x6F. It can be battery backed, if the backup battery is connected to pin 32 (+VBAT\_IN) of the SO-DIMM interface connector.

The accuracy of the RTC is based on the operation of the 32.768KHz watch crystal. The calibration tolerance is  $\pm$ 20ppm, which provides an accuracy of  $\pm$ 1 minute per month when the board is operated at an ambient temperature of +25°C. When the board is operated outside this temperature, the accuracy may be degraded by 0.035ppm/°C  $\pm$ 10% typical. The watch crystal's accuracy will age by  $\pm$ 3ppm maximum in the first year, then  $\pm$ 1ppm maximum in the year after, decreasing logarithmically in subsequent years.

The Intersil ISL1208 RTC provides the following basic functions:

- Real Time Clock/calendar:

- Tracks time in hours, minutes, and seconds.

- Includes day of the week, day, month, and year.

- Single alarm:

- Settable to the second, minute, hour, day of the week, day, or month.

- Single event or pulse interrupt mode.

- Two bytes of battery-backed user SRAM.

- I<sup>2</sup>C interface.

## Watchdog timer

The PXA270 processor has internal support for a watchdog timer. A 32-bit internal register is incremented on the rising edge of the internal 3.25MHz clock. On reaching the preset value, the output pin nRESET\_OUT is asserted; a reset is applied to the PXA270 processor and most internal states are cleared. The only way to clear this pin is with a reset function (hardware reset, sleep-exit reset, watchdog reset, or GPIO reset).

The internal watchdog timer can be used to protect against erroneous software. Timeout periods can be adjusted from 307ns to around 22 minutes. When a timeout occurs the entire board is reset. On reset, the watchdog timer is disabled until it is enabled again by the software.

In addition, an external WD timer is included on the QUANTUM. This external watchdog is not a part of the standard QUANTUM configuration: contact Eurotech Ltd for availability (for full contact details, please see <u>Appendix A – Contacting Eurotech</u> <u>Ltd</u>, page <u>55</u>). TPS3828 is used as a reset monitor with watchdog function.

If an external WD timer is used, WD\_EN(GPIO101)=log 1 activates watchdog functionality and WD\_N(GPIO103) is used for WD refresh.

For further details, see the Eurotech Ltd operating system technical manual and the *Intel<sup>®</sup> developer's manual* on the development kit CD.

## Memory

The QUANTUM has three types of memory fitted:

- 1, 16, 32 or 64MB resident FlashDisk containing:

- Bootloader to boot operating system.

- Operating system (except 1MB size).

- Application images.

- 64(32)MB of SDRAM for system memory.

- Static RAM: 256KB of SRAM internal to the PXA270.

#### Flash memory/silicon disk

The QUANTUM supports two basic concepts of Flash memory configuration:

- Small capacity FlashDisk (1MB Spansion Flash memory).

- High capacity FlashDisk (16/32/64MB MirrorBit Flash Spansion memory).

The Flash memory is arranged as 16Mbit x 16-bit (32MB device) or as 32Mbit x 16-bit (64MB device).

The Flash memory array is divided into equally-sized symmetrical blocks that are 64-Kword in size (128 KB) sectors. A 256Mbit device contains 256 blocks, and a 512Mbit device contains 512 blocks.

#### SDRAM

QUANTUM is designed for use with one 512/256 MBit SDRAM chip (64/32MB). SAMSUNG K4M513233C is assembled as a standard. The 512MBit is configured as 16M x 32-bit, and the 256MBit as 8M x 32-bit.

The SDRAM memory controller is set to run at a frequency of 104MHz.

#### Static RAM

The PXA270 processor provides 256KB of internal memory-mapped SRAM. The SRAM is divided into four banks, each consisting of 64KB.

## Bus extension interfaces

There are several extension interfaces on the QUANTUM, which are interconnected to the main SO-DIMM interface or the on-board Disk-on-Module/IDE interface. These interfaces are controlled by the Xilinx CPLD device.

They are the:

- Static memory bus extension interface.

- CompactFlash interface.

- Disk-on-Module/QUANTUM Ethernet module interface.

#### Complex Programmable Logic Device (CPLD)

The Xilinx device XC9536XL-7CSG48I is used for control logic for the IDE interface, the QUANTUM Ethernet module bus interface and the CompactFlash interface. Depending on which module is connected to the Disk-On-Module interface, jumper JP2 has to be set (see <u>JP2 – User jumper (Disk-On-Module interface functionality)</u>, page <u>48</u>). The status of JP2 can be also read on GPIO105 of PXA270.

#### Static memory bus extension

The memory controller of the PXA270 processor supports three different memory spaces: SDRAM, static memory, and PC card space. The SDRAM has four partitions, the static memory has six partitions, and the PC card space has two partitions (or sockets).

The static memory interface is used for connecting Flash, UARTs, IDE interfaces and bus extensions. As a result of this, two CS signals (NCS2 and NCS4) are connected to the SO-DIMM pins. The static memory space bus extension is available via the D0-D15 data pins and the SA0-SA10 and SA21 address pins. Pin 89 of the SO-DIMM interface (PXa270 GPIO114) can be used as an interrupt signal from the bus extension interface.

#### Disk-on-Module/IDE interface

The 44 pin IDE connector is designed for connecting a 3.3V Disk-on-Module device (for a signal description, see J2 - IDE/bus extension connector, page 54). The IDE interface is implemented in static memory space (via NCS5) glue to logic in CPLD and it is addressed by signal CS5 and A21, A22 address pins. The same connector is designed for the QUANTUM Ethernet Module (QEM) also. It is the HW configurable option (see JP2 - User jumper (Disk-On-Module interface functionality), page 48).

Because Disk-on-Module devices and the Quantum Ethernet module (QEM) have a power consumption of only 1-10mA, in low power modes, there is a power supply switch included to switch off the 3.3V supply to the Disk-On-Module interface. It is controlled by GPIO100:

| GPIO100 level | 3.3V IDE supply |  |

|---------------|-----------------|--|

| Low           | Enable          |  |

| High          | Disable (OFF)   |  |

The addressing of the Disk-on-Module device is as follows:

| Address range (A21,A22)        | Region name                                               |  |

|--------------------------------|-----------------------------------------------------------|--|

| 0x14400000<br>(MA21=0, MA22=1) | First set of registers (addressed by A1,A2,A3) – IDE_CS0  |  |

| 0x14200000<br>(MA21=1, MA22=0) | Second set of registers (addressed by A1,A2,A3) – IDE_CS1 |  |

The interface supports the following signals:

| Signal name        | Description                               |

|--------------------|-------------------------------------------|

| NRESET#            | IDE/QEM reset signal                      |

| SA_D0 – SA_D15     | 16-bit data bus                           |

| SA_A1-SA_A4, SA_21 | Selected address bus signals              |

| IDEIOW#(nPWE/nWR)  | IOW# for IDE or nWR for QEM               |

| IDEIOR#(nOE)       | IOR# for IDE or nOE for QEM               |

| IDE_IRQ(IRQ)       | Interrupt form IDE/QEM                    |

| IDECSO#(CS1)       | IDE_CS0 for IDE or CS for QEM             |

| CS3FX#(CS2)        | IDE_CS1 for IDE                           |

| SA_RDY#_GPIO18     | Data RDY for IDE                          |

| GPIO001            | Not used for IDE or button status for QEM |

| GPIO002            | Not used for IDE or LED1 for QEM          |

| GPIO003            | Not used for IDE or LED2 for QEM          |

### QUANTUM Ethernet Module (QEM)

The QEM was designed for debugging and developing purposes, but can be used generally as well. Because QEM is plugged into J2, you cannot use it at the same time as the Disk-on-Module.

There is one difference between the mapping of the Disk-on-Module device and that of the QEM: while the IDE device is mapped into CS5 memory space, QEM is mapped into CS4 memory space (it is addressed by the address signal lines A1 and A21), but both devices use the same interrupt signal. Address line A21 selects whether the DoM Ethernet chip or secondary Ethernet (connected via SO-DIMM bus interface, e.g. QUANTUM Base Board V2) is selected (by CPLD).

The addressing of the DM9000A QEM Ethernet chip is as follows:

| Address (addressed by A1, A21=0) | Region name               |

|----------------------------------|---------------------------|

| 0x1000000                        | DM9000A device INDEX port |

| 0x10000002                       | DM9000A device DATA port  |

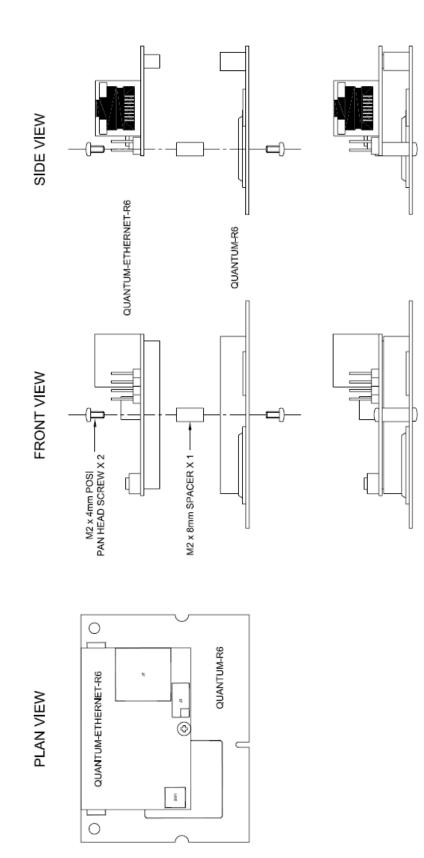

Correct placement of the QEM on the QUANTUM is illustrated below:

#### CompactFlash

A CompactFlash extension interface for full I/O mode operation is provided using slot 0 (and slot 1 optionally) of the PXA270 PC card controller, and supports type I and II CF+ cards. It appears in PC card memory space socket 0.

| Address                 | Region name                      |

|-------------------------|----------------------------------|

| 0x20000000 – 0x23FFFFFF | Socket 0 I/O space.              |

| 0x24000000 – 0x27FFFFFF | Reserved.                        |

| 0x28000000 – 0x2BFFFFFF | Socket 0 attribute memory space. |

| 0x2C000000 – 0x2FFFFFFF | Socket 0 common memory space.    |

| 0x30000000 – 0x33FFFFFF | Socket 1 I/O space.              |

| 0x34000000 – 0x37FFFFFF | Reserved.                        |

| Address                 | Region name                      |

|-------------------------|----------------------------------|

| 0x38000000 – 0x3BFFFFFF | Socket 1 attribute memory space. |

| 0x3C000000 – 0x3FFFFFFF | Socket 1 common memory space.    |

As a default configuration, only one CF socket (slot 0) is supported. This is a hot-swappable 3.3V interface. The external power switch can be controlled by the MMC/CF\_EN signal. The card insertion is detected by the zero level on pins CF\_CD1# and CF\_CD2#. The CompactFlash interrupt signal (IRQ\_CF#) is on PXA270 pin GPIO14.

If the application requires two CF slots (e.g. a IPS-100 board), the second CF slot uses the PXA270 GPIO 27 signal as an interrupt pin, in case the SSP port doesn't support external clocking for the SPP interface. CF slots don't support power control (because the MMC/CF\_EN signal, GPIO19, is used for CF2 RESET functionality) and CF\_CD2# is used as a CF2 card insert detection (CF1 uses CD\_CF1# only in this case, instead of both CD\_CF1# and CD\_CF2#, when only one CF socket is used).

Many CF+ cards require a reset once they have been inserted. Resetting the CompactFlash interface is possible by low level on the CF\_RST(GPIO90) pin – CF Slot 0 -or GPIO19 (if two CF slots are used).

CF+ is a small form factor card standard. It encompasses CompactFlash (CF) data storage cards; magnetic disk cards and I/O cards (including serial cards); Ethernet cards and fax/modem cards; digital phone cards; USB devices; barcode scanners; Bluetooth<sup>®</sup>; IEEE802.11b (WiFi); wireless digital cell phone cards etc. For more details about CF+ standards and the availability of particular CF+ peripherals, visit the website www.compactflash.org.

The CF+ card provides high capacity data storage and I/O functions that comply with the Personal Computer Memory Card International Association (PCMCIA) standard.

Except standard PXA270 CF-interface signals, there is a designed signal PADDREN, generated by CPLD. This can be used (on external board) to address buffers enable.

## Flat panel display

The Intel PXA270 processor contains an integrated LCD display controller. It is capable of supporting both colour and monochrome single and dual-scan display modules. It supports active (TFT) and passive (STN) LCD displays from 1x1 to 800x600 pixels.

The PXA270 can drive displays with a resolution up to 800x600, but as the PXA270 has a unified memory structure, the bandwidth to the application decreases significantly. If the application makes significant use of memory - such as when video is on-screen - you may also experience FIFO under-runs, causing the frame rates to drop or display image disruption. Reducing the frame rate to the slowest speed possible gives the maximum bandwidth to the application. The display quality for an 800x600 resolution LCD is dependent on the compromises that can be made between the LCD refresh rate and the application. The PXA270 is optimised for 640x480 display resolution.

A full explanation of the graphics controller operation can be found in the *PXA270 developer's manual* included on the support CD.

The flat panel data and control signals are routed to the board interface connector J1. See the section J1 - Module Interface Connector, page <u>49</u>, for pin assignments.

The following tables provide a cross-reference between the flat panel data signals and their function when configured for different displays.

| Panel data bus bit | 18-bit TFT | 12-bit TFT | 9-bit TFT |

|--------------------|------------|------------|-----------|

| LCD_15             | R5         | R3         | R2        |

| LCD_14             | R4         | R2         | R1        |

| LCD_13             | R3         | R1         | R0        |

| LCD_12             | R2         | R0         | -         |

| LCD_11             | R1         | -          | -         |

| GND                | R0         | -          | -         |

| LCD_10             | G5         | G3         | G2        |

| LCD_9              | G4         | G2         | G1        |

| LCD_8              | G3         | G1         | G0        |

| LCD_7              | G2         | G0         | -         |

| LCD_6              | G1         | -          | -         |

| LCD_5              | G0         | -          | -         |

| LCD_4              | B5         | В3         | B2        |

| LCD_3              | B4         | B2         | B1        |

| LCD_2              | B3         | B1         | B0        |

| LCD_1              | B2         | В0         | -         |

| LCD_0              | B1         | -          | -         |

| GND                | B0         | -          | -         |

#### TFT panel data bit mapping to the QUANTUM

The PXA270 can directly interface with 18-bit displays, but from a performance point of view it is better to use 16 bits only. 18-bit operation requires twice the bandwidth of 16-bit operation.

| Panel data bus bit | Dual scan colour STN | Single scan colour STN | Dual scan mono STN |

|--------------------|----------------------|------------------------|--------------------|

| LCD_15             | DL7(G)               | -                      | -                  |

| LCD_14             | DL6(R)               | -                      | -                  |

| LCD_13             | DL5(B)               | -                      | -                  |

| LCD_12             | DL4(G)               | -                      | -                  |

| LCD_11             | DL3(R)               | -                      | -                  |

| LCD_10             | DL2(B)               | -                      | -                  |

| LCD_9              | DL1(G)               | -                      | -                  |

| LCD_8              | DL0(R)               | -                      | -                  |

| LCD_7              | DU7(G)               | D7(G)                  | DL3                |

| LCD_6              | DU6(R)               | D6(R)                  | DL2                |

| LCD_5              | DU5(B)               | D5(B)                  | DL1                |

| LCD_4              | DU4(G)               | D4(G)                  | DL0                |

| LCD_3              | DU3(R)               | D3(R)                  | DU3                |

| LCD_2              | DU2(B)               | D2(B)                  | DU2                |

| LCD_1              | DU1(G)               | D1(G)                  | DU1                |

| LCD_0              | DU0(R)               | D0(R)                  | DU0                |

### STN panel data bit mapping to the QUANTUM

Below is a table covering the clock signals required for passive and active type displays:

| QUANTUM  | Active display signal (TFT) | Passive display signal (STN) |

|----------|-----------------------------|------------------------------|

| LCD_PCLK | Clock                       | Pixel clock                  |

| LCD_LCLK | Horizontal sync             | Line clock                   |

| LCD_FCLK | Vertical sync               | Frame clock                  |

| LCD_BIAS | DE (Data Enable)            | Bias                         |

The display signals are +3.3V compatible. The QUANTUM doesn't contain power control circuitry for the flat panel logic supply and backlight supply.

## Secure Digital Input/Output (SDIO)

The SDIO interface is connected directly from PXA270's MMC/SD/SDIO controller to the SO-DIMM interface. It consists of 4/1 (MMDAT0-MMDAT3) data, one clock (MMCLK) and one command (MMCMD) line.

The MMC/SD/SDIO controller supports MultiMedia Cards (MMC), Secure Digital (SD) and Secure Digital I/O (SDIO) communications protocols. The MMC controller supports the MMC system, a low-cost data storage and communications system. The MMC controller in the PXA270 processor is based on the standards outlined in the *Multimedia Card System Specification Version 3.2*. The SD controller supports one SD or SDIO card based on the standards outlined in the *SD Memory Card Specification Version 1.01* and *SDIO Card Specification Version 1.0 (Draft 4)*.

The MMC/SD/SDIO controller features:

- Data-transfer rates of up to 19.5Mbps for MMC, 1-bit SD/SDIO, and SPI mode data transfers.

- Data-transfer rates of up to 78Mbps for 4-bit SD/SDIO data transfers.

- Support for all valid MMC and SD/SDIO protocol data-transfer modes.

This is a hot-swappable 3.3V interface, controlled by the detection of an inserted card (falling edge on MMC\_DET-GPIO95 when a SD card has been inserted, and a rising edge when a SD card is removed).

SD card write-protection is connected to PXA270's MMC\_WP-GPIO86 signal.

A variety of SDIO cards are available, such as Bluetooth<sup>®</sup> and IEEE802.11b (WiFi). More information can be found at <u>www.sdcard.org/about/sdio</u>.

### Audio

A Wolfson WM9712L AC'97 audio codec is used to support the audio features of the QUANTUM. Audio inputs supported by the WM9712L are a stereo Line In and a mono microphone input.

The following analogue signals are on the QUANTUM interface:

| Function   | Interface pin | Signal                 | Signal levels (max) | Frequency<br>response (Hz) |

|------------|---------------|------------------------|---------------------|----------------------------|

| Microphone | 60            | MIC input              | 1Vrms               | 20 – 20K                   |

| Line In    | 56            | Line input left        | 1Vrms               | 20 – 20K                   |

|            | 58.           | Line input right       | TVIIIS              |                            |

| Line Out   | 52            | Line output left       | 1Vrms               | 20 – 20K                   |

| Line Out   | 54            | Line output right      | TVIIIIS             | 20 – 20K                   |

|            | 62            | Audio ground reference |                     |                            |

|            |               |                        |                     |                            |

In the EuroTech-compatible version (variants 01, 03 and 06, Wolfson WM9712 is not fitted), the wires used for analogue signals in the previous table are used for AC'97 bus connectivity to the SO-DIMM interface. Factory-fitted resistors are used for this purpose.

## **Touchscreen controller**

The QUANTUM supports 4-wire analogue resistive touchscreens, using the touchscreen controller available on the Wolfson WM9712L audio codec. The touchscreen controller supports the following functions:

- X co-ordinate measurement.

- Y co-ordinate measurement.

- Pen down detection with programmable sensitivity.

- Touch pressure measurement.

The touchscreen can be used as a wake-up source for PXA270 from sleep mode.

The touchscreen interface is broken out on the SO-DIMM interface J1. For details see J1 - Module interface connector, page <u>49</u>.

The following signals are used for touchscreens on the QUANTUM interface:

| Interface pin | Signal    | Alternative functionality |

|---------------|-----------|---------------------------|

| 64            | PWM0/TPX+ | PWM0 output.              |

| 66            | PWM1/TPX- | PWM1 output.              |

| 93            | TPY+      | USB host 2 - USB_DR2+.    |

| 95            | TPY-      | USB host 2 - USB_DR2      |

For variants of the QUANTUM module without on-board AC'97 codec (variants 01 and 03), these signals have an alternative functionality. Use of these alternative functions is dependent on the factory-fitted resistors.

## USB ports

There are two USB host interfaces available on the QUANTUM. These comply with the Universal Serial Bus Specification Rev. 1.1, supporting data transfer at full-speed (12Mbit/s) and low-speed (1.5Mbit/s).

There is no power management circuitry implemented on QUANTUM. USB power control switches must be implemented on the Base Board to control the power and protect against short-circuit conditions.

The USB port 2 can be configured as a client port internally within the PXA270 USB controller, or alternatively can be connected to SO-DIMM interface J1.

Below is a table covering the USB port 2 signals assignment to the SO-DIMM interface:

| PXA270 signal | SO-DIMM interface pin no. | USB port 2 mode |  |

|---------------|---------------------------|-----------------|--|

| USB_DR2+      | 93                        |                 |  |

| USB_DR2-      | 95                        | USB host        |  |

| USB_DR2+      | 3                         |                 |  |

| USB_DR2-      | 5                         | USB client      |  |

More information about the USB bus and the availability of particular USB peripherals can be found at the website <u>www.usb.org.</u>

The mode of the USB 2 channel is depend on factory-fitted resistors, and can't be changed by software configuration only. The default is client mode.

## Serial UART ports

The PXA270 processor has three UARTs:

- Full-function (FFUART).

- Bluetooth<sup>®</sup> (BTUART).

- Standard (STUART).

These UARTs use the 16550 programming model. The transmit and receive buffers are 64 bytes deep. Each serial port contains a UART, and a slow infrared transmit encoder and receive decoder that conforms to the IrDA serial infrared specification.

FFUART supports full modem-control capability; the maximum baud rate is 921.6Kbaud.

STUART does not support modem control capability; the maximum baud rate is 921.6Kbaud.

BTUART is a high-speed UART that supports baud rates of up to 921.6Kbaud. It supports only two modem control pins (CTS# and RTS#).

Further information can be found in the *Intel<sup>®</sup> developer's manual*, available on the development kit CD .

In addition to these three serial ports, an external dual UART controller device is included on QUANTUM to provide two additional 16C550 compatible serial ports (the Exar XR16V2752: product information is available at <u>www.exar.com/product.php?</u> <u>ProdNumber=XR16V2752&arealD=3</u>). The UART controller uses a 14.7456MHz clock input and will support data rates up to 921.6Kbaud. It supports only two modem control signals: CTS# and RTS#. It also supports automatic RS485 half-duplex direction control output via RTS#. The UART device is connected to the memory controller interface of PXA270.

| Port      | Address                 | IRQ    | FIFO Rx/Tx | Signals                                  |

|-----------|-------------------------|--------|------------|------------------------------------------|

| Ext UART1 | 0x04000010 - 0x0400001E | GPIO11 | 64/64      | EXT1_RXD,EXT1_TXD,<br>EXT1_CTS, EXT1_RTS |

| Ext UART2 | 0x04000000 – 0x0400000E | GPIO10 | 64/64      | EXT2_RXD,EXT2_TXD,<br>EXT2_CTS, EXT2_RTS |

The first channel of the dual UART, Ext UART1, is connected directly to the SO-DIMM interface. The second channel, Ext UART2 has signal lines shared with the SSP3 synchronous serial port.

The standard version of QUANTUM uses signals 14, 16, 18, and 20 of SO-DIMM as a fifth serial port. To enable the use of the SSP3 interface (a factory-fitted option) contact Eurotech Ltd (see <u>Appendix A – Contacting</u> <u>Eurotech Ltd</u>, page <u>55</u>, for details).

## Synchronous Serial Protocol (SSP) ports

There are two SSP (Synchronous Serial Protocol) ports on QUANTUM. These interfaces connect to a variety of external analogue-to-digital (A/D) converters; audio and telecommunication codecs; and many other devices that use serial protocols for data transfer. The SSP ports provide support for the following protocols:

- Texas Instruments (TI) Synchronous Serial Protocol (SSP).

- Motorola Serial Peripheral Interface (SPI) protocol.

- National Semiconductor Microwire.

- Programmable Serial Protocol (PSP).

The SSP ports operate as full-duplex devices for the SPI, PSP and TI Synchronous Serial protocols, and as a half-duplex device for the Microwire protocol.

The SSP1 is a 5-wire bus and has dedicated pins on the SO-DIMM interface (see the section J1 - Module interface connector, page <u>49</u>, for pin assignments). The SSP3 is a 4-wire bus (which doesn't include EXT\_CLK support), and has a pin shared with the Ext UART2 serial port (see the section <u>Serial UART ports</u>, page <u>35</u>, for details).

## I<sup>2</sup>C bus

There are two I<sup>2</sup>C buses on the PXA270: a standard I<sup>2</sup>C bus and a secondary I<sup>2</sup>C bus, dedicated for the power management control. There are two devices on the QUANTUM board, connected to the main I<sup>2</sup>C bus; an RTC ISL1208 and an AT97SC3203S TPM chip (optional: contact Eurotech Ltd for availability – see <u>Appendix A – Contacting Eurotech Ltd</u>, page <u>55</u>). A standard PXA270 I<sup>2</sup>C interface is connected to the SO-DIMM interface as well, see the table below:

| Bus                           | Signal name | SO-DIMM pin no. |

|-------------------------------|-------------|-----------------|

| Standard I <sup>2</sup> C bus | I2C_SDA     | 25              |

|                               | I2C_SCL     | 23              |