# Capacitance-Digital-Converter LSI for Electrostatic Capacitive Touch Sensors Evaluation Board User's Manual

ON Semiconductor®

http://onsemi.com

## **EVAL BOARD USER'S MANUAL**

#### Introduction

This manual contains configuration, usage and main specifications regarding Electrostatic Capacitive Touch Sensor Evaluation Board (LC717A10ARGPGEVB).

For the latest edition of this manual, please refer to ON Semiconductor homepage. (http://www.onsemi.com)

### **Product Outline**

This product is a board to have you evaluate touch sensor LSI "LC717A10AR". Because it is 600 mil width DIP shape, it is a board which it is easy to use. So it can be performed easily to evaluate one's own switch pattern.

To evaluate it, it is necessary to have an USB-to-Serial conversion module for SPI communication, the PC to operate evaluation software and any board which designed the switch pattern.

- Electrostatic Capacitive Touch Sensor Evaluation Board LC717A10ARGPGEVB

- Accessory Connector Pin (8pin)

#### **EVALUATION BOARD**

#### LC717A10ARGPGEVB Evaluation Board Outline

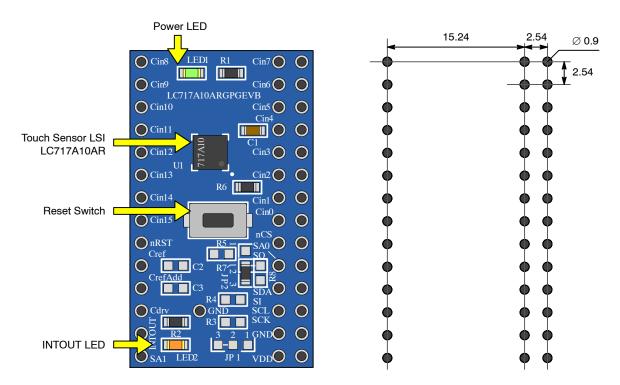

Figure 1. Configuration of LC717A10ARGPGEVB

- Touch Sensor LSI:

Electrostatic Capacitive Touch Sensor LSI LC717A10AR

- Power LED:

When a power is supplied, it turns on. Power supply voltage is 2.6 to 5.5 V.

- Reset Switch:

This is used to RESET Touch Sensor LSI. Use this switch if any abnormality is found during operation.

- *INTOUT LED:* When the INTOUT signal outputs, it turns on.

## **Evaluation Board Specifications**

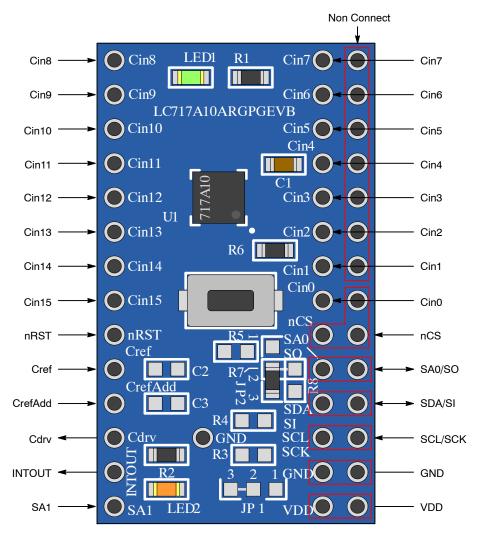

Figure 2. Terminal Pin Layout

**Table 1. SIGNAL PIN FUNCTIONS**

| Pin Name | I/O | Pin Functions                                                                       |  |  |

|----------|-----|-------------------------------------------------------------------------------------|--|--|

| Cin0     | I/O | Capacitance Sensor Input                                                            |  |  |

| Cin1     | I/O | Capacitance Sensor Input                                                            |  |  |

| Cin2     | I/O | Capacitance Sensor Input                                                            |  |  |

| Cin3     | I/O | Capacitance Sensor Input                                                            |  |  |

| Cin4     | I/O | Capacitance Sensor Input                                                            |  |  |

| Cin5     | I/O | Capacitance Sensor Input                                                            |  |  |

| Cin6     | I/O | Capacitance Sensor Input                                                            |  |  |

| Cin7     | I/O | Capacitance Sensor Input                                                            |  |  |

| Cin8     | I/O | Capacitance Sensor Input                                                            |  |  |

| Cin9     | I/O | Capacitance Sensor Input                                                            |  |  |

| Cin10    | I/O | Capacitance Sensor Input                                                            |  |  |

| Cin11    | I/O | Capacitance Sensor Input                                                            |  |  |

| Cin12    | I/O | Capacitance Sensor Input                                                            |  |  |

| Cin13    | I/O | Capacitance Sensor Input                                                            |  |  |

| Cin14    | I/O | Capacitance Sensor Input                                                            |  |  |

| Cin15    | I/O | Capacitance Sensor Input                                                            |  |  |

| Cref     | I/O | Reference Capacitance Input                                                         |  |  |

| CrefAdd  | I/O | Reference Capacitance Input for Addition                                            |  |  |

| Cdrv     | 0   | Output for Capacitance Sensors Drive                                                |  |  |

| INTOUT   | 0   | Interrupt Output                                                                    |  |  |

| SCL/SCK  | I   | Clock Input (I <sup>2</sup> C)/Clock Input (SPI)                                    |  |  |

| nCS      | I   | Interface Selection/Chip Select Inverting Input (SPI)                               |  |  |

| nRST     | I   | External Reset Signal Inverting Input (2.2 kΩ Pull-up, with Switch)                 |  |  |

| SA1      | I   | Slave Address Selection (I <sup>2</sup> C)                                          |  |  |

| SDA/SI   | I/O | Data Input and Output (I <sup>2</sup> C)/Data Input (SPI)                           |  |  |

| SA0/SO   | I/O | Slave Address Selection (I <sup>2</sup> C)/Data Output (SPI) (JP2 100 kΩ Pull-down) |  |  |

| VDD      | -   | Power Supply (2.6 V to 5.5 V). It is Connected to V <sub>DD</sub> of LC717A10AR     |  |  |

| GND      | _   | Ground (Earth). It is Connected to V <sub>SS</sub> of LC717A10AR                    |  |  |

# **Table 2. MAIN SPECIFICATIONS**

| Parameter                   | Conditions         | Remarks                                                               |

|-----------------------------|--------------------|-----------------------------------------------------------------------|

| Board Size                  | 35.56 × 20.32 (mm) |                                                                       |

| Board Material              | Glass Epoxy (FR4)  | Copper Foil: 35 µm, Thickness: 1.6 mm, 2-layer Board                  |

| Supply Voltage              | 2.6 to 5.5 V       |                                                                       |

| Capacitance Touch Sensor    | LC717A10AR         |                                                                       |

| Communication Specification | SPI                | It can be change to I <sup>2</sup> C Compatible Bus by Parts Exchange |

**Table 3. JUMPER, PATTERN FOR ADDITIONAL PARTS**

| Pattern | Parameter                                                                           | Set Contents                                                                                                                                                                                                                                                                                                      |  |  |

|---------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| C2      | Pattern for Cref Capacity Adjustment                                                | Implement capacitor of any capacity as needed. (Size: 1608)                                                                                                                                                                                                                                                       |  |  |

| С3      | Pattern for CrefAdd Capacity<br>Adjustment                                          | Implement capacitor of any capacity as needed. (Size: 1608)                                                                                                                                                                                                                                                       |  |  |

| R3      | Pattern for SCL Pull-up                                                             | When I $^2$ C compatible bus is chosen by nCS, implement a resistance of 2.2 k $\Omega$ . (Size: 1608) (Pull-up VDD)                                                                                                                                                                                              |  |  |

| R4      | Pattern for SDA Pull-up                                                             | When I <sup>2</sup> C compatible bus is chosen by nCS, implement a resistance of 2.2 k $\Omega$ . (Size: 1608) (Pull-up VDD)                                                                                                                                                                                      |  |  |

| R5      | Pattern for nCS Pull-up                                                             | When I²C compatible bus is chosen by nCS, implement a resistance of 2.2 k $\Omega$ . (Size: 1608) (Pull-up VDD)                                                                                                                                                                                                   |  |  |

| R7      | Reserve Pattern                                                                     | (R7 Initialization: Short) (Size: 1608)                                                                                                                                                                                                                                                                           |  |  |

| R8      | Reserve Pattern                                                                     | (R8 Initialization: Open) (Size: 1608)                                                                                                                                                                                                                                                                            |  |  |

| JP1     | Pattern for I <sup>2</sup> C Compatible Bus Slave<br>Address Selection              | When I <sup>2</sup> C compatible bus is chosen by nCS, set the I <sup>2</sup> C compatible bus slave address by JP1 and JP2. When SPI is chosen, connect to the ground. (JP1 Initialization: Ground Short)  1–2 Short: H Level 2–3 Short: L Level                                                                 |  |  |

| JP2     | Pattern for I <sup>2</sup> C Compatible Bus Slave<br>Address Selection/SO Pull-down | When I <sup>2</sup> C compatible bus is chosen by nCS, set the I <sup>2</sup> C compatible bus slave address by JP1 and JP2. When SPI is chosen, implement a resistance of 100 k $\Omega$ between 2 to 3. (It has been implemented.) (JP2 Initialization: Ground Pull-down) 1–2 Short: H Level 2–3 Short: L Level |  |  |

#### Table 4. LC717A10AR I2C COMPATIBLE BUS SLAVE ADDRESS

| SA1 Input<br>(JP1) | SA0 Input<br>(JP2) | 7bit Slave Address | Binary Notation   | 8bit Slave Address |

|--------------------|--------------------|--------------------|-------------------|--------------------|

| Low                | Low                | 0x16               | 00101100b (Write) | 0x2C               |

|                    |                    |                    | 00101101b (Read)  | 0x2D               |

| Low                | High               | 0x17               | 00101110b (Write) | 0x2E               |

|                    |                    |                    | 00101111b (Read)  | 0x2F               |

| High               | Low                | 0x18               | 00110000b (Write) | 0x30               |

|                    |                    |                    | 00110001b (Read)  | 0x31               |

| High               | High               | 0x19               | 00110010b (Write) | 0x32               |

|                    |                    |                    | 00110011b (Read)  | 0x33               |

## **HOW TO USE**

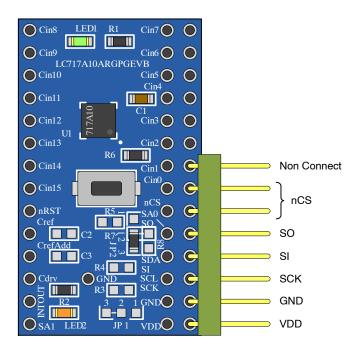

- 1. Connection of connector pin.

Solder attached connector pin (8pin) at the position of the Figure 3.

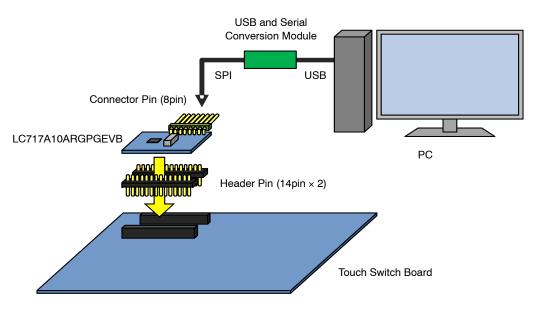

- 2. Connect LC717A10ARGPGEVB to the board which designed the switch pattern.

When design the switch pattern, please refer to the User's manual and FAQ pages in "http://www.sanyosemi.com/en/touch-sensor/index.php".

- 3. Connect LC717A10ARGPGEVB to PC through an USB-to-Serial conversion module. Supply the power, and verify the Power LED is turned on.

- 4. Install evaluation software to PC. Evaluation software is able to download from "http://www.sanyosemi.com/en/touch-sensor/index.php". Double-click to the icon "LC717A10App.exe" in the folder installed, and start it. Please refer to "LC717A10 demo application soft user's manual".

- 5. Press RESET Switch when evaluation board is acting strange.

- 6. Please note: If the user directly touches the LSI on the evaluation board or patterns with their finger, it may cause malfunction or breakdown.

Figure 3. Connection of Connector Pin

(Other than LC717A10ARGPGEVB and Connector Pin (8pin) are not Attached.)

Figure 4. Connection Example of LC717A10ARGPGEVB

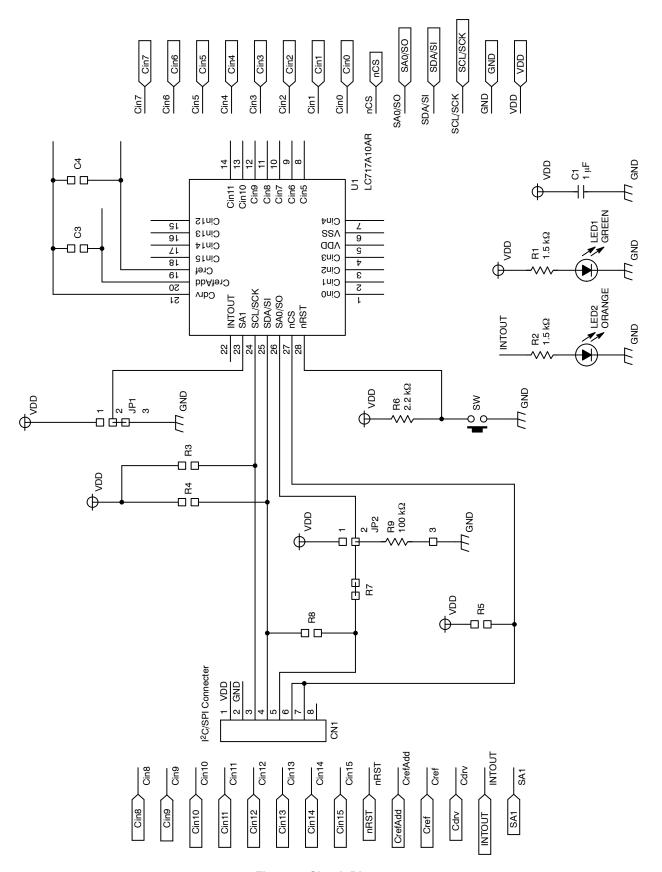

# **CIRCUIT DIAGRAMS**

Figure 5. Circuit Diagrams

#### PRECAUTION FOR USE

For approach in the use of LSI and the design rule of the switch pattern: Please refer to the User's manual and FAQ pages in ON Semiconductor homepage.

Touch sensor introduction page URL <a href="http://www.sanyosemi.com/en/touch-sensor/index.php">http://www.sanyosemi.com/en/touch-sensor/index.php</a>

I<sup>2</sup>C is a trademark of Philips

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. SCILLC solutions or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative