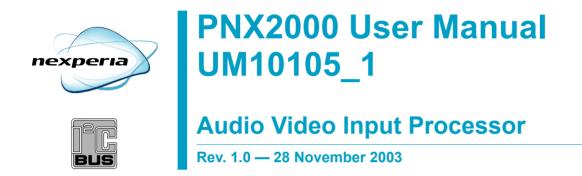

# **PNX2000**

Audio Video Input Processor

# **Table of Contents**

# **Chapter 1: Functional Specification**

| 1.1     | Introduction1-1             |

|---------|-----------------------------|

| 1.2     | PNX2000 Feature Summary 1-1 |

| 1.2.1   | Video Features 1-1          |

| 1.2.1.1 | 1FH Video                   |

| 1.2.1.2 | 2FH Video 1-1               |

| 1.2.1.3 | VBI Data Capture 1-1        |

| 1.2.1.4 | ITU656 output interface1-2  |

| 1.2.2   | Audio Features 1-2          |

| 1.2.2.1 | Demodulator and decoder     |

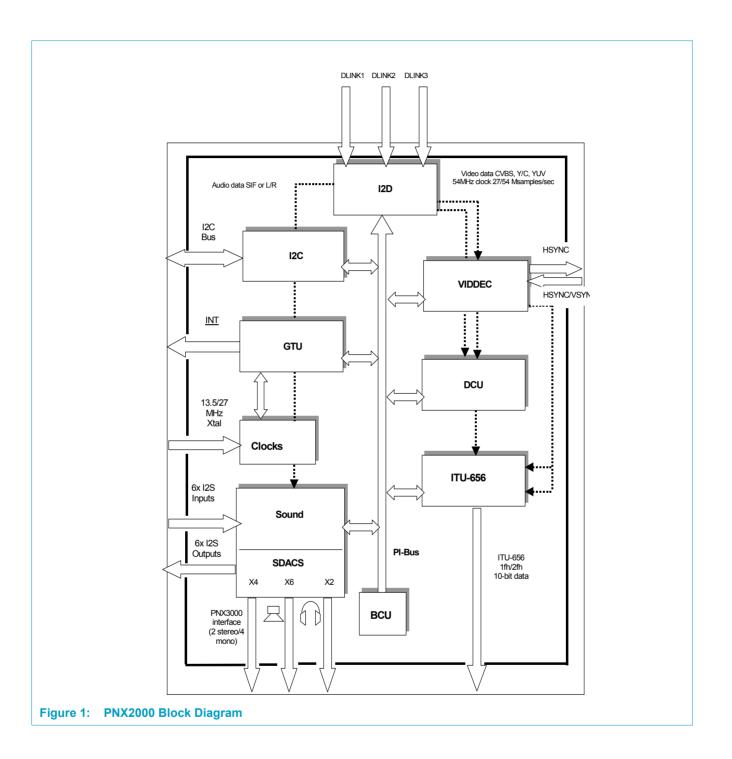

#### **Chapter 2: Control Interface**

| 2.1     | PNX2000 Control Interface        |

|---------|----------------------------------|

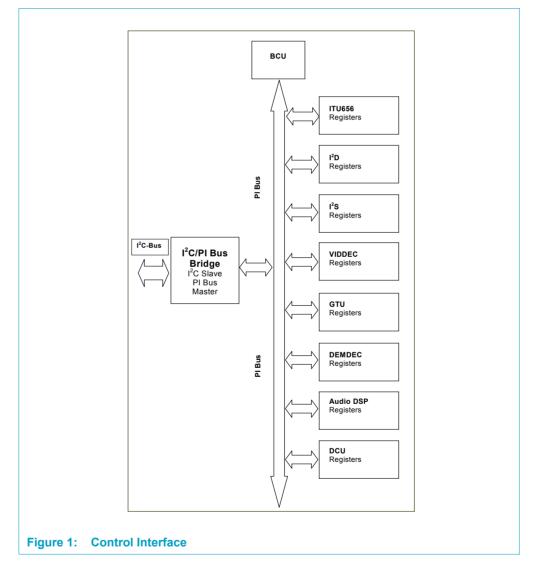

| 2.2     | I2C Bus Interface                |

| 2.2.1   | I2C Bus Features 2-2             |

| 2.2.2   | Allocated I2C Address 2-2        |

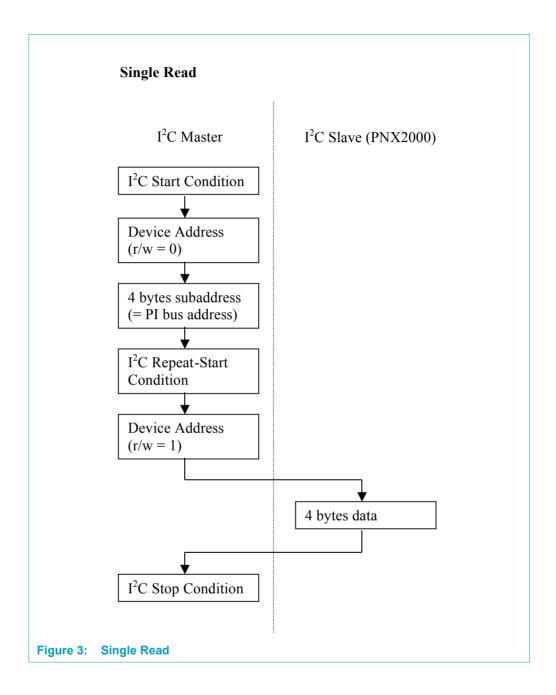

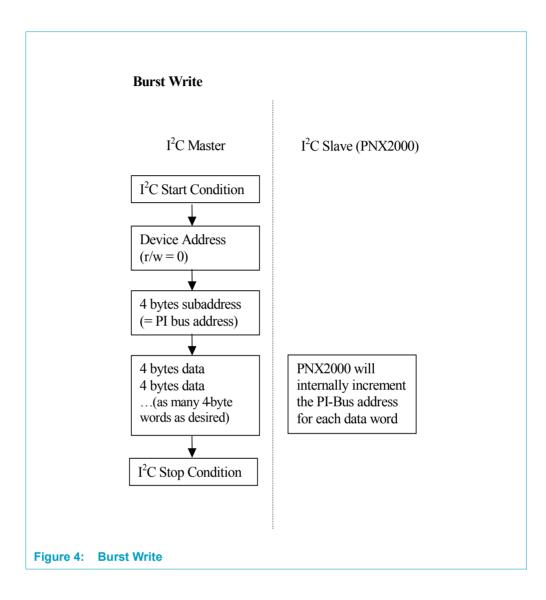

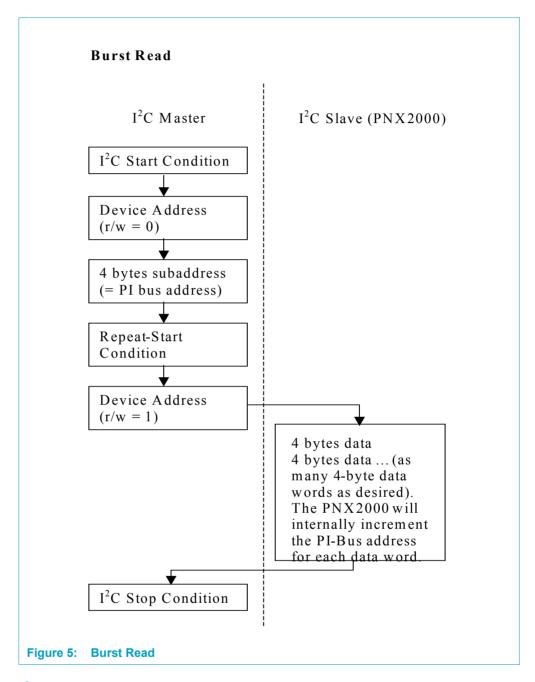

| 2.2.3   | I2C Register Access Protocol 2-2 |

| 2.2.4   | I2C Interface Block 2-6          |

| 2.3     | BCU Module                       |

| 2.3.1   | BCU Features 2-7                 |

| 2.3.2   | Registers 2-7                    |

| 2.3.2.1 | BCU Interrupt Status Register    |

|         | (BCU_INT_STATUS)                 |

| 2.3.2.2 | BCU Interrupt Enable Register    |

|         | (BCU_INT_ENABLE)                 |

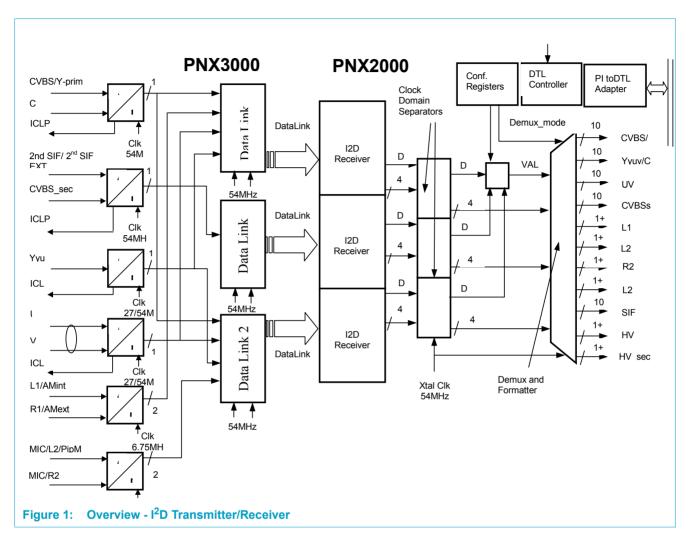

## Chapter 3: I2D

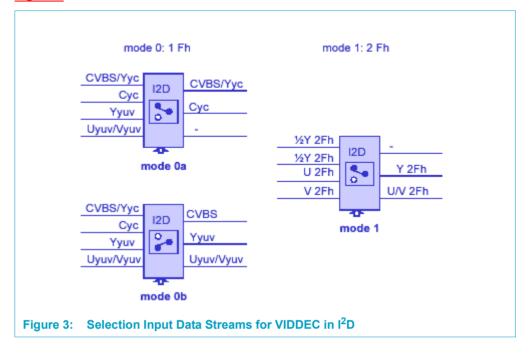

| 3.1     | Introduction                                  |  |

|---------|-----------------------------------------------|--|

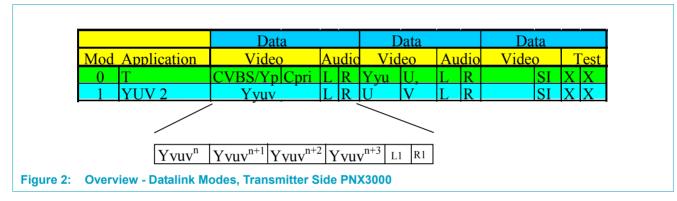

| 3.2     | Functional Capabilities of the Links 3-2      |  |

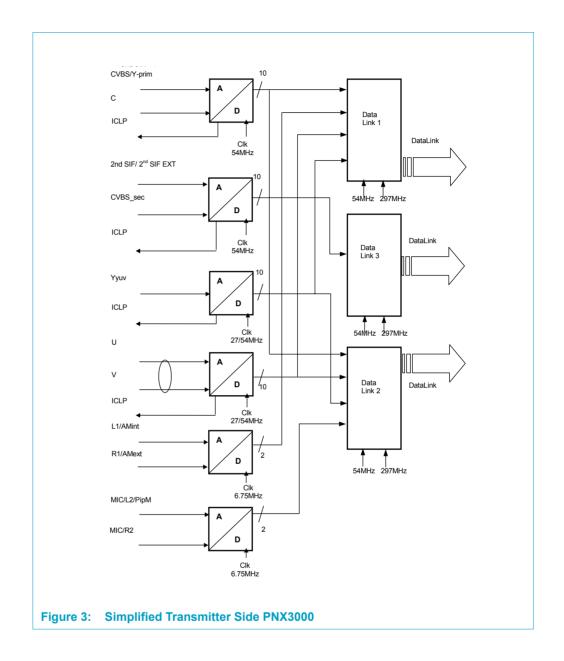

| 3.3     | Transmitter                                   |  |

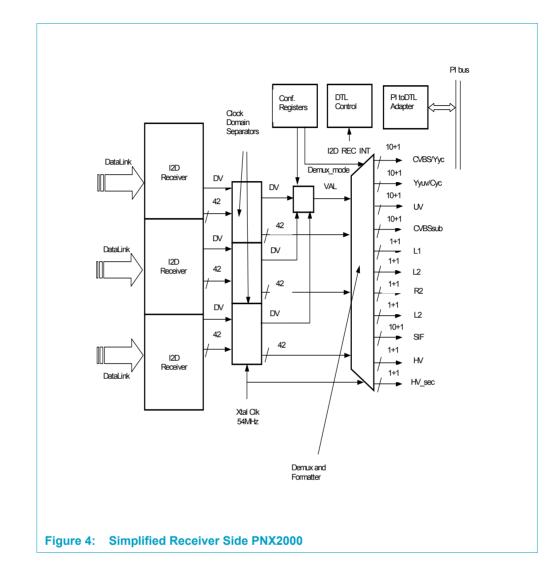

| 3.4     | <b>Receiver</b>                               |  |

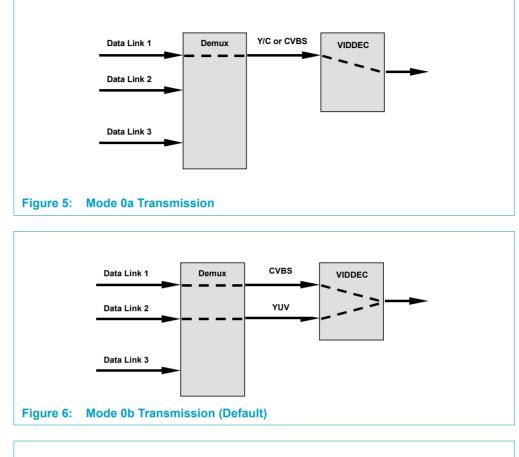

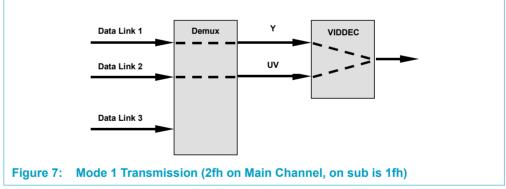

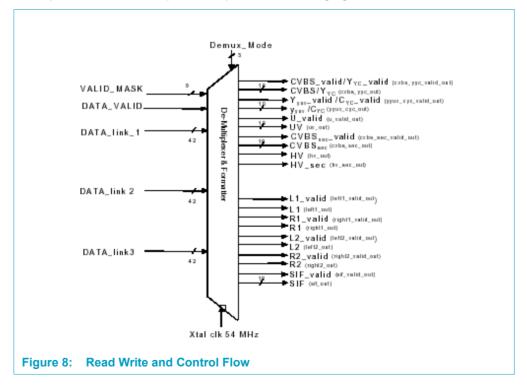

| 3.4.1   | Transmitter / Receiver Transmission Modes 3-6 |  |

| 3.4.2   | Data Rate and Timing Output Signals 3-8       |  |

| 3.5     | Configuration Registers. 3-9                  |  |

| 3.5.1   | I2D Register Map 3-10                         |  |

| 3.5.1.1 | I2D_RX_CTRL                                   |  |

| 3.5.1.2 | I2D_RX_STATUS                                 |  |

| 3.5.1.3 | I2D_REC_DEMUX_MODE                            |  |

| 3.5.1.4 | I2D _REC_SYNC_LOST                            |  |

| 3.5.1.5 | I2D _PRBS_STAT 3-13                           |  |

| 3.5.1.6 | I2D _PRBS_CTRL                                |  |

| 3.5.1.7 | I2D INT STATUS                                |  |

## Chapter 4: Video Processing (Viddec)

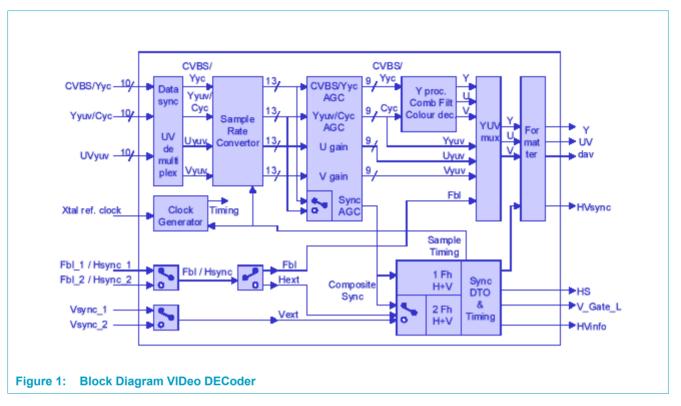

| 4.1   | <b>Overview</b>                   |

|-------|-----------------------------------|

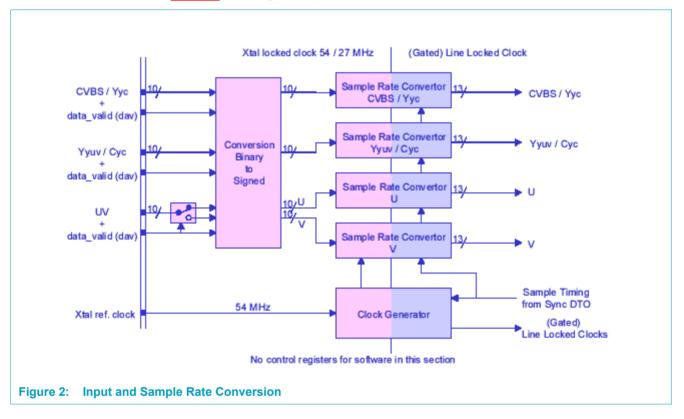

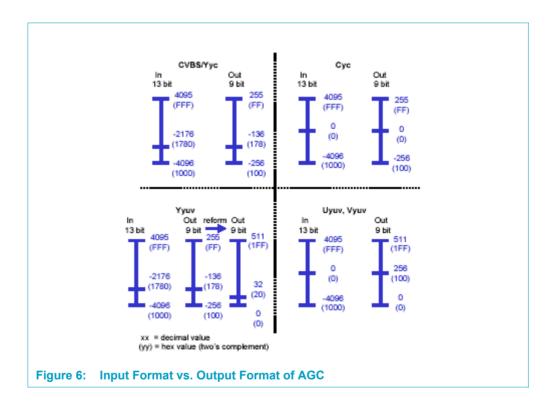

| 4.2   | Data input, Sample Rate Converter |

|       | and timing 4-3                    |

| 4.2.1 | Short Description 4-3             |

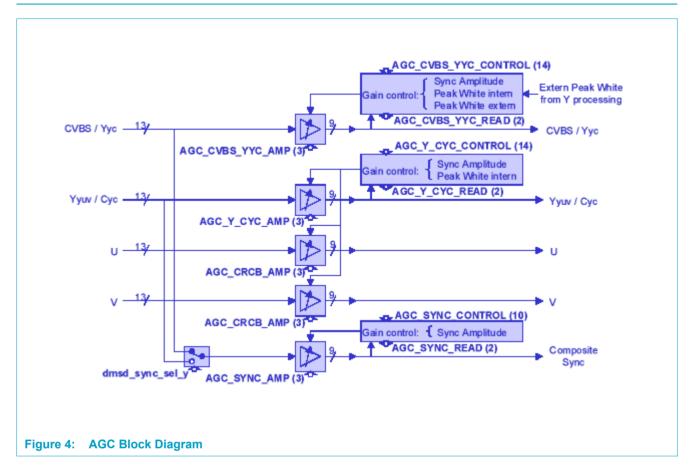

| 4.3   | AGC                               |

| 4.3.1 | Short Description 4-5             |

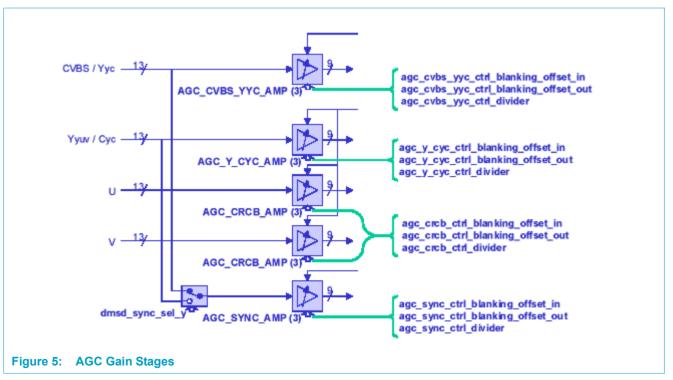

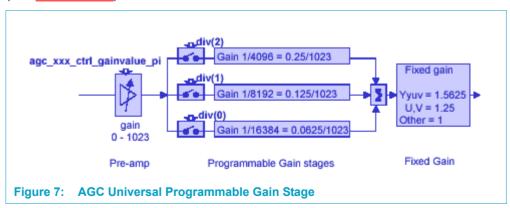

| 4.3.2 | AGC Gain Stages 4-6               |

| 1.4     | <b>Overview of Functional Partitioning</b> 1-6 |

|---------|------------------------------------------------|

| 1.3     | Functional Description1-4                      |

| 1.2.2.6 | Interfaces and switching1-4                    |

|         | downmix and split1-3                           |

| 1.2.2.5 | Psychoacoustic spatial algorithms,             |

| 1.2.2.4 | Reflection and delay1-3                        |

| 1.2.2.3 | Volume and tone control                        |

| 1.2.2.2 | Audio Multi Channel Decoder                    |

|         |                                                |

| 2.3.2.3 | BCU Interrupt Status Set Command      |

|---------|---------------------------------------|

|         | (BCU_INT_SET)                         |

| 2.3.2.4 | BCU Interrupt Status Clear Command    |

|         | (BCU_INT_CLEAR)2-9                    |

| 2.3.2.5 | BCU Bus Fault Status Register         |

|         | (BCU_FAULT_STATUS)2-10                |

| 2.3.2.6 | BCU Bus Fault Address Register        |

|         | (BCU_FAULT_ADDR) 2-10                 |

| 2.3.2.7 | BCU Time-Out Register (BCU_TOUT) 2-11 |

| 2.3.2.8 | BCU Memory Coherency Register         |

|         | (BCU_SNOOP)                           |

| 2.4     | Memory Map2-12                        |

|         |                                       |

| I2D _INT_ENABLE                           |

|-------------------------------------------|

| I2D _INT_CLEAR                            |

| I2D_INT_SET                               |

| I2D _MOD_ID                               |

| Interrupt Procedure                       |

| Interrupt Behaviour                       |

| Software Action with Registers            |

| Start Up                                  |

| Normal Operation                          |

| Soft_reset                                |

| Change of Source Selection                |

| Sync lost on a datalink (Out Of Sync)3-18 |

| Missing data_valid pulses                 |

| Test mode                                 |

|                                           |

| 4.3.3   | AGC Control Circuit4-11                      |

|---------|----------------------------------------------|

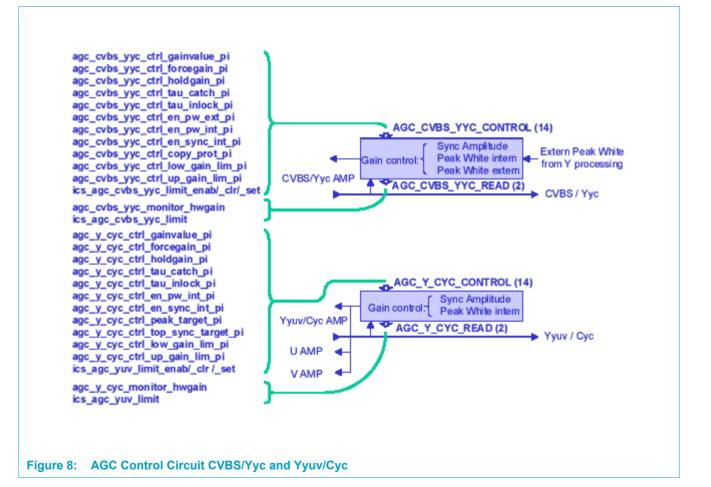

| 4.3.3.1 | AGC Control Circuit for CVBS / Yyc path 4-11 |

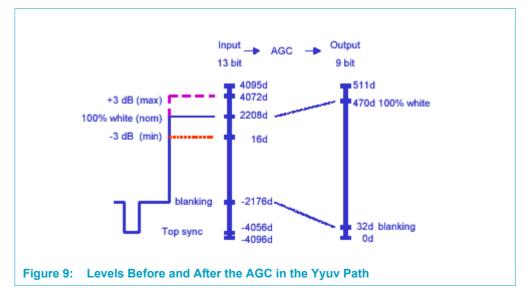

| 4.3.3.2 | AGC Control Circuit for Yyuv / Cyc Path 4-14 |

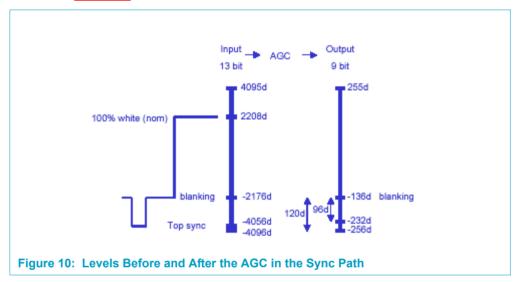

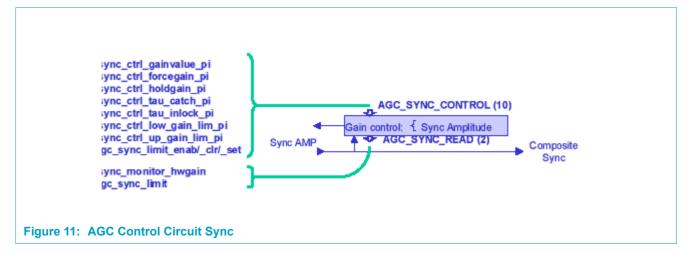

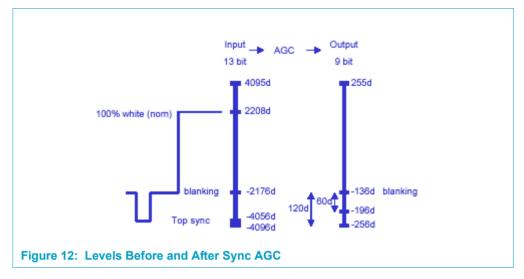

| 4.3.3.3 | AGC Control Circuit for the Sync Path 4-22   |

|         |                                              |

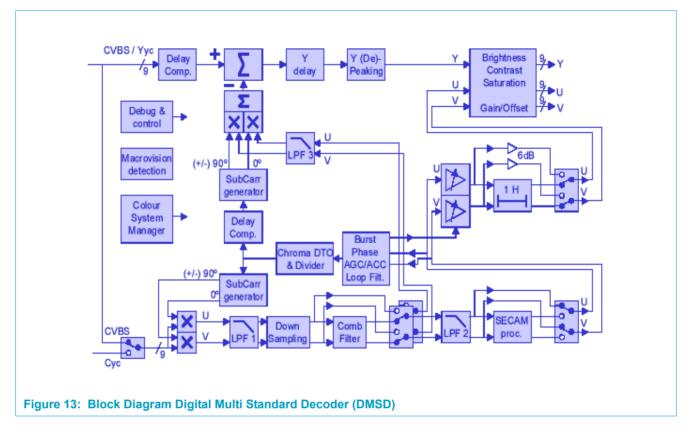

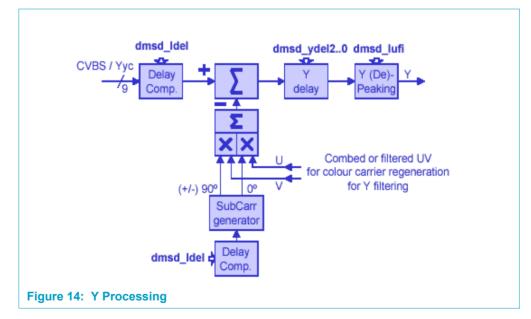

| 4.4     | Digital Multi Standard Decoder               |

| 4.4     | Digital Multi Standard Decoder<br>(DMSD)4-23 |

© Koninklijke Philips Electronics N.V. 2003. All rights reserved.

#### Audio Video Input Processor

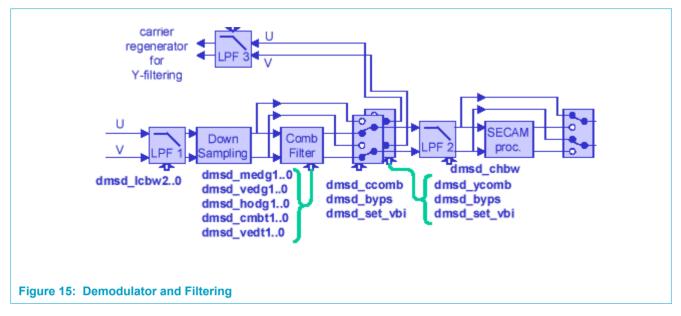

| 4.4.2   | Demodulator, Filtering (Combfilter)         |

|---------|---------------------------------------------|

|         | and SECAM Decoder 4-27                      |

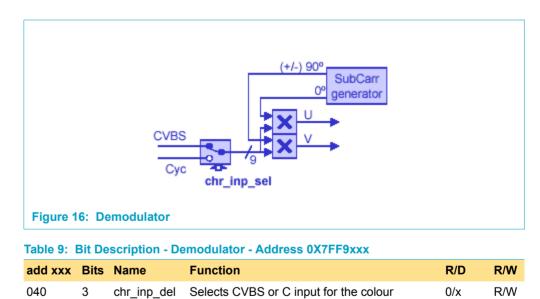

| 4.4.2.1 | Demodulator 4-28                            |

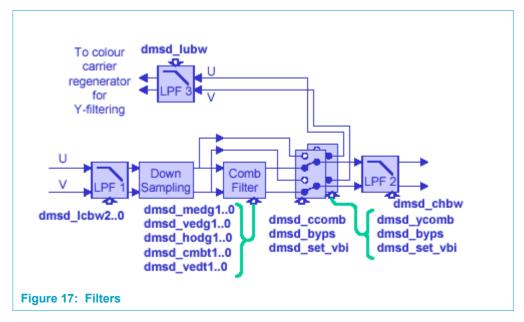

| 4.4.2.2 | Filtering 4-29                              |

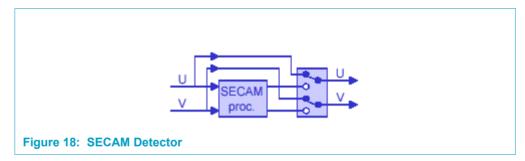

| 4.4.2.3 | SECAM decoder 4-32                          |

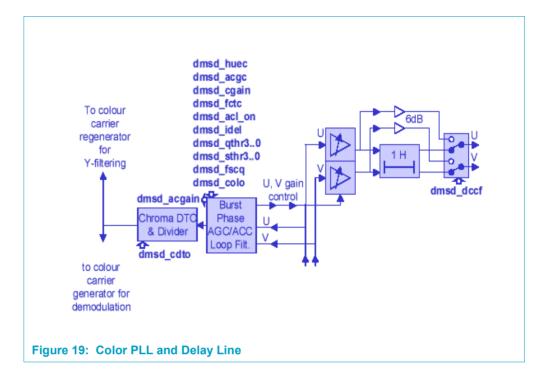

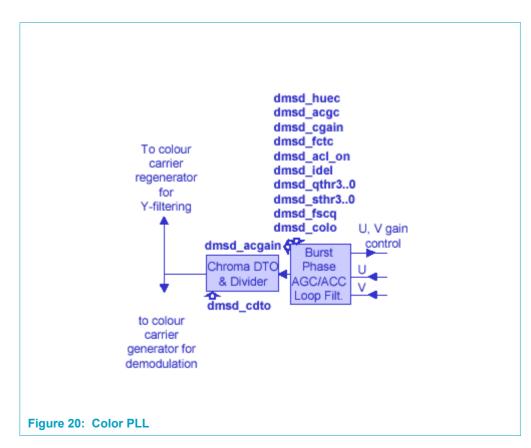

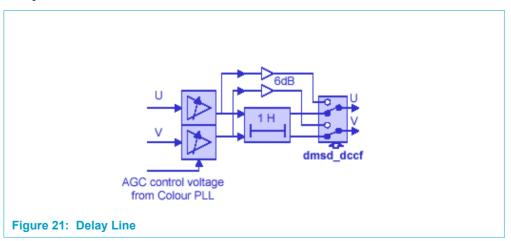

| 4.4.3   | Color PLL and Delay Line 4-33               |

| 4.4.3.1 | Color PLL 4-33                              |

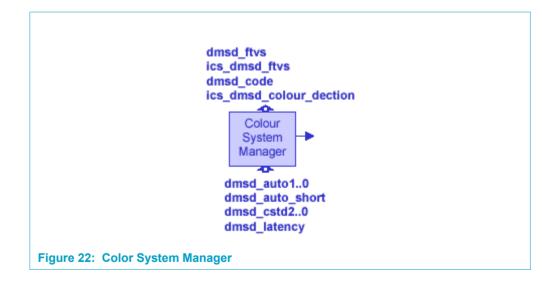

| 4.4.4   | Color System Manager 4-38                   |

| 4.4.5   | Signal controls, Macrovision and Debug 4-46 |

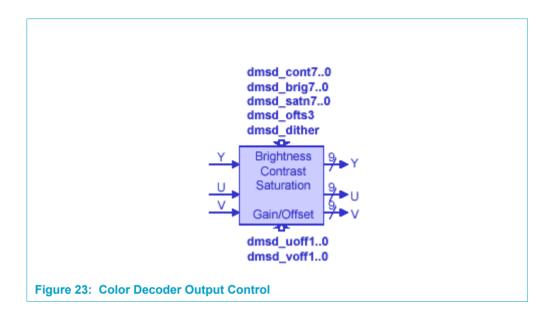

| 4.4.5.1 | Signal Controls 4-46                        |

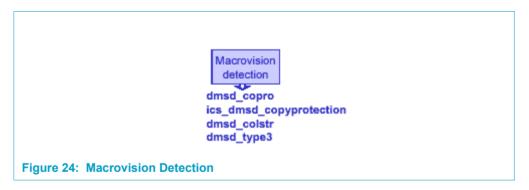

| 4.4.5.2 | Macrovision 4-47                            |

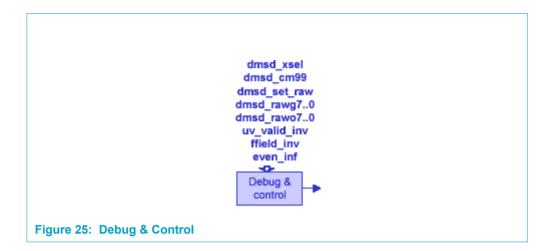

| 4.4.5.3 | Debug & Control 4-49                        |

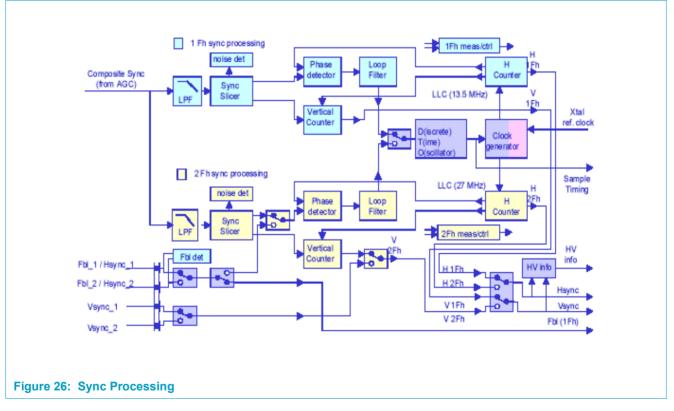

| 4.4.6   | Sync Processing 4-50                        |

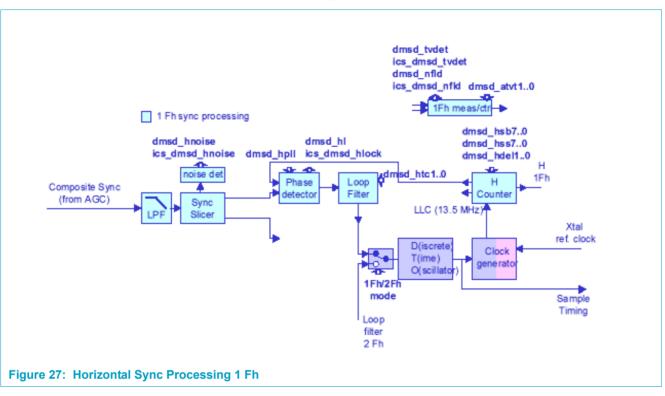

| 4.4.6.1 | Horizontal Sync Processing 1 Fh             |

|         | and Measurement/Control 4-52                |

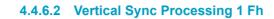

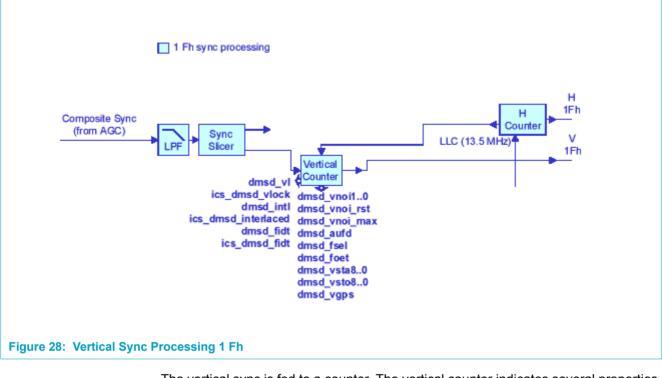

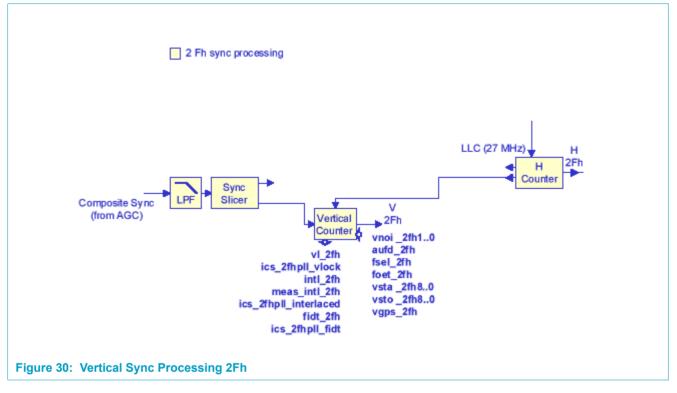

| 4.4.6.2<br>4.4.6.3<br>4.4.6.4 | Vertical Sync Processing 1 Fh                           |

|-------------------------------|---------------------------------------------------------|

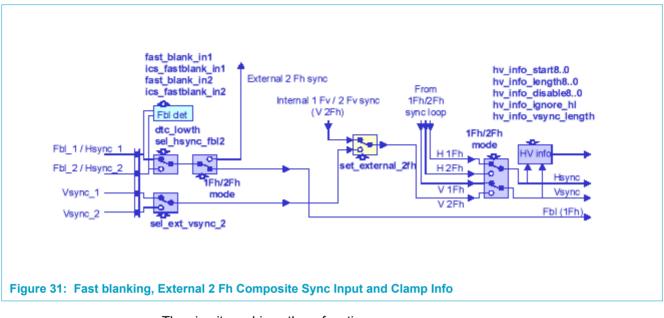

| 4.4.6.5                       | Fast Blanking / External 2 Fh Sync /         Clamp Info |

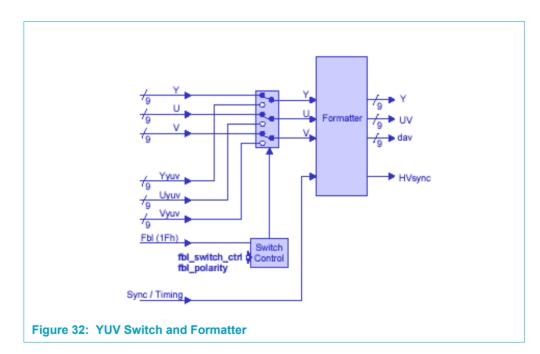

| 4.4.6.6                       | YUV Switch + Formatter                                  |

| 4.4.7                         | Switching VIDDEC between 1Fh and 2Fh 4-80               |

| 4.4.8                         | Use of interrupt bits4-81                               |

| 4.4.9                         | Automatic selection of different                        |

|                               | input signal formats4-82                                |

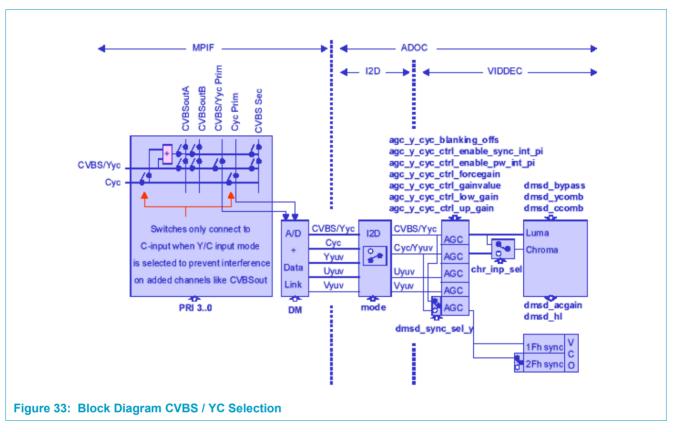

| 4.4.9.1                       | CVBS or Y/C Input Selection                             |

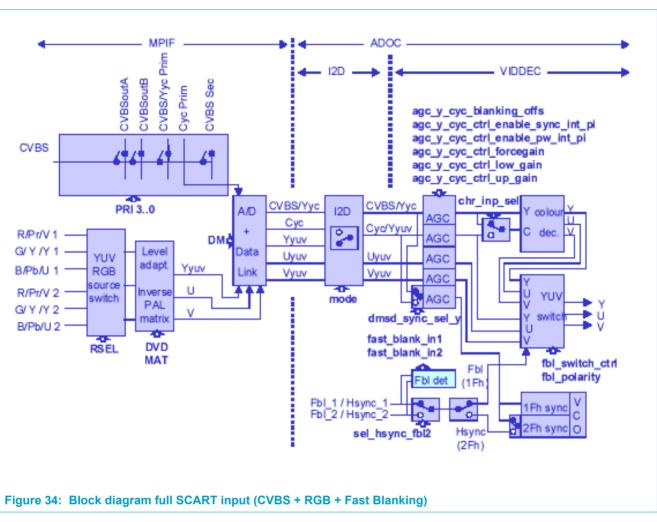

| 4.4.9.2                       | CVBS + RGB Insert via SCART4-86                         |

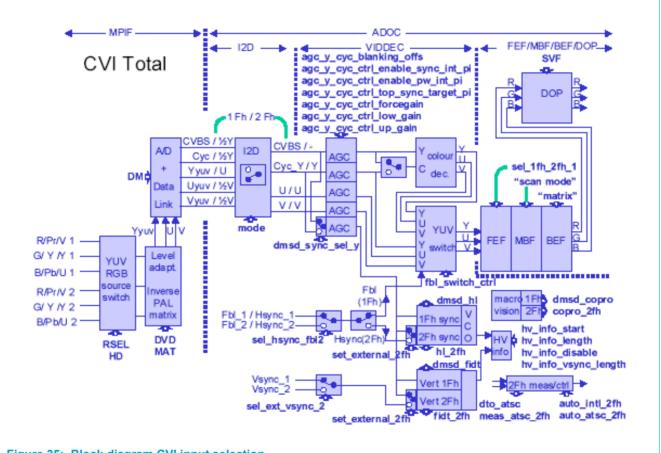

| 4.4.9.3                       | CVI Input Selection                                     |

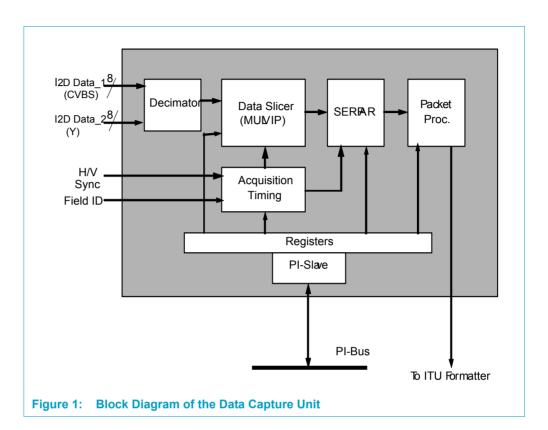

# Chapter 5: Data Capture Unit

| 5.1   | Summary of Functions 5-1            | 5.         |

|-------|-------------------------------------|------------|

| 5.2   | Block Diagram                       | 5.         |

| 5.2.1 | Block Description 5-2               | 5.         |

| 5.3   | Design Specification 5-3            | 5.         |

| 5.4   | Data Packet Formats                 | 5.<br>5.   |

| 5.4.1 | Status Bytes 5-4                    | 5.         |

| 5.4.2 | Euro WST, US WST and NABTS Data 5-4 | •          |

| 5.4.3 | WSS625 Data 5-4                     | 5.         |

| 5.4.4 | WSS525 Data 5-5                     | 5.0        |

| 5.4.5 | VPS Data 5-5                        | 5.0        |

| 5.4.6 | Closed Caption 5-6                  | 5.0        |

| 5.4.7 | Moji (Japanese Text) 5-6            | _          |

| 5.4.8 | VITC Data 5-6                       | 5.         |

| 5.4.9 | Open Data Types 5-6                 | 5.0<br>5.0 |

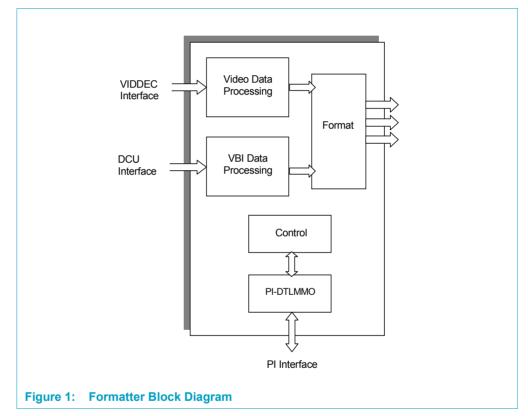

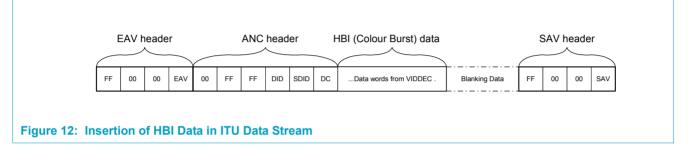

# Chapter 6: ITU656

| •        |                                              |            |

|----------|----------------------------------------------|------------|

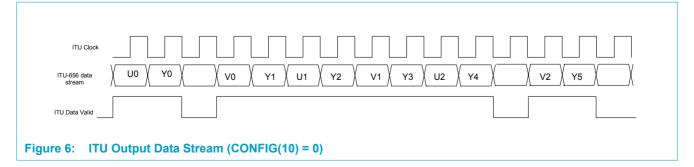

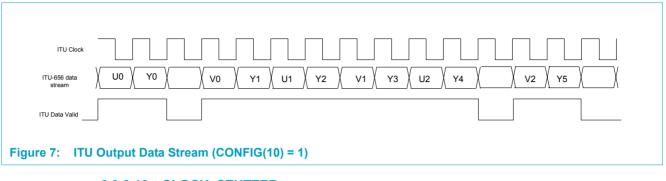

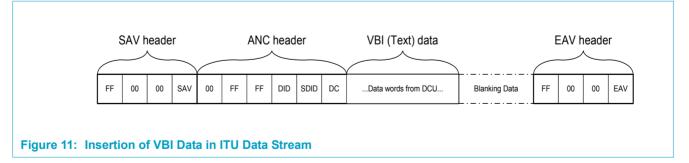

| 6.1.     | ITU656 Formatter Overview6-1                 | 6.3        |

| 6.2.     | ITU656 Formatter Data Interfaces 6-2         | 6.3        |

| 6.3.     | Control Registers                            | 6.3        |

| 6.3.1    | ITU656 Formatter Registers                   | 6.3        |

| 6.3.2    | CONFIG Register 6-3                          | 6.3        |

| 6.3.2.1  | MODE                                         | 6.3        |

| 6.3.2.2  | Columbus                                     | 6.3<br>6.3 |

| 6.3.2.3  | VBI_CONTROL6-5                               | 6.         |

| 6.3.2.4  | VBI_ONLY                                     | 6.         |

| 6.3.2.5  | CVBS_COMPL 6-6                               | 6.3        |

| 6.3.2.6  | UV_COMPL6-6                                  | 6.3        |

| 6.3.2.7  | DITHER 6-6                                   | 6.3        |

| 6.3.2.8  | DC_JUSTIFIED6-7                              | 6.3        |

| 6.3.2.9  | CLOCK_INVERT 6-7                             | 6.3        |

| 6.3.2.10 |                                              | 6.3        |

| 6.3.2.11 |                                              | 6.3        |

| 6.3.2.12 |                                              | 6.3        |

| 6.3.2.13 |                                              | 6.         |

| 6.3.2.14 |                                              | 6.4        |

| 6.3.3    | Data Identification Register – VBI data 6-9  | 6.4        |

| 6.3.4    | Data Identification Register – HBI data 6-10 | 0.4<br>6.4 |

| 6.3.5    | CAPTURE Register 6-10                        | 0.4        |

|          |                                              |            |

| 5.5     | Packet Processing Capabilities5-7          |

|---------|--------------------------------------------|

| 5.5.1   | Magazine and Packet Number Decoding 5-7    |

| 5.5.1.1 | Input Data Format5-7                       |

| 5.5.1.2 | Output Data Format5-7                      |

| 5.5.2   | Page Header Decoding5-8                    |

| 5.5.3   | WSS525 CRC Checking5-8                     |

| 5.5.4   | Packet Validity Checking 5-8               |

| 5.6     | Registers5-9                               |

| 5.6.1   | DCR1: Data Capture Register (Write)5-10    |

| 5.6.2   | DCR2: Data Capture Register 2 (Write) 5-11 |

| 5.6.3   | LCR2LCR24: Line Control                    |

|         | Registers (Write) 5-11                     |

| 5.6.4   | DCS: Data Capture Status (Read)5-13        |

| 5.6.5   | Interrupt Registers (Read/Write)5-14       |

| 5.6.6   | MODULE_ID (Read)5-14                       |

| .3.6          | FIFO Register6-11                         |

|---------------|-------------------------------------------|

| .3.7          | VF CONTROL Register                       |

| .3.8          | VF SYNC Register6-11                      |

| .3.9          | FIELD 1 Register                          |

| .3.10         | FIELD 2 Register6-12                      |

| .3.11         | VBI 1 Register                            |

| .3.12         | VBI 2 Register                            |

| .3.13         | VBI 3 Register                            |

| .3.14         | VBI 4 Register                            |

| .3.15         | PROG HBI Register6-13                     |

| .3.16         | YUV Offset Register 6-14                  |

| .3.17         | Interrupt Registers6-14                   |

| .3.17.1       | INT_STATUS Register6-14                   |

| .3.17.2       | INT_ENABLE Register6-15                   |

| .3.17.3       | INT_CLEAR Register6-15                    |

| .3.17.4       | INT_SET Register6-15                      |

| .3.18         | MODULE_ID Register6-15                    |

| .3.19         | Debug Control Register                    |

| 6.4. <b>\</b> | /ideo Line Interface Signal Structure6-17 |

| .4.1          | PNX2000 (Mode 0) in Columbus Mode6-17     |

| .4.2          | PNX2000 (Mode 1) in Columbus Mode6-18     |

| .4.3          | PNX2000 (Mode 0) in PNX8550 mode 6-18     |

|               |                                           |

6.4.6 PN

PNX2000 (Mode 3) in PNX8550 mode . . . . . 6-19

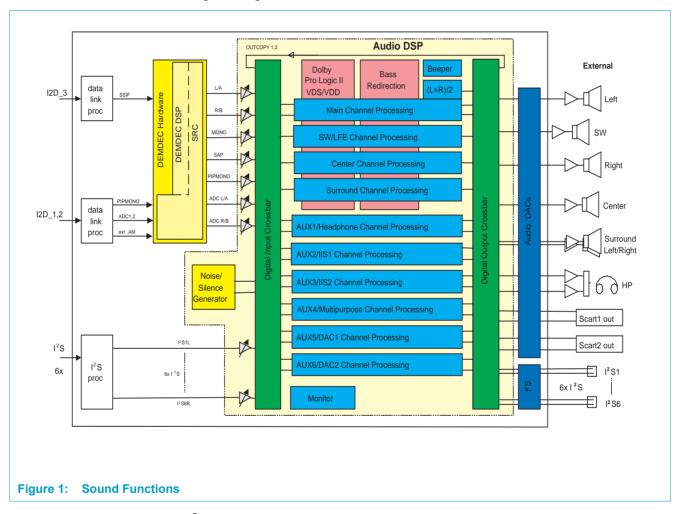

# **Chapter 7: Audio Processing**

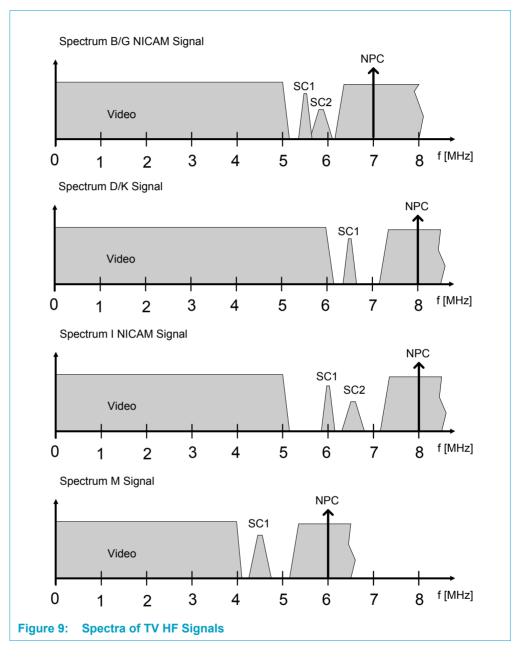

| 7.2       Supported Standards       7-2         7.2.1       Analogue 2-carrier Systems       7-3         7.2.2       2-carrier Systems with NICAM       7-3         7.2.3       Satellite Systems       7-4         7.2.4       BTSC/SAP, Japan (EIAJ) and FM Radio       Systems         7.3       Features       7-4         7.3.1       Demodulator and Decoder       7-4         7.3.2       Audio Multi Channel Decoder       7-4         7.3.3       Volume and Tone Control.       7-5         7.3.4       Reflection and Delay       7-6         7.3.5       Psychoacoustic Spatial Algorithms,<br>Downmix and Split       7-6         7.3.6       Interfaces and Switching.       7-6         7.4       Functional Overview of the<br>Sound Core       7-7         7.5       Sound Core Control Interface       7-8         7.6       I2S       7-9         7.7       Digital-Analogue Converters       7-11         7.8       Demdec DSP       7-11         7.8.1       DEP Doses NOT Do.       7-13         7.8.2       What DDEP Doses NOT Do.       7-13         7.8.3       Design Considerations       7-14         7.8.4       DDEP Doses NOT Do.                                                                                                        | 7.1     | General Description         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------|

| 7.2.2       2-carrier Systems with NICAM.       7-3         7.2.3       Satellite Systems       7-4         7.2.4       BTSC/SAP, Japan (EIAJ) and FM Radio<br>Systems       7-4         7.3       Features       7-4         7.3.1       Demodulator and Decoder       7-4         7.3.2       Audio Multi Channel Decoder       7-4         7.3.3       Volume and Tone Control.       7-5         7.3.4       Reflection and Delay       7-6         7.3.5       Psychoacoustic Spatial Algorithms,<br>Downnix and Split       7-6         7.3.6       Interfaces and Switching       7-6         7.3.6       Interfaces and Switching       7-6         7.4       Functional Overview of the<br>Sound Core       7-7         7.5       Sound Core Control Interface       7-8         7.6       I2S       7-9         7.7       Digital-Analogue Converters       7-11         7.8       Demdec DSP       7-11         7.8       Demdec DSP       7-13         7.8.1       DDEP basics and Usage       7-15         7.8.2       What DDEP Does NOT Do       7-13         7.8.3       Design Considerations       7-14         7.8.4       DDEP Basics and Usage                                                                                                      | 7.2     | Supported Standards 7-2     |

| 7.2.3       Satellite Systems       7-4         7.2.4       BTSC/SAP, Japan (EIAJ) and FM Radio         Systems       7-4         7.3       Features       7-4         7.3.1       Demodulator and Decoder       7-4         7.3.2       Audio Multi Channel Decoder       7-5         7.3.3       Volume and Tone Control       7-5         7.3.4       Reflection and Delay       7-6         7.5       Psychoacoustic Spatial Algorithms,<br>Downmix and Split       7-6         7.3.6       Interfaces and Switching       7-6         7.4       Functional Overview of the<br>Sound Core       7-7         7.5       Sound Core Control Interface       7-8         7.6       I2S       7-9         7.7       Digital-Analogue Converters       7-11         7.8       Demdec DSP       7-11         7.8.1       DDEP in Brief       7-12         7.8.2       What DDEP Does NOT Do       7-13         7.8.3       Design Considerations       7-14         7.8.4       DDEP Hasics and Usage       7-15         7.8.5       DEMDEC Hardware Blocks and the<br>Sample Rate Problem       7-15         7.8.6       Signal Processing in DSP Software       7-16      <                                                                                               | 7.2.1   | Analogue 2-carrier Systems  |

| 7.2.4       BTSC/SAP, Japan (EIAJ) and FM Radio         Systems       7-4         7.3       Features       7-4         7.3.1       Demodulator and Decoder       7-4         7.3.2       Audio Multi Channel Decoder       7-5         7.3.3       Volume and Tone Control       7-5         7.3.4       Reflection and Delay       7-6         7.3.5       Psychoacoustic Spatial Algorithms,<br>Downmix and Split       7-6         7.3.6       Interfaces and Switching       7-6         7.4       Functional Overview of the<br>Sound Core       7-7         7.5       Sound Core Control Interface       7-8         7.6       I2S       7-9         7.7       Digital-Analogue Converters       7-11         7.8       Demdec DSP       7-11         7.8.1       DDEP in Brief       7-12         7.8.2       What DDEP Does NOT Do       7-13         7.8.3       Design Considerations       7-14         7.8.4       DDEP Basics and Usage       7-15         7.8.5       DEMDEC Hardware Blocks and the<br>Sample Rate Problem       7-15         7.8.6       Signal Processing in DSP Software       7-16         7.8.7       SRC constraints       7-19                                                                                                     | 7.2.2   |                             |

| Systems         7-4           7.3         Features         7-4           7.3.1         Demodulator and Decoder         7-4           7.3.2         Audio Multi Channel Decoder         7-5           7.3.3         Volume and Tone Control         7-5           7.3.4         Reflection and Delay         7-6           7.3.5         Psychoacoustic Spatial Algorithms,<br>Downmix and Split         7-6           7.3.6         Interfaces and Switching         7-7           7.5         Sound Core         7-7           7.5         Sound Core Control Interface         7-8           7.6         I2S         7-9           7.7         Digital-Analogue Converters         7-11           7.8         Demdec DSP         7-11           7.8.1         DDEP in Brief         7-12           7.8.2         What DDEP Does NOT Do.         7-13           7.8.3         Design Considerations         7-14           7.8.4         DDEP Basics and Usage         7-15           7.8.5         DEMDEC Hardware Blocks and the         Sample Rate Problem         7-15           7.8.6         Signal Processing in DSP Software         7-16           7.8.7         SRC constraints         7-23                                                                 | 7.2.3   | Satellite Systems 7-4       |

| 7.3       Features       7-4         7.3.1       Demodulator and Decoder       7-4         7.3.2       Audio Multi Channel Decoder       7-5         7.3.3       Volume and Tone Control       7-5         7.3.4       Reflection and Delay       7-6         7.3.5       Psychoacoustic Spatial Algorithms,<br>Downmix and Split       7-6         7.3.6       Interfaces and Switching       7-6         7.4       Functional Overview of the<br>Sound Core       7-7         7.5       Sound Core Control Interface       7-8         7.6       I2S       7-9         7.7       Digital-Analogue Converters       7-11         7.8       Demdec DSP       7-11         7.8.1       DDEP in Brief       7-12         7.8.2       What DDEP Does NOT Do.       7-13         7.8.3       Design Considerations       7-14         7.8.4       DDEP Basics and Usage       7-15         7.8.5       DEMDEC Hardware Blocks and the<br>Sample Rate Problem       7-16         7.8.7       SRC constraints       7-19         7.8.8       The DDEP Control Register       7-23         7.8.8.1       Mode Selection       7-24         7.8.8.2       Starting and Restarting                                                                                                | 7.2.4   |                             |

| 7.3.1       Demodulator and Decoder       7.4         7.3.2       Audio Multi Channel Decoder.       7.5         7.3.3       Volume and Tone Control.       7.5         7.3.4       Reflection and Delay       7.6         7.3.5       Psychoacoustic Spatial Algorithms,<br>Downmix and Split       7.6         7.3.6       Interfaces and Switching.       7.6         7.3.6       Interfaces and Switching.       7.6         7.4       Functional Overview of the<br>Sound Core       7.7         7.5       Sound Core Control Interface       7.8         7.6       I2S       7.9         7.7       Digital-Analogue Converters       7.11         7.8       Demdec DSP       7.11         7.8       Demdec DSP       7.11         7.8.1       DDEP in Brief       7.12         7.8.2       What DDEP Does NOT Do.       7.13         7.8.3       Design Considerations       7.14         7.8.4       DDEP Basics and Usage       7.15         7.8.5       DEMDEC Hardware Blocks and the<br>Sample Rate Problem       7.15         7.8.6       Signal Processing in DSP Software       7.16         7.8.7       SRC constraints       7.23         7.8.8       The DDEP                                                                                           |         | •                           |

| 7.3.2       Audio Multi Channel Decoder.       7-5         7.3.3       Volume and Tone Control.       7-5         7.3.4       Reflection and Delay       7-6         7.3.5       Psychoacoustic Spatial Algorithms,<br>Downmix and Split       7-6         7.3.6       Interfaces and Switching.       7-6         7.3.6       Interfaces and Switching.       7-6         7.4       Functional Overview of the<br>Sound Core       7-7         7.5       Sound Core Control Interface       7-8         7.6       I2S       7-9         7.7       Digital-Analogue Converters       7-11         7.8       Demdec DSP       7-11         7.8.1       DDEP in Brief       7-12         7.8.2       What DDEP Does NOT Do.       7-13         7.8.3       Design Considerations       7-14         7.8.4       DDEP Basics and Usage       7-15         7.8.5       DEMDEC Hardware Blocks and the<br>Sample Rate Problem       7-15         7.8.6       Signal Processing in DSP Software       7-16         7.8.8       The DDEP Control Register       7-23         7.8.8.1       Mode Selection       7-24         7.8.8.2       Statring and Restarting       7-24         7.8.8.3 </td <td>7.3</td> <td>Features</td>                                               | 7.3     | Features                    |

| 7.3.3       Volume and Tone Control       7-5         7.3.4       Reflection and Delay       7-6         7.3.5       Psychoacoustic Spatial Algorithms,<br>Downmix and Split       7-6         7.3.6       Interfaces and Switching       7-6         7.3.6       Interfaces and Switching       7-6         7.4       Functional Overview of the<br>Sound Core       7-7         7.5       Sound Core Control Interface       7-8         7.6       I2S       7-9         7.7       Digital-Analogue Converters       7-11         7.8       Demdec DSP       7-11         7.8.1       DDEP Does NOT Do       7-13         7.8.2       What DDEP Does NOT Do       7-13         7.8.3       Design Considerations       7-14         7.8.4       DDEP Basics and Usage       7-15         7.8.5       DEMDEC Hardware Blocks and the<br>Sample Rate Problem       7-16         7.8.6       Signal Processing in DSP Software       7-16         7.8.8       The DDEP Control Register       7-23         7.8.8.1       Mode Selection       7-27         7.8.8.2       Starting and Restarting       7-24         7.8.8.3       DDEP Control Variables       7-24         7.8.8.4                                                                                       |         |                             |

| 7.3.4       Reflection and Delay       7-6         7.3.5       Psychoacoustic Spatial Algorithms,<br>Downmix and Split       7-6         7.3.6       Interfaces and Switching       7-6         7.4       Functional Overview of the<br>Sound Core       7-7         7.5       Sound Core Control Interface       7-8         7.6       I2S       7-9         7.7       Digital-Analogue Converters       7-11         7.8       Demdec DSP       7-11         7.8.1       DDEP in Brief       7-12         7.8.2       What DDEP Does NOT Do.       7-13         7.8.3       Design Considerations       7-14         7.8.4       DDEP Basics and Usage       7-15         7.8.5       DEMDEC Hardware Blocks and the<br>Sample Rate Problem       7-15         7.8.6       Signal Processing in DSP Software       7-16         7.8.8       The DDEP Control Register       7-23         7.8.8.1       Mode Selection       7-24         7.8.8.2       Starting and Restarting       7-24         7.8.8.3       DDEP Control Variables       7-30         7.8.8.4       Dependencies Between Variables in<br>the DDEPR       7-30         7.8.8.5       Automute Function       7-27                                                                                   |         |                             |

| 7.3.5       Psychoacoustic Spatial Algorithms,<br>Downmix and Split       7-6         7.3.6       Interfaces and Switching       7-6         7.4       Functional Overview of the<br>Sound Core       7-7         7.5       Sound Core Control Interface       7-8         7.6       I2S       7-9         7.7       Digital-Analogue Converters       7-11         7.8       Demdec DSP       7-11         7.8.1       DDEP in Brief       7-12         7.8.2       What DDEP Does NOT Do.       7-13         7.8.3       Design Considerations       7-14         7.8.4       DDEP Basics and Usage       7-15         7.8.5       DEMDEC Hardware Blocks and the<br>Sample Rate Problem       7-15         7.8.6       Signal Processing in DSP Software       7-16         7.8.7       SRC constraints       7-19         7.8.8       The DDEP Control Register       7-23         7.8.8.1       Mode Selection       7-24         7.8.2       Starting and Restarting       7-24         7.8.8.3       DDEP Control Variables       7-24         7.8.4       Dependencies Between Variables in<br>the DDEPR       7-27         7.8.8.5       Automute Function       7-27         7.8.                                                                              |         |                             |

| Downmix and Split7-67.3.6Interfaces and Switching7-67.4Functional Overview of the<br>Sound Core7-77.5Sound Core Control Interface7-87.6I2S7-97.7Digital-Analogue Converters7-117.8Demdec DSP7-117.8.1DDEP in Brief7-127.8.2What DDEP Does NOT Do.7-137.8.3Design Considerations7-147.8.4DDEP Basics and Usage7-157.8.5DEMDEC Hardware Blocks and the<br>Sample Rate Problem7-167.8.7SRC constraints7-197.8.8The DDEP Control Register7-237.8.8.1Mode Selection7-247.8.8.2Starting and Restarting7-247.8.8.3DDEP Control Variables7-247.8.4.4DEPRR7-277.8.8.5Automute Function7-327.8.8.7Amplitude and Noise Threshold Registers7-307.8.8.9EIAJ Subcarrier Detection7-327.8.9Other DEMDEC Control Options7-337.8.10Status Registers7-377.8.10.2NICAM Status Registers7-377.8.10.1DEMDEC Status Registers7-407.8.11Noise Detection7-427.8.11Noise Detection7-427.8.12Muting all DEMDEC Outputs7-417.8.13Using DDEP in a Set Design7-427.8.13Application Related Constant Settings7-427.8.13 <td>-</td> <td></td>                                                                                                                                                                                                                                                           | -       |                             |

| 7.3.6       Interfaces and Switching.       7-6         7.4       Functional Overview of the<br>Sound Core       7-7         7.5       Sound Core Control Interface       7-8         7.6       I2S       7-9         7.7       Digital-Analogue Converters       7-11         7.8       Demdec DSP       7-11         7.8       Demdec DSP       7-11         7.8.1       DDEP in Brief       7-12         7.8.2       What DDEP Does NOT Do.       7-13         7.8.3       Design Considerations       7-14         7.8.4       DDEP Basics and Usage       7-15         7.8.5       DEMDEC Hardware Blocks and the<br>Sample Rate Problem       7-16         7.8.7       SRC constraints       7-19         7.8.8       The DDEP Control Register       7-23         7.8.8.1       Mode Selection       7-24         7.8.8.2       Starting and Restarting       7-24         7.8.8.3       DDEP Control Variables       7-24         7.8.4       Dependencies Between Variables in<br>the DDEPR       7-27         7.8.8.5       Automute Function       7-27         7.8.8.6       NICAM Configuration       7-32         7.8.9       Other DEMDEC Control Options                                                                                                 | 7.3.5   |                             |

| 7.4       Functional Overview of the<br>Sound Core       7-7         7.5       Sound Core Control Interface       7-8         7.6       I2S       7-9         7.7       Digital-Analogue Converters       7-11         7.8       Demdec DSP       7-11         7.8       Demdec DSP       7-11         7.8.1       DDEP in Brief       7-12         7.8.2       What DDEP Does NOT Do.       7-13         7.8.3       Design Considerations       7-14         7.8.4       DDEP Basics and Usage       7-15         7.8.5       DEMDEC Hardware Blocks and the<br>Sample Rate Problem       7-16         7.8.7       SRC constraints       7-19         7.8.8       The DDEP Control Register       7-23         7.8.8.1       Mode Selection       7-24         7.8.3       DDEP Control Variables       7-24         7.8.4.3       DDEP Control Variables       7-24         7.8.4.4       Dependencies Between Variables in<br>the DDEPR       7-27         7.8.8.5       Automute Function       7-28         7.8.8.7       Amplitude and Noise Threshold Registers       7-30         7.8.8.9       EIAJ Subcarrier Detection       7-32         7.8.9       Other DEMDEC                                                                                           | 700     | Downmix and Split           |

| Sound Core         7-7           7.5         Sound Core Control Interface         7-8           7.6         I2S         7-9           7.7         Digital-Analogue Converters         7-11           7.8         Demdec DSP         7-11           7.8         Demdec DSP         7-11           7.8.1         DDEP in Brief         7-12           7.8.2         What DDEP Does NOT Do.         7-13           7.8.3         Design Considerations         7-14           7.8.4         DDEP Basics and Usage         7-15           7.8.5         DEMDEC Hardware Blocks and the         Sample Rate Problem         7-16           7.8.7         SRC constraints         7-19         7.8.8         The DDEP Control Register         7-23           7.8.8.1         Mode Selection         7-23         7.8.8.1         Mode Selection         7-24           7.8.8.2         Starting and Restarting         7-24         7.8.8.3         DDEP Control Variables         7-24           7.8.8.5         Automute Function         7-27         7.8.8.5         Automute Function         7-28           7.8.8.7         Amplitude and Noise Threshold Registers         7-30         7.8.8.5         AP Detection         7-32 <tr< td=""><td></td><td>-</td></tr<> |         | -                           |

| 7.5       Sound Core Control Interface       7-8         7.6       I2S       7-9         7.7       Digital-Analogue Converters       7-11         7.8       Demdec DSP       7-11         7.8.1       DDEP in Brief       7-12         7.8.2       What DDEP Does NOT Do       7-13         7.8.3       Design Considerations       7-14         7.8.4       DDEP Basics and Usage       7-15         7.8.5       DEMDEC Hardware Blocks and the       Sample Rate Problem       7-16         7.8.6       Signal Processing in DSP Software       7-16         7.8.8       The DDEP Control Register       7-23         7.8.8.1       Mode Selection       7-23         7.8.8.2       Starting and Restarting       7-24         7.8.8.3       DDEP Control Variables       7-24         7.8.8.4       Dependencies Between Variables in       1         the DDEPR       7-27       7.8.8.6       NICAM Configuration       7-32         7.8.8.7       Amplitude and Noise Threshold Registers       7-30       7.38         7.8.8.9       EIAJ Subcarrier Detection       7-32       7.38       7.37         7.8.9       Other DEMDEC Control Options       7-33       7.36                                                                                             | 7.4     |                             |

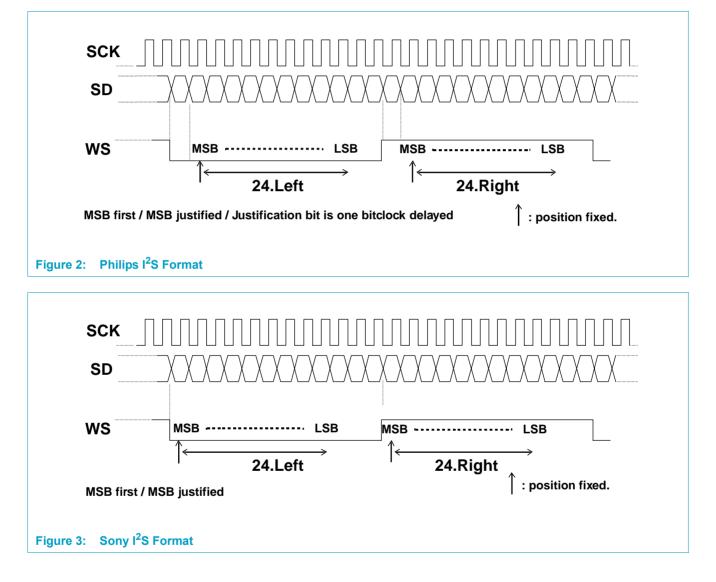

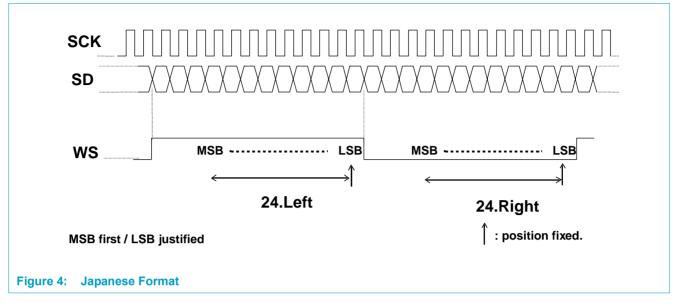

| 7.6       I2S       7-9         7.7       Digital-Analogue Converters       7-11         7.8       Demdec DSP       7-11         7.8.1       DDEP in Brief       7-12         7.8.2       What DDEP Does NOT Do       7-13         7.8.3       Design Considerations       7-14         7.8.4       DDEP Basics and Usage       7-15         7.8.5       DEMDEC Hardware Blocks and the<br>Sample Rate Problem       7-15         7.8.6       Signal Processing in DSP Software       7-16         7.8.7       SRC constraints       7-19         7.8.8       The DDEP Control Register       7-23         7.8.8.1       Mode Selection       7-24         7.8.8.2       Starting and Restarting       7-24         7.8.8.3       DDEP Control Variables       7-27         7.8.8.4       Dependencies Between Variables in<br>the DDEPR       7-27         7.8.8.5       Automute Function       7-32         7.8.8.7       Amplitude and Noise Threshold Registers       7-30         7.8.8.9       EIAJ Subcarrier Detection       7-32         7.8.9       Other DEMDEC Control Options       7-33         7.8.9       Other DEMDEC Control Options       7-37         7.8.10 <th></th> <th></th>                                                                    |         |                             |

| 7.7       Digital-Analogue Converters       7-11         7.8       Demdec DSP       7-11         7.8.1       DDEP in Brief       7-12         7.8.2       What DDEP Does NOT Do.       7-13         7.8.3       Design Considerations       7-14         7.8.4       DDEP Basics and Usage       7-15         7.8.5       DEMDEC Hardware Blocks and the<br>Sample Rate Problem       7-15         7.8.6       Signal Processing in DSP Software       7-16         7.8.7       SRC constraints       7-19         7.8.8       The DDEP Control Register       7-23         7.8.8.1       Mode Selection       7-24         7.8.8.2       Starting and Restarting       7-24         7.8.8.3       DDEP Control Variables       7-27         7.8.8.4       Dependencies Between Variables in<br>the DDEPR       7-27         7.8.8.5       Automute Function       7-32         7.8.8.7       Amplitude and Noise Threshold Registers       7-30         7.8.8.8       SAP Detection       7-32         7.8.9       Other DEMDEC Control Options       7-33         7.8.9       Other DEMDEC Control Options       7-37         7.8.10       DEMDEC Status Registers       7-37         <                                                                                |         |                             |

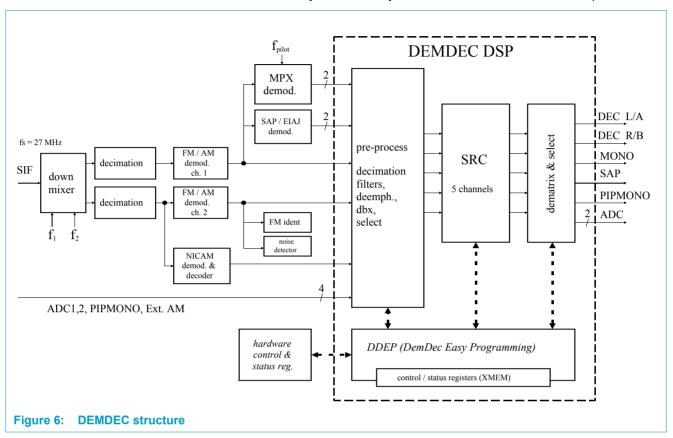

| 7.8Demdec DSP.7-117.8.1DDEP in Brief7-127.8.2What DDEP Does NOT Do.7-137.8.3Design Considerations7-147.8.4DDEP Basics and Usage7-157.8.5DEMDEC Hardware Blocks and the<br>Sample Rate Problem7-157.8.6Signal Processing in DSP Software7-167.8.7SRC constraints7-197.8.8The DDEP Control Register7-237.8.8.1Mode Selection7-247.8.8.2Starting and Restarting7-247.8.8.3DDEP Control Variables7-247.8.8.4Dependencies Between Variables in<br>the DDEPR7-277.8.8.5Automute Function7-277.8.8.6NICAM Configuration7-287.8.8.7Amplitude and Noise Threshold Registers7-307.8.8.8SAP Detection7-327.8.9Other DEMDEC Control Options7-337.8.10Status Registers7-377.8.10.1DEMDEC Status Register7-377.8.10.2NICAM Status Registers7-407.8.11Noise Detection7-417.8.12Muting all DEMDEC Outputs7-417.8.13Application Related Constant Settings7-427.8.13.3Auto-tune Process7-42                                                                                                                                                                                                                                                                                                                                                                                                |         |                             |

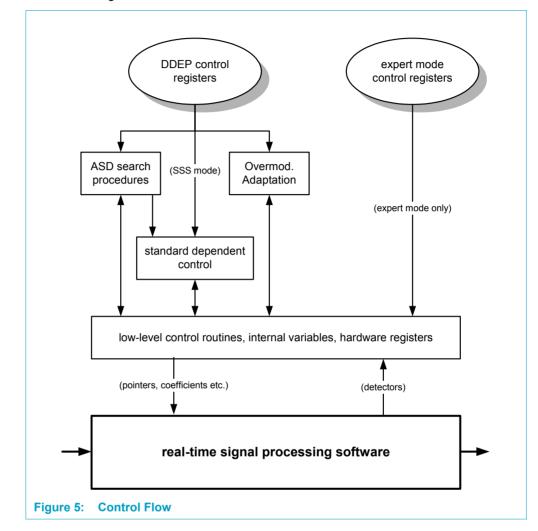

| 7.8.1DDEP in Brief7-127.8.2What DDEP Does NOT Do.7-137.8.3Design Considerations7-147.8.4DDEP Basics and Usage7-157.8.5DEMDEC Hardware Blocks and the<br>Sample Rate Problem7-157.8.6Signal Processing in DSP Software7-167.8.7SRC constraints7-197.8.8The DDEP Control Register7-237.8.8.1Mode Selection7-237.8.8.2Starting and Restarting7-247.8.8.3DDEP Control Variables7-247.8.8.4Dependencies Between Variables in<br>the DDEPR7-277.8.8.5Automute Function7-277.8.8.6NICAM Configuration7-287.8.8.7Amplitude and Noise Threshold Registers7-307.8.8.8SAP Detection7-327.8.9Citharnel Control7-367.8.10Status Registers7-377.8.10.1DEMDEC Status Register7-377.8.10.2NICAM Status Registers7-407.8.11Noise Detection7-417.8.12Muting all DEMDEC Outputs7-417.8.13Jsing DDEP in a Set Design7-427.8.13.1Application Related Constant Settings7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                       | 7.7     | Digital-Analogue Converters |

| 7.8.2What DDEP Does NOT Do.7-137.8.3Design Considerations7-147.8.4DDEP Basics and Usage7-157.8.5DEMDEC Hardware Blocks and the<br>Sample Rate Problem7-157.8.6Signal Processing in DSP Software7-167.8.7SRC constraints7-197.8.8The DDEP Control Register7-237.8.8.1Mode Selection7-247.8.8.2Starting and Restarting7-247.8.8.3DDEP Control Variables7-277.8.8.4Dependencies Between Variables in<br>the DDEPR7-277.8.8.5Automute Function7-277.8.8.6NICAM Configuration7-287.8.8.7Amplitude and Noise Threshold Registers7-307.8.8.8SAP Detection7-327.8.9Other DEMDEC Control Options7-337.8.10Status Registers7-377.8.10.1DEMDEC Status Register7-377.8.10.2NICAM Status Registers7-407.8.11Noise Detection7-417.8.12Muting all DEMDEC Outputs7-417.8.13Jusing DDEP in a Set Design7-427.8.13.1Application Related Constant Settings7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                 | 7.8     | Demdec DSP                  |

| 7.8.3Design Considerations7-147.8.4DDEP Basics and Usage7-157.8.5DEMDEC Hardware Blocks and the<br>Sample Rate Problem7-157.8.6Signal Processing in DSP Software7-167.8.7SRC constraints7-197.8.8The DDEP Control Register7-237.8.8.1Mode Selection7-247.8.8.2Starting and Restarting7-247.8.8.3DDEP Control Variables7-247.8.8.4Dependencies Between Variables in<br>the DDEPR7-277.8.8.5Automute Function7-277.8.8.6NICAM Configuration7-287.8.8.7Amplitude and Noise Threshold Registers7-307.8.8.8SAP Detection7-327.8.9Cither DEMDEC Control Options7-337.8.10Status Registers7-377.8.10.1DEMDEC Status Registers7-377.8.10.2NICAM Status Registers7-407.8.11Noise Detection7-417.8.12Muting all DEMDEC Outputs7-417.8.13Application Related Constant Settings7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7.8.1   | DDEP in Brief               |

| 7.8.4DDEP Basics and Usage7-157.8.5DEMDEC Hardware Blocks and the<br>Sample Rate Problem7-157.8.6Signal Processing in DSP Software7-167.8.7SRC constraints7-197.8.8The DDEP Control Register7-237.8.8.1Mode Selection7-247.8.8.2Starting and Restarting7-247.8.8.3DDEP Control Variables7-247.8.8.4Dependencies Between Variables in<br>the DDEPR7-277.8.8.5Automute Function7-277.8.8.6NICAM Configuration7-287.8.8.7Amplitude and Noise Threshold Registers7-307.8.8.8SAP Detection7-327.8.9EIAJ Subcarrier Detection7-327.8.10Status Registers7-377.8.10.1DEMDEC Status Registers7-377.8.10.2NICAM Status Registers7-407.8.11Noise Detection7-417.8.12Muting all DEMDEC Outputs7-417.8.13.1Application Related Constant Settings7-427.8.13.2Prerequisites and User Interface7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7.8.2   |                             |

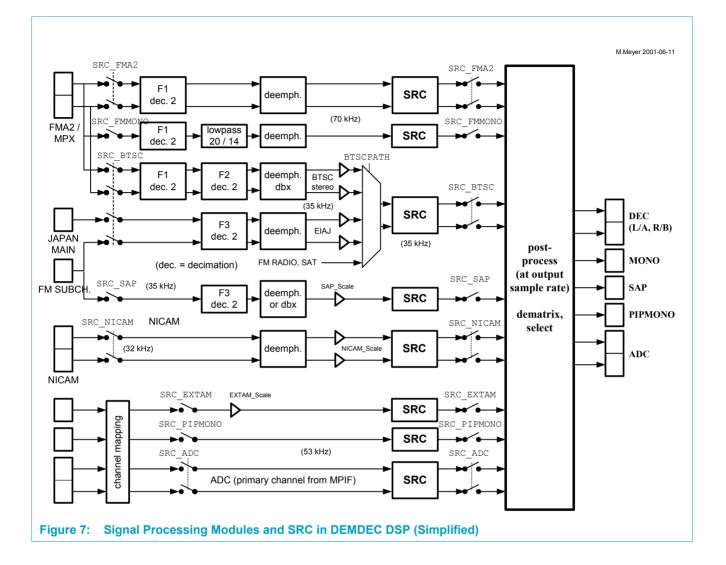

| 7.8.5DEMDEC Hardware Blocks and the<br>Sample Rate Problem7-157.8.6Signal Processing in DSP Software7-167.8.7SRC constraints7-197.8.8The DDEP Control Register7-237.8.8.1Mode Selection7-237.8.8.2Starting and Restarting7-247.8.8.3DDEP Control Variables7-247.8.8.4Dependencies Between Variables in<br>the DDEPR7-277.8.8.5Automute Function7-277.8.8.6NICAM Configuration7-287.8.8.7Amplitude and Noise Threshold Registers7-307.8.8.8SAP Detection7-327.8.9EIAJ Subcarrier Detection7-327.8.10Status Registers7-377.8.10.1DEMDEC Status Registers7-377.8.10.2NICAM Status Registers7-407.8.11Noise Detection7-417.8.12Muting all DEMDEC Outputs7-417.8.13Application Related Constant Settings7-427.8.13.3Auto-tune Process7-42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7.8.3   |                             |

| Sample Rate Problem7-157.8.6Signal Processing in DSP Software7-167.8.7SRC constraints7-197.8.8The DDEP Control Register7-237.8.8.1Mode Selection7-237.8.8.2Starting and Restarting7-247.8.8.3DDEP Control Variables7-247.8.8.4Dependencies Between Variables in<br>the DDEPR7-277.8.8.5Automute Function7-277.8.8.6NICAM Configuration7-287.8.8.7Amplitude and Noise Threshold Registers7-307.8.8.8SAP Detection7-327.8.9EIAJ Subcarrier Detection7-327.8.10Status Registers7-377.8.10.1DEMDEC Status Registers7-377.8.10.2NICAM Status Registers7-407.8.11Noise Detection7-417.8.12Muting all DEMDEC Outputs7-417.8.13Using DDEP in a Set Design7-427.8.13.2Prerequisites and User Interface7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -       |                             |

| 7.8.6Signal Processing in DSP Software7-167.8.7SRC constraints7-197.8.8The DDEP Control Register7-237.8.8.1Mode Selection7-237.8.8.2Starting and Restarting7-247.8.8.3DDEP Control Variables7-247.8.8.4Dependencies Between Variables in<br>the DDEPR7-277.8.8.5Automute Function7-277.8.8.6NICAM Configuration7-287.8.8.7Amplitude and Noise Threshold Registers7-307.8.8.8SAP Detection7-327.8.9EIAJ Subcarrier Detection7-327.8.10Status Registers7-377.8.10.1DEMDEC Control Options7-377.8.10.2NICAM Status Registers7-377.8.10.2NICAM Status Registers7-407.8.11Noise Detection7-417.8.12Muting all DEMDEC Outputs7-417.8.13Using DDEP in a Set Design7-427.8.13.1Application Related Constant Settings7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7.8.5   |                             |

| 7.8.7SRC constraints7-197.8.8The DDEP Control Register7-237.8.8.1Mode Selection7-237.8.8.2Starting and Restarting7-247.8.8.3DDEP Control Variables7-247.8.8.4Dependencies Between Variables in<br>the DDEPR7-277.8.8.5Automute Function7-277.8.8.6NICAM Configuration7-287.8.8.7Amplitude and Noise Threshold Registers7-307.8.8.8SAP Detection7-327.8.9EIAJ Subcarrier Detection7-327.8.10Status Registers7-377.8.10.1DEMDEC Status Register7-377.8.10.2NICAM Status Registers7-407.8.11Noise Detection7-417.8.12Muting all DEMDEC Outputs7-417.8.13Using DDEP in a Set Design7-427.8.13.2Prerequisites and User Interface7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                             |

| 7.8.8The DDEP Control Register7-237.8.8.1Mode Selection7-237.8.8.2Starting and Restarting7-247.8.8.3DDEP Control Variables7-247.8.8.4Dependencies Between Variables in<br>the DDEPR7-277.8.8.5Automute Function7-277.8.8.6NICAM Configuration7-287.8.8.7Amplitude and Noise Threshold Registers7-307.8.8.8SAP Detection7-327.8.9EIAJ Subcarrier Detection7-327.8.10Status Registers7-377.8.10.1DEMDEC Status Register7-377.8.10.2NICAM Status Registers7-407.8.11Noise Detection7-417.8.12Muting all DEMDEC Outputs7-417.8.13Using DDEP in a Set Design7-427.8.13.2Prerequisites and User Interface7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                             |

| 7.8.8.1Mode Selection7-237.8.8.2Starting and Restarting7-247.8.8.3DDEP Control Variables7-247.8.8.4Dependencies Between Variables in<br>the DDEPR7-277.8.8.5Automute Function7-277.8.8.6NICAM Configuration7-287.8.8.7Amplitude and Noise Threshold Registers7-307.8.8.8SAP Detection7-327.8.9EIAJ Subcarrier Detection7-327.8.9Other DEMDEC Control Options7-337.8.10Status Registers7-377.8.10.1DEMDEC Status Register7-377.8.10.2NICAM Status Registers7-407.8.11Noise Detection7-417.8.12Muting all DEMDEC Outputs7-417.8.13Using DDEP in a Set Design7-427.8.13.2Prerequisites and User Interface7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -       |                             |

| 7.8.8.2Starting and Restarting7-247.8.8.3DDEP Control Variables7-247.8.8.4Dependencies Between Variables in<br>the DDEPR7-277.8.8.5Automute Function7-277.8.8.6NICAM Configuration7-287.8.8.7Amplitude and Noise Threshold Registers7-307.8.8.8SAP Detection7-327.8.9EIAJ Subcarrier Detection7-327.8.10Status Registers7-377.8.10Status Registers7-377.8.10.1DEMDEC Status Registers7-377.8.10.2NICAM Status Registers7-407.8.13Using DDEP in a Set Design7-427.8.13.1Application Related Constant Settings7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |                             |

| 7.8.8.3DDEP Control Variables7-247.8.8.4Dependencies Between Variables in<br>the DDEPR7-277.8.8.5Automute Function7-277.8.8.6NICAM Configuration7-287.8.8.7Amplitude and Noise Threshold Registers7-307.8.8.8SAP Detection7-327.8.9EIAJ Subcarrier Detection7-327.8.9Other DEMDEC Control Options7-337.8.10Status Registers7-377.8.10.1DEMDEC Status Registers7-377.8.10.2NICAM Status Registers7-407.8.11Noise Detection7-417.8.12Muting all DEMDEC Outputs7-417.8.13Using DDEP in a Set Design7-427.8.13.2Prerequisites and User Interface7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |                             |

| 7.8.8.4Dependencies Between Variables in<br>the DDEPR7-277.8.8.5Automute Function7-277.8.8.6NICAM Configuration7-287.8.8.7Amplitude and Noise Threshold Registers7-307.8.8.8SAP Detection7-327.8.8.9EIAJ Subcarrier Detection7-327.8.9Other DEMDEC Control Options7-337.8.9.1ADC Channel Control7-367.8.10Status Registers7-377.8.10.1DEMDEC Status Registers7-407.8.11Noise Detection7-417.8.12Muting all DEMDEC Outputs7-417.8.13Using DDEP in a Set Design7-427.8.13.1Application Related Constant Settings7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |                             |

| the DDEPR         7-27           7.8.8.5         Automute Function         7-27           7.8.8.5         Automute Function         7-27           7.8.8.6         NICAM Configuration         7-28           7.8.8.7         Amplitude and Noise Threshold Registers         7-30           7.8.8.8         SAP Detection         7-32           7.8.8.9         EIAJ Subcarrier Detection         7-32           7.8.9         Other DEMDEC Control Options         7-33           7.8.9.1         ADC Channel Control         7-36           7.8.10         Status Registers         7-37           7.8.10.1         DEMDEC Status Register         7-37           7.8.10.2         NICAM Status Registers         7-40           7.8.11         Noise Detection         7-41           7.8.12         Muting all DEMDEC Outputs         7-41           7.8.13         Using DDEP in a Set Design         7-42           7.8.13.1         Application Related Constant Settings         7-42           7.8.13.2         Prerequisites and User Interface         7-42           7.8.13.3         Auto-tune Process         7-44                                                                                                                                       |         |                             |

| 7.8.8.5       Automute Function       7-27         7.8.8.6       NICAM Configuration       7-28         7.8.8.7       Amplitude and Noise Threshold Registers       7-30         7.8.8.8       SAP Detection       7-32         7.8.8.9       EIAJ Subcarrier Detection       7-32         7.8.9       Other DEMDEC Control Options       7-33         7.8.9       Other DEMDEC Control Options       7-36         7.8.10       Status Registers       7-37         7.8.10.1       DEMDEC Status Registers       7-37         7.8.10.2       NICAM Status Registers       7-40         7.8.11       Noise Detection       7-41         7.8.12       Muting all DEMDEC Outputs       7-41         7.8.13       Using DDEP in a Set Design       7-42         7.8.13.1       Application Related Constant Settings       7-42         7.8.13.2       Prerequisites and User Interface       7-42         7.8.13.3       Auto-tune Process       7-44                                                                                                                                                                                                                                                                                                                       | 1.0.0.1 |                             |

| 7.8.8.6       NICAM Configuration       7-28         7.8.8.7       Amplitude and Noise Threshold Registers.       7-30         7.8.8.8       SAP Detection       7-32         7.8.8.9       EIAJ Subcarrier Detection       7-32         7.8.9       Other DEMDEC Control Options       7-33         7.8.9       Other DEMDEC Control Options       7-36         7.8.10       Status Registers       7-37         7.8.10.1       DEMDEC Status Registers       7-40         7.8.10.2       NICAM Status Registers       7-41         7.8.12       Nuing all DEMDEC Outputs       7-41         7.8.13       Using DDEP in a Set Design       7-42         7.8.13.1       Application Related Constant Settings       7-42         7.8.13.2       Prerequisites and User Interface       7-42         7.8.13.3       Auto-tune Process       7-44                                                                                                                                                                                                                                                                                                                                                                                                                          | 7.8.8.5 |                             |

| 7.8.8.7       Amplitude and Noise Threshold Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7.8.8.6 |                             |

| 7.8.8.9       EIAJ Subcarrier Detection.       7-32         7.8.9       Other DEMDEC Control Options.       7-33         7.8.9       ADC Channel Control       7-36         7.8.10       Status Registers.       7-37         7.8.10.1       DEMDEC Status Register.       7-37         7.8.10.2       NICAM Status Registers.       7-40         7.8.11       Noise Detection.       7-41         7.8.12       Muting all DEMDEC Outputs       7-41         7.8.13       Using DDEP in a Set Design       7-42         7.8.13.1       Application Related Constant Settings.       7-42         7.8.13.2       Prerequisites and User Interface       7-42         7.8.13.3       Auto-tune Process       7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7.8.8.7 |                             |

| 7.8.8.9       EIAJ Subcarrier Detection.       7-32         7.8.9       Other DEMDEC Control Options.       7-33         7.8.9       ADC Channel Control       7-36         7.8.10       Status Registers.       7-37         7.8.10.1       DEMDEC Status Register.       7-37         7.8.10.2       NICAM Status Registers.       7-40         7.8.11       Noise Detection.       7-41         7.8.12       Muting all DEMDEC Outputs       7-41         7.8.13       Using DDEP in a Set Design       7-42         7.8.13.1       Application Related Constant Settings.       7-42         7.8.13.2       Prerequisites and User Interface       7-42         7.8.13.3       Auto-tune Process       7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7.8.8.8 | SAP Detection               |

| 7.8.9.1ADC Channel Control7-367.8.10Status Registers7-377.8.10.1DEMDEC Status Register7-377.8.10.2NICAM Status Registers7-407.8.11Noise Detection7-417.8.12Muting all DEMDEC Outputs7-417.8.13Using DDEP in a Set Design7-427.8.13.1Application Related Constant Settings7-427.8.13.2Prerequisites and User Interface7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7.8.8.9 | EIAJ Subcarrier Detection   |

| 7.8.10Status Registers7-377.8.10.1DEMDEC Status Register7-377.8.10.2NICAM Status Registers7-407.8.11Noise Detection7-417.8.12Muting all DEMDEC Outputs7-417.8.13Using DDEP in a Set Design7-427.8.13.1Application Related Constant Settings7-427.8.13.2Prerequisites and User Interface7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7.8.9   |                             |

| 7.8.10.1DEMDEC Status Register.7-377.8.10.2NICAM Status Registers7-407.8.11Noise Detection.7-417.8.12Muting all DEMDEC Outputs7-417.8.13Using DDEP in a Set Design7-427.8.13.1Application Related Constant Settings7-427.8.13.2Prerequisites and User Interface7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7.8.9.1 |                             |

| 7.8.10.2NICAM Status Registers7-407.8.11Noise Detection7-417.8.12Muting all DEMDEC Outputs7-417.8.13Using DDEP in a Set Design7-427.8.13.1Application Related Constant Settings7-427.8.13.2Prerequisites and User Interface7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         | Status Registers 7-37       |

| 7.8.11Noise Detection.7-417.8.12Muting all DEMDEC Outputs7-417.8.13Using DDEP in a Set Design7-427.8.13.1Application Related Constant Settings7-427.8.13.2Prerequisites and User Interface7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |                             |

| 7.8.12Muting all DEMDEC Outputs7-417.8.13Using DDEP in a Set Design7-427.8.13.1Application Related Constant Settings7-427.8.13.2Prerequisites and User Interface7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                             |

| 7.8.13Using DDEP in a Set Design7-427.8.13.1Application Related Constant Settings7-427.8.13.2Prerequisites and User Interface7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -       |                             |

| 7.8.13.1Application Related Constant Settings7-427.8.13.2Prerequisites and User Interface7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | •                           |

| 7.8.13.2Prerequisites and User Interface7-427.8.13.3Auto-tune Process7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                             |

| 7.8.13.3 Auto-tune Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |                             |

| 7.8.13.4 Channel Switch Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                             |

| 7.8.14               | Details of Operation                                                      | 7-45  |

|----------------------|---------------------------------------------------------------------------|-------|

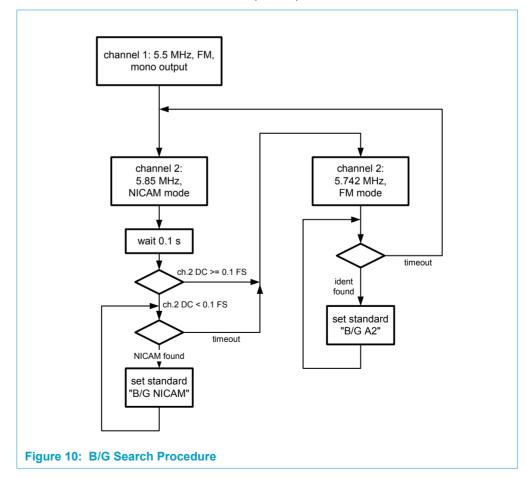

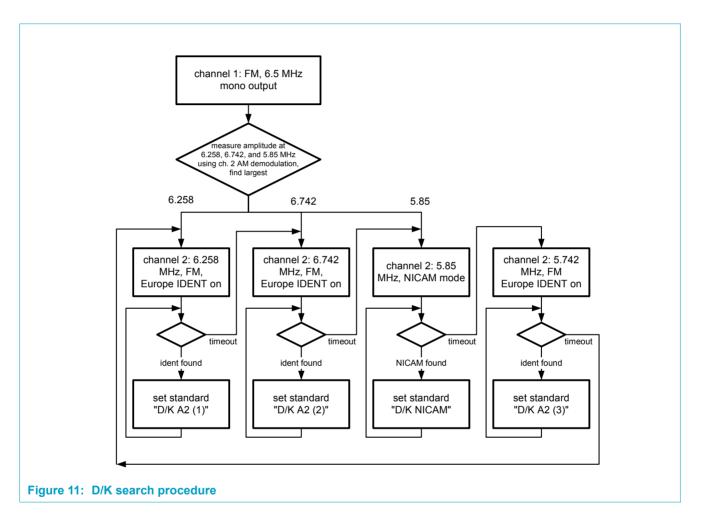

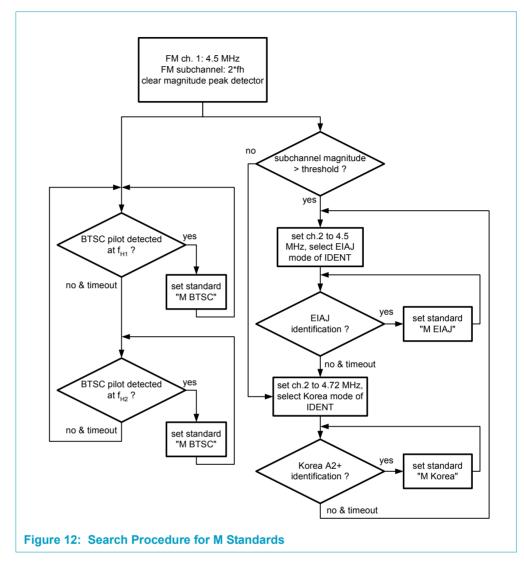

| 7.8.14.1             | Search Procedures (ASD Mode)                                              | 7-45  |

| 7.8.14.2             | Using the SSS Mode                                                        | 7-52  |

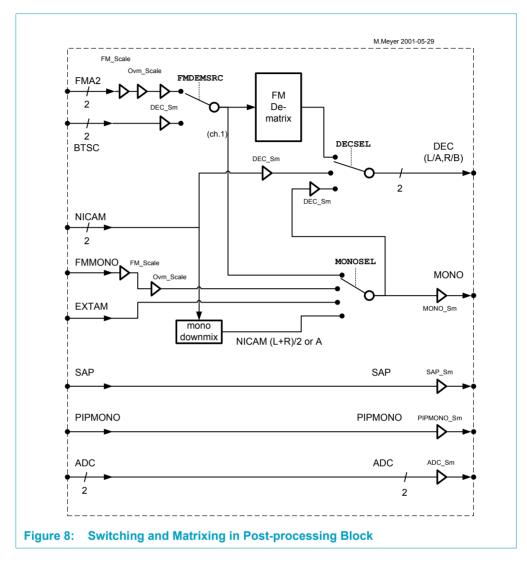

| 7.8.14.3             | Automatic Signal Switching and Routing .                                  | 7-54  |

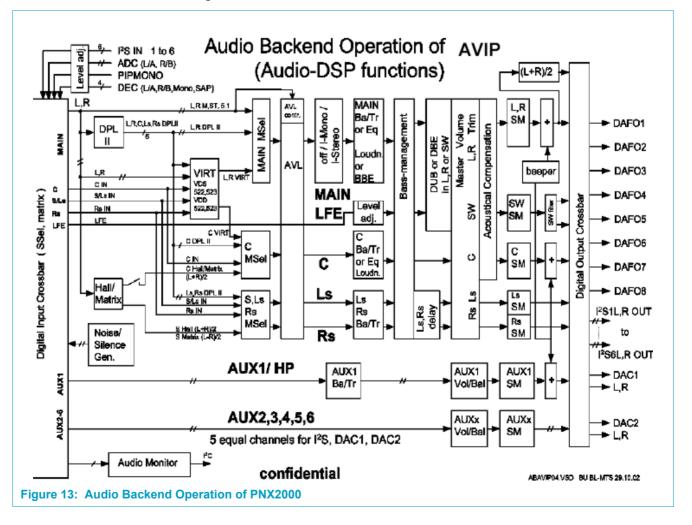

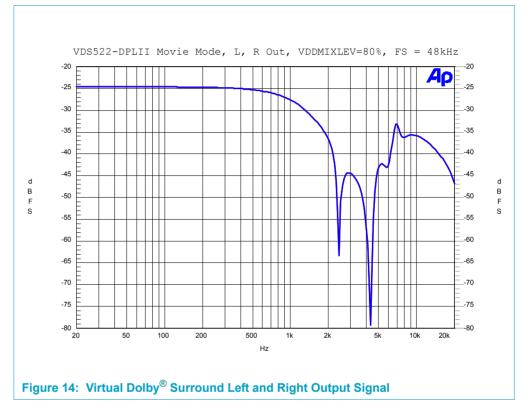

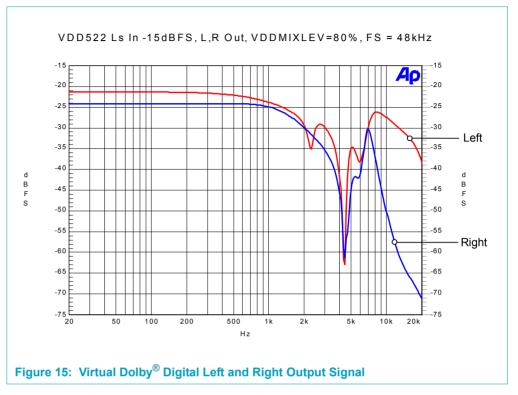

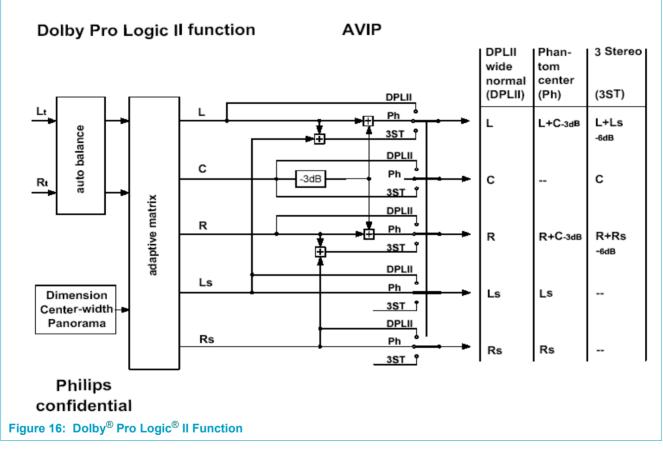

| 7.9 A                | UDIO-DSP                                                                  | 7-59  |

| 7.9.1                | Functional Overview                                                       | 7-59  |

| 7.9.2                | Loudspeaker Channel Sound Modes                                           |       |

| 7.9.3                | Comments about Function Control                                           | 7-63  |

| 7.9.3.1              | Automatic Volume Levelling (AVL)                                          |       |