# Precision RTL Synthesis Users Manual

2003c Update1

March 2004

Copyright © Mentor Graphics Corporation 2002-2004.

All rights reserved.

This document contains information that is proprietary to Mentor Graphics Corporation. The original recipient of this document may duplicate this document in whole or in part for internal business purposes only, provided that this entire notice appears in all copies. In duplicating any part of this document, the recipient agrees to make every reasonable effort to prevent the unauthorized use and distribution of the proprietary information.

End-User License Agreement

Trademark Information

This document is for information and instruction purposes. Mentor Graphics reserves the right to make changes in specifications and other information contained in this publication without prior notice, and the reader should, in all cases, consult Mentor Graphics to determine whether any changes have been made.

The terms and conditions governing the sale and licensing of Mentor Graphics products are set forth in written agreements between Mentor Graphics and its customers. No representation or other affirmation of fact contained in this publication shall be deemed to be a warranty or give rise to any liability of Mentor Graphics whatsoever.

MENTOR GRAPHICS MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OR MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

MENTOR GRAPHICS SHALL NOT BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL, OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATED TO THIS PUBLICATION OR THE INFORMATION CONTAINED IN IT, EVEN IF MENTOR GRAPHICS CORPORATION HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

#### **RESTRICTED RIGHTS LEGEND 03/97**

U.S. Government Restricted Rights. The SOFTWARE and documentation have been developed entirely at private expense and are commercial computer software provided with restricted rights. Use, duplication or disclosure by the U.S. Government or a U.S. Government subcontractor is subject to the restrictions set forth in the license agreement provided with the software pursuant to DFARS 227.7202-3(a) or as set forth in subparagraph (c)(1) and (2) of the Commercial Computer Software - Restricted Rights clause at FAR 52.227-19, as applicable.

Contractor/manufacturer is:

Mentor Graphics Corporation

8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777.

This is an unpublished work of Mentor Graphics Corporation.

# **Table of Contents**

| About This Manual                                       | ix   |

|---------------------------------------------------------|------|

| Chapter 1                                               |      |

| Introducing Precision RTL Synthesis                     | 1-1  |

| Precision RTL Synthesis Features                        | 1-1  |

| Intuitive User Interface                                |      |

| Project Manager                                         |      |

| Advanced Synthesis Algorithms                           |      |

| Constraint Driven Synthesis                             |      |

| Boundaryless Optimization                               |      |

| FSM Optimization                                        |      |

| PreciseTimeTM Timing Analysis                           |      |

| Interactive Timing Analysis                             |      |

| Register Retiming                                       |      |

| Schematic Viewing with Critical Path Fragment Filtering |      |

| Integrated Creation and Analysis Tools                  |      |

| Design Bar                                              |      |

| HDLInventor                                             |      |

| Project Browser                                         | 1-5  |

| Design Browser                                          |      |

| Schematic Viewing                                       | 1-6  |

| P&RIntegrator                                           | 1-6  |

| Documentation Available Online                          | 1-7  |

| Context-Sensitive Help                                  | 1-7  |

| Product Manuals                                         | 1-8  |

| Chapter 2                                               |      |

| Setting Up a Design and Compiling                       | 2-1  |

|                                                         |      |

| Invoking Precision RTL Synthesis                        |      |

| Invoking the Precision GUI                              |      |

| Invoking Precision from a Shell                         |      |

| Setting up the Design Environment                       |      |

| The Project Directory and the Results Directory         |      |

| Setting the Input Directory                             |      |

| Setting the Technology                                  |      |

| Adding Input Files to the Project                       |      |

| Setting Synthesis Options                               |      |

| Compiling the Design                                    |      |

| Evaluating the Results                                  |      |

| Setting Timing and Design Constraints                   |      |

| Synthesizing the Design                                 |      |

| Evaluating the Results                                  | 2-19 |

# **Table of Contents (cont.)**

| Performing Initial Place and Route                        | 2-22 |

|-----------------------------------------------------------|------|

| Chapter 3                                                 |      |

| Setting Constraints and Synthesizing                      | 3-1  |

| Managing a Master Constraint File                         | 3-1  |

| Creating a Master Constraint File                         |      |

| Maintaining a Master Constraint File                      |      |

| Setting Timing Constraints                                |      |

| Setting Global Timing Constraints                         |      |

| Clocks Overview                                           |      |

| Derived Clocks                                            |      |

| Report Timing and Clock Names                             |      |

| Specifying Clock Constraints                              | 3-7  |

| Handling Multiple Clocks                                  | 3-9  |

| Specifying Input Delay                                    | 3-10 |

| Specifying Output Delay                                   | 3-13 |

| Setting False Paths                                       |      |

| Setting Multicycle Paths                                  | 3-17 |

| Setting Mapping Constraints                               | 3-18 |

| Mapping Ports to Pin Numbers and IO Pads                  | 3-18 |

| Mapping Operators, Counters, and Memory to Chip Resources | 3-21 |

| Setting Other Constraints                                 | 3-21 |

| Controlling Hierarchy                                     | 3-21 |

| Protecting Blocks from Change (dont_touch)                | 3-23 |

| Controlling Fanout on Data Nets                           | 3-23 |

| Chapter 4                                                 |      |

| Managing Projects                                         | 4-1  |

| The Project Manager                                       | 4-1  |

| Bypassing the Project Manager                             |      |

| Using the Project Manager Interactively                   |      |

| Creating a Project.                                       |      |

| Opening a Project                                         |      |

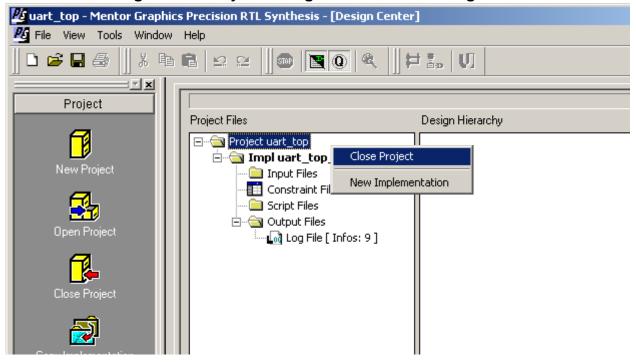

| Closing a Project                                         |      |

| Setting Up the Implementation                             | 4-10 |

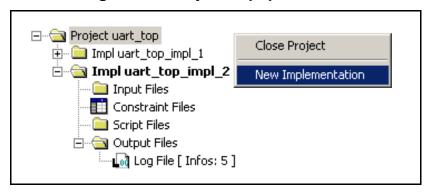

| Creating a New Implementation                             |      |

| Creating an Implementation from the Command Line          |      |

| Saving the Active Implementation                          |      |

| Renaming an Implementation                                |      |

| Activating an Implementation                              |      |

| Copying an Implementation                                 |      |

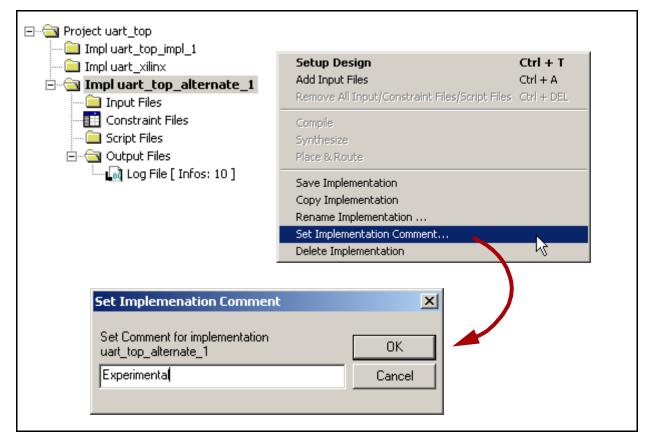

| Commenting an Implementation                              | 4-15 |

# **Table of Contents (cont.)**

| Deleting an Implementation                                           | 4-17 |

|----------------------------------------------------------------------|------|

| Creating a Script from a Precision.log File                          |      |

| Scripts for Creating New Projects or Reusing Existing Projects       |      |

| Exporting your Settings                                              | 4-20 |

| Actions to Take if the Project, Input Directory, or Input Files Move |      |

| Backward Compatibility with Pre-2003c Projects                       |      |

| Chamter 5                                                            |      |

| Chapter 5 Viewing a Schematic                                        | 5_1  |

|                                                                      |      |

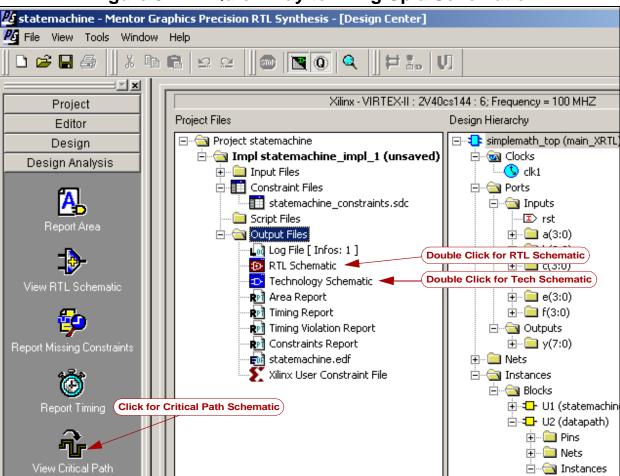

| A Quick Way to Bring Up a Schematic                                  | 5-1  |

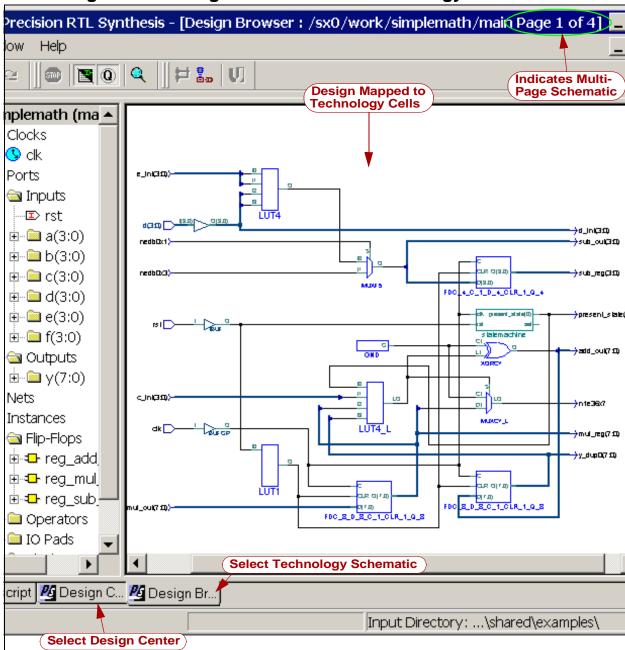

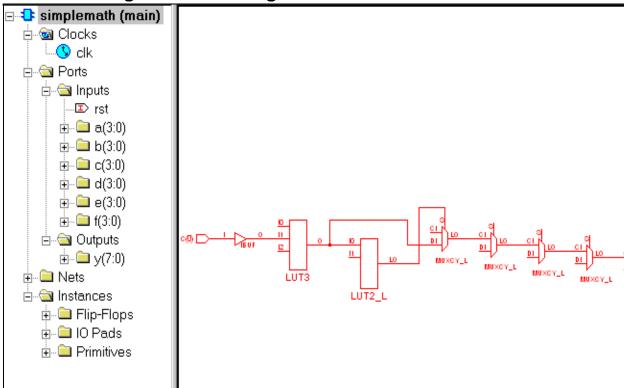

| Viewing the RTL Schematic.                                           |      |

| Viewing the Technology Schematic                                     |      |

| Viewing the Critical Path Schematic                                  | 5-4  |

| Understanding the Left Mouse Button Actions                          | 5-5  |

| Traversing the Schematic with Strokes                                |      |

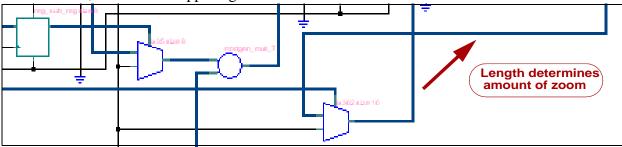

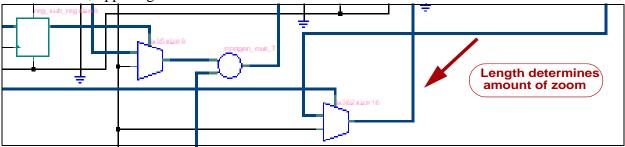

| Zooming to Area                                                      | 5-5  |

| Zooming Out                                                          | 5-6  |

| Zooming In                                                           | 5-6  |

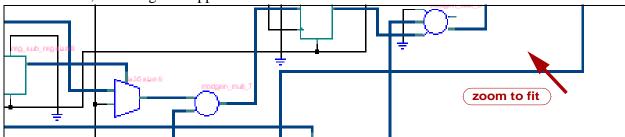

| Zooming to Fit                                                       | 5-6  |

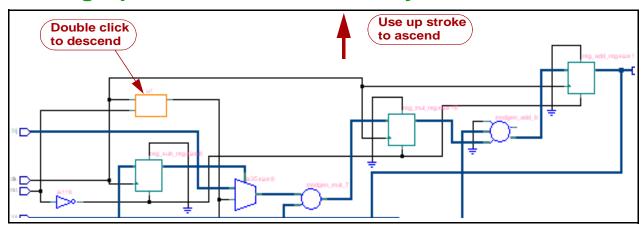

| Moving Up and Down the Hierarchy                                     | 5-7  |

| Paging Forward ( ) and Paging Back ( )                               | 5-7  |

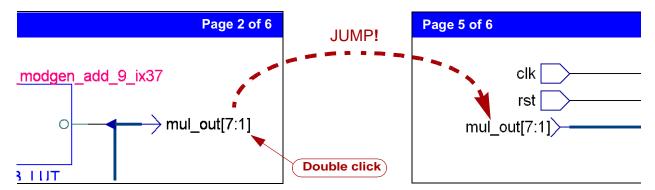

| Tracing a Signal to the Next Page                                    | 5-8  |

| Panning the Schematic                                                | 5-8  |

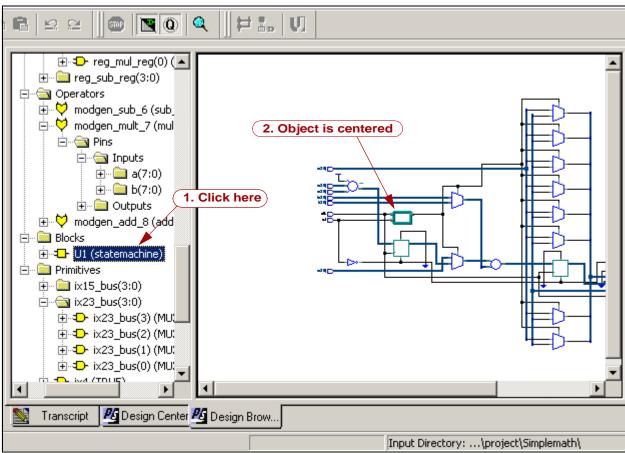

| Centering an Object in the Schematic View                            | 5-9  |

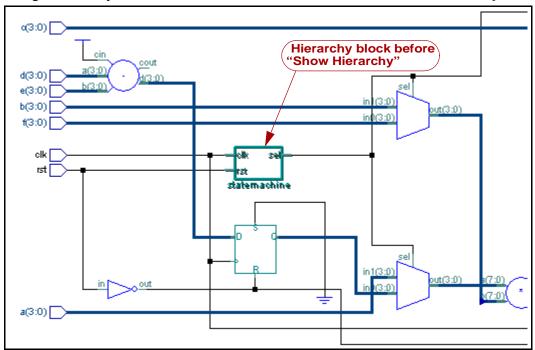

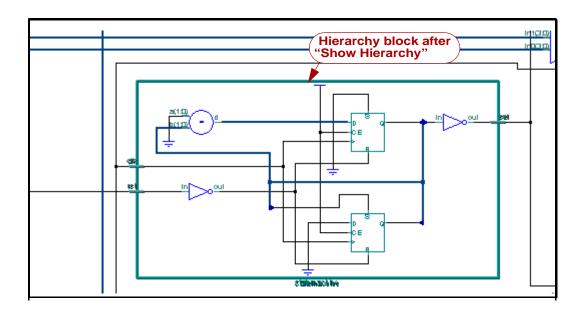

| Viewing the Internals of a Hierarchy Block                           | 5-10 |

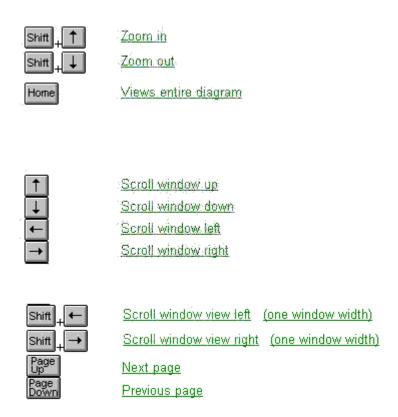

| Traversing the Schematic Using Keyboard shortcuts                    | 5-11 |

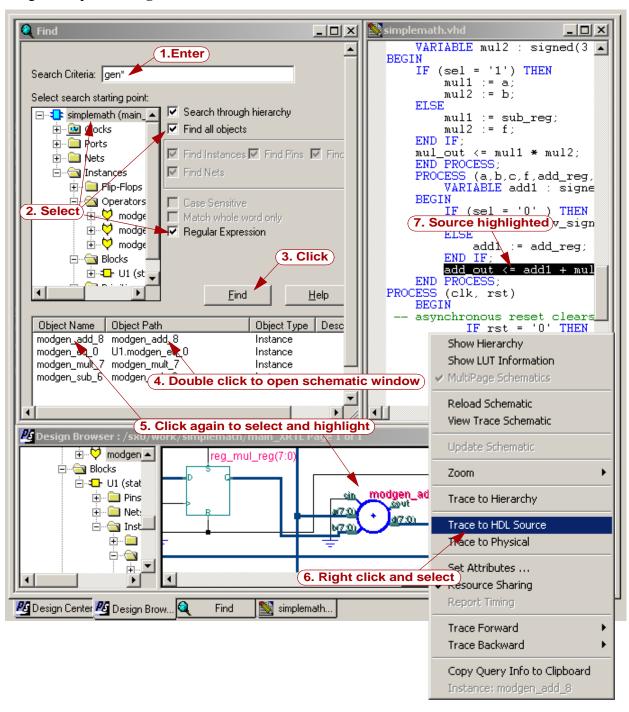

| Using the Cross Probe Features                                       | 5-12 |

| Cross Probing from Schematic to the HDL Source                       | 5-12 |

| Cross Probing to HDL Designer from Precision RTL Synthesis           | 5-12 |

| Viewing Schematic Fragments                                          | 5-13 |

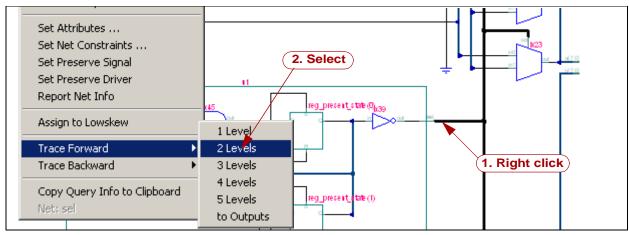

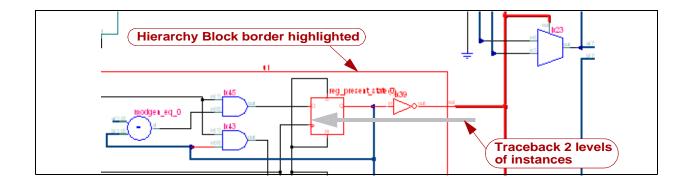

| Tracing a Signal                                                     | 5-13 |

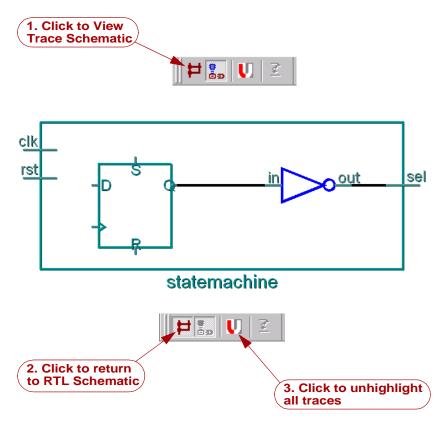

| Viewing a Trace Schematic                                            | 5-14 |

| Click and Sprout the Trace Path                                      | 5-14 |

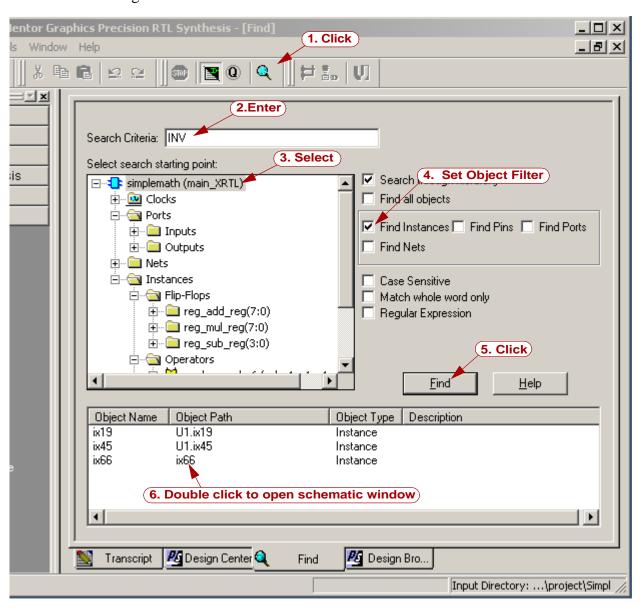

| Using the Find Window Features                                       |      |

| Conducting a Simple Search for Objects                               |      |

| Searching for Objects Using Regular Expressions                      |      |

| Setting Schematic Viewing Options                                    |      |

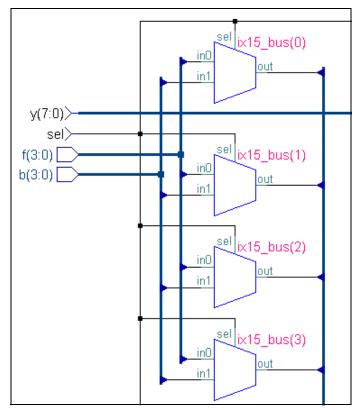

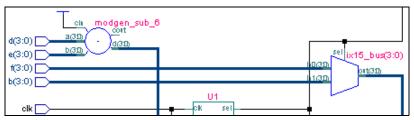

| Understanding the Term "Bused Instance"                              |      |

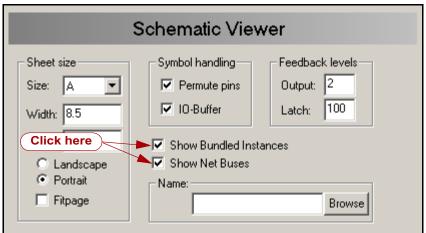

| Viewing Bundled Instances and Net Buses                              |      |

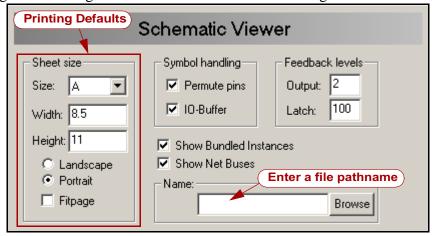

| Changing the Schematic Printing Defaults                             |      |

| Changing the Way Symbols are Handled                                 |      |

| Changing the Placement of Output Devices                             |      |

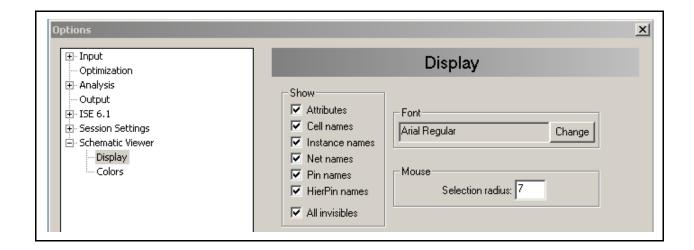

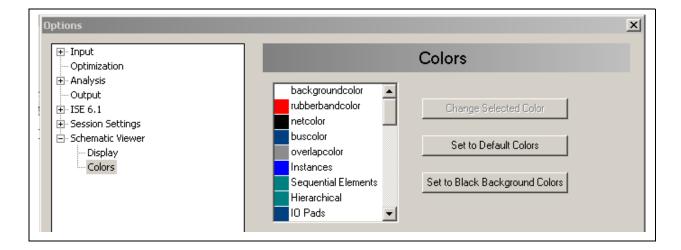

| Changing the Viewer Display and Color Options                        |      |

# **List of Figures**

| Figure 2-1. | The Design Center Window                                      | 2-3  |

|-------------|---------------------------------------------------------------|------|

|             | Specifying Input File Properties                              |      |

| Figure 2-3. | Preparing the Input UCF File                                  | 2-18 |

| Figure 2-1. | The Constraint Relationship                                   | 2-21 |

| Figure 3-1. | Clocks Example                                                | 3-4  |

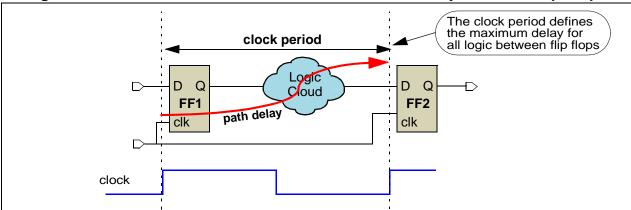

| Figure 3-2. | The Clock Period Defines the Maximum Delay Between Flip Flops | 3-7  |

| Figure 3-3. | Setting the Clock Constraints from the GUI                    | 3-8  |

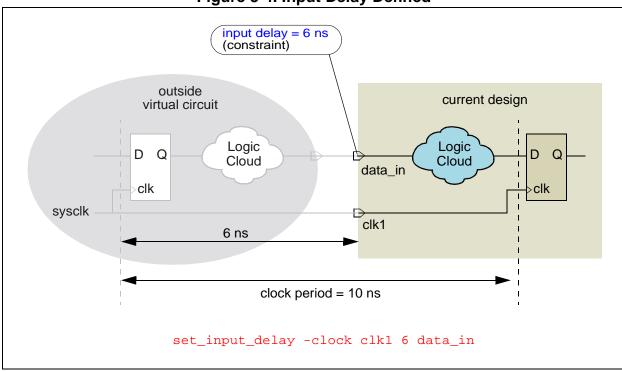

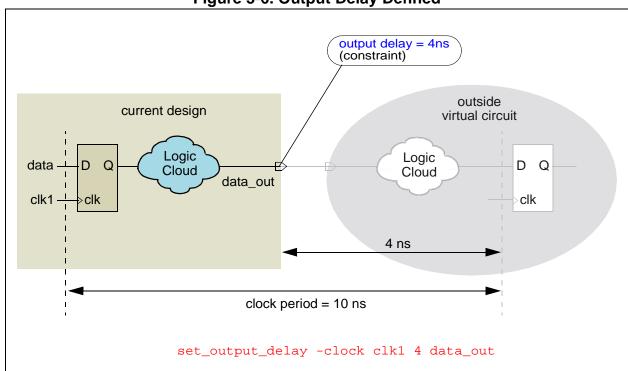

| Figure 3-4. | Input Delay Defined                                           | 3-10 |

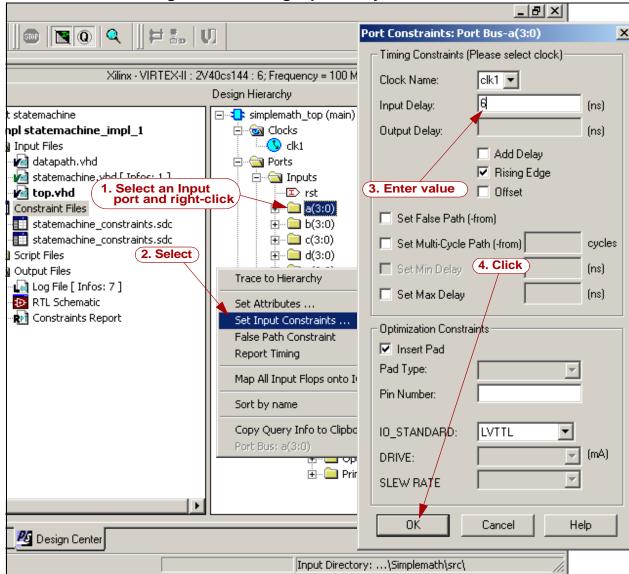

| Figure 3-5. | Setting Input Delay from the GUI                              | 3-11 |

|             | Output Delay Defined                                          |      |

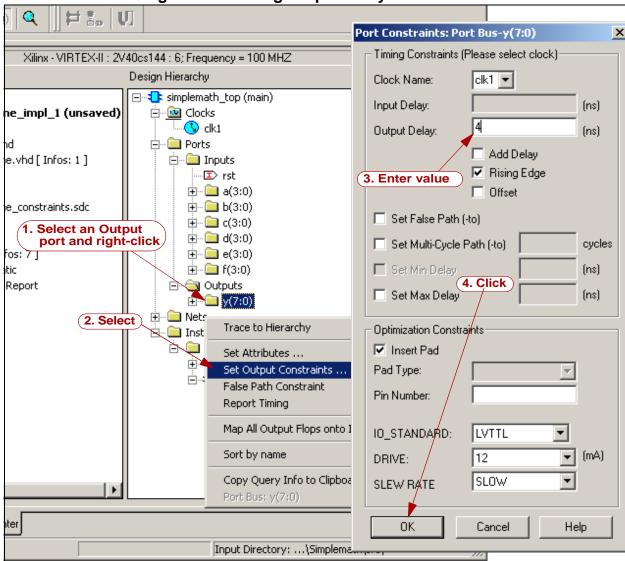

| Figure 3-7. | Setting Output Delay from the GUI                             | 3-14 |

| Figure 3-8. | Setting a False Path from the GUI                             | 3-16 |

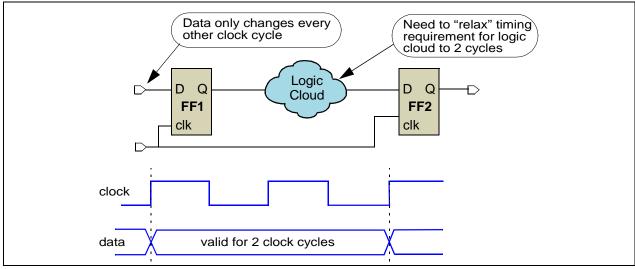

| Figure 3-9. | Multicycle Path Defined                                       | 3-17 |

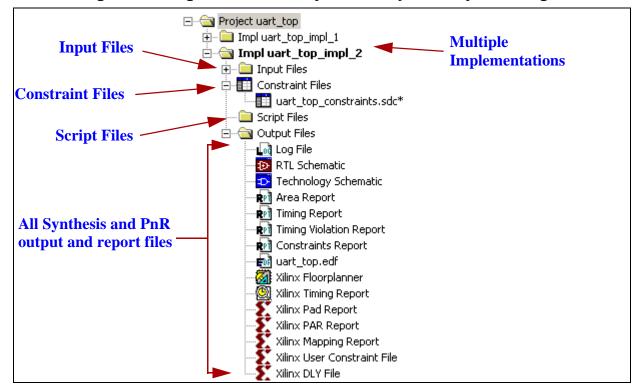

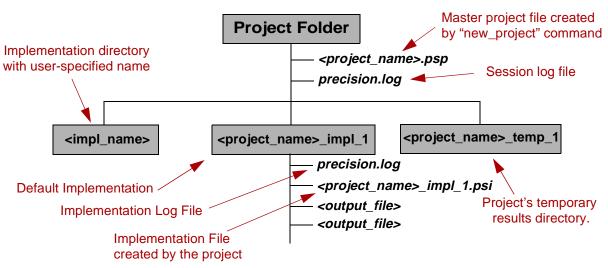

| Figure 4-1. | Organization of Project Files by the Project Manager          | 4-2  |

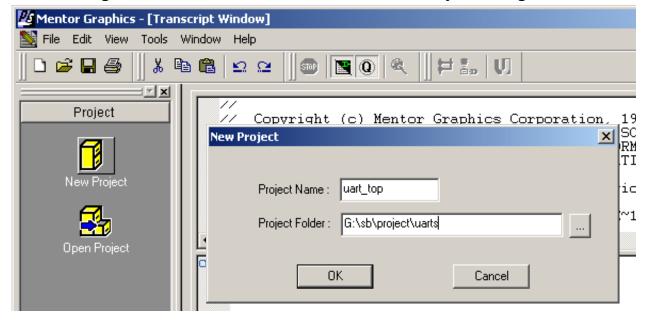

| Figure 4-2. | Initial Session Window and New Project Dialog Box             | 4-3  |

| Figure 4-3. | Newly Created Project and Implementation                      | 4-5  |

| Figure 4-4. | Hierarchical Project File Structure                           | 4-6  |

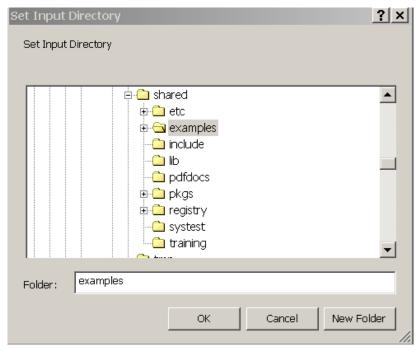

| Figure 4-5. | Setting the Input Directory                                   | 4-8  |

| Figure 4-6. | Project Manager Icons on the Design Bar                       | 4-9  |

| Figure 4-7. | Project Popup Menu                                            | 4-10 |

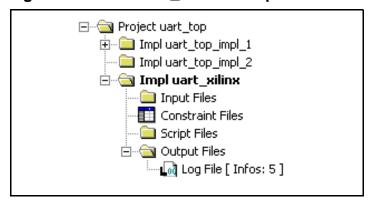

| Figure 4-8. | New uart_xilinx Implementation                                | 4-11 |

| Figure 4-9. | Menu and Dialog for Renaming the Active Implementation        | 4-12 |

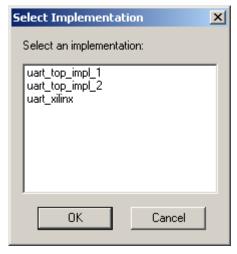

| Figure 4-10 | . Select Implementation Dialog Box                            | 4-13 |

| Figure 4-11 | . Dialog Box Listing all Inactive Implementations             | 4-14 |

| Figure 4-12 | . Menu and Dialog for Editing Implementation Comment Property | 4-16 |

| Figure 5-1. | A Quick Way to Bring Up a Schematic                           | 5-1  |

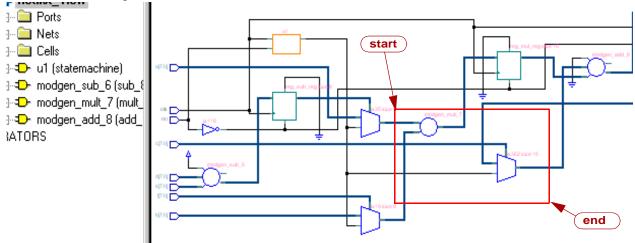

| Figure 5-2. | Design Browser with RTL Schematic                             | 5-2  |

|             | Design Browser with Technology Schematic                      |      |

| Figure 5-4. | Viewing the Critical Path Schematic                           | 5-4  |

# **List of Tables**

| Table 3-1. Technology Pin Name Attributes               | 3-18 |

|---------------------------------------------------------|------|

| Table 3-2. Handling Different IO Pad Scenarios          |      |

| Table 3-3. Handling Different Clock Buffering Scenarios |      |

| Table 4-1. Deprecated Commands                          | 4-21 |

# **List of Tables (cont.)**

# **About This Manual**

Precision™ RTL Synthesis is a comprehensive tool suite, providing design capture in the form of VHDL and Verilog entry, advanced register- transfer-level logic synthesis, constraint-based optimization, state-of-the-art timing analysis, schematic viewing and encapsulated place-androute. This manual describes the synthesis design process using the Precision RTL Synthesis Graphical User Interface (GUI) and provides information on how to perform synthesis tasks and analysis procedures.

# Chapter 1 Introducing Precision RTL Synthesis

Precision<sup>TM</sup> RTL Synthesis is a synthesis platform the maximizes the performance of both existing programmable logic devices (CPLDs and FPGAs) and next-generation, multi-million gate field programmable system-on-chip (FPSoC) devices. Precision RTL Synthesis is a comprehensive tool suite, providing design capture in the form of VHDL and Verilog entry, advanced register- transfer-level logic synthesis, constraint-based optimization, state-of-the-art timing analysis, schematic viewing and encapsulated place-and-route. Precision RTL Synthesis runs on PC platforms using Windows 2000/NT/XP and Linux RedHat; and UNIX Sun and HP platforms. Refer to the Precision Synthesis Installation Guide for detailed information about supported system configurations and requirements.

# **Precision RTL Synthesis Features**

#### **Intuitive User Interface**

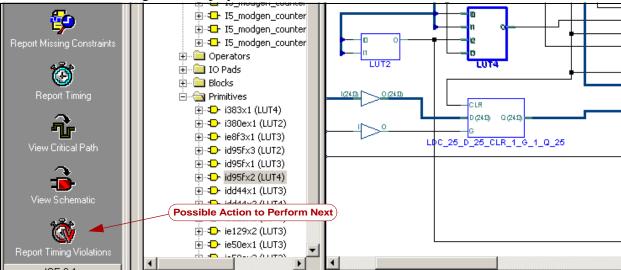

The graphical Design Bar and the Design Center window guides both novice and expert users alike easily through the synthesis process. A progressive disclosure paradigm presents only valid next steps reducing frustration and confusion. When optimization completes, additional design bars appear to assist you with design analysis and place and route.

# **Project Manager**

The Project Manager offers a framework that supports and promotes a design process based on experimentation. The Project Manager system is based on *projects* which contain multiple *implementations*. Each implementation within a project is a separate workspace in which you can experiment with different synthesis strategies and configurations. Implementations keep track of all of the design settings, input files, and output files that comprise its configuration. The Project Manager facilitates your design efforts by allowing you to create, delete, copy, edit and save implementations. For more information refer to Chapter 4, Managing Projects.

# **Advanced Synthesis Algorithms**

Precision RTL Synthesis includes a suite of unique algorithms called Architecture Signature Extraction (A.S.E.) optimization that automatically focus specific optimizations on areas of the design that are most likely to hinder overall performance, such as finite state machines (FSM), cross-hierarchical paths, or paths with excessive combinational logic. ASE uses an automated, heuristic approach to deliver smaller and faster designs without the need for iterative manual user intervention.

# **Constraint Driven Synthesis**

As FPGAs continue to grow in size and complexity, designers need a synthesis tool that delivers excellent results the first time. Timing constraints, based on the industry standard Synopsys Design Constraint (SDC) format, are all the information Precision needs to deliver correct results without endless iterations.

Missing timing constraints result in incomplete timing analysis and may allow timing errors to go undetected. Precision eliminates this by performing a complete constraint analysis prior to synthesis to insure that designs are fully and accurately constrained. First time success in the lab requires a fully and accurately constrained design during synthesis.

# **Boundaryless Optimization**

Precision's advanced optimization technology breaks down performance limiting design barriers such as register, hierarchy and operator boundaries. A powerful retiming algorithm balances logic across register boundaries; hierarchy optimization minimizes logic between modules and pipelining moves registers into multipliers. Precision understands when and where to employ these algorithms, which can improve circuit performance by up to 70%.

#### **FSM Optimization**

Finite state machines are automatically detected and optimized by Precision. Complete analysis is performed on each FSM to locate and eliminate all unnecessary states. A variety of encoding styles are then evaluated to determine the best implementation for the design and target technology. If you choose, you can override the automatic feature and specify a specific state machine encoding. You can even specify a "safe" state machine for radiation environments. Refer to the Precision Synthesis RTL Style Guide for more detailed information on state machine synthesis.

# PreciseTime™ Timing Analysis

Precision's PreciseTime™ timing analysis is capable of finding the true critical paths in even the most complicated designs and clocking schemes. PreciseTime employs the concept of clock domains, a combination of timing analysis technologies to correctly handle even the most complex circuits.

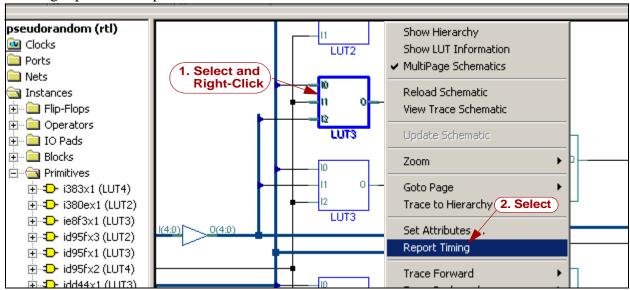

# **Interactive Timing Analysis**

A designer's information about device timing should not be limited to a few pre-selected paths in a synthesis report. Interactive timing analysis can instantaneously generate detailed timing reports from any port, pin or instance in the design. Timing queries can be initiated throughout the user interface including selected objects in the schematic viewer.

# **Register Retiming**

Precision Synthesis includes a powerful optimization algorithm called *register retiming* for improving performance in FPGA designs. Retiming allows the optimizer to move registers across combinatorial logic to improve circuit performance. Improvements of up to 50% are not uncommon when using this algorithm. Refer to the topic Register Retiming on page 4-12 of the Precision Synthesis Reference Manual for more information.

# Schematic Viewing with Critical Path Fragment Filtering

An integrated schematic viewer provides a clear visualization of the synthesis process. High-level RTL schematics help you determine the impact of coding styles while detailed technology schematics show where and how device specific resources such as RAM and ROM are utilized. Patented path viewing and filtering technology displays concise fragments of timing critical logic.

# **Integrated Creation and Analysis Tools**

The following additional standard features allow you to complete the entire synthesis task within Precision RTL Synthesis.

# **Design Bar**

The Design Bar provides you with a visual path through the synthesis flow. Progressive discloser in the Design Bar helps you determine what to do next.

#### **HDLInventor**

The HDLInventor is an interactive source code editor in Precision RTL Synthesis. You can double click on errors, warnings, and information (red, green, and blue dots) in the Transcript window or click on the name of your input file to bring up the HDLInventor.

```

UNSIGNED(data width - 1 downto 0)

signal count_reg :

constant max_count : UNSIGNED(data_width - 1 downto 0) := (others =>

begin

cont_it

process(clk,reset)

begin

if (reset = '1') then

count_reg <= (others => '0');

elsif (clk = '1' and clk'event) then

if (load = '1') then

count_reg <= data_in ;

count_reg <= count_reg + "01" ;

end if ;

end if;

end process ;

divide <= '1' when count_reg = max_count else '0' ;</pre>

end RTL ;

Library IEEE ;

use IEEE.std_logic_1164.all ;

use IEEE.std_logic_arith.all ;

entity dlatrg is

: natural := 16 );

generic (data_width

port (

data_in : in UNSIGNED(data_width - 1 downto 0) ;

clk : in std_logic ;

•

ы

```

The HDLInventor interactively highlights syntax and synthesis construct errors found during the Compile process. You can make your edits in this window and, if required, insert template(s) of HDL code that you frequently use.

# **Project Browser**

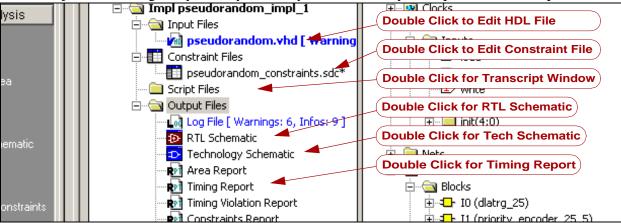

The Project Browser gives you fully visibility and access to your input files and output files.

# **Design Browser**

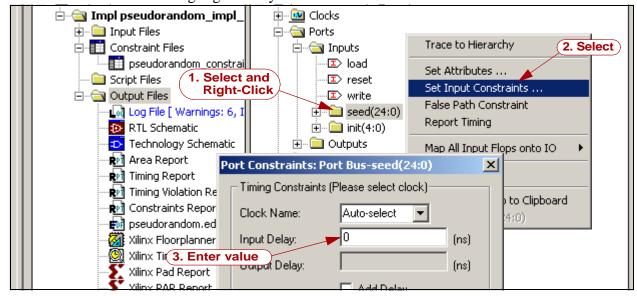

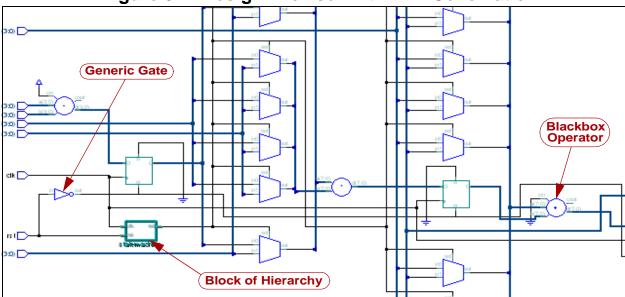

The Design Browser is a graphical representation of the in-memory design database and allows you to traverse through the design hierarchy to observe and set constraints such as Input Delay on ports and "Don't Touch" attributes on modules. You can also use the Design Browser to flatten or preserve the design hierarchy. Objects selected and highlighted may also be highlighted in the schematic viewer. Furthermore, if the selected object initiates cross probing, then that line of code is highlighted in your HDL source code.

# **Schematic Viewing**

Schematic Viewing is integrated with the advanced debug and analysis environment. As shown below, the advanced features allow you to select an object in a path and generate an instant timing report on that path.

The schematic viewer also allows you, for example, to: (1) Cross-probe between HDL source code, RTL schematic, and Technology schematic. This correlation allows for easy debugging. In addition, you can cross probe a schematic generated in HDL Designer with a schematic generated in Precision RTL Synthesis. (2) You can view the whole critical path in one window, even if the path traverses multiple levels of hierarchy. (3) You can view fanout and fanin cones of logic from a selected net or instance. (4) When the critical path viewer is in query mode, detailed timing popup information is displayed for the objects in the critical path. (5) The schematic viewer search utility allows you to search for instance, net, and port; and lists these items for you in a window.

#### **P&RIntegrator**

P&RIntegrator automatically sub-invokes vendor backend place and route tools from within Precision RTL Synthesis. Currently the following environments are supported: Actel Designer, Altera MAX+PLUS II, Altera Quartus II, Lattice ispLEVER, Lattice ispLEVER ORCA and Xilinx ISE. The vendor's backend tools then create a binary program file which is used to

program FPGA and CPLD devices.Refer to Chapter 4 Running Physical Implementation for more information on a particular Vendor environment.

# **Documentation Available Online**

#### **Context-Sensitive Help**

Precision RTL Synthesis has context-sensitive help throughout the GUI. You can press **F1** to open a context-sensitive help or press the HELP button. The GUI window must be selected first to be in current focus when using **F1**. **Note: F1** does not work on UNIX.

Online help is available in Windows 95 format. You can view frames of help text and graphics by moving your cursor to the Help pulldown menu and selecting:

#### **Help > Help Contents...**

You can expand the Table of Contents and select from a variety of topics or do a full index search for keywords.

#### **Product Manuals**

All Precision RTL Synthesis product manuals are available for on-screen viewing and printing with the Adobe Acrobat Reader after Precision RTL Synthesis and the Adobe Acrobat Reader are installed from the Precision RTL Synthesis CD-ROM.

You can view the manuals by selecting the following pulldown menu from the Main menu:

#### **Help > Open Manuals Bookcase**

The PDF manuals and the Manuals Bookcase also contain HyperText links that guide you to related vendor documentation on the Web, provided your web browser is operational and properly configured.

# Chapter 2 Setting Up a Design and Compiling

# **Invoking Precision RTL Synthesis**

You can run Precision RTL Synthesis from the Graphical User Interface (GUI) or from a Shell command line. Typically, you will use the GUI while you are learning to use the tool and for setting up your initial synthesis runs. Once your design is setup and the initial constraints are specified, you can easily generate a Project File and a Master Constraint File. You will typically do the remaining synthesis runs by opening the Project File and making minor adjustments to the Master Constraint File.

# **Invoking the Precision GUI**

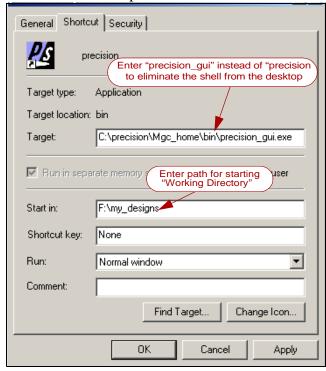

You invoke the Precision RTL Synthesis GUI by entering the precision command from a Windows shell or a Unix shell. In a Windows environment, you can optionally create a Shortcut on your Desktop and set the Shortcut Properties similar to that shown in the following figure.

# **Invoking Precision from a Shell**

You can invoke Precision in non-GUI mode by using the command precision -shell. In this mode you can source Tcl scripts or you can interactively enter commands from the shell prompt. A typical command line entry might be the following where a Tcl command file is specified to set constraints and guide the tool through the synthesis process:

```

% precision -shell -file dofile.tcl

```

You can also export your script settings. For more information, see Exporting your Settings. The precision command and its optional switches is fully documented in the section titled Commands in the Precision Synthesis Reference Manual.

# **Setting up the Design Environment**

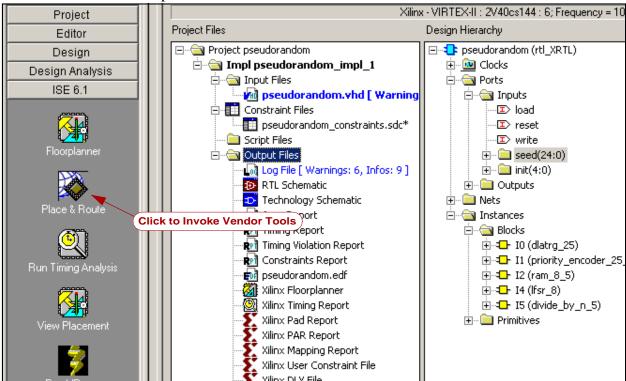

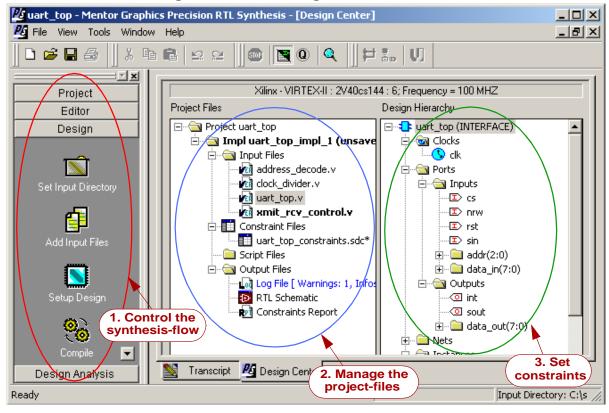

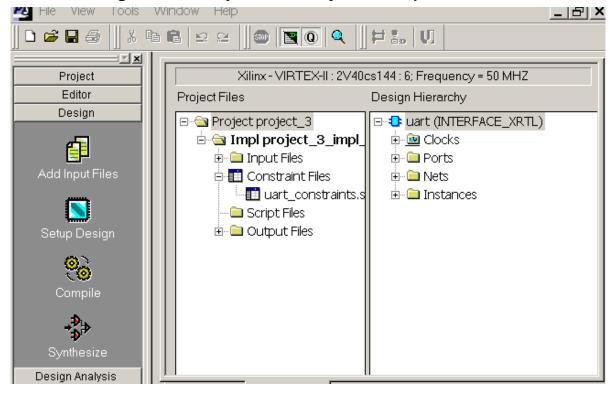

As shown Figure 2-1, the Main window has three primary control areas. The Design Bar (on the left) controls the synthesis flow. You will manage your project files from the Project pane (center) and apply constraints to design objects in the Design Hierarchy pane (right). The Design Bar provides a visual indicator of the sequential steps in the synthesis flow. Using progressive disclosure, the icons in the Design Bar change depending on where you are in the flow and reveal the possible next steps.

Figure 2-1. The Design Center Window

The following list shows some hints for using the Precision GUI:

- If you don't know what to do, try right-clicking on a folder, file, or object. The Design Center window is right-click driven. Right-clicking on the folders and files in the Project Files pane will pop up a menu of commands specifically for the selected object. Also, you can set constraints by right-clicking on design objects in the Design Hierarchy pane. Thus, you can drive the entire flow from the Design Center window.

- View messages by double-clicking on the Log File. Doubling clicking on the Log File brings up the *Transcript* window (and its associated Interactive Command Line pane). You can scroll up and down the transcript to read messages and review the history of the current session. Double-clicking on an error message in the transcript brings up the associated HDL source file for review and editing.

Precision commands executed from the GUI are recorded in the transcript. These commands are highlighted in blue. The transcript is saved in Precision log files (precision.log). A session log records all commands executed during an entire Precision session, and is saved in the project directory. In addition, an implementation

log is saved inside the active implementation directory which records only the commands executed while that implementation is active.

If the results directory was set using the set\_results\_dir command, only the session log file is created, and it is saved in the results directory.

- View Schematics/Reports by double-clicking on Schematic/Report Files. Doubling clicking on a Schematic File or a Report File in the Design Center window brings up the the content of that file in a separate window.

- Constraints that are Set in the GUI are Saved to an SDC File. The synthesis process is "constraint driven" and your objective is to create a Master Constraint File that can be read as part of the Input File List. The constraint file format is Synopsys Design Constraints (SDC). One of the easiest ways to create an initial constraint file is to manually set constraints on design objects in the Design Hierarchy window. As you do so, the constraints are automatically saved to a generated.sdc file and placed in your implementation directory. For future synthesis runs, you can include this generated constraint file as one of your input files.

# The Project Directory and the Results Directory

Generally speaking, a *project directory* and a *results directory* are user specified locations where Precision saves output files during a particular session. A project directory is created by the Precision's Project Manager when you create a new project. On the other hand, if you want to work without using the Project Manager, you must set the results directory location by calling the set\_results\_dir command. In this case, all output files go into the results directory.

The structure and organization of each type of output directory is different and reflects purpose of the directory. The purpose of the project directory is support the organizational functions of Precision's Project Manager. Therefore, the project directory is hierarchical in structure. The top-level is the project level, and it contain multiple sub-directories, each of which is dedicated to a different implementation of your design. For detailed information about the file structure of a project directory, refer to Creating a Project on page 4-3.

The purpose of the results directory is simply a repository for single implementation usage of Precision Synthesis. This type of usage is typically carried out by batch scripts or from the command line interface. Because this usage model deals with only a single implementation, it does not require the organizational structure provided by the Project Manager. Therefore, the file structure is flat. All output files are stored in the results directory without hierarchy.

When working with the project, synthesis design work is not automatically saved to the implementation directory but is held in a temp directory until you save your work. For more information, see The Precision Temp Directory.

#### **Setting the Project Directory**

You specify the location of a project directory when you first create the project. Once the project is created, the location is implicitly set each time you reopen the project (because the project file resides inside the project directory). You cannot open a project if a results directory is currently set.

#### **Setting the Results Directory**

You set the location of the results directory by calling the <u>set\_results\_dir</u> command. This command is not available if a project is already open. Within scripts, it must be the first command called in order for Precision to run without using the Project Manager. When the results directory is set, no Project Manager commands are available until you call the close\_results\_dir command.

# **Setting the Input Directory**

The input directory is the location where Precision will look for input files by default. The input directory can be independent of the project directory. When you ask Precision to access an input file, you can give it the full pathname of the file or a partial pathname. If you specify a partial pathname, that pathname must be relative to the input directory. In other words, the full path to the file must be equivalent to the combination of the input directory path and the partial file path (<input\_dir>/<partial\_path>).

You can change the input directory at any time, either from the GUI or by calling the set\_input\_dir command. Resetting the input directory while you are working in Precision can be a useful strategy. For example, you can create multiple input directories that contains variations of the same set of input files. Then you can easily switch back and forth as you experiment. For this strategy to work, all of the input files that have the same name must be added to the project using a relative pathname (relative to the input directory).

# **Setting the Technology**

In order for Precision RTL Synthesis to map your design to a specific technology, you must specify a target technology. Precision RTL Synthesis provides a number of CPLD and FPGA libraries from major vendors. These libraries includes the technology-specific cell definitions and custom operator implementations. They also contain global library defaults such as route tables and fanout constraints.

To specify the technology and global options, you should follow these steps:

1. Click on the Setup Design icon in the Design Bar (left side of the GUI)

This action displays the Setup Technology dialog box containing all technology libraries that are included with Precision RTL Synthesis.

2. Select the target technology by clicking on the vendor and technology name

This action adds a set of default technology settings that you can modify.

- 3. Verify and or modify the default technology settings

- 4. Optionally set a global design frequency

This value serves as a starting point for clock constraints on all clocks. After the Compile step, you will be able to select each clock in the Design Hierarchy pane and adjust the constraints accordingly.

5. Optionally set the default Input Delay and Output Delay

Input Delay refers to the delay consumed outside the design before a data signal reaches the input port of your design. Output Delay is the delay required outside the design in order to properly clock the device being driven by your design. These optional default values serve as a starting point for setting I/O constraints. After the Compile step, you will be able to select each I/O port in the Design Hierarchy pane and adjust the constraints accordingly.

6. Apply the Setup Technology dialog box

This action executes a series of setup\_design commands that inform Precision RTL

Synthesis about the technology and the global options you entered. Precision RTL

Synthesis does not actually load the synthesis library into memory until the command to

Compile is executed.

After you specify the technology and verify the options, you can add your design files to the project.

#### **Adding Input Files to the Project**

Precision RTL Synthesis does not read or reference pre-compiled HDL libraries, packages, or designs from disk. Instead, the library and package source files and the design source files are read directly into memory where Precision builds an EDIF-like in-memory database. The design source files may reside in any location and may even reside in more than one location.

To add your input files to the project from the GUI, follow these steps:

1. Click on the Add Input Files icon in the Design Bar

This action opens the Add Input Files dialog box.

2. Navigate to and select a source file(s), then click Open.

Since Precision analyzes all of the files in the input file list together, the order that you add the files is usually not important. Precision RTL Synthesis will auto-detect the top level. If your design files reference a standard library or package, such as an IEEE library, then Precision RTL Synthesis will automatically open and load that library or package file which is located in the cprecision install directory>/pkgs/techdata/vhdl directory.

If you include Xilinx Coregen files in this list, Precision will read the coregen block and mark it as a dont\_touch block (so Precision will not optimize it but will consider it for fanout and timing analysis. For more information, refer to "Including Xilinx Coregen-Generated Modules" in the Precision Synthesis Reference Manual.

3. (optional) Adjust the file type by right-clicking on the file name and selecting Properties.

Precision detects the file type based on the file extension. Valid values are vhdl (.vhd/.vho), verilog (.v,.vo), edif(.edif, .edn, .edf), syn, tcl, xnf, xdb, and sdf. If a file does not use a valid extension, then you can use this form to specify the file type.

4. Apply the Add Input Files setting by clicking on the Apply button.

This dialog box may execute a series of add\_input\_file, move\_input\_file and set\_input\_file commands (depending on how you add the files).

#### **Setting Input File Properties**

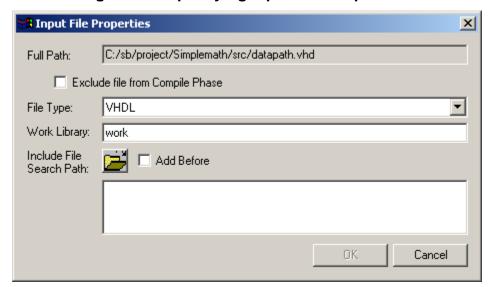

Once you include a file in the Input File List, you can right-click on the file in the Project Files pane and specify the Properties of the file. Figure 2-2 illustrates the dialog box options and the text following the Figure explains the options in detail.

Figure 2-2. Specifying Input File Properties

#### File Type

Allows you to specify the file type for file names that don't have the proper extension. If this option is not used and a valid extension exists, then the file type will be automatically detected.

#### Passing Files from Input to Output

You can use this option when you wish to add one or more files to the Input File List, but exclude them from the Compile phase. Files marked with the exclude property are copied into the implementation directory after the synthesis phase is complete. Also, files of an unknown type are automatically marked as "Exclude" and copied to the implementation directory. This mechanism is handy for passing a file, such as a place and route control file, around the synthesis process and onto the physical implementation tools.

#### **Work Library**

Specifies the name of the work library for compiling the content of the VHDL file. If not specified, then the work library name work is assumed.

#### **Include File Search Path**

Specifies additional directories that are pre-pended to the global search path that is specified from the pulldown menu **Tools** > **Set Options** > **Input**.

#### **Searching for Verilog 'include' Files**

If a Verilog file is being added and additional files are referenced via the 'include' directive, then the search for the include file is conducted in the following order:

- 1. The directory of the file that specifies the include directive

- 2. The directories that are specified for this file in the Input File Properties dialog box.

- 3. The directories that are specified for global searches in the pulldown menu **Tools > Set Options... Input**

Assume, for example, that the file being added is located in the directory F:/design/src and this search path is set to the following:

```

{"C:/my_include_files" "F:/more_include_files"}

```

During the compile operation for this file, Precision RTL Synthesis first searches for any specified include files starting in directory F:/design/src, then C:/my\_include\_files then directory F:/more\_include\_files. If the file is not found, the directories specified in the pulldown menu **Tools** > **Set Options... Input** are searched. As soon as the file is found, the search ends.

#### **Searching for VHDL files**

When the file being added is compiled and it references a VHDL library or a package that has not yet been compiled, a search is conducted for this package file by that library or package name so it can be compiled first. Assume, for example, that this input file contains the following the clause:

```

use lib.my_package.all;

```

When the file is compiled, Precision RTL Synthesis looks in the library work to see if my\_package has been compiled. If not, a search begins in the directory where this input file resides, then the search directories that are specified for this file. The search continues in the global directories that are specified in the pulldown menu Tools > Set Options... Input and finally the directory cprecision install directory/pkgs/techdata/vhdl is searched. As soon as the file is found, the search ends, the package file is compiled and the specified input file is compiled. If the package file is not found, Precision RTL Synthesis issues an error message.

#### **VHDL Considerations**

Before you use Precision to perform VHDL synthesis, you should already have a good understanding of the syntax and semantics of VHDL. If your design references custom libraries and packages, then you must include these package source files for reading before your design files are read. The methods for doing this are fully discussed in the Precision RTL Synthesis Style Guide.

The following list shows some common issues when loading VHDL designs into memory:

- Read source (not compiled) VHDL files Precision RTL Synthesis can not read compiled HDL databases from any simulator or synthesis tool. You must read the VHDL source code, including libraries and packages.

- Auto-Loading IEEE Libraries Precision RTL Synthesis automatically loads the IEEE standard std\_logic\_1164 and numeric\_std packages. It also loads (if necessary) the Synopsys std\_logic\_arith, std\_logic\_unsigned, and std\_logic\_signed packages in the IEEE library. You do not have to include these packages in the Input File List in Precision RTL Synthesis.

- **Auto-Top Detection** In most simulators, you must compile the VHDL code using a bottom-up order. Precision RTL Synthesis should auto-detect the top-level of the design and automatically determine the compile order of the input VHDL files.

- Library/Use Clauses for referring to technology cells. Because synthesis tools use a different scheme to locate technology cell instantiations (compared to simulators), you should pragma out any VHDL Library and Use clauses for these cells using translate\_on and translate\_off. Precision RTL Synthesis will still locate these cell instantiations because Precision RTL Synthesis loads the technology library prior to compiling the VHDL source code.

```

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

USE IEEE.numeric_std.all;

-- pragma translate_off

USE a42mx.components.all;

-- pragma translate_on

```

• Case Sensitivity Although VHDL is not case sensitive, in order to handle mixed language designs (VHDL and Verilog), Precision RTL Synthesis considers VHDL to be case sensitive. Since most cell and port names in the technology libraries are uppercase, the case of instantiated technology cells must also be uppercase.

#### **Verilog Considerations**

Before you use Precision to perform Verilog synthesis, you should already have a good understanding of the syntax and semantics of Verilog. Using Verilog synthesis also requires knowledge of the guidelines presented in the Precision RTL Synthesis Style Guide.

- **Auto-Top Detection** Precision RTL Synthesis auto-detects the top-level of the design and automatically determined the compile order of the input Verilog files.

- **Include Files** If additional Verilog files are referenced via the 'include' directive in an input file, then the file is searches for in a pre-defiled order. This search order was described in the previous topic Include File Search Path.

- Full Case When a case statement is used in your Verilog design, the Full Case switch tells Precision that all conditions of the case statement are specified. If a default assignment is not used, for example, then this option prevents the implementation of extraneous latches. This switch is set from the pulldown menu Tools > Set Options > Input > Verilog.

- Parallel Case When using a CASE statement in your Verilog design and the case conditions are mutually exclusive, a multiplexer is often the preferred implementation (instead of priority encoding a state machine). You should select Parallel Case to direct Precision RTL Synthesis to treat case conditions as mutually exclusive and implement a multiplexer logic structure. This switch is set from the pulldown menu Tools > Set Options > Input > Verilog.

- Verilog 2001 Support Precision Synthesis provides support for Verilog 2001 constructs. Refer the to Precision RTL Synthesis Style Guide for details.

#### **EDIF Considerations**

Precision RTL Synthesis only supports the reading of EDIF files that were generated by Mentor Graphics synthesis tools or FPGA place/route tools. If Precision determines that the EDIF file is from Xilinx CoreGen, Precision RTL Synthesis automatically applies a dont\_touch attribute to the instantiated CoreGen block.

Although Precision RTL Synthesis supports the EDIF format, you may not be able to read EDIF from other tools (e.g. schematic capture) because the cell sets and pin names may not match between the two tools.

#### **XDB Considerations**

Precision RTL Synthesis can only read and properly interpret an .xdb file that was first generated by Precision RTL Synthesis.

#### **SDC** considerations

By default, Precision RTL Synthesis saves all timing constraints and attributes generated from the GUI in a file named <design\_name>.sdc located in the current implementation directory. If you added any additional constraints or attributes via the command line, you must manually add these commands to the Master Constraint File if you want them included in the next synthesis run.

# **Setting Synthesis Options**

You direct and refine the behavior of the synthesis process by selecting options from the pulldown menu **Tools** > **Set Options...** The options are described online if you click on the HELP button at the bottom of each dialog box. The following list describes some of the common options that you should verify the default settings.

Set State Machine encoding.

You can allow Precision Synthesis to automatically select a Finite State Machine encoding style for you (the default) or you can specify a specific encoding style. Precision Synthesis also supports the ability to create a Safe State Machine. A safe state machine is a state machine in which a transition will always be to a valid state. Refer to the Precision Synthesis RTL Style Guide for more information on how to set these options.

#### • Setting Output Options

Precision saves the output netlists for the implementation tools along with area and timing reports in the current *implementation* directory. These file are also listed in the Project File pane of the Design Center window.

By default, the base name (leaf name) of the generated output file is taken from the name of the last HDL input file to be read. You can change this name by specifying a new name from the pulldown menu **Tools** > **Set Options** > **Output** > **Output File Base Name**.

Generating Output Files in Different Formats

If you need Precision RTL Synthesis to generate additional netlists (e.g. an HDL netlist for simulation), you need to set this additional output netlist option from the pulldown menu **Tools > Set Options > Output**. A separate file is generated for each type that is selected (EDIF, Verilog, VHDL).

# **Compiling the Design**

Once you have specified the target technology and your source HDL files, Precision RTL Synthesis can compile the design into a technology-independent implementation. To compile your design, click on the Compile icon in the Design Bar.

If the Compile icon does not appear, verify that you on using the Design Center tab and that you have specified a target technology in the design setup.

If you get any errors or warnings, you can edit the source file by double-clicking on either the message in the Transcript window or on the file name in the Design Center.

An in-memory design database is created by reading one or more source files into memory. Precision converts any of the initial input formats into an intermediate representation which permits the tool to efficiently optimize designs. Within the views, Precision RTL Synthesis uses the following naming convention for different types of logic:

- $ix^* = instance$  name for boolean gate

- reg\_signal = flip-flop with the q output driving signal

- ? or "unknown" = power/ground net

- lat signal = latch with the q output driving signal

- modgen\_\* = cell used to implement an operator

#### **Evaluating the Results**

By examining the transcript and viewing the RTL Schematic, you can determine whether Precision has created the generic gate-level implementation that you expect. You can analyze both the warnings in the transcript and the quality of the initial results. Even though the output of the compile command is technology independent, the quality of the compiled design is a precursor to the quality of the final technology design.

#### **Reviewing Warnings and Errors in the Transcript**

The following list shows some typical warning messages and their causes:

Messages about overwriting designs—

```

Warning: Overwriting netlist work.comb (INTERFACE)

```

Typically, you expect these warnings when you read a new block into the overall design and that block matches an empty or existing cell. However, you should investigate these messages to make sure you have not unintentionally overwritten an in-memory block.

Messages about the sensitivity list—

```

"arbiter.v", line 873: Warning, interleave should be present in the 'always' condition.

```

Because sensitivity lists are ignored during synthesis, Precision builds combinational logic as if such missing signals are present in the sensitivity list. This can lead to simulation mismatches.

Messages about unused nets—

```

"arbiter.v", line 441: Warning, extranet is never used

```

These warnings indicate local nets that were declared but never used within the design. Such nets are dissolved during constant propagation. Often the indicated nets lead to expected unused output ports from instantiated blocks. Consider removing such unused internal nets. However, you should analyze the nets to ensure that a design error does not exist.

Messages about unused ports—

```

"arbiter.v", line 441: Warning, input extraport is never used

```

Warnings about unused ports are more specific cases of the preceding warning about unused nets. You should consider removing any ports that are declared but never used within the Verilog code.

Messages about latches—

```

"arbiter.v",line 638: Warning, start_dir_ras_tmp is not always assigned. latches could be needed.

```

Warnings about latches may be given when Precision inserts transparent latches for combinational processes. This circuitry is inferred from code (the lack of else statements, typically) that does not account for all the possible conditions within a conditional construct. Precision infers that it needs to store the states for these conditions, which results in unexpected circuitry.

Messages about parallel case—

```

"arbiter.v", line 1028: Warning, case choices are not mutually exclusive, parallel case pragma may induce simulation mismatch.

```

Warnings about parallel case may be given when Precision encounters case structures that you have specified as having conditions that are not to be prioritized during synthesis. This can lead to simulation mismatches.

Messages about black boxes—

```

Warning: cell xcve.DLL (INTERFACE) marked black box.

```

Make sure that the black boxes represent empty modules for incremental synthesis or vendor cell instantiation (use the Area Report to examine results). Otherwise, these messages indicate that Precision could not find certain cells in the design.

If the design is read in, but you see unexpected black boxes on technology cell instantiations, verify that the cell and port names in the HDL code match the cell and port names in the technology library in Precision RTL Synthesis. All port names must be included. You can display this information using the get\_lib\_cell and get\_lib\_ports commands. The case of these names must also match (even for VHDL which is not case sensitive). Precision RTL Synthesis must maintain case sensitivity on all objects to support mixed-HDL designs. If the instantiation uses positional association to map the net to the cell port (compared to including the port name and net name in the instantiation), you should verify that Precision RTL Synthesis is making the same assumptions about pin ordering.

#### **Evaluating Quality of Initial Results**

After you have fixed any errors and have a satisfactory explained of the warnings produced during the compile run, you should examine the quality of the compiled design. Although you can not generate a timing report on the technology-independent design, examining the compiled design will give you an early opportunity to address any Quality of Results issues.

To help you evaluate the design, the following features are available.

- The session transcript in the Transcript Window (double-click on the Log File)

- The RTL schematic (double-click on the RTL Schematic file)

- Cross-probing features

To evaluate the quality of the initial results, double-click on the Area Report in the Output File list and examine the following issues:

• Check for latches (in the transcript during the compiling of each cell)

In FPGA designs, synthesis tools infer latches due to incomplete signal assignments. Unintended latches have two negative affects on the design. One, they increase the size of the design because these sequential cells prevent the optimizer from combining boolean logic on either side of the latch. Two, unintended latches block timing analysis.

• Verify the number of inferred flip-flops in each block (in the Area Report)

Since synthesis tools only optimize boolean logic, it is very important that you verify that each block is inferring the approximate number of flip-flops that you expected. Once a flip-flop or latch is part of the design, the synthesis tool will not optimize it away as long as it affects the design.

During optimization, Precision RTL Synthesis will only add/remove flip-flops in your design in the following cases:

- Register replication for timing or DRC fixes

- Register removal due to D-input being driven by a constant (these situations will be reported in the transcript).

- Verify the number and type of inferred operators (in the Design Browser in the Operators folders)

Since the critical path within most designs propagates through operators, it is very important that you verify you are inferring the correct number/size of operators.

• Verify the number of inferred memories and counters (in transcript after the pre\_optimize operation)

Precision RTL Synthesis utilizes special mapping algorithms to target counters and memories from your HDL code. If Precision does not infer the correct number of RAMs, ROMs or Counters, refer to the Precision RTL Synthesis Style Guide to verify that the HDL code matches the coding style that Precision expects. For RAMs that do not infer properly, try to cut and paste one of the examples. For counters, verify that the reset condition is either all zeros or all ones. The Precision RTL Synthesis counter operator only has an asynchronous reset or set (no asynchronous load). You can work around this issue by muxing the data and reset value.

If your compiled design meets expectations, you can continue by setting constraints on your design as described in the next chapter. You may also want to save the present state of the implementation. Simply right-click on the implementation in the Project Files pane of the Design Center window, then choose **Save Implementation** from the popup menu.

If your compiled design does not meet your expectations, you will probably need to make changes to your HDL source code and follow the recommendations in the Precision RTL Synthesis Style Guide.

# **Setting Timing and Design Constraints**

After the design has been compiled, you can set design constraints on the design so that Precision can address the critical timing paths in your design. At a minimum, you should set the global frequency. Since Precision automatically detects all of the clocks in the design after compile, it is highly recommended that you specify clock constraints on each detected clock. This method will insure that Precision focuses on the critical timing paths in the design.

Constraints can be set from the using any combination of the following methods:

Adding an SDC File to the Input File List

This file is called the Master Constraint File, but the filename may be any name you specify as long as it have an .sdc extension. As previously described, if you don't have a Master Constraint File, you can use Precision RTL Synthesis to generate one for you on the first synthesis run. Technically, you can have more than one .sdc file in the Input File List, however, it is a common practice to maintain only one Master Constraint File.

• Entering Constraints from the Precision GUI

You can manually add constraints to the in-memory design objects with the GUI. A record of the changes are saved in a generated .sdc file that is placed in the current implementation directory.

• Entering Constraints from the Command Line

You can use the Interactive Command Line Shell to add constraints to the in-memory design. You may do this while experimenting with different constraint sets. You must realize, however, that any constraints entered this way will not be saved to the generated .sdc file. If you want to save one of these constraints for the next synthesis run, you must manually type the constraint directly into the Master Constraint File.

Adding a Xilinx UCF File to the Input File List

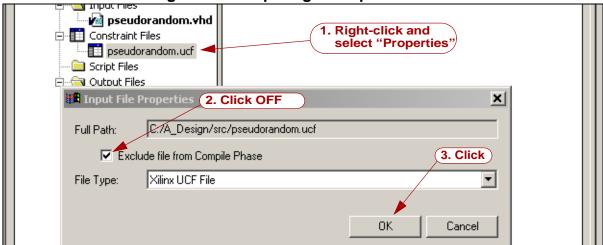

Precision Synthesis has the ability to read the timing constraints from a Xilinx UCF file and apply those constraints to the in-memory design. This is handy, for example, if you have a design that was generated by another synthesis tool and you have timing constraints that are expressed in Xilinx UCF format. You can include only one UCF file in the Input File List and to read the UCF timing constraints, you must remove the "Excluded" attribute from the file as shown in the figure below. The procedure is to right-click on the file from the Design Browser and select "Properties". Click off the

"Exclude file from Compile Phase", then click OK. When the Design is compiled, the UCF timing constraints will be applied to the in-memory design.

Figure 2-3. Preparing the Input UCF File

You may include other SDC constraint files with the UCF input file, however, you should make sure that the constraints in different files don't conflict. If a conflict occurs, the constraints in the last file read (last file in the list) prevail.

Specifying Attributes or Pragmas in the HDL Source

Constraints that rarely change can be added directly to the HDL source files by using VHDL attributes or Verilog pragmas. An example might be a physical pin number assignment that is set by the system specification or a dont\_touch attribute that is set on a block of IP (Intellectual Property). Refer to the chapter titled Attributes in the Precision Synthesis Reference Manual for details and examples.

For more information on setting a specific timing or design constraint, refer to "Setting Constraints and Synthesizing" on page 3-1.

# Synthesizing the Design

During synthesis, Precision performs the following high-level tasks:

- 1. Implement operators

- 2. Perform intelligent auto-dissolve on smaller hierarchical blocks

- 3. Perform initial quick optimization of each block

- 4. Determine the blocks that do not meet timing and perform additional optimizations where necessary.

5. Write out netlists and reports to the implementation directory

# **Evaluating the Results**

After the synthesis run is complete, you should evaluate the quality of the results. Although the natural inclination is to look at the maximum frequency, this value can be mis-leading until you verify that your clock distribution is correct. To get a complete view of the synthesis quality, you should check the areas described below.

#### **Analyzing the Cell Usage**

As part of the evaluation of your synthesis results, you should use the Area Report and Schematic Viewer to verify that key resources were utilized to their fullest potential. The following list shows some areas that you should check:

- Empty IP blocks.

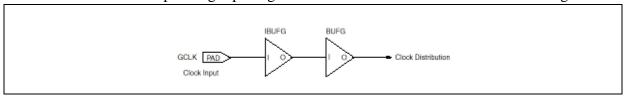

- Clock Buffers.

- IO cell usage

- Memories.

- Unexpectedly removed ports or instances

### **Analyzing the Timing Results**

After you run Synthesize, you can view a timing report. Timing reports display timing paths through hierarchical boundaries. The following list provides the typical results of *initially* analyzing critical paths and the actions that you should take based upon the results:

Positive slack time

If the design produces a positive slack time for critical paths, you do not have to perform any further performance optimization steps and you can proceed to Place and Route.

Small negative slack time

If your design produces a negative slack time for critical paths that is about 10% or less than the overall cycle time, you should perform a quick check of the hints in the following two sections and proceed to Place and Route. Since the initial synthesis pass uses pre-layout timing estimates, it is possible that small negative violates can be fixed in placement during Place/Route.

#### Large negative slack time

If your design produces a negative slack time for critical paths that is 10% or greater than the overall cycle time, you need to verify you are reporting a *true critical path* (not a multicycle, false path, or invalid clock interaction) and then analyze the elements within the critical paths. Using the hints in the following two subsections, you need to identify the HDL code that is causing the critical path and possibly make adjustments in the HDL code.

If your design is still not meeting performance requirements, you can either loosen your timing constraints or re-synthesis using a faster speed grade for the device. If you are within 10% of your timing goals, you may want to run the design through the vendor implementation tools to get more accurate post-place/route timing values. Precision RTL Synthesis calculates delays using a conservative pre-layout estimate. If you are close to meeting your timing constraint (according to Precision's estimate), you may have actually met the timing constraint according to the accurate post-layout value produced by the physical implementation tools.

To obtain the fastest design, consider doing the following:

- *Don't over-constrain paths.* Precision RTL Synthesis will spend a lot of CPU time trying to obtain an impossible goal while greatly increasing the size of the design.

- Check for asynchronous signals exist on the critical path. Asynchronous signals (such as set or reset) cause negative slack because they typically arrive well before the data to the synchronous device is available for clocking.

Examine your timing report for the following statement with the *Source* or *Dest* fields in order to determine the existence of asynchronous signals:

```

Combinational path through sequential primitive. Probably an asynchronous set/reset.

```

Since asynchronous signals are usually connected to external ports, you can correct the negative slack by setting the input constraint on the port to -1 clock cycle (e.g., -100ns). Then the asynchronous signal is a static value 1 clock cycle before the input to the synchronous device is available.

- Multi-cycle paths exist on the critical path. You can detect multi-cycle paths in timing reports by observing a negative slack value that is greater than the clock cycle. You will also notice that the path starts with and ends with a synchronous device.

- Examine the type of logic (boolean or operators).

- Effective use of operators

- Check fanout

• Consider using Retiming. Precision includes a highly effective register balancing algorithm. This algorithm is disabled by default in RTL synthesis and enabled by default in physical synthesis.

To enable retiming in the entire design:

```

setup_design -retiming=true

```

Retiming will affect the observability of internal registers. If observability of a particular internal register is an issue then set a "don't\_retime" attribute on those specific registers. For example:

```

set_attribute -name DONT_RETIME -value TRUE -instance U1/reg_pipe(*)

```

• Incorrect constraints. Typically, setting the input/output constraints incorrectly may over-constrain the design such that Precision reports a negative slack that can never be corrected. Setting constraints incorrectly is usually the result of not understanding the relationship between Input Delay and setup time, as shown in Figure 2-1. Basically, the Input Delay is defined with respect to the first clock edge, and the setup time is defined with respect to the last edge of one clock cycle. The difference (delta) between these two times is the delay available for the circuit. When this delta is zero or when the times overlap, Precision reports an un-correctable negative slack.

Figure 2-1. The Constraint Relationship

- *Fine tune constraints*. Refine the constraints to meet the "real world" conditions of the complete design.

- *Flatten blocks*. If the area results are acceptable, begin to flatten hierarchical blocks in order to improve timing results on subsequent synthesis runs.

- Turn off resource sharing. If you have a large operator in the critical path that is resource shared, try turning off resource sharing. Click off the radio button Tools > Set Options... Input > Resource Sharing and click Synthesize again. The additional operators may increase the area, but the eliminated mux circuitry may solve the timing problem.

- Return to the HDL source design and re-implement. You might have to re-design a critical path in the HDL source in order to create a parallel (faster) design or you may have to increase the latency of the path by a cycle or two.

- Switch speed grades. Last, check with your vendor to determine if there is a faster version of the chip available that represents a higher performance technology.

#### **Determining the Next Step**

If your design meets the specified performance requirements, then move on to Place & Route.

If your design is still not meeting performance requirements, you can either loosen the timing constraints or select the Register Retiming option and re-run Synthesis. If you are within 10% of your timing goals, you may want to run the design through the physical implementation tools to get accurate post-place/route timing values. Precision RTL Synthesis calculates delays using a conservative pre-layout estimate. If you are close to meeting your timing constraints (according to Precision's estimate), you may have actually met the timing constraints according to the accurate post-layout value produced by the physical implementation tools.

# **Performing Initial Place and Route**

Precision RTL Synthesis has a built in Place & Route environment that allows you to move seamlessly from synthesis to the physical implementation of your design. Once your design is synthesized, icons for the Vendor's implementation tools appear in the Precision Design Bar. The current implementation directory becomes the *project directory* for the Vendor tools and you can proceed to Place and Route.

Like the synthesis process, the place and route process is controlled by two primary commands. Synthesis options are set by the setup\_design command and the flow is executed with the synthesize command. In a parallel way, place and route options are set by the setup\_place\_and\_route command and the flow is executed with the place\_and\_route command.

The Precision GUI interface to the setup\_place\_and\_route command appears after you select the target technology. The pulldown menu **Tools** > **Set Options** > (**Vendor Environment Name**) becomes available.

After Precision output files are written to the implementation directory, the Vendor Tools icons are revealed in the Design Bar. You can invoke the automated Place & Route flow, or you can invoke the Vendor's project browser and manually step through the implementation process. You can also view Vendor-generated reports and invoke Vendor tools such as timing analyzers and power analyzers.

# Chapter 3 Setting Constraints and Synthesizing

When you Compile a design, a technology-independent database is created in memory. The next step involves setting constraints and mapping the design to technology-specific cells. By default, Precision RTL Synthesis maps the design to the fastest possible implementation that meets your timing constraints. In order to accomplish this, you must, at a minimum, specify timing on the automatically determined clock sources. With this information, Precision performs static timing analysis to determine the location of the critical timing paths. Although Precision will map your design to the target technology without any timing information, Precision will produce the best results with this information.

# **Managing a Master Constraint File**

Typically, you will make more than one synthesis run before you achieve the best results. During this process, you guide Precision toward the ideal solution by setting constraints. The constraints will be timing constraints, mapping constraints, and constraints that control the structure of the implemented design. The constraints you specify first are usually estimates that you'll want to change and refine on future synthesis runs.

# **Creating a Master Constraint File**

The recommended methodology is to create a Master Constraint File (.sdc file) and add this file as the last item in the Input File List. You can create this file with a common text editor or use Precision to generate one for you on the first synthesis run. You then add this generated file to the Input File List as your Master Constraint File. During the Compile phase on a future synthesis run, the in-memory design is created from the HDL source files, then the Master Constraint File is read and the constraints are applied to in-memory design objects.

# Maintaining a Master Constraint File

Typically, you will add and change constraints on future synthesis runs. Constraint changes that that are made to the RTL in-memory design from the GUI are logged to a newly generated constraint file. This .sdc file is saved to the current implementation directory. As previously

stated, on the first run you can use this file as a template for your Master Constraint File. On subsequent runs, you should regard this file only as a record of constraint changes. Some of the constraints will be a record of your experimentation while other constraints are changes you'll want to keep by adding them to your Master Constraint File. The methodology is to use a text editor to manually "copy and paste" the new or modified constraints to the Master Constraint File.

For the purpose maintaining the integrity of the .sdc file, the only time the Precision GUI will save constraint settings in the .sdc file is when you apply the constraints to the in-memory RTL design. If you add or edit constraints on the gate-level in-memory design, your changes are applied to the design, but not saved in the .sdc file. For your convenience, the Design Hierarchy pane of the Design Center window always displays the RTL design. To view a gate-level design after synthesizing, double-click on the Technology Schematic file in the Project Files pane of the Design Center window.

Likewise, when you manually enter constraints into a .sdc file, be sure to use the **-design** option that is available on all constraint related commands. That option takes one of two arguments, **rtl** or **gatelevel**, that specifies the design file to which the constraint will be applied. The default value is **rtl**.

Continually managing the Master Constraint File is a primary task and you should be diligent to maintain the accuracy and content of the file. To properly edit the file, you'll need to learn the syntax of the SDC commands. These commands are fully documented in the section titled Commands in the Precision Synthesis Reference Manual. In addition, examples of SDC commands will be presented in this Chapter.

# **Setting Timing Constraints**

If you do not specify timing constraints, Precision will map your design to technology cells but will not perform timing optimization. When you specify timing constraints, you only need to specify constraints on the top-level ports and Precision will characterize the top-level timing constraints through the lower-level blocks of hierarchy.

With timing constraints, Precision can make informed decisions about how to implement logic using technology cells. After the design is mapped, PreciseTime preforms static timing analysis to identify the paths that do not meet timing. If there are violations, Precision performs additional synthesis on these timing paths to increase the speed. This usually results in more hardware on the critical paths due to an increase in parallel structures, but only the critical paths are affected, not the whole design.

# **Setting Global Timing Constraints**

As a starting point, you can set the default global timing during the Design Setup step. After you Compile the design, you can add, refine and finalize the constraints before the Synthesize step.

You do this by selecting design objects in either the Design Browser or Schematic Viewer and use the right mouse button to display the timing constraint dialog box. Constraints that you apply to the an in-memory RTL design from the Precision GUI are automatically saved in the Precision generated .sdc file. The constraints are later reapplied to subsequent compile/synthesis iterations.

**NOTE:** For the purpose maintaining the integrity of the .sdc file, only constraint settings applied to the in-memory RTL design are saved to the .sdc file. If you add or edit constraints on the gate-level in-memory design, your changes are applied to the design, but not saved in the .sdc file. Based on this policy, the Design Hierarchy pane of the Design Center window always displays the RTL design.

Additionally, all of the constraint related commands now provide the -design option. This option takes one of two arguments, rtl or gatelevel, that specifies the design file to which the constraint will be applied. The default value is rtl.

Although setting constraints can be as simple as specifying a target design frequency or as powerful as indicating several multi-cycle paths, at a minimum, you should define the clock period on every detected clock pin. Precision displays these clocks in the right side of the Design Center.

By default, Precision does not check timing paths from inputs to registers or registers to outputs unless you specify timing constraints on the top-level input and output ports.

**NOTE:** As defined by the industry standard SDC format, since timing constraints must be set relative to defined clocks, you must specify your clocks prior to applying any other timing constraints.

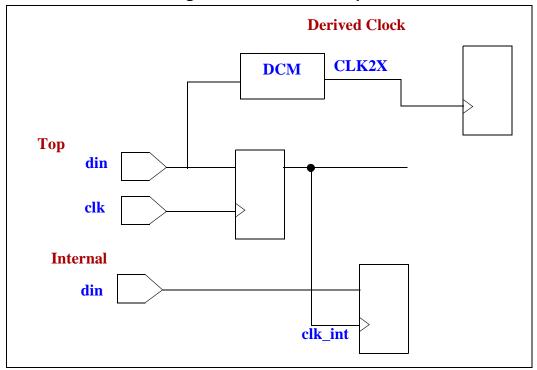

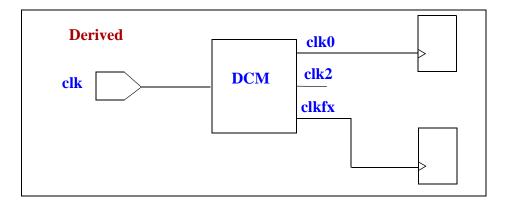

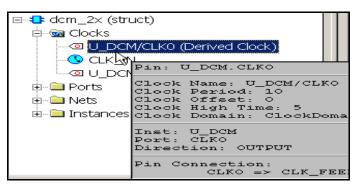

### **Clocks Overview**