PUBLICATION OF THE ASSOCIATION OF COMPUTER-CHIP EXPERIMENTERS (ACE) 1981

| Executive Corner                               | 2  |

|------------------------------------------------|----|

| Editors Corner                                 | 3  |

| Members Corner                                 | 3  |

| Netronics Full Basic and the Infamous EF2 Line | 5  |

| Tiny Basic Programs                            | 8  |

| The Megabyte Elf                               | 11 |

| Hex Keyboard for the Elf                       | 16 |

| 1802 to S-100 Bus Converter                    | 18 |

| A Notable Assembler                            | 21 |

| A Hardware Clock for the 1802                  | 26 |

| 1802 Plotter                                   | 34 |

| SPRECH - A Simple Software Voice Synthesizer   | 37 |

| Club Communique                                | 41 |

|                                                |    |

IPSO FACTO is published by the ASSOCIATION OF COMPUTER-CHIP EXPERIMENTERS (A.C.E.), a non-profit, educational organization. Information in IPSO FACTO is believed to be accurate and reliable. However, no responsibility is assumed by IPSO FACTO or the ASSOCIATION OF COMPUTER-CHIP EXPERIMENTERS for its use; nor for any infrigements of patents or other rights of third parties which may result from its use.

#### 1981/82 EXECUTIVE OF THE ASSOCIATION OF COMPUTER-CHIP EXPERIMENTERS

| President:                         | John Norris                                                                                                                             | 416-239-8567                 | Vice-President:           | Ken Bevis                                                    | 416-277-2495 |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------|--------------------------------------------------------------|--------------|

| Treasurer:                         | Mike Franklin                                                                                                                           | 416-878-0740                 | Secretary:                | Tony Hill                                                    | 416-523-7368 |

| Directors:                         | Bernie Murphy<br>Fred Pluthero                                                                                                          | 416-845-1630<br>416-389-4070 |                           |                                                              |              |

| Newsletter:                        |                                                                                                                                         |                              | Membership:               | Bob Silcox<br>Earle Laycock                                  | 416-681-2848 |

| Production<br>Manager:<br>Editors: | Mike Franklin<br>Fred Feaver<br>Steve Carter                                                                                            | 416-878-0740 🖋               | Program Convener:         | Bernie Murphy<br>Bert Dekat                                  |              |

|                                    | Bob Siddall<br>Tony Hill                                                                                                                |                              | Tutorial/Seminars:        | Ken Bevis<br>Fred Feaver                                     |              |

| Advertizing:                       | Fred Pluthero                                                                                                                           | 416-389-4070                 | Draughtsman:              | John Myszkowski                                              |              |

| Publication:                       | Dennis Mildon<br>John Hanson                                                                                                            |                              |                           |                                                              |              |

| Hardware &                         | Ken Bevis                                                                                                                               | 416-277-2495                 | Software:                 | Wayne Bowdish                                                | 416-388-7116 |

| K. and D.                          | Fred Pluthero<br>Dave Belgrave                                                                                                          |                              | Product Mailing:          | Ed Leslie                                                    | 416-528-3222 |

| Advertizing:<br>Publication:       | Steve Carter<br>Bob Siddall<br>Tony Hill<br>Fred Pluthero<br>Dennis Mildon<br>John Hanson<br>Ken Bevis<br>Don McKenzie<br>Fred Pluthero |                              | Draughtsman:<br>Software: | Ken Bevis<br>Fred Feaver<br>John Myszkowski<br>Wayne Bowdish |              |

#### CLUB MAILING ADDRESS:

A.C.E. c/o Bernie Murphy 102 McCraney Street East Oakville, Ontario Canada L6H 1H6 Phone: 416-845-1630

#### CLUB MEETINGS:

Meetings are held on the second Tuesday of each Month, September through June at 7:30 in Room B123, Sheridan College, 1430 Trafalgar Road, Oakville, Ontario. A one hour tutorial proceeds each meeting. The college is located approximately 1.0 km north of the QEW, on the west side. All members and interested visitors are welcome.

#### ARTICLE SUBMISSIONS:

The majority of the content of Ipso Facto is voluntarily submitted by club members. While we assume no responsibility for errors nor for infringement upon copyright, the Editorial staff verify article content as much as possible. We can always use articles, both hardware and software, of any level or type relating directly to the 1802 or to micro computer components, periferals, products, etc. Please specify the equipment or support software upon which the article content applies. Articles which are typed are prefered, and usually printed first, while handwritten articles require some work. Please, please send original, not photocopy material. We will return photocopies of original material if requested. Photocopies usually will not reproduce clearly.

#### ADVERTISING POLICY

ACE will accept advertising for commercial products for publication in Ipso Facto at the rate of \$25 per quarter page per issue with the advertiser submitting camera-ready copy. All advertisements must be pre-paid.

#### PUBLICATION POLICY

The newsletter staff assume no responsibility for article errors nor for infringement upon copyright. The content of all articles will be verified, as much as possible and limitations listed (ie Netronics Basic only, Quest Monitor required, requires 16K at 0000-3FFF etc.). The newsletter staff will attempt to publish Ipso Facto by the first week of: Issue 25 - Oct 81, 26 - Dec 81, 27 - Feb 82, 28 - Apr 82, 29 - Jun 82, and 30 - Aug 82. Delays may be incurred as a result of loss of staff, postal disruptions, lack of articles, etc. We apologize for such inconvenience, however they are generally caused by factors beyond the control of the club.

#### MEMBERSHIP POLICY

A membership is contracted on the basis of a club year - September through the following August. Each member is entitled to, among other privileges of membership, all 6 issues of Ipso Facto published during the club year.

# EDITORS CORNER

I am sure you are pleasantly surprised to see a newsletter so soon after receiving Number 26. There is a reason for our haste. The Canada Post Corporation has raised postage by over 100% effective January 1, 1982. This cost increase was beyond the club's budgeted increase, and quite frankly, beyond our ability to absorb. Since we operate on a annual subscription basis, we have no mechanism to generate more revenue from our members, so we must cut costs. By mailing this issue in 1981, we saved considerable postage costs. Unfortunately, it will not be enough. After much deliberation, the executive decided to restrict the size of newsletters to 42 pages (the size of issues 26 and 27). Forty-two pages will still permit the editors to create a broad ranging newsletter, which is just under the weight ceiling of level 2 first class mail rates. So far now, the 60 page encyclopedia newsletter is gone. We will still meet our commitment for 6 newsleters for this club year.

Your comments would be appreciated.

# Club Products

The club is currently field testing a prototype EPROM board designed to accommodate 2716/32/64 single 5 volt supply EPROM (28 pin JEDEC standard). We expect to be able to offer the board for sale by 31 March 1982. Current projects underway include a redesigned club 44 pin buss back plane and a new micro processor board for the club buss.

# Forth

Tony Hill made an excellent presentation on FORTH at the 8 December 1981 club meeting. His work on FORTH is well advanced and I should be able to report ordering information in the next newsletter.

Interested FORTH uses should be approaching FIG and Mountainview Press for appropriate documentation.

Best Article Issue 26: P. Liescheski - The Shroedinger Equation.

## MEMBERS CORNER

## FOR SALE.

- by Chuck Reid, 423 Huxley Ave., Sarnia, Ontario, N7S 4Z1

|   |                                                        | <u>Ca</u> | nadian Funds |

|---|--------------------------------------------------------|-----------|--------------|

| 2 | - Netronics 4K Static Ram Boards                       | 0         | \$50.00 each |

| 1 | <ul> <li>Netronics 4K Static Ram Board</li> </ul>      | 0         | \$25.00      |

|   | <ul> <li>memory bug, needs trouble shooting</li> </ul> |           |              |

| 1 | - Netronics Giant Board                                | 0         | \$20.00      |

| 1 | - Netronics AP-1 5 Amp Power Supply                    | 0         | \$20.00      |

| 1 | - SSM VB1C Video Display Board                         | 0         | \$100.00     |

| 1 | - Netronics VDB Video Display Board                    | 0         | \$150.00     |

|   |                                                        |           |              |

All boards are fully functional (except where noted) and are fully socketed (except Giant Board).

## FOR SALE:

BASIC NETRONICS ELF II, factory assembled and tested, brand new condition, Netronics metal cabinet and cover 1/4 K Ram, UHF channel 33 modulator, 5V power supply, Quest interface board with hexdisplays up to 65K and all mode indicators factory assembled and tested, all original Netronics and RCA documentation, almost all Questdata and IPSO FACTO newsletter. - \$200.00 or best offer.

Alain Jacynas, 3093 Allard, Montreal, P.Q., Canada, H4E 2M8 - Phone: DAY - 514-282-6530, EVENING - 514-761-7447

FOR SALE:

| 1 | Netronics ELF II                             | \$80.00  |

|---|----------------------------------------------|----------|

| 2 | Netronics 4K Static Memory - each            | \$78.00  |

| 1 | Case Computer                                | \$25.00  |

| 1 | 5 Amp Power Supply                           | \$30.00  |

| 1 | GIANT BOARD I/O                              | \$35.00  |

| 1 | Netronics Protobard                          | \$15.00  |

| 1 | Netronics Video display board with ASCII K/B | \$150.00 |

|   | and RF Modulator only                        |          |

Most chips socketed professionally assembled. All manuals included. OR

Everything for \$500.00 with Tiny Basic on Tape. Will consider trade for 8" disck drives.

Also available - Olivetti daisy wheel KSR terminal. RS-232 Interface inc. - \$2,350.00 NEW

S. Carter, 8086 Islington Ave., Woodbridge, Ontario, L4L 1W3, Phone: 851-2921

### FOR SALE:

- by Joe Matherly, Room 222A, 460 NE 215th St., Miami, Florida, 33179 Tel: 305-653-4900

NETRONICS ELF II 4K Boards, fully socketed, all chips included, DIP Switch addressing, excellent working condition. All 3 for \$130.00 or \$50.00 each if sold separately. I'll pay postage.

## FOR SALE:

Quest Super Elf with Expansion Board. All on-board options. Godbout 8K S100 video. Quest Super Color 6847-based board (partially assembled). ASC11 Keyboard. Full manuals and documentation, with some programs on cassette tapes. Quest Tiny Basic included.

All the above for \$650.00 US. I will ship. My cost was over \$1,000.

Also - ASR33 Teletype W/Modern. Everything works except tape reader unrealiable. \$250 US. Included full documentation including schematics with diagrams. Also some spare parts.

A. D. Barksdale Garbee II, 1601 Clayton Avenue, Lynchburg, Virginia, 24503, USA, Phone: (804) 384-2470

# NETRONICS FULL BASIC AND THE INFAMOUS EF 2 LINE

- by J. Vaal, 6535 Velmar Dr., Ft. Wayne, Indiana, USA, 46811

After reading the last several issues of <u>Ipso-Facto</u>, I almost regretted that I ordered Netronics Full BASIC last Winter. Well, Full BASIC LEV III A1 arrived a couple weeks ago, complete with a user manual, chock full of errors (including the ending address of the program). My two biggest complaints about this system are: 1, The RPN format is not identical to HP calculators and 2, The modifications to the GIANT BOARD significantly degrade the performance of the cassette read hardware. Problem 1 can be evidenced by solving the equation:

# $X = 5^2 + 6^2$

Quickly you can see the difference in stack operations. Unfortunately I do not have a solution to this problem.

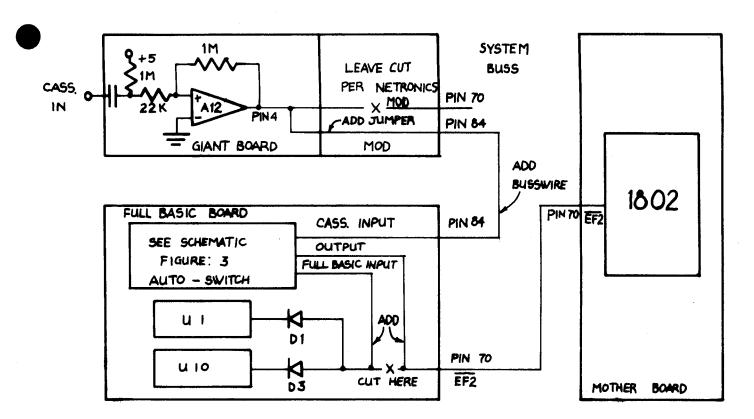

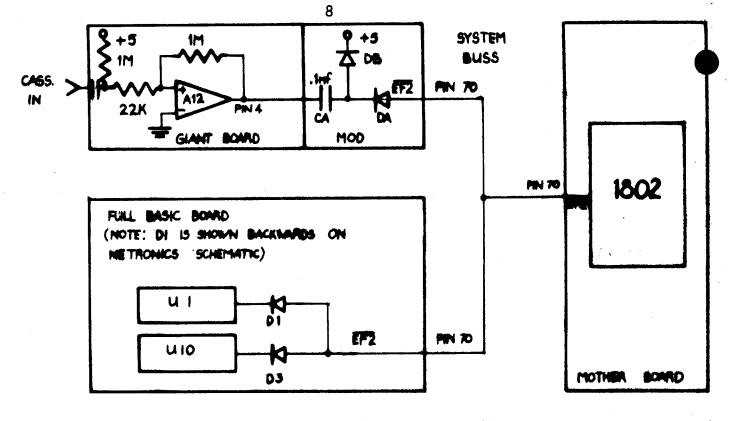

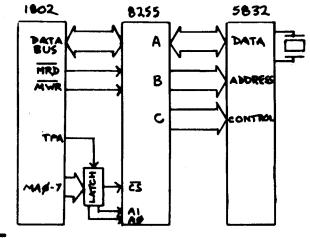

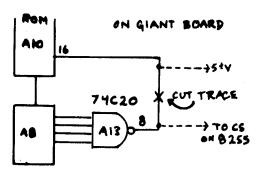

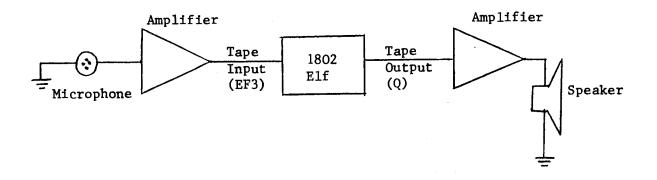

Problem 2, which, I believe is actually two sub-problems, can be neatly solved. The first, as described by Mr. M.E. Franklin in Issue #17, where the math chip holds the EF2 line low, occurs only when an error is detected by the math chip and the program is terminated or when the user terminates the program during math function execution. The capacitor / diode modification to the GIANT BOARD is not actually intended to and will not solve this problem. I believe, however, that the degradation of the cassette read hardware as a result of this modification is a far more significant problem. Figure 1 is a block diagram of the affected portions of the system when Full BASIC is installed. Capacitor Ca is added to the GIANT BOARD because the output of A12 (Pin 4) is normally low. Diode Db is a clamp on the output signal during cassette read and maintains the proper dc operating level. The problem with this modification, is that it partially defeats the purpose of the cassette read circuit (A12). This amplifier is intended to "square-up" the cassette signal, but capacitor Ca reduces the effectiveness of this circuit. Diodes Da (GIANT BOARD), D1, and D3 (BASIC board) comprise a "wired OR" so that the EF2 line may be shared.

#### AUTO-SWITCH CIRCUIT OPERATION

1

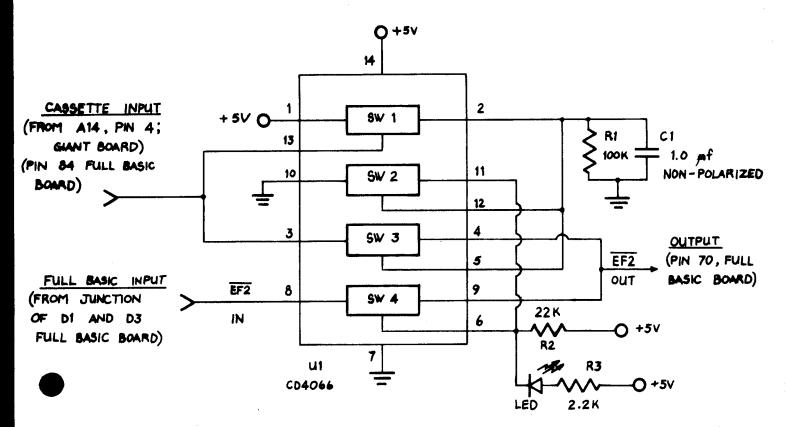

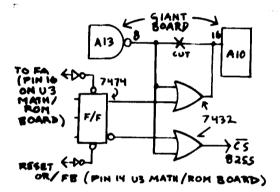

Figure 2 is a block diagram of the system where the Full BASIC GIANT BOARD modifications are removed and the Auto-Switch modifications added to the Full BASIC board. This circuit (Figure 3) is essentially an automatic switch that connects either the cassette read or the Full BASIC EF2 signals to the buss. The basic circuit consists of four components; U1 CD 4066 (quad bi-lateral switch), R1, R2, and C1. R3 and the LED are optional.

### AUTO-SWITCH CIRCUIT OPERATION continued

SW1 acts as a buffer for the A12 GIANT BOARD EF2 signal. When a cassette signal is present, C1 is charged to 5 volts which enables SW3 to put the cassette signal on the buss. SW2 is <u>simply</u> an inverter of the output of SW1 and turns off the Full BASIC EF2 signals. (SW4). The optional LED turns on when the cassette line takes control. When no cassette signal is present, SW4 is turned on, and the Full BASIC board has control of the EF2 line.

This modification eliminates the ac coupling of the cassette signal to the buss and allows a cassette read even when the Full BASIC board would be holding EF2 low. It should be noted, however, that after the program is loaded, it still may be necessary to enter "PR CL#" to resume normal operation of Full BASIC. This is because the "LOAD" routine does not reset the math chip.

This circuit does give priority to cassette operations and therefore the cassette recorder should not be operated during Full BASIC program execution.

#### CONSTRUCTION DETAILS

The circuit shown in Figure 3 may be readily added to the Full BASIC P.C. board in the area reserved for user hardware in the lower right hand corner of the board. The following modifications are necessary.

- 1) Remove the .1uf capacitor and the two diodes that were added to the GIANT BOARD for Full BASIC.

- 2) Connect a wire from A12 Pin 4 (where the capacitor was) to Pin 84.

- 3) Connect a wire on the mother board between pins 84 of the GIANT and Full BASIC board sockets.

- 4) On the Full BASIC board, cut the trace to Pin 70 after the junction of D1 and D3.

- 5) Wire up the Auto-Switch circuit as shown in Figure 3.

- 6) The total system should now be wired as shown in Figure 2.

At this point, one note of caution is in order. If the Full BASIC board is removed from the system, Pin 70 on the GIANT BOARD must be reconnected for cassette read operation. I have been using Full BASIC with this modification for several days now and have encountered no problems. As long as one remembers that the cassette will take priority over the math chip (as described earlier) there should be no problems. One interesting side effect of this modification is that the LED acts as a cassette signal present indicator, which is cute if not functional.

FIGURE 3: EF2 LINE AUTO-SWITCH

7

FIGURE 1: SYSTEM WITH NETRONICS MIL

# TINY BASIC PROGRAMS

-by G. Caughman - 3795 Somerset Dr., Margetta, Georgia, USA, 30064

DECIMAL TO HEX CONVERSION ROUTINE

10 REM INPUT DECIMAL VALUE AND THIS ROUTINE WILL 20 REM CONVERT IT TO AN EQUIVALENT HEX VALUE 100 INPUT X 110 LET I=X/16 120 U=X-16#I 130 LET J=1/16 1140 T=I-16#J 150 LET K=J/16 160 **S=J-**16#K 170 LET L=K/16 180 **R=K-16#L** 400 LET V=R 410 GOSUB 500 420 LET V=5 430 GOSUB 500 440 LET V=T 450 GOSUB 500 560 LET V=U **455 GOBUB 500**0 470 GOSUB 1000

500 IF V<10 GOTO 570 510 IF M=10 PRINT "A"; 530 IF V=11 PRINT "B" 550 IF V=12 FRINT "C" 552 IF V=13 PRINT "D" 554 IF V=14 PRINT "E": 556 IF V>15 PRINT "F" 560 RETURN 570 PRINT "V": 580 RETURN 1000 PRINT 1010 END TINY BASIC HEX TO DECIMAL ROUTINE 10 LET A=10 20 LET B=II 30 LET C=12 40 LET D=13 50 LET E=14 55 LET F=15 60 PRINT "INPUT FOUR HEX DIGITS EACH FOLLOWED BY COMMAS": 65 PRINT "EXCEPT LAST DIGIT. (MAX. 7, F, F, F)" 70 INPUT U,T,V,W **₹**5 U=U+16+16+16 80 T=T+16+16 85 V=V\*16

- 90 X=U+T+V+W

- 95 PRINT X

100 END

5 6 PRINT "MEMORY DISPLAY PROGRAM" PRINT PRINT "ENTER THE STARTING ADDRESS AS FOLLOWS: N,N,N,N."; 7 BRINT "WHERE N EQUALS EACH HEX DIGIT. (MAX 7, F, F, F)" 11 GO SUB 1010 20 25 LET Y = XPRINT "ENTER LAST ADDRESS THE SAME WAY" GO SUB 1010 30 35 40 LET Z = X50 REM CLEAR SCREEN AND SPACE PLOT (12) 51 52 56 PRINT LET X=Y 57 58 GO SUB 110 LET W = PEEK (Y) 59 Y=Y+1 65 LET X=W 72 REM SET BYTE FLAG FOR HEX OUTPUT ROUTINE 73 LET P=1 75 GO SUB 110 80 IF Y < 2 + 1THEN GO TO 56 85 END

REM HEX OUTPUT ROUTINE 100 110 LET I = X/16U = X - 16 + I120 LET J = I/16130 T = I - 16 \* J140 150 LET K = J/16160 S = J - 16 \* K170 LET L = K/16R = K - 16 \* L180 400 LET V=R 402 IF P=1 GOTO 435 410 GOSUB 500 420 LET V=S 430 GOSUB 500 434 REM RESET BYTE FLAG IF SET 435 LET P=0 **4**40 LET V=T 450 GOSUB 500 460 LET V=U 465 GOSUB 500 466 REM ALLOW TWO SPACES 470 PRINT "; 475 RETURN 500 IF V<10 GOTO 570 IF V=10 PR "A"; IF V=11 PR "B"; **51**0 530 IF V=12 PR "C" 550 IF V=13 PR "D"; IF V=14 PR "E"; 552 554 IF V=15 PR "F": 556 560 RETURN 570 PRINT V; 580 RETURN 1000 REM HEX TO DECIMAL ROUTINE 1010 LET A=10 1020 LET B=11 1021 LET C=12 1022 LET D=13 1023 LET E=14 1024 LET F\*15 1030 INPUT U,T,V,W 1040 U=U\*16\*16\*16 1050 **T=T+16+1**6 1060 V=V+16 1070 X=U+T+V+W 1090 RETURN

## THE MEGABYTE ELF

- by R. Siddall - 40 Cadillac Ave., Downsview, Ontario, Canada, M3H 1S2

#### INTRODUCTION

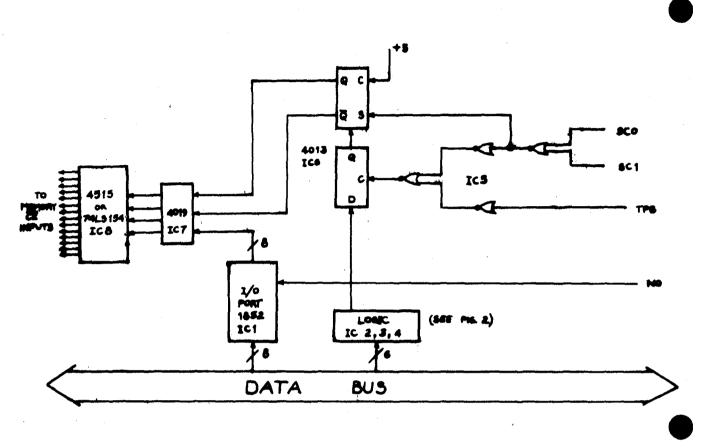

UP TO NOW, FEW HOBBYISTS HAVE FOUND THE 64K ADDRESSIBILITY LIMIT OF THE 1802 TO BE MUCH OF A PROBLEM. THE SITUATION MAY SOON CHANGE, HOWEVER. WITH THE APPEARENCE ON THE MARKET OF 64K X 1 RAM CHIPS, AND THE CONSTANTLY DECREASING COST OF OTHER LESS CAPACIOUS MEMORY CHIPS, IT MAY SOON BE NECESSARY TO FIND A WAY TO EXPAND THE USABLE MEMORY SPACE. TO ADDRESS THE PROBLEM (IF YOU WILL PARDON THE PUN) I HAVE DEVISED A MEMORY MANAGEMENT SCHEME THAT WOULD PERMIT AN 1802-BASED COMPUTER TO USE UP TO 1 MEGABYTE OF MEMORY, IN 64K SEGMENTS. OTHER BENEFITS OF MY SCHEME WOULD BE A MEMORY PROTECTION CAPABILITY, AND AN ABILITY TO SEPARATE THE PROGRAM SPACE FROM THE ADDRESS SPACE.

THIS SYSTEM IS AT PRESENT MERELY 'THEORETICAL', BUT IT IS RELATIVELY STRAIGHTFORWARD, AND I HOPE TO MAKE A BREADBOARD IMPLEMENTATION SOMEDAY. I ALSO INVITE OTHERS TO TRY IT OUT AND LET ME KNOW WHAT PROBLEMS I HAVE FAILED TO FORSEE.

ACCESSING 1 MEGABYTE REQUIRES A 20 BIT ADDRESS, 4 BITS MORE THAN IS PROVIDED BY THE 1802 ARCHITECTURE. IN MY SCHEME, TWO 4-BIT 'NYBBLES' WOULD BE LATCHED OFF THE DATA BUS BY AN I/O INSTRUCTION IN THE PROGRAM BEING EXECUTED. ONE OF THESE WOULD BE USED AS THE 'SEGMENT ADDRESS' (I.E. ADDRESS BITS 17-20) WHENEVER THE PROGRAM COUNTER REGISTER IS BEING USED TO ACCESS MEMORY: DURING THE FETCH CYCLE, AND WHENEVER AN 'IMMEDIATE' OR BRANCH INSTRUCTION IS BEING EXECUTED. THE OTHER SEGMENT ADDRESS IS USED FOR ALL OTHER MEMORY ACCESSES INCLUDING DMA REQUESTS. THE PROGRAMMER MAY CHOOSE TO MAKE THESE TWO SEGMENT ADDRESSES POINT TO THE SAME SECMENT, OR HE CAN HAVE A 64K PROGRAM SPACE AND A 64K DATA SPACE SIMULTANEOUSLY ACCESSIBLE.

#### HARDWARE

FIGURE I SHOWS THE HARDWARE REQUIRED. IC1 IS A STANDARD 1852 I/O PORT CONTROLLED BY AN I/O LINE FROM THE CPU. IT HOLDS ONTO THE SEGMENT ADDRESSES SENT TO IT BY THE CPU WHEN THE APPROPRIATE OUTPUT INSTRUCTION IS EXECUTED. AN RC CIRCUIT ON THE CLEAR PIN COULD BE USED TO SET BOTH SEGMENT ADDRESSES TO 0 AT POWER ON.

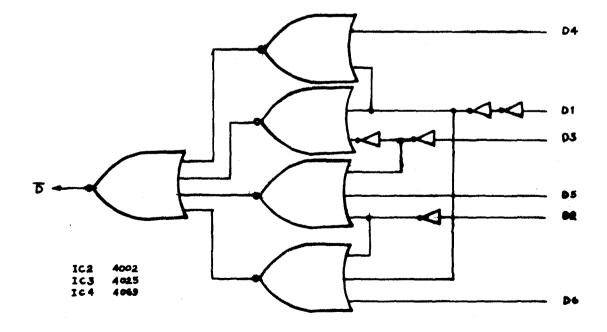

IC2, IC3, AND IC4 CONSTITUTE A LOGICAL ARRAY WHICH DISTINGUISHES WHETHER AN INSTRUCTION BEING FETCHED ON THE DATA BUS WILL REQUIRE DATA TO BE READ FROM THE PROGRAM SPACE (I.E. VIA REGISTER P) OR THE DATA SPACE (VIA REGISTER X OR ANY REGISTER OTHER THAN P). THE TRUE/FALSE OUTPUT OF THIS LOGICAL ARRAY IS HELD AFTER A FETCH CYCLE IN ONE HALF OF A 4018 DUAL D LATCH (IC6). I CALL THIS CIRCUIT (FIG. 2) THE 'INSTRUCTION/DATA DISCRIMINATOR'.

IC5 IS USED TO DISCRIMINATE BETWEEN A FETCH AND AN EXECUTE CYCLE. THE OTHER HALF OF IC6 PUTS OUT A TRUE/FALSE SIGNAL (AND ITS INVERSE) DEPENDING ON WHICH OF THE SEGMENT ADDRESSES IS TO BE USED IN THE SUBSEQUENT FETCH. IC7 IS A 4019 4 OF 8 SELECTOR WHICH PUTS OUT EITHER ONE OR THE OTHER SEGMENT ADDRESS FROM IC 1 DEPENDING ON THE OUTPUT OF IC6. IC8 IS A 4 TO 16 LINE DECODER WHICH WILL SELECT THE SEGMENT OF MEMORY REQUIRED.

I HAVE SPECIFIED CMOS ICS THROUGHOUT THE CIRCUIT, BUT I FULLY REALIZE THAT TIMING WILL PROBABLY BE A CRITICAL FACTOR, AND SOME OR ALL OF THE ICS MAY HAVE TO BE STTL OR EVEN ECL EQUIVALENTS TO THE CHIPS INDICATED TO MAKE THE SYSTEM WORK.

### SOFTWARE

THE 1852 I/O PORT WHICH HOLDS THE SEGMENT ADDRESSES CAN BE TIED TO ANY AVAILABLE I/O LINE ON THE 1802. IN WHAT FOLLOWS I ASSUME IT IS TIED TO NO. AN 'OUT1' (61) INSTRUCTION CAN THEN BE USED TO WRITE THE SEGMENT ADDRESSES TO THIS PORT. THE HIGH ORDER 4 BITS OF THE BYTE STORED IN THE PORT WOULD CONTAIN THE PROGRAM SEGMENT WHILE THE LOW ORDER 4 BITS WOULD CONTAIN THE DATA SEGMENT.

THE DATA SEGMENT CAN EASILY BE CHANGED AT ANY TIME UNDER PROGRAM CONTROL. LISTING I GIVES A SMALL PROGRAM THAT WOULD COPY DATA FROM SEGMENT 1 TO SEGMENT 2.

CHANGING THE PROGRAM SEGMENT WOULD BE A LITTLE MORE DIFFICULT, SINCE THE PROGRAM COUNTER WOULD BE UNAFFECTED BY THE CHANGE OF SEGMENT ADDRESS. FOR EXAMPLE, IF THE 'OUT1' INSTRUCTION THAT CHANGED THE SEGMENT ADDRESS WERE AT LOCATION 001FO, AND THE SEGMENT WERE CHANGED FROM 0 TO 2, THE NEXT INSTRUCTION EXECUTED WOULD BE THE ONE AT LOCATION 201F1. TO GET AROUND THIS, A PROGRAM SEGMENT CHANGE CONVENTION OF SOME KIND WOULD HAVE TO BE SET UP. MY SUGGESTION IS THAT EVERY SEGMENT USED AS A PROGRAM SEGMENT HAVE A 'SEP RO' INSTRUCTION IN LOCATION 0000 AND AN 'OUT1' INSTRUCTION IN LOCATION FFFF (THIS COULD BE IMPLEMENTED IN HARDWARE). THEN, TO CHANGE PROGRAM SEGMENTS, THE PROCEDURE WOULD BE AS FOLLOWS:

-SWITCH THE PC TO A REGISTER OTHER THAN RO,

-POINT THE X-REGISTER TO A BYTE CONTAINING THE TWO NEW SEGMENT ADDRESSES,

-POINT REGISTER RO TO THE ENTRY POINT OF THE PROGRAM TO BE EXECUTED IN THE NEW SEGMENT,

-BRANCH TO LOCATION FFFF.

CONTROL WOULD THEN JUMP TO THE 'OUT1' INSTRUCTION AT LOCATION FFFF, THE SEGMENT WOULD CHANGE. THE NEXT INSTRUCTION EXECUTED WOULD BE THE 'SEP RO' INSTRUCTION AT LOCATION 0000 OF THE NEW SEGMENT, CAUSING A BRANCH TO THE DESIRED PROGRAM.

TO TAKE ADVANTAGE OF THE SEPARATE ADDRESS SPACE, SPECIAL ASSEMBLER AND BASIC SOFTWARE WOULD HAVE TO BE DEVELOPED. FOR EXAMPLE, ADDRESS LABELS WOULD HAVE TO BE MARKED SOMEHOW AS TO WHETHER THEY WERE ADDRESSES IN THE PROGRAM OR DATA SPACE. EXISTING SOFTWARE WOULD STILL RUN, BUT IT WOULD BE CONFINED TO THE USUAL 64K. MEMORY PROTECTION

INHERENT IN THIS SCHEME IS A USEFUL FORM OF MEMORY PROTECTION. IF THE PROGRAM AND DATA SEGMENTS ARE DIFFERENT, IT IS IMPOSSIBLE FOR THE PROGRAM TO BE CLOBBERED BY A STRAY DATA POINTER OR FOR THE SYSTEM TO ATTEMPT TO EXECUTE DATA. FURTHERMORE, DATA IN SEGMENTS OTHER THAN THE TWO ACTIVE ONES CANNOT BE ACCESSED AT ALL, UNLESS AN ERRONEOUS 'OUT 1' INSTRUCTION IS EXECUTED.

FRONT PANEL FUNCTIONS

WITH A BIT OF ADDITIONAL HARDWARE, A FEW USEFUL FRONT PANEL FEATURES COULD BE ADDED. FOR EXAMPLE

- -THE OUTPUT OF IC6 COULD BE USED TO LATCH OUT THE CURRENT TRUE PROGRAM COUNTER FROM THE ADDRESS LINES.

- -THE ACTIVE SEGMENT ADDRESS(ES) COULD BE DISPLAYED ON THE FRONT PANEL.

- -THE PROGRAM AND DATA SEGMENTS COULD BE CONTROLLED FROM THE FRONT PANEL BY OVERRIDING THE OUTPUT OF IC7.

**OTHER CONSIDERATIONS**

OF COURSE, IT WOULD NOT BE NECESSARY TO ACTUALLY HAVE A MEGABYTE OF STORAGE, OR EVEN 64K, TO TAKE ADVANTAGE OF THIS SCHEME. IN THE SYSTEM I ENVISAGE, SEGMENT O WOULD CONSIST ENTIRELY OF ROM, AND WOULD CONTAIN THE OPERATING SYSTEM (STARTUP PROGRAMS, MONITOR, INTERPRETERS, MATHEMATICAL SUBROUTINES, ETC.). SEGMENT 1 WOULD BE RAM, BUT PART OF IT WOULD BE RESERVED FOR USE BY THE OPERATING SYSTEM TO STORE DATA, MAINTAIN STACKS, PASS PARMETERS, ETC. SEGMENTS 3 TO F WOULD BE AVAILABLE TO THE USER. IF NOT USED FOR MEMORY, ONE OR MORE OF THE SEGMENTS COULD BE USED FOR MEMORY-MAPPED I/O. SOME OF THE SEGMENTS COULD BE MISSING ALTOGETHER OR COULD CONTAIN LESS THAN 64K. IT WOULD, OF COURSE, BE UP TO THE USER TO REMEMBER WHERE THE HOLES ARE IN HIS ADDRESS SPACE.

ONE IDEA THAT INTRIGUES ME IS TO HAVE A 64K APL INTERPRETER IN SEGMENT O, WITH THE OTHER 15 SEGMENTS AVAILABLE AS APL WORKSPACES. (APL IS MY FAVOURITE LANGUAGE.)

IT WOULD BE NICE IF RCA (OR SOME ENTERPRISING SECOND-SOURCER) CAME OUT WITH A ONE-CHIP CMOS IC CONTAINING THE ABOVE CIRCUITRY, WITHOUT THE 4515, BUT INCLUDING A LATCH TO TAKE OFF THE UPPER ADDRESS BYTE. THE WHOLE THING COULD BE DONE IN A SINGLE 40 PIN IC. WHICH WOULD ADD A LOT OF POWER TO THE 1802 SERIES, AND ALSO MAKE LIFE EASIER FOR US HOMEBREWERS.

FIGURE 1 - MEMORY

MANAGEMENT CIRCUIT

FIGURE 2 - INSTRUCTION / DATA DISCRIMINATORS

# CONCLUSION AS I SAID EARLIER, THIS WHOLE SCHEME IS JUST THEORY AT THE MOMENT. UNFORTUNATELY I AM NOT VERY WELL EQUIPPED FOR THE AMOUNT OF BREADBOARDING THAT THIS SYSTEM WOULD ENTAIL. I WELCOME ANYONE ELSE TO TRY IT OUT AND SEND ME ANY COMMENTS THEY MAY HAVE.

LISTING I - SAMPLE PROGRAM TO COPY DATA BETWEEN SEGMENTS

- \* THIS PROGRAM COPIES DATA FROM SEGMENT 1 TO SEGMENT 2.

- \* \* R8 - STACK POINTER FOR DATA SEGMENT 1

- \* R9 STACK POINTER FOR DATA SEGMENT 2

LOOP

- **\*** RA CONTAINS START ADDRESS OF DATA IN SEGMENT 1

- \* RB CONTAINS DESTINATION ADDRESS IN SEGMENT 2

- \* RC CONTAINS NUMBER OF BYTES TO BE COPIED

| SEX  | R8   |                               |

|------|------|-------------------------------|

| LDI  | -X02 | SEGMENT POINTER P=0 D=2       |

| STR  | R8   | SAVE ON STACK IN SEGMENT 1    |

| OUT1 |      | SWITCH DATA SEGMENT TO 2      |

| DEC  | R8   |                               |

| SEX  | R9   |                               |

| LDI  | -X01 | SEGMENT POINTER P=0 D=1       |

| STR  | R9   | SAVE ON STACK IN SEGMENT 2    |

| OUT1 |      | SWITCH DATA SEGMENT BACK TO 1 |

| DEC  | R9   |                               |

| LDR  | RA   | GET BYTE TO BE COPIED         |

| SEX  | R8   |                               |

| OUT1 |      | SWITCH DATA SEGMENT TO 2      |

| DEC  | R8   |                               |

| STR  | RB   | STORE IN DATA SEGMENT 2       |

| SEX  | R9   |                               |

| OUT1 |      | SWITCH DATA SEGMENT TO 1      |

| DEC  | R9   |                               |

| INC  | RA   |                               |

| INC  | RB   |                               |

| DEC  | RC   |                               |

| GLO  | RC   |                               |

| BNZ  | LOOP | BRANCH BACK UNTIL RC IS ZERO  |

| GHI  | RC   |                               |

| BNZ  | LOOP |                               |

| *END |      |                               |

# HEXKEYBOARD FOR THE ELF

- by

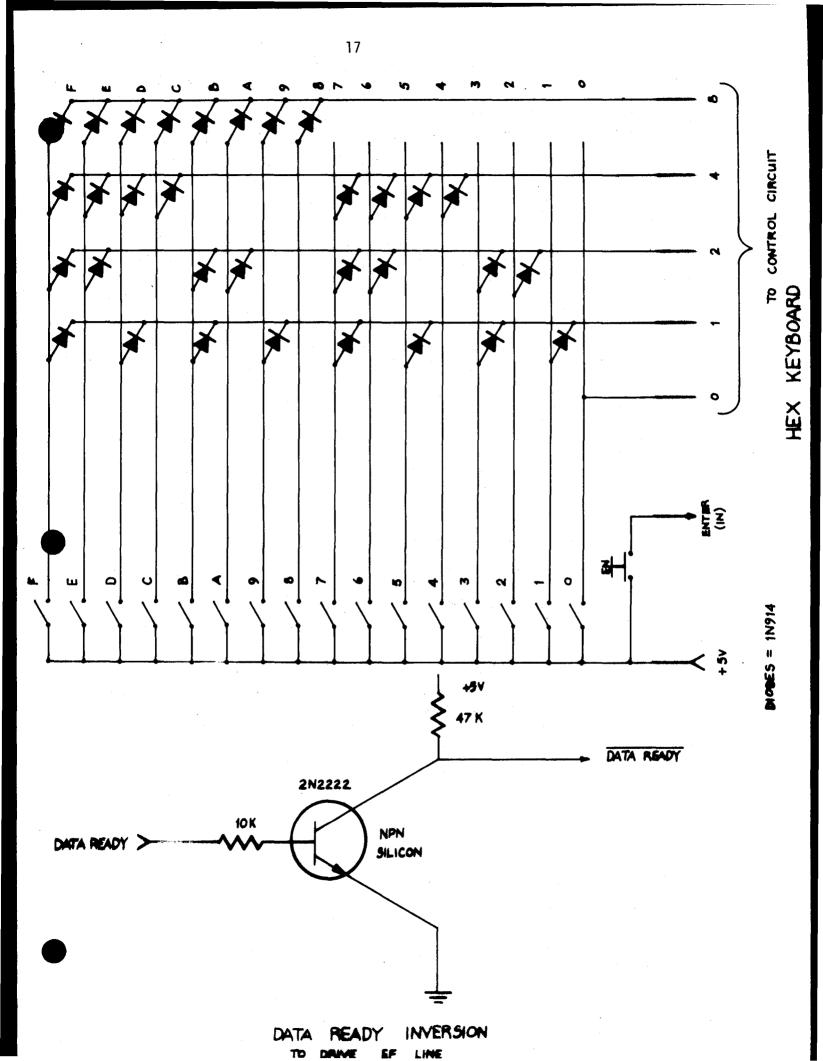

Here is another simple keyboard that will replace the data switches on the original ELF. The original circuit was taken from ETI Magazine (September 77, pa.60) and modified to hold the data into two latches. The circuit uses TTL chips because they were handy and cost me almost nothing. The circuit could be modified to use CMOS or LSTTL. The keypad comes from a surplus calculator keyboard bought from Rdio Shack. It was modified to make it a 16 spst switches arrangement with one side common. This was done by cutting the printed circuit and rewiring the switches. There are various surplus keyboard on the market and it should be easy to do the same with any keyboard providing you have access to the switches or the printed circuit. Most keyboard are 'matrix' type so they have to be modified to work in this circuit. 16 spst switches could also be used (push button type). Use IC socket for your circuit. The control circuit was built on a small phenolic board and screwed under the keypad with 12 wires coming out. (8 data, 45v, grd, strobe, enter). The extra switch replaces the IN switch in the original ELF I call it ENTER. A led (kbd ready) indicates the circuit is ready to accept another byte. When the second digit is pressed a data ready strobe is generated and inverted to drive an EF line on the 1802. I am including a short program that will input data in memory sequencely, it uses EF2 for input strobe.

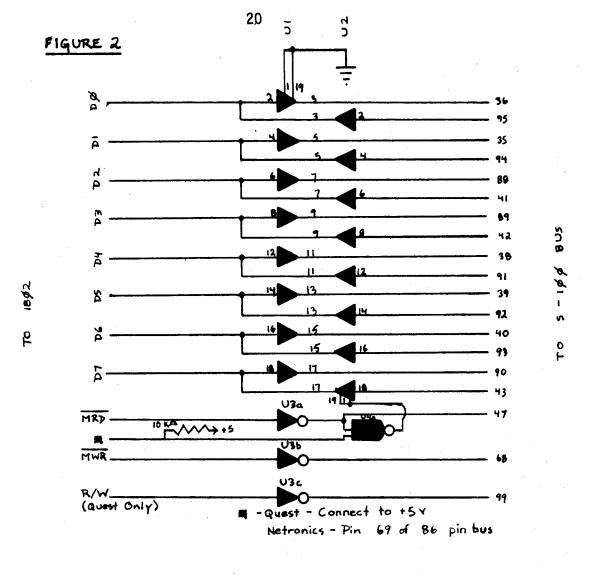

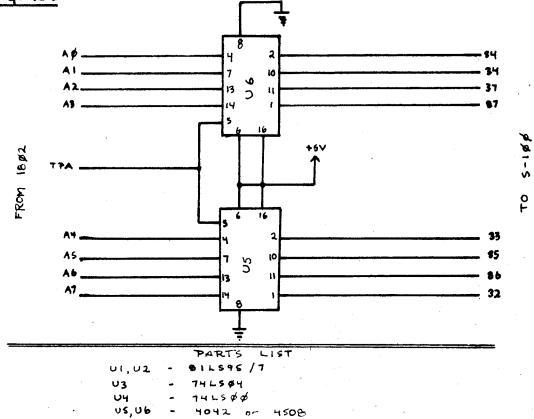

1802 TO S-100 BUS CONVERTER

- by David W. Schuler, 3032 Avon Road, Bethlehem, Pa. 18017, U.S.A.

Theory of Operation:

Bus buffer Ul is used to buffer the data lines from the 1802. Since the S-100 bus has separate data in/out lines, the chip select of the buffer is always enabled (pins 1 and 19 = 0). U2 is used to strobe the data from the S-100 bus onto the 1802 bi-directional data bus when a memory read is requested. The chip select of U2 is generated by U3a and U4a on the Elf II only. On the Elf II, pin 1 of U4a is connected to pin 69 of the 86 pin bus on the main board. This line indicates if an on-board memory address has been selected. If pin 69 = 0, the S-100 buffer is disabled. If pin 69 = 1, the S-100 bus buffer is enabled when a memory read request is received.

The Netronics Elf II also requires a latch for the upper 8 address bits (A8 to Al5). The required circuit is in Figure 3. This will latch the 8 high order addr. bits, and then the lower 8 address bits. This is because the S-100 board specifications require that the full 16 bit address be present on the bus at the same time.

For both the Quest Super Elf and the Netronics Super Elf, U3a, U3b, and U3c are required to invert the 1802 signals to the required S-100 signals.

Construction:

The entire circuit can be built on one S-100 interface card by either wire wrapping or point-to-point connections. If the Super Elf or the Elf II with Quest Adapter board is used, only a 50 conductor cable and S-100 prototyping card are needed. If only an Elf II is used, a Kludge Card for the 86 pin bus, an S-100 prototyping card and appropriate cable will be required. In either case, a S-100 mother board will be required.

Elf II Note:

In some cases, transistor Ql on all 4K Static RAM cards will have to be replaced with a higher speed transistor. Also, sometimes diode D4 on the Giant Board will have to be replaced with a higher speed germanium diode.

If there are any questions or comments on the interface outlined here, please send a SASE (Self Addressed Stamped Enveloped) along with your questions and I will try to help you out.

19

FIGURE 1

| <b>S-1</b> 00                          |               | connect to | 1802          |

|----------------------------------------|---------------|------------|---------------|

|                                        |               |            |               |

| (Pin #)                                | (Signal name) |            | (Signal name) |

| 1                                      | +8VDC         | 61         |               |

| 2                                      | +16VDC        | <b>8</b> 8 |               |

| 20                                     | GND           | 59         |               |

|                                        |               | **         |               |

| 25                                     | pSTVAL        |            | TPA           |

| 29                                     | <b>A</b> 5    | <b>99</b>  | <b>A</b> 5    |

| 30                                     | <b>A</b> 4    | **         | <b>A</b> 4    |

| 31                                     | A3            | **         | A3            |

| 22                                     | ÃI 5          | 87 .       | A15 (Note 1)  |

| 22                                     |               | n          |               |

| 33                                     | A12           |            | A12 (Note 1)  |

| 34                                     | A9            | <b>F</b> # | A9 (Note 1)   |

| 35                                     | DO            |            | DO1 (Note 2)  |

| 32<br>33<br>34<br>35<br>36<br>37<br>38 | DOØ           | **         | DOØ (Note 2)  |

| 37                                     | A1Ø           | **         | A1Ø (Note 1)  |

| 20                                     |               | **         |               |

|                                        | DO4           | 11         | DO4 (Note 2)  |

| 39                                     | D05           |            | D05 (Note 2)  |

| 40                                     | <b>D</b> 06   | Ħ          | DO6 (Note 2)  |

| 41                                     | DI2           | ¥9         | DI2 (Note 2)  |

| 42                                     | DI3           | **         | DI3 (Note 2)  |

| 43                                     | DI7           | **         | DI7 (Note 2)  |

|                                        |               | H          |               |

| 45                                     | sout          | **         | GND           |

| 46                                     | sINP          |            | GND           |

| 47                                     | SMEMR         | 88         | (Note 3)      |

| 50                                     | GND           | **         | GND           |

| 51                                     | +8VDC         | **         |               |

| 52                                     | -16VDC        | 87         |               |

| 52<br>68                               | MWRT          | 79         | (Nato 2)      |

| 00                                     |               |            | (Note 3)      |

| 70                                     | GND           |            |               |

| 77                                     | pWR           | **         | MWR           |

| 79                                     | AØ            | 71         | AØ            |

| 80                                     | AI            | ••         | AI            |

| 81                                     | A2            | 60         | A2            |

| 82                                     | <b>A</b> 6    | **         |               |

|                                        |               | 11         | <b>A</b> 6    |

| 83                                     | A7            |            | Α7            |

| 84                                     | <b>A</b> 8    | <b>91</b>  | A8 (Note 1)   |

| 85                                     | A13           | #          | A13 (Note 1)  |

| 86                                     | <b>A1</b> 4   | 54         | A14 (Note 1)  |

| 87                                     | A11           | 17         | A11 (Note 1)  |

| 88                                     | DO2           | <b>er</b>  | DO2 (Note 2)  |

| 89                                     |               | **         |               |

|                                        | D03           | 19         | D03 (Note 2)  |

| 90                                     | D07           |            | D07 (Note 2)  |

| <b>91</b>                              | DI4           | <b>99</b>  | DI4 (Note 2)  |

| 92                                     | DI5           | **         | DI5 (Note 2)  |

| 93                                     | DIĞ           | 84         | DIG (Note 2)  |

| 94                                     | DI1           | 88         | DI1 (Note 2)  |

| 95                                     | DIØ           |            | DIØ (Note 2)  |

| 99                                     | POC           | H          |               |

|                                        |               | 11         | (Note 3)      |

| 100                                    | GND           |            | GND           |

|                                        |               |            |               |

Notes: 1 - Elf II only: See Figure 3 for latch circuit for Address lines A8 to A15.

2 - <u>All</u>: See Figure 2 for data latch. 3 - <u>All</u>: See Figure 2 for circuit data. 4 - Other S-100 lines may have to be added as required by individual boards.

# A NOTABLE ASSEMBLER LOADER

- by D. Stevens, 4 Washington Sq. Village, #13R, N.Y., N.Y., USA, 10012

This routine allows one to assemble long object files without using tape or disk; it can produce an object file with length = RAM/3. I wrote it because I am tired of hand assembling my codes and do not have a terminal or an assembler, just an ELF-II with 8 K RAM. The source (which is machine code + address instructions) is usually less than twice as long as the assembled object file. The routine fits in 3 pages and runs slowly, needing for instance 20 seconds to process its own source (5 pages) and needing 200 seconds to process my operating system (source = 15 pages, object length = 08A0). It requires only 3 pages because it keeps no tables. It will run much faster and can be used as a loader if just the high address bytes are computed.

The source for the assembler has no mnemonics, only op codes and address data. The address data is given in strings of bytes all beginning with 68. For example, the address of a particular op code is given the name "AB" by preceeding the op code with "68 61 AB", it is given the name "CD EF" by preceeding it with "68 62 CD EF". In the source file, a short branch to these locations would be "30 68 11 AB" and "30 68 12 CD EF". When the assembler encounters a data form such as is in the left column below it performs the action described in the right column. Now look at the source listing of the assembler. The first two bytes tell the assembler to write the object code starting at 1000, the 68 03 01 00 tells the assembler that the load address of the object code is 01 00. The next data up to 0417 is op codes, compare with the object code listing. At 0418 is 68 22 01 26, At 0112 in the object listing the byte 03 then more op codes. occurs instead. The name "01 26" is defined at 0823 (the 68 62 01 26) and the address of the following byte is 035D.

Data String Compiler Action

68 00 A "68" will be inserted in the object code.

68 01 xx yy The address of the next byte in the object code will be the address of the last byte in the object code plus xx yy. This is a SKIP instruction to the compiler.

68 02 xx yy The low byte of the address of the next byte in the object code will be yy. The high byte will be the high byte of the last byte plus xx.

68 03 xx yy The address of the next byte in the object code will be xx yy This is an ORG instruction to to the compiler.

| ··              | name will be inserted.                                                                                                                                                                                                                                                                                                                      |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 68 2j (j bytes) | The high byte of the address associated with the name will be inserted.                                                                                                                                                                                                                                                                     |

| 68 3j (j bytes) | The high and low bytes of the address associated with the name will be inserted.                                                                                                                                                                                                                                                            |

| 68 4j (j bytes) | A preprocessor changes the source file as<br>follows: if the current object address is on<br>the same page as the address of the name<br>the 4j will be changed to 1j and the byte<br>preceeding the 68 will be changed from xy<br>to 3y. Oherwise the 4j will be changed to<br>3j and the byte preceeding the 68 will be<br>changed to Cy. |

| 68 6j (j bytes) | The name is associated with the address of the<br>next byte of the object code. The name is a<br>statement label.                                                                                                                                                                                                                           |

68 7j(j bytes)hhll The name refers to address hhll. This is an EQUATE instruction to the compiler.

The routine is used as follows. It is assumed that your system uses SCRT. The assembler object code is put at 0100-03D8. R8 should point to the low address end of a RAM area, the assembler will store useful data, described below. R9 should point to the start of a source file, and RA should point to the end of the file. The last byte in the file should not be part of address specifier; if it is, add a 00 to the end of your a 68... source. Note the 00 at the end of the source listing of the The source should start with uu vv 68 03 xx yy, where assembler. uu vv is the memory location where the object code will be put by the assembler and xx yy is the load address where the code will run. The assembler output should not overwrite the source. During assembly the high address byte of the source byte being processed is displayed. On return only registers R8, R9, RA and RF are changed. R9 now has uu vv and RA points to the end of the object code just generated. The source is modified; 68 4J patterns are changed to 68 1J or to 68 3J patterns.

If a 68 1j .... combination occurs and the referenced address is on a different page, the assembled program possibly will not be ok. So a list of all such questionable references is made with R8 the stack pointer. This stack grows upward. If for instance on entry R8 was 1400 and on exit R8 was 1404, then [1400] [1401] is the address in the source of a questionable combination, and also [1402] [1403]. Entries are also made if a 68 3j .... combination refers to an address which is on the same page.

The routine at 0327 - 0337 puts out the object bytes (the 5F instruction). This may be modified to fill a buffer and write to tape or disk rather than to memory.

22

68 11 (1 bytes)

The low byte of the address associated with the

If an error in the source data is detected the program branches to COOO. This error branch address can be changed, it is at 036C in the object code in the listing and at 0842 in the source part of the listing. The routine at COOO (or wherever) should save R3, R9, and RB. The error table below lists the possible error conditions.

# Error Table

| R3 | <b>D d a a a</b> | !-    |  |

|----|------------------|-------|--|

| רא |                  |       |  |

|    |                  | nosis |  |

019B illegal data at RB

01AE a "4j" in the source was not changed, is the source in ROM? 01B0 illegal data at RB

0227 illegal data at RB-1

0281 RB points to the last byte of a name which wasn't found

02C6 illegal data at R9

0305 illegal data at R9-1

### Summary of Usage

1. Set up the source file

- a. First five bytes are uu vv 68 xx yy

- b. No mnemonics

- c. Final byte not compiler instruction (68.....)

- 2. Put the assembler at 0100

- 3. Put an error handling routine at COOO (or an address you pick)

- 4. Set up R8, R9 and RA

- 5. Do SCRT call to 0100

6. If the routine exits to the error routine use the table above

7. If the routine makes a normal exit, check R8 and the data in the R8 stack.

#### Listing of Assembler Object Code

| 0100 | E2         | 8E | 73         | 9E  | 73 | 87 | 73  | 97         | 73 | 82        | FF         | 24         | A7  | 92 | 7 F        | 00         |

|------|------------|----|------------|-----|----|----|-----|------------|----|-----------|------------|------------|-----|----|------------|------------|

| 0110 | B7         | F8 | 03         | BE  | F8 | 5D | AE  | DE         | 04 | 19        | 19         | D4         | 03  | 38 | 05         | 40         |

| 0120 | FO         | 68 | FF         | 02  | D4 | 03 | 8C  | 17         | 07 | 32        | 69         | <b>8</b> A | 73  | 9A | 73         | 17         |

| 0130 | 47         | BA | BB         | BC  | 07 | AA | AB  | AC         | 1B | 1C        | D4         | 02         | A2  | 47 | BD         | 12         |

| 0140 | 42         | BA | 02         | AA  | D4 | 02 | 4A  | E7         | 9D | F3        | 17         | 32         | 5 B | 0C | FB         | 70         |

| 0150 | 5C         | 2C | 2 C        | 0C  | FA | 0F | F9  | <b>C</b> 0 | 5C | 30        | 1 B        | 0C         | FB  | 50 | 5C         | 2C         |

| 0160 | 2C         | 0C | FA         | 0F  | F9 | 30 | 5C  | 30         | 1B | 99        | BB         | 89         | AB  | 2B | 19         | 19         |

| 0170 | 19         | E9 | OB         | F7  | AC | 2B | 29  | <b>0B</b>  | 77 | BC        | 1B         | 29         | 29  | 8B | 52         | E2         |

| 0180 | <b>8</b> A | F3 | 3A         | 8A  | 9B | 52 | 9 A | F3         | 32 | FE        | 1B         | 9B         | 52  | 64 | 22         | <b>0</b> B |

| 0190 | FB         | 68 | 3A         | BE  | 1B | OB | FE  | 3B         | 9B | DE        | 00         | F6         | F6  | F6 | F6         | F6         |

| 01A0 | FE         | FC | <b>A</b> 4 | A3  | 30 | C5 | 30  | C8         | 30 | DC        | 30         | E2         | DE  | 00 | DE         | 00         |

| 01B0 | 30         | F9 | 0B         | FA  | OF | FC | 02  | 1B         | FF | 01        | 3A         | B7         | 30  | 7D | 0B         | B5         |

| 01C0 | D4         | 03 | 27         | 30  | 7D | C0 | 02  | 16         | 9B | 58        | 18         | 8B         | 58  | 28 | D4         | 02         |

| 01D0 | 4A         | 9D | E7         | F3  | 32 | D8 | 18  | 18         | 17 | 07        | 30         | BF         | D4  | 02 | <b>4</b> A | 47         |

| 01E0 | 30         | BF | 9B         | 58  | 18 | 8B | 58  | 28         | D4 | 02        | 4A         | 9D         | E 7 | F3 | 3 <b>A</b> | F2         |

| 01F0 | 18         | 18 | 47         | B5  | D4 | 03 | 27  | 30         | D9 | <b>0B</b> | FA         | OF         | 30  | B7 | 9F         | BA         |

| 0200 | 8F         | AA | DE         | 08  | 29 | 09 | AF  | 29         | 09 | <b>B9</b> | 8F         | A9         | 12  | 42 | B7         | 42         |

| 0210 | A7         | 42 | BE         | 02  | AE | D5 | 4B  | 32         | 27 | FF        | 01         | 32         | 2D  | FF | 01         | 32         |

| 0220 | 3D         | FF | 01         | 32  | 46 | DE | 00  | F8         | 68 | 2B        | CO         | 01         | BF  | 1B | OB         | 52         |

| 0230 | <b>8</b> D | F4 | AD         | 2 B | 4B | 52 | 9D  | 74         | BD | 2D        | <b>C</b> 0 | 01         | 7 D | 4B | 52         | 9D         |

| 0240 | F4         | BD | <b>0B</b>  | AD  | 30 | 3A | 4B  | BD         | 30 | 42        | DE         | 01         | 0B  | FA | 0F         | <b>A8</b>  |

| 0250           | B8 1B | FF    | 01 | 3A | 51       | 9B | BF | 8B | AF | OF        | 2F  | Е7 | 73         | F8        | FF         |

|----------------|-------|-------|----|----|----------|----|----|----|----|-----------|-----|----|------------|-----------|------------|

| 0260           |       | 88    |    |    | 98       |    | 60 |    |    | EF        |     | F8 | 68         | 73        | F8         |

| 0270           | FF 73 |       |    |    | 73       |    |    |    |    | 47        |     |    | 2          | 81        |            |

|                | 00 47 |       |    |    | 1A       |    |    |    |    | 92        |     | D4 |            | A2        |            |

| 0280           |       |       |    |    |          |    |    |    |    |           |     |    |            | 0A        |            |

| 0290           | 02 D5 |       | 1A |    | 01       |    |    |    | 1A |           | 0A  |    |            |           |            |

| <b>02A</b> 0   | 30 8F |       |    |    | 52       |    |    |    |    | 99        | 52  |    | F3         |           | B8         |

| 02B0           | 88 57 |       |    |    | DE       |    |    |    |    | 68        |     |    | 18         |           | A4         |

| 02C0           | 09 FE |       |    |    | 00       |    |    |    |    | F6        |     |    | CF         | A3        |            |

| 02D0           | FO 30 | ) ED  | 30 | ED | 30       | EC | 30 |    |    | 00        |     | E9 | 49         | 19        | 19         |

| 02E0           | FA OF | 19    | FF | 01 | 3A       | E2 | 30 | A4 | 49 | 30        | EO  | 18 | 18         | 30        | E9         |

| 02F0           | 49 C2 |       |    | FF | 01       | C2 | 03 | 09 | FF | 01        | C2  | 03 | 19         | FF        | 01         |

| 0300           | C2 03 |       |    |    | 18       |    |    | A4 | 19 | 09        | 52  | 88 | F4         | <b>A8</b> | 29         |

| 0310           | 49 19 |       |    |    | B8       |    |    |    |    | 52        |     |    |            |           | <b>A8</b>  |

| 0320           | CO 02 |       |    | B8 |          | 1E |    |    |    | F4        |     |    |            |           | 74         |

| 0330           | BF 95 |       |    | B5 |          | 9F |    |    |    | E7        |     | 73 |            |           |            |

| 0340           | 3B D5 |       |    |    | 73       |    |    |    |    | 8B        |     |    |            |           |            |

|                | 8A 73 |       |    |    | 73       |    |    |    |    | 98        |     |    |            |           | F6         |

| 0350           |       |       |    |    |          |    |    |    |    | 90<br>7D  |     |    |            |           | 42         |

| 0360           | 33 50 |       |    |    | F6       |    |    |    |    |           |     |    |            |           | BB         |

| 0370           | B8 42 |       |    |    | 42       |    |    |    |    |           | 30  |    |            |           |            |

| 0380           | 42 AF |       |    |    | AC       |    |    |    |    | 30        |     |    |            |           | 04         |

| <b>039</b> 0   | 17 07 |       |    |    | B8       |    |    |    |    | 2A        |     |    |            |           | AB         |

| 0 3A0          | E7 99 |       |    |    | 98       |    |    |    |    | 17        |     |    |            |           | C1         |

| 03B0           |       | B 3A  |    |    | 73       |    |    |    |    | 57        |     |    |            |           | 02         |

| 0 <b>3CO</b>   | D5 E2 | 299   | 52 | 9A | F3       | 32 | CB | 19 | 30 | 9E        | 89  | 52 | <b>8</b> A | F3        | 3A         |

| 0 <b>3 D O</b> | C8 21 | 3 8 B | 32 | BA | 17       | 17 | 30 | D1 |    |           |     |    |            |           |            |

| 0400           | 11 00 | ) 68  | 03 | 01 | 00       | E2 | 8E | 73 | 9E | 73        | 87  | 73 | 97         | 73        | 82         |

| 0410           | FF 24 |       |    | 7F |          | B7 |    |    |    | 01        |     |    | F8         |           |            |

| 0420           |       | 5 AE  |    |    | 00       |    |    |    |    | 19        |     |    |            |           | D4         |

| 0430           |       | 2 01  |    | 05 |          | FO |    |    |    | 02        |     | 68 |            |           | DO         |

| 0440           | 17 07 |       |    | 12 |          |    | 8A |    |    | 73        |     | 47 |            |           | BC         |

| 0440           | 07 AA |       |    |    | 10       |    |    |    |    | 0A        |     |    |            |           | BA         |

|                | 07 AF |       |    |    |          |    |    |    |    |           |     |    |            |           |            |

| 0460           |       |       |    |    | 01       |    |    |    | F3 |           | 32  | 68 |            |           | E2         |

| 0470           |       | B 70  |    |    | 2C       |    |    |    |    | C0        |     |    | 68         |           |            |

| 0480           | E1 68 |       |    |    | 00       |    |    |    |    |           |     |    | OF         |           | 30         |

| 0490           | 5C 30 |       |    |    | E1       |    |    |    |    | 99        |     |    |            |           | 19         |

| 04A0           | 19 19 |       |    |    | AC       |    |    |    |    | BC        |     |    |            |           | 62         |

| 04B0           | 00 E4 |       |    |    |          |    | 3A |    |    |           | E5  |    |            |           | F3         |

| 04C0           | 32 68 |       |    |    | 68       |    |    |    |    |           | 52  |    |            |           | FB         |

| 04D0           | 68 00 |       |    |    | 00       |    |    |    |    |           | 68  |    |            |           | DE         |

| 04E0           | 00 68 | 3 62  | 00 | E6 | F6       | F6 | F6 | F6 | F6 | FE        | FC  | 68 | 12         | 00        | E7         |

| 04F0           | A3 68 | 3 62  | 00 | E7 | 30       | 68 | 12 | 00 | EB | 30        | 68  | 12 | 00         | EC        | 30         |

| 0500           | 68 12 |       |    |    | 68       |    |    |    |    |           | DE  |    |            |           | 12         |

| 0510           | 00 F2 |       |    |    | FC       |    |    |    |    |           | 1 B |    |            |           | . 68       |

| 0520           | 12 00 |       |    |    | 12       |    |    |    |    |           | E9  |    |            |           | 00         |

| 0530           | EA BS |       |    |    | 01       |    |    |    |    | 00        |     |    |            |           | EB         |

| 0540           | CO 68 |       |    |    | 68       |    |    |    |    | 58        |     |    |            |           | D4         |

| 0550           | 68 32 |       |    |    | E7       |    |    |    |    | 00        |     |    |            |           | 62         |

| 0560           | 00 EI |       |    |    | ыл<br>00 |    |    |    | 68 |           | 00  |    |            |           | 02         |

|                |       |       |    |    |          |    |    |    |    |           |     |    |            |           |            |

| 0570           | EF D4 |       |    |    | 00       |    |    | 68 |    |           | EA  |    |            |           | FO         |

| 0580           | 9B 58 |       |    |    | 28       |    |    |    | 01 |           | 9D  |    | F3         |           | . 68       |

| 0590           | 12 00 |       |    |    | 68       |    |    |    |    | B5        |     | 68 |            |           | 1F         |

| 05A0           | 30 68 |       |    |    | 68       |    |    |    |    | FA        |     |    |            |           | 00         |

| <b>05B</b> 0   | E8 68 | 8 62  | 00 | F3 | 9F       | BA | 8F | AA | DE | <b>08</b> | 29  | 09 | AF         | 29        | 0 <b>9</b> |

|                |       |       |    |    |          |    |    |    |    |           |     |    |            |           |            |

24

.

.

| 05C0 | B9 8F | A9 12 | 42 B7          | 42 A7 | 42 BE   | 02 AE         | D5 68 62 00        |

|------|-------|-------|----------------|-------|---------|---------------|--------------------|

| 05D0 | F4 4B | 32 68 | 12 00          | F5 FF | 01 32   | 68 12         | 00 F6 FF 01        |

| 05E0 | 32 68 |       | F8 FF          | 01 32 | 68 12   | 00 FA         | DE 00 68 62        |

| 05F0 | 00 F5 |       | 00 2B          |       |         | EA 68         | 62 00 F6 1B        |

| 0600 | OB 52 |       | AD 2B          |       |         | BD 2D         | 68 62 00 F7        |

| 0610 | CO 68 |       | E4 68          |       |         | 52 9D         | F4 BD 68 62        |

| 0620 | 00 F9 |       | 30 68          |       |         | 62 00         | FA 4B BD 30        |

| 0630 | 68 12 |       | 68 62          |       |         | OB FA         | OF A8 B8 68        |

| 0640 | 62 01 |       | FF 01          |       |         | 01 <b>9</b> B | BF 8B AF 68        |

| 0650 | 62 01 |       | 2F E7          |       |         | 28 88         | 3A 68 12 01        |

| 0660 | 02 98 |       | 73 F8          |       |         | 00 73         | F8 FF 73 98        |

| 0670 | FC 02 |       | 68 32          |       |         | FB 55         | 32 68 12 01        |

| 0680 | 03 DE |       | 62 01          |       |         | AA 1A         | OA FA 10 3A        |

| 0690 | 68 12 |       | 2A D4          |       |         | 68 62         | 01 04 DE 02        |

| 06A0 | D5 68 |       | 05 98          |       |         | 1A FF         | 01 3A 68 12        |

| 06B0 | 01 06 |       | E7 0A          |       |         | 30 68         | 12 01 04 68        |

| 0600 | 62 01 |       | 01 68          |       |         | 52 8A         | F3 3A 68 12        |

| 06D0 | 01 00 |       | 9A F3          |       |         | 0C 88         | 57 27 98 57        |

| 06E0 | DE 02 |       | 62 01          |       |         | 00 32         | 68 12 01 0D        |

| 06F0 | 18 30 |       | 01 OF          |       |         | 09 FE         | <b>3B</b> 68 12 01 |

| 0700 | OE DE |       | 62 01          |       |         | F6 F6         | FE FC 68 12        |

| 0710 | 01 OF |       | 62 01          |       |         | 01 15         | 30 68 12 01        |

| 0720 | 14 30 |       | 01 14          |       |         | 13 30         | 68 12 01 13        |

| 0730 | DE 00 |       | 12 01          |       |         | 68 62         | 01 10 FA OF        |

| 0740 | 68 62 |       | 12 01<br>19 FE |       |         | 01 11         | 30 68 12 01        |

| 0750 | OB 68 |       | 12 49          |       |         | 10 68         | 62 01 13 18        |

| 0760 | 68 62 |       | 18 30          |       |         | 68 62         | 01 15 49 C2        |

| 0770 | 68 32 |       | FF 01          |       |         | 17 FF         | 01 C2 68 32        |

| 0780 | 01 18 |       | C2 68          |       |         | 00 68         | 62 01 16 18        |

| 0790 | C0 68 |       | 0B 68          |       |         | 09 52         | 88 F4 A8 29        |

| 07A0 | 49 19 |       | 74 B8          |       |         | 01 1A         | 68 62 01 18        |

| 07B0 | 49 52 |       | B8 68          |       |         | A8 68         | 62 01 1A CO        |

| 07C0 | 68 32 |       | 68 62          |       |         | 30 68         | 12 01 19 68        |

| 0700 | 62 01 |       | 52 80          |       |         | 9C 74         | BF 95 5F 94        |

| 07E0 | B5 1D |       | 68 62          |       |         | E7 68         | 62 01 21 46        |

| 07E0 | 73 2F |       | 68 12          |       |         | 62 01         | 23 8D 73 9D        |

| 0800 | 73 8C | -     | 73 8B          |       |         | 68 12         | 01 25 68 62        |

| 0810 |       | 8A 73 |                | 89 73 | 99 73   |               | 98 73 68 62        |

| 0820 | 01 25 |       | 62 01          |       |         | 33 68         | 12 01 24 F6        |

| 0830 | 33 68 |       | 27 F6          |       |         | 23 F6         | 33 68 12 01        |

| 0840 | 28 CO |       | 68 62          |       |         | B8 42         | A8 42 B9 42        |

| 0850 |       | BA 02 | AA 30          |       | 01 25   |               | 01 28 12 42        |

| 0860 |       | AB 42 | BC 42          |       |         | AD 30         | 68 12 01 25        |

| 0870 |       | 00 D0 | DE 01          |       |         | 68 62         | 00 D1 BB AB        |

| 0880 | 97 B8 |       | 1A 68          |       |         | 2A 8B         | <b>3A 68 12 00</b> |

| 0890 |       | 62 00 | D3 9B          |       |         | 89 AC         | 98 B7 88 A7        |

| 08A0 | 68 62 |       | 4C 17          |       |         | 68 12         | 00 D6 2B 8B        |

| 08B0 | 3A 68 |       | D4 89          | 73 99 |         | 55 68         | 62 00 D5 57        |

| 0800 | 27 DE |       | 02 D5          | 68 62 |         | E2 99         | 52 9A F3 32        |

| 08D0 |       | 00 D8 | 68 62          | 00 D7 | 19 30   |               | 00 D3 68 62        |

| 08E0 | 00 D8 |       | 8A F3          | 3A 68 | 12 00 1 |               | 62 00 D9 2B        |

| 08F0 | 8B 32 |       | 00 D5          |       |         | 12 00         | D9 00              |

|      |       |       |                | -· /  | 55 56   | ~~ 00         |                    |

# A HARDWARE CLOCK FOR THE 1802

- by J. Swofford, 2302 N. Fairview Ave. Decater, Illinois, USA, 62526

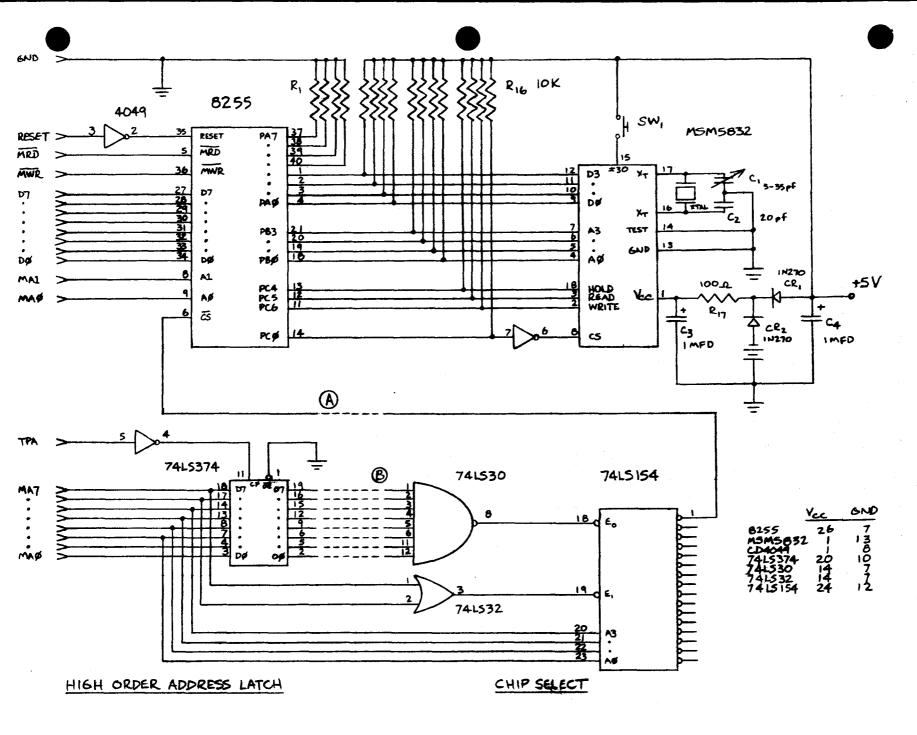

Last spring I ordered an OKI real-time clock/calendar to fill a need for time-keeping in my ELF II. My circuit built around this I.C. is memory-mapped via 8255 PPI and allows access to time in hours, minutes and seconds and the date as well as the day-ofweek. Time can be kept in either a 12 or 24 hour format and leap year compensation is provided. My system has the 8255 located at FFOOH to FFO3H. Unfortunately, the Netronics monitor interferes with locations beyond FDFFH, so some ELF II owners may wish to locate the 8255 elsewhere or, as I did, enable the Netronics monitor only for FOOOH to FOFFH (as it should have been, anyway).

# INTERFACING THE CLOCK

The data sheet from OKI shows a suggested arrangement using the Intel 8255 PPI. Since I already had a few spares, it seemed the easiest route to take. The capabilities of the PPI are too extensive to cover here so I will be concerned with only those aspects which affect this application. Memory locations FFOOH to FFO3H will be assumed. All three of the 8255 I/O ports are used. The PPI operates here in mode O in two configurations; one to read

from the clock and one to write to the clock (see figure 1). These states are created by writing 80H into location FF03H for clock WRITE and 90H for clock READ. These bytes control how the 8255 itself operates. An 80H will allow port A to be an output port (ports B and C remain output ports for both clock READ and clock WRITE). Similarly, 90H allows port A to input the data nibble from the clock data lines. Port B is used to provide the clock address nibble and port G

is for clock control (see table 1). When the 8255 is reset, all 24 bits (three 8 bit ports) normally float. In this circuit, R1-R16 will pull these lines high. This would normally place the clock in a HOLD state, stopping the time increment. Therefore, PCO (bit 0-port C) is inverted before going to the chip select pin on the clock. This removes all control (including HOLD) from the

clock and allows it to continue keeping time. The upper portions of ports A and B (PA4-7 and PE4-7) are not used. PA4-7 is tied to ground through 10K resistors to avoid having to 'strip' them off in software during clock READ.

## ADDRESSING

Since I use other 8255s in my system, the schematic shows a 74LS154 providing  $\overline{CS}$  for the clock's 8255. Using this arrangement, 16 different PPIs can be selected yielding 48 8-bit I/O ports. Many good methods of high order address latching and chip selection have appeared in Ipso Facto. This one works for me. Since you may not have an interest in this expansion idea, you may wish to use an alternate method of chip select which eliminates the 74LS30, 74LS32, 74LS154 and 74LS374 (figure 2). Cut the trace on the Netronics Giant Board between pin 8 on A13 and pin 16 on A10. Run a line from A13 pin 8 to point  $\triangle$  (chip select-see clock schematic). A10 pin 16 should be tied high to disable the ROM. The 8255 will now have addresses F000H to F003H. The Demo program will run unmodified with this arrangement. I have tried thisit works. It should be possible to place a switch on the Giant

FIGURE 2

Board to switch from the monitor to the clock and vice versa. If you are using Netronics' Full BASIC, the only way to into BASIC is through the monitor. You may want to develop the idea in figure 3 using SF1# to enable the clock once BASIC has been entered (I have not tried this). The modular appearance of the address and select circuitry is to emphasize the idea

of using presently available circuitry you may already have in your system. If you have the upper address bits already latched from some other project, try connecting those lines to the 74LS30 at point (B), eliminating the 74LS374. I should mention that the Netronics 4K memory board has these address bits already latched and marked on the board itself. I have not tried using them, however. Note that CMOS was not used. I have had no problems using TTL but you may wish to use the 74C series, anyway.

THE CLOCK

The MSM5832 is basically a digital watch in a DIP package. Each of the 13 digits available (HH MM SS W MM DD YY) must be called for one at a time. This is done by addressing the digit to be read/written (don't confuse with the ELF address/data lines), commanding the clock and reading/writing the clock (see figure 4). The HOLD line should not be high for more than one second in order that the clock can increment. The demo program does not use HOLD on READ due partly to this requirement (see figure 5).

The H1O and D1O digits are special. The H1O digit contains flags for PM and 24 hour operation. The D1O digit contains a flag for leap year (table 2). The  $\pm 30$  second adjust causes 1 minute to be added to the LSB of the minutes if seconds are 30 or more as the seconds are set to zero. If less than 30 seconds, only the seconds

## FIGURE 3

If less than 30 seconds, only the seconds are affected. Battery backup is provided by 2 alkaline penlight cells. Backup is not required; it is recommended. It is a pain to reload the clock every time the computer has been powered down. Just ask any TRS-80 model III owner. The very low drain of the 5832 should give many months (years?) of service. Time regulation is through C1. Decrease C1 to speed the clock; increase C1 to slow the clock.

# SOFTWARE

The clock demo was written for an ELF II using the Netronics video board and the 8255 at FFOOH. In Cenker's BASIC ver. 5, this program uses about 1.5K of memory without REMs. The program is easily altered to run at any location by changing line 60 ("#" and "@" indicates hexidecimal in Quest BASIC). The clock READ did not use HOLD since BASIC tied up the clock too long and caused it to lose time. Constant interrogation of the clock should be done in machine code. The time and date is updated on the CRT about every 4 seconds. A more frequent update can be achieved by leaving out the unnecessary statements and not calling for the date everytime.

## COMMENTS

Information on obtaining parts is in order. The MSM5832 and crystal (32.768 Hz) is available form several sources including Concord Computer Products, 1971 So. State College, Anaheim, Ca. 92806 and Digi-Key, Hiway 32 South, P.O. Box 677, Thief River Falls, Mn. Both suppliers provide the data sheet. The 8255 and other 56701 ICs are available from just about anywhere. The trimmer (C1) is sold by Jameco, 1355 Shoreway Road, Belmont, Ca. 94002. The components can be mounted on a Radio Shack perf board P/N 276-1395. For those of us who aren't made of money, here are a couple of suggestions. Don't throw away 5832 that digital watch. You may be able to use the 92 DATA 1/0 31 small crystal in it like I did (32.768Hz). As 76 for the other parts, try a hamfest. I have A3 A7 ANDR LINES 4 saved millions(?) by doing my parts procurement AØ. at hamfests. Ask any amateur radio operator for HOLD WRITE information on where and when. CELECT

One aspect of the 5832 which I have FIGURE 4 not mentioned is the interrupt signals (figure 6). While I have not made use of them in this circuit, there are many ways to utilize these pulses which, I hope, others will find. For example, the 1024 Hz and 1 Hz could be combined for a software controlled beeper (see figure 7) while the clock is not being accessed. The 60 Hz pulse could be used for a time base in an UPS (Uninterruptable Power Supply) system. The 1 Hz could be used to flash lights. I suppose you could even use these signals for interrupts. What about the clock? How about this:

\*Interrupt driven timer

\*Countdown timer with a HOLD capability

\*Event control (ESR control system)

\*Data timestamping

The design is relatively simple, the applications are many. From control to display, this clock can be a useful addition to any system.

# Ref. OKI data sheet, March 1980

Intel data manual, October 1977, pp 6-223 to 6-240

FIGURE 5

| ABLE         | <u>1</u> de  | emo pro         | gram varial                            | oles summary                            |

|--------------|--------------|-----------------|----------------------------------------|-----------------------------------------|

| orm          | hex v        | value           | decimal val                            | lue used in program for:                |

| A            | FF           | 00              | <b>6528</b> 0                          | ELF memory address-port A (clk I/O      |

| в            | FF           | D <b>1</b>      | 6528 <b>1</b>                          | ELF memory address-port B (clk adr)     |

| C            | FFC          | 02              | 65282                                  | ELF memory address-port C (clk contl)   |

| D            | FF           | 03              | 65283                                  | ELF memory address-8255 contl port      |

| E            | 90           |                 | 1 կկ                                   | control for 8255 (A=input)              |

| F            | 20           |                 | 32                                     | port C-enable clk SELECT/READ           |

| G            | 50           |                 | 80                                     | port C-enable clk SELECT/HOLD/WRITE     |

| H            | 80           |                 | 128                                    | 8255 control-ports A, B, C are outputs  |

| ===:         | ====:        |                 | ====================================== | *                                       |

| TAB          |              | clock           | functions                              |                                         |

| clo<br>da    |              |                 | clock<br>address                       | comments                                |

| sec          | onds         | lsb             | 00000                                  | seconds are automatically set to zero   |

| SOC          | on <b>ds</b> | msb             | <b>0</b> 001                           | when clk is written into                |

| min          | ites         | lsb             | 0010                                   |                                         |

| min          | ites         | msb             | 0011                                   |                                         |

| hou          | rs           | lsb             | 01 00                                  |                                         |

| hou          | rs           | msb             | <b>01</b> 01                           | bit 2 high=PM bit 3 high=24 hour format |

| wee]         | £            |                 | 0110                                   | range 0-6 (0=Sunday)                    |

| day          |              | lsb             | <b>01 1</b> 1                          |                                         |

| day          |              | msb             | 1000                                   | bit 2=leap year                         |

| mon          |              | 1 <b>s</b> b    | 1001                                   |                                         |

| mon          | th           | msb             | <b>101</b> 0                           |                                         |

| yea          |              | 1 <b>s</b> b    | 1011                                   |                                         |

| <b>yea</b> : | r<br>        | msb             | 1100                                   |                                         |

| ===:         |              | ======<br>. \$( | ====================================== |                                         |

5852

1

HOLD MIST BE LOW, READ, SELECT AF-7 MUST BE HIGH TO ALLOW INT. PULSES FIGURE 6

FIGURE 7

;

```

10 REM***************

20

CLOCK DEMO

REM***

****

30 REM** J. SWOFFORD 11-7-81 **

40 REM*********************

50 REMNAN SET MEMORY POINTERS *

60 A=@FF00:B=@FF01:C=@FF02:D=@FF03

70 REMNAN DATA USED FOR CONTROL

80 E=#90:H=#80:REM 8255 CONTROL BYTES

90 F=#20:G=#50:REM CLOCK CONTROL BYTES

100 \text{ DIM } T(13)

110 TS=" ":REM INITIALIZE TS

120 B$="N":REM INITIALIZE B$

130 REM

140 REM*** INPUT TIME/DATE ***

150 CLS

160 INPUT "CHANGE TIME/DATE--Y OR N" AS

170 IF A$="N" GOTO 450

180 IF A$<>"Y" GOTO 160

190 PRINT "INPUT TIME IN THIS FORMAT"

200 PRINT" H,H,M,M"

210 INPUT T(6), T(5), T(4), T(3)

220 T(2)=0:T(1)=0:REM SECONDS ARE SET TO ZERO BY CLK, ANYWAY

230 INPUT "24 HOUR FORMAT--Y/N" B$

240 IF B$="Y" T(6)=T(6)+#08:GOTO 270:REM BIT 3 INDICATES 24 HR FORMAT

250 INPUT "(A)M OR (P)M" C$

260 IF C$="P" T(6)=T(6)+#04:REM SET BIT 2 FOR PM

270 REM

280 REM

290 PRINT "INPUT DATE IN THIS FORMAT"

300 PRINT" W, M, M, D, D, Y, Y"

310 INPUT T(7),T(11),T(10),T(9),T(8),T(13),T(12)

320 T(7)=T(7)-1:REM RANGE FOR DAY-OF-WEEK IS 0-6 (SUNDAY-SATURDAY)

330 INPUT "LEAP YEAR--Y OR N" D$

340 IF D$="Y" T(9)=T(9)+#04:REM BIT 2 FOR LEAP YEAR

350 REM

360 INPUT "PRESS RETURN TO ENTER TIME/DATE" ES:REM ENTER TIME ON QUEUE

370 REM

```

```

380 POKE (D, H): REM SET UP 8255-PORTS A, B, C AS OUTPUTS

390 POKE (C.G.): REM PORT C (CLK CONTROL) CLOCK WRITE

400 REM

410 FOR I=1 TO 13

420 POKE (B, I-1) : REM SET CLK ADDRESS LINES

430 POKE (A.T(I)): REM SHOVE T(I) INTO CLOCK

山O NEXT I

450 POKE (D,E):REM MAKE PORT A AN INPUT, PORTS B & C ARE OUTPUTS

460 POKE (C,F):REM CLOCK READ

470 REM .

180 CLS

490 FOR I=1 TO 7

500 READ AS(I):REM USED FOR DAY-OF-WEEK

510 NEXT I

520 REM

530 PRINT CHR$(4);:REM CURSOR HOME

540 REM

550 FOR I=1 TO 13

560 POKE (B.I-1): REM CLOCK ADDRESS LINES

570 T(I) = PEEK(A): REM LOAD T(I)

580 NEXT I

590 TS=" AM":REM TS DEFAULT

600 IF INT(T(6)/#02)>0 T$=" PM":REM IF BIT 1 THEN PM

610 IF INT(T(6)/#08)>0 T$=" HRS":REM IF BIT 3 THEN 24 HR FORMAT

620 IF T(6)>2 IF T(6)<7 T(6)=T(6)-#04:REM STRIP OF BIT 2

630 IF T(6) > 7 T(6) = T(6) - \#08:REM STRIP OFF BIT 3