# **Freescale Semiconductor**

# **Application Note**

AN2743 Rev. 0.1, 08/2004

# Software Analysis on Genesi Pegasos II Using PMON and AltiVec

by Maurie Ommerman and Sergei Larin CPD Applications Freescale Semiconductor, Inc. Austin, TX

This application note is the sixth in a series describing the Genesi Pegasos II system, which contains a PowerPC<sup>TM</sup> microprocessor, and its various applications. This document describes software analysis using the PMON facility for using its PowerPC processor performance measurement registers. It also describes the general compiler tool set, GCC, and some AltiVec constructs.

# 1 Introduction

This application note describes some features of the AltiVec constructs and the PMON kernel interface and how to use one of the PowerPC performance monitor measuring facilities. The PMON facility is an application written by the Freescale application team and is described in this applications note. Even though this document is part of the series on Genesi Pegasos II systems, the PMON facility is available on any Linux System running on a PowerPC processor. The PMON facility is preloaded on the Genesi Pegasos II system, but may be download by request for any PowerPC Linux Platform. This paper assumes that the user will log in as guest with password guest, and all the examples discussed in this paper, with the exception of the hello world programs, are in the /home/guest/fae-training-04/library directory.

#### Contents

| 1. | Introduction                                   |     |  |  |

|----|------------------------------------------------|-----|--|--|

| 2. | Terminology                                    | . 2 |  |  |

| 3. | Introduction to Compiling on Linux with GCC    | . 2 |  |  |

| 4. | Defining and Using an AltiVec Vector           |     |  |  |

| 5. | Jsing the Performance Monitors for Performance |     |  |  |

|    | Gathering                                      | 23  |  |  |

| 6. | Using the PMON Facility                        | 34  |  |  |

| 7. | More Advanced Examples                         | 3   |  |  |

| 8. | Conclusion                                     | 59  |  |  |

| 9. | References                                     | 60  |  |  |

| n  | Revision History                               | 60  |  |  |

#### **Terminology**

# 2 Terminology

The following terms are used in this document.

Linux OS Linux operating system

PMON Performance monitor facility

GCC Gnu compiler collections and GNU utilities

Performance monitors MPC74xx processors contain registers that can be used to monitor system activity

AltiVec Processing engine on the MPC74xx processors that allows for SIMD functionality

SIMD Single instruction multiple data paths

POSIX Portable operating system interface (POSIX) standardization effort that was

formerly run by the POSIX standards committee

OEA PowerPC operating environment architecture that defines supervisor-level resources

typically required by an operating system

# 3 Introduction to Compiling on Linux with GCC

The GNU native tool chain is available on the Genesi Pegasos II system with both the Debian and Yellow Dog Linux distribution. This applications note will concentrate on the Debian Linux, however, it translates directly to the Yellow Dog Linux system and any other native PowerPC Linux distribution.

The GCC compiler executable command resides in the /usr/bin directory. The include files all reside in the /usr/include. All of the relative tool chain libraries reside in /usr/lib/gcc-lib. Version 3.3.3 GCC is used in this paper.

In order to compile any C application program, the simple gcc command can be used with all the default parameters.

All the examples, except the "hello world" programs discussed in this paper are in the /home/guest/fae-training-04/library directory.

# 3.1 The Objective and Tools for Achieving Software Development

The main objective is to familiarize ourselves with this new software development platform

# 3.1.1 Software Development Tools

The Pegasos software development system consists of the following items.

- MPC7447 + Discovery II

- Running Debian Linux

- · Standard GNU tool set

- GCC V3.3.3 for PPC, Supports AltiVec

- GNU utilities: gdb, objdump etc.

- Customized tool set for PPC monitoring

- PMON

- SimG4+

- Text editor of your choice:

— vi, vim, emacs, gnome text editor (gedit)

### 3.1.2 PMON – Performance Monitor

PMON is a kernel module, which allows non-root users to set the performance monitors to count specific CPU activities, such as cycles. See Section 5, "Using the Performance Monitors for Performance Gathering" for more details.

PMON is a limited application which can count only (32 bits) approximately 4 billion items. Similar tools are available from commercial software vendors.

A user can read these registers and develop statistical analysis, however, to determine which CPU activities to gather requires changing OEA/supervisor registers, thus by calling PMON, the user can request that the performance registers collect specific counts.

Using PMON is described in this applications note, however, the implementation of the PMON kernel module is described in the Freescale application note *PMON Module—An Example of Writing Kernel Module Code for Debian 2.6 on Genesi Pegasos II* (AN2744).

### 3.1.3 A Simple "Hello World" Program

Navigate to the directory /home/fae-training-04/library directory, create a local directory, navigate to it and type in this program.

```

cd fae-training-04/library

mkdir localperson

cd localperson

<editor of your choice> hello.c

#include <stdio.h>

main()

{

printf("Hello World!\n");

}

```

Compile and run this program, the executable elf file will be called a out by default. Since the local directory is not in the PATH, local executables must be preceded by the '.''/' two characters, thus the construct, ./a.out.

You can get general help information for GCC with the gcc -h command.

```

gcc hello.c

./a.out

Hello World!

```

# 3.2 A Simple AltiVec "hello World" Program

Using the same program above, compile it with the AltiVec flags, -maltivec -mabi=altivec.

```

gcc -maltivec -mabi=altivec hello.c

./a.out

Hello World!

```

There is not any difference. That is because there are no AltiVec constructs in this program.

# 3.3 An AltiVec "Hello AltiVec from vecChar" Program with Some AltiVec Char Constructs.

AltiVec intrinsics are built into the GCC compiler and will be explained as they are encountered in this program. See Section 9, "References" 9 and 10.

This program illustrates some AltiVec constructs. The numbers allow a description of the constructs, do not type in the numbers if you wish to try this program for yourself.

```

guest@debian:~/fae-training-04/library/maurie$ cat -n vecChar.c

#include <altivec.h>

#include <stdio.h>

3

void print char vector(vector unsigned char *this one);

void print int vector(vector int *this one);

5

vector unsigned char vec array[16];//only using vec array[1]

7

8

main()

9

10

int i;

vector unsigned char vec a;

11

unsigned char a1[16] __attribute__ ((aligned (16)))

= \{1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16\};

13

unsigned char a2[16] attribute ((aligned (16)))

14

= \{11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26\};

15

vec a = vec ld(0,a1);

16

17

vec array[1] = vec ld(0,a2);

printf("\nHello AltiVec from vecChar!\n");

18

printf("vec a = ");

19

20

print char vector(&vec a);

printf("\n");

21

```

```

printf("vec array[1] = ");

22

23

print char vector(&vec array[1]);

printf("\n");

24

25

26

void print char vector(vector unsigned char *this one)

27

28

29

%02x)",

30

((unsigned char*)this one)[0],

31

((unsigned char*)this one)[1],

32

((unsigned char*)this one)[2],

((unsigned char*)this one)[3],

33

34

((unsigned char*)this one)[4],

35

((unsigned char*)this one)[5],

((unsigned char*)this one)[6],

36

37

((unsigned char*)this one)[7],

38

((unsigned char*)this one)[8],

((unsigned char*)this one)[9],

39

40

((unsigned char*)this one)[10],

41

((unsigned char*)this one)[11],

42

((unsigned char*)this one)[12],

43

((unsigned char*)this one)[13],

44

((unsigned char*)this one)[14],

45

((unsigned char*)this one)[15]);

46

void print int vector(vector int *this one)

47

{

48

49

printf("(%08x,%08x,%08x,%08x)",

((int*)this one)[0],

50

51

((int*)this one)[1],

52

((int*)this one)[2],

```

```

53 ((int*)this_one)[3]);

54 }

```

The line numbers described here are the AltiVec constructs, the non-AltiVec C constructs will not be explained.

1 Include the GCC standard AltiVec header file. AltiVec intrinsics are built into the GCC compiler, this header will expand the constructs during compilation time.

4 and 5 are standard prototypes for these functions, which will be described later. However, the construct "vector", indicates that a vector variable is being used.

5 and 11 The construct vector invokes a vector array of 16 vector (i.e. 128 bit) elements in memory, which are aligned on a 16 byte boundary, i.e. an address that ends with 4 bits of zero, e.g. 0x10105660. This example only uses one of those vectors.

12, 13, 14, and 15. These are normal character arrays, however, the attribute signature forces 16 byte boundary alignment. We will discuss this more in the align example in Section 3.5, "An AltiVec "Alignment" Program Demonstrating Alignment Considerations."

16 and 17. Load a single vector vec\_a from the address of the character array a1, and load a single 16 byte element of a vector array from the address of a character array a2. This will be discussed in more detail in Section 4, "Defining and Using an AltiVec Vector." Suffice it to say that the 16 bytes starting at the address of the a1 character array, '1','2','3', etc will be written to the vector (either a true AltiVec register, or a memory location representing that AltiVec register) and the result is that the location of vec\_a will now contain the characters, '1','2','3', etc. The same logic applies to line 17, except that the 2nd element (i.e. address of vec\_array + 16 will contain the characters from the char array a2, '11','12','13', etc.

20 calls the function print char vector, which I will discuss in line 27.

27 through 46 is a function to print the contents of the vector in memory, one byte at a time for a total of 16 bytes. Since a vector is a 16 byte quantity, we can treat each byte independently, similar to a char array of 16 bytes. Since we are giving the address of the first byte of the vector to this function, we access each additional byte by an array increment, which is equivalent to adding 1 to the previous address.

47 though 54 is a similar function to print the contents of the vector in memory, one int (i.e. 4 bytes) at a time, for a total of 4 ints (16 bytes). This function will be used in the next example explained in, Section 3.4, "An AltiVec "Hello AltiVec from vecInt" Program with Some AltiVec Int Constructs."

We can compile and execute this example in several ways. I will describe three ways here.

1. Explicitly type in the command, as shown in the second example above in Section 3.2, "A Simple AltiVec "hello World" Program"

```

gcc -maltivec -mabi=altivec vecChar.c

./a.out

```

2. Create a shell script that is easier to remember and type. Use any editor to create a file, call it compile, and add the gcc command, and change the permission set to execute. The contents of the file can just be input from the cat command, the \$1 indicates the first parameter and \$2 indicates the second parameter. In this case we only have one parameter vecChar.c

```

cat >compile

gcc -maltivec -mabi=altivec $1 $2

^d (i.e. a control d on the keyboard)

```

```

chmod 777 compile

./compile vecChar.c

./a.out

```

3. Create a Makefile. Edit the file. The permissions do not need to be changed. However, type in a tab character, not 8 spaces in front of the make commands. So ensure that while typing the contents to Makefile, that indentations are made with the tab key.

```

cat >Makefile

make: vecChar.c

gcc -maltivec -mabi=altivec vecChar.c

clean:

rm -rf *.o a.out

^d (i.e. control d)

make clean

make

./a.out

In any case the output we see is this.

guest@debian:~/fae-training-04/library/maurie$ ./a.out

Hello AltiVec from vecChar!

vec a = (01,02,03,04,05,06,07,08,09,0a,0b,0c,0d,0e,0f,10)

vec array[1] = (0b,0c,0d,0e,0f,10,11,12,13,14,15,16,17,18,19,1a)

Note that the first array, vec_a contains the bytes loaded from char array a1, and

vec_array[1] contains the bytes loaded from char array a2.

```

# 3.4 An AltiVec "Hello AltiVec from vecInt" Program with Some AltiVec Int Constructs.

The only difference in this program is that we are loading from an integer array and we can demonstrate the offset capability of the  $\text{vec\_ld}(a,b)$  intrinsics.

The numbers allow a description of the constructs, do not type in the numbers if you wish to try this program for yourself.

```

3

4 void print char vector (vector unsigned char *this one);

5 void print int vector(vector int *this one);

6 vector unsigned char vec array[256];

7

vector int vec int;

8

main()

10

{

11

int i;

unsigned int a3[16] attribute ((aligned (16)))

12

13

=\{1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16\};

vec int = vec ld(0, (vector int *)a3);

14

printf("\nHello AltiVec from vecInt!\n");

15

16

printf("vec int offset by 0 = ");

print int vector(&vec int);

17

18

printf("\n");

print char vector((vector unsigned char *)&vec int);

19

20

printf("\n\n");

vec int = vec ld(16, (vector int *)a3);

21

printf("\nHello AltiVec from vecInt!\n");

22

printf("vec int offset by 16 = ");

print int vector(&vec int);

24

25

printf("\n\n");

26

vec int = vec ld(32, (vector int *)a3);

printf("\nHello AltiVec from vecInt!\n");

27

printf("vec int offset by 32 = ");

print_int_vector(&vec_int);

29

printf("\n\n");

30

31

vec int = vec ld(48, (vector int *)a3);

printf("\nHello AltiVec from vecInt!\n");

32

printf("vec int offset by 48 = ");

34 print int vector(&vec int);

```

```

printf("\n\n");

35

36

37

void print char vector(vector unsigned char *this one)

39

{

40

%02x)",

41

((unsigned char*)this one)[0],

42

((unsigned char*)this one)[1],

43

((unsigned char*)this one)[2],

44

((unsigned char*)this one)[3],

45

((unsigned char*)this one)[4],

((unsigned char*)this one)[5],

46

47

((unsigned char*)this one)[6],

48

((unsigned char*)this one)[7],

((unsigned char*)this one)[8],

49

50

((unsigned char*)this one)[9],

51

((unsigned char*)this one)[10],

((unsigned char*)this one)[11],

52

53

((unsigned char*)this one)[12],

54

((unsigned char*)this one)[13],

55

((unsigned char*)this one)[14],

56

((unsigned char*)this one)[15]);

57

void print int vector(vector int *this one)

59

60

printf("(%08x,%08x,%08x,%08x)",

61

((int*)this one)[0],

62

((int*)this one)[1],

((int*)this_one)[2],

63

((int*)this one)[3]);

64

65

```

The code is almost the same. The code in these line numbers are different.

7 defines a vector of type int, instead of type char, vec\_int. A vector of type char, indicates that the 128 bit vector is divided into 16 bytes of 8 bits each. A vector of type int, indicates that the 128 bit vector is divided into 4 ints of 32 bits each.

12 invokes an int array of 16 elements, each 32 bits long. The values, '1','2','3', etc are stored into these ints. In the previous example, then the char values, '1','2','3', were each 8 bits long. In this example, the ints '1','2','3', etc are 32 bits long. Hence the char values contained all 16 values, '1','2','3', etc in 128 bits. The int values contains only '1','2','3','4' in the first 128 bits, and '5','6'.'7','8' in the next 128 bits, etc.

14 stores the 4 int values, 128 bits of 0x00000001, 0x00000002, 0x00000003, 0x000000004, into the vec\_int.

21 stores the 4 int values, 128 bits of 0x0000005, 0x00000006, 0x00000007, 0x000000008 into the vec-int, because the a value in vec\_ld(a,b) indicates to offset 16 bytes. Now if  $0 \le a \le 16$ , we offset by 0, because a must be a multiple of 16. Thus in this case,  $16 \le a \le 32$ , so the offset is 16 bytes.

26 store the 4 int values, 128 bits of 0x00000009, etc in vec\_int.

31 stores the next int values, starting with 0x0000000d.

We can now use any of the three methods described in the previous example to compile and execute this program, changing vecChar.c to vecInt.c

```

guest@debian:~/fae-training-04/library/maurie$ ./compile vecInt.c

guest@debian:~/fae-training-04/library/maurie$ ./a.out

Hello AltiVec from vecInt!

vec_int offset by 0 = (00000001,00000002,00000003,00000004)

(00,00,00,01,00,00,00,02,00,00,00,03,00,00,00,00,04)

Hello AltiVec from vecInt!

vec_int offset by 16 = (00000005,00000006,00000007,00000008)

Hello AltiVec from vecInt!

vec_int offset by 32 = (00000009,0000000a,0000000b,0000000c)

Hello AltiVec from vecInt!

vec_int offset by 48 = (00000000d,0000000e,0000000f,00000010)

```

guest@debian:~/fae-training-04/library/maurie\$

# 3.5 An AltiVec "Alignment" Program Demonstrating Alignment Considerations

This example demonstrates the necessity of forcing alignment onto a 16 byte boundary for AltiVec vector operations. You can find this example in /home/guest/fae-training-04/library/align. It has been modified slightly to emphasize what we are demonstrating.

```

guest@debian:~/fae-training-04/library/align$ cat -n align.c

2

// Modified slightly from the example

// Alignment example

4

5

#include <altivec.h>

6

#include <stdio.h>

7

8

9

#define START TIMER

10

11

start time

= read 744x upmc1();\

start ins

12

= read 744x upmc2();

13

#define STOP TIMER \

14

15

asm volatile("eieio"); \

16

stop time

= read 744x upmc1(); \

= read 744x upmc2();

17

stop ins

18

19

#if TRACE

20

#define START TRACING

asm (".long 0x14000001");

asm (".long 0x14000002");

21

#define STOP TRACING

22

#define MAX SIZE

64

23

#define REPEAT

24

#else

```

```

25

#define START TRACING

26

#define STOP TRACING

27

#define MAX SIZE

256

#define REPEAT

10000

#endif

29

30

31

#define FORCE ALIGNMENT 0

* 1 forces alignment

32

* 0 forces non alignment

33

*/

34

35

int start pmon(int p1,int p2,int p3, int p4);

36

unsigned int read 744x upmc1(void);

37

38

unsigned int read 744x upmc2(void);

39

unsigned int read 744x upmc3(void);

unsigned int read 744x upmc4(void);

40

41

char outOfAlignment;

42

43

#if FORCE ALIGNMENT

char aa_array[MAX_SIZE] __attribute__ ((aligned (16)));

44

char ab_array[MAX_SIZE] __attribute__ ((aligned (16)));

46

#else

char aa array[MAX SIZE];

48

char ab array[MAX SIZE];

#endif

49

50

void print_int_vector(vector int *this_one) {

51

printf("{%08x,%08x,%08x,%08x}\n",

52

53

((int *)this one)[0],

54

((int *)this_one)[1],

55

((int *)this one)[2],

56

((int *)this one)[3]);

```

```

}

57

58

void print char vector(vector unsigned char *this one) {

59

60

%02x}\n",

61

((unsigned char*)this one)[0],

((unsigned char*)this_one)[1],

62

63

((unsigned char*)this one)[2],

64

((unsigned char*)this one)[3],

65

((unsigned char*)this one)[4],

66

((unsigned char*)this one)[5],

67

((unsigned char*)this one)[6],

((unsigned char*)this one)[7],

68

69

((unsigned char*)this one)[8],

70

((unsigned char*)this one)[9],

71

((unsigned char*)this one)[10],

72

((unsigned char*)this one)[11],

73

((unsigned char*)this one)[12],

((unsigned char*)this one)[13],

74

75

((unsigned char*)this one)[14],

76

((unsigned char*)this_one)[15]);

77

78

79

vector unsigned char vectorLoadUnaligned( vector unsigned char *v ) {

80

vector unsigned char permuteVector = vec lvsl( 0, (int*) v );

81

vector unsigned char low = vec ld( 0, v );

82

vector unsigned char high = vec ld( 16, v );

return vec perm( low, high, permuteVector );

83

84

85

86 void vectorStoreUnaligned( vector unsigned char v, vector unsigned char

*where) {

```

```

vector unsigned char permuteVector

= vec lvsr( 0, (int*) where );

87

88

vector unsigned char low,high,tmp,mask;

89

vector unsigned char ones

= vec splat u8( 0xff );

90

vector unsigned char zeroes

= vec splat u8(0);

91

low

= vec ld ( 0, where );

//Load the surrounding area

92

93

high = vec ld (16, where);

//Make a mask for which parts of the vectors to swap out

94

mask = vec perm( zeroes, ones, permuteVector );

95

= vec perm( tmp, tmp, permuteVector );

96

tmp

//Right rotate our

input data

97

= vec sel( tmp, low, mask );

// Insert masked data to

low

aligned vector

high = vec sel( high, v, mask );

98

99

100

vec st ( low, 0, where );

//Store aligned results

vec st ( high, 16, where );

101

102

103

int main(){

104

105

106

vector unsigned char vec a;

107

int j,i;

108

int s1,s2,s3;

109

unsigned int

start time, stop time;

110

unsigned int

start ins, stop ins;

111

112

for(i=0;i<MAX SIZE;i++) {</pre>

aa array[i] = i;

113

114

ab array[i] = i;

}

115

116

117

printf("\nAlignment Test\n");

```

```

118

119

start pmon(1, 2, 1, 2);

120

121

START TIMER;

122

for(i=0;i<REPEAT;i++)</pre>

123

vec a = vec ld(0, (vector unsigned char *) aa array);

124

STOP TIMER;

125

126

print char vector(&vec a);

127

printf("%d\tInstructions,\t%d Cycles\t%f IPC \n",

128

stop time-start time,

stop ins-start ins,

129

130

((double)(stop ins-start ins)/(double)(stop time-start time)));

131

132

133

START TIMER;

134

for(i=0;i<REPEAT;i++)</pre>

vec a = vectorLoadUnaligned( (vector unsigned char *)aa array);

135

136

STOP TIMER;

137

138

print_char_vector(&vec_a);

printf("%d\tInstructions,\t%d Cycles\t%f IPC\n",

139

140

stop time-start time,

stop ins-start ins,

141

142

((double)(stop ins-start ins)/(double)(stop time-start time)));

143

return 0;

144

145

```

This example serves double duty, it demonstrates the necessities of alignment, and is a simple example of using performance monitoring, which is in Section 3.6, "An AltiVec Program Demonstrating the Use of PMON for Obtaining Performance Statistics." Here the lines associated with demonstrating alignment are discussed.

quest@debian:~/fae-training-04/library/align\$

- 31 through 34 This defined variable can force 16 byte alignment or not, as shown starting in line 42.

- 42 through 49 can force 16 byte alignment due to the \_\_attribute\_\_ ((aligned(16))) intrinsic. When FORCE\_ALIGNMENT is 0 we skip the two lines with this attribute and use the two lines without the attribute. line 42, aligns to a byte, which will not be on a 16 byte address. FORCE\_ALIGNMENT is 1, we use the two lines with the attribute and skip the two lines without the attribute. Thus, this code will run with non 16 byte alignment and will not give us the correct answer. We will change this later and show the correct answer.

- 51 through 77 is the previously described print an int vector and a char vector.

- 79 through 84 is a function to load unaligned vectors correctly.

- 86 through 102 can store vectors correctly to unaligned memory.

- 112 though 115 fills these two aligned or unaligned, depending on FORCE\_ALIGNMENT, arrays with the numbers 0 through 15.

- 123 stores the 16 bytes starting at aa\_array into the vector vec\_a, but since it is unaligned we will get unexpected results.

- Since the macro REPEAT is set to 1, we only perform this loop once.

- 135 stores the 16 bytes starting at ab\_array into the vector vec\_a, but regardless of alignment of this array, the function vectorLoadUnaligned will aligned the data properly.

126 and 138 print the vectors.

Compile and execute this example using this Makefile.

CPU = 7457.

```

CPU 7457, has 6 PMCs

Monitoring events are PMC[0]:1

Monitoring events are PMC[1]:2

Monitoring events are PMC[2]:1

Monitoring events are PMC[3]:2

Monitoring events are PMC[4]:0

Monitoring events are PMC[5]:0

{fc,fd,fe,ff,00,01,02,03,04,05,06,07,08,09,0a,0b}

.

125266 Instructions, 110163 Cycles 0.879433 IPC

{00,01,02,03,04,05,06,07,08,09,0a,0b,0c,0d,0e,0f}

549870 Instructions, 480786 Cycles 0.874363 IPC

```

The ignored lines are PMON output and will be explained in the next example, in Section 3.6, "An AltiVec Program Demonstrating the Use of PMON for Obtaining Performance Statistics."

Looking at the two lines of output, we see that the first un aligned array starts with the value 'fc' and it should start with '00'. This is because the arrays aa\_array and ab\_array are not on a 16 byte boundary. The second unaligned array vector will print correctly, since the vectorLoadUnaligned function aligned the data before storing it in the vector.

By using the command, which will disassemble an elf executable file:

```

guest@debian:~/fae-training-04/library/align$ objdump -D test > j

```

Looking at the assembly saved in file, j, we see that aa\_array and ab\_array start at address,10011a04, and 10011b04, which are not on a 16 byte boundary, the last 4 bits of the address are not zero.

guest@debian:~/fae-training-04/library/align\$ ./test

```

Ignore the lines in italics, they will be described later.

Alignment Test

CPU = 7457,

CPU 7457, has 6 PMCs

Monitoring events are PMC[0]:1

Monitoring events are PMC[1]:2

Monitoring events are PMC[2]:1

Monitoring events are PMC[3]:2

Monitoring events are PMC[4]:0

Monitoring events are PMC[5]:0

{00,01,02,03,04,05,06,07,08,09,0a,0b,0c,0d,0e,0f}

125423 Instructions, 110162 Cycles 0.878324 IPC

{00,01,02,03,04,05,06,07,08,09,0a,0b,0c,0d,0e,0f}

549744 Instructions, 480785 Cycles 0.874562 IPC

quest@debian:~/fae-training-04/library/align$

We now see that both arrays are loaded correctly because the aa_array and the ab_array are on a 16 byte boundary.

10011a10 <ab array>:

. . .

10011b10 <aa_array>:

```

Thus, it is important to guarantee 16 byte alignment for all memory that will be associated with AltiVec operations.

# 3.5.1 More Information on AltiVec Data Alignment.

# 3.5.1.1 Obtaining Data Alignment for AltiVec with Compiler Constructs

It is strongly recommended that you align all data structures to 16 byte boundary if AltiVec is used Different compilers have different means of achieving it, but all of them have some method.

Here is a GCC example...

```

#include <altivec.h>

typedef union {

```

```

vector unsigned int vec;

int elements[4];

} LongVector __attribute__ ((aligned (16)));

unsigned char bitbuf8[16] __attribute__ ((aligned (16)))

={

#include "attribute_table.txt"

};

```

Where the file, attribute\_table.txt, is in the local directory and contains some constant data, such as "data".

In this example every variable of data type Long Vector will be aligned on quad-word boundaries and bitBuf8 is also aligned In this case bitBuf8 will be filled with the data in the \_table.txt file that is in this local directory. I.e., including attribute\_table.txt is another way of initializing an array.

Data Alignment is absolutely critical for mapping algorithms on AltiVec.

### 3.5.1.2 Obtaining Data Alignment for AltiVec with a Function

Loading Unaligned Data using the function, vectorLoadUnaligned, requires loading twice the data you really need, which is more inefficient then just aligning with the compiler \_\_attribute\_\_ ((aligned (16))).

```

vector unsigned char vectorLoadUnaligned( vector unsigned char *v ){

vector unsigned char permuteVector = vec_lvsl( 0, (int*) v );

vector unsigned char low = vec_ld( 0, v );

vector unsigned char high = vec_ld( 16, v );

return vec_perm( low, high, permuteVector );

}

```

# 3.5.2 Obtaining Data Alignment for Altivec with a More Efficient Function

This function is more efficient than the previous one, vectorLoadUnaligned, but is still less efficient then just aligning the data with the compiler \_\_attribute\_ ((aligned (16))).

```

void vectorStoreUnaligned( vector unsigned char v, vector unsigned char *where){

vector unsigned char permuteVector = vec_lvsr( 0, (int*) where );

vector unsigned char low,high,tmp,mask;

vector unsigned char ones = vec_splat_u8( 0xff );

vector unsigned char zeroes = vec_splat_u8( 0 );

low = vec_ld ( 0, where ); //Load the surrounding area

```

```

high = vec_ld ( 16, where );

//Make a mask for which parts of the vectors to swap out

mask = vec_perm( zeroes, ones, permuteVector );

tmp = vec_perm( tmp, tmp, permuteVector ); //Right rotate our input data

low = vec_sel( tmp, low, mask ); // Insert masked data to aligned vector

high = vec_sel( high, v, mask );

vec_st ( low, 0, where ); //Store aligned results

vec_st ( high, 16, where );

}

```

# 3.6 An AltiVec Program Demonstrating the Use of PMON for Obtaining Performance Statistics

The code for this example and that used in Section 3.5, "An AltiVec "Alignment" Program Demonstrating Alignment Considerations" is the same. What follows discusses the lines that are associated with using the pmon.c code facility.

A more complete discussion of using the PMON facility is discussed in Section 5, "Using the Performance Monitors for Performance Gathering."

10 through 17 defines a macro that can be used to turn on performance monitor gathering, the functions here are described in Section 5, "Using the Performance Monitors for Performance Gathering."

11,12 and 16, 17 call the functions read\_744x\_upmc, which is defined in pmon.c, described in Section 5.2.2, "PMON Interface File Code."

19 through 29 is used for the simg4plus facility

36 through 40 are prototypes.

119 through 121 call the PMON facility and tell it to monitor performance monitors 1 and 2, which count number of instructions and number of cycles, see Section 5.2.2, "PMON Interface File Code."

124 turns off the counters.

127 through 130 display the results, the number of instructions and cycles used to perform the code between the START\_TIMER and the STOP\_TIMER.

133 and 134 same as 119 through 121, except that it calls the function vecotrLoadUnaligned, which will execute more instruction then the previous 133 and 134 lines.

136 same as 124.

139 through 142 same as 127 through 130.

Lets look at the result of running this program again and explain the previously ignored output lines.

```

guest@debian:~/fae-training-04/library/align$ ./test > j

```

```

guest@debian:~/fae-training-04/library/align$ cat -n j

1

2

Alignment Test

3

CPU = 7457,

CPU 7457, has 6 PMCs

Monitoring events are PMC[0]:1

5

Monitoring events are PMC[1]:2

7

Monitoring events are PMC[2]:1

Monitoring events are PMC[3]:2

Monitoring events are PMC[4]:0

Monitoring events are PMC[5]:0

{00,01,02,03,04,05,06,07,08,09,0a,0b,0c,0d,0e,0f}

11

124813 Instructions,

110166 Cycles

0.882648 IPC

13

{00,01,02,03,04,05,06,07,08,09,0a,0b,0c,0d,0e,0f}

541317 Instructions,

480033 Cycles

0.886787 IPC

quest@debian:~/fae-training-04/library/align$

```

3 and 4 tells us what processor we are using and the number of performance monitors that are available.

5 though 8 indicate we are monitoring 1 and 2, twice, i.e. instructions and cycles. Note we are only using PMC1 and PMC2 in the START\_TIME and STOP\_TIME macros. We are ignoring the other 4 counters.

12 tells us that it took 124813 instructions and 110166 cycles to load vec\_a for one (REPEAT=1) time. By dividing the instructions by the cycles we get 0.882648 instructions per cycle.

14 tells us that we executed 4 times the number of instructions and cycles to perform vectorLoadUnalligned, than the previous code, which just loaded aligned data. Hence, it is obviously more efficient to use 16 byte aligned data then to execute a function to align non 16 byte aligned data for AltiVec operations.

As you can see this is a rudimentary look at our code, but we can become much more sophisticated in our measurements, which we will see in Section 7, "More Advanced Examples"

# 4 Defining and Using an AltiVec Vector

AltiVec vectors are a 128 bit quantity aligned on a 16 byte boundary. How do we manipulate it?

We load it with the vec\_ld(a,b) which loads 16 bytes into the vector, regardless of how we define it, char, short, int, float, double. So the receiver is a vector and the sender is an offset (offset by 16) and a memory address of 16 bytes.

Thus if we define an array of 16 bytes and a char vector as

```

char aa_array[MAX_SIZE] __attribute__ ((aligned (16)));

vector unsigned char vec_a;

```

#### **Defining and Using an AltiVec Vector**

Remember to align to 16 bytes. And then we fill it with numbers from 0 to 15.

Now starting at the address of aa\_array, i.e. &aa\_array, we have the 16 bytes set to the numbers from 0 to 15.

E.g. assume that aa\_array starts at address 10011b10 <aa\_array>, then the following values are stored in memory.

```

10011b10 0

10011b11 1

10011b12 2

...

10011b1f 15

```

Now when we use the intrinsic,

```

vec a = vec ld(0, (vector unsigned char *)aa array);

```

We are loading the values one byte at a time from 10011b10 through 10011b1f into the vector (register or memory location). thus the vector vec\_a now contains the char values from 0 to 1 in each of the bytes of the vector.

For int arrays, we have the same scenario, however, each int is 4 bytes. So for the example below, we are assigning 16 integer values of 4 bytes each, which is 64 bytes.

Lets just consider the first 4 integers, which is 16 bytes. Assume that int array a3 starts at 10011b10.

```

10011b10 0

10011b11 0

10011b12 0

10011b13 1

10011b14 0

10011b15 0

10011b16 0

10011b17 2

.....

```

10011b1d 0 10011b1e 0

10011b1f 4

Now after the vec\_ld instruction, the vector, vec\_int, has 16 bytes of data copied from the addresses 10011b10 through 10011b1f, which is 0,0,0,1,0,0,2,0,0,0,3,0,0,4. It still has 16 bytes, but only four integer values.

# 5 Using the Performance Monitors for Performance Gathering

# 5.1 General Description

All G4 parts contain special hardware to collect certain statistical information about the CPU state and events.

The MPC7447 contains six performance counters accessible as privileged SPRs: PMC1-PMC6, which can monitor up to 242 unique events.

Normally these are 32bit HW counters. If you count an event every cycle at a speed of 1GHz, you will overflow these counters in 4.3 seconds. It is possible to extend them to 64 bits, and/or write code to off load the results, but that is beyond the scope of this applications note.

The full list of monitor able statistics is given in MPC7450 RISC Microprocessor Family User's Manual.

Below is a short list.

Table 11-9. PMC1 Events—MMCR0[PMC1SEL] Select Encodings

| Number       | Event                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 (000_0000) | Nothing                 | Register counter holds current value                                                                                                                                                                                                                                                                                                                                                                                         |

| 1 (000_0001) | Processor cycles        | Counts every processor cycle                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2 (000_0010) | Instructions completed  | Counts all completed PowerPC and AltiVec instructions. Load/store multiple instructions (Imw, stmw) and load/store string instructions (IswI, Iswx, stswI, stswx) are only counted once. Does not include folded branches. The counter can increment by 0, 1, 2, or 3, depending on the number of completed instructions per cycle. Branch folding must be disabled (HID0[FOLD] = 0) in order to count all the instructions. |

| 3 (000_0011) | TBL bit transitions     | Counts transitions from 0 to 1 of TBL bits specified through MMCR0[TBSEL].  00 = uses the TBL[31] bit to count  01 = uses the TBL[23] bit to count  10 = uses the TBL[19] bit to count  11 = uses the TBL[15] bit to count                                                                                                                                                                                                   |

| 4 (000_0100) | Instructions dispatched | Counts dispatched instructions. The counter can increment by 0, 1, 2, or 3, depending on the number of dispatched instructions per cycle.                                                                                                                                                                                                                                                                                    |

In this applications note, we have seen the use of counting cycles and processor instructions, which can be seen from the above table are counter 1, processor cycles, and 2, instructions completed.

# 5.2 A Code Example Using the PMON Facility to Gather Performance Statistics

As described earlier, the align.c program is linked with the pmon.c program, which supplies the calls to the PMON facility, which is described in Section 6, "Using the PMON Facility."

Looking in the directory /home/guest/fae\_training-04/library/align we see two c files, align.c and pmon.c.

### 5.2.1 Makefile

The Makefile shown below, compiles align.c and pmon.c and links them together. Since the target line 1 is named test, then the gcc line 2 generates an elf executable named test, and that is the file we execute with the ./test command. There is a bug in this makefile, in the clean target line 4, we rm pmon\_test, however, the Makefile generates the file, test. So, the clean target does not work, change pmon\_test to test in the clean target and the clean target will work as expected, which is to remove the executable.

```

guest@debian:~/fae-training-04/library/align$

```

Change the following line in the makefile to remove the executable, text, with the clean target.

```

4 rm -rf *.o test

```

### 5.2.2 PMON Interface File Code

We have already discussed align.c

The program pmon.c described below is intended to be linked with any other program that wishes to set up performance monitors. It has a limit of 4 performance monitor registers that can be used at any one time. It can be easily changed to handle up to 6 registers by changing line 24 to accept 6 arguments, and changing lines 88 and 89 to use these two new arguments.

Another example of this interface program rewritten to be stand-alone and allow the user to input performance monitor register numbers via the keyboard is available in /root/ppctools/pmon/usr/pmon\_test.c.

The pmon.c program is listed here, taken from /home/guest/fae-training-04/library/align, with line numbers, which are obtained with the cat -n command. A description of all these lines follow.

The program pmon.c described below. It is intended to be linked with any other program that wishes to set up performance monitors. It has a limit of 4 performance monitor registers that can be used at any one time. It can be easily changed to handle up to 6 registers by changing line 24 to accept 6 arguments, and changing lines 88 and 89 to use these two new arguments.

Another example of this interface program rewritten to be stand-alone and allow the user to input performance monitor register numbers via the keyboard is available in /root/ppctools/pmon/usr/pmon\_test.c.

guest@debian:~/fae-training-04/library/align\$ cat -n pmon.c

```

#include <string.h>

9

#include <fcntl.h>

10

#include <unistd.h>

11

12

#include <sys/uio.h>

#define MAX PMC NUM (6)

13

static unsigned int pmc_sel[MAX_PMC_NUM];

14

15

unsigned int read 744x upmc1(void);

16

unsigned int read 744x upmc2(void);

17

18

unsigned int read 744x upmc3(void);

unsigned int read 744x upmc4(void);

20

unsigned int read 744x upmc5(void);

21

unsigned int read 744x upmc6(void);

22

void show upmcs(unsigned int* upmc);

23

24

int start pmon(int p1,int p2,int p3, int p4)

{

25

static unsigned int upmc begin[6], upmc end[6];

26

27

int i, fd, byteCount, len, n read;

28

unsigned int cycles;

char* textLine= NULL;

29

30

char item[32], delim[32], name[32];

31

int total pmc= 0;

32

FILE* p cpuinfo;

33

34

/* id CPU to decide how many PMCs we have on this machine */

p_cpuinfo = fopen("/proc/cpuinfo", "r");

35

36

if(p cpuinfo == NULL)

37

printf("ERR: unable to open cpuinfo \n");

38

39

return 0;

40

}

```

```

41

while((n read = getline(&textLine, &len, p cpuinfo))!=-1)

{

42

sscanf( textLine,"%s%s%s*", item, delim,name);

43

44

#ifdef DBG PMON

printf("INFO: getline %s\n", textLine);

45

46

printf("INFO:item=%s, delim=%s, name=%s\n", item, delim,name);

47

#endif

if(!memcmp(item, "cpu", 4))

48

49

printf("CPU = %s\n", name);

50

if(!memcmp(name, "744",3))

51

total pmc = 6;

52

else if(!memcmp(name, "745",3))

53

54

total pmc = 6;

else if(!memcmp(name, "741",3))

55

total pmc = 4;

56

else

57

{

58

59

printf("ERR: unsupported CPU %s\n", name);

60

return 0;

61

62

printf("CPU %s has %d PMCs\n", name, total pmc);

63

break:

}

64

65

66

if(textLine)

free(textLine);

67

68

fclose(p cpuinfo);

69

70

/* FIXME: let usr choose which event for which PMCs based on cpuinfo */

71

/* hardcode pmc event number for each pmc */

/*

72

```

```

printf("Please choose PMC events\n");

73

74

for(i=0;i<total pmc;i++)</pre>

75

{

printf("PMC[%d] event:\t", i);

76

77

if(getline(&textLine, &len, stdin)!=-1)

78

{

79

sscanf( textLine,"%d*", &pmc_sel[i]);

//

printf("%d\n", pmc sel[i]);

80

}

81

}

82

* /

83

84

pmc sel[0]

= p1;

pmc sel[1]

85

= p2;

86

pmc sel[2]

= p3;

87

pmc sel[3]

= p4;

pmc sel[4]

88

= 0;

pmc sel[5]

89

= 0;

90

for (i=0;i<total pmc;i++)</pre>

91

printf("Monitoring events are PMC[%d]:%d\n", i, pmc sel[i]);

92

fd = open("/dev/pmon", O RDWR);

93

if(fd == -1)

94

95

printf("ERR: unable to open device /dev/pmon\n");

96

97

return 0;

}

98

99

/* Write to pmc selection information to pmon device driver */

100

101

write(fd, pmc sel, sizeof(pmc sel));

102

for(i=0; i<=10;i++)

103

104

byteCount=read(fd, &cycles, sizeof(int) );

```

```

if(byteCount == -1)

105

{

106

107

printf("ERR: read failed\n");

108

return 0; // can read again

}

109

else if (byteCount < sizeof(cycles))</pre>

110

{

111

printf("ERR: not read enough data\n");

112

return 0; // can read again

113

114

115

//printf("PMC count = 0x%08X\n", cycles);

}

116

close(fd);

117

118

//show upmcs(upmc begin);

//printf("Running my code ..\n\n\n");

119

120

//asm volatile("eieio");

121

//show upmcs(upmc end);

122

return 0;

}

123

124

void show upmcs(unsigned int* upmc)

125

126

127

int i;

128

upmc[0] = read 744x upmc1();

upmc[1] = read 744x upmc2();

129

130

upmc[2] = read 744x upmc3();

upmc[3] = read_744x_upmc4();

131

132

upmc[4] = read 744x upmc5();

133

upmc[5] = read 744x upmc6();

for (i=0; i<6; i++)

134

135

printf("UPMC[%d]=0x%08x\n", i,upmc[i]);

136

```

```

137

138

139

unsigned int read 744x upmc1(void)

140

unsigned int val32;

141

asm volatile("mfspr %0, 937" : "=r"(val32));

142

143

return val32;

144

unsigned int read_744x_upmc2(void)

145

146

147

unsigned int val32;

asm volatile("mfspr %0, 938" : "=r"(val32));

148

149

return val32;

150

unsigned int read 744x upmc3 (void)

151

152

153

unsigned int val32;

asm volatile("mfspr %0, 941" : "=r"(val32));

154

155

return val32;

156

}

unsigned int read_744x_upmc4(void)

158

unsigned int val32;

159

asm volatile("mfspr %0, 942" : "=r"(val32));

160

return val32;

161

162

unsigned int read_744x_upmc5(void)

163

164

165

unsigned int val32;

asm volatile("mfspr %0, 929" : "=r"(val32));

166

167

return val32;

168 }

```

```

169 unsigned int read_744x_upmc6(void)

170 {

171    unsigned int val32;

172    asm volatile("mfspr %0, 930" : "=r"(val32));

173    return val32;

174 }

```

Description of the output lines follow:

- 1-5 comments

- 6 Don't know what defining \_GNU\_SOURCE does

- 7 through 12 include header files from the standard include directory at /usr/include, not from the kernel sources.

- 13 Define the maximum PMC counters

- 14 create an array of unsigned ints to store the values for each counter selection.

- 16 through 21 are prototypes for functions that read the non privileged counter registers UPMC1 through UPMC6.

- 22 is the prototype for the function that prints out the contents of the UPMC registers obtained from the functions prototypes in lines 16 through 21. It is not used in this program.

- 24 through 123 is the function that initializes the performance registers.

- 26 through 31 are declarations.

- 32 through 68 declares a FILE type which will be used to read the /proc/cpuinfo pseudo file, which specifies the CPU information on the running system. Try the shell command cat /proc/cpuinfo. It is this information that is being read here and checking for the existence of an MPC744x, MPC745x, or MPC741x processor, which are the only processors that have performance monitor registers.

- 70 through 83 is commented out, hence we do not give the caller the opportunity to choose which events to count, we just use the events passed to this function in four arguments, p1 through p4.

- 84 through 89, set the pmc\_sel to the arguments in preparation to monitor these counters.

- 90 and 91 print out the events that are going to be monitored, which corresponds to the lines 5 through 10 in the output listings below

- 93 through 99, opens the char device we have defined for this PMON facility, /dev/pmon using the standard IO call, open, which will invoke the pmon26.ko module function, pmon\_open. We check to see if it is available and if not print the error message we see in line 11 in the Section 5.2.3, "Results When /dev/pmon is Not Available."

- 101 Calls the pmon26.ko module function, pmon\_write, to write the selection bits to the privileged performance monitor selector registers, MMCR0 and MMCR1 and zero the counters.

- 102 through 117 calls the pmon26.ko function pmon\_read to read the contents of SPR937, UPMC1, which does not even require this module, and then we would print out the values in line 115, but it is commented out, so this is some debug code.

- 118 through 121 are commented out, so they are some debug lines.

- 122 through 123 returns from this function.

- 125 through 136 is the function to print out all the UMPC values, which are not privileged. This function is not called by align.c.

139 through 144 is a function to read the UPMC1, SPR938 register, which is not privileged. Thus we can just read this register as a normal user. It is used by align.c to read each of the counters and print out the lines 13 and 15 in the results shown below.

145 through 174 are the functions to get all the other counter values.

### 5.2.3 Results When /dev/pmon is Not Available

```

guest@debian:~/fae-training-04/library/align

Running the executable again, we get this result.

guest@debian:~/fae-training-04/library/align$ ./test > j

quest@debian:~/fae-training-04/library/align$ cat -n j

2

Alignment Test

CPU = 7457,

3

CPU 7457, has 6 PMCs

4

Monitoring events are PMC[0]:1

Monitoring events are PMC[1]:2

Monitoring events are PMC[2]:1

8

Monitoring events are PMC[3]:2

Monitoring events are PMC[4]:0

10

Monitoring events are PMC[5]:0

ERR: unable to open device /dev/pmon

{00,01,02,03,04,05,06,07,08,09,0a,0b,0c,0d,0e,0f}

13

Instructions,

0 Cycles

nan IPC

{00,01,02,03,04,05,06,07,08,09,0a,0b,0c,0d,0e,0f}

Instructions,

0 Cycles

15

nan IPC

```

In this case, line 13 and 15 gives 0 answers, because at line 11, the module gave an error, because pmon26.ko has not been started or /dev/pmon does not exist, or /dev/pmon has the wrong permissions, they must be 777 all permissions.

# 5.2.4 All These Conditions Must Be Met for the PMON Facility to Work.

- 1. The module, pmon26.ko must be built

- 2. The module, pmon26.ko must be installed, insmod pmon26.ko

- 3. /dev/pmon must be created, mknod /dev/pmon c <node number> 0

- 4. The permissions must be 777, chmod 777 /dev/pmon

The node number can be determined from the /proc/devices file. After the insmod pmon26.ko, look at the /dev/devices files, find the entry for PMON, and the node number will be displayed. Then enter the mknod command. It may be necessary to remove the current /dev/mknod entry if it does not correspond to the /proc/devices id number as listed.

```

for example.

root@debian:~/ppctools/pmon# insmod pmon26.ko

root@debian:~/ppctools/pmon# cat /proc/devices

Character devices:

1 mem

4 /dev/vc/0

... intervening lines removed

171 ieee1394

180 usb

254 pmon

Block devices:

1 ramdisk

3 ide0

8 sd

....remaining lines removed

root@debian:~/ppctools/pmon# mknod /dev/pmon c 254 0

root@debian:~/ppctools/pmon# chmod 777 /dev/pmon

root@debian:~/ppctools/pmon# ls -l /dev/pmon

1 root

254,

0 Jul 12 16:28 /dev/pmon

crwxrwxrwx

root

```

As can be seen from this example /proc/devices shows that the PMON device is assiged to id 254.

Further, for this example, align, to work, these conditions must also be met

- 1. align.c and pmon.c must be built

- 2. The resultant executable must be run.

# 5.2.5 Results When /dev/pmon is Available and pmon26.ko is Installed

Now that all these conditions have been met, lets run it again.

```

guest@debian:~/fae-training-04/library/align$ cat -n j

1

2 Alignment Test

```

#### **Using the PMON Facility**

```

3

CPU = 7457,

CPU 7457, has 6 PMCs

Monitoring events are PMC[0]:1

Monitoring events are PMC[1]:2

7

Monitoring events are PMC[2]:1

Monitoring events are PMC[3]:2

Monitoring events are PMC[4]:0

10

Monitoring events are PMC[5]:0

{00,01,02,03,04,05,06,07,08,09,0a,0b,0c,0d,0e,0f}

11

0.823988 IPC

12

134610 Instructions,

110917 Cycles

{00,01,02,03,04,05,06,07,08,09,0a,0b,0c,0d,0e,0f}

540918 Instructions,

480033 Cycles

0.887441 IPC

guest@debian:~/fae-training-04/library/align$

```

Description of the output lines follow.

Previous line 11 is not printed, so /dev/pmon was found correctly. Lines 12 and 14 have values.

2 printed by line 117 in align.c

3 and 4 printed by line 50 and 62 in pmon.c

5 through 10 printed by line 91 in pmon.c

11 printed by line 126 in align.c

12 printed by line 127 in align.c

13 printed by line 138 in align.c

14 printed by line 139 in align.c

# 6 Using the PMON Facility

Since, some of the performance registers are privileged registers, only the Linux root user can change those. Therefore, it is necessary for a normal user to call a kernel support function to set these registers. Linux does not supply such a facility, however, the PMON facility included in the pegasos II system does contain such a facility, which was written by the Freescale CPD applications team. This facility, called PMON, is supplied as a kernel module in the root directory at /root/ppctools/pmon.

Since PMON is not a normally supplied module, the user is required to start and stop it. In addition, PMON uses the char device /dev/pmon for it's operation. The user must therefore create this device.

Create the /dev/pmon device with the command:

```

mknod -c /dev/pmon c <pmon id> 0

```

To determine the PMON ID, see Section 5.2.4, "All These Conditions Must Be Met for the PMON Facility to Work."

Instantiate the PMON facility by navigating to the /root/ppctools/pmon directory and performing this command:

insmod pmon26.ko

To stop this facility, use this command:

rmmod pmon26.ko

Remember to change back into a regular user after starting PMON.

To reiterate, in order to use the PMON facility, these steps must be performed.

- 1. The module, pmon26.ko must be built

- 2. The module, pmon26.ko must be installed, insmod pmon26.ko

- 3. /dev/pmon must be created, mknod /dev/pmon c <node number> 0

- 4. The permissions must be 777, chmod 777 /dev/pmon

The node number can be determined from the /proc/devices file. After the insmod pmon26.ko, look at the /dev/devices files, find the entry for PMON, and the node number will be displayed. Then enter the mknod command. It may be necessary to remove the /dev/mknod entry if it does not correspond to the /proc/devices id number as listed.

Further, for this example, align, to work, these conditions must also be met

- 1. align.c and pmon.c must be built

- 2. The resultant executable must be run.

See Freescale application note *PMON Module—An Example of Writing Kernel Module Code for Debian 2.6 on Genesi Pegasos II* (AN2744) for more information.

A normal user cannot do any of the above, thus the user is required to change to the root user.

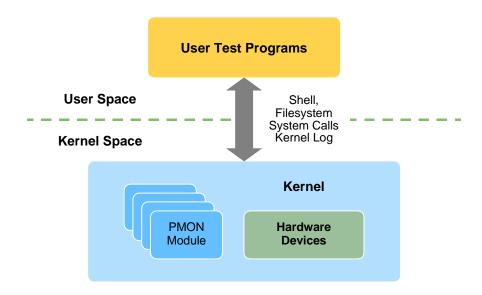

Figure 1. User Interaction with Kernel Module PMON

#### Using the PMON Facility

Figure 1 shows that the User program, which runs as a normal user, interfaces to the kernel via a call to the PMON module, which can in turn perform root activities for the user program.

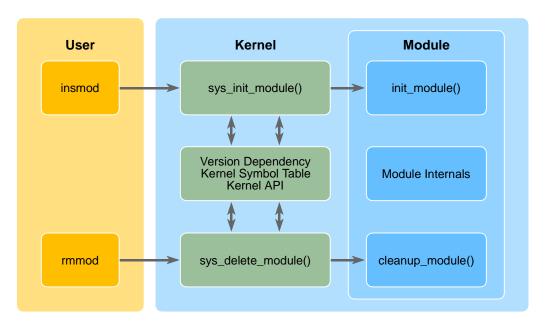

Figure 2. Instantiating the PMON Module

A user cannot instantiate a kernel module. Hence the module must be instantiated at boot time or by a root user with the insmod command. The insmod command, which means, instantiate module, will install the module in the kernel, then call the init\_module of PMON, which will initialize itself and wait for user calls to the PMON module. The rmmod command will de-instantiate it, that is, call the cleanup\_module to clean up any memory or other resources it is using and then remove it from the kernel module list.

Figure 2 shows the interaction of the user with the kernel, however, the user in this case must be the root user. The command insmod calls the kernel function sys\_inti\_module which adds the module to the kernels list and invokes the initialization function of the module. Modules are version dependent since once instantiated, they are part of the kernel and must have access to all the kernel symbols. The module internals are invoked by normal users making function calls to the device that is owned by the module. Finally, only the root user can remove a module with the rmmod command, which will call the modules clean up code and remove the module from the kernel list.

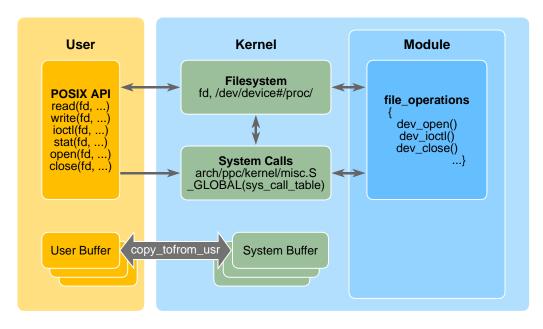

Figure 3. User Interaction to the Module

Figure 3 shows that once running, normal users can interface to the module with the standard POSIX API, using file commands, like open and read and write. This is because PMON instantiates itself as a char device and will get a device entry in /dev of /dev/pmon.

In summary, a root user must start PMON with the insmod pmon26.ko command. A shell script is available for this action, /root/ppcttools/pmon/install.sh If the system is rebooted, then PMON must be reinstalled.

# 7 More Advanced Examples

There are several more examples in the /guest/fae-training-04/library directory. We are going to discuss just one of them in detail, the Dot Product. Several other examples will be overviewed, the reader is encouraged to look at the other code. The mathlib directory has some AltiVec functions that can be used in your own programs.

# 7.1 Dot Product Example

In this example, the simg4plus facility is invoked with the -DTRACE=1 parameter as shown in the ,build.sh file. In order to use the PMON facility instead of simg4plus, use the Makefile, which does not define the TRACE macro.

True data dependency as well as some classical code optimization can often prevent vectorization. But in some cases the data dependency can be prevented and a gain in efficiency and speed can be obtained by using the AltiVec engine for vectorization. This example shows how to vectorize a classical data dependency problem.

Consider the dot product of two Matrixes, X and Y vectors of size N.

$$Dot_Product(x[n], y[n]) = \sum_{i=1}^{n} x[i] * y[i]$$

The classic code solution:

```

float\ DotProduct(\ float\ *X,\ float\ *Y,\ int\ length\ ) \{ int\ temp=0; //\ \underline{N\ Iterations} for(\ int\ i=0;\ i< length;\ i++)\ \{ temp=X[i]*Y[i]+temp; \} return\ temp; \}

```

This same function could be written in vector form, where each vector can contain 4 integers, thus v1 and v2 are size of N/4, thus we use four times fewer iterations. There is some set up time, but the dot product algorithm is operating four times faster.

However, there is data dependency, only 1 madd can complete every 4 cycles.

```

float\ VectorDotProduct(\ vector\ float\ *v1,\ vector\ float\ *v2,\ int\ length\ )\{\\ vector\ float\ temp = (vector\ int)\ vec\_splat\_u32(0);\\ float\ result;\\ //\ Loop\ over\ the\ length\ of\ the\ vectors\ multiplying\ like\ terms\ and\ summing\\ //\ Number\ of\ iterations\ is\ N/4\\ for(\ int\ i=0;\ i< length;\ i++)\\ temp = vec\_madd(\ v1[i],\ v2[i],\ temp);\\ //\ true\ data\ dependency\\ //\ only\ 1\ madd\ every\ 4\ cycles\\ temp = vec\_add(\ temp,\ vec\_sld(\ temp,\ temp,\ 4\ ));\\ temp = vec\_add(\ temp,\ vec\_sld(\ temp,\ temp,\ 8\ ));\\ vec\_ste(\ temp,\ 0,\ \&result\ );\\ return\ result;\\ \}

```

We can eliminate this dependency by performing 4 madd in a row, filling the pipeline, by doing 4 vectors at a time, incrementing our for loop by 4 each time, instead of once.

```

int FastVectorDotProduct( vector float *v1, vector float *v2, int length ){

vector float temp = (vector float) vec_splat_s8(0);

vector float temp2 = temp; vector float temp3 = temp;

vector float temp4 = temp; vector float result;

for( int i = 0; i < length; i += 4){

//Loop over the length of the vectors.

temp = vec madd(v1[i], v2[i], temp);

//this time doing 4 vectors in parallel

temp2 = vec_madd( v1[i+1], v2[i+1], temp2);

// to fill the pipeline

temp3 = vec\_madd(v1[i+2], v2[i+2], temp3);

temp4 = vec_madd(v1[i+3], v2[i+3], temp4);

//Sum our temp vectors

= vec_add( temp, temp2 );

temp

temp3

= vec_add( temp3, temp4 );

temp

= vec_add( temp, temp3 );

//Add across the vector

= vec_add( temp, vec_sld( temp, temp, 4 ));

temp

= vec_add(temp, vec_sld( temp, temp, 8 ));

//Copy the result to the stack so we can return it via the IPU

vec_ste( temp, 0, &result );

return result;

```

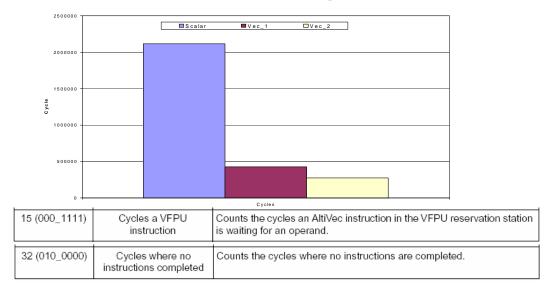

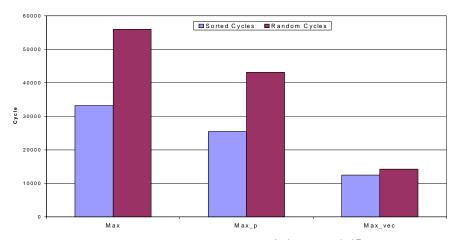

This code example, dot\_product, procedes using these three methods, the classic method, the one madd at a time, and 4 madd at a time for one fourth the iterations. PMON is used to calculate the number of cycles and instructions used in each method. As we will see, the vector method is significantly better than the classic method, and the 4 madd at a time is again significantly better, i.e. more efficient and faster than either of the others.

### 7.1.1 Makefile

Line 2 in the Makefile below will compile and link our dot product example using the AltiVec intrinsics including our pmon.c interface to PMON, generating an elf executable whose name is test, because that is the name of the make target it line 1. Line 3 is the clean target, which invokes line 4 to remove all the objects and the elf file, test.

```

guest@debian:~/fae-training-04/library/dot_product$ cat -n Makefile

1 test: dot_product.c pmon.c

2 gcc -maltivec -mabi=altivec -O3 pmon.c dot product.c -o $@

```

## 7.1.2 Code Listing and Explanation

The listing is the same as in the example in the Genesi Pegasos II directory and file, /home/guest/fae-training-04/library/dot\_product/dot\_product.c with the exception, that the printf statements at lines 177, 195, 197, 215, 217, and 235 have been changed to make the printing easier to discuss, and lines 184, 204, and 224 have been corrected to avoid the warning errors in the original.

```

/guest@debian:~/fae-training-04/library/dot product$ cat -n dot product.c

1

// Sergei Larin

// Bitreversal example

//

4

5

#include <altivec.h>

#include <stdio.h>

8

9

#define START TIMER

10

11

start time

= read 744x upmc1();\

12

start ins

= read 744x upmc2();

13

14

#define STOP TIMER \

15

asm volatile("eieio"); \

= read 744x upmc1(); \

16

stop time

17

stop ins

= read 744x \text{ upmc2()};

18

#if TRACE

19

asm (".long 0x14000001");

20

#define START TRACING

21

#define STOP TRACING

asm (".long 0x14000002");

64

#define MAX SIZE

22

```

```

#define REPEAT

23

1

24

#else

25

#define START TRACING

26

#define STOP TRACING

#define MAX SIZE

27

4*1024

#define REPEAT

100

28

29

#endif

30

31

int start pmon(int p1, int p2, int p3, int p4);

unsigned int read 744x upmc1(void);

32

33

unsigned int read 744x upmc2(void);

34

unsigned int read 744x upmc3(void);

unsigned int read 744x upmc4(void);

35

36

attribute ((aligned (16))) ;

37

float aa[MAX SIZE]

__attribute__ ((aligned (16))) ;

38

float ab[MAX SIZE]

39

void print int vector(vector int *this one) {

40

printf("{%08x,%08x,%08x,%08x}\n",

41

((int *)this one)[0],

42

((int *)this_one)[1],

43

44

((int *)this one)[2],

45

((int *)this one)[3]);

46

47

float dot_product(float *a,float *b, int num_elements) {

49

50

int i;

float tmp

51

= 0;

52

53

for(i=0;i<num elements;i++) {</pre>

54

tmp += a[i] * b[i];

```

```

55

56

return tmp;

57

58

float dot p vec 1(vector float *va, vector float *vb, int num elements) {

59

60

61

vector float temp = (vector float) vec splat u32(0);

62

int i;

float result;

63

64

65

for(i = 0; i < num elements/4; i++)

66

temp = vec madd( va[i], vb[i], temp);

67

temp = vec add( temp, vec_sld( temp, temp, 4 ));  // Vector Shift Left

68

Double

temp = vec add( temp, vec sld( temp, temp, 8 ));

69

70

vec ste( temp, 0, &result );

71

72

return result;

73

}

74

float dot p vec 2(vector float *v1, vector float *v2, int num elements) {

75

76

77

vector float temp = (vector float) vec splat s8(0);

vector float temp2 = temp;

78

vector float temp3 = temp;

79

vector float temp4 = temp;

80

81

vector float *v1p

= v1;

82

vector float *v2p

= v2;

vector float t1,t2,t3,t4,t5,t6,t7,t8;

83

float result;

84

85

int i

= 0;

```

```

86

for (i = 0; i < num elements/4; i += 4)

87

//Loop over

the length of the vectors,

temp = vec madd(v1[i], v2[i], temp);

//this time doing 4

vectors in parallel

89

temp2 = vec madd(v1[i+1], v2[i+1], temp2); // to fill the pipeline

90

temp3 = vec madd( v1[i+2], v2[i+2], temp3);

temp4 = vec madd( v1[i+3], v2[i+3], temp4);

91

92

93

for(i = 0; i < num elements/16; i++){

//Loop over the

length of the vectors,

temp = vec madd( *(v1p++), *(v2p++), temp);

//this time doing

4 vectors in parallel

temp2 = vec madd( *(v1p++), *(v2p++), temp2); // to fill the pipeline

96

97

temp3 = vec madd( *(v1p++), *(v2p++), temp3);

temp4 = vec madd( *(v1p++), *(v2p++), temp4);

98

99

100

* /

101 /*

for(i = 0; i < num elements/16; i++){

102

//Loop over the

length of the vectors,

= vec ld(0,v1p);

103

t1

= vec ld(0, v2p);

104

t2

105

t3

= vec ld(1, v1p);

106

= vec ld(1, v2p);

t4

= vec madd(t1, t2, temp); //this time doing 4 vectors

107

temp

in parallel

108

t5

= vec ld(2, v1p);

109

t6

= vec ld(2, v2p);

temp2 = vec madd( t3, t4, temp2);  // to fill the pipeline

110

t7

= vec ld(3, v1p);

111

= vec ld(3, v2p);

112

t8

temp3 = vec madd( t5, t6, temp3);

113

```

```

114

v1p++;

115

v2p++;

116

temp4 = vec madd(t7, t8, temp4);

117

* /

118

119

120

do{

temp = vec madd( v1[i], v2[i], temp);

121

//this time doing 4

vectors in parallel

temp2 = vec madd(v1[i+1], v2[i+1], temp2); // to fill the pipeline

122

123

temp3 = vec madd( v1[i+2], v2[i+2], temp3);

124

temp4 = vec madd( v1[i+3], v2[i+3], temp4);

i+=4;

125

}while(i<num elements/4);</pre>

126

127

* /

/*

128

while(1){

129

130

if(i>= num elements/4) break;

temp = vec madd(v1[i], v2[i], temp);

//this time doing 4

131

vectors in parallel

132

temp2 = vec madd(v1[i+1], v2[i+1], temp2); // to fill the pipeline

133

temp3 = vec madd( v1[i+2], v2[i+2], temp3);

134

temp4 = vec madd( v1[i+3], v2[i+3], temp4);

135

i+=4;

136

*/

137

138

//Sum our temp vectors

139

temp

= vec add( temp, temp2 );

= vec add( temp3, temp4 );

140

temp3

141

temp = vec add( temp, temp3 );

//Add across the vector

142

temp = vec add( temp, vec sld( temp, temp, 4 ));

143

144

temp

= vec add(temp, vec sld( temp, temp, 8 ));

```

```

//Copy the result to the stack so we can return it via the IPU

145

vec_ste( temp, 0, &result );

146

147

return result;

148

149

150

int main(){

151

int j,i;

152

int s1, s2, s3;

153

unsigned int

start time, stop time;

154

unsigned int start ins, stop ins;

155

unsigned int

start pc3, stop pc3, start pc4, stop pc4;

156

= 0.0;

float

157

result

158

for(i=0;i<MAX SIZE/2;i+=2) {</pre>

159

aa[i] = (float)i;

160

aa[i+1] = (float)-i;

161

162

ab[i] = (float)i;

ab[i+1] = (float)i;

163

164

}

165

#if TRACE

166

167

START TRACING;

//result = dot product(&aa,&ab,MAX SIZE);

168

//result = dot p vec 1(&aa,&ab,MAX SIZE);

169

170

result = dot p vec 2(&aa,&ab,MAX SIZE);

171

172

STOP TRACING;

173

return (int)result;

#else

174

175

start pmon(1,2,1,2); // 1,2,1,15, 56,23

176

```

```

printf("Scalar function timing:\n \t");

177

178

179

start pc4

= read 744x upmc4();

180

start pc3

= read 744x \text{ upmc3()};

START TIMER;

181

182

183

for(i=0;i<REPEAT;i++)</pre>

result = dot product(aa,ab,MAX SIZE);

184

185

STOP TIMER;

186

187

stop pc3

= read 744x upmc3();

= read 744x upmc4();

188

stop pc4

printf("(%d), t ins (%d), t(%d) t(%d) n",

189

190

stop time-start time,

191

stop ins-start ins,

stop pc3-start pc3,

192

stop pc4-start pc4);

193

194

Output: (%f) n=====n", result);

195

printf("

196

printf("Parallel version: \n \t");

197

198

199

start pc4

= read 744x upmc4();

= read 744x upmc3();

200

start pc3

START TIMER;

201

202

203

for(i=0;i<REPEAT;i++)</pre>

result = dot p vec 1((vector float *) aa, (vector float *) ab,MAX_SIZE);

204

205

206

STOP_TIMER;

207

stop pc3

= read 744x \text{ upmc3()};

208

stop pc4

= read 744x upmc4();

```

```

printf("(%d), t ins (%d), t(%d) t(%d) n",

209

210

stop time-start time,

211

stop ins-start ins,

212

stop pc3-start pc3,

stop pc4-start pc4);

213

214

215

printf("

Output: (%f) \n===== \n'', result);

216

printf("Parallel version 2:

217

\n \t");

218

219

start pc4

= read 744x upmc4();

start pc3

220

= read 744x upmc3();

START TIMER;

221

222

223

for(i=0;i<REPEAT;i++)</pre>

224

result = dot p vec 2((vector float *) aa, (vector float *) ab, MAX SIZE);

225

STOP TIMER;

226

227

stop pc3

= read 744x upmc3();

= read 744x upmc4();

228

stop pc4

printf("(%d), t ins (%d), t(%d) t(%d) n",

229

230

stop time-start time,

231

stop ins-start ins,

stop pc3-start pc3,

232

stop pc4-start pc4);

233

234

printf("

Output: (%f) = = = n", result);

235

236

237

#endif

return 0;

238

239

quest@debian:~/fae-training-04/library/dot product$

```

Line explanation:

1 though 5 are comments

6 is the header to define the AltiVec intrinsics.

10 through 17 define macros for getting the start and stop time used in calculating the number of units used in a timing session, in this case cycles and instructions.

19 through 24 are used for simg4plus, which are not used here, since TRACE is not defined by the Makefile.

25 through 28 are used for PMON, however, 25 and 26 just shut off the simg4plus tracing facility.

31 through 35 are prototypes for the PMON functions, which are defined in pmon.c in this directory.

37 and 38 declare our float vectors, which are aligned to 16 bytes, a requirement for vector, AltiVec, operations.

40 through 46 is a function to print vectors, it is not used.

48 through 57 is the scalar function to perform a dot product.

59 through 73 is a vectorization of the dot product algorithm, which can only perform 1 madd per 4 cycles, because of data dependency.

75 though 148 is the same vectorization, however, it can perform 4 madd per 4 cycles, i.e. 1 madd per cycle, by filling the pipe with four madd in a row. 93 through 137 are all commented out and therefore ignored. They do not participate in this algorithm.

150 through 157 is the beginning of the main function and the declaration of variables.

159 through 164 initialize the two arrays to values that will product a result of 0 in the dot product, no matter how many elements are in the array, as long as there are an even number of elements. This is described in Section 7.1.3, "Results and Explanation."