# User's Manual

## MSC Q7-A50M Qseven Module

Rev. 0.6 June 27th, 2013

#### **Preface**

#### Copyright Notice

Copyright © 2008 MSC Vertriebs GmbH. All rights reserved.

Copying of this document, and giving it to others and the use or communication of the contents thereof. are forbidden without express authority. Offenders are liable to the payment of damages.

All rights are reserved in the event of the grant of a patent or the registration of a utility model or design.

### Important Information

This documentation is intended for qualified audience only. The product described herein is not an end user product. It was developed and manufactured for further processing by trained personnel.

#### Disclaimer

Although this document has been generated with the utmost care no warranty or liability for correctness or suitability for any particular purpose is implied. The information in this document is provided "as is" and is subject to change without notice.

#### **EMC Rules**

This unit has to be installed in a shielded housing. If not installed in a properly shielded enclosure, and used in accordance with the instruction manual, this product may cause radio interference in which case the user may be required to take adequate measures at his or her own expense.

#### **Trademarks**

All used product names, logos or trademarks are property of their respective owners.

#### Certification

MSC Vertriebs GmbH is certified according to DIN EN ISO 9001:2000 standards.

## Life-Cycle-Management

MSC products are developed and manufactured according to high quality standards. Our life-cyclemanagement assures long term availability through permanent product maintenance. Technically necessary changes and improvements are introduced if applicable. A product- change-notification and end-of-life management process assures early information of our customers.

### **Product Support**

MSC engineers and technicians are committed to provide support to our customers whenever needed. Before contacting Technical Support of MSC Vertriebs GmbH, please consult the respective pages on our web site at www.mscembedded.com for the latest documentation, drivers and software downloads. If the information provided there does not solve your problem, please contact our Technical Support:

> Phone: +49 - 8165 906 - 200 Fax: +49 - 8165 906 - 201

Email: support@mscembedded.com

## Content

| 1 |        | ral Information                      |     |

|---|--------|--------------------------------------|-----|

|   | 1.1    | Revision History                     |     |

|   | 1.2    | Reference Documents                  |     |

|   | 1.3    | Introduction                         |     |

| 2 |        | nical Description                    |     |

|   | 2.1    | Key Features                         |     |

|   | 2.2    | Block Diagram                        |     |

|   | 2.3    | Power Supply                         |     |

|   | 2.4    | Power Dissipation                    |     |

|   | 2.5    | Mechanical Dimensions                |     |

|   | 2.6    | Thermal Specifications               |     |

|   | 2.7    | Signal description                   |     |

|   | 2.7.1  | High Definition Audio                |     |

|   | 2.7.2  | Ethernet                             |     |

|   | 2.7.3  | Serial ATA                           |     |

|   | 2.7.4  | PCI Express Lanes                    | 13  |

|   | 2.7.5  | USB                                  | 13  |

|   | 2.7.6  | LVDS Flat Panel                      | 14  |

|   | 2.7.7  | LPC Bus                              | 15  |

|   | 2.7.8  | HDMI                                 | 15  |

|   | 2.7.9  | DisplayPort                          | 15  |

|   | 2.7.10 | Express card support                 | 16  |

|   | 2.7.11 | Miscellaneous                        | 16  |

|   | 2.7.12 | Power and System Management          | 17  |

|   | 2.7.13 | Power and GND                        | 17  |

|   | 2.8    | Connectors                           | 19  |

|   | 2.8.1  | Module connector                     | 19  |

|   | 2.8.2  | USB Port assignment                  |     |

| 3 |        | m Resources                          |     |

| • | 3.1    | SMB Address Map                      |     |

|   | 3.2    | PCI Express Lanes                    | 23  |

|   | 3.3    | USB                                  | 23  |

|   | 3.4    | PCI Interrupt Routing Table          | 24  |

|   | 3.5    | IRQ Lines in Legacy IRQ Mode         |     |

|   | 3.6    | IRQ Lines in APIC Mode               |     |

| 4 | BIOS   |                                      |     |

|   | 4.2.2  | The Main Menu                        |     |

|   | 4.2.3  | The Advanced Menu                    | 30  |

|   | 4.3    | Chipset                              |     |

|   | 4.3.2  | Boot                                 |     |

|   | 4.3.3  | Security                             |     |

|   | 4.3.4  | The Save & Exit Menu                 |     |

|   | 4.4    | BIOS and Firmware Update             |     |

|   | 4.8    | EAPI                                 |     |

|   |        | ·· · · · · · · · · · · · · · · · · · | ◡ . |

#### 1 General Information

## 1.1 Revision History

| Rev. | Date                           | Description                                                  |

|------|--------------------------------|--------------------------------------------------------------|

| 0.1  | Dec 23 <sup>th</sup> 2012      | Initial version                                              |

| 0.2  | April 11 <sup>th</sup> , 2012  | Corrections and Enhancements                                 |

| 0.3  | October 5 <sup>th</sup> , 2012 | Added Bios chapter according to Rev. X1.00c ALPHA; LVDS path |

| 0.4  | March 1 <sup>st</sup> , 2013   | Updated Bios chapter                                         |

| 0.5  | April 8 <sup>th</sup> , 2013   | Updated Bios chapter                                         |

| 0.6  | June 27 <sup>th</sup> , 2013   | Enhancements                                                 |

|      |                                |                                                              |

|      |                                |                                                              |

|      |                                |                                                              |

|      |                                |                                                              |

|      |                                |                                                              |

## 1.2 Reference Documents

[1] Qseven Specification

Revision 1.11

Last update: Nov. 26<sup>th</sup> 2008

[2] PCI Local Bus Specification Rev. 2.1

PCI21.PDF

Last update: June 1<sup>st</sup>, 1995 http://www.pcisig.com

[3] Serial ATA Specification Serial ATA 1.0 gold.pdf

Last update: August 29<sup>th</sup>, 2002 Rev.1.0

http://www.sata-io.org/

[4] IEEE Std. 802.3-2002 802.3-2002.pdf http://www.ieee.org

[5] Universal Bus Specification

usb\_20.pdf

Last update: April 27<sup>th</sup>, 2000

http://www.usb.org

#### 1.3 Introduction

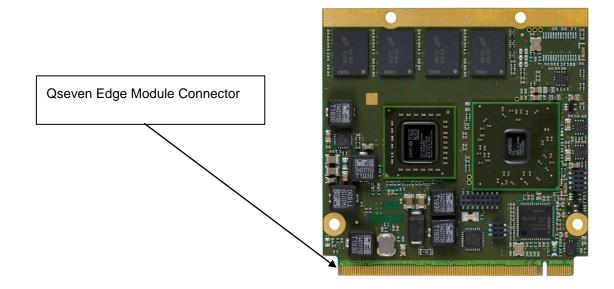

Qseven modules are compact, highly integrated Single Board Computers.

Typically a Qseven module consists of CPU, chipset, memory, Ethernet controller,

BIOS flash, SATA- and USB controller. Interface controllers (e.g. for PCMCIA) or connectors (e.g. RJ45) are implemented on a base board on to which the Qseven module can be mounted.

In addition to the power supply PCIe, SATA, USB, LPC etc. interfaces are present on the connector.

Thanks to the standardized mechanics and interfaces the system can be scaled arbitrarily. Despite the modular concept the system design is very flat and compact.

Qseven modules require a base board to build a working system. For evaluation purposes MSC recommends the official Qseven Reference Platform MSC Q7-MB-RP.

This documentation describes the Qseven module Revison 1.

## 2 Technical Description

### 2.1 Key Features

#### Core:

#### **Processors:**

AMD G-SeriesT40E dual core (1.0 GHz) on MSC-Q7-A50M-002 and -004

AMD G-SeriesT40R single core (1.0 GHz) on MSC-Q7-A50M-001

AMD G-SeriesT16R single core (615 MHz) on MSC-Q7-A50M-003

#### **Chipset:**

AMD A50M

#### Memory:

DDR3 533MHz, soldered down.

2GB

#### **PCI Express Interface:**

Four PCIe x1 channel

#### Video:

Built-in AMD Radeon™ HD 6250 18-24 Bit dual or single channel LVDS via ANX3110 DP-to-LVDS Converter 1x DVI / DisplayPort™

#### **Ethernet:**

10/100/1000 Base -T (Intel 82574, Device ID 8086/10D3)

#### Audio:

**High-Definition Audio**

#### **USB**:

8x USB Ports 2.0

**I2C Bus**

**SMBus**

**LPC Bus**

#### **SATA**

2x SATA ports

#### **FLASHDrive**

Optional FerriSSD SATA FLASH

#### **BIOS**:

AMI BIOS with optional TPM support. Supports SPI ROM on base board

#### **EEPROM:**

An SMBus EEPROM is implemented for backup of the CMOS data including user BIOS setup.

#### **Realtime Clock:**

An RTC (integrated in A50M chipset) is available.

#### Watchdog

- Watchdog with programmable time-out

- Watchdog enabled via BIOS or application programs

#### **System Monitoring:**

Monitored values:

- Temperatures (CPU and Board)

- CPU and system fan speed

#### Fan support:

Optional connector on module to run active cooling fan or system fan. Speed control via monitoring device

#### TPM:

Optional Infineon TPM 1.2

#### **SuperIO support:**

The Bios supports the following Super IO chips: Winbond 82627 HF SMSC SCH3114-NU

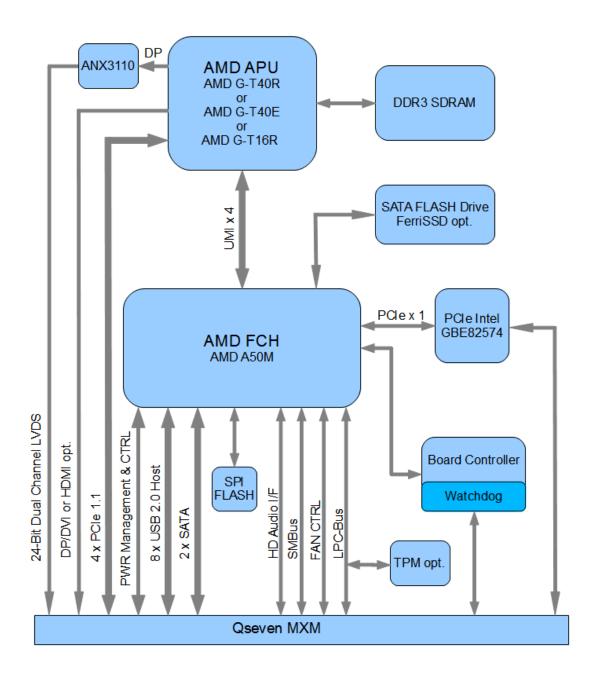

## 2.2 Block Diagram

Fig. 1: MSC Q7-A50M-001 (T40R) / MSC Q7-A50M-002 (T40E) / MSC Q7-A50M-003 (T16R) Block Diagram

## 2.3 Power Supply

- +5V primary power supply input

- +5V standby

- 3.3V RTC power supply

BIOS SETUP data is stored in a non volatile backup memory device (EEPROM), therefore configuration data will be retained during RTC-Power loss (except for time and date information)

| Voltage              | Input range     | Current          |

|----------------------|-----------------|------------------|

| +5V                  | +4.75V - 5.25V  | See next table   |

| +5V Standby          | +4.75V - 5.25 V |                  |

| +3V RTC power supply | +2.0V - 3.3V    | ca. 4uA/ max 6uA |

## 2.4 Power Dissipation

CPU: T40E 1.0 GHz RAM: 2GByte

Test software: Performance Test

|         |    | Idle       | Calculation | Memory     | Graphic            | Graphic      |

|---------|----|------------|-------------|------------|--------------------|--------------|

|         |    | Find prime |             |            | 2D Graphic complex | 3D Graphic   |

|         |    | Idle       | Number      | Block read | test               | complex test |

| DOS     |    | 7.2 W      |             |            |                    |              |

| Windows | S0 | 6.0 W      | 8.4 W       | 8.4 W      | 8.6 W              | 9.7 W        |

|         | S3 | 0.3 W      |             |            |                    |              |

CPU: T40R 1 GHz RAM: 2GByte

|         |    | Idle   | Calculation | Memory     | Graphic            | Graphic      |

|---------|----|--------|-------------|------------|--------------------|--------------|

|         |    |        | Find prime  |            | 2D Graphic complex | 3D Graphic   |

|         |    | Idle   | number      | Block read | test               | complex test |

| DOS     |    | 8.75 W |             |            |                    |              |

| Windows | S0 | 6.0 W  | 9.0 W       | 10.0 W     | 9.25 W             | 9.75 W       |

|         | S3 | 0.5 W  |             |            |                    |              |

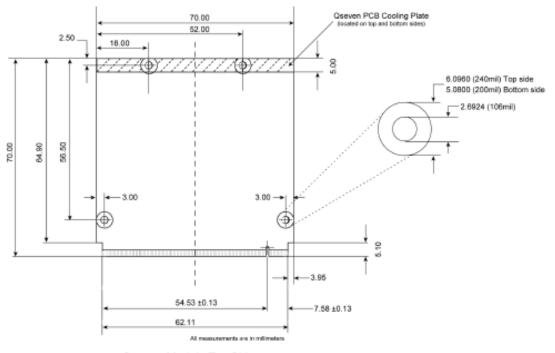

## 2.5 Mechanical Dimensions

Qseven Module Top Side

The height is dependent on the MXM connector used on the baseboard.

Fig. 2: MSC Q7-A50M Mechanical Dimensions

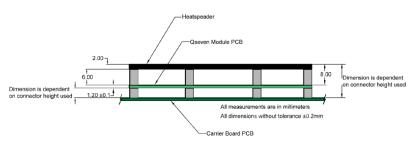

#### 2.6 Thermal Specifications

The cooling solution for a Qseven module is based on a heatspreader concept.

A heatspreader is a metal plate (typically aluminium) mounted on top of the module. The connection between this plate and the module components is typically made using thermal interface materials such as phase change foils, gap pads and copper or aluminium blocks. A very good thermal conductivity is required in order to transfer the heat from the cpu and the chipset to the heatspreader plate.

The heatspreader used by the MSC module is thermally attached using phase change materials and small aluminium blocks filling the gap between cpu and chipset dies and heatspreader plate.

The heatspreader is not a heatsink! It is a defined thermal interface for the system designer with fixed mechanical dimensions, so it should be possible to use different module types without problem.

The main goal for the thermal design of a system is that each device on the module is operated within its specified thermal limits. The max temperature of CPU and chipset are 90°C, so there may be system implementations where the heatspreader temperature could be higher.

In any case it has to be validated that there are no thermal spec violations of any assembled part over the system temperature range even under worst case conditions.

## 2.7 Signal description

In the following tables signals are marked with the power rail associated with the pin, and, for input and I/O pins, with the input voltage tolerance. The pin power rail and the pin input voltage tolerance **may** be different.

An additional label, "Suspend", indicates that the pin is active during suspend states (S3, S4, S5). If suspend modes are used, then care must be taken to avoid loading signals that are active during suspend to avoid excessive suspend mode current draw.

### 2.7.1 High Definition Audio

| Signal   | Pin    | Signal | Power | Power     | PU/PD | Description                                                      | Source / |

|----------|--------|--------|-------|-----------|-------|------------------------------------------------------------------|----------|

|          | Type   | Level  | Rail  | Tolerance |       |                                                                  | Target   |

| HDA_RST# | Output | CMOS   | Core  | 3.3V      |       | Reset output to CODEC, active low.                               | A50M     |

| HDA_SYNC | Output | CMOS   | Core  | 3.3V      |       | 48kHz fixed-rate, sample-synchronization signal to the CODEC(s). | A50M     |

| HDA_CLK  | Output | CMOS   | Core  | 3.3V      |       | 24.00 MHz serial data clock                                      | A50M     |

| HDA_SDO  | Output | CMOS   | Core  | 3.3V      |       | Serial TDM data output to the CODEC.                             | A50M     |

| HDA_SDI  | Input  | CMOS   | Core  | 3.3V      |       | Serial TDM data inputs from up to 3 CODECs.                      | A50M     |

#### 2.7.2 Ethernet

| Signal                           | Pin              | Signal | Power        | Power               | PU/PD | Description                                                                                                                                                                                              | Source / |

|----------------------------------|------------------|--------|--------------|---------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                  | Type             | Level  | Rail         | Tolerance           |       |                                                                                                                                                                                                          | Target   |

| GBE0_MDI[0:3]+<br>GBE0_MDI[0:3]- | Input/<br>Output | Analog | 3.3V<br>Sus. |                     |       | Gigabit Ethernet Controller 0: Media Dependent Interface Differential Pairs 0,1,2,3. The MDI can operate in 1000, 100 and 10 Mbit / sec modes.  MDI[0]+/- B1_DA+/- MDI[1]+/- B1_DB+/- MDI[2]+/- B1_DC+/- | 82574    |

| GBE0_ACT#                        | Open<br>Drain    | CMOS   | 3.3V<br>Sus. | 3.3V                |       | MDI[3]+/- B1_DD+/- Gigabit Ethernet Controller 0 activity indicator, active low.                                                                                                                         | 82574    |

| GBE0_LINK100#                    | Open<br>Drain    | CMOS   | 3.3V<br>Sus. | 3.3V                |       | Gigabit Ethernet Controller 0 100 Mbit / sec link indicator, active low.                                                                                                                                 | 82574    |

| GBE0_LINK1000#                   | Open<br>Drain    | CMOS   | 3.3V<br>Sus. | 3.3V                |       | Gigabit Ethernet Controller 0 1000 Mbit / sec link indicator, active low.                                                                                                                                | 82574    |

| GBE0_CTREF                       | REF              |        |              | GND min<br>3.3V max |       | 82574 (1000MBit): 1,9V                                                                                                                                                                                   | LDO      |

### 2.7.3 Serial ATA

| Signal    | Pin  | Signal | Power | Remark     | PU/PD | Description                                      | Source / |

|-----------|------|--------|-------|------------|-------|--------------------------------------------------|----------|

|           | Type | Level  | Rail  |            |       |                                                  | Target   |

| SATA0_TX+ | 0    | SATA   | 3.3V  | AC coupled |       | Serial ATA Channel 0 transmit differential pair. | A50M     |

| SATA0_TX- |      |        |       | on module  |       | ·                                                |          |

| SATA0_RX+ | I    | SATA   | 3.3V  | AC coupled |       | Serial ATA Channel 0 receive differential pair.  | A50M     |

| SATA0_RX- |      |        |       | on module  |       | ·                                                |          |

| SATA1_TX+ | 0    | SATA   | 3.3V  | AC coupled |       | Serial ATA Channel 1 transmit differential pair. | A50M     |

| SATA1_TX- |      |        |       | on module  |       | ·                                                |          |

| SATA1_RX+ | I    | SATA   | 3.3V  | AC coupled |       | Serial ATA Channel 1 receive differential pair.  | A50M     |

| SATA1_RX- |      |        |       | on module  |       |                                                  |          |

| SATA_ACT# | 0    | CMOS   | 3.3V  | 3.3V       |       | SATA activity indicator, active low.             | A50M     |

## 2.7.4 PCI Express Lanes

| Signal                         | Pin<br>Type | Signal<br>Level |              | Remark /<br>Power Tol. | Description                                    | Source /<br>Target |

|--------------------------------|-------------|-----------------|--------------|------------------------|------------------------------------------------|--------------------|

| PCIE_TX[0:3]+<br>PCIE_TX[0:3]- | 0           | PCle            | Core         | AC coupled on module   | PCI Express Differential Transmit Pairs 0 to 3 | APU                |

| PCIE_RX[0:3]+<br>PCIE_RX[0:3]- | _           | PCIe            | Core         | AC coupled off module  | PCI Express Differential Receive Pairs 0 to 3  | APU                |

| PCIE_WAKE#                     | I           | CMOS            | 3.3V<br>Sus. |                        | PCI Express wake event signal                  |                    |

| PCIE_RST#                      | 0           | CMOS            | 3.3V         |                        | Reset signal for external devices              |                    |

## 2.7.5 USB

| Signal    | Pin<br>Type | Signal<br>Level | Power<br>Rail | Remark / Power Tol. | PU/PD |                                              | Source /<br>Target |

|-----------|-------------|-----------------|---------------|---------------------|-------|----------------------------------------------|--------------------|

| USB[0:7]+ | I/O         | USB             | 3.3V Sus.     | 3.3V                |       | USB differential pairs, channels 0 through 7 | A50M               |

| USB[0:7]- |             |                 |               |                     |       |                                              |                    |

| Signal      | Pin<br>Type | Signal<br>Level | Power<br>Rail | Remark /<br>Power Tol. | PU/PD  | Description                                                                                                                                                                                                                                     | Source /<br>Target |

|-------------|-------------|-----------------|---------------|------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| USB_0_1_OC# | I           | CMOS            | 3.3V Sus.     | 3.3V                   | 10k PU | USB over-current sense, USB channels 0 and 1. A pull-up for this line is present on the module. An open drain driver from a USB current monitor on the Carrier Board may drive this line low.  Do not pull this line high on the Carrier Board. | A50M               |

| USB_2_3_OC# | I           | CMOS            | 3.3V Sus.     | 3.3V                   | 10k PU | USB over-current sense, USB channels 2 and 3. A pull-up for this line is present on the module. An open drain driver from a USB current monitor on the Carrier Board may drive this line low.  Do not pull this line high on the Carrier Board. | A50M               |

| USB_4_5_OC# | I           | CMOS            | 3.3V Sus.     | 3.3V                   | 10k PU | USB over-current sense, USB channels 4 and 5. A pull-up for this line is present on the module. An open drain driver from a USB current monitor on the Carrier Board may drive this line low.  Do not pull this line high on the Carrier Board. | A50M               |

| USB_6_7_OC# | I           | CMOS            | 3.3V Sus.     | 3.3V                   | 10k PU | USB over-current sense, USB channels 6 and 7. A pull-up for this line is present on the module. An open drain driver from a USB current monitor on the Carrier Board may drive this line low.  Do not pull this line high on the Carrier Board. | A50M               |

### 2.7.6 LVDS Flat Panel

| Signal                       | Pin<br>Type | Signal<br>Level | Power<br>Rail | Remark /<br>Power Tol. | PU/PD  | Description                             | Source /<br>Target |

|------------------------------|-------------|-----------------|---------------|------------------------|--------|-----------------------------------------|--------------------|

| LVDS_A[0:3]+<br>LVDS_A[0:3]- | 0           | LVDS            | Core          |                        |        | LVDS Channel A differential pairs       | ANX3110            |

| LVDS_A_CK+<br>LVDS_A_CK-     | 0           | LVDS            | Core          |                        |        | LVDS Channel A differential clock       | ANX3110            |

| LVDS_B[0:3]+<br>LVDS_B[0:3]- | 0           | LVDS            | Core          |                        |        | LVDS Channel B differential pairs       | ANX3110            |

| LVDS_B_CK+<br>LVDS_B_CK-     | 0           | LVDS            | Core          |                        |        | LVDS Channel B differential clock       | ANX3110            |

| LVDS_PPEN                    | 0           | CMOS            | Core          | 3.3V                   |        | LVDS panel power enable                 | ANX3110            |

| LVDS_BLEN                    | 0           | CMOS            | Core          | 3.3V                   |        | LVDS panel backlight enable             | ANX3110            |

| LVDS_BKLT_CTRL               | 0           | CMOS            | Core          | 3.3V                   |        | LVDS panel backlight brightness control | ANX3110            |

| LVDS_DID_CLK                 | I/O OD      | CMOS            | 3.3V          | 3.3V                   | 10k PU | I2C clock output for LVDS display use   | ANX3110            |

| LVDS_DID_DAT                 | I/O OD      | CMOS            | 3.3V          | 3.3V                   | 10k PU | I2C data line for LVDS display use      | ANX3110            |

## 2.7.7 LPC Bus

| Signal      | Pin  | Signal | Power | Remark /   | PU/PD  | Description                                   | Source / |

|-------------|------|--------|-------|------------|--------|-----------------------------------------------|----------|

|             | Type | Level  | Rail  | Power Tol. |        |                                               | Target   |

| LPC_AD[0:3] | I/O  | CMOS   | Core  | 3.3V       |        | LPC multiplexed address, command and data bus | A50M     |

| LPC_FRAME#  | 0    | CMOS   | Core  | 3.3V       |        | LPC frame indicates the start of an LPC cycle | A50M     |

| LPC_LDRQ#   | I    | CMOS   | Core  | 3.3V       | 10k PU | LPC serial DMA request, not supported         | A50M     |

| SERIRQ      | I/O  | CMOS   | Core  | 3.3V       | 10k PU | LPC serial interrupt                          | A50M     |

| LPC_CLK     | 0    | CMOS   | 3.3V  | 3.3V       |        | LPC clock output - 33MHz nominal              | A50M     |

### 2.7.8 HDMI

| Signal                     | Pin<br>Type | Signal<br>Level | Power<br>Rail | Remark /<br>Power Tol. | PU/PD     | Description                                                                                        | Source /<br>Target |

|----------------------------|-------------|-----------------|---------------|------------------------|-----------|----------------------------------------------------------------------------------------------------|--------------------|

| TMDS_LANE2+<br>TMDS_LANE2- | 0           | TMDS            |               | AC coupled on module   |           | Serial Digital Video output differential pair shared with signal SDVO_RED+ / SDVO_RED-             | APU                |

| TMDS_LANE1+<br>TMDS_LANE1- | 0           | TMDS            |               | AC coupled on module   |           | Serial Digital Video output differential pair shared with signal SDVO_GREEN+ / SDVO_GREEN-         | APU                |

| TMDS_LANE0+<br>TMDS_LANE0- | 0           | TMDS            |               | AC coupled on module   |           | Serial Digital Video output differential pair shared with signal SDVO_BLUE+ / SDVO_BLUE-           | APU                |

| TMDS_CLK+<br>TMDS_CLK-     | 0           | TMDS            |               | AC coupled on module   |           | Serial Digital Video clock output differential pair.<br>shared with signal SDVO_BCLK+ / SDVO_BCLK- | APU                |

| HDMI_CTRL_CLK              | I/O         | CMOS            | Core          | 3.3V                   | 4K7<br>PU | HDMI I2C clock line - to set up HDMI peripherals. shared with signal SDVO_CTRL_CLK                 | APU                |

| HDMI_CTRL_DAT              | I/O         | CMOS            | Core          | 3.3V                   | 4K7<br>PU | HDMI I2C data line - to set up HDMI peripherals. shared with signal SDVO_CTRL_DAT                  | APU                |

## 2.7.9 DisplayPort

| Signal    | Pin  | Signal | Power | Remark /   | PU/PD | Description                                  | Source / |

|-----------|------|--------|-------|------------|-------|----------------------------------------------|----------|

|           | Type | Level  | Rail  | Power Tol. |       |                                              | Target   |

| DP_LANE0+ | 0    | PCle   |       | AC coupled |       | DisplayPort output differential pair         | APU      |

| DP_LANE0- |      |        |       | on module  |       | shared with signal SDVO_RED+ / SDVO_RED-     |          |

| DP_LANE1+ | 0    | PCIe   |       | AC coupled |       | DisplayPort output differential pair         | APU      |

| DP_LANE1- |      |        |       | on module  |       | shared with signal SDVO_GREEN+ / SDVO_GREEN- |          |

| Signal    | Pin  | Signal | Power |            | Description                                                   | Source / |

|-----------|------|--------|-------|------------|---------------------------------------------------------------|----------|

|           | Type | Level  | Rail  | Power Tol. |                                                               | Target   |

| DP_LANE2+ | 0    | PCIe   |       | AC coupled | DisplayPort output differential pair                          | APU      |

| DP_LANE2- |      |        |       | on module  | shared with signal SDVO_BLUE+ / SDVO_BLUE-                    |          |

| DP_LANE3+ | 0    | PCle   |       | AC coupled | DisplayPort output differential pair.                         | APU      |

| DP_LANE3- |      |        |       | on module  | shared with signal SDVO_BCLK+ / SDVO_BCLK-                    |          |

| DP_AUX+   | I/O  | PCle   |       | AC coupled | Auxiliary channel differential pair                           | APU      |

| DP_AUX-   |      |        |       | off module | shared with signal SDVO_FLDSTALL+ / SDVO_FLDSTALL-            |          |

| DP_HPD#   | 1    | CMOS   | Core  | 3.3V       | Hot plug detection signal that serves as an interrupt request | APU      |

## 2.7.10 Express card support

| Signal       | Pin  | Signal | Power | Remark /   | PU/PD | Description                      | Source / |

|--------------|------|--------|-------|------------|-------|----------------------------------|----------|

|              | Type | Level  | Rail  | Power Tol. |       |                                  | Target   |

| EXCD0_CPPE#  | I    | 3.3V   | Core  | 3.3V       |       | Express card slot 0 card request | A50M     |

| EXCD0_PERST# | 0    | 3.3V   | Core  | 3.3V       |       | Express card slot 0 reset        | A50M     |

| EXCD1_CPPE#  | I    | 3.3V   | Core  | 3.3V       |       | Express card slot 1 card request | A50M     |

| EXCD1_PERST# | 0    | 3.3V   | Core  | 3.3V       |       | Express card slot 1 reset        | A50M     |

### 2.7.11 Miscellaneous

| Signal        | Pin  | Signal | Power | Remark /   | PU/PD  | U/PD Description                                                |                 |

|---------------|------|--------|-------|------------|--------|-----------------------------------------------------------------|-----------------|

|               | Type | Level  | Rail  | Power Tol. |        |                                                                 | Target          |

| I2C_CLK       | I/O  | CMOS   | 3.3V  | 3.3V       |        | General purpose I2C port clock output                           |                 |

| I2C_DAT       | I/O  | CMOS   | 3.3V  | 3.3V       |        | General purpose I2C port data I/O line                          |                 |

| SPKR          | 0    | CMOS   | 3.3V  | 3.3V       |        | Output for audio enunciator - the "speaker" in PC-AT systems    |                 |

| BIOS_DISABLE# | I    | CMOS   | 3.3V  | 3.3V       | 10k PU | Module BIOS disable input. Pull low to disable module BIOS.     |                 |

| WDOUT         | 0    | CMOS   | 3.3V  | 3.3V       |        | Output indicating that a watchdog time-out event has occurred.  | Microcontroller |

| WDTRIG#       | I    | CMOS   | 3.3V  | 3.3V       |        | Watchdog trigger input. This signal restarts the watchdog timer | Microcontroller |

| FAN_TACHOIN   | I    | CMOS   | 3.3V  |            |        | Tachometer input                                                | A50M            |

| FAN_PWMOUT    | 0    | CMOS   | 3.3V  |            |        | Pulse width modulation output for fan speed control A50M        |                 |

## 2.7.12 Power and System Management

| Signal     | Pin<br>Type | Signal<br>Level       | Power<br>Rail | Remark /<br>Power Tol. | PU/PD   | Description                                                                                                                                           | Source /<br>Target |

|------------|-------------|-----------------------|---------------|------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| PWRBTN#    | I           | CMOS                  | 3.3V Sus.     | 3.3V                   | 10k PU  | Power button to bring system into a power state. (Negative pulse)                                                                                     |                    |

| RSTBTN#    | I           | CMOS                  | 3.3V Sus.     | 3.3V                   | 10k PU  | Reset button input. Active low input. System is held in hardware reset while this input is low, and comes out of reset upon release. (Negative pulse) |                    |

| SUS_STAT#  | 0           | CMOS                  | 3.3V Sus.     | 3.3V                   |         | Indicates low power suspend operation                                                                                                                 |                    |

| SUS_S3#    | 0           | CMOS                  | 3.3V Sus.     | 3.3V                   |         | Indicates system is in Suspend to RAM state. Active low output.                                                                                       |                    |

| SUS_S5#    | 0           | CMOS                  | 3.3V Sus.     | 3.3V                   |         | Indicates system is in Soft Off state. Also known as "PS_ON" and can be used to control an ATX power supply.                                          |                    |

| WAKE#      | I           | CMOS                  | 3.3V Sus.     | 3.3V                   | 10k PU  | External system wake up signal.                                                                                                                       |                    |

| BATLOW#    | I           | CMOS                  | 3.3V Sus.     | 3.3V                   | 10k PU  | Indicates that external battery is low.                                                                                                               |                    |

| THRM#      | I           | CMOS                  | 3.3V          | 3.3V                   | 8k2 PU  | Input from off-module temp sensor indicating an over-temp situation.                                                                                  |                    |

| THERMTRIP# | 0           | CMOS                  | 3.3V          | 3.3V                   |         | Active low output indicating that the CPU has entered thermal shutdown.                                                                               |                    |

| SMB_CLK    | I/O         | CMOS                  |               | 3.3V                   | 10k PU  | System management clock line                                                                                                                          |                    |

| SMB_DAT    | I/O         | CMOS                  |               | 3.3V                   | 10k PU  | System management data line                                                                                                                           |                    |

| SMB_Alert  | I/O         | CMOS                  |               | 3.3V                   |         | System management bus alert input                                                                                                                     |                    |

| SLP_BTN#   | I           | CMOS                  |               | 3.3V Sus               | 10k PU  | Sleep button. Low active signal to bring the system in sleep state. (Negative pulse)                                                                  |                    |

| LID_BTN#   | I           | CMOS                  |               | 3.3V Sus               | 10k PU  | LID button. Low active signal detect a LID switch to bring the system in sleep state or wake up again.(Low signal)                                    |                    |

| BATLOW#    | I           | CMOS                  |               | 3.3V Sus               |         | Battery low input indicates a external battery low state                                                                                              |                    |

| PWGIN      | I           | Low<0.6V<br>High>0.8V |               | 5V                     | 120k PD | Indicates that the external power supply is ready                                                                                                     |                    |

### 2.7.13 Power and GND

| Signal     | Pin<br>Type | Signal<br>Level | Power<br>Rail | Remark /<br>Power Tol. | Description                                                                                                                                                                                                      | Source /<br>Target          |

|------------|-------------|-----------------|---------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| VCC_5V     | Power       |                 | 5V (±5%)      |                        | Primary power input: +5V (±5%)                                                                                                                                                                                   | Voltage<br>Regulators       |

| VCC_5V_SBY | Power       |                 | 5V (±5%)      |                        | Standby power input: +5.0V (±5%) All available VCC_5V_SBY pins on the connector(s) shall be used. Used for microcontroller and standby and suspend functions. If no standby power is available connect to VCC_5V | VCC3.3V<br>SUS<br>regulator |

| VCC_RTC    | Power       |                 |               |                        | Real-time clock circuit-power input: +3.0V (+2.0V to +3.3V)                                                                                                                                                      |                             |

| Signal | Pin<br>Type | Signal<br>Level | Power<br>Rail | Remark / Power Tol. | Description                                                                                                                                 | Source /<br>Target |

|--------|-------------|-----------------|---------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| GND    | Power       |                 |               |                     | Ground - DC power and signal and AC signal return path. All available GND connector pins shall be used and tied to Carrier Board GND plane. |                    |

## 2.8 Connectors

## 2.8.1 Module connector

| Row A |               | Row B |               |

|-------|---------------|-------|---------------|

| 1     | GND           | 2     | GND           |

| 3     | GBE_MDI3-     | 4     | GBE_MDI2-     |

| 5     | GBE_MDI3+     | 6     | GBE_MDI2+     |

| 7     | GBE_LINK100#  | 8     | GBE_LINK1000# |

| 9     | GBE_MDI1-     | 10    | GBE_MDI0-     |

| 11    | GBE_MDI1+     | 12    | GBE_MDI0+     |

| 13    | NC            | 14    | GBE_ACT#      |

| 15    | GBE_CTREF     | 16    | SUS_S5#       |

| 17    | WAKE#         | 18    | SUS_S3#       |

| 19    | SUS_STAT#     | 20    | PWRBTN#       |

| 21    | SLP_BTN#      | 22    | LID_BTN#      |

| 23    | GND           | 24    | GND           |

| KEY   |               | KEY   |               |

| 25    | GND           | 26    | PWGIN         |

| 27    | BATLOW#       | 28    | RSTBTN#       |

| 29    | SATA0_TX+     | 30    | SATA1_TX+     |

| 31    | SATA0_TX-     | 32    | SATA1_TX-     |

| 33    | SATA_ACT#     | 34    | GND           |

| 35    | SATA0_RX+     | 36    | SATA1_RX+     |

| 37    | SATA0_RX-     | 38    | SATA1_RX-     |

| 39    | GND           | 40    | GND           |

| 41    | BIOS_DISABLE# | 42    | NC            |

| 43    | NC            | 44    | NC            |

| 45    | NC            | 46    | NC            |

| 47    | NC            | 48    | NC            |

| 49    | NC            | 50    | NC            |

| 51  | NC             | F2  | NC           |

|-----|----------------|-----|--------------|

|     |                | 52  |              |

| 53  | NC NO          | 54  | NC           |

| 55  | NC             | 56  | NC           |

| 57  | GND            | 58  | GND          |

| 59  | HDA_SYNC       | 60  | SMB_CLK      |

| 61  | HDA_RST#       | 62  | SMB_DAT      |

| 63  | HDA_BITCLK     | 64  | SMB_ALERT#   |

| 65  | HDA_SDI        | 66  | I2C_CLK      |

| 67  | HDA_SDO        | 68  | I2C_DAT      |

| 69  | THRM#          | 70  | WDTRIG#      |

| 71  | THRMTRIP#      | 72  | WDOUT        |

| 73  | GND            | 74  | GND          |

| 75  | USB_P7-        | 76  | USB_P6-      |

| 77  | USB_P7+        | 78  | USB_P6+      |

| 79  | USB_6_7_OC#    | 80  | USB_4_5_OC#  |

| 81  | USB_P5-        | 82  | USB_P4-      |

| 83  | USB_P5+        | 84  | USB_P4+      |

| 85  | USB_2_3_OC#    | 86  | USB_0_1_OC#  |

| 87  | USB_P3-        | 88  | USB_P2-      |

| 89  | USB_P3+        | 90  | USB_P2+      |

| 91  | USB_CL_PRES    | 92  | USB_HC_SEL   |

| 93  | USB_P1-        | 94  | USB_P0-      |

| 95  | USB_P1+        | 96  | USB_P0+      |

| 97  | GND            | 98  | GND          |

| 99  | LVDS_A0+       | 100 | LVDS_B0+     |

| 101 | LVDS_A0-       | 102 | LVDS_B0-     |

| 103 | LVDS_A1+       | 104 | LVDS_B1+     |

| 105 | LVDS_A1-       | 106 | LVDS_B1-     |

| 107 | LVDS A2+       | 108 | LVDS_B2+     |

| 109 | LVDS_A2-       | 110 | LVDS_B2-     |

| 111 | LVDS_PPEN      | 112 | LVDS_BLEN    |

| 113 | LVDS_A3+       | 114 | LVDS_B3+     |

| 115 | LVDS A3-       | 116 | LVDS B3-     |

| 117 | GND            | 118 | GND          |

| 119 | LVDS_A_CLK+    | 120 | LVDS_B_CLK+  |

| 121 | LVDS A CLK-    | 122 | LVDS B CLK-  |

| 123 | LVDS_BLT_CTRL  | 124 | RSVD         |

| 125 | LVDS_DID_DAT   | 126 | LVDS_BLC_DAT |

| 127 | LVDS DID CLK   | 128 | LVDS BLC CLK |

| 129 | RSVD           | 130 | RSVD         |

| 131 | TMDS_CLK+      | 132 | NC NC        |

| 133 | TMDS_CLK-      | 134 | NC NC        |

| 135 | GND            | 136 | GND          |

| 137 | TMDS_LANE1+    | 138 | DP_AUX+      |

| 139 | TMDS_LANE1-    | 140 | DP_AUX-      |

| 141 | GND            | 142 | GND          |

| 143 | TMDS LANE0+    | 144 | NC           |

| 143 | TIVIDO_LAINEUT | 144 | INO          |

| 145 | TMDS_LANE0-   | 146 | NC            |

|-----|---------------|-----|---------------|

| 147 | GND           | 148 | GND           |

| 149 | TMDS_LANE2+   | 150 | HDMI_CTRL_DAT |

| 151 | TMDS_LANE2-   | 152 | HDMI_CTRL_CLK |

| 153 | DP1_HPD       | 154 | DP1_HPD       |

| 155 | PCIE_CLK_REF+ | 156 | PCIE_WAKE#    |

| 157 | PCIE_CLK_REF- | 158 | PCIE_RST#     |

| 159 | GND           | 160 | GND           |

| 161 | PCIE3_TX+     | 162 | PCIE3_RX+     |

| 163 | PCIE3_TX-     | 164 | PCIE3_RX-     |

| 165 | GND           | 166 | GND           |

| 167 | PCIE2_TX+     | 168 | PCIE2_RX+     |

| 169 | PCIE2_TX-     | 170 | PCIE2_RX-     |

| 171 | EXCD0_PERST#  | 172 | EXCD1_PERST#  |

| 173 | PCIE1_TX+     | 174 | PCIE1_RX+     |

| 175 | PCIE1_TX-     | 176 | PCIE1_RX-     |

| 177 | EXCD0_CPPE#   | 178 | EXCD1_CPPE#   |

| 179 | PCIE0_TX+     | 180 | PCIE0_RX+     |

| 181 | PCIE0_TX-     | 182 | PCIE0_RX-     |

| 183 | GND           | 184 | GND           |

| 185 | LPC_AD0       | 186 | LPC_AD1       |

| 187 | LPC_AD2       | 188 | LPC_AD3       |

| 189 | LPC_CLK       | 190 | LPC_FRAME#    |

| 191 | SERIRQ        | 192 | LPC_LDRQ#     |

| 193 | VCC_RTC       | 194 | SPKR          |

| 195 | FAN_TACHOIN   | 196 | FAN_PWMOUT    |

| 197 | GND           | 198 | GND           |

| 199 | SPI_MOSI      | 200 | SPI_CS0       |

| 201 | SPI_MISO      | 202 | RSVD          |

| 203 | SPI_SCK       | 204 | RSVD          |

| 205 | VCC_5V_SB     | 206 | VCC_5V_SB     |

| 207 | NC            | 208 | NC            |

| 209 | NC            | 210 | NC            |

| 211 | VCC           | 212 | VCC           |

| 213 | VCC           | 214 | VCC           |

| 215 | VCC           | 216 | VCC           |

| 217 | VCC           | 218 | VCC           |

| 219 | VCC           | 220 | VCC           |

| 221 | VCC           | 222 | VCC           |

| 223 | VCC           | 224 | VCC           |

| 225 | VCC           | 226 | VCC           |

| 227 | VCC           | 228 | VCC           |

| 229 | VCC           | 230 | VCC           |

## 2.8.2 USB Port assignment

Note: The assignment of the USB Ports from Chipset to Q7 connector is as follows:

| Chipset | Q7 Connector |

|---------|--------------|

| Port 0  | Port 5       |

| Port 1  | Port 3       |

| Port 2  | Port 0       |

| Port 3  | Port 2       |

| Port 4  | Port 6       |

| Port 5  | Port 4       |

| Port 6  | Port 1       |

| Port 7  | Port 7       |

In Bios setup, all USB port numbers are related to the chipset

## 3 System Resources

## 3.1 SMB Address Map

| Device               | A6 | A5 | A4 | A3 | A2 | A1 | A0 | R/W | address *) |

|----------------------|----|----|----|----|----|----|----|-----|------------|

| CMOS backup EEPROM   | 1  | 0  | 1  | 0  | 1  | 0  | 0  | Х   | A8h / 54h  |

| SPD EEPROM (SO-DIMM) | 1  | 0  | 1  | 0  | 0  | 0  | 0  | Х   | A0h / 50h  |

<sup>\*) 8</sup> bit address (with R/W) / 7 bit address (without R/W)

## 3.2 PCI Express Lanes

| Signal /Slot             | Source             |

|--------------------------|--------------------|

| PCIE_TX[0]<br>PCIE_RX[0] | PCIe-Channel 3 APU |

| PCIE_TX[1]<br>PCIE_RX[1] | PCIe-Channel 2 APU |

| PCIE_TX[2]<br>PCIE_RX[2] | PCIe-Channel 1 APU |

| PCIE_TX[3]<br>PCIE_RX[3] | PCIe-Channel 0 APU |

## 3.3 USB

| Signal             | Source / Target | Remark      |

|--------------------|-----------------|-------------|

| USB[0]+<br>USB[0]- | USB0 A50M       | USB1.1/2.0  |

| USB[1]+<br>USB[1]- | USB2 A50M       | USB1.1/2.0) |

| USB[2]+<br>USB[2]- | USB1 A50M       | USB1.1/2.0  |

| USB[3]+<br>USB[3]- | USB3 A50M       | USB1.1/2.0  |

| USB[4]+<br>USB[4]- | USB4 A50M       | USB1.1/2.0  |

| USB[5]+<br>USB[5]- | USB5 A50M       | USB1.1/2.0  |

| USB[6]+<br>USB[6]- | USB6 A50M       | USB1.1/2.0  |

| USB[7]+<br>USB[7]- | USB7 A50M       | USB1.1/2.0  |

## 3.4 PCI Interrupt Routing Table

| Qseven                                |            |       |                   | Int               | errupt            | s of Co           | ntrolle           | er (TC1           | <sup>-</sup> C)   |                   |

|---------------------------------------|------------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| Slot Number<br>(or Onboard<br>Device) | Dev / Func | Bus # | PIRQ 0<br>(INT A) | PIRQ 1<br>(INT B) | PIRQ 2<br>(INT C) | PIRQ 3<br>(INT D) | PIRQ 4<br>(INT E) | PIRQ 5<br>(INT F) | PIRQ 6<br>(INT G) | PIRQ 7<br>(INT H) |

| Internal<br>Graphic<br>Device         | 01h/01     | 0     |                   |                   | А                 |                   |                   |                   |                   |                   |

| HD Audio                              | 14h/02     | 0     | Α                 |                   |                   |                   |                   |                   |                   |                   |

| PCI Express<br>Root Port 0            | 15h/0      | 0     | Α                 |                   |                   |                   |                   |                   |                   |                   |

| USB OHCI<br>Host Controller           | 12h/0      | 0     |                   |                   | Α                 |                   |                   |                   |                   |                   |

| USB OHCI<br>Host Controller           | 13h/0      | 0     |                   |                   | Α                 |                   |                   |                   |                   |                   |

| USB EHCI<br>Host Controller           | 12h/02     | 0     |                   | В                 |                   |                   |                   |                   |                   |                   |

| USB EHCI<br>Controller                | 13h/02     | 0     |                   | В                 |                   |                   |                   |                   |                   |                   |

| SATA                                  | 11h/0      | 0     |                   |                   |                   | Α                 |                   |                   |                   |                   |

| PCI to PCI<br>Host Bridge             | 0h/07      | 0     |                   |                   |                   | A                 |                   |                   |                   |                   |

| HD Audio<br>AMD                       | 01h/01     | 0     |                   |                   |                   | В                 |                   |                   |                   |                   |

## 3.5 IRQ Lines in Legacy IRQ Mode

| IRQ# | Available | Typical Interrupt Source         |

|------|-----------|----------------------------------|

| 0    | No        | Counter 0                        |

| 1    | No        | Keyboard                         |

| 2    | No        | Cascade Interrupt from Slave PIC |

| 3    | Yes       |                                  |

| 4    | Yes       |                                  |

| 5    | Yes       |                                  |

| 6    | Yes       |                                  |

| 7    | Yes       |                                  |

| 8    | No        | RTC                              |

| 9    | Limited   | In ACPI mode used for SCI        |

| 10   | Yes       |                                  |

| 11   | Yes       |                                  |

| IRQ# | Available | Typical Interrupt Source |

|------|-----------|--------------------------|

| 12   | Yes       |                          |

| 13   | No        | Math coprocessor         |

| 14   | Yes       |                          |

| 15   | Yes       |                          |

## 3.6 IRQ Lines in APIC Mode

| IRQ# | Available | Typical Interrupt Source         | Connected to Pin |

|------|-----------|----------------------------------|------------------|

| 0    | No        | Counter 0                        |                  |

| 1    | No        | Keyboard                         |                  |

| 2    | No        | Cascade Interrupt from Slave PIC |                  |

| 3    | Yes       |                                  |                  |

| 4    | Yes       |                                  |                  |

| 5    | Yes       |                                  |                  |

| 6    | Yes       |                                  |                  |

| 7    | Yes       |                                  |                  |

| 8    | No        | RTC                              |                  |

| 9    | Yes       | shared SCI                       |                  |

| 10   | Yes       |                                  |                  |

| 11   | Yes       |                                  |                  |

| 12   | No        |                                  |                  |

| 13   | No        | Math processor                   |                  |

| 14   | Yes       |                                  |                  |

| 15   | Yes       |                                  |                  |

| 16   | Yes       |                                  | PIRQA            |

| 17   | Yes       |                                  | PIRQB            |

| 18   | Yes       |                                  | PIRQC            |

| 19   | Yes       |                                  | PIRQD            |

| 20   | No        |                                  |                  |

| 21   | No        |                                  |                  |

| 22   | No        |                                  |                  |

| 23   | No        |                                  |                  |

#### 4 BIOS

#### 4.1 Introduction

This guide describes the AMI Aptio Setup Startup screen and contains information on how to access Aptio setup to modify the settings which control AMI pre-OS (operating system) functions.

#### 4.1.1 Startup Screen Overview

The AMI Aptio Startup screen is a graphical user interface (GUI) that is included in AMI Aptio products. The default bios behavior is to show an informational text screen during bios POST phase, but the graphical boot screen can be enabled in the bios setup. The standard boot screen is a black screen without any logo.

#### 4.1.2 Activity Detection Background

While the startup screen is displayed, press the Setup Entry key (F2 or DEL). The system acknowledges the input, and at the end of POST, the screen clears and setup launches.

#### 4.2 Aptio Setup Utility

With the AMI Aptio Setup program, you can modify Aptio settings and control the special features of your computer. The setup program uses a number of menus for making changes and turning the special features on or off. This chapter provides an overview of the setup utility and describes at a high-level how to use it.

#### 4.2.1 Configuring the System BIOS

To start the AMI Aptio Setup utility, press [F2 or DEL] to launch Setup. The setup main menu appears.

## **The BIOS Menu Structure**

The BIOS Menu is structured in the following way:

| Main                               |

|------------------------------------|

| MSC Board Info                     |

| Hardware Monitoring Measurement    |

| Advanced                           |

| PCI Subsystem Settings             |

| ACPI Settings                      |

| Trusted Computing                  |

| CPU Configuration                  |

| SATA Configuration                 |

| USB Configuration                  |

| WB627 SIO Configuration            |

| AMI Graphic Output Protocol Policy |

| Chipset                            |

| North Bridge                       |

| LVDS Config Select                 |

| South Bridge                       |

| Boot                               |

| Security                           |

| Save & Exit                        |

#### The Menu Bar

The Menu Bar at the top of the window lists these selections:

| Menu Items  | Description                                                                                  |

|-------------|----------------------------------------------------------------------------------------------|

| Main        | Use this menu for basic system information.                                                  |

| Advanced    | Use this menu to set the Advanced Features available on your system's chipset.               |

| Chipset     | Use this menu to set Chipset Features.                                                       |

| Security    | Use this menu to set User and Supervisor Passwords and the Backup and Virus-Check reminders. |

| Boot        | Use this menu to set the boot order in which the BIOS attempts to boot to OS.                |

| Save & Exit | Saves and Exits the Aptio setup utility.                                                     |

Use the left and right arrow keys on your keyboard to make a menu selection.

### The Legend Bar

Use the keys listed in the legend bar on the right side of the screen to make your selections, or to exit the current menu. The following table describes the legend keys and their alternates:

| Key                       | Function                                         |

|---------------------------|--------------------------------------------------|

| Esc                       | Exit submenu / Exit Setup utility without saving |

| Left and right arrow keys | Select Screen.                                   |

| Up and down arrow keys    | Select Item.                                     |

| +/-                       | Change Option.                                   |

| F1                        | General Help window.                             |

| F2                        | Previous Values                                  |

| F3                        | Optimized Defaults                               |

| F4                        | Save and Exit                                    |

#### Select an item

To select an item, use the arrow keys to move the cursor to the field you want. Then use the plus-and-minus value keys to select a value for that field. Alternatively the Enter key can be used to select a value from a Pop Up menu. The Save Values commands in the Exit Menu save the values currently displayed in all the menus.

## Display a submenu

To display a submenu, use the arrow keys to move the cursor to the sub menu you want. Then press Enter. A pointer marks all submenus.

#### 4.2.2 The Main Menu

You can make the following selections on the Main Menu itself. Use the sub menus for other selections.

| Feature         | Options                  | Description                                                                                                                                      |

|-----------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Bios Vendor     | Informative              | Shows the Bios Vendor                                                                                                                            |

| Core Version    | Informative              | Shows the Aptio Core Version                                                                                                                     |

| Compliancy      | Informative              | Shows the UEFI Compliance Version                                                                                                                |

| Project Version | Informative              | Shows the Project Version                                                                                                                        |

| Build Date      | Informative              | Shows the Build Date                                                                                                                             |

| Total Memory    | Informative              | Shows the amount of RAM                                                                                                                          |

| MSC Board Info  | Submenu                  | Shows board specific information                                                                                                                 |

| System Date     | Enter Date ( MM:DD:YYYY) | Set the system date on the real time clock.                                                                                                      |

| System Time     | Enter Time (HH:MM:SS)    | Set the system time on the real time clock.                                                                                                      |

| Access Level    | Informative              | This feature shows what kind of user has entered the Aptio setup. It depends on the Security Tab if a Administrator and/or User password is set. |

## 4.2.2.1 MSC Board Info

| Feature                 | Options            | Description                                      |

|-------------------------|--------------------|--------------------------------------------------|

| Manufacturer            | MSC Vertriebs GmbH |                                                  |

| Board Name              | Informative        | Shows the board name                             |

| Board Revision          | Informative        | Shows the board revision                         |

| Bios Version            | Informative        | Shows the bios version                           |

| Serial Number           | Informative        | Shows the boards serial number                   |

| Boot Counter            | Informative        | Shows the amount of boots                        |

| EC Bootloader Version   | Informative        | Shows the Embedded Controller Bootloader version |

| EC Firmwaer Version     | Informative        | Shows the Embedded Controller Firmware version   |

| Onboard Lan MAC adresse | Informative        | Shows the onboard Lan MAC adresse                |

| UUID                    | Informative        | Shows the UUID of the system                     |

## 4.2.2.2 Hardware Monitoring Measurement

| Feature             | Options     | Description                 |

|---------------------|-------------|-----------------------------|

| CPU Temperature     | Informative | Shows CPU Temperature       |

| Chipset Temperature | Informative | Shows Chipset Temperature   |

| CPU Fan Speed       | Informative | Shows the current fan speed |

### 4.2.3 The Advanced Menu

| Feature                | Options | Description                         |

|------------------------|---------|-------------------------------------|

| PCI Subsystem Settings | Submenu | PCI, PCI-X and PCI Express settings |

| ACPI Settings          | Submenu | System ACPI Parameters              |

| Trusted Computing      | Submenu | Trusted Computing ( TPM ) settings  |

| CPU Configuration      | Submenu | CPU Configuration Parameters        |

| SATA Configuration     | Submenu | AHCI SATA Configuration settings    |

| USB Configuration      | Submenu | USB configuration parameters        |

| Feature                               | Options | Description                                                                     |

|---------------------------------------|---------|---------------------------------------------------------------------------------|

| WB627 SIO Configuration               | Submenu | Submenu for Super-IO Winbond<br>W82627                                          |

| Embedded Controller<br>Features       | Submenu | Embedded Controller Features                                                    |

| Serial Port Console<br>Redirection    | Submenu | Serial Port Console Redirection                                                 |

| AMI Graphic Output<br>Protocol Policy | Submenu | Graphic Output adjustment ( appears only if Video Oprom policy is set to UEFI ) |

## 4.2.3.1 PCI Subsystem Settings Submenu

| Feature              | Options                                           | Description                                            |

|----------------------|---------------------------------------------------|--------------------------------------------------------|

| PCI Latency Timer    | 32, 64, 96, 128, 160, 192, 224,<br>248 PCI Clocks | Value to be programmed into PCI latency timer register |

| VGA Palette Snoop    | Enabled, Disabled                                 | Enables or disables VGA Palette registers snooping     |

| PERR# Generation     | Enabled, Disabled                                 | Enables or disables PCI device to generate PERR#       |

| SERR# Generation     | Enabled, Disabled                                 | Enables or disables PCI device to generate SERR#       |

| PCI Express Settings | Submenu                                           | Configure PCI Express                                  |

## 4.2.3.1.1 PCI Express Settings

| Feature              | Options                                     | Description                                                                                |

|----------------------|---------------------------------------------|--------------------------------------------------------------------------------------------|

| Relaxed Ordering     | Enabled, Disabled                           | Enables or disables PCI Express<br>Device Relaxed Ordering                                 |

| Extended Tag         | Enabled, Disabled                           | If enabled allows device to use 8-bit Tag field as a requester                             |

| No Snoop             | Enabled, Disabled                           | Enables or disables PCI Express Device No Snoop option                                     |

| Maximum Payload      | Auto, 128, 256, 512, 1024, 2048. 4096 Bytes | Set maximum payload of PCI Express<br>Device or allow system Bios to select<br>the value   |

| Maximum Read Request | Auto, 128, 256, 512, 1024, 2048. 4096 Bytes | Set read request size of PCI Express<br>Device or allow system Bios to select<br>the value |

| Feature                  | Options                    | Description                                                                                                                                                                               |

|--------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASPM Support             | Disabled, Auto, Force L0s  | Set the ASPM level: Force L0s State:<br>Auto: Bios configures ASPM<br>Force L0s: L0s will be forced<br>Disabled: No ASPM will be used                                                     |

| Extended Synchronization | Enabled, Disabled          | Enabled allows generation of extended synchronization patterns                                                                                                                            |

| Link Training Retry      | Disabled, 2, 5, 10         | Defines number of retry. Attempt software will take to retrain the link if previous training attempt was unsuccessful.                                                                    |

| Link Training Timeout    | 10us to 1000us             | Defines number of microseconds software will wait before polling "Link Training" bit in link status register. Value range from 10 to 1000us.                                              |

| Unpopulated Links        | Kepp Link ON, Disable Link | In order to save power, software will disable unpopulated PCI Express links, if this option set to disabled.                                                                              |

| Restore PCIe Register    | Enabled, Disabled          | On non-PCI Express aware OS 's (<br>Pre Windows Vista) some devices may<br>not be correctly reinitialized after S3.<br>Enabling this restores PCIe device<br>configurations on S3 resume. |

## 4.2.3.2 ACPI Settings

| Feature               | Options                                                          | Description                                                                                                      |

|-----------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Enable ACPI Auto Conf | Enabled, Disabled                                                | Enables or disables BIOS ACPI Auto Configuration.                                                                |

| Enable Hibernation    | Enabled, Disabled                                                | Enables or disables system ability to Hibernate (OS/S4 Sleep State). This option may not effective with some OS. |

| ACPI Sleep State      | Suspend Disabled, S1 (CPU<br>Stop Clock), S3 (Suspend to<br>RAM) | Select the highest ACPI Sleep state the system will enter, when the Suspend button is pressed.                   |

| Lock Legacy Resources | Enabled, Disabled                                                | Enables or disables lock of Legacy parameters.                                                                   |

| LID Switch Support    | Disabled, Active High, Active Low                                | Define the behavior of the LID switch. Active High = Lid is open with high level                                 |

|                       |                                                                  | Active low= Lid is open with low level                                                                           |

## 4.2.3.3 TPM

| Feature           | Options                                                               | Description                                                                                                                                 |

|-------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| TPM Support       | Enabled, Disabled                                                     | Enables or disables TPM support. OS will not show TPM. Reset of platform is required                                                        |

|                   |                                                                       | For more information see also technotes in chapter 4.9                                                                                      |

| TPM state         | Enabled, Disabled                                                     | Turn TPM Enable/Disable. NOTE:<br>Your Computer will reboot during<br>restart in order to change State of<br>TPM.                           |

| Pending Operation | None,<br>Enable take ownership<br>Disable take ownership<br>TPM clear | Schedule an operation for the Security Device.  Note: Your computer will reboot during restart in order to change State of Security Device. |

## 4.2.3.4 **CPU Configuration**

Note: Dependent on used CPU, available setup options may vary

| Feature            | Options            | Description                                                            |

|--------------------|--------------------|------------------------------------------------------------------------|

| PSS Support        | Enabled, Disabled  | Enables or disables the generation of the _PPC, _PSS and _PCT objects. |

| PState Adjustment  | PState 0, PState 1 | Provide to adjust startup P_state level                                |

| PPC Adjustment     | PState 0, PState 1 | Provide to adjust _PPC object for ACPI OS.                             |

| NX Mode            | Enabled, Disabled  | Enables or disables NO-execute page protection function.               |

| SVM Mode           | Enabled, Disabled  | Enable or disables CPU virtualization.                                 |

| C6 Mode            | Enabled, Disabled  | Enables or disables C6                                                 |

| CPB Mode           | Auto, Disabled     | Auto/disable CPB                                                       |

| Node 0 Information | Submenu            | View CPU and Cache Information related to Node 0                       |

## 4.2.3.5 SATA Configuration

| Feature     | Options     | Description                     |

|-------------|-------------|---------------------------------|

| SATA Port 0 | Informative | Shows the SATA Device on Port 0 |

| SATA Port 1 | Informative | Shows the SATA Device on Port 1 |

| SATA Port 2 | Informative | Shows the SATA Device on Port 2 |

## 4.2.3.6 USB Configuration

| Feature                                     | Options                                        | Description                                                                                                                                                                                                 |

|---------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Legacy USB Support                          | Enabled, Disabled                              | Enables Legacy USB support. AUTO option disables legacy support if no USB devices are connected. DISABLE option will keep USB devices available only for EFI applications.                                  |

| EHCI Hand-off                               | Enabled, Disabled                              | This is a workaround for OSes without EHCI hand-off support. The EHCI ownership change should be claimed by EHCI driver.                                                                                    |

| Port 60/64 Emulation                        | Enabled, Disabled                              | Enables I/O port 60h/64h emulation support. This should be enabled for the complete USB keyboard legacy support for non-USB aware OSes.                                                                     |

| USB transfer time-out                       | 1,5,10,20 sec                                  | The time-out value for Control, Bulk, and Interrupt transfers.                                                                                                                                              |

| Device reset time-out                       | 10,20,30,40 sec                                | USB mass storage device Start Unit command time-out.                                                                                                                                                        |

| Device power-up delay                       | Auto, Manual                                   | Maximum time the device will take before it properly reports itself to the Host Controller. 'Auto' uses default value: for a Root port it is 100 ms, for a Hub port the delay is taken from Hub descriptor. |

| Device power-up delay                       | Value 1-40                                     | Delay range is 140 seconds, in one second increments.                                                                                                                                                       |

| USB Mass Storage<br>Device ( e.g USB Stick) | Auto, Floppy, Forced FDD,<br>Hard Disk, CD-ROM | Select Mass storage device emulation type.  Auto enumerates devices according to their media format. Optical drives are emulated as CDROM, drives with no media will be emulated according to a drive       |

# 4.2.3.7 Winbond WB627 / SMSC3114 SuperIO Configuration (if available on carrier board)

| Feature        | Options                                                                                                                                                                                                                            | Description                               |