# 1-Axis Motor Control IC with High Functions

# MCX501 User's Manual

2011-12-27 Ver. 1 2012-11-14 Ver. 1.0

**NOVA** electronics

# Prevent Electrostatic Discharge

**ATTENTION**: This IC is sensitive to electrostatic discharge, which can cause internal damage and affect normal operation. Follow these guidelines when you handle this IC:

- •Touch a grounded object to discharge potential static.

- ·Wear an approved grounding wrist strap.

- •Do not touch pins of this IC.

- •Store this IC in appropriate static-safe packaging when not in use.

# Safety Notice

**WARNING**: This IC is not designed or intended to be fail-safe, or for use in any application requiring fail-safe performance, such as in life-support or safety devices or systems that could lead to death, personal injury or severe property or environmental damage (individually and collectively, "critical applications"). Customer must be fully responsible for the use of this IC in critical applications.

Provide adequate design and operating safeguards in order to minimize risks associated with customer's applications when incorporating this IC in a system.

# Compliance

**ATTENTION**: "Japanese Foreign Exchange and Foreign Trade Act" and other export-related laws and regulations must be observed and complied with. Do not use this IC for the purpose of the development of weapons such as mass destruction weapons and any military purposes. This IC shall not be used in equipment that manufacture, use and sale are prohibited by Japanese and foreign laws and regulations.

# Before you begin

**ATTENTION**: Before using this IC, read this manual thoroughly to ensure correct usage within the scope of the specification such as the signal voltage, signal timing, and operation parameter values.

#### Installation of this IC

**ATTENTION**: This IC is provided in the form of a lead-free package. The installation conditions are different from those of the conventional lead-soldered IC. See Chapter 11 for the installation conditions of this IC.

#### About Reset

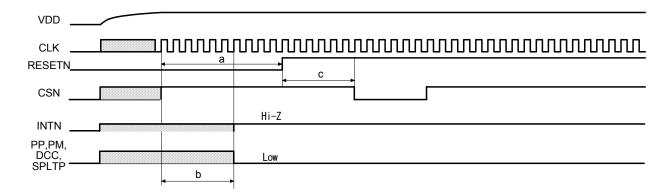

**ATTENTION**: Make sure to reset the IC when the power is on. This IC will be reset if RESETN signal is set to Low for more than 8 CLK cycles when a stable clock has been input. Please note that the IC will not be reset if the clock is not input.

# Treatment of unused pins

**ATTENTION**: Make sure that unused input pins are connected to GND or VDD. If these pins are open, the signal level of pins will unstable and may cause malfunction. Make sure that unused bi-directional pins are connected to VDD or GND through high impedance (about  $10k\sim 100~k\Omega$ ). If these pins are directly connected to GND or VDD, the IC may be damaged by overcurrent in case of such as a programming mistake causes the output state.

#### Notes on S-curve acceleration/deceleration driving

**ATTENTION**: This IC is equipped with a function that performs decelerating stop For a fixed pulse drive with S-curve deceleration of the symmetrical acceleration /deceleration. However, when the initial speed is set to an extremely low speed (10 or less), slight premature termination or creep may occur. Before using a S-curve deceleration drive, make sure that your system allows premature termination or

#### **Technical Information**

**ATTENTION**: Before using this IC, read "Appendix B Technical Information" on the last pages of this manual without fail because there are some important information.

The descriptions of this manual may change without notice because of the progress of the technologies, etc. Please download the up-date data from our website (http://www.novaelec.co.jp/eng) and/or ask us to supply you directly.

# ■ Terms and Symbols used in the Manual

Active The function of a signal is the state of being enabled.

Drive Action to output pulses for rotating a motor to the driver (drive unit) of a pulse type servo

motor or setepping motor.

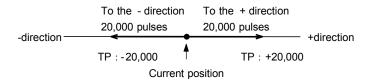

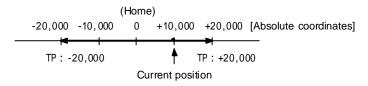

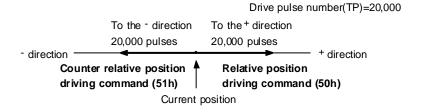

Fixed pulse drive Drive that outputs specified pulses. Three types of drives: relative position drive, counter

relative position drive and absolute position drive are available.

Continuous pulse drive Drive that outputs pulses up to infinity unless a stop factor becomes active.

Jerk Acceleration increasing/decreasing rate per unit time. This term includes a decreasing rate of

acceleration (=Jerk).

Deceleration increasing rate Deceleration increasing/decreasing rate per unit time. This term includes a decreasing rate of

deceleration.

2's complement is used to represent negative numbers in binary.

[Example] In 16-bit length, -1 is FFFFh, -2 is FFFEh, -3 is FFFDh, ... -32768 is 8000h.

Creep In deceleration of acceleration/ deceleration fixed pulse driving, output of specified driving

pulses is not completed even if the speed reaches the initial speed and the rest of driving

pulses is output at the initial speed (= Creep).

Premature termination In deceleration of acceleration/ deceleration fixed pulse driving, output of specified driving

pulses is completed and driving is terminated before the speed reaches the initial speed. This is

a reverse behavior of creep.

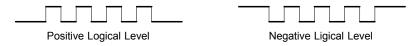

The rising edge of when a signal changes its level from Low to Hi.

The falling edge of when a signal changes its level from Hi to Low.

# Contents

| 1. OL          | JTLINE                                                  |    |

|----------------|---------------------------------------------------------|----|

| 1.1            | The Main Features of Functions                          |    |

|                | Functional Block Diagram                                |    |

|                | Specification Table                                     |    |

| 2. Th          | e Descriptions of Functions                             | 10 |

| 2.1 F          | Fixed Pulse Driving and Continuous Pulse Driving        | 10 |

| 2.1.1          | Relative Position Driving                               |    |

| 2.1.2          | Absolute Position Driving                               | 11 |

| 2.1.3          | Counter Relative Position Driving                       | 11 |

| 2.1.4          | Continuous Pulse Driving                                | 13 |

| 2.2 A          | Acceleration and Deceleration                           | 15 |

| 2.2.1          | Constant Speed Driving                                  |    |

| 2.2.2          | Trapezoidal Driving [Symmetrical]                       |    |

| 2.2.3          | Non-Symmetrical Trapezoidal Acceleration                |    |

| 2.2.4          | S-curve Acceleration/Deceleration Driving [Symmetrical] |    |

| 2.2.5          | Non-symmetrical S-Curve Acceleration/Deceleration       |    |

| 2.2.6          | Pulse Width and Speed Accuracy                          |    |

| 2.3 F          | Position Control                                        |    |

| 2.3.1          | Logical Position Counter and Real position Counter      |    |

| 2.3.2          | Position Comparison                                     |    |

| 2.3.3          | Software Limit                                          |    |

| 2.3.4          | Position Counter Variable Ring                          |    |

|                | Multi-Purpose Register                                  |    |

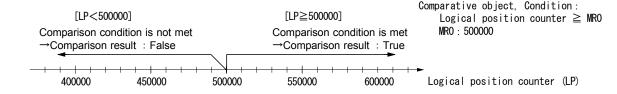

| 2.4.1          | Comparative Object and Comparison Condition             |    |

| 2.4.2          | Usage of Comparison Result                              |    |

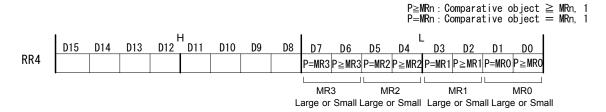

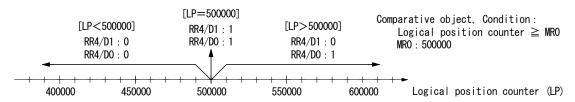

| 2.4.3          | Comparison Result of Large or Small                     |    |

| 2.4.4          | Load / Save of Parameters by Synchronous Action         |    |

|                | Automatic Home Search                                   |    |

| 2.5.1          | Operation of Each Step                                  |    |

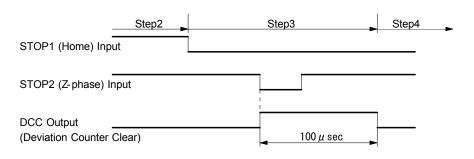

| 2.5.2          | Deviation Counter Clearing Signal Output                |    |

| 2.5.3<br>2.5.4 | Timer Between Steps  Setting a Search Speed and a Mode  |    |

| 2.5.4          | Execution of Automatic Home Search and the Status       |    |

| 2.5.6          | Errors Occurring at Automatic Home Search               |    |

| 2.5.7          | Notes on Automatic Home Search                          |    |

| 2.5.7          | Examples of Automatic Home Search                       |    |

|                | Synchronous Action                                      |    |

| 2.6.1          | Activation Factor                                       |    |

| 2.6.2          | Action                                                  |    |

| 2.6.3          | Synchronous Action Settings                             |    |

| 2.6.4          | Synchronous Action Execution                            |    |

| 2.6.5          | Interrupt by Synchronous Action                         |    |

| 2.6.6          | Examples of Synchronous Action                          |    |

| 2.6.7          | Synchronous Action Delay Time                           |    |

|                | Split Pulse                                             |    |

| 2.7.1          | Split Pulse Setting                                     |    |

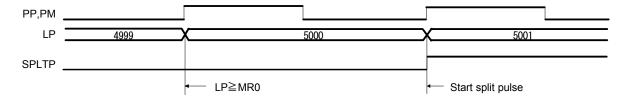

| 2.7.2          | Start / Termination of Split Pulse                      |    |

| 2.7.3          | Split Pulse in Synchronous Action                       |    |

| 2.7.4          | Interrupt by Split Pulse                                |    |

| 2.7.5          | Notes on Split Pulse                                    |    |

| 2.7.6          | Examples of Split Pulse                                 |    |

|                |                                                         |    |

| 2.8                                                                                                                                        | General Purpose Input / Output Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 80                       |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 2.8.1                                                                                                                                      | 1 PIOn Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 80                       |

| 2.8.2                                                                                                                                      | 2 Other Input Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 82                       |

| 2.8.3                                                                                                                                      | 3 High word Data Signal in 8-bit Data Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 82                       |

| 2.9                                                                                                                                        | Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 83                       |

| 2.9.1                                                                                                                                      | 1 Timer Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 83                       |

| 2.9.2                                                                                                                                      | 2 Timer Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 84                       |

| 2.9.3                                                                                                                                      | 3 Timer-Start / Timer-Stop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 84                       |

| 2.9.4                                                                                                                                      | 4 Timer and Synchronous Action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 84                       |

| 2.9.5                                                                                                                                      | 5 Timer Operating State and Current Timer Value Reading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 84                       |

| 2.9.6                                                                                                                                      | 6 Interrupt by Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 84                       |

| 2.9.7                                                                                                                                      | 7 Examples of Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 85                       |

| 2.10                                                                                                                                       | Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 88                       |

| 2.11                                                                                                                                       | Input Signal Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 90                       |

| 2.11                                                                                                                                       | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |

| 2.11                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

| 2.12                                                                                                                                       | Other Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

| 2.12                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

| 2.12                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

| 2.12                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

| 2.12                                                                                                                                       | • ••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |

| 2.12                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

| 2.12                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

| 2.12                                                                                                                                       | 3 · , · · · p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |

|                                                                                                                                            | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |

| 3. P                                                                                                                                       | in Assignments and Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 100                      |

| 3.1                                                                                                                                        | Pin Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

| 3.2                                                                                                                                        | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| 3.3                                                                                                                                        | Input/Output Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| 3.3                                                                                                                                        | • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| 3 /                                                                                                                                        | Pemarks of Logic Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 106                      |

| 3.4                                                                                                                                        | Remarks of Logic Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

|                                                                                                                                            | Remarks of Logic Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

|                                                                                                                                            | legister                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 107                      |

| 4. R                                                                                                                                       | Register Address by 16-bit Data Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 107                      |

| 4.1<br>4.2                                                                                                                                 | Register Address by 16-bit Data Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 107<br>107<br>108        |

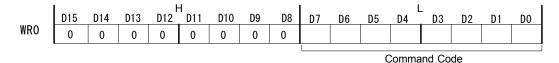

| 4.1<br>4.2<br>4.3                                                                                                                          | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 107<br>107<br>108<br>109 |

| 4.1<br>4.2<br>4.3<br>4.4                                                                                                                   | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 107<br>107<br>108<br>109 |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5                                                                                                            | Register Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6                                                                                                     | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7                                                                                              | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8                                                                                       | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4 Data Register: WR6/WR7                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |

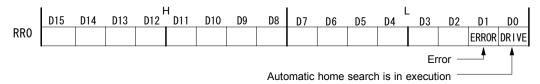

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9                                                                                | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4 Data Register: WR6/WR7 Main Status Register: RR0                                                                                                                                                                                                                                                                                                                                                                                                  |                          |

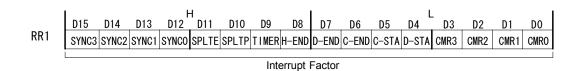

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10                                                                        | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4 Data Register: WR6/WR7 Main Status Register: RR0 Status Register 1: RR1                                                                                                                                                                                                                                                                                                                                                                           |                          |

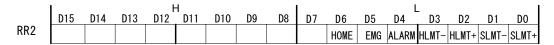

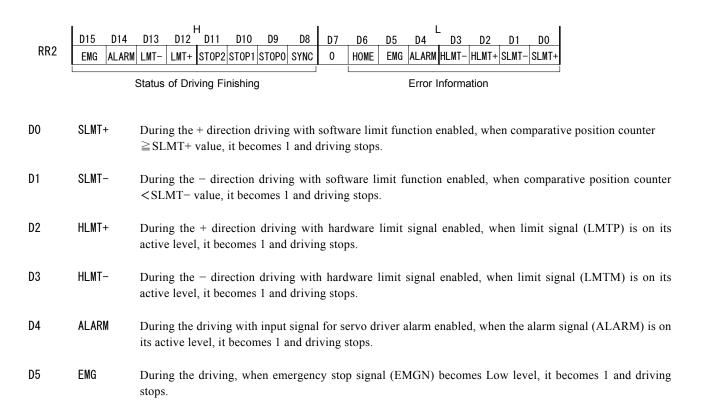

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11                                                                | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4 Data Register: WR6/WR7 Main Status Register: RR0 Status Register 2: RR2                                                                                                                                                                                                                                                                                                                                                                           |                          |

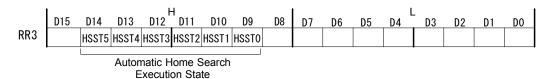

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12                                                        | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4 Data Register: WR6/WR7 Main Status Register: RR0 Status Register 1: RR1 Status Register 2: RR2 Status Register 3: RR3                                                                                                                                                                                                                                                                                                                             |                          |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13                                                | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4 Data Register: WR6/WR7 Main Status Register: RR0 Status Register 1: RR1 Status Register 2: RR2 Status Register 3: RR3 Status Register 4: RR4                                                                                                                                                                                                                                                                                                      |                          |

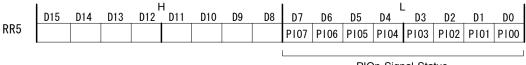

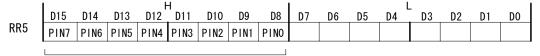

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13<br>4.14                                        | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4 Data Register: WR6/WR7 Main Status Register: RR0 Status Register 1: RR1 Status Register 2: RR2 Status Register 3: RR3 Status Register 4: RR4 PIO Read Register: RR5                                                                                                                                                                                                                                                                               |                          |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13                                                | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4 Data Register: WR6/WR7 Main Status Register: RR0 Status Register 1: RR1 Status Register 2: RR2 Status Register 3: RR3 Status Register 4: RR4                                                                                                                                                                                                                                                                                                      |                          |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13<br>4.14<br>4.15                                | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4 Data Register: WR6/WR7 Main Status Register: RR0 Status Register 1: RR1 Status Register 2: RR2 Status Register 3: RR3 Status Register 4: RR4 PIO Read Register: RR5                                                                                                                                                                                                                                                                               |                          |

| 4. R 4.1 4.2 4.3 4.4 4.5 4.6 4.7 4.8 4.9 4.10 4.11 4.12 4.13 4.14 4.15 6. C                                                                | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4 Data Register: WR6/WR7 Main Status Register: RR0 Status Register 1: RR1 Status Register 2: RR2 Status Register 3: RR3 Status Register 4: RR4 PIO Read Register: RR6 / RR7 Commands                                                                                                                                                                                                                                                                |                          |

| 4. R  4.1  4.2  4.3  4.4  4.5  4.6  4.7  4.8  4.9  4.10  4.11  4.12  4.13  4.14  4.15  5. C                                                | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4 Data Register: WR6/WR7 Main Status Register: RR0 Status Register 1: RR1 Status Register 2: RR2 Status Register 3: RR3 Status Register 4: RR4 PIO Read Register: RR5 Data-Read Register: RR6 / RR7 Commands Command Lists                                                                                                                                                                                                                          |                          |

| 4. R  4.1  4.2  4.3  4.4  4.5  4.6  4.7  4.8  4.9  4.10  4.11  4.12  4.13  4.14  4.15  5. C  5.1  5.2                                      | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR6/WR7 Main Status Register: RR0 Status Register 1: RR1 Status Register 2: RR2 Status Register 3: RR3 Status Register: RR4 PIO Read Register: RR5 Data-Read Register: RR6 / RR7 Commands Commands for Writing Data                                                                                                                                                                                                                                   |                          |

| 4. R  4.1  4.2  4.3  4.4  4.5  4.6  4.7  4.8  4.9  4.10  4.11  4.12  4.13  4.14  4.15  5. C  5.1  5.2  5.2.1                               | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR6/WR7 Main Status Register: RR0 Status Register 1: RR1 Status Register 2: RR2 Status Register 3: RR3 Status Register: RR4 PIO Read Register: RR5 Data-Read Register: RR6 / RR7 Commands Commands for Writing Data 1 Jerk Setting.                                                                                                                                                                                                                   |                          |

| 4. R  4.1  4.2  4.3  4.4  4.5  4.6  4.7  4.8  4.9  4.10  4.11  4.12  4.13  4.14  4.15  5. C  5.1  5.2  5.2.1  5.2.2                        | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4 Data Register: WR6/WR7 Main Status Register: RR0 Status Register 1: RR1 Status Register 2: RR2 Status Register 3: RR3 Status Register 4: RR4 PIO Read Register: RR5 Data-Read Register: RR6 / RR7 Commands Command Lists Commands for Writing Data 1 Jerk Setting. 2 Deceleration Increasing Rate Setting                                                                                                                                         |                          |

| 4. R  4.1  4.2  4.3  4.4  4.5  4.6  4.7  4.8  4.9  4.10  4.11  4.12  4.13  4.14  4.15  5. C  5.1  5.2  5.2.2  5.2.3                        | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4 Data Register: WR6/WR7 Main Status Register: RR0 Status Register 1: RR1 Status Register 2: RR2 Status Register 3: RR3 Status Register 4: RR4 PIO Read Register: RR5 Data-Read Register: RR6 / RR7 Commands Command Lists Commands for Writing Data 1 Jerk Setting. 2 Deceleration Increasing Rate Setting. 3 Acceleration Setting.                                                                                                                |                          |

| 4. R  4.1  4.2  4.3  4.4  4.5  4.6  4.7  4.8  4.9  4.10  4.11  4.12  4.13  4.14  4.15  5. C  5.1  5.2  5.2.2  5.2.3  5.2.2                 | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4 Data Register: WR6/WR7 Main Status Register: RR0 Status Register 1: RR1 Status Register 2: RR2 Status Register 3: RR3 Status Register 4: RR4 PIO Read Register: RR6 / RR7 Commands Command Lists Commands for Writing Data 1 Jerk Setting. 2 Deceleration Increasing Rate Setting. 3 Acceleration Setting. 4 Deceleration Setting.                                                                                                                |                          |

| 4. R  4.1  4.2  4.3  4.4  4.5  4.6  4.7  4.8  4.9  4.10  4.11  4.12  4.13  4.14  4.15  5. C  5.1  5.2  5.2.2  5.2.3  5.2.4  5.2.5          | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4 Data Register: WR6/WR7 Main Status Register : RR0 Status Register 1: RR1 Status Register 2: RR2 Status Register 3: RR3 Status Register 3: RR3 Status Register 4: RR4 PIO Read Register: RR5 Data-Read Register: RR6 / RR7  Commands Commands Commands 1 Jerk Setting 2 Deceleration Increasing Rate Setting 3 Acceleration Setting 4 Deceleration Setting 5 Initial Speed Setting                                                                 |                          |

| 4. R  4.1  4.2  4.3  4.4  4.5  4.6  4.7  4.8  4.9  4.10  4.11  4.12  4.13  4.14  4.15  5. C  5.1  5.2.2  5.2.3  5.2.2  5.2.5  5.2.5  5.2.5 | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR6/WR7 Main Status Register: RR0 Status Register 1: RR1 Status Register 2: RR2 Status Register 3: RR3 Status Register 3: RR3 Status Register 4: RR4 PIO Read Register: RR5 Data-Read Register: RR6 / RR7 Commands Commands Commands for Writing Data 1 Jerk Setting. 2 Deceleration Increasing Rate Setting. 4 Deceleration Setting. 5 Initial Speed Setting. 6 Drive Speed Setting.                                                                 |                          |

| 4. R  4.1  4.2  4.3  4.4  4.5  4.6  4.7  4.8  4.9  4.10  4.11  4.12  4.13  4.14  4.15  5. C  5.1  5.2  5.2.2  5.2.3  5.2.4  5.2.5          | Register Address by 16-bit Data Bus Register Address by 8-bit Data Bus Command Register: WR0 Mode Register1: WR1 Mode Register2: WR2 Mode Register3: WR3 Output Register: WR4 Data Register: WR6/WR7 Main Status Register 1: RR1 Status Register 1: RR1 Status Register 2: RR2 Status Register 3: RR3 Status Register 3: RR3 Status Register 4: RR4 PIO Read Register: RR6 / RR7 Commands Command Lists Commands for Writing Data 1 Jerk Setting 2 Deceleration Increasing Rate Setting 3 Acceleration Setting 4 Deceleration Setting 5 Initial Speed Setting 6 Drive Speed Setting 7 Drive pulse number / Finish point setting |                          |

| 5.2.9  | Logical Position Counter Setting                        | 126 |

|--------|---------------------------------------------------------|-----|

| 5.2.10 | Real Position Counter Setting                           | 126 |

| 5.2.11 | Software Limit + Setting                                | 126 |

| 5.2.12 | Software Limit - Setting                                | 126 |

| 5.2.13 | Acceleration Counter Offsetting                         | 127 |

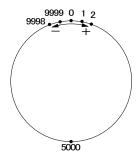

| 5.2.14 | Logical Position Counter Maximum Value Setting          | 127 |

| 5.2.15 | Real Position Counter Maximum Value Setting             | 127 |

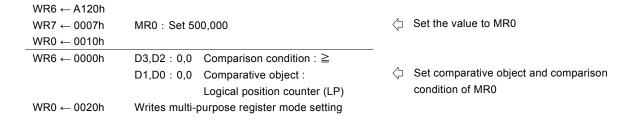

| 5.2.16 | Multi-Purpose Register 0 Setting                        | 127 |

| 5.2.17 | Multi-Purpose Register 1 Setting                        | 128 |

| 5.2.18 | Multi-Purpose Register 2 Setting                        | 128 |

| 5.2.19 | Multi-Purpose Register 3 Setting                        | 128 |

| 5.2.20 | Home Search Speed Setting                               | 129 |

| 5.2.21 | Speed Increasing / Decreasing Value Setting             | 129 |

| 5.2.22 | Timer Value Setting                                     | 129 |

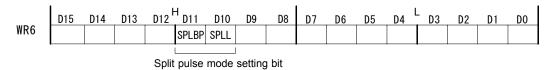

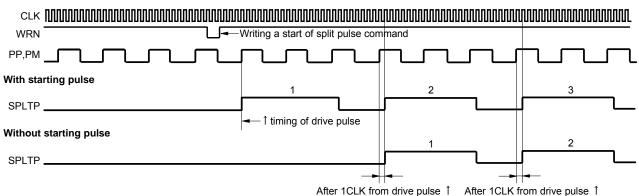

| 5.2.23 | Split Pulse Setting 1                                   | 130 |

| 5.2.24 | Split Pulse Setting 2                                   | 130 |

| 5.3 C  | Commands for Writing Mode                               | 131 |

| 5.3.1  | Multi-Purpose Register Mode Setting                     | 131 |

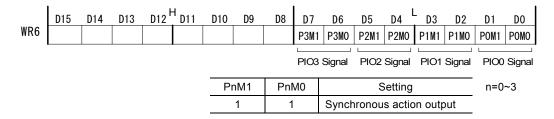

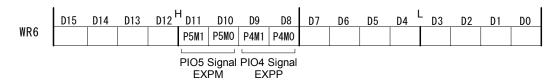

| 5.3.2  | PIO Signal Setting 1                                    | 132 |

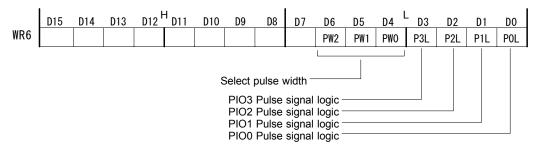

| 5.3.3  | PIO Signal Setting 2 · Other Settings                   | 133 |

| 5.3.4  | Automatic Home Search Mode Setting 1                    | 135 |

| 5.3.5  | Automatic Home Search Mode Setting 2                    | 136 |

| 5.3.6  | Input signal filter mode setting                        | 138 |

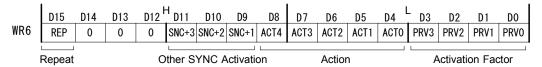

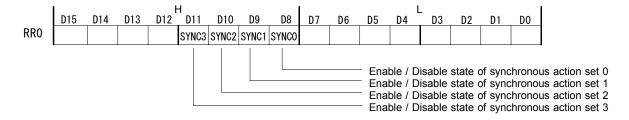

| 5.3.7  | Synchronous Action SYNC0, 1, 2, 3 Setting               | 139 |

| 5.4 C  | Commands for Reading Data                               | 141 |

| 5.4.1  | Logical Position Counter Reading                        | 141 |

| 5.4.2  | Real Position Counter Reading                           | 141 |

| 5.4.3  | Current Drive Speed Reading                             | 141 |

| 5.4.4  | Current Acceleration / Deceleration Reading             | 142 |

| 5.4.5  | Multi-Purpose Register 0 Reading                        | 142 |

| 5.4.6  | Multi-Purpose Register 1 Reading                        | 142 |

| 5.4.7  | Multi-Purpose Register 2 Reading                        | 142 |

| 5.4.8  | Multi-Purpose Register 3 Reading                        | 143 |

| 5.4.9  | Current Timer Value Reading                             | 143 |

| 5.4.10 | WR1 Setting Value Reading                               | 143 |

| 5.4.11 | WR2 Setting Value Reading                               | 143 |

| 5.4.12 | WR3 Setting Value Reading                               | 144 |

| 5.4.13 | Multi-Purpose Register Mode Setting Reading             | 144 |

| 5.4.14 | PIO Signal Setting 1 Reading                            | 144 |

| 5.4.15 | PIO Signal Setting 2 Reading                            | 144 |

| 5.4.16 | Acceleration Setting Value Reading                      | 145 |

| 5.4.17 | Initial Speed Setting Value Reading                     | 145 |

| 5.4.18 | Drive Speed Setting Value Reading                       | 145 |

| 5.4.19 | Drive Pulse Number / Finish Point Setting Value Reading | 145 |

| 5.4.20 | Split Pulse Setting 1 Reading                           | 146 |

| 5.5 D  | Priving Commands                                        | 147 |

| 5.5.1  | Relative position driving                               | 147 |

| 5.5.2  | Counter relative position driving                       | 148 |

| 5.5.3  | + Direction continuous pulse driving                    | 148 |

| 5.5.4  | - Direction continuous pulse driving                    | 148 |

| 5.5.5  | Absolute position driving                               | 149 |

| 5.5.6  | Decelerating Stop                                       | 149 |

| 5.5.7  | Instant Stop                                            | 149 |

| 5.5.8  | Direction Signal + Setting                              | 149 |

| 5.5.9  | Direction Signal - Setting                              | 150 |

| 5.5.10 | Automatic Home Search Execution                         | 150 |

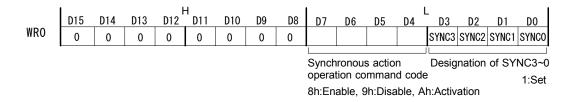

| 5.6 Synchronous Action Operation Commands                              | 151 |

|------------------------------------------------------------------------|-----|

| 5.6.1 Synchronous Action Enable Setting                                |     |

| 5.6.2 Synchronous Action Disable Setting                               |     |

| 5.6.3 Synchronous Action Activation                                    |     |

| 5.7 Other Commands                                                     |     |

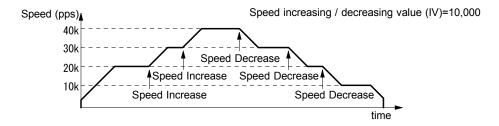

| 5.7.1 Speed Increase                                                   |     |

| 5.7.2 Speed Decrease                                                   |     |

| 5.7.3 Deviation Counter Clear Output                                   |     |

| 5.7.4 Timer-Start 5.7.5 Timer-Stop                                     |     |

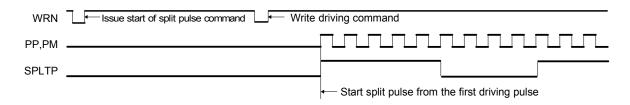

| 5.7.6 Start of Split Pulse                                             |     |

| 5.7.7 Termination of Split Pulse                                       |     |

| 5.7.8 Error / Finishing Status Clear                                   |     |

| 5.7.9 NOP                                                              |     |

| 5.7.10 Command Reset                                                   |     |

|                                                                        |     |

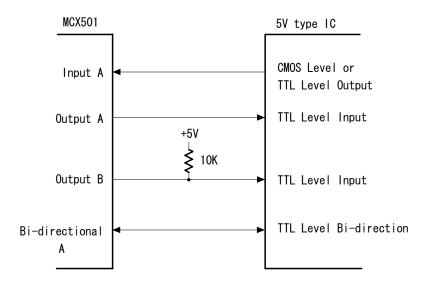

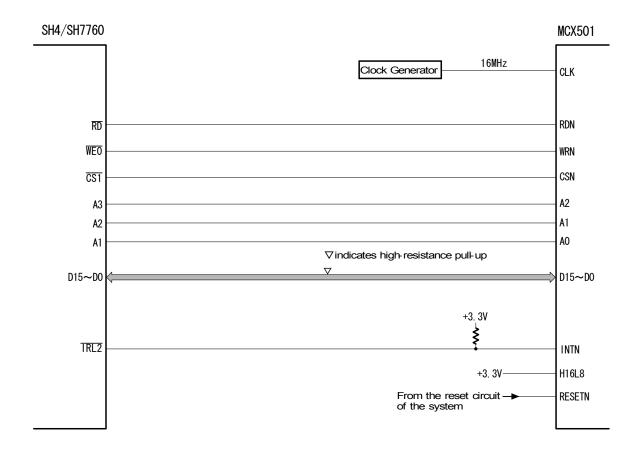

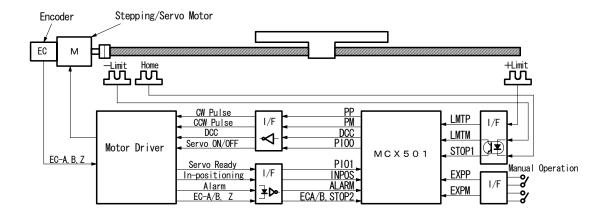

| 6. Connection Examples                                                 | 150 |

| 6.1 Example of Connection with SH-4 CPU                                |     |

| 6.2 Connection Example                                                 | 157 |

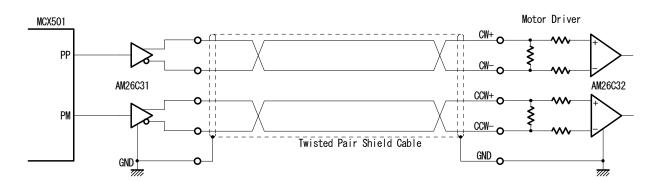

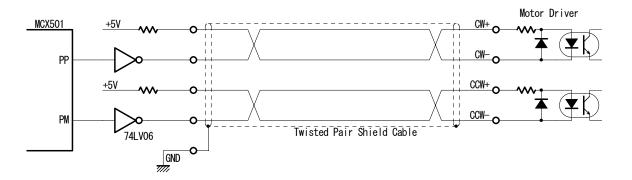

| 6.3 Pulse Output Interface                                             |     |

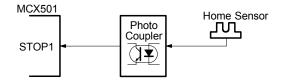

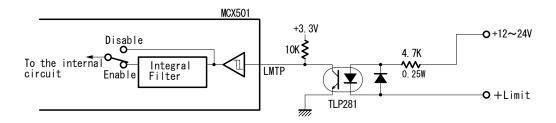

| 6.4 Connection Example for Input Signals                               |     |

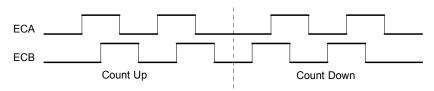

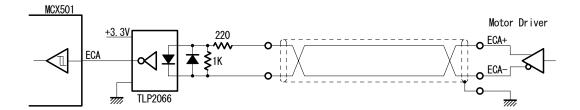

| 6.5 Connection Example for Encoder                                     | 158 |

| 7. Example Program                                                     | 159 |

|                                                                        |     |

| 8. Electrical Characteristics                                          | 169 |

| 8.1 DC Characteristics                                                 | 169 |

| 8.2 AC Characteristics                                                 |     |

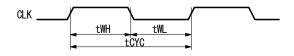

| 8.2.1 Clock                                                            | 170 |

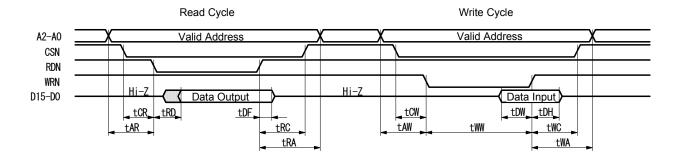

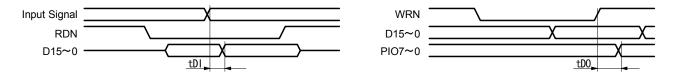

| 8.2.2 Read / Write Cycle                                               | 170 |

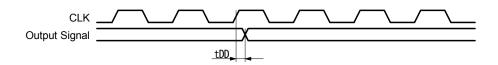

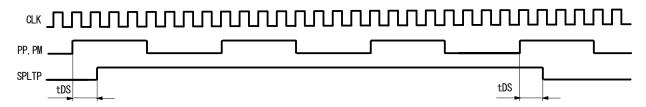

| 8.2.3 CLK / Output Signal Timing                                       | 171 |

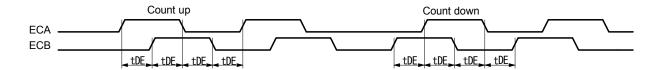

| 8.2.4 Input Pulses                                                     | 171 |

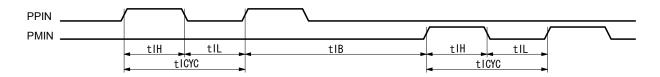

| 8.2.5 General Purpose Input / Output Signals (PIO7~0)                  | 172 |

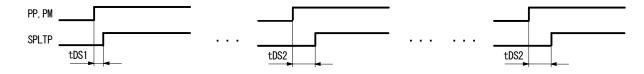

| 8.2.6 Split Pulse                                                      | 172 |

| 9. Timing of Input / Output Signals                                    | 173 |

|                                                                        |     |

| 9.1 Power-On Reset                                                     | 173 |

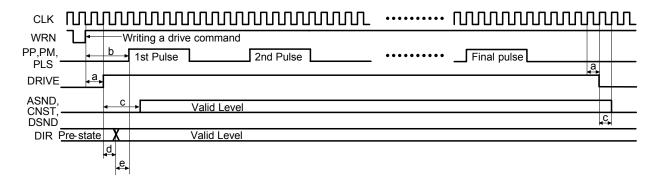

| 9.2 Fixed Pulse or Continuous Pulse Driving                            |     |

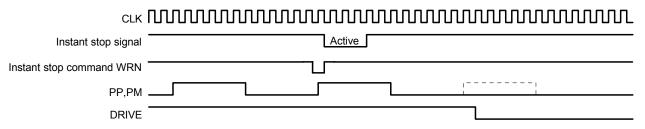

| 9.3 Instant Stop                                                       |     |

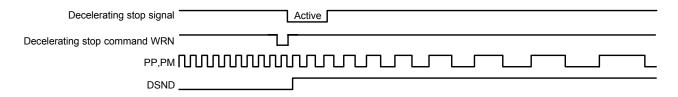

| 9.4 Decelerating Stop                                                  |     |

|                                                                        |     |

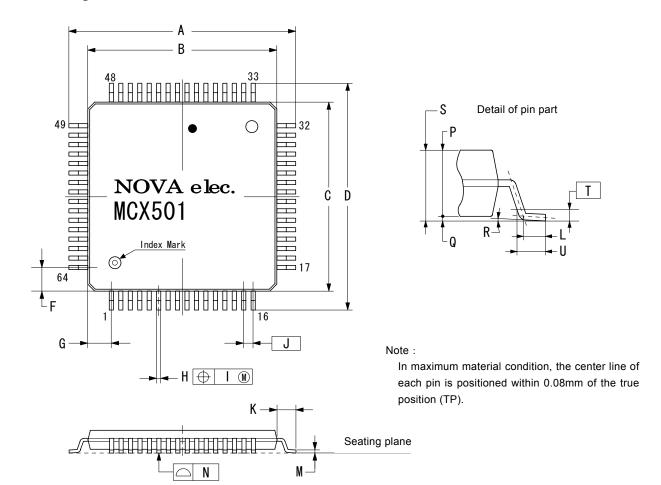

| 10. Package Dimensions                                                 | 175 |

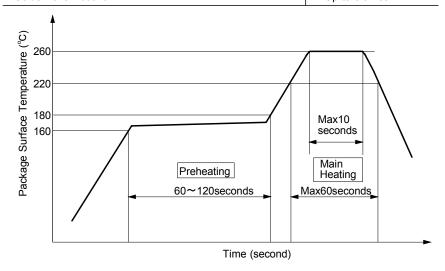

| 11 Storage and Decommended Installation Conditions                     | 177 |

| 11. Storage and Recommended Installation Conditions                    | 1// |

| 11.1 Storage of this IC                                                | 177 |

| 11.2 Standard Installation Conditions by Soldering Iron                | 177 |

| 11.3 Standard Installation Conditions by Solder Reflow                 | 177 |

|                                                                        |     |

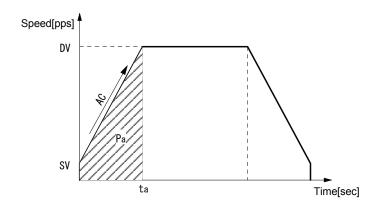

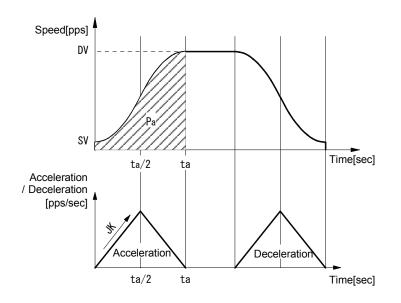

| Appendix A Calculation Formula of Acceleration/Deceleration Drive      | A-1 |

| ••                                                                     |     |

| A-1 Case of Trapezoidal Acceleration/Deceleration Driving              |     |

| -                                                                      |     |

| Appendix B Parameter Calculation Formula when Input Clock except 16MHz | B-1 |

| Annondis C Differences with MCV200 estimate                            | 0.4 |

| Appendix C Differences with MCX300 series                              | C-1 |

# Update history

# Nov/14/2012

Revised for the reason of a literal error.

# 1. OUTLINE

#### 1.1 The Main Features of Functions

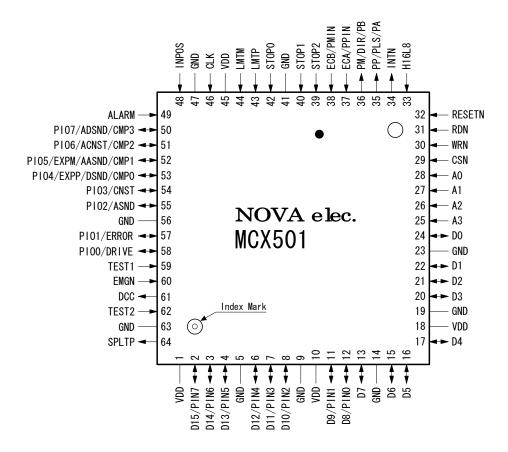

MCX501 is 1-axis motion control IC which connects to the master CPU with 8-bit or 16-bit bus and can control either a stepper motor driver or pulse type servo driver for position and speed.

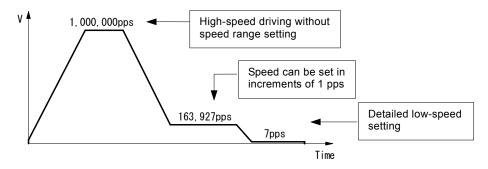

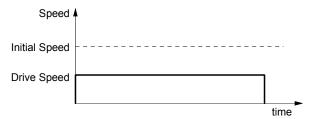

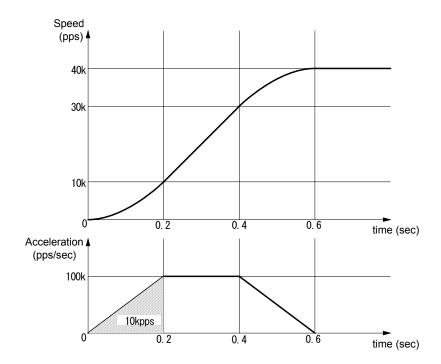

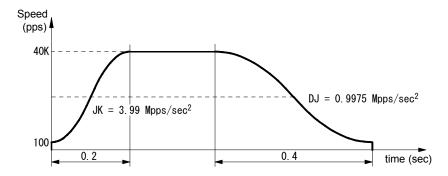

This IC has no multiple of speed (Range Setting) to set the drive speed, that is to say it can freely output the drive speed from 1 pps up to 8 Mpps in increments of 1pps. Acceleration/deceleration driving can perform trapezoidal acceleration/deceleration and smooth S-curve acceleration/deceleration.

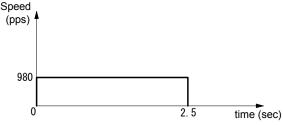

# Speed Range-Free

MCX501 is a new motion control IC that has no multiple of speed (Range Setting) to set the drive speed. This will enable us to freely set the speed from 1 pps up to 8 Mpps in increments of 1 pps.

When using the multiples of speed to set the speed by existing method, there are restrictions as described below.

- For the detaild speed setting of low-speed, less multiples of speed must be set.

- → As a result, driving cannot be shifted to high-speed.

- To perform the high-speed driving, larger multiples of speed must be set.

- → As a result, the detaild setting of drive speed cannot be configured.

MCX501 brings solutions to the inconvenience described above by Speed range-free, which makes it possible to directly change the speed from low-speed such as 1 or 2 pps to high-speed such as 1 Mpps during the driving.

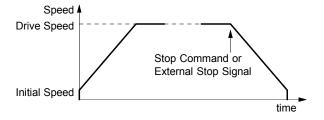

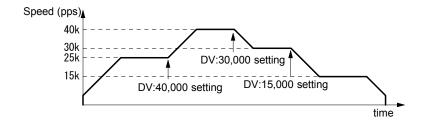

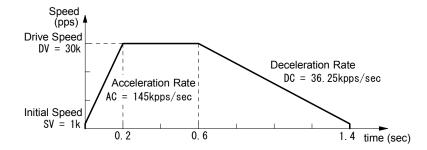

Fig. 1.1-1 Speed Range-Free

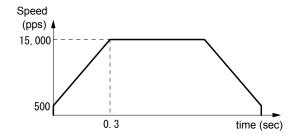

# ■ Easy and High-Accuracy Speed Setting

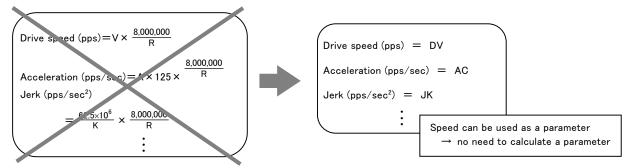

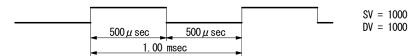

Since there is no need to set multiples of speed (Range Setting), the user can set a drive speed of output pulses as a speed parameter (at CLK = 16MHz).

Fig. 1.1-2 Speed Parameter Setting

In the range of 1 pps to 8 Mpps, it can output the drive speed that is set with high accuracy. Speed accuracy of the pulse output is less than  $\pm$  0.1%, which is on the assumption that there is no frequency error of input clock (CLK). In fact, there is a frequency error of input clock (CLK), and speed accuracy depends on it.

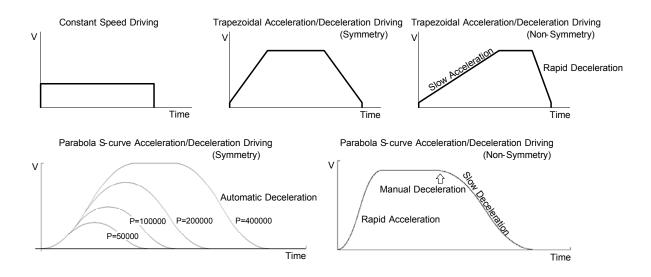

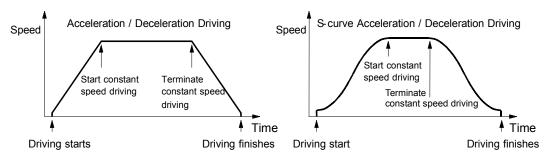

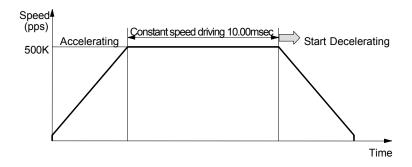

# Various Acceleration / Deceleration Drive Mode

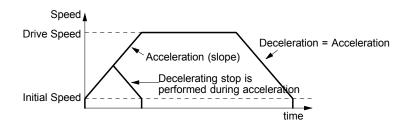

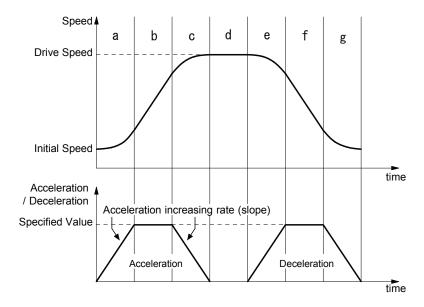

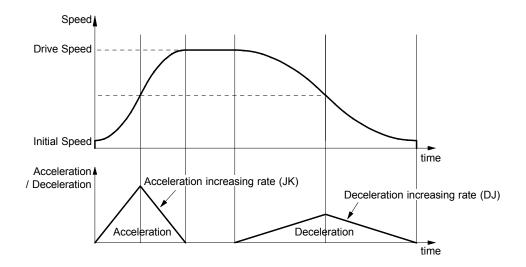

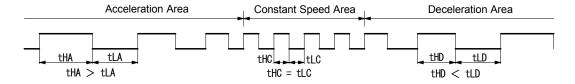

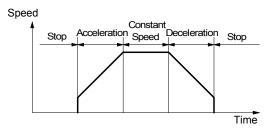

#### ◆ Types of acceleration/deceleration driving

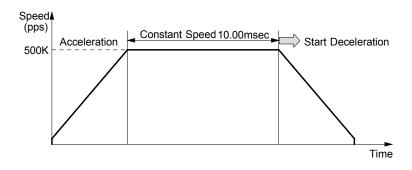

Acceleration/deceleration driving can perform the following driving.

Constant speed driving

Linear acceleration/deceleration driving (symmetry/non-symmetry)

S-curve acceleration/deceleration driving (symmetry/non-symmetry)

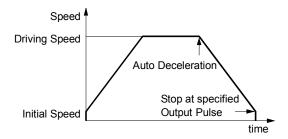

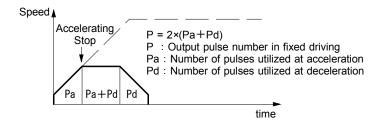

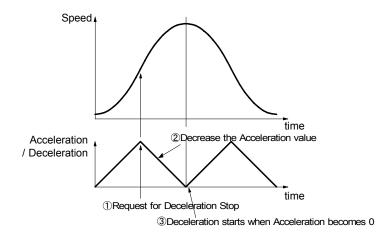

#### Automatic deceleration start

In position driving of linear acceleration/deceleration (symmetry) and S-curve acceleration/deceleration (symmetry), the IC calculates the deceleration start point when in deceleration, and automatically starts deceleration. (This is not applied to non-symmetry S-curve acceleration/deceleration driving.)

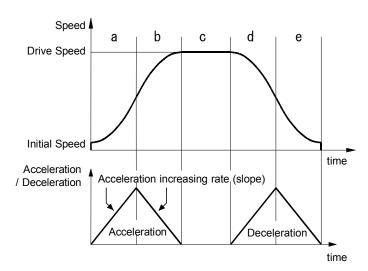

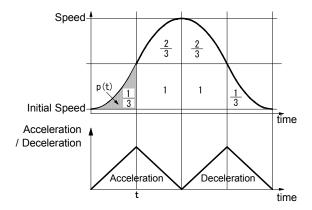

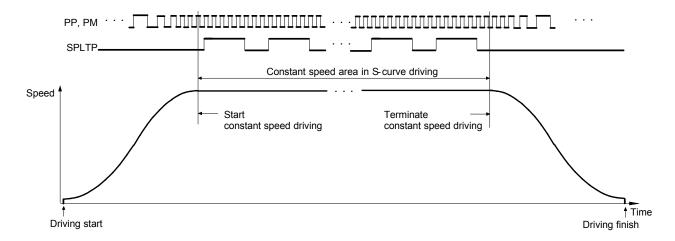

#### ◆ S-curve acceleration/deceleration curve

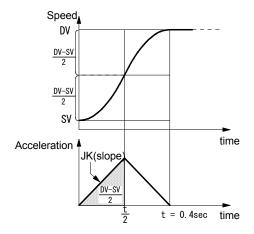

S-curve acceleration/deceleration uses the method which increases/decreases acceleration or deceleration in a primary line, and the speed curve forms a secondary parabola acceleration/deceleration. In addition, it prevents triangle waveforms by a special method during S-curve acceleration/deceleration.

Fig. 1.1-3 Acceleration / Deceleration Drive Mode

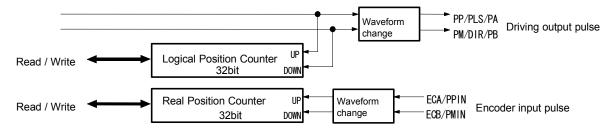

# ■ Position Control

MCX501 has two 32-bit position counters: one is a logical position counter that counts the number of output pulses and the other is a real position counter that counts the feedback number of pulses from an external encoder.

The current position can be read by data reading commands anytime.

By using with synchronous action, the operation by the activation factor based on position data, such as a timer starts/stops at a specified position, can be performed.

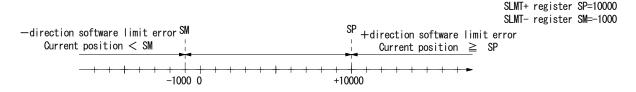

# Software Limit

MCX501 has a software limit function that controls driving to stop when the position counter is over a specified range. There are 2 stop types for when the software limit function is enabled: decelerating stop and instant stop.

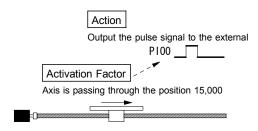

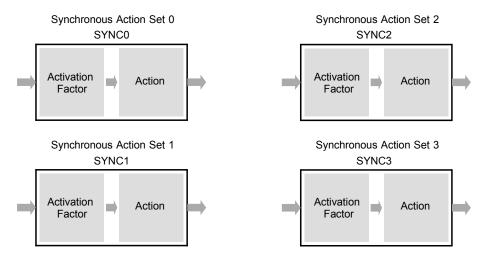

# Various Synchronous Actions

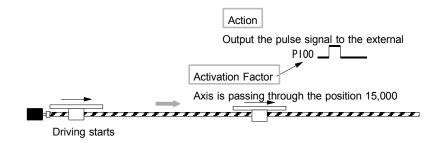

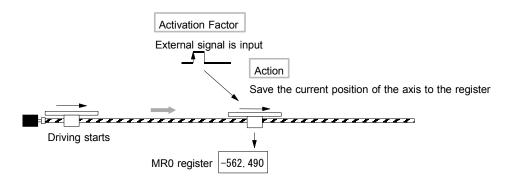

Synchronous action is the function that executes a specified action together with if a specified activation factor generates. These synchronous actions can be performed fast and precisely, independent of the CPU.

Synchronous action is possible to set up to 4 sets.

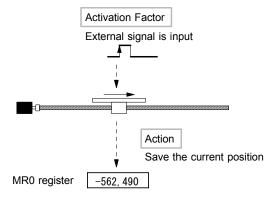

1 set of synchronous actions is configured with one specified activation factor and one specified action. 15 types of activation factors are provided, such as the passage of a specified position, start/termination of driving, the rising/falling edge of an external signal and expiring of an internal timer. In addition, 28 types of actions are provided, such as start/termination of driving, save the current position counter value to multi-purpose register and writing of a drive speed.

Multiple synchronous action sets can be used in combination, which allows users to develop a wide array of applications.

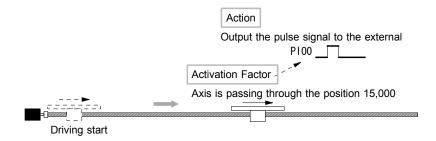

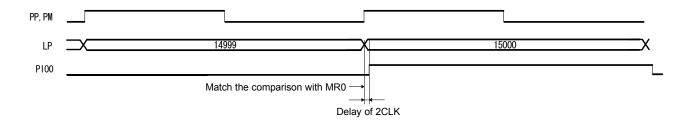

Fig. 1.1-4 Synchronous Action

## Examples

- Outputs an external signal when passing through a specified position during the driving.

- Saves the current position to a specified register when an external signal is input during the driving.

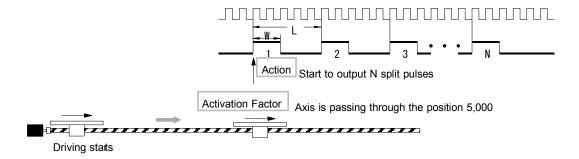

- Outputs N split pulses from a specified position to the external during the driving.

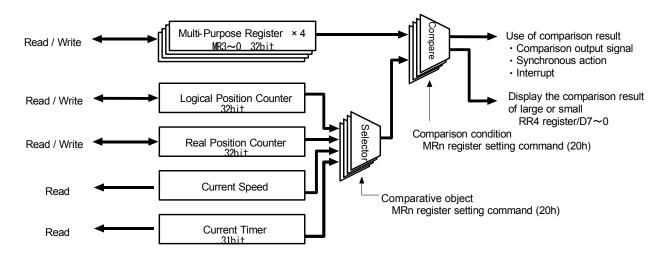

# ■ Four Multi-Purpose Registers

MCX501 has four 32-bit length multi-purpose registers.

Multi-purpose register can be used to compare with the current position, speed and timer, and then can read out the status which represents comparison result and can output as a signal. In addition, it can activate a synchronous action according to comparison result or can generate an interrupt.

By using with synchronous action, it can save values of the position or current speed during the driving to multi-purpose registers and load values to parameters from multi-purpose registers.

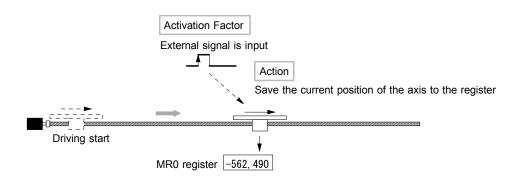

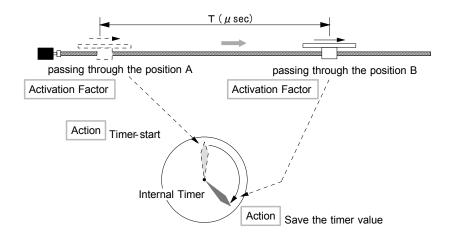

# ■ Timer Function

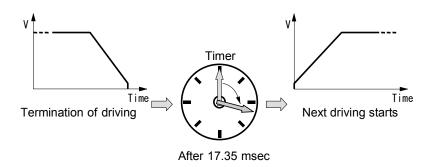

MCX501 is equipped with the timer which can set with the range of  $1 \sim 2,147,483,647 \,\mu$  sec in increments of  $1 \,\mu$  sec (at CLK = 16MHz). By using with synchronous action, the following operations can be performed precisely.

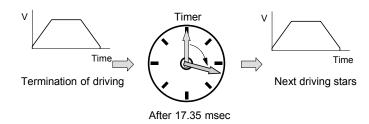

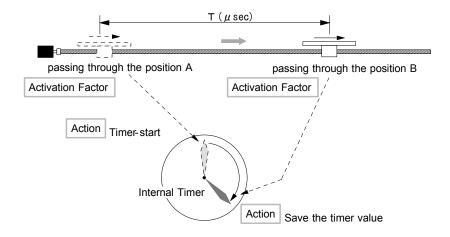

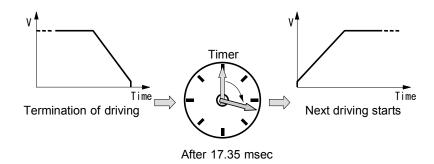

Fig. 1.1-5 Timer Function

#### Examples

- Starts driving after specified periods when the driving is finished.

- Starts driving after specified periods after an external signal is input.

- Stops continuous pulse driving after specified periods.

- Times from position A to position B.

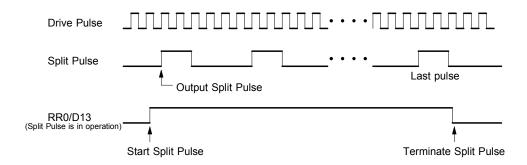

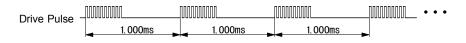

# Output of Split Pulse

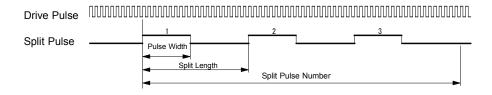

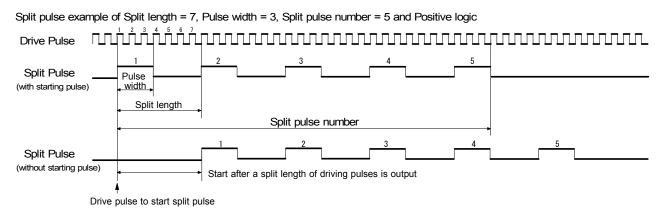

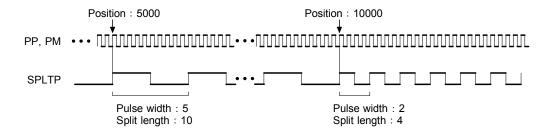

This is a function that outputs split pulses during the driving, which synchronizes axis driving and performs various operations in the specified intervals.

The split length, pulse width of a split pulse and split pulse number can be set. By using with synchronous action, the output of split pulses can be started/terminated from a specified position and the split length or pulse width of a split pulse can be changed by an external signal.

Fig. 1.1-6 Split Pulse Output

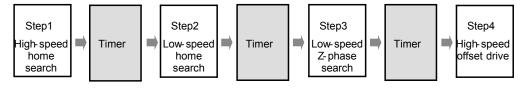

# Automatic Home Search Function

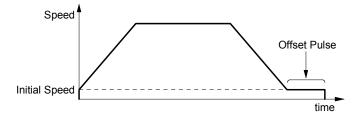

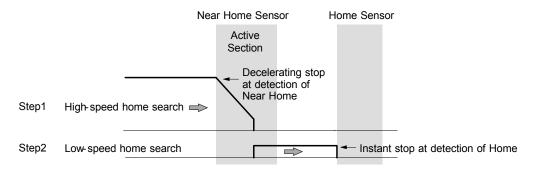

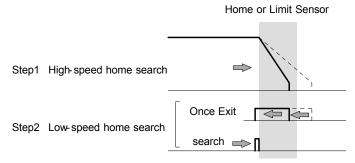

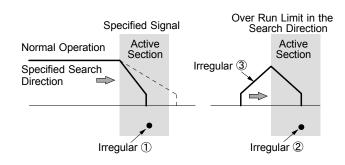

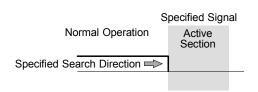

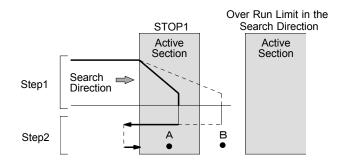

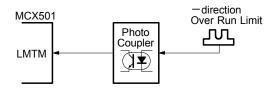

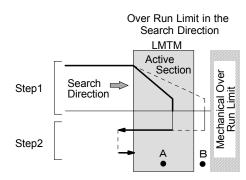

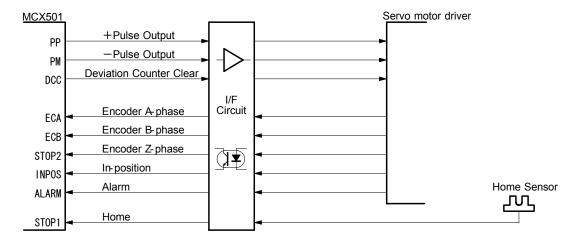

This IC is equipped with the function that automatically executes a home search sequence without CPU intervention. The sequence comprises high-speed home search  $\rightarrow$  low-speed home search  $\rightarrow$  encoder Z-phase search  $\rightarrow$  offset drive.

Deviation counter clear pulses can be output for a servo motor driver. In addition, the timer between steps which sets stop time among each step is available, and the operation for a home search of a rotation axis is provided.

# ■ Servo Motor Feedback Signals

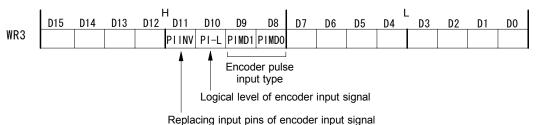

MCX501 has input pins for servo feedback signals such as encoder 2-phase, in-positioning and alarm signals. An output signal for clearing a deviation counter is also available.

# Interrupt Signals

Interrupt signals can be generated by various factors. For example, (1). at the start/finish of a constant speed drive during the acceleration/deceleration driving, (2). at the end of driving, and (3). when the comparison result of a multi-purpose register with a position counter changes.

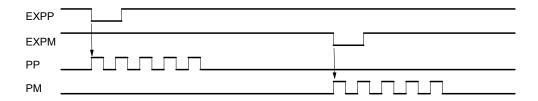

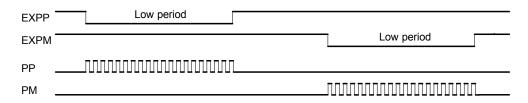

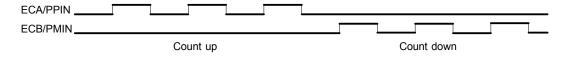

# Driving by External Signals

Driving can be controlled by external signals, which are the relative position driving, continuous pulse driving and MPG driving. This function is used for JOG feed or teaching mode, reducing the CPU load and making operations smooth.

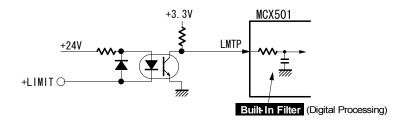

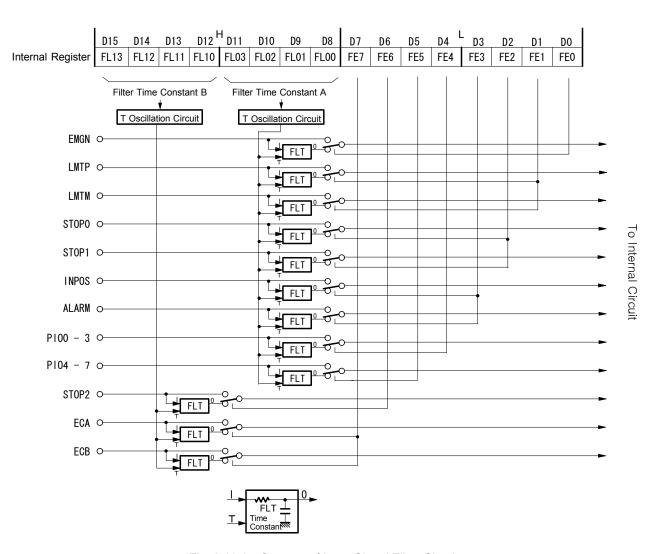

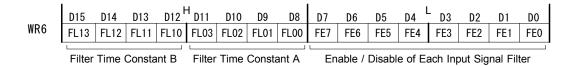

# ■ Built-in Input Signal Filter

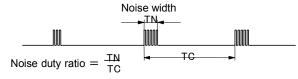

The IC is equipped with an integral type filter in the input step of each input signal. It is possible to set for each input signal whether the filter function is enabled or the signal is passed through. A filter time constant can be selected from 16 types  $(500 \text{nsec} \sim 16 \text{msec})$ .

Fig. 1.1-7 Built-in Input Signal Filter

# Real Time Monitoring

During the driving, the current status such as logical position, real position, drive speed, acceleration/deceleration, status of accelerating/constant speed driving/decelerating/acceleration increasing/acceleration constant/acceleration decreasing and a timer can be read in real time.

# ■ 8 or 16 Bits Data Bus Selectable

MCX501 can be connected to either 8-bit or 16-bit CPU.

If 8-bit data bus is used, eight pins which are not used for the data bus can be used as general purpose input signals.

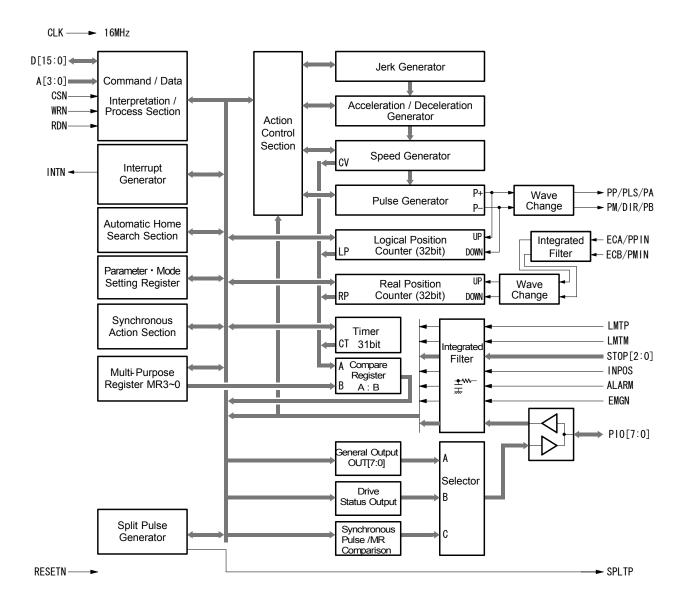

# 1.2 Functional Block Diagram

MCX501 functional block diagram is shown as below.

Fig. 1.2-1 MCX501 Functional Block Diagram

# 1.3 Specification Table

(CLK=16MHz)

| Item             | Subitem                   | Description (CLK – 10)                                                             | Note |

|------------------|---------------------------|------------------------------------------------------------------------------------|------|

| Control Axis     |                           | 1-axis                                                                             |      |

| Data Bus         |                           | 16/8-bit selectable                                                                |      |

| Drive Pulses     | Drive Speed Range         | 1 pps ~ 8,000,000 pps                                                              |      |

| Output           |                           | (When CLK=20MHz: up to 10,000,000 pps)                                             |      |

|                  | Initial Speed Range       | 1 pps ~ 8,000,000 pps                                                              |      |

|                  | Pulse Output Accuracy     | ± 0.1% or less (according to the setting speed)                                    |      |

|                  | Acceleration Range        | 1 pps/sec ~ 536,870,911pps/sec                                                     |      |

|                  | Acceleration Increasing/  | 1 pps/sec <sup>2</sup> ~ 1,073,741,823 pps/sec <sup>2</sup>                        | +4   |

|                  | Decreasing Rate Range     |                                                                                    | *1   |

|                  | Acceleration/Deceleration | Constant speed,                                                                    |      |

|                  | Curve                     | Symmetrical/non-symmetrical linear acceleration/deceleration,                      |      |

|                  |                           | Symmetrical/non-symmetrical parabola S-curve acceleration/                         |      |

|                  |                           | deceleration                                                                       |      |

|                  | Drive Pulse Range         | •Relative position driving : -2,147,483,646 ~ 2,147,483,646                        | *2   |

|                  |                           | -Absolute position driving : -2,147,483,646 ~ 2,147,483,646                        |      |

|                  | Position Driving          | Automatic decelerating stop                                                        | *3   |

|                  | Decelerating Stop Mode    | Manual decelerating stop                                                           | 3    |

|                  | Override                  | Output pulse number and drive speed are changeable during the                      | *4   |

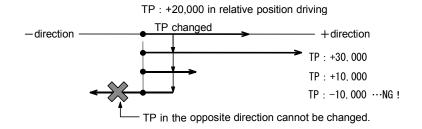

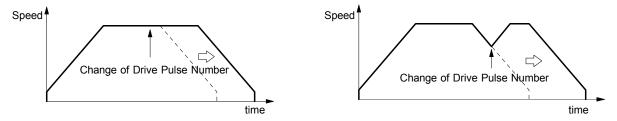

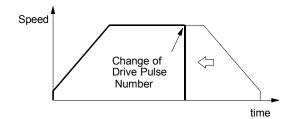

|                  |                           | driving                                                                            | 4    |