# FILE MANAGEMENT OF A USB FLASH DRIVE AND MEMORY CARD VIA MICRO SD CARD SLOT OF A MOBILE PHONE

By

Meryl Filomena B. Coching Kristine Doctor Francis Mark V. Evangelista Lynda Clarissa C. Santos

A Design Report Submitted to the School of Electrical Engineering, Electronics Engineering, and Computer Engineering in Partial Fulfilment of the Requirements for the Degree

# **Bachelor of Science in Computer Engineering**

Mapua Institute of Technology October 2011

#### Approval Sheet

### Mapua Institute of Technology School of EE-ECE-CoE

This is to certify that we have supervised the preparation of and read the design report prepared by Meryl Anne Filomena B. Coching, Kristine Doctor, Francis Mark V. Evangelista and Lynda Clarissa C. Santos entitled File Management of a USB Flash Drive and Memory Card via Micro SD Card Slot of a Mobile Phone and that the said report has been submitted for final examination by the Oral Examination Committee.

Felicito S. Caluyo

Design Adviser

As members of the Oral Examination Committee, we certify that we have examined this design report presented before the committee on **October 3**, **2011**, and hereby recommend that it be accepted as fulfilment of the design requirement for the degree in **Bachelor of Science in Computer Engineering**.

Ernesto M. Vergara Jr. Panel Member

M. annon hone Ramon G. Garcia

Panel Member

Marianne M. Sejera Chairman

This design is hereby approved and accepted by the School of Electrical Engineering, Electronics and Communications Engineering, and Computer Engineering as fulfilment of the design requirement for the degree in **Bachelor** of Science in Computer Engineering.

Feliat S

Felicito S. Caluyo Dean, School of EE-ECE-CoE

ii

# **TABLE OF CONTENTS**

| Objectives of the Design<br>Impact of the Design<br>Design Constraints<br>Definition of terms<br>Chapter 2: REVIEW OF RELATED LITERATURE AND RELATED STUDIES<br>Chapter 3: DESIGN PROCEDURES<br>Conceptual Diagram<br>Block Diagram<br>Schematic Diagram<br>Program Flowchart<br>Prototype Development<br>Chapter 4: TESTING, PRESENTATION, AND INTERPRETATION OF DATA<br>Chapter 5: CONCLUSION AND RECOMMENDATION<br>Conclusion<br>Recommendation                                                                                                   | ITLE PAGE                                                                                        | i                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------|

| LIST OF TABLES LIST OF FIGURES ABSTRACT Chapter 1: DESIGN BACKGROUND AND INTRODUCTION Background Statement of the Problem Objectives of the Design Impact of the Design Design Constraints Definition of terms Chapter 2: REVIEW OF RELATED LITERATURE AND RELATED STUDIES Chapter 3: DESIGN PROCEDURES Conceptual Diagram Block Diagram Schematic Diagram Program Flowchart Prototype Development Chapter 4: TESTING, PRESENTATION, AND INTERPRETATION OF DATA Chapter 5: CONCLUSION AND RECOMMENDATION Conclusion Recommendation BIBLIOGRAPHY      | PPROVAL SHEET                                                                                    | ii                         |

| LIST OF FIGURES ABSTRACT Chapter 1: DESIGN BACKGROUND AND INTRODUCTION Background Statement of the Problem Objectives of the Design Impact of the Design Design Constraints Definition of terms Chapter 2: REVIEW OF RELATED LITERATURE AND RELATED STUDIES Chapter 3: DESIGN PROCEDURES Conceptual Diagram Block Diagram Schematic Diagram Program Flowchart Prototype Development Chapter 4: TESTING, PRESENTATION, AND INTERPRETATION OF DATA Chapter 5: CONCLUSION AND RECOMMENDATION Conclusion Recommendation BIBLIOGRAPHY                     | ABLE OF CONTENTS                                                                                 | iii                        |

| ABSTRACT<br>Chapter 1: DESIGN BACKGROUND AND INTRODUCTION<br>Background<br>Statement of the Problem<br>Objectives of the Design<br>Impact of the Design<br>Design Constraints<br>Definition of terms<br>Chapter 2: REVIEW OF RELATED LITERATURE AND RELATED STUDIES<br>Chapter 3: DESIGN PROCEDURES<br>Conceptual Diagram<br>Block Diagram<br>Program Flowchart<br>Prototype Development<br>Chapter 4: TESTING, PRESENTATION, AND INTERPRETATION OF DATA<br>Chapter 5: CONCLUSION AND RECOMMENDATION<br>Conclusion<br>Recommendation<br>BIBLIOGRAPHY | IST OF TABLES                                                                                    | v                          |

| Chapter 1: DESIGN BACKGROUND AND INTRODUCTION Background Statement of the Problem Objectives of the Design Impact of the Design Design Constraints Definition of terms Chapter 2: REVIEW OF RELATED LITERATURE AND RELATED STUDIES Chapter 3: DESIGN PROCEDURES Conceptual Diagram Block Diagram Schematic Diagram Program Flowchart Prototype Development Chapter 4: TESTING, PRESENTATION, AND INTERPRETATION OF DATA Chapter 5: CONCLUSION AND RECOMMENDATION Conclusion Recommendation BIBLIOGRAPHY                                              | IST OF FIGURES                                                                                   | vi                         |

| Background<br>Statement of the Problem<br>Objectives of the Design<br>Impact of the Design<br>Design Constraints<br>Definition of terms<br>Chapter 2: REVIEW OF RELATED LITERATURE AND RELATED STUDIES<br>Chapter 3: DESIGN PROCEDURES<br>Conceptual Diagram<br>Block Diagram<br>Schematic Diagram<br>Program Flowchart<br>Prototype Development<br>Chapter 4: TESTING, PRESENTATION, AND INTERPRETATION OF DATA<br>Chapter 5: CONCLUSION AND RECOMMENDATION<br>Conclusion<br>Recommendation                                                         | BSTRACT                                                                                          | vii                        |

| Statement of the Problem<br>Objectives of the Design<br>Impact of the Design<br>Design Constraints<br>Definition of terms<br>Chapter 2: REVIEW OF RELATED LITERATURE AND RELATED STUDIES<br>Chapter 3: DESIGN PROCEDURES<br>Conceptual Diagram<br>Block Diagram<br>Schematic Diagram<br>Program Flowchart<br>Prototype Development<br>Chapter 4: TESTING, PRESENTATION, AND INTERPRETATION OF DATA<br>Chapter 5: CONCLUSION AND RECOMMENDATION<br>Conclusion<br>Recommendation                                                                       | hapter 1: DESIGN BACKGROUND AND INTRODUCTION                                                     | 1                          |

| Chapter 3: DESIGN PROCEDURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | tatement of the Problem<br>Objectives of the Design<br>Mpact of the Design<br>Design Constraints | 1<br>2<br>3<br>4<br>5<br>6 |

| Conceptual Diagram<br>Block Diagram<br>Schematic Diagram<br>Program Flowchart<br>Prototype Development<br>Chapter 4: TESTING, PRESENTATION, AND INTERPRETATION OF DATA<br>Chapter 5: CONCLUSION AND RECOMMENDATION<br>Conclusion<br>Recommendation                                                                                                                                                                                                                                                                                                   | hapter 2: REVIEW OF RELATED LITERATURE AND RELATED STUDIES                                       | 8                          |

| Block Diagram       2         Schematic Diagram       2         Program Flowchart       2         Prototype Development       2         Chapter 4: TESTING, PRESENTATION, AND INTERPRETATION OF DATA       2         Chapter 5: CONCLUSION AND RECOMMENDATION       4         Conclusion       4         Recommendation       4                                                                                                                                                                                                                      | hapter 3: DESIGN PROCEDURES                                                                      | 21                         |

| Chapter 5: CONCLUSION AND RECOMMENDATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | lock Diagram<br>chematic Diagram<br>rogram Flowchart                                             | 21<br>23<br>25<br>28<br>30 |

| Conclusion 2<br>Recommendation 2<br>BIBLIOGRAPHY 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | hapter 4: TESTING, PRESENTATION, AND INTERPRETATION OF DATA                                      | 36                         |

| Recommendation 24<br>BIBLIOGRAPHY 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | hapter 5: CONCLUSION AND RECOMMENDATION                                                          | 45                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                  | 45<br>46                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IBLIOGRAPHY                                                                                      | 47                         |

| AFFLINDIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PPENDIX                                                                                          | 49                         |

| A. Operation's Manual                    | 49  |

|------------------------------------------|-----|

| 1. System Requirement                    | 49  |

| 2. Installation Procedure                | 49  |

| 3. User's Manual                         | 50  |

| 4. Troubleshooting Guides and Procedures | 51  |

| 5. Error Definitions                     | 52  |

| B. Complete Set of Data Sheets           | 53  |

| C. Program Listing                       | 100 |

| D. Pictures of Prototype                 | 102 |

| E. IEEE Format Article of the Design     | 104 |

# **List of Tables**

| Table 4.1: File Copy Speed Test Results using Phone Model<br>Nokia C3 at file size of 1 MB  | 38 |

|---------------------------------------------------------------------------------------------|----|

| Table 4.2: File Copy Speed Test Results using Phone Model<br>Nokia C3 at file size of 10 MB | 40 |

| Table 4.3: Average Transfer Speed at 1 MB and 10 MB                                         | 41 |

| Table 4.4: Variance and Standard Deviation at 1 MB and 10 MB                                | 42 |

# List of Figures

| Figure 3.1: Conceptual Diagram of the Design | 21 |

|----------------------------------------------|----|

| Figure 3.2: Block Diagram of the Design      | 23 |

| Figure 3.3: Schematic Diagram of the Design  | 25 |

| Figure 3.4: Program Flowchart                | 28 |

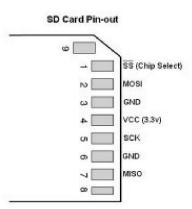

| Figure 3.5: SD Memory Card Slot & Pin-out    | 32 |

| Figure 3.6: micro SD Sniffer                 | 34 |

# ABSTRACT

Most of modern mobile phones have a micro SD slot that is used for expanded storage. Inspired by the recently released Nokia N8 which has a USB On-the-Go feature that allows a flash drive to be connected via a cable used, the researchers constructed a design wherein the micro SD slot is used as a pathway to incorporate the USB port and the memory card port/s. The purpose of the design is to give the mobile phone additional storage and to access/transfer data using another media, in substitute for desktop PCs particularly. The flash drive to be used should comply with USB 2.0 and the memory card is limited to SD/mini SD with maximums of 2GB and 4GB total space limit respectively. The device is intended for mobile phones with a micro SD slot. The major hardware components of the design consist of SD memory slots, USB to SDIO Bridge Chip Host interface Transfer for the USB flash drive, relay circuits and a microcontroller which is programmed for port switching and a micro SD sniffer for the main output device. The single file copy speed test is conducted to test the functionality of the device. The transfer speeds for each flash memory are also looked upon and was observed that compared to the theoretical data transfer rates for the USB flash drive and SD memory card to the computer, the data transfer rates from the said flash memories with respect to the researchers device are acceptable. After testing the prototype, the researchers satisfied the assumptions that the file management is successful and the file integrity is preserved.

Keywords: micro SD, USB 2.0, USB On-the-Go, SD memory card, File Transfer

#### Chapter 1

#### **DESIGN BACKGROUND AND INTRODUCTION**

### Background

Mobile phones have limited capabilities to access storage devices such as thumb drives and other memory cards that do not fit into the phone except card slots installed on the phone. Most of phones today have micro SD memory card slots installed. Almost all people nowadays have mobile phones, and almost all people have the need to transfer files quickly and want to ensure that data are successfully sent. As of now, the available media to send files are via infrared, Bluetooth, and one card slot that depends on what is installed on the phone. But what if the files needed are saved on a USB flash drive, SD memory card or mini SD memory card? Let's say one's phone only accepts a micro SD memory card. One solution is to have a computer to access files to transfer to one's phone. Not all people carry their laptops all the time; or to have access to a PC.

A memory card (sometimes called a flash memory card or a storage card) is a small storage medium used to store data such as text, pictures, audio, and video, for use on small, portable or remote computing devices. Most of the current products use flash memory, although other technologies are being developed. Memory cards offer a number of advantages over the hard disk drive: they're much smaller and lighter, extremely portable, completely silent, allow more immediate access, and are less prone to mechanical damage. A USB flash drive is portable memory storage. It is re-writeable and holds its memory without a power supply, unlike RAM. USB flash drives will fit into any USB port on a computer. For a USB flash drive to function, it needs a host controller. Just like a PC, all flash drives have a storage device controller for it to read the device. This functionality is lacking in mobile phones since phones do not have a USB host controller.

This design is intended for on the go use. The user can simply insert the storage device and can easily manage files on their phones and the storage device. The phone will read the storage device as a memory card that is inserted in its memory card slot. Only one storage device can be read at a given time. To do this, there is a switch for every device wherein the users can mount the storage device they want to use. The design has a switching capability to choose what device is mounted.

The major components of this design are the SD card slots and USB flash drive slot wherein the user can insert a storage device. The design has a micro SD card sniffer so that the phone can access the storage inserted through this micro SD card sniffer. Switching components are used to access just one USB flash drive or either one of the memory cards at a time, because phones have a limited capability to read simultaneously storage devices.

#### **Statement of the Problem**

Being students of Mapua Institute of Technology, the researchers continue to find ways to make life easy by innovating current technology advancements. This study's topic is mainly concerned with portable storage devices and mobile

2

phones. There is a need for a multi-purpose USB plus memory card reader/writer to host demanding storage applications and on-the-go access of the data.

The design is inspired by the fact that modern mobile phones like smart phones use the general purpose micro SD slot for data storage which limits the capability of the mobile phone to store data on other portable storage media like flash drives or other memory cards. Additionally, USB OTG (on-the-go) which is used by Nokia N8 to access/transfer data using a flash drive is limited only in their platform while other manufacturers of mobile phones do not incorporate such technology in their devices.

### **Objectives of the Design**

The main objective of this study is to design and construct a device that can manage files in a USB flash drive and memory card in a mobile phone via its micro SD card slot". Its specific objectives are as follows:

To construct the main circuitry of the device which will consist of the design's input, process, and output.

To create the prototype that will be able to route the data inside the flash memory for a specific destination.

To create a program that will make the device capable of responding to the user's selection of which flash memory device is to be activated in the mobile phone.

To test if the device is capable of managing files between the mobile phone and the activated flash memory device. To verify that the data transferred to and from the device is intact with no corruption.

## Impact of the design

The significance of this design is to provide people a flexible way of transferring data. Mobile phones are limited to the use of memory cards, although nowadays some mobile phones have a micro USB port that supports USB OTG (on-the-go) that allows USB flash drives including external hard drives to be connected. However, only a few models have this feature and people are forced or enticed to buy them, which are quite expensive. More widespread are mobile phones that have a memory card; however these are restricted to the space they provide and users of these phones need to buy another memory card or delete some files if they need more space. People who need additional storage in different kinds of media will benefit from the proposed device because they will not be limited to the space that their memory card provides; they do not need to buy a new mobile phone and they do not need to worry if they need to access a file.

The design will not be costly to implement. The embedded system only uses a small of amount of power to operate, the carbon footprint is minimal and resource utilization is low so no significant harmful effects contribute to the environment. Ethically, people will refrain from using and bringing their PCs just to transfer data because mobile phones are much more portable than PCs. Health and safety concerns will not be likely a problem because the design does

4

not emit harmful radiation. The design manufacturability is high especially when developed with surface mount technology and finally sustainability will be longterm due to modern mobile phones' heavy reliance on micro SD technology.

# **Design Constraints**

The design covers the USB and memory card slot/s that can be accessed using mobile phones with a micro SD slot.

The design utilizes the PIC microcontroller to manage the selection of which will route the data that will go through.

It is powered by a DC battery or adaptor due to the power requirements of the PIC microcontroller.

There are one USB port and two SD/MMC memory card ports.

The mobile phone can read all files of different types inside the activated flash memory to perform different file management features.

The design will utilize the Nokia C3 as the mobile phone model in the testing part of this study.

The following are the design constraints:

The USB flash drive to be used should be compliant with USB 2.0 standard or lower.

The USB flash drive to be used is limited to 4 GB of total memory space.

Mobile phones with micro SD slots are supported unless the memory card slot is located at the back of the device.

The memory card slot supports a mini SD with an adapter attached and SDs of up to 8GB total memory space.

All files inside the USB flash drive or memory card can be read but cannot be opened or executed unless they are supported by the mobile phone (e.g. mp3 or jpg files )

The size of the files to be transferred from the activated flash memory depends on the internal memory capacity of the mobile phone. Nowadays, mobile phones with micro SD slots have up to 8 GB internal mass memory.

#### **Definition of terms**

**Microcontrollers** - are dedicated to one task and run one specific program. The program is stored in ROM (read-only memory) and generally does not change.

**Memory card** - sometimes called a flash memory card or a storage card, is a small storage medium used to store data for use on small, portable or remote computing devices.

**USB Host** - is where the USB host controller is installed and where the client software/device driver runs.

**The USB Host Controller** - is the interface between the host and the USB peripherals. The host is responsible for detecting the insertion and removal of USB devices, managing the control and data flow between the host and the devices, providing power to attached devices, and more.

**PDAs**– acronym for Personal Digital Assistants. It is a mobile device that functions as a personal information manager.

**Flash Memory** - is a non-volatile computer storage chip that can be electrically erased and reprogrammed. Types of flash memory are USB flash drives and SD memory cards.

**EEPROM** - stands for Electrically Erasable Programmable Read-Only Memory and is a type of non-volatile memory used in computers and other electronic devices to store small amounts of data that must be saved when power is removed.

**Voltage Amplifier** - An amplifier designed primarily to build up the voltage of a signal, without supplying it.

**Serial Port** - a serial communication physical interface through which information transfers in or out one bit at a time.

**Biasing** - is the method of establishing predetermined voltages and/or currents at various points of an electronic circuit to set an appropriate operating point.

**Voltage drop** - is the reduction in voltage in the passive elements (not containing sources) of an electrical circuit.

**Saturation** - is the fully conducting state in a semiconductor junction. The term is used especially in applications involving diodes and bipolar transistors

#### **Chapter 2**

#### **REVIEW OF RELATED DESIGN LITERATURES AND STUDIES**

### Digital Memory Card Market and Technology

In recent years, the proliferation of portable consumer electronics such as MP3s, digital cameras, and3G mobile phones has created a tremendous appetite for digital memory cards that use non-volatile flash memory for information and data storage. There are different card formats and designs such as Secure Digital (SD), mini-SD, MultimediaCards (MMC) and MMCmobile. These cards are assembled by either a chip-on-board (COB) process using bare dice, or surface mount technology (SMT) using packaged flash and controller components. The last step in card assembly is accomplished by using either a pre-mold cover or an injection mold process over a PCA (Printed Circuit board Assembly. (Wei Koh, 2005

# Flash Memory Types

The NOR (Not OR) type flash memory was invented by Fujio Masuoka of Toshiba in 1984 and Intel developed it further for initial mass production. In 1987 Masuoka also invented the NAND (Not AND) type flash. Because these two kinds of flash function differently, their applications are suitable for different purposes. The fundamental reason is due to the cell design of the memory—a NAND cell size is smaller hence more density can be packed in an IC chip, where as the NOR flash requires a larger transistor cell, hence lower density on the same sized IC. Due to its faster speed and accuracy, NOR is typically used for code execution and NAND, being higher capacity but a little lower, is used more for data storage. The differences between the two types in functionality, however, are becoming smaller as their design and technology are merging together more closely in recent years.(Wei Koh, 2005)

### Flash Markets

In recent years, the growth of NAND is expanding much faster than NOR. The applications in portable data storage, the wide popularity and growth in USB drives and digital still cameras all contribute to the need for more NAND memory. Whereas for NOR, its use in cell phones is now more limited to low-end and mid-range phones. For 3G and higher performance multimedia phones, or so-called smart phones, the trend is now using NAND and DRAM. For low and mid-range phones, the NOR and PSRAM (pseudo static random access memory) combination is used for initial phone registration with the base station and for code executions. For multimedia phones and smart phones, the trend is switching to the use of the SDRAM/NAND combination to increase memory storage capability.(Wei Koh, 2005)

# **Digital Card Formats**

The following are the card formats using NAND flash memory for data storage: Compact Flash (CF), Multimedia Card (MMC), and Secure Digital (SD). Currently, CF card market shares are gradually being taken over by thinner and smaller cards such as MMC and SD, as the memory density in these cards go up and increase their storage capacity. In coming years, each card format may come to be specialized in certain applications. For example, CF cards may concentrate on very high capacity (4 GB or higher) for use in high resolution (>6 million pixel) professional, high-end digital still cameras or even camcorders for high volume recording and storage. On the other end of the spectrum, the thin form factor cards are becoming even thinner and smaller for portable devices such as cellphones and multimedia phones or PDAs. The reduction in sizes in MMCcalled MMC-mobile and the miniSD that is about half the size of a regular SD card--are obviously intended for mobile applications. Most recently, there are microSDs and MMCmicro. The microSD card is based on SanDisk Transflash cards. Due to their minuscule sizes, initially, their memory densities are typically no more than 50% of their respective "mother" cards, or in the range of 128/256 MB. With use of MCP (multichip package), however, stacked flash die inside the card will enable even the smallest cards to have memory densities in the512MB and even 1GB range.(Wei Koh, 2005)

#### MMC versus SD

When selecting the types of flash cards for application and devices, performance and other factors such as license, royalty, security, and standards are all part of design considerations. Currently MMC and SD cards are the two more dominant 10 formats of choice. The design and performance difference between the two cards are now nearly equal. One useful factor to note is that, because both MMC and SD cards have the same outer envelope, the MMC cards can be used in the same slot for SD cards and most readers are designed to accept both MMC and SD cards.(Wei Koh, 2005)

## Summary

The growth of NAND and NOR-type flash memory cards has been phenomenal in the past few years with the proliferation of consumer use of portable devices and digital storage. The flash market in 2005 is \$17 billion for both NAND and NOR; however, NAND growth is expected to outpace NOR and will have higher revenue in the years to come. Currently, many different card formats are all growing in popularity, but SD and MMC cards are the leading formats as their memory density increases while CF cards are becoming more specialized in highend professional digital photography. The fabrication process of MMC and SD cards is moving toward SIP and MCP, due to continued reduction in card size and thickness. Of 1.0mm and lower, the main manufacturing challenges include using a thin die stack, thin substrates and method of forming the final card dimensions by either applying a thin cover or directly over the mold.

# USB on-the-go interface for portable devices

Until recently, most portable electronic devices used proprietary wired interfaces for connecting to a PC, accessories or chargers. Such portable electronic devices include cell phones, digital cameras, personal digital assistants and mini-USB plugs. Not only was the mechanical interface different for different models from different vendors, but so also were the electrical and protocol interfaces. Proprietary cables and software packages were often required to connect these devices to PCs and connecting one portable device to another portable device was generally not possible. In recent years, the processing power and data storage capacity of portable devices has increased dramatically. Both manufacturers and consumers desire a standard data interface on portable devices in order to allow data sharing between portable devices, and allow the use of standard cables and accessories. Many of today's portable devices are moving towards the Universal Serial Bus (USB) electrical interface as a way of connecting to a PC, although as desktop interface, it is not well suited for portable devices. The PC acts as host (or master), and all other devices are peripherals (or slaves). Hosts cannot connect to hosts, and to peripherals. (Remple, T.B., 2003)

The mini USB plugs are smaller than the standard USB plugs, and are better suited for portable devices. In standard USB, each cable has a +plug on one end, and a B-plug on the other end. The A-plug goes to the PC, which acts as the host or master, and the B-plug goes to the peripheral. This cabling 12

arrangement prevents pc3s (hosts) from being plugged into each other; and also prevents peripherals from being plugged into each other, works cannot connect to peripherals. However, when connecting portable devices together, one of the devices needs to accept a mini.i plug and act as the host, while the other needs to accept a mini-B plug and act as the peripheral. To avoid requiring portable devices to have both connectors are too large for portable devices. The mini AB receptacle accepts either a mini-A plug, or a mini-B plug. A device with a mini-AB receptacle is referred to as an OTG device. When a mini-A plug is inserted into an OTG device, it is referred to as an A-device. When a mini-B plug is inserted into a device, it is referred to as a B-device. The A-device defaults to being the host when the two devices are first connected. The A-device is always responsible for outputting power to the B-device. The following are the features that are required by portable devices, host capability for portable devices smaller connectors low power features in order for cell phones to use the mini-USB connectors instead of existing proprietary connectors, and the OTG interface also has to allow cell phones to connect to analog circuits. (Remple, T.B., 2003)

# Host Negotiation Protocol

In order for an OTG device to act as host, it needs to have a software driver that can recognize and control the peripheral that is connected to it. When two OTG devices are connected, it is possible that the A-device does not have a software driver for the B-device, while the B-device does have a driver for the A-device. If 13 the A-device continues to act as host, then the two devices would not be able to communicate. To address this issue, the OTG Supplement defines a Host Negotiation Protocol (HNP). HNP allows an A-device and a B-device to swap the role of host automatically, in a way that is transparent to the user.

## Low Power Features

The USB Specification requires that a PC (or A-device) is able to output 500mA. Moreover, the PC must always provide power to the bus, even when a remote device is not connected. These requirements are not practical for portable devices such as cell phones and PDAs. To accommodate portable devices, the OTG supplement requires an OTG device to output 8mA instead of 500 mA. Moreover, the A-device is only required to power the bus when the A-device and B-device are communicating. When the bus is powered down, the B-device requires a way of notifying the A-device that it wants to communicate. For this reason, the OTG Supplement defines a Session Request Protocol (SRP). SRP allows a B-device to request service from the A-device when the bus is powered down. (Remple, T.B., 2003)

# Mini-USB AnalogCarkit Interface

In order for a cell phone to use the mini-USB connector as its primary data connector, the mini-USB connector must provide an interface to an analogcarkit. The interface allows several different signaling modes. In all modes, the VBUS

and GND pins are used for power. The remaining three pins can be used for either USB signaling, UART signaling, or analog signaling. The phone determines which signaling mode it should use by first detecting the state of the ID pin. If the ID pin is floating or grounded, then the phone uses USB signaling. If the ID pin is resistively coupled to ground, then the phone knows it is connected to a carkit. (Remple, T.B., 2003)

# Dominant design or multiple designs: The Flash Memory Card case

Any technology currently in use struggled with similar competing products before gaining the dominant design. The famous case of the VHS videotape is the best known example of such a battle. The emergence of a dominant design is very hard to predict and cannot be entirely explained by the economic literature. 'The dominant design is not automatically the technologically superior one, nor will it meet the needs of a particular class to the same extent as a customized design would' (Anderson & Tushman, 1990 and Suárez & Utterback, 1995). The emergence process for dominant designs has typically been viewed as a black box process involving a sophisticated interaction of technological and nontechnological factors (Lee et al., 1995). There is even a possibility that no dominant design will emerge, even many years after product introduction. Examples of cases with no dominant design include: Smartphones, PDA phones, Blackberry, regular and advanced cell phones (including clock, photo camera, agenda); HDTV, regular LCD and the plasma screens; Microsoft Xbox, Nintendo 15

Wii, Playstation 3;DVD-R, DVD-RW, DVD-RAM, DVD-D, DVD+R, DVD+RW, DVD+R DL, HD-DVD and Blu-ray. (deVries, H.J., de Ruijter, J.P.M., & Argam, N., 2007)

## Available flash memory cards

The most common data storage technology is the magnetic disk or hard disk. Beyond these systems, optical systems are recognized as dominant in archival digital data storage. Despite their numerous virtues, these systems also come with several disadvantages. For example, the magnetic and optical data storage systems are not always perfect, especially in small devices with limited power supply. To avoid these disadvantages, flash memory is a good alternative. A flash memory card differs from existing memory storage in that it needs no power supply (nonvolatile) and can be found in a wide range of portable electronic devices. There are a number of industrial standards for memory cards. Different companies produce different types of memory cards, all with different dimensions. In general, these different types are not interchangeable. Currently, roughly six types of flash memory cards exist.

1. *CompactFlash (CF).* CF was introduced by Sandisk Corporation in 1994. Currently, CF is offered by multiple manufacturers. CF is superior in data transfer rates and capacity, but the large size and (relatively) high power consumption make it less suitable for small electronic devices, such as mobile phones.

16

2. *SmartMedia (SM).* SM, owned by Toshiba, was launched in 1996. It was one of the smallest and the thinnest early memory cards, and maintained the most favorable cost ratio. It used to be the favourite card for digital cameras.

3. *Multi-MediaCard (MMC).* MMC was developed by Siemens (Sandisk as well later on) in 1997. Nowadays, it is offered by multiple manufacturers. MMC micro is the smallest card in the world, (backwards) compatible with other cards, without a write or copyright protection (thinner profiled) and it is available to all developers.

4. *Memory Stick (MS).* MS was developed and introduced by Sony in 1998. Sony uses this card for a range of different products and licenses it to other companies. MS Duo is the small version for pocket devices.

5. *Secure Digital Card (SD).* SD was introduced by multiple manufacturers in 2001. The SD card is based on the MMC card but includes a built-in security function and a write protection switch. It is the most common used memory card because of its small size and low power consumption.

6. *Extreme Digital-Picture Card (xD).* Olympus and Fujifilm introduced xD in 2002 for use in their cameras.

Compact Flash typically uses flash memory in a standardized enclosure. This form was first specified and produced by Sandisk in 1994. Compact Flash lacks the mechanical write protection switch that some other devices have, as seen in a comparison of memory cards. Compact Flash does not have any built in DRM or cryptographic features like on some USB flash drives and other formats such

17

as Secure Digital. Such features are rarely used on other cards, however, and are therefore mostly superfluous. Toshiba launched Smart Media to compete with MiniCard, CompactFlash, and PC card formats. A Smart Media card consists of a single NAND flash chip embedded in a thin plastic card (though some higher capacity cards contain multiple, linked chips). It was one of the smallest and the thinnest of the early memory cards, and managed to maintain a favorable cost ratio as compared to the others. It lacks a built-in controller, which keeps the cost down. This feature later caused problems, since some older devices would require firmware updates to handle larger capacity cards. The Multi Media Card is based on Toshiba's NAND-based flash memory, and is therefore much smaller than earlier systems based on Intel NOR-based memory such as Compact Flash. MMC originally used a 1-bit serial interface, but newer versions of the specification allow transfers of 4 or sometimes even 8 bits at a time. (deVries, H.J., de Ruijter, J.P.M., & Argam, N., 2007)

Digital cards (SD card) still see significant use because MMC cards can be used in most devices which support SD cards and they are cheaper than SD cards. RS-MMC cards (Reduced-Size Multi Media Cards) are smaller MMC cards; by using a simple mechanical adapter to elongate the card, an RS-MMC card can be used in any MMC slot. The only significant hardware licensors of RS-MMC cards are Nokia and Siemens. Sometimes a memory USB-stick is called a memory stick, but in this study it refers to the brand name of Sony's flash memory card Memory Stick<sup>™</sup>. Memory Stick is a removable flash memory card format. The Memory 18

Stick family includes the Memory Stick PRO, a revision that allows greater maximum storage capacity and faster file transfer speeds; Memory Stick Duo, a small-form-factor version of the Memory Stick (including the PRO Duo); and the even smaller Memory Stick Micro (M2). (deVries, H.J., de Ruijter, J.P.M., & Argam, N., 2007)

In summary, there are a host of factors indicating one dominant design to emerge, in particular the network externalities characterizing the market and the need to exchange cards between different products. However, a combination of factors at both the supplier and the consumer side outweigh these factors, instead favoring multiple cards. Some factors at the supplier side make it attractive for companies to introduce or maintain their own cards, to be used in own products or for other products as well. Moreover, the speed of technological development has prompted companies to introduce new cards before a battle could turn into a victory for one of the designs. At the consumer side, a combination of two factors make it easy to live with different cards: consumers buy the host devices and take the related card format for granted rather than consciously choose a certain card format. Furthermore, gateway technologies allow them to do this: the compatibility issues can be solved in a relatively easy way resulting in the advantages related to network externalities to remain. (deVries, H.J., de Ruijter, J.P.M., & Argam, N., 2007)

19

# Memory card address bus design

The need to store large quantities of data and information for a certain period of time determines the memory capability of a system. In a typical computer system, the central processing unit (CPU) generates the address of the particular memory location and places it on the address lines that makeup an address bus. A memory card has many parallel address lines connected to a number of memory chips. These memory chips may supply program and data to the CPU or hold output data from arithmetic calculations or for printed output or displays. The address bit combination on the address lines determines which word line will be addressed for a particular operation. The designer must fully understand the requirements of the memory operation so the necessary address bit combination occurs at the proper time during the memory cycle.(deVries, H.J., de Ruijter, J.P.M., & Argam, N., 2007)

# Chapter 3

# **DESIGN PROCEDURES**

# HARDWARE DEVELOPMENT

# **Conceptual Diagram**

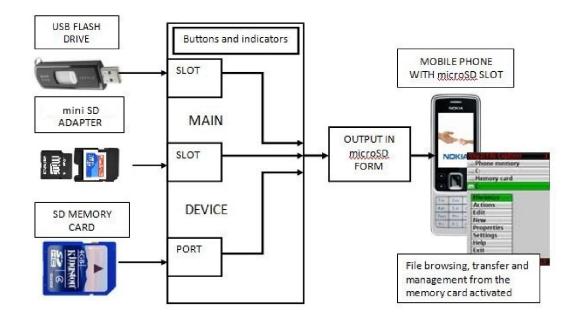

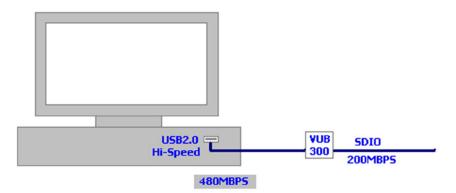

# Figure 3.1 – Conceptual Diagram of the Design

The design paradigm shows the relationship between the components involved in the conceptualization of the file management of a USB flash drive and memory card via the micro SD card slot of a mobile phone. There are three major parts of the conceptualized design: the input, which comprises the memory cards and USB flash drive to be inserted individually into the main device slots; the circuitry of the main device; and lastly, the output, which comprises the device output in micro SD form to be inserted in the mobile phone for the corresponding application of browsing, transferring and management of files inside the flash memory.

First is the connection of the flash memory to the device. The user inserts the necessary USB flash drive or memory cards to the memory slot of the device. Once the flash memory is plugged in, the user will activate the circuit that corresponds to the slot through the button attached to the device and it will be connected to the micro SD slot of the mobile phone. In case multiple memory devices are connected in the circuit, a program switch inside the main device will be responsible so that the user can view only the specified flash memory that is selected through buttons. An indicator will be visible for the user to know which flash memory is activated and read by the mobile phone. The actual file management is done by the user. The user is able to browse and manage the file/s inside the flash memory inserted.

The functionality of the device depends on its input and is tested for its output. The device should be able to connect to the micro SD card slot of the mobile phone and be recognized as the phone's external memory. Furthermore, the files inside the flash memory can be seen and the phone is ready to initiate file management. Successful file transfer from one memory to another, in this case, flash memory to phone memory or vice versa, is one of the main objectives of this design. The successful file transfer happens when a file has been copied completely, without any error. Therefore, the integrity of the file being transferred must be looked forward to.

22

# **Block Diagram**

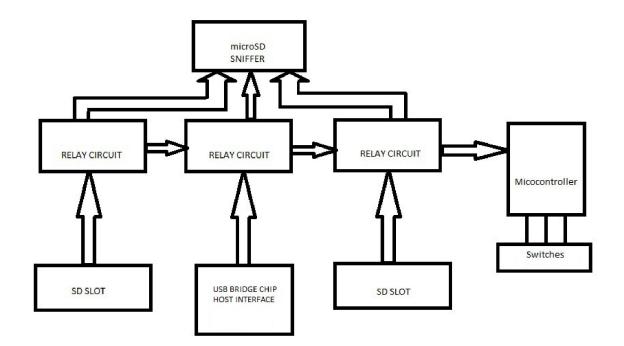

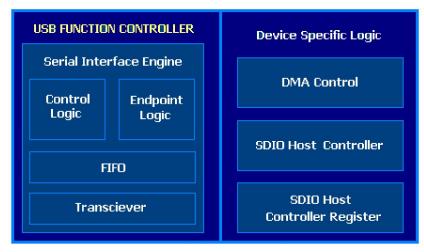

Figure 3.2 - Block Diagram of the Design

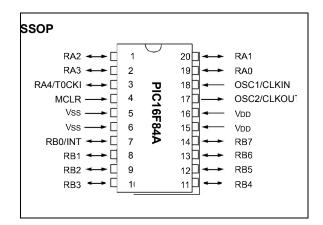

The researchers established a block diagram to guide the whole process of designing. The block diagram serves as the backbone of the design. The figure above illustrates the block diagram used by the group.

Three memory slots, particularly two SD/MMC slots and one Universal Serial Bus (USB) Bridge Chip Host Interface, are provided in the circuit for data input. Each of them is then connected to its corresponding relay circuit which will cut and short the lines in the data and power of the memory slots. Each of the slots has eight lines connected to the relay circuit. The relay circuits are then connected to the microcontroller. The microcontroller will be the one to digitally switch the relay circuits in response to the input signal given by the user. The switches will

serve as the main input device from which the user will select the corresponding circuit to be activated. The three relay circuits are then connected independently to the micro SD sniffer, which serves as the output line of the device to be connected to the micro SD slot of the mobile phone. When one of the switches has been activated, it will proceed to the micro SD sniffer and will be accessed through the mobile phone.

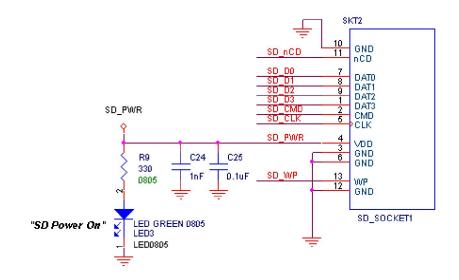

# Schematic Diagram

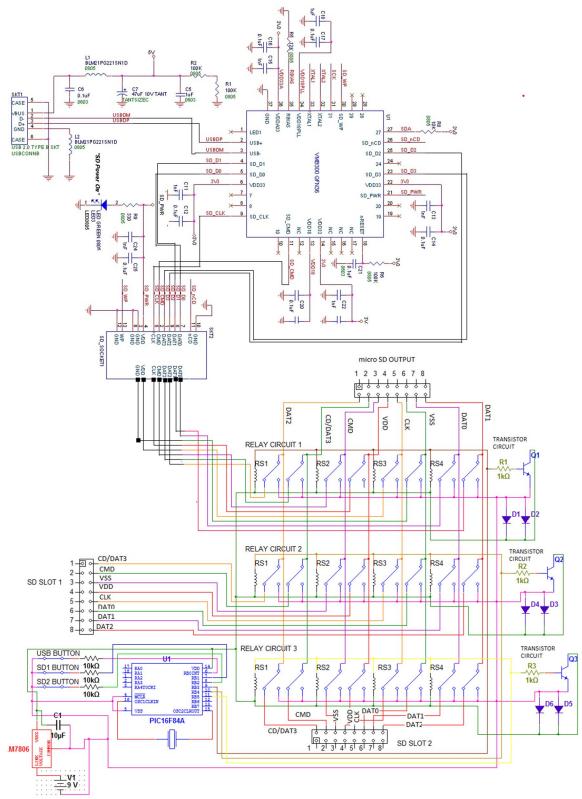

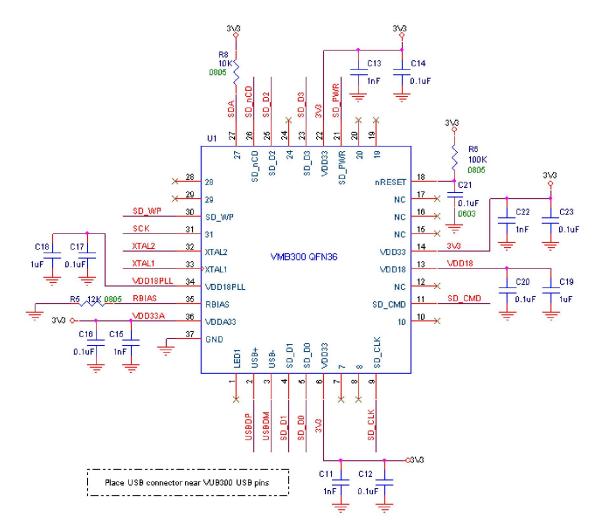

Figure 3.3 Schematic Diagram of the Design

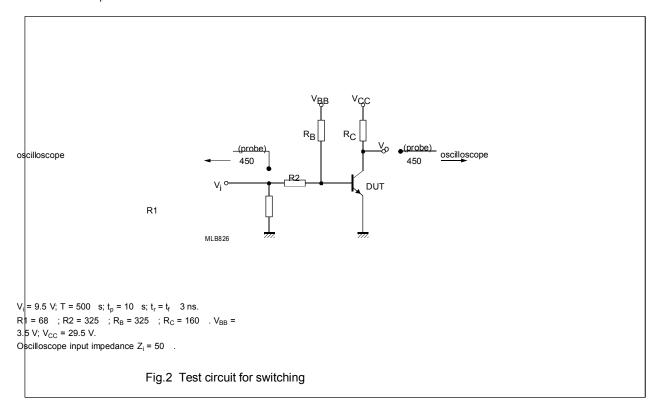

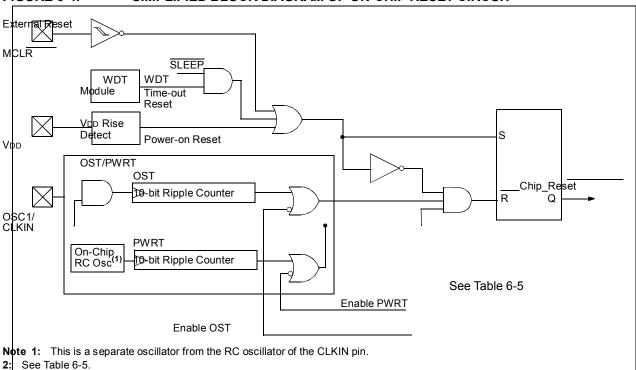

Figure 3.3 shows the schematic/circuit diagram of the whole system. From a 9V DC battery, it will be regulated to 5V to comply with the microcontroller's operating state. A 10 micro-Farad capacitor is connected to the output voltage of the regulator and the ground to filter out the noise coming from the regulator. Each of the switches is then connected to a 10k pull down resistor. The switches are connected to the microcontroller pins for input port assignment. The output line of the each relay circuit is then connected to the output ports of the microcontroller and also to the transistor circuit. The transistor circuit is composed of an NPN Bipolar Junction Transistor (BJT), a 10 kilo-ohms base resistor, and two germanium diodes. The two pins of each relay ICs are connected to every two input lines of the micro SD sniffer. They are connected accordingly to their corresponding pin assignments in order to respond to the operating state of the micro SD output. The output lines of the USB to SDIO bridge chip interface are connected to the corresponding input lines of the relay circuit for it to be processed before going directly to the micro SD output lines. The formula used in getting the value of the capacitor is shown below:

$$C = \frac{5 X I}{V x f} = \frac{5 X 6.2 x 10 - 4}{5.8 x 60} = 10.34 uF$$

Where: C= computed capacitance in farads (F),

I = measured output current from the supply in amps (A),

V = measured supply voltage in volts (V),

f = frequency of the AC supply in hertz (Hz)

When interfacing the switches to the microcontroller, the formula below is used to get the value of the resistor:

$$R = \frac{V}{I} = \frac{5.8}{600 \, x \, 10-6} = 9.67 \, x \, 10^3$$

Where: R = resistance in ohms

V = measured supply voltage in volts (V)

I = measured current flow through resistor in amperes (A)

The base resistor of each transistor circuit is obtained using the formula shown below:

$$Rb = \frac{Vb - Vbe}{Ib} = \frac{5.8 - 0.7}{5 x \, 10 - 3} = 1020$$

Where: Rb = computed base resistor in ohms

Vb = the base voltage in volts (V)

Vbe = the difference from the base voltage to the base emitter

Ib = measured base current in amperes (A)

# SOFTWARE DEVELOPMENT

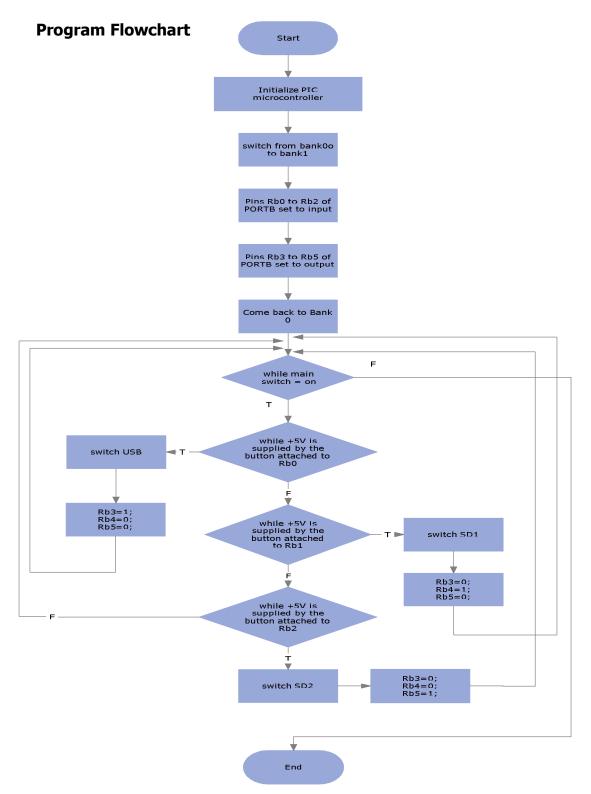

#### Figure 3.4 – Program Flowchart

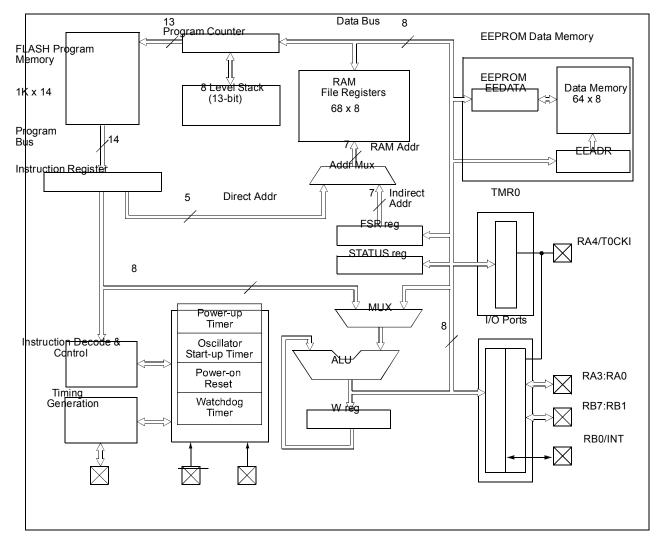

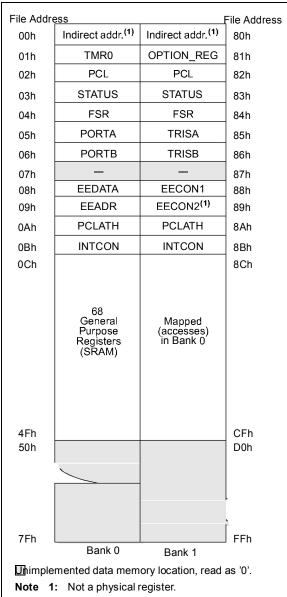

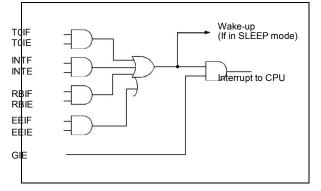

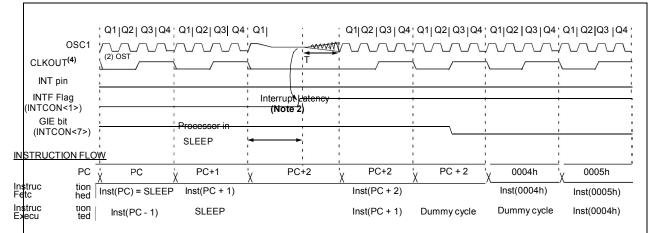

Figure 3.4 shows how the PIC microcontroller behaves as soon as it is enabled. The first process is the initialization of the PIC microcontroller; this is where it initializes Port B. The initialization process comes in four stages; first is the bank switching from bank 1 to bank 0. Bank 1 is used to control the operation of the PIC, and bank 0 is used to manipulate the data. Initially, the PIC is in bank 0. It is then switched to bank 1 to assign the input and output ports needed. Second, the researchers assign pins 0, 1 and 2 of Port B to be the input data. The researchers then assign all pins 3, 4 and 5 of Port B to be the output data. Lastly, the bank returns to bank 0 for manipulation of data.

After the initialization process, the program for data selection is next. Since there are three memory slots connected in the circuit, it is then programmed for data activation/deactivation. While the circuit is in its operating state, the program will wait for a +5V input from the button associated with pin 0 of port B. While a high signal is received, the program will proceed to the function that will activate SD card slot 1. Else, the function call is skipped and will proceed to the next statement. The same procedure for data selection is done for pins 1 and 2 of port B. When a high signal is received from either of the two ports, then the statement will proceed to the function call that will activate the USB port and SD card slot 2, respectively. If it does not satisfy the condition, it will return to the

selection process. Also, the function call will return to the selection process and will continue to accept and perform the specified operation.

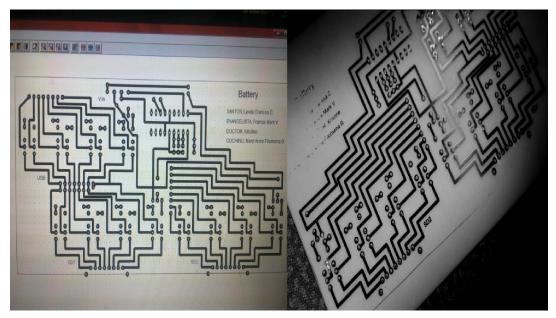

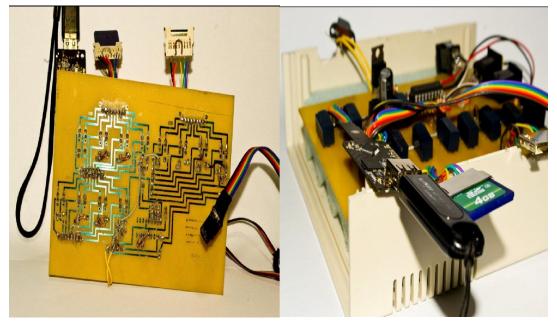

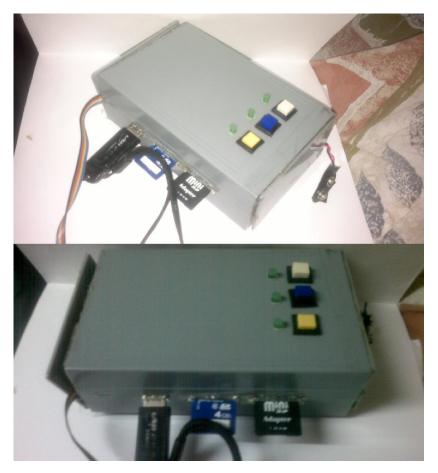

### **PROTOTYPE DEVELOPMENT**

The first step to do is to provide the needed materials and equipment to be used in building the prototype. The researchers discussed both software and hardware specifications separately in the design procedure. The materials and components that were utilized are as follows:

## **Hardware Components**

## **PIC Microcontroller**

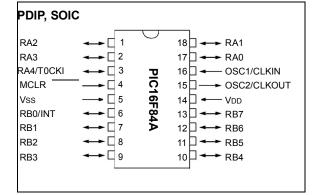

The microcontroller serves as the main processor of the design which has the capability to store the program that must be implemented in the design. The microcontroller used is PIC16F84A, 18-pin enhanced FLASH/EEPROM 8-bit microcontroller. The PIC16F84A has the capability to accept data coming from a serial port directly.

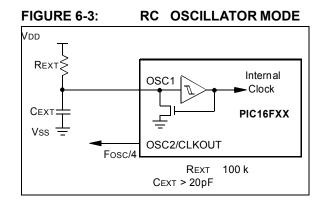

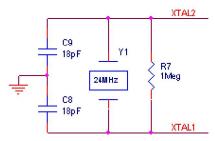

## **Crystal Oscillator 4MHz**

The microcontroller will need a Crystal Oscillator 4MHz as shown in Figure 3.4. This oscillator will act as a clock feed into the PIC microcontroller; the frequency of the oscillator will affect the instruction per second process of the PIC microcontroller.

### **Push Button Switches**

Three push button switches are used and will serve as the main input device from which the user will select the corresponding circuit to be activated. The blue and yellow switches correspond to the activation of the two SD memory slots while the white switch corresponds to the activation of the USB Flash Drive.

#### 10K 1/4W Pull-Down Resistor

The microcontroller also needs to have a pull down resistor, typically a 10k resistor. It is used to limit the current that can flow between Vcc and ground. Since it is a pull-down resistor, one of its legs is connected to the ground.

#### 5V Relay Switch

A relay is used to isolate one electrical circuit from another. The main device consists of 12 relay switches to power up and to electronically switch the corresponding input lines of a memory slot being activated. One relay circuit comprises of four relays in each memory slot, two lines from which are supplied by one relay switch.

#### NPN type Bipolar Junction Transistor (BJT)

The relay coil's current requirement is usually about 100mA for small relays and the microcontroller cannot supply this much of current to relay by itself. A transistor is used to handle this current requirement. At the same time, it acts as a voltage amplifier to drive the relays in their operating state. One transistor is used for each relay circuit.

#### 1/2 Watt 47 Ohms Resistor

Bipolar transistor amplifiers must be properly biased to operate correctly. Biasing networks consisting of resistors are commonly employed. A series base resistor of 47 ohms is used to set the base current, so that the transistor is driven into 32 saturation (fully turned on) when the relay is to be energized. That way, the transistor will have minimal voltage drop, and hence dissipate very little power.

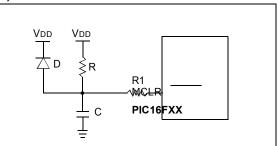

#### **Germanium Diode**

A power diode is connected across the relay coil, to protect the transistor from damage due to the back-EMF pulse generated in the relay coils inductance when it turns off. Ideally, each of the relays should have its own diode. However, diodes may also consume an amount of current in the circuit. That's why in this particular circuit, having two diodes per relay circuit is enough to protect the transistors from damage.

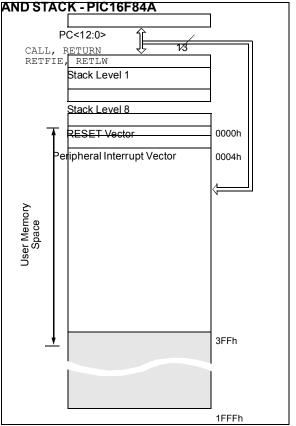

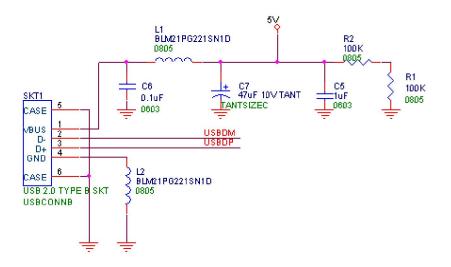

#### SD Memory Card Slot & Pin-out

#### Figure 3.5 – SD Memory Card Slot & Pin-out

Two Secure Digital (SD) memory card slots are mounted in the main device. It is where SD memory cards will be inserted to begin with the operation of the device and to enable the file management of the SD memory cards through the mobile phone. The SD card slot has nine interface pins in contact with the SD memory card inserted which are connected to their corresponding data lines to be processed by the main device circuit.

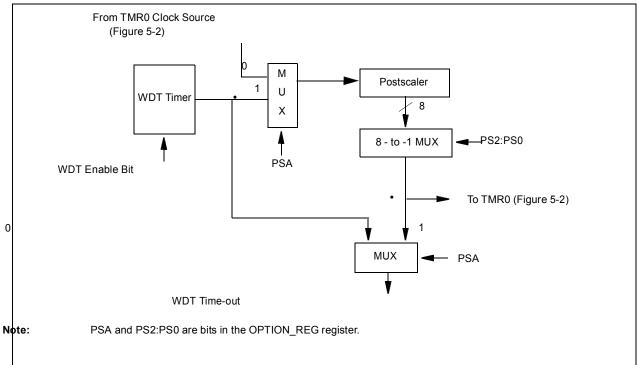

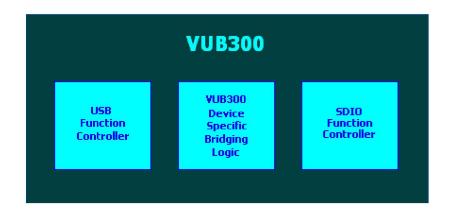

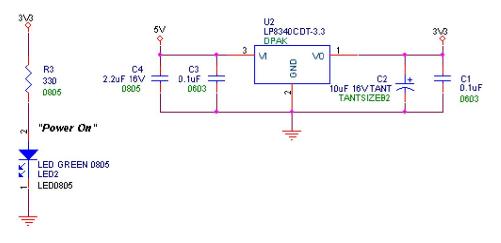

#### **USB to SD IO host controller bridge chip interface**

This chip is used to bridge and process the data lines USB Flash Drive into its corresponding SD input/output lines. It consists of different components and integrated circuits such as the USB chip embedded host controller to access generic USB mass-storage devices; Integrated PCMCIA / CF device designed to bridge chips using serial or parallel-bit streams; USB transceiver to handle connection detection functionality as well as providing the analog electrical signaling required to meet the specification; USB to 16-bit PC Card Interface Device to enable connection of Compact Flash devices via the USB bus; and the Field-programmable Gate Array (FPGA) to configure and translate the USB flash drive into a micro SD-like form.

#### 10uF and 0.1uF Capacitors

A value of 10uF capacitor is used to filter the ripple coming from the regulator so that a smooth form of supply will be delivered to the microcontroller. Since microcontroller circuits are designed as direct current (DC) circuits, variations in the voltages of these circuits can cause problems. If the voltages swing too much, the circuit may operate incorrectly. For most practical purposes, a voltage that fluctuates is considered an AC component. The function of the 0.1uF bypass capacitor is to dampen or isolate the AC, or the electric noise in the circuit.

### 9V Battery Supply and Standard Battery Connector

The device is operated using a 9V battery supply with its connector to make the device portable.

## **6V Voltage Regulator**

The 9V supply of the device will be regulated into 6V to maintain the voltage range of the microcontroller's operating state, which is 5V-6V, and prevent it from being damaged by a power surge.

## **Stranded wires**

Stranded wires are used in this design to connect the data lines from the SD memory card slots and the USB bridge chip host interface transfer to the output data lines which corresponds to the micro SD sniffer. Stranded wires are used over solid wires because they are flexible and the pins of the data lines are thin and small enough for that particular wire to fit in.

## **Micro SD Sniffer**

## Figure 3.6 – micro SD Sniffer

The output of the main device is called the micro SD sniffer. It is a dummy micro SD card having no memory chip inside and is intended for accessing the output data lines coming from the SD memory cards and USB flash drive inserted in the main device. When the selected flash memory has been processed by the 35

device, the memory of the sniffer will be that of the selected flash memory device and it will be inserted to the mobile phone for file management.

## SOFTWARE COMPONENTS

The program for the device is made using C programming language and MikroC as the program compiler. Pickit2 is utilized to program and debug the microcontroller.

#### **Chapter 4**

#### **TESTING, PRESENTATION, AND INTERPRETATION OF DATA**

This chapter discusses the testing part of the design; results to those tests can be found in this part so that it can be determined whether the design is effective and accurate or not.

#### Single File Copy Speed Test

The purpose of this is to test if the device is capable of responding efficiently with the file management features of the mobile phone, specifically the COPY function of the mobile device. Furthermore, the accuracy of a file when being transferred from all of the three flash memory devices to the corresponding memory of the phone is being tested. As indicated in the scope of this study, the mobile phone model to be used for this purpose is the Nokia C3. The sizes of the SD Memory Card, mini SD Memory Card and USB Flash Drive are tested based on the memory size supported by most mobile phone switch is 4 GB of memory. Another purpose of this test is to determine the causes of errors and data loss in transferring a file, if there are any. After this test, the functionality of the device and how successful a single file is transferred without data loss can be determined. The transfer speed of each file is also measured and observed after this test.

These are the procedures to be followed in conducting the test:

The COPY function of the mobile phone will be used to duplicate a file from the given SD memory cards and USB flash drive or vice versa.

For each memory type, the maximum memory capacities of the three flash memories in accordance with the design's delimitation will be used. For both SD memory card and mini SD memory card, 4 GB memory size will be used; and for USB flash drive, 8 GB memory size will also be used.

The file sizes that will be used for testing are 1 MB and 10 MB whose file types/extensions to be used are .jpg (picture file) and .mp4 (video file) respectively. Note that these files are supported by the test phone. Separate tables will be provided for each file size.

Thirty trials will be made to test and observe the consistency of the file transfer speed.

To make sure that the data transferred is correct and is the same file from the source, a prompt should be displayed on the mobile phone indicating that the file has been successfully transmitted. Moreover, the file that has been transferred should be similar to the source file being copied from in terms of their size in bytes. If the mobile phone supports the file format of the file being transferred (e.g., music, documents, pictures), then it should be opened successfully in the mobile phone. On the other hand, a corrupted icon or image is displayed by the mobile phone if it is not successful at all.

The results to be displayed in the tables are the transfer speed of the file in seconds out of 30 trials made. A timer is used to measure the transfer speed of the file copied from the flash memory to the phone memory in seconds. The

38

average transfer speed computed from the results of the 30 trials is displayed at another table.

The REMARKS column is intended for the instance of having successful or unsuccessful file transfers during the actual process, and if the files are successfully copied only from the external memory to the mobile phone, the other way around, or both.

## Tables of data collected:

## Table 4.1. File Copy Speed Test Results using Phone Model Nokia C3 at

| TRIAL | Transfer<br>Speed of File<br>Copied from<br>SD Memory<br>(sec) | Transfer<br>Speed of File<br>Copied from<br>Mini SD<br>Memory<br>(sec) | Transfer<br>Speed of File<br>Copied from<br>USB Flash<br>Drive<br>(sec) | REMARKS                                 |

|-------|----------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------|

| 1     | 3.2 s                                                          | 4.3 s                                                                  | 5.2 s                                                                   | File copied to and<br>from both devices |

| 2     | 3.2 s                                                          | 4.3 s                                                                  | 5.3 s                                                                   | File copied to and from both devices    |

| 3     | 3.1 s                                                          | 4.3 s                                                                  | 5.2 s                                                                   | File copied to and<br>from both devices |

| 4     | 3.2 s                                                          | 4.3 s                                                                  | 5.4 s                                                                   | File copied to and<br>from both devices |

| 5     | 3.2 s                                                          | 4.5 s                                                                  | 5.4 s                                                                   | File copied to and<br>from both devices |

| 6     | 3.3 s                                                          | 4.5 s                                                                  | 5.4 s                                                                   | File copied to and<br>from both devices |

| 7     | 3.2 s                                                          | 4.5 s                                                                  | 5.4 s                                                                   | File copied to and<br>from both devices |

| 8     | 3.2 s                                                          | 4.5 s                                                                  | 5.4 s                                                                   | File copied to and<br>from both devices |

| 9     | 3.1 s                                                          | 4.5 s                                                                  | 5.4 s                                                                   | File copied to and<br>from both devices |

| file size ( | of 1 MB |

|-------------|---------|

|-------------|---------|

| 10 | 3.2 s | 4.5 s | 5.4 s            | File copied to and |

|----|-------|-------|------------------|--------------------|

|    |       |       |                  | from both devices  |

| 11 | 3.3 s | 4.5 s | 5.4 s            | File copied to and |

|    |       |       |                  | from both devices  |

| 12 | 3.3 s | 4.5 s | 5.4 s            | File copied to and |

|    |       |       |                  | from both devices  |

| 13 | 3.3 s | 4.3 s | 5.4 s            | File copied to and |

|    |       |       |                  | from both devices  |

| 14 | 3.3 s | 4.3 s | 5.4 s            | File copied to and |

|    |       |       |                  | from both devices  |

| 15 | 3.3 s | 4.4 s | 5.4 s            | File copied to and |

|    |       |       |                  | from both devices  |

| 16 | 3.2 s | 4.5 s | 5.4 s            | File copied to and |

|    |       |       |                  | from both devices  |

| 17 | 3.3 s | 4.5 s | 5.4 s            | File copied to and |

|    |       |       |                  | from both devices  |

| 18 | 3.2 s | 4.3 s | 5.4 s            | File copied to and |

|    |       |       |                  | from both devices  |

| 19 | 3.2 s | 4.4 s | 5.4 s            | File copied to and |

|    |       |       |                  | from both devices  |

| 20 | 3.2 s | 4.5 s | 5.4 s            | File copied to and |

|    |       |       |                  | from both devices  |

| 21 | 3.3 s | 4.5 s | 5.3 s            | File copied to and |

|    |       |       |                  | from both devices  |

| 22 | 3.3 s | 4.4 s | 5.4 s            | File copied to and |

|    |       |       |                  | from both devices  |

| 23 | 3.1 s | 4.4 s | 5.4 s            | File copied to and |

|    |       |       |                  | from both devices  |

| 24 | 3.3 s | 4.5 s | 5.4 s            | File copied to and |

|    |       |       |                  | from both devices  |

| 25 | 3.2 s | 4.4 s | 5.3 s            | File copied to and |

|    |       |       |                  | from both devices  |

| 26 | 3.3 s | 4.4 s | 5.4 s            | File copied to and |

|    |       |       |                  | from both devices  |

| 27 | 3.2 s | 4.4 s | 5.3 s            | File copied to and |

|    |       |       | from both devi   |                    |

| 28 | 3.3 s | 4.4 s | 5.4 s            | File copied to and |

|    | *     |       | from both device |                    |

| 20 | 3.2 s | 4.5 s | 5.4 s            | File copied to and |

| _• |       |       |                  | from both devices  |

| 30 | 3.2 s | 4.5 s | 5.4 s            | File copied to and |

|    | 5.2.5 |       |                  | from both devices  |

|    |       |       |                  |                    |

## Table 4.2. File Copy Speed Test Results using Phone Model Nokia C3 at

| TRIAL | Transfer<br>Speed of File<br>Copied from<br>SD Memory<br>(sec) | Transfer<br>Speed of File<br>Copied from<br>Mini SD<br>Memory<br>(sec) | Transfer<br>Speed of File<br>Copied from<br>USB Flash<br>Drive<br>(sec) | REMARKS                                                      |

|-------|----------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------|

| 1     | 13.2 s                                                         | 13.6                                                                   | 16.5 s                                                                  | File copied to and                                           |

| 2     | 13.2 s                                                         | 13.8                                                                   | 16.6 s                                                                  | from both devices<br>File copied to and<br>from both devices |

| 3     | 13.2 s                                                         | 13.8                                                                   | 16.5 s                                                                  | File copied to and from both devices                         |

| 4     | 13.2 s                                                         | 13.6                                                                   | 16.5 s                                                                  | File copied to and from both devices                         |

| 5     | 13.2 s                                                         | 13.6                                                                   | 16.5 s                                                                  | File copied to and<br>from both devices                      |

| 6     | 13.2 s                                                         | 13.6                                                                   | 16.5 s                                                                  | File copied to and from both devices                         |

| 7     | 13.2 s                                                         | 13.6                                                                   | 16.5 s                                                                  | File copied to and<br>from both devices                      |

| 8     | 13.2 s                                                         | 13.8                                                                   | 16.6 s                                                                  | File copied to and from both devices                         |

| 9     | 13.2 s                                                         | 13.8                                                                   | 16.5 s                                                                  | File copied to and<br>from both devices                      |

| 10    | 13.1 s                                                         | 13.9                                                                   | 16.5 s                                                                  | File copied to and<br>from both devices                      |

| 11    | 13.2 s                                                         | 13.8                                                                   | 16.6 s                                                                  | File copied to and from both devices                         |

| 12    | 13.2 s                                                         | 13.5                                                                   | 16.5 s                                                                  | File copied to and from both devices                         |

| 13    | 13.2 s                                                         | 13.6                                                                   | 16.5 s                                                                  | File copied to and from both devices                         |

| 14    | 13.2 s                                                         | 13.5                                                                   | 16.5 s                                                                  | File copied to and from both devices                         |

## file size of 10 MB

| 15 | 13.1 s | 13.8 | 16.6 s | File copied to and |

|----|--------|------|--------|--------------------|

|    |        |      |        | from both devices  |

| 16 | 13.2 s | 13.4 | 16.5 s | File copied to and |

|    |        |      |        | from both devices  |

| 17 | 13.2 s | 13.5 | 16.6 s | File copied to and |

|    |        |      |        | from both devices  |

| 18 | 13.3 s | 13.8 | 16.5 s | File copied to and |

|    |        |      |        | from both devices  |

| 19 | 13.2 s | 13.8 | 16.5 s | File copied to and |

|    |        |      |        | from both devices  |

| 20 | 13.1 s | 13.7 | 16.7 s | File copied to and |

|    |        |      |        | from both devices  |

| 21 | 13.2 s | 13.8 | 16.6 s | File copied to and |

|    |        |      |        | from both devices  |

| 22 | 13.2 s | 13.8 | 16.5 s | File copied to and |

|    |        |      |        | from both devices  |

| 23 | 13.2 s | 13.6 | 16.6 s | File copied to and |

|    |        |      |        | from both devices  |

| 24 | 13.3 s | 13.6 | 16.6 s | File copied to and |

|    |        |      |        | from both devices  |

| 25 | 13.2 s | 13.8 | 16.7 s | File copied to and |

|    |        |      |        | from both devices  |

| 26 | 13.2 s | 13.7 | 16.7 s | File copied to and |

| _  |        | _    |        | from both devices  |

| 27 | 13.2 s | 13.8 | 16.7 s | File copied to and |

|    |        |      |        | from both devices  |

| 28 | 13.2 s | 13.8 | 16.6 s | File copied to and |

|    |        |      |        | from both devices  |

| 20 | 13.2 s | 13.7 | 16.7 s | File copied to and |

|    |        |      |        | from both devices  |

| 30 | 13.3 s | 13.7 | 16.5 s | File copied to and |

|    | 2010 0 |      |        | from both devices  |

| L  | 1      | 1    |        |                    |

The average file transfer speed for each flash memory device is computed using the formula:

##

## Table 4.3 Average Transfer Speed at 1 MB and 10 MB

42

| File Size | Average<br>Transfer Speed<br>in SD Memory<br>Card | Average<br>Transfer Speed<br>In mini SD<br>Memory Card | Average<br>Transfer Speed<br>in USB Flash<br>Drive |

|-----------|---------------------------------------------------|--------------------------------------------------------|----------------------------------------------------|

| 1 MB      | 3.2 s                                             | 4.4 s                                                  | 5.4 s                                              |

| 10 MB     | 13.2 s                                            | 13.7 s                                                 | 16.6 s                                             |

The formula below is used to get the standard deviation for each proportion. This will determine how much variation or "dispersion" there is from the average transfer speed of each flash memory with respect to our device.

$$s^2 = \frac{\sum (X - M)^2}{N}$$

Where  $s^2$  is the variance, X is the speed value per n trial, and N is the number of trials which is 30. The standard deviation S is simply the square root of variance.

Table 4.4 summarizes the variance and standard deviation of the results in Tables 4.1 and 4.2.

Table 4.4 Variance and Standard Deviation at 1 MB and 10 MB

|           | Transfer Speed<br>in SD Memory<br>Card | Transfer Speed<br>In mini SD<br>Memory Card | Transfer Speed<br>in USB Flash<br>Drive |

|-----------|----------------------------------------|---------------------------------------------|-----------------------------------------|

| Variance  | 0.004241379                            | 0.006850575                                 | 0.003402299                             |

| Standard  | 0.065125873                            | 0.082768199                                 | 0.058329228                             |

| Deviation |                                        |                                             |                                         |

Based on the results gathered in Tables 4.1 and 4.2, the file copy test is successful for the mobile phone model Nokia C3 to and from SD memory cards and USB flash drives. It can be implied that the device is capable of copying files of different types and sizes such as 1 MB and 10 MB. The transfer speed is also measured and was observed to be close to each other.

With regards to the transfer speed of the files copied from the USB flash drive or SD memory card to the mobile phone, it was observed that the average transfer rate of the flash memories with respect to the prototype. The actual transfer speed of the Mini SD Card was lower than the SD Memory card because the Mini SD card is connected to another adaptor which implies an additional data rate going to the destination. Nevertheless, since the standard deviation was smaller than half of the average for all the three flash memories, the results are said to be consistent which makes device functional and reliable with regards to the file transfer speed value.

The transfer speed for the USB flash drive to the mobile phone is lower than the transfer speed of SD memory card and Mini SD memory card. This is due to the technology of the USB flash drive compared to memory cards which has larger power dissipation for data transfer.