# **ERES104** 2 Channel Syncro/Resolver Interface User's Manual

CReal Time Devices)

RTD Embedded Technologies, Inc.

"Accessing the Analog World"®

ISO9001 and AS9100 Certified

BDM-610020065 Rev. B

# **ERES104**

# 2 Channel PC/104 Syncro/Resolver Interface User's Manual

**RTD Embedded Technologies, Inc.**

103 Innovation Blvd. State College, PA 16803-0906

Phone: +1-814-234-8087 FAX: +1-814-234-5218

<u>E-mail</u> sales@rtd.com techsupport@rtd.com

<u>Web site</u> http://www.rtd.com

#### **Revision History**

Rev. AConverted to RTD format, fixed jumper settingsRev. B Mar 9, 2011Corrected Table 2-3, added 2V resistor part number, Fixed IDAN pin out

Published by:

RTD Embedded Technologies, Inc. 103 Innovation Blvd. State College, PA 16803-0906

Copyright 1999, 2002-2011 RTD Embedded Technologies, Inc. All rights reserved Printed in U.S.A.

The RTD Logo is a registered trademark of RTD Embedded Technologies. cpuModule and dataModule are trademarks of RTD Embedded Technologies. MS-DOS, Windows, Windows 95, Windows 98 and Windows NT are trademarks of Microsoft Corp. PC/104 is a registered trademark of PC/104 Consortium. All other trademarks appearing in this document are the property of their respective owners.

# TABLE OF CONTENTS

| CHAPTER 1     | INTRODUCTION                       |    |

|---------------|------------------------------------|----|

| SYNCRO/RESO   | OLVER INPUTS                       | 1  |

|               | CIRCUITRY                          |    |

|               | DESCRIPTION                        |    |

| CONNECTOR I   | DESCRIPTION                        |    |

|               | S WITH YOUR BOARD                  |    |

|               | s Manual                           |    |

|               |                                    |    |

|               | EED HELP                           |    |

| CHAPTER 2     | CONFIGURING THE ERES104            |    |

| FACTORY-CO    | NFIGURED JUMPER SETTINGS           | 3  |

|               | SS JUMPERS                         |    |

|               | HANNEL                             |    |

|               | D SENSOR 2 CONFIGURATION           |    |

|               | PERS                               |    |

| CHAPTER 3     | INSTALLING THE ERES104             | 8  |

| RECOMMEND     | ed Procedure                       | 8  |

| CHAPTER 4     | CONNECTING THE ERES104             |    |

| FINDING PIN 1 | 1 of Connectors                    | 10 |

|               | OLVER CONNECTOR                    |    |

|               |                                    |    |

| CHAPTER 5     | HARDWARE DESCRIPTION               |    |

| RESOLVER TO   | ) DIGITAL CONVERTERS               |    |

|               | g Resolvers to ERES104             |    |

|               | g Inductosyn to ERES104            |    |

|               | g Syncros to ERES104               |    |

|               | z LVDT's to ERES104                |    |

|               | SCOTT-T CONVERTER                  |    |

| SINE WAVE E   | EXCITATION                         |    |

| REFERENCE C   | CONNECTION                         |    |

| CHAPTER 6     | BOARD OPERATION AND PROGRAMMING    | 23 |

| DEFINING THE  | Е І/О Мар                          |    |

| BASE+0h       | INHIBIT CHANNEL 1 (1b AFTER RESET) |    |

| BASE+2h       | INHIBIT CHANNEL 2 (1b AFTER RESET) |    |

| BASE+4h       | IRQ_CONF (0000b AFTER RESET)       |    |

| BASE+6h       | BOARD_CNTRL (0111b AFTER RESET)    |    |

| BASE+8h       | RD_RESOLUTION (00h AFTER RESET)    |    |

| BASE+Ah       | INCREMENT DIGITAL POT              |    |

| BASE+Ch       | READ CHANNEL #1                    |    |

| BASE+Eh       | READ CHANNEL #2                    |    |

| BASE+10h      | CLEAR CHANNEL #1 INTERRUPT         |    |

| BASE+12h      | n CLEAR CHANNEL #2 INTERRUPT       |    |

| SETTING UP T  | HE ERES104 BOARD                   |    |

| CHAPTER 7     | IDAN DIMENSIONS AND PINOUT         | 26 |

| CHAPTER 8     | RETURN POLICY AND WARRENTY         |    |

| RETURN POLI   | СҮ                                 |    |

| LIMITED WA    | RRANTY                             |    |

# FIGURES

| Eisens 2.1. Deand lawart above in a jump on la actions                                             | 2   |

|----------------------------------------------------------------------------------------------------|-----|

| Figure 2-1: Board layout showing jumper locations                                                  |     |

| Figure 2-2 Base Address jumper block (A8 to top, A5 to bottom)                                     | 4   |

| Figure 2-3: Interrupt Selection Jumpers                                                            | 5   |

| Figure 2-4 Board layout showing solder jumper locations                                            | 7   |

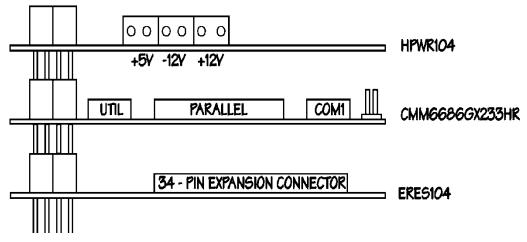

| Figure 3-1 Example of ERES104 in a stack                                                           | 9   |

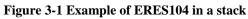

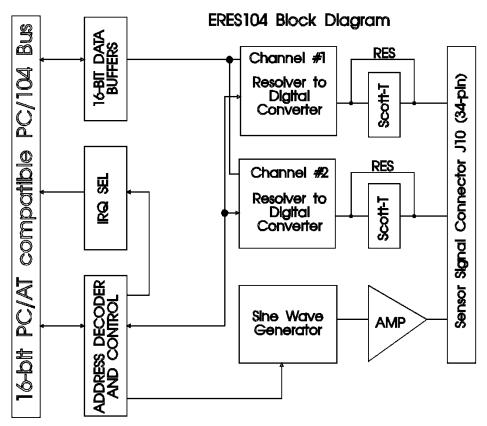

| Figure 5-1 ERES104 Block diagram                                                                   | .12 |

| Figure 5-2 Differential Resolver connection to a ERES104                                           | .13 |

| Figure 5-3 Differential Resolver input using DDC-49530 (11.8V), DDC-49590 (90V), or DDC-76037 (2V) | .14 |

| Figure 5-4 Inductosyn Connections                                                                  | .15 |

| Figure 5-5 Syncro Input                                                                            |     |

| Figure 5-6: Syncro Input using DDC-49530 (11.8V), DDC-49590 (90V), or DDC-76037 (2V)               | .16 |

| Figure 5-7 A generic 2 wire LVDT connection to a converter                                         | .17 |

| Figure 5-8 Solid State Scott-T converter circuit                                                   | .18 |

| Figure 5-9 Reference input for sensor 1                                                            | .19 |

| Figure 5-10 Reference input for sensor 2                                                           | .20 |

| Figure 5-11 Phase shift compensation                                                               |     |

| Figure 5-12 Board layout showing reference components                                              |     |

| Figure 5-13 Block diagram of ERES104 board                                                         |     |

| Figure 7-1: IDAN Mechanical Drawing                                                                |     |

| Figure 7-2 IDAN connector location                                                                 |     |

# TABLES

| Table 2-1 Factory Default Jumper Settings                                   | 3  |

|-----------------------------------------------------------------------------|----|

| Table 2-2 Base Address Jumper Settings                                      |    |

| Table 2-3 Jumper configuration for the Sensor configuration terminal blocks |    |

| Table 2-4 Solder jumper configuration:                                      |    |

| Table 4-1 Sensor Interface connector J10 pin out                            |    |

| Table 5-1 RD converter external component values                            |    |

| Table 6-1 ERES104 I/O Map                                                   | 23 |

| Table 6-2 Base +8 in Resolver Mode                                          | 24 |

| Table 6-3 Base +8 in LVDT Mode                                              | 24 |

| Table 7-1 IDAN pin out                                                      | 27 |

## Chapter 1 INTRODUCTION

This user's manual describes the operation of the ERES104 2-Channel PC/104 Syncro/Resolver subsystem.

- 2 independent Differential Syncro/Resolver/LVDT channels

- Connection to 2, 11.8V or 90V Syncros with onboard solid State Scott-T circuitry

- External Reference or programmable Sine wave excitation from 400 Hz to 1.6 KHz

- Programmable resolution 10, 12, 14, or 16 bits.

- Accuracy: 2 +1 LSB

- Repeatability: 1 LSB

- Fully PC/104 compliant

- +5V only operation

The following paragraphs briefly describe the major features of the ERES104. A more detailed discussion is included in Chapter 5 (Hardware description). The board setup is described in Chapter 2 (Configuring the ERES104).

### Syncro/Resolver Inputs

The ERES104 provides two independently configurable input channels. Both channels support Syncro, Resolver or LVDT interface. The voltage of the Syncro inputs can be selected to 2V, 11.8V or 90V standard devices. You may use the onboard excitation oscillator or an external reference source. The external reference signal is scalable with an onboard voltage divider. Reference phase shift can be adjusted with a resistor/capacitor pair for each channel. Special design procedures have been followed to ensure error free stable operation even up to 16-bit resolution. Both input channels have independent grounds for reference and sensors. Syncro signals are converted to sine/cosine resolver signals with a laser trimmed precision solid state Scott-T converter. The resolver signal is then digitized by the onboard resolver-to-digital converters.

### **Excitation Circuitry**

A programmable reference oscillator is available onboard to drive sensors. The frequency and amplitude of the sine wave are programmable. Digital potentiometers are used to give stable operation and flexible 32-step adjustment of excitation characteristics. The reference source is common to both channels. The onboard DC/DC converter can be used to drive total loads of 1,5W. The excitation frequency is factory set to 400 Hz to 1.6K Hz range. This range can easily be increased to 2.6K Hz to work with common resolver types with a small adjustment. Please consult the factory for more details.

### Mechanical description

The ERES104 is designed on a PC/104 form factor. An easy mechanical interface to both PC/104 and EUROCARD systems can be achieved. Stack your ERES104 directly on a PC/104 compatible computer using the onboard mounting holes. Care must be taken to ensure good quality cabling to ensure high quality noise free operation.

### **Connector description**

The connections are made by header type terminals. The PC/104 bus connector is 16-bit wide stack through type.

### What comes with your board

You receive the following items in your ERES104 package:

- ERES104 PC/104 resolver to digital converter board

- Companion CD

```

Notes: Latest software and drivers can be downloaded from our website.

```

If any item is missing or damaged, please contact RTD Embedded Technologies.

# Scope of this Manual

This manual expects the user to be familiar with syncros and resolvers. The theory and operation or these sensors is not within the scope of this manual.

## Using this manual

This manual is intended to help you install your new ERES104 card and get it running quickly, while also providing enough detail about the board and its functions so that you can enjoy maximum use of its features even in the most demanding applications.

## When you need help

This manual and all the example programs will provide you with enough information to fully utilize all the features on this board. If you have any problems installing or using this board, contact our Technical Support Department (814) 234-8087 during EST business hours, or send an Email to techsupport@rtd.com. When sending an Email request, please include your company's name and address, your name, your telephone number, and a detailed description of the problem.

# Chapter 2 CONFIGURING THE ERES104

The ERES104 board has jumper settings to configure the operation of the board. Special care must be taken to make correct connections since high voltage input signals may be used.

# Factory-Configured Jumper Settings

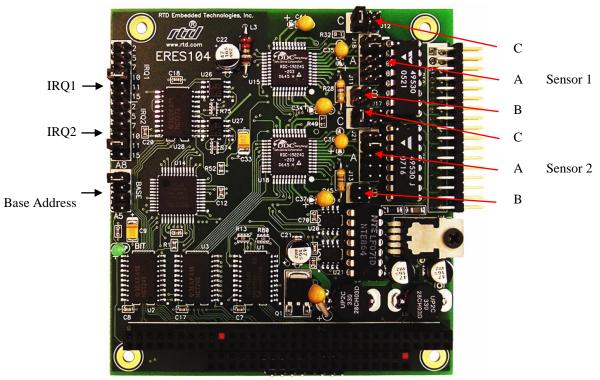

The figure below illustrates the factory jumper setting for the ERES104. The figure below shows the board layout and the locations of the jumpers. The factory setting is resolver input with internal reference on both sensors. The following paragraphs explain how to change the factory jumper settings to suit your specific application.

| Jumper Name  | Description         | Number of Jumpers | Factory Default |  |

|--------------|---------------------|-------------------|-----------------|--|

| Base Address | Base Address        | 4                 | 0x300           |  |

| IRQ1         | Interrupt Channel 1 | 6                 | 10              |  |

| IRQ2         | Interrupt Channel 2 | 6                 | 11              |  |

| Sensor 1 A   | Sensor selection    | 3                 | 1-2             |  |

| Sensor 1 B   | Sensor selection    | 5                 | 3-4             |  |

| Sensor 1 C   | Sensor selection    | 2                 | Open            |  |

| Sensor 2 A   | Sensor selection    | 3                 | 1-2             |  |

| Sensor 2 B   | Sensor selection    | 5                 | 3-4             |  |

| Sensor 2 C   | Sensor selection    | 2                 | Open            |  |

Figure 2-1: Board layout showing jumper locations

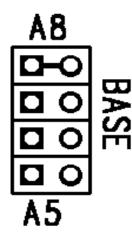

# Base Address jumpers

(Factory setting: 300h)

The most common cause of failure when you are first setting up your module is address contention. Some of your computers I/O space is already occupied by other internal I/O devices and expansion boards. When the ERES104 attempts to use its reserved I/O addresses already used by another peripheral device erratic performance may occur and data read from the board may be corrupted.

To avoid this problem make sure you set up the base address first using the five jumpers which let you choose from 32 different I/O addresses in your computers I/O map. Should the factory installed setting of 300h be unusable for your system configuration, you may change this setting to another using the options illustrated in Table 1-2. The table shows the switch settings and their corresponding values in hexadecimal values. Make sure you verify the correct location of the base address jumpers. When the jumper is removed it corresponds to a logical "0", connecting the jumper to a "1".

| Base Address<br>Hex / (Decimal) | Jumper Settings<br>A5 – A8 | Base Address<br>Hex / (Decimal) | Jumper Settings<br>A5 – A8 |

|---------------------------------|----------------------------|---------------------------------|----------------------------|

| 200/(512)                       | 0000                       | 300/(768)                       | 0001                       |

| 220/(544)                       | 1000                       | 320/(800)                       | 1001                       |

| 240/(576)                       | 0100                       | 340/(832)                       | 0101                       |

| 260/(592)                       | 1100                       | 360/(848)                       | 1101                       |

| 280/(512)                       | 0010                       | 380/(768)                       | 0011                       |

| 2A0/(544)                       | 1010                       | 3A0/(800)                       | 1011                       |

| 2C0/(576)                       | 0110                       | 3C0/(832)                       | 0111                       |

| 2E0/(592)                       | 1110                       | 3E0/(848)                       | 1111                       |

**Table 2-2 Base Address Jumper Settings**

Figure 2-2 Base Address jumper block (A8 to top, A5 to bottom)

### Interrupt channel

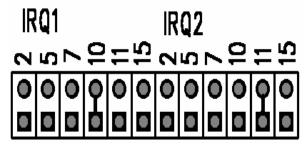

(Factory setting: IRQ1 = 10, IRQ2 = 11)

Each sensor connected to the ERES104 can assert a host interrupt using the hardware interrupts IRQ 2, 5, 7, 10, 11, 15. The selection of these interrupts is performed by closing one position on the jumper header connector marks IRQ1 for channel 1 or alternatively IRQ2 for channel 2. The interrupt header is illustrated below in the following figure.

Figure 2-3: Interrupt Selection Jumpers

The interrupt is caused by an external trigger event that has transferred the storage latch data to the output latch of the isolated digital output stage.

## Sensor 1 and Sensor 2 Configuration

(Factory setting: Differential Resolver)

The sensor configuration jumper blocks consist of 3 parts A, B and C. The jumper blocks are identical for channels 1 and 2 and are located on top of each other on the board.

| Sensor Type            | J10 Connections             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Jumper |     | r   | Picture                                                      |  |

|------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|--------------------------------------------------------------|--|

|                        | Sensor 1                    | Sensor 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Α      | В   | С   |                                                              |  |

| Differential Resolver  |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     | 1-2 | J12 or J17 0 0 0 2 4 6 C<br>0 0 1 3 5                        |  |

| Use                    | 20 8                        | 20 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |     |     |                                                              |  |

| DDC-49530 (11.8V)      | 20 – Sin+<br>19 – Sin-      | 28 – Sin+<br>27 – Sin-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-4    |     |     | <b>G</b> 0 3-4                                               |  |

| or<br>DDC-49590 (90 V) | $13 - 5m^{-1}$<br>23 - Cos+ | 27 - Sm - 31 - Cos + | 5-4    |     |     | J18 or J21 0 0 5-6 A                                         |  |

| or                     | 22 – Cos-                   | 30 – Cos-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |     |     | 0 0 7-8                                                      |  |

| DDC-76037 (2V)         |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |     | 0 0 9-10                                                     |  |

| (Default setting)      |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        | OFF |     | J11 or J13 $\bigcirc \bigcirc 24$<br>$\square \bigcirc 13$ B |  |

|                        |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |     |                                                              |  |

Table 2-3 Jumper configuration for the Sensor configuration terminal blocks

| Sensor Type                                                                                        | J10 Connections                                  |                                                  |                    | Jumper     |            | Picture                                                                                                                            |  |

|----------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------|------------|------------|------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                    | Sensor 1                                         | Sensor 2                                         | Α                  | В          | С          |                                                                                                                                    |  |

| Inductosyn                                                                                         |                                                  |                                                  |                    |            | 1-2        | J12 or J17 0 0 2 4 6 C<br>0 0 1 3 5                                                                                                |  |

| (Special case of<br>resolver requires<br>external preamplifier)<br>2 Vrms input with<br>any R-pack | 20 - Sin+<br>19 - Sin-<br>23 - Cos+<br>22 - Cos- | 28 - Sin+<br>27 - Sin-<br>31 - Cos+<br>30 - Cos- | 1-2<br>5-6<br>7-8  |            |            | J18 or J21<br>J18 or J21<br>J18 or J21<br>J18 or J21<br>J12<br>J1-2<br>J-2<br>J-2<br>J-2<br>J-2<br>J-2<br>J-2<br>J-2<br>J          |  |

|                                                                                                    |                                                  |                                                  |                    | OFF        |            | J11 or J13 $\bigcirc \bigcirc 24$<br>$\square \bigcirc 13$ B                                                                       |  |

| Syncro                                                                                             |                                                  |                                                  |                    |            | 3-4<br>5-6 | J12 or J17 O 2 4 6 C 1 3 5 C                                                                                                       |  |

| Use<br>DDC-49530 (11.8V)<br>or<br>DDC-49590 (90V)<br>or                                            | 19 - S1<br>24 - S2<br>20 - S3                    | 27 - S1<br>32 - S2<br>28 - S3                    | 5-6                |            |            | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                             |  |

| DDC-76037 (2V)                                                                                     |                                                  |                                                  |                    | 1-2<br>3-4 |            | J11 or J13                                                                                                                         |  |

| LVDT/RVDT                                                                                          |                                                  |                                                  |                    |            | OFF        | J12 or J17 0 0 0 2 4 6 C<br>0 0 1 3 5                                                                                              |  |

| 2 Vrms input with<br>any R-Pack<br>Open B1 and/or B2                                               |                                                  |                                                  | 1-2<br>7-8<br>9-10 |            |            | J18 or J21<br>J18 or J21<br>J18 or J21<br>J18 or J21<br>J1-2<br>J1-2<br>J1-2<br>J-2<br>J-2<br>J-2<br>J-2<br>J-2<br>J-2<br>J-2<br>J |  |

|                                                                                                    |                                                  |                                                  |                    | OFF        |            | $\begin{array}{c c} 0 & 0 & 2 & 4 \\ \hline 111 \text{ or } J13 & 0 & 1 & 3 & B \end{array}$                                       |  |

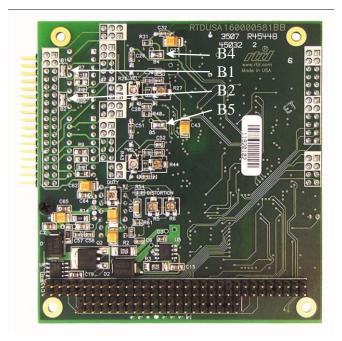

# Solder Jumpers

Figure 2-4 Board layout showing solder jumper locations

| Table 2-4 | Solder | jumper | configuration: |

|-----------|--------|--------|----------------|

|-----------|--------|--------|----------------|

| Solder | Open                                 | Short                                                  | Factory |

|--------|--------------------------------------|--------------------------------------------------------|---------|

| Jumper | Function                             | Function                                               | Default |

| B1     | Use external excitation for sensor 1 | Use internal excitation for sensor 1                   | Short   |

| B2     | Use external excitation for sensor 2 | Use internal excitation for sensor 1                   | Short   |

| B3     | Unused                               | Unused                                                 | Unused  |

| B4     | Isolated analog ground for sensor 1  | Analog ground connected to digital ground for sensor 1 | Short   |

| B5     | Isolated analog ground for sensor 2  | Analog ground connected to digital ground for sensor 2 | Short   |

# Chapter 3 INSTALLING THE ERES104

Keep your board in its antistatic bag until you are ready to install it to your system. When you are ready to install your board, remove it from the bag, and hold the board at the edges, try to avoid contact with the components or connectors. Please handle the board in an antistatic environment and use a grounded workbench for testing and handling of your hardware.

Before installing the board in your computer, check the jumper settings. Chapter 1 reviews the factory settings and how to change them. If you need to change any settings, refer to the appropriate instructions in Chapter 1. Note that incompatible jumper settings can result in unpredictable board operation and erratic response.

## **Recommended Procedure**

We recommend you follow the procedure below to ensure that stacking of the modules does not damage connectors or electronics.

- Turn off power to the PC/104 system or stack.

- Select and install standoffs to properly position the ERES104 on the PC/104 stack.

- Touch a grounded metal part of the stack to discharge any buildup of static electricity.

- Remove the ERES104 from its anti-static bag.

- Verify the jumper settings of the ERES104.

- Check that keying pins in the PC/104 bus connector are properly positioned.

- Hold the ERES104 by its edges and orient it so the bus connector pins line up with the matching connector on the stack.

- Gently and evenly press the ERES104 onto the PC/104 stack.

CAUTION: Do not force the board onto the stack! Wiggling the board or applying too much force may damage it. If the board does not readily press into place, remove it, check for bent pins or out-of-place keying pins, and try again.

# Chapter 4 CONNECTING THE ERES104

The following sections describe connectors of the ERES104.

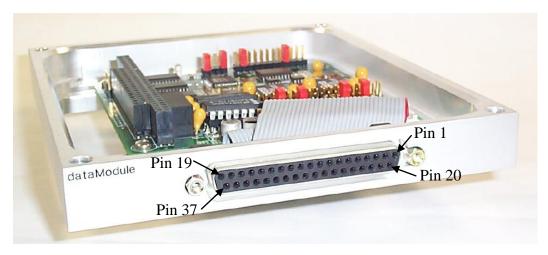

# Finding Pin 1 of Connectors

A white area silk-screened on the PC board indicates the pin 1 end of connectors. A square solder pad visible on the bottom of the PC board indicates pin 1.

Please make certain you have correctly identified pin 1 of a connector before you connect to it and attempt to use the ERES104.

# Syncro/Resolver Connector

The two sensor inputs are located in header connector J10 to the right side of the board. Signals are connected as described below:

| ERES104<br>J10 Pin # | Function                                                      | ERES104<br>J10 Pin #  | Function                   |

|----------------------|---------------------------------------------------------------|-----------------------|----------------------------|

| 1*                   | Excitation Output<br>REF_OSC1                                 | 2                     | Digital Ground             |

| 3                    | SIN1 (+S on RDC1)                                             | 4                     | Channel 1 Analog Ground    |

| 5                    | COS1 (+C on RDC1)                                             | 6                     | Channel 1 Analog Ground    |

| 7                    | External Reference Input 1<br>(Must have B1 open)<br>EXT_REF1 | 8                     | Channel 1 Analog Ground    |

| 9*                   | Excitation Output<br>REF_OSC2                                 | 10                    | Digital Ground             |

| 11                   | SIN2 (+S on RDC2)                                             | 12                    | Channel 2 Analog Ground    |

| 13                   | COS2 (+C on RDC2)                                             | 14                    | Channel 2 Analog Ground    |

| 15                   | External Reference Input 2<br>(Must have B2 open)<br>EXT REF2 | 16                    | Channel 2 Analog Ground    |

| 17                   | VEL1 (VEL output of RDC1)                                     | 18                    | VEL2 (VEL output of RDC2)  |

| 19                   | S1_1/S1_DR1                                                   | 20                    | S3_1/S3_DR1                |

| 21                   | Channel 1 Analog Ground                                       | 22                    | S4_DR1                     |

| 23                   | S2_DR1                                                        | 24                    | S2_DR1                     |

| 25                   | Same as Pin J10-7<br>EXT_REF1                                 | 26                    | Same as J10-15<br>EXT_REF2 |

| 27                   | S1_2/S1_DR2                                                   | 28                    | S3_2/S3_DR2                |

| 29                   | Channel 2 Analog Ground                                       | 30                    | S4_DR2                     |

| 31                   | S2_DR2                                                        | 32                    | S2_DR2                     |

| 33                   | Digital Ground                                                | 34                    | Digital Ground             |

| * REF_OSC1 an        | d REF_OSC2 are derived from the sa                            | me source and physica | ally connected together    |

#### Table 4-1 Sensor Interface connector J10 pin out

# /BIT LED

A LED on the ERES104 indicated that either Channel #1 or Channel #2 Built-in-test error is active. If no error exists on either channel the LED is off. Note that if you have only one sensor connected the LED is always lit since the other channel indicated loss of signal error through it's built in test signal.

| Note: | Two locations on the bus have mechanical keying pins to help prevent misconnection of the PC/104 bus. These keying pins are a part of the PC/104 standard, and we strongly recommend you leave them in place. |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | If you have other modules without keying pins, we suggest you modify them to include keying.                                                                                                                  |

# Chapter 5 HARDWARE DESCRIPTION

This section describes the functionality of the vital subsections of the ERES104 board. These include the Resolver-to-Digital converters, Solid state Scott-T converter and Sine wave excitation oscillator.

Figure 5-1 ERES104 Block diagram

#### BELOW ARE LISTED THE EXTERNAL COMPONENT VALUES OF THE RDC-19220 RESOLVER-TO-DIGITAL CONVERTER. FOR MORE INFORMATION ON SELECTING THESE COMPONENTS, PLEASE REFER TO THE APPLICATION NOT DOCUMENTATION ON THE WEBSITE WWW.DDC-WEB.COM.

| Table 5-1 RD converter external | component values |

|---------------------------------|------------------|

|---------------------------------|------------------|

| RC     | 30K                                      |

|--------|------------------------------------------|

| RS     | 53K                                      |

| REF+   | INPUT RESISTANCE 2K                      |

| RV     | 39K WITH 20K TRIMPOT (CENTERED), EQ. 49K |

| CBW    | 4, 7nF                                   |

| RB     | 100K                                     |

| CBW/10 | 470 pF                                   |

### **Resolver to Digital Converters**

Two independent resolver-to-digital converters condition the sensor inputs. These versatile chips have programmable resolution and internal diagnostic functions. The control of these converters is performed by the host computer. These converters support a variety of operational modes provided by the circuitry onboard, these include Resolvers, Inductosyns, Syncros and LVDT's that can be converted with up to 16-bit resolution. The following passage will illustrate these connections.

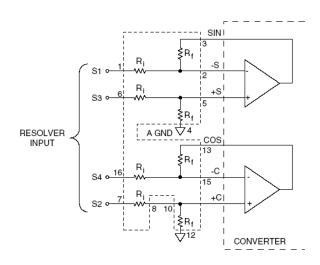

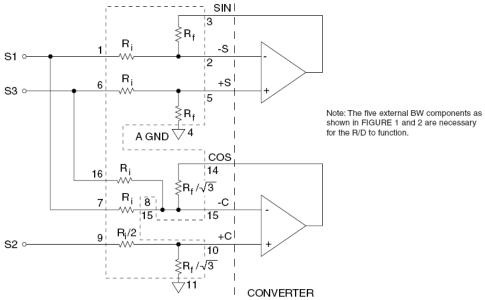

#### **Connecting Resolvers to ERES104**

The figure below illustrates a generic resolver connection scheme to the converter. The next figure shows a real connection that is used on the ERES104. The dashed line describes the onboard precision resistor pack that is used to precondition the voltage range of the sensors to a suitable level. If non-differentially connected resolvers are used they connect directly to the sin and cos inputs of the appropriate channels.

Notes:

1) S1 and S3, S2 and S4, and RH and RL should be ideally twisted shielded, with the shield tied to GND at the converter. 2) For 2V direct input use 10k $\Omega$  matched resistors for Ri & Rf.

#### Figure 5-2 Differential Resolver connection to a ERES104

1) S1 and S3, S2 and S4, and RH and RL should be ideally twisted shielded, with the shield tied to GND at the converter.

2) For DDC-49530 or DDC-57470: Ri = 70.8 kΩ, 11.8 V input, synchro or resolver. For DDC-49590: Ri = 270 kΩ, 90 V input, synchro or resolver.

3) Maximum additional error is 1 LSB using recommended thin film package.

4) Note on DC Offset Gains: Input options affect DC offset gains and therefore affect carrier frequency ripple and jitter. Offsets gains associated with differential mode, (offset gain for differential configuration = 1 + RF/RI) and direct mode (offset gain for direct configuration = 1), show differential will always be higher. Higher DC offsets cause higher carrier frequency ripple due to demodulation process. This carrier frequency ripple because it is riding on the top of the DC error signal causes jitter. A higher carrier frequency vs bandwidth ratio will help decrease ripple and jitter associated with offsets. Summary: R/D's with differential inputs are more susceptible to offset problems than R/D's in single ended mode. RD's in higher resolutions, such as 16 bit, will further compound offset issues due to higher internal voltage gains. Although the differential configuration has a higher DC offset gain, the differential configuration's common mode noise rejection makes it the preferred input option. The tradeoffs should be considered on a design to design basis. Also refer to FAQ-GIQ-021.

#### Figure 5-3 Differential Resolver input using DDC-49530 (11.8V), DDC-49590 (90V), or DDC-76037 (2V)

Notes:

- S1 is pin 19, S2 is pin 23, S3 is pin 20, and S4 is pin 22 of J10 as an example for channel 1.

- S1 is pin 27, S2 is pin 31, S3 is pin 28, and S4 is pin 30 of J10 as an example for channel 2.

- The resistors inside the dashed lines are in the DDC-49530 (11.8V), DDC-49590 (90V), or DDC-76037 (2V)

- Connect A jumper 3-4; and C jumper 1-2

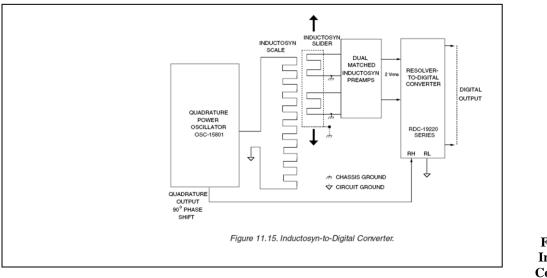

#### **Connecting Inductosyn to ERES104**

The ERES104 can be used to interface to Inductosyn type scales. The Inductosyn scale output is very low, in the range of 2-10mV pp. The signal is identical to that of a resolver. From the point of view of the RD-converter the Inductosyn signal must be preamplified to the level of 2V rms that is required by the chips. This must be performed by an external balanced preamplifier pair external to the ERES104. Please consult the factory for extra assistance on Inductosyn interfacing.

The onboard sine wave oscillator output current drive is limited. This means that it will not in many cases be sufficient to drive a low impedance Inductosyn slide that may have a resistance in the magnitude of Ohms.

#### Figure 5-4 Inductosyn Connections

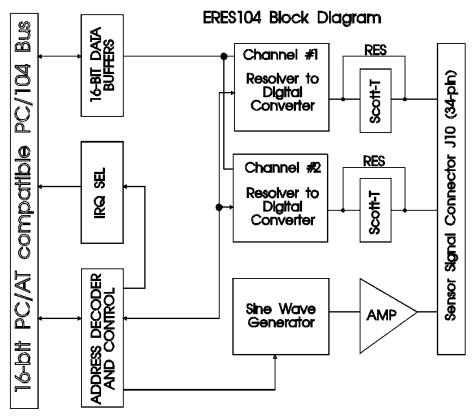

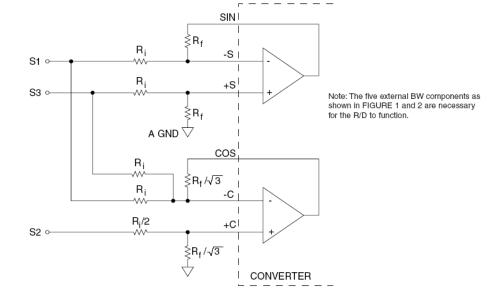

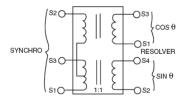

#### **Connecting Syncros to ERES104**

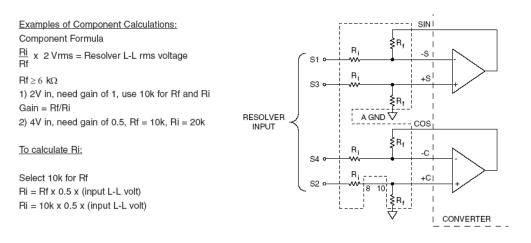

The figure below illustrates a generic syncro connection scheme to the converter. The next figure shows a real connection that is used on the ERES104. The dashed line describes the onboard precision resistor pack that is used to precondition the voltage range of the sensors to a suitable level of 2V.

$\frac{Ri}{Rf}$  x 2 Vrms = Synchro L-L rms voltage

$Rf \ge 6 k\Omega$

S1, S2, and S3 should be triple twisted shielded; RH and RL should be twisted shielded. In both cases the shield should be tied to GND at the converter.

#### **Figure 5-5 Syncro Input**

S1, S2, and S3 should be triple twisted shielded; RH and RL should be twisted shielded, In both cases the shield should be tied to GND at the converter. 90 V input = DDC-49590: Ri = 270 kΩ, 90 V input, synchro or resolver.

11.8 V input = DDC-49530 or DDC-57470: Ri = 70.8 kΩ, 11.8 V input, synchro or resolver.

Maximum additional error is 1 LSB when using recommended thin-film packages.

#### Figure 5-6: Syncro Input using DDC-49530 (11.8V), DDC-49590 (90V), or DDC-76037 (2V)

#### Notes:

- S1 is pin 19, S2 is in pin 24, and S3 is pin 20 of J10 as an example for channel #1.

- S1 is pin 27, S2 is pin 32, S3 is pin 28 of J10 as an example for channel #2

- The resistors inside the dashed lines are in the DDC-49530 (11.8V), DDC-49590 (90V), or DDC-76037 (2V)

- Connect A jumper: 5-6; B jumper: 1-2, 3-4; and C jumper: 3-4, 5-6.

#### **Connecting LVDT's to ERES104**

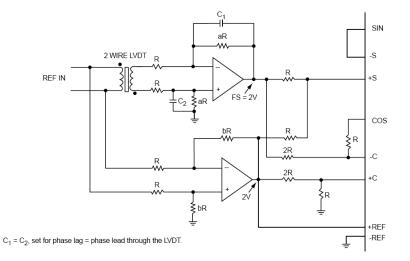

Standard 2-wire LVDT's interface to the Resover-to-Digital converters as illustrated below. Please consult the factory in applications involving LVDT interfacing.

Figure 5-7 A generic 2 wire LVDT connection to a converter

The precision amplifier circuitry presented above is external to the ERES104. Such LVDT preamplifier modules are available from RTD as standard products, or they may be designed by RTD to suit customer specific requirements. Please contact RTD for more information on different solutions for LVDT interfacing.

### Solid State Scott-T Converter

Syncro signals must be converted to SIN and COS resolver signals that can be directly be interfaced by the Resolver-to-Digital converters. The classical transformer coupled connection is often too cumbersome to use. The ERES104 module uses the internal operational amplifiers of the Resolver-to-Digital converters and precision resistors to implement the Solid State Scott-T circuit seen below. The most important design criteria in this connection is the perfect matching of the resistors. Precision is maintained by using a special trimmed resistor network together with the internal Opamps. These resistor networks are available for the three standard voltage levels 2V, 11.8V and 90V syncros. The resistor network value ratios are pre-trimmed to produce the 2V rms input signal required by the converters. Jumper fields A, B and C as discussed previously will select the right resistor configuration for the circuit.

You may separately purchase resistor networks for both standard voltages from RTD. They may be easily configured channel-by-channel by inserting the correct resistor network into the onboard sockets. The resistor networks are used as follows:

DDC-49530 are used with 11.8V inputs DDC-49590 are used with 90V inputs DDC-76037 are used with 2V inputs

Figure 1.10f. Scott-T Transformer.

Figure 1.10g. Solid-State Scott-T Transformer.

Figure 5-8 Solid State Scott-T converter circuit

### Sine Wave Excitation

A special programmable AC excitation source is available on the ERES104. It can be used to drive different sensors directly. The amplitude and frequency are programmable from the host interface.

The adjustment of the oscillator is performed with digital potentiometers providing a very stable non drifting performance. The digital adjustment potentiometers have 32 steps. The output adjustable frequency span is in the range of 400 Hz to 1.6K Hz.

Amplitude adjustment ranges from 0 to about 21 Vp-p. Adjustment of the gain can be performed in 32 steps also. Note that the settings of the frequency and gain are non-volatile and will be automatically stored in the EEPROM of the trim pots

The output of the reference oscillator source is buffered with a power Op-amp. It derives its power from the onboard DC/DC converter or the PC/104 bus. The onboard excitation source will work well with resolutions up to 16 bits. In case you desire to use 16-bit resolution you must make sure that cabling and shielding is performed carefully.

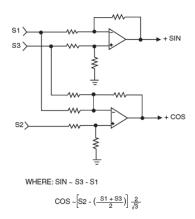

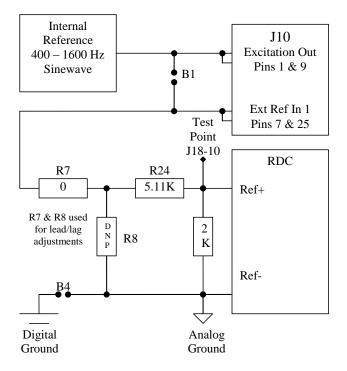

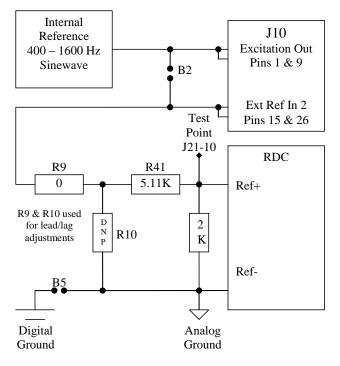

### **Reference Connection**

The reference feedback that is connected to the RD converter must fulfill two main criteria. Firstly the single-ended incoming signal must be +/-5V max and secondly it must be in phase with the incoming signal. In case the reference (excitation feedback) is too high in amplitude a series resistor may be added either externally, or by soldering one on the board. There are two locations reserved for voltage divider resistors R24 for channel #1 and R41 for channel #2. The default

resistors are 5.11K ohm and the input resistance is 2K, so the input signal can be +/-9V (18V p-p).

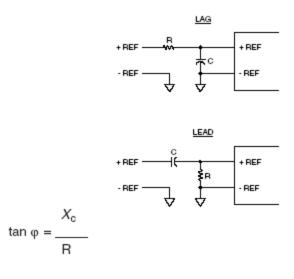

In case of reference signal phase lag or lead you can correct it by installing an external capacitor. Phase-shift correction will improve accuracy and quadrature rejection. The size of the capacitor can be selected as follows:

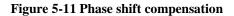

Xc = 1 / (2x PI x F) where F = excitation frequency and tan (Phi) = Xc/R and where Phi = desired phase shift for more information, please consult the component specific datasheet of the RD converter chips. On the solder side of the board are locations for an additional resistor/capacitor for phase correction for each channel. The components for channel #1 are labeled R8/R7; for channel #2 R9/R10. The factory default setting for R7 and R9 is 0 Ohms, R8 and R10 are do not populate (DNP) which is no phase adjustment.

Figure 5-9 Reference input for sensor 1

Figure 5-10 Reference input for sensor 2

Where  $\phi$  = desired phase-shift

$$X_{c} = \frac{1}{2\pi fc}$$

Where f = carrier frequency Where c = capacitance

Figure 5-12 Board layout showing reference components

Figure 5-13 Block diagram of ERES104 board

# Chapter 6 BOARD OPERATION AND PROGRAMMING

This section will describe how to program the ERES104 host interface from both directions as well as explain how the onboard Resolver-to-Digital converters and the programmable sine wave oscillators are programmed from the host computer.

## Defining the I/O Map

The I/O map of the ERES104 is shown in Table 6-1 below. As shown the module occupies 8 addresses. In the table BA stands for Base Address. The following sections describe the register contents of each address used in the I/O map.

| Address     | Function             | Direction |

|-------------|----------------------|-----------|

| BASE + 0    | INHIBIT CHANNEL #1   | WR        |

| BASE + 2    | INHIBIT CHANEL #2    | WR        |

| BASE + 4    | IRQ_CONF             | WR/RD     |

| BASE + 6    | BOARD_CNTRL          | WR/RD     |

| BASE + 8    | RD_RESOLUTION        | WR        |

| BASE + A    | INCREMENT            | WR/RD     |

| BASE + C    | /ENABLE CHANNEL #1   | RD        |

| BASE + E    | /ENABLE CHANNEL #2   | RD        |

| BASE + 10   | IRQ_CLEAR CHANNEL #1 | WR/RD     |

| BASE + 12   | IRQ_CLEAR CHANNEL #2 | WR/RD     |

| BASE + 400h | RTD ID Data          | RD        |

| BASE + 401h | RTD ID Data          | RD        |

| BASE+402h   | RTD ID Data          | RD        |

#### Table 6-1 ERES104 I/O Map

#### BASE+0h INHIBIT CHANNEL 1 (1b AFTER RESET)

The RD converter #1 Inhibit signal is controlled by this address. If this signal is set low (0), the RD converter stored the current reading in the internal counter into a latch from where the angle data can then be read.

| D0 | = | 1 | conversion being updated continuously |

|----|---|---|---------------------------------------|

| D0 | = | 0 | freeze counter to latch for reading   |

#### BASE+2h INHIBIT CHANNEL 2 (1b AFTER RESET)

The RD converter #2 Inhibit signal is controlled by this address. If this signal is set low (0), the RD converter stored the current reading in the internal counter into a latch from where the angle data can then be read.

| D0 | = | 1 | conversion being updated continuously |

|----|---|---|---------------------------------------|

| D0 | = | 0 | freeze counter to latch for reading   |

#### BASE+4h IRQ\_CONF (0000b AFTER RESET)

This register controls the host interrupts. The source of the interrupt can be either /BIT (built in test error) or alternatively CB (Controller busy; code has changed 1 LSB)

| D0 | = | IRQ enable bit, Channel 1; 0 disable, 1 enable    |

|----|---|---------------------------------------------------|

| D1 | = | IRQ enable bit, Channel 2; 0 disable, 1 enable    |

| D2 | = | IRQ source selection bit, Channel 1; 0 /BIT, 1 CB |

| D3 | = | IRQ source selection bit, Channel 2; 0 /BIT, 1 CB |

#### BASE+6h BOARD\_CNTRL (0111b AFTER RESET)

This register controls reset control as well as control of the digital trim pots.

| D0 | = | /Chip select of frequency control trim pot, active when 0       |

|----|---|-----------------------------------------------------------------|

| D1 | = | /Chip select of amplitude control trim pot, active when 0       |

| D2 | = | UP/DN control of digital trim pots, $1 = up$ , $0 = down$       |

| D3 | = | Enable reset, 0 enables host reset to reset resolution register |

|    |   | 1 disables host reset to reset resolution register              |

#### BASE+8h RD\_RESOLUTION (00h AFTER RESET)

This register controls the resolution of the RD converters

#### Table 6-2 Base +8 in Resolver Mode

| Mode             | Bit 7-6 | Bit 5-4 | Bit 3-2 | Bit 1-0 |

|------------------|---------|---------|---------|---------|

| Channel 1 10-bit | X-X     | 0-0     | X-X     | 0-0     |

| Channel 1 12-bit | X-X     | 0-0     | X-X     | 0-1     |

| Channel 1 14-bit | X-X     | 0-0     | X-X     | 1-0     |

| Channel 1 16-bit | X-X     | 0-0     | X-X     | 1-1     |

| Channel 2 10-bit | 0-0     | X-X     | 0-0     | X-X     |

| Channel 2 12-bit | 0-0     | X-X     | 0-1     | X-X     |

| Channel 2 14-bit | 0-0     | X-X     | 1-0     | X-X     |

| Channel 2 16-bit | 0-0     | X-X     | 1-1     | X-X     |

#### Table 6-3 Base +8 in LVDT Mode

| Mode             | Bit 7-6 | Bit 5-4 | Bit 3-2 | Bit 1-0 |

|------------------|---------|---------|---------|---------|

| Channel 1 8-bit  | X-X     | 1-0     | X-X     | 0-0     |

| Channel 1 10-bit | X-X     | 0-1     | X-X     | 0-0     |

| Channel 1 12-bit | X-X     | 1-1     | X-X     | 1-0     |

| Channel 1 14-bit | X-X     | 1-1     | X-X     | 0-0     |

| Channel 2 8-bit  | 1-0     | X-X     | 0-0     | X-X     |

| Channel 2 10-bit | 0-1     | X-X     | 0-1     | X-X     |

| Channel 2 12-bit | 1-1     | X-X     | 1-0     | X-X     |

| Channel 2 14-bit | 1-1     | X-X     | 0-0     | X-X     |

#### BASE+Ah INCREMENT DIGITAL POT

Writing to this address will increment the counter of the selected digital trim pots that control the excitation frequency and amplitude. The direction of the increment is set by the UP/DN bit in address BASE+6 BOARD\_CNTRL.

To increment the trim pots you must bring the increment signal low and return the signal high again under software control by writing to BASE+A a 0 and a 1. Please refer to the example programs on how to do this.

#### BASE+Ch READ CHANNEL #1

Reading from this address will output the RD converter #1 data to the host. Note that the ERES104 is a true AT board, and it will output a 16-bit value from addresses BASE+C. *The ERES104 does not support a XT host!*

#### BASE+Eh READ CHANNEL #2

Reading from this address will output the RD converter #2 data to the host. Note that the ERES104 is a true AT board, and it will output a 16-bit value from addresses BASE+E. *The ERES104 does not support a XT host!*

#### BASE+10h CLEAR CHANNEL #1 INTERRUPT

Reading or writing to this address will clear the pending interrupt condition for RD converter #1. Make sure you perform this clear operation before you exit from your ISR.

#### BASE+12h CLEAR CHANNEL #2 INTERRUPT

Reading or writing to this address will clear the pending interrupt condition for RD converter #2. Make sure you perform this clear operation before you exit from your ISR.

## Setting up the ERES104 board

1. Excitation selection, either onboard excitation or external excitation source. In case you need to interface to high voltage syncros or resolvers you must use an external reference source. If you use 12V resolvers or syncros you may use the onboard reference oscillator. Solder jumpers B1 and B2 must be set.

2. Program the frequency of the oscillator (400 to 1.6K Hz) by programming Trim pot #1. The frequency output can easily be measured with an oscilloscope from the pin #9 of the 8038 signal generator chip. The sine wave output has the same frequency as the square wave output at pin #9.

3. Program the excitation gain to give a 2Vrms at the sensor outputs. Note that the power amplifier is AC coupled. Changing the frequency will also affect the amplitude of the excitation gain.

4. The reference feedback is by factory default set to a voltage division of 5.11K over 2K. Change the 5.11K series resistor to suit the correct level of Reference feedback in case it is too low. It should be in the range of 2 - 5V p-p. You can measure the feedback reference signal of the RD converter after voltage scaling from pin #10 in header "A"

Closing solder blobs B1 and B2 on the board will automatically connect the onboard excitation source to the voltage divider for the reference feedback. B1 and B2 are located on the solder side of the board and are closed in the factory default condition. *In cases that you use external sensor excitation you must remove these solder jumpers.*

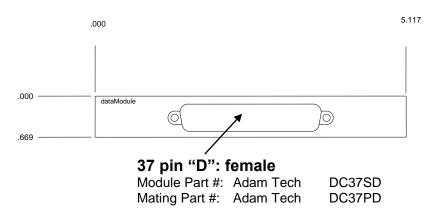

# Chapter 7 IDAN DIMENSIONS AND PINOUT IDAN-ERES104-62S Synchro/Resolver Interface Module

Figure 7-1: IDAN Mechanical Drawing

Drawings not to scale.

Figure 7-2 IDAN connector location

| IDAN Pin out<br>Syncro/Resolver – 37 pin "D" Connector (Female) |                                |           |               |

|-----------------------------------------------------------------|--------------------------------|-----------|---------------|

|                                                                 |                                |           | IDAN<br>Din # |

| Pin #                                                           |                                | J10 Pin # |               |

| 1                                                               | Excitation Output              | 1         |               |

|                                                                 | REF_OSC1                       |           |               |

| 2                                                               | SIN1 (+S on RDC1)              | 3         |               |

| 3                                                               | COS1 (+C on RDC1)              | 5         |               |

| 4                                                               | External Reference Input 1     | 7         |               |

|                                                                 | (Must have B1 open)            |           |               |

| ~                                                               | EXT_REF1                       | 0         |               |

| 5                                                               | Excitation Output (same J10-1) | 9         |               |

|                                                                 | REF_OSC2                       | 11        |               |

| 6                                                               | SIN2 (+S on RDC2)              | 11        |               |

| 7                                                               | COS2 (+C on RDC2)              | 13        |               |

| 8                                                               | External Reference Input 2     | 15        |               |

|                                                                 | (Must have B2 open)            |           |               |

| 0                                                               | EXT_REF2                       | 17        |               |

| 9                                                               | VEL1 (VEL output of RDC1)      | 17        |               |

| 10                                                              | S1_1/S1_DR1                    | 19        |               |

| 11                                                              | Channel 1 Analog Ground        | 21        |               |

| 12                                                              | S2_DR1                         | 23        |               |

| 13                                                              | Same as Pin J10-7 (EXT_REF1)   | 25        |               |

| 14                                                              | S1_2/S1_DR2                    | 27        |               |

| 15                                                              | Channel 2 Analog Ground        | 29        |               |

| 16                                                              | S2_DR2                         | 31        |               |

| 17                                                              | Digital Ground                 | 33        |               |

| 18                                                              | RESERVED                       | -         |               |

| 19                                                              | RESERVED                       | -         |               |

| 20                                                              | Digital Ground                 | 2         |               |

| 21                                                              | Channel 1 Analog Ground        | 4         |               |

| 22                                                              | Channel 1 Analog Ground        | 6         |               |

| 23                                                              | Channel 1 Analog Ground        | 8         |               |

| 24                                                              | Digital Ground                 | 10        |               |

| 25                                                              | Channel 2 Analog Ground        | 12        |               |

| 26                                                              | Channel 2 Analog Ground        | 14        |               |

| 27                                                              | Channel 2 Analog Ground        | 16        |               |

| 28                                                              | VEL2 (VEL output of RDC2)      | 18        |               |

| 29                                                              | S3_1/S3_DR1                    | 20        |               |

| 30                                                              | S4_DR1                         | 22        |               |

| 31                                                              | S2_DR1                         | 24        |               |

| 32                                                              | Same as J10-15 (EXT_REF2)      | 26        |               |

| 33                                                              | S3_2/S3_DR2                    | 28        |               |

| 34                                                              | S4_DR2                         | 30        |               |

| 35                                                              | S2_DR2                         | 32        |               |

| 36                                                              | Digital Ground                 | 34        |               |

| 37                                                              | RESERVED                       | -         |               |

#### Table 7-1 IDAN pin out

# Chapter 8 RETURN POLICY AND WARRENTY

# **Return Policy**

If you wish to return a product to the factory for service, please follow this procedure:

Read the Limited Warranty to familiarize yourself with our warranty policy.

Contact the factory for a Return Merchandise Authorization (RMA) number.

Please have the following available:

- Complete board name

- Board serial number

- A detailed description of the board's behavior

List the name of a contact person, familiar with technical details of the problem or situation, along with their phone and fax numbers, address, and e-mail address (if available).

#### List your shipping address!!

Indicate the shipping method you would like used to return the product to you. *We will not ship by next-day service without your pre-approval.*

Carefully package the product, using proper anti-static packaging.

Write the RMA number in large (1") letters on the outside of the package.

Return the package to:

RTD Embedded Technologies, Inc. 103 Innovation Blvd. State College PA 16803-0906 USA

# LIMITED WARRANTY

RTD Embedded Technologies, Inc. warrants the hardware and software products it manufactures and produces to be free from defects in materials and workmanship for one year following the date of shipment from RTD Embedded Technologies, INC. This warranty is limited to the original purchaser of product and is not transferable.