# **WESTERN AVIONICS**

# **MIL-STD-1553-USB**

# Hardware / Software User Manual

**UM 11061 Rev C**

© Western Avionics Ltd. 13/14 Shannon Free Zone Co. Clare Ireland

# **Table of Contents**

| 1 | GEN            | NERAL INFORMATION                                                | 6   |

|---|----------------|------------------------------------------------------------------|-----|

|   | 1.1            | INTRODUCTION                                                     | 6   |

|   | 1.2            | MANUAL DESCRIPTION                                               |     |

|   | 1.3            | CAPABILITIES                                                     |     |

|   | 1.3.1          |                                                                  |     |

|   | 1.3.2          |                                                                  |     |

|   | 1.3.3          | , , , , , , , , , , , , , , , , , , ,                            |     |

|   | 1.3.4          | - · · · · · · · · · · · · · · · · · · ·                          |     |

|   | 1.3.5<br>1.3.6 |                                                                  |     |

|   | 1.3.7          |                                                                  |     |

|   | 1.3.7          | THE IIB-1553-USB ARCHITECTURE                                    |     |

|   | 1.5            | PROTOCOL MANAGEMENT UNIT                                         |     |

|   | 1.6            | 1553B INTERFACE                                                  |     |

|   | 1.7            | FEATURES                                                         |     |

|   | 1.8            | SYSTEM CHARACTERISTICS AND SPECIFICATIONS                        |     |

|   | 1.9            | LIST 0F FURNISHED ITEMS                                          |     |

|   | 1.10           | LIST 0F RELATED PUBLICATIONS                                     |     |

|   | 1.11           | STORAGE DATA                                                     |     |

|   | 1.12           | TOOLS AND TEST EQUIPMENT                                         |     |

|   | 1.13           | CONNECTIONS, USB UNIT TO 1553 SYSTEM                             |     |

|   | 1.14           | CONNECTIONS, USB UNIT TO HOST SYSTEM                             |     |

|   | 1.15           | INDICATORS                                                       | 13  |

| 2 | INS'           | TALLATION AND PREPARATION FOR USE                                | 14  |

|   | 2.1            | GENERAL                                                          | 1.4 |

|   | 2.2            | PREPARATION FOR USE                                              |     |

|   | 2.3            | INSTALLATION OF 1553-USB                                         |     |

|   | 2.4            | RESET                                                            |     |

|   | 2.5            | SPECIFIC FEATURES                                                |     |

|   | 2.5.1          | l Control Register Features                                      | 15  |

|   | 2.5.2          |                                                                  |     |

|   | 2.5.3          | 00                                                               |     |

|   | 2.5.4          | 88                                                               |     |

|   |                | USB INTERFACE                                                    |     |

|   | 2.6.1          |                                                                  |     |

|   | 2.6.2          |                                                                  |     |

|   | 2.6.3          | r                                                                |     |

|   | 2.7            | 1553B INTERFACE                                                  |     |

|   | 2.7.1<br>2.7.2 |                                                                  |     |

|   | ,              |                                                                  |     |

| 3 | OPE            | ERATION                                                          | 17  |

|   | 3.1            | INTRODUCTION                                                     | 17  |

|   | 3.2            | CONVENTIONS                                                      |     |

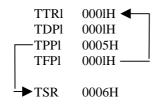

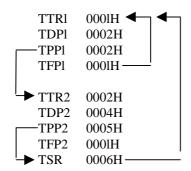

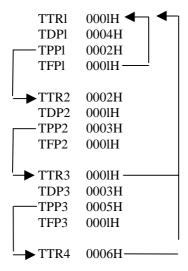

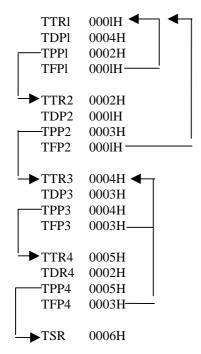

|   | 3.3            | ORGANISATION DIAGRAM                                             | 17  |

|   | 3.4            | BASE REGISTERS                                                   | 17  |

|   | 3.4.1          | Base Register Names and Locations                                | 19  |

|   | 3.4.2          |                                                                  |     |

|   |                | 4.2.1 Control Register (Write) (00H)                             |     |

|   |                | 4.2.2 Clock Hl Word (Read) (00H) (Clock LO Word (Read) (02H)     |     |

|   |                | 4.2.3 Command Register (CR) (04H)                                |     |

|   |                | 4.2.4 Status Register (SR) (06H)                                 |     |

|   |                | 4.2.5 Background Running Pointer (BRP) (08H)                     |     |

|   |                | 4.2.6 Insertion Running Pointer (IRP) (OAH)                      |     |

|   |                | 4.2.7 Reserved (OCH)                                             |     |

|   |                | 4.2.9 Reserved (10H)                                             |     |

|   |                | 4.2.10 HPIQAP (12H) High priority interrupt queue start address. |     |

|   |                | 4.2.11 Reserved (14H)                                            |     |

|   |                | · /                                                              | •   |

|         | 2 MIQAP (16H) Message interrupt queue start address |    |

|---------|-----------------------------------------------------|----|

|         | 3 Reserved (18H)                                    |    |

|         | 4 SRQAP (IAH) Status report queue start address.    |    |

|         | 5 Reserved (ICH)                                    |    |

|         | 6 RTSTAD (IEH) RT simulation table start address.   |    |

|         | 7 Reserved (20H)                                    |    |

|         | 8 Reserved (22H)                                    |    |

|         | 9 Toggle Buffer Address Offset (24H)                |    |

|         | O Set of Messages Start Address (26H)               |    |

|         | 1 Global RT Response Time Register (28H)            |    |

|         | 2 RT No Response Time-Out Register (2AH)            |    |

|         | 3 IRQ Selection Register (34H)                      |    |

|         | 4 Test and Set Register and SRQADP (3CH)            |    |

|         | 25 Reserved (46H)                                   |    |

|         | 26 PRI/SEC 1553B RT TX Inhibit HI-LO (48H – 4EH)    |    |

|         | MOTE TERMINAL SIMULATION TABLE                      |    |

| 3.5.1   | Simulation Type Word                                |    |

| 3.5.2   | Status Word                                         |    |

| 3.5.3   | 1553B Last Command Word                             |    |

| 3.5.4   | 1553B Bit Word                                      | 31 |

| BUS CO  | NTROLLER MODE OF OPERATION                          | 32 |

| 4.1 INT | RODUCTION                                           | 22 |

|         | SSAGE DESCRIPTOR BLOCK (MDB)                        |    |

| 4.2.1   | Message Number (00H)                                |    |

| 4.2.1   | 1553B Event Mask (02H)                              |    |

| 4.2.3   | Message Type Word (04H)                             |    |

| 4.2.4   | 1553B Message Error Phase Definition (06H)          |    |

| 4.2.5   | 1553B Message Error Description Word (08H)          |    |

| 4.2.6   | Address in Look-Up Table (0AH)                      |    |

| 4.2.7   | Command Word 1 (0CH)                                |    |

| 4.2.8   | Command Word 2 (0EH)                                |    |

| 4.2.9   | Retry Subroutine Absolute Address (14H)             |    |

| 4.2.10  | Inter-message Gap Time (18H)                        |    |

| 4.2.11  | Status Word 1 (ICH)                                 |    |

| 4.2.12  | Status Word 2 (lEH)                                 |    |

|         | ΓΑ BUFFERS SIMULATION AND MONITORING                |    |

| 4.3.1   | Look-Up-Table                                       | 39 |

| 4.3.2   | Data Descriptor Block                               | 39 |

| 4.3.2.1 | Option Mask (00H)                                   | 40 |

| 4.3.2.2 | Data Status Report (06H)                            | 40 |

| 4.3.2.3 | Toggle Frequency and Buffer Address HI (08H)        | 40 |

| 4.3.2.4 | Link Pointer to New DDB (0CH)                       | 41 |

| 4.3.2.5 |                                                     |    |

| 4.3.2.6 | · · · · · · · · · · · · · · · · · · ·               |    |

| 4.3.3   | Data Buffers                                        | 42 |

| 4.4 MO  | DE COMMANDS                                         | 43 |

| 4.5 INT | ERRUPT REQUESTS                                     | 44 |

| 4.5.1   | Interrupt Coding                                    | 44 |

| 4.5.2   | Set Message Interrupts                              |    |

| 4.5.3   | Message Status Report Oueue                         | 45 |

| 5 | MULT              | TPLE REMOTE TERMINAL MODE OF OPERATION                 | 46 |

|---|-------------------|--------------------------------------------------------|----|

|   | 5.1 IN            | TRODUCTION                                             | 46 |

|   |                   | OOK-UP-TABLES                                          |    |

|   | 5.3 M             | ODE COMMANDS SPECIFICATIONS                            | 47 |

|   | 5.4 D             | ATA WORDS STORAGE                                      | 47 |

|   | 5.5 15            | 53B ERROR INJECTION DEFINITION                         | 47 |

|   | 5.5.1             | Global RT Error Description Word (RT Simulation Table) | 48 |

|   | 5.5.2             | Message Error Injection Word (Look-up-Table)           | 49 |

|   | 5.6 IN            | TERRUPTS CODING                                        | 50 |

|   | 5.6.1             | Low and High Priority Interrupts (two word code)       | 50 |

|   | 5.6.2             | Message Interrupts (or set of messages interrupt)      | 50 |

|   | 5.6.3             | Status Report Queue (two words per report)             | 50 |

|   | 5.7 SF            | PECIFIC FUNCTIONS                                      | 50 |

|   | 5.7.1             | Data Message Reception                                 | 50 |

|   | 5.7.2             | Reception of Mode Commands Data Words                  |    |

|   | 5.7.3             | Mode Command "Synchronise with Data Word"              |    |

|   | 5.7.4             | Frequency Toggle                                       | 51 |

|   |                   |                                                        |    |

| 6 | CHRO              | NOLOGICAL BUS MONITOR MODE OF OPERATION                | 52 |

|   | 6.1 IN            | TRODUCTION                                             | 52 |

|   |                   | ASE REGISTERS                                          |    |

|   | 6.2.1             | Control Register (Write) (00H)                         |    |

|   | 6.2.2             | Command Register (CR)                                  |    |

|   | 6.2.3             | Status Register (SR)                                   |    |

|   | 6.2.4             | IRQ Selection Register (34H)                           |    |

|   | 6.2.5             | Load Clock HI/LO Registers (+38H1 / +3AH)              |    |

|   | 6.2.6             | Current Address Register (CAR) (+42H)                  |    |

|   | 6.2.7             | Trigger Occurrence Register (TOR) (+44H)               |    |

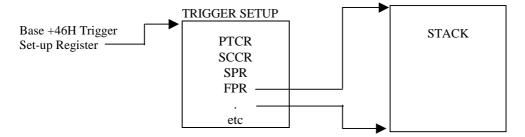

|   | 6.2.8             | Trigger Set-up Pointer (TSP) (+46H)                    |    |

|   | 6.2.8             |                                                        |    |

|   |                   | ETAILED TRIGGER DESCRIPTION                            |    |

|   | 6.4 ST            | TACK DATA FORMAT                                       | 67 |

|   | 6.4.1             | Previous Address Pointer                               | 67 |

|   | 6.4.2             | Time Stamp HI/LO                                       | 67 |

|   | 6.4.3             | Data                                                   | 67 |

|   | 6.4.4             | Next Address Pointer                                   | 68 |

|   | 6.4.5             | RT Response Time 1/2                                   | 68 |

|   | 6.4.6             | Flow Diagram                                           | 68 |

| 7 | SOFT              | WARE TOOLS AND SUPPORT                                 | 69 |

|   |                   | TRODUCTION                                             |    |

|   | 7.1.1             | Loading Software                                       |    |

|   | 7.1.1             | Up-grading Software                                    |    |

|   | 7.1.2             | Op-grading Software On-line support                    |    |

|   | 7.1.3<br>7.1.4    | Comments and suggestions                               |    |

|   | /.1. <del>4</del> | Commens and suggestions                                |    |

# **List of Figures**

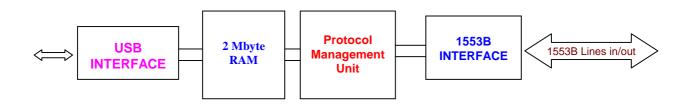

| Figure 1-1.                                      | 1553-USB Functional Block Diagram                                                                                 | 9        |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------|

| Figure 1-2.                                      | 1553-USB Output Connectors                                                                                        | 12       |

| Figure 1-3                                       | 1553-USB Input Connectors                                                                                         |          |

| Figure 1-4                                       | 1553-USB Indicators                                                                                               | 13       |

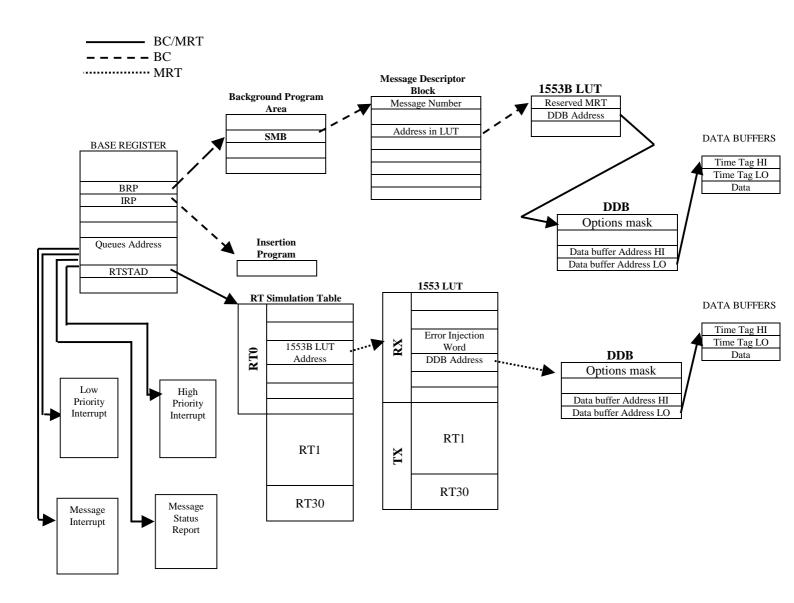

| Figure 3-1                                       | Organisation Diagram                                                                                              | 18       |

| Figure 3-2.                                      | Remote Terminal Simulation Table                                                                                  | 29       |

| Figure 4-1                                       | Bus Controller Organisation Diagram                                                                               | 32       |

| Figure 4-2.                                      | Data Buffers Simulation and Monitoring                                                                            | 38       |

| Figure 5-1                                       | Multiple Remote Terminal Organisation Diagram                                                                     | 46       |

|                                                  | List of Tables                                                                                                    |          |

| Table 3-1                                        | Base Register Names and Locations                                                                                 | 19       |

| Table 3-2                                        | Command Register (CR)                                                                                             | 21       |

| Table 3-3                                        | Communa register (Cit)                                                                                            |          |

| Table 4-1                                        | Status Register                                                                                                   | 22       |

| Tuble 1 1                                        | Status Register                                                                                                   | 33       |

| Table 4-2                                        | Status Register                                                                                                   | 33<br>39 |

| Table 4-2<br>Table 4-3                           | Status Register                                                                                                   |          |

| Table 4-2<br>Table 4-3<br>Table 6-1              | Status Register                                                                                                   |          |

| Table 4-2<br>Table 4-3<br>Table 6-1<br>Table 6-2 | Status Register  Message Descriptor Block  Data Descriptor Block  Data Buffers  Base Registers  Command Registers |          |

| Table 4-2<br>Table 4-3<br>Table 6-1              | Status Register                                                                                                   |          |

#### 1 GENERAL INFORMATION

#### 1.1 INTRODUCTION

The Western Avionics IIB-1553-USB is designed to meet the requirements of MIL-STD-1553B and STANAG 3838, within a small self-contained unit that can be connected to a host system with a standard USB cable.

The Western Avionics IIB-1553-USB provides one 1553 channel, dual redundant, to give a powerful and intelligent interface between a PCI or PDA based host equipment and the 1553B data bus. Bus Controller and Multi-Remote Terminal functions can operate both independently or simultaneously. An additional independent Chronological Bus Monitor function is provided. The Western Avionics IIB-1553-USB provides complete and comprehensive test and simulation functions for all applications in MIL-STD-1553B systems, in a small self-contained unit.

The IIB-1553-USB unit does not draw any power from the host system across the USB interface cable, having an internal Lithium battery for all internal power requirements. A complete power management system is incorporated into the unit, and it is supplied with an external PSU for battery charging.

#### 1.2 MANUAL DESCRIPTION

The following paragraphs provide a general description of the manual layout and content:

- Section 1 General Information contains a brief description of the manual, and a general

description of the Western Avionics IIB-1553-USB. This section also contains the

architecture, protocol management, MIL-STD-1553B interface information, instrument

specifications, information concerning accessories, furnished items and also safety

precautions.

- Section 2 Installation and Preparation for Use contains instructions on installation, preparation for use, self-test and reset of the Western Avionics IIB-1553-USB unit.

- Section 3 Operation contains a functional description of the Western Avionics IIB-1553-USB and operating procedures necessary to run the unit.

- Section 4 Bus Controller Mode of Operation contains information on the mode of operation for the Bus Controller function of the Western Avionics IIB-1553-USB unit.

- Section 5 Multiple Remote Terminal Mode of Operation contains information on the mode of operation for the Multiple Remote Terminal function of the Western Avionics IIB-1553-USB unit.

- Section 6 Chronological Bus Monitor Mode of Operation contains information on the mode of operation for the Chronological Bus Monitor function of the Western Avionics IIB-1553-USB unit.

- Section 7 Software tools and support by web access for up-grades contains information on the various software support packages that are available for this unit, together with information of obtaining up-grades, by web access.

#### 1.3 CAPABILITIES

The Western Avionics IIB-1553-USB provides the following capabilities and functions.

#### 1.3.1 General

- Memory mapped real-time universal USB interface.

- 2MByte of RAM.

- 1553B data protocol managed by a micro-controller providing flexibility and extensibility.

- Comprehensive Error Injection.

- External Triggers.

- Internal Self-tests.

### 1.3.2 Bus Controller (BC) Features (With MRT Simulation and Data Monitoring)

- Bus Control:

- Autonomous frame control using comprehensive set of instructions and message descriptor blocks.

- Acyclic message insertion.

- Error injection.

- Frame frequency selection.

- Inter-message gap selection.

- Response time-out selection.

- Bus events detection, mask, storage, and reporting (bus errors, status word bits).

- Simultaneous MRT Simulation (up to 31).

- Data Words Transfers:

- Data buffer simulation for the BC and the simulated RT's.

- Sub-address based data buffer access with data descriptor blocks defining each bus message;

- Multi-buffering (linked buffers or frequency-toggled buffers).

- Interrupt queues.

- Data status report.

- Data buffer time tagging (32 bits time tag).

- Simultaneous monitoring of all data buffers.

#### **1.3.3** Multiple Remote Terminal (MRT) Features

- Simulation:

- Up to 31 1553B RT simulations.

- Mode and Broadcast commands handling.

- Comprehensive Error Injection.

- Data Words Transfers:

- Data buffer simulation for simulated RTs.

- Sub-address based data buffer access offering the same powerful data buffering as in the bus controller mode.

- All non-transmitted data messages are monitored.

#### 1.3.4 Chronological Bus Monitor (CM) Features

- Capture of all bus activity in chronological stack, with time tagging of each message.

- Comprehensive multi-trigger facilities allowing selective capture and interrupts to be performed on complex data sequence.

- Cyclical stack up to 2Mbyte, with interrupt on completion of capture.

- All 1553B errors detected.

#### 1.3.5 Indicators

LED indicators are fitted to the front face of the USB unit, and are positioned as shown below. The three Status indicators are, PWR (green LED) showing that the power supply and battery supply is healthy, ACTY (yellow LED) which indicates 1553 activity on the bus, and FAIL (red LED) showing a fault in the 1553 hardware within the USB. The two Power indicators show CHARGING (green LED) indicating that the unit battery is accepting a charge current from the battery charger unit, and CHARGED (red LED) indicating that the charging process is completed.

#### 1.3.6 Power source

The USB power source is a 3.6 volt, 4.6Ah Lithium Ion battery, built into the base of the unit, which is charged through a charge management control circuit built into the USB unit. Power is supplied to the charge management control circuit from the DC in socket shown in Figure 2, which when connected to the matching 6V DC power supply unit furnished, will enable the USB unit to be run from the power supply directly, or enable the battery to be re-charged. The 1553-USB unit will run for a minimum of 8 hours from a fully charged battery, at maximum current demand from the 1553 hardware. The 1553-USB battery charging circuit restricts the charge current to 500 mA, which means that the unit will take approximately 9 hours to recharge from a flat battery condition.

#### 1.3.7 Power supply

The 6-volt power supply unit supplied with the USB unit has been selected to provide optimum input voltage and supply current for the USB units "on-card" battery charge management circuitry. Please ensure that the voltage selection switch located on the rear face of the PSU is set to 6V. Substitution of this PSU is not recommended. Should the user wish to use an alternative PSU, then this should be restricted to a 6 volt DC output type, as PSU's with supply voltages in excess of this value will cause undue heat dissipation within the USB unit. Excessive temperature rise within the USB will cause the battery charge cycle to be inhibited. This condition will be indicated by both the Charging and Charged LED's being on. Charging will remain inhibited until the temperature falls within pre-set threshold limits.

#### 1.4 The IIB-1553-USB ARCHITECTURE

The Western Avionics IIB-1553-USB unit is a memory mapped MIL-STD-1553B interface with high performance architecture and complex features. The IIB-1553-USB unit provides enhanced test and simulation functions for all modes of operation of a MIL-STD-1553B bus. The host equipment, using the on-board RAM, defines all configuration and data structures.

Figure 1-1. 1553-USB Functional Block Diagram

#### 1.5 PROTOCOL MANAGEMENT UNIT

A micro-controller based structure running at 40Mhz handles the management of the 1553B protocol for each of the operating modes (BC, MRT, BM). The micro-controller works each of the 1553B command, status and data words functions of its operating mode and the configuration tables in RAM. The micro-controller management unit allows flexibility and expandability for the bus control tasks and user interface.

#### 1.6 1553B INTERFACE

The 1553B interface is a dual redundant interface, which includes a standard dual redundant transceiver and a Manchester encoder/decoder with full error detection and error injection capabilities, which include:

- Manchester bit error

- Synch bit error

- Parity error

- Word length error

- Wrong bus error

- Both bus error

- Response time error

#### 1.7 FEATURES

The features of the Western Avionics IIB-1553-USB unit are listed as follows:

- USB revision 2.0 interface.

- Memory mapped real-time interface.

- 2MByte of RAM.

- Multiple interrupt queues for various events.

- 1553B data protocol managed by a micro-controller providing complete flexibility and extension capability.

- Error Injection and detection.

- External Triggers.

- Internal Self-tests.

# 1.8 SYSTEM CHARACTERISTICS AND SPECIFICATIONS

The characteristics and specifications of the Western Avionics IIB-1553-USB are listed as follows:

• Dimensions 200mm x 100mm x 50mm

Weight 480 grams

• Power usage +5Vdc @ 500 mAmps (Maximum)

Provided from internal battery pack

• Temperature:

Operating:  $0^{\circ}\text{C to } +50^{\circ}\text{C}$ Non-operating:  $-20^{\circ}\text{C to } +70^{\circ}\text{C}$

Humidity 5% – 95% Non-condensing

- MTBF (MIL 217F):

- 187,932 Hrs (Ground Benign @ 25°C)

#### • Front Panel Connectors:

•J1 (1553 Primary) Tri-axial connector (type BJ76) •J2 (1553 Secondary) Tri-axial connector (type BJ76)

•J3 (Signal I/O use) 9 pin sub-miniature "D" (type SDES9SN)

#### 1.9 LIST OF FURNISHED ITEMS

The following is a list of furnished items:

- Bus Analyser/Simulator, Model IIB-1553-USB

Power Supply Unit (PSU)

- 3. USB interface cable

- 4. User Manual UM 11061 (This document)

- 5. C drivers and Windows GUI installation disk.

- 6. C Driver manual

# 1.10 LIST OF RELATED PUBLICATIONS

The following is a list of related publications:

MIL-STD-1553 1.

#### 1.11 STORAGE DATA

As the USB unit contains electrostatic sensitive devices (ESD's), special storage and handling is required. Do not store near electrostatic, electromagnetic, magnetic or radiation fields.

## 1.12 TOOLS AND TEST EQUIPMENT

No special tools or test equipment is required to test the Western Avionics IIB-1553-USB unit.

#### 1.13 CONNECTIONS, USB UNIT TO 1553 SYSTEM

Connections from the USB to the 1553 system are made at the top face of the USB unit, as shown in Figure 1-2 below. Two sub-miniature tri-axial connectors (type BJ76) are provided for 1553 bus connections (Primary (J1) and Secondary (J2)) with conventional +ve 1553 signal wiring to the centre pin, -ve 1553 to the outer ring. A 9-pin sub-miniature 'D' type socket connector (type SDES9SN) is also provided at J3 for signal I/O use. This 9-pin connector is wired as follows:

| Pin number | Connection           | Comments                             |

|------------|----------------------|--------------------------------------|

| 1          | WRITEPROT            | Reserved, see Note below             |

| 2          | TRIG-IN (ANODE)      | Trigger input, anode connection      |

| 3          | TRIG-OUT (COLLECTOR) | Trigger output, collector connection |

| 4          | GROUND               |                                      |

| 5          | EXT-TRIG (EMITTER)   | External trigger, emitter            |

| 6          | TRIG-IN (CATHODE)    | Trigger input, cathode connection    |

| 7          | TRIG-OUT (EMITTER)   | Trigger output, emitter connection   |

| 8          | NOT USED             |                                      |

| 9          | +5V                  | +5V, reserved, see note below        |

NOTE: Pins 1 and 9 are reserved pins that are used with factory furnished adapter, in event of firmware upgrades and modifications that may be supplied. Do not use these connections for any other purpose, as damage to the unit may result.

Figure 1-2. 1553-USB Output Connectors

#### 1.14 CONNECTIONS, USB UNIT TO HOST SYSTEM

The 1553-USB is connected to the host system using the supplied USB interface cable, which connects to the USB unit at the Input side, located on the bottom face of the unit, as shown on Figure 1-3. On this same end, the Power (On/Off) switch is located to on the right, with a Reset switch on the left, and the DC in socket (for connection to the external PSU unit) to the left of this.

Figure 1-3 1553-USB Input Connectors

# 1.15 INDICATORS

Five LED indicators are provided on the unit, the functions of which are as follows.

PWR (Green LED) indicates healthy supply when unit is turned on.

ACTY (Yellow LED) indicates unit activity when unit is being used in BC, MRT or Monitor mode.

FAIL (Red LED) indicates failure of unit to pass self-test.

CHARGING (Green LED) indicates that the unit is charging the internal battery correctly, when connected to the external PSU.

CHARGED (Red LED) indicates that the internal battery is fully charged from the external PSU.

Layout of these indicators is as shown below.

Figure 1-4 1553-USB Indicators

# 2 INSTALLATION AND PREPARATION FOR USE

#### 2.1 GENERAL

On delivery, inspect the unit for possible damage. If it is damaged, notify the shipping company, and contact your distributor, or Western Avionics, for details of return procedure. When unpacking remove all protective covering and store covering and packing container, as unit may need to be reshipped at a later date.

#### **CAUTION**

The IIB-1553-USB unit contains Electrostatic Sensitive Devices (ESD's).

Observe ESD handling requirements, and do not ship or store near electro-static, electromagnetic, magnetic or radioactive fields.

#### 2.2 PREPARATION FOR USE

Prior to installing and using the Western Avionics 1553-USB, ensure that the unit is capable of operating by turning the unit on, and observing that the Power indicator (green LED) on the unit is lit. Should this fail to operate, then the unit will require connection to the external PSU unit through the DC socket, to charge up the internal battery, or supply power to the unit. The external PSU is supplied with various input connections to allow use on a wide variety of mains supplies, including 110 volt and 220 volt supplies.

#### 2.3 INSTALLATION OF 1553-USB

- 1. <u>Before</u> connecting the 1553-USB to the PC, install the GUI using the <u>setup\_WA.exe</u> supplied.

- 2. Connect the 1553-USB to the PC, and turn the unit on. The unit will perform system self-test on each channel for the BC, MRT and CM lasting approximately four seconds, during which time the fail LED (red) will remain lit, and extinguish on completion.

- 3. The PC will detect 'new device' and start the device wizard.

- 4. Do <u>not</u> let the wizard look for the best drivers. Direct the wizard manually to the USB\_DRVS subfolder within the GUI installation folder.

- 5. The PC will now a second device and start the device wizard

- 6. Do <u>not</u> let the wizard look for the best drivers. Direct the wizard manually to the USB\_DRVS subfolder within the GUI installation folder.

- 7. Once you have installed the USB drivers, go to the "**Device Manager**" and look in the "**Ports".** You should have the new virtual **Comm** port defined for the USB interface.

- 8. Highlight the USB serial port and right click.

- 9. Select Properties and then Select Port settings.

- 10. Click advanced

- 11. In BM features select a latency of 2 (2ms).

- 12. Click OK.

- 13. Launch the GUI and in the hardware set-up, select the USB 1553 type, and set the **Comm** port number to the value defined in the **Device Manager.**

- 14. You are now ready to use the 1553 USB interface.

# 2.4 RESET

The Western Avionics 1553-USB hardware and firmware are reset as follows:

# Reset:

- Power-up and power-down.

- Bit location in control register accessible by the USB interface.

#### 2.5 SPECIFIC FEATURES

#### 2.5.1 Control Register Features

This is a 16-bit write only register accessible from the USB interface.

This register is mapped into the memory field. The features are as follows:

- Hardware reset

- Three prioritised interrupts to the local on-board processor for indication and control

- Acknowledge Interrupt

#### 2.5.2 Counter Features

This 32-bit counter is a free running counter with a  $0.5\mu s$  or  $10\mu s$  LSB and can be read from a memory mapped location via the USB interface. The counter should be read in a single 32-bit access. The counter can be updated and used by the on-board processor as follows-

• *Used:* Data buffers time tagging

Frame cycles control Bus Monitoring

• *Updated:* User request

1553B command

#### 2.5.3 Trigger-In Features

Trigger-In enters the unit through a 9-way socket connector and then an opto-coupler. Inputs to this feature can be used for hardware starts of the major and/or minor frames, or external trigger for the bus monitor.

## 2.5.4 Trigger Out Features

Trigger-Out is in fact a bit in a register accessible by the on-board processor to indicate to the external world that an event has been detected. This event can be as follows:

- Beginning of the major and/or minor frames

- Beginning of a message

- Bus Monitor trigger detected

Trigger-Out exits the unit through an opto-coupler and a nine-way socket connector on the front panel.

#### 2.6 USB INTERFACE

#### 2.6.1 Introduction

The USB interface on the Western Avionics IIB-1553-USB unit conforms to Revision 2.0 of the USB specification.

#### 2.6.2 Electrical Characteristics

• All driving and loading rules are respected.

# 2.6.3 Capabilities

The Western Avionics IIB-1553-USB unit is used as a 2Mbyte field.

- R/W Static RAM (2Mbyte).

- Read only 32-bit counter (one 32-bit access)

- Write only 16-bit register (one 16-bit access).

#### **2.7 1553B INTERFACE**

#### 2.7.1 Introduction

The 1553B interface matches the MIL-STD-1553B Standard.

#### 2.7.2 Electrical Characteristics

The 1553B interface provides one dual redundant bus.

Primary bus J1.Secondary bus. J2

The 1553B interface can be programmed to be:

- Transformer coupled.

- Direct coupled.

# **3 OPERATION**

#### 3.1 INTRODUCTION

The Western Avionics IIB-1553-USB provides a single dual redundant 1553 channel, which provides Bus Controller (BC), Multi-Remote Terminal (MRT), functions, which may be run either independently or simultaneously. An independent Chronological Bus Monitor (CM) is also provided. In order to run any of these functions, information must be loaded into specific fixed register locations (Base Registers). Some of these registers contain pointers to other areas of memory/registers. The selection of these pointers is left up to the discretion of the user. Therefore, memory blocks can be positioned in the on-board memory to suit user requirements. This set-up means that fixed position registers are minimal.

#### 3.2 CONVENTIONS

- 1. BASE = Base Address of this unit.

- 2. The memory range BASE+10000H to End of Memory is reserved for the 1553B data blocks. All other data must reside in the first 64Kbytes.

After a Power-On:

- On-board processor doing its power-on initialisation,

- Then executing Self-Test.

- Then waiting for a user command.

- DSI per default (insertion program is disabled)

# 3.3 ORGANISATION DIAGRAM

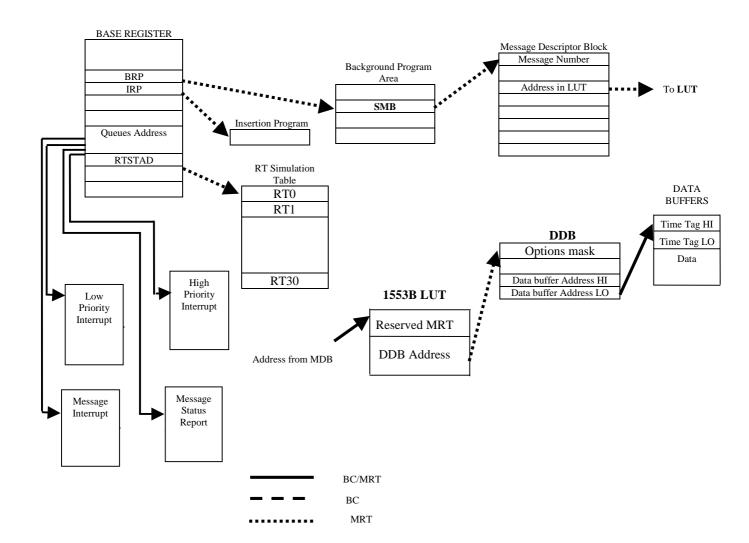

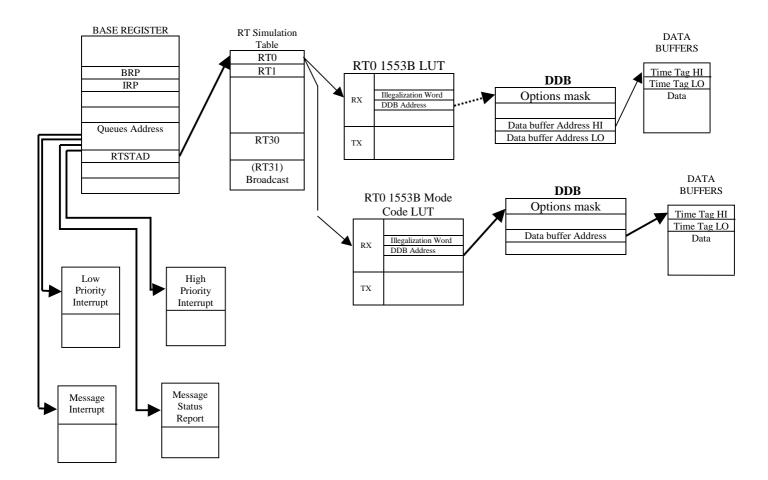

The organisation diagram figure 3-1 shows how the functional areas of the Western Avionics IIB-1553-USB unit can be controlled.

#### 3.4 BASE REGISTERS

The only fixed position registers are the Base Registers. The Base Registers are the starting points for a description of operation of any of the three modes of operation, (BC, MRT and CM).

They are located starting at the units Base Address.

Figure 3-1 Organisation Diagram

# 3.4.1 Base Register Names and Locations

The names and locations of the Base Registers are contained in table 3-1.

Table 3-1 Base Register Names and Locations

| BASE | Control Register(Write)/Clock HI Word (Read)        |

|------|-----------------------------------------------------|

| +02H | Clock LO Word (Read only)                           |

| +04H | Command Register (CR)                               |

| +06H | Status Register (SR)                                |

| +08H | Background Running Pointer (BRP) Address of Program |

| +0AH | Insertion Running Pointer (IRP) Address of Program  |

| +0CH | Reserved                                            |

| +0EH | Low Priority Interrupt Queue Start Address Pointer  |

| +10H | Reserved                                            |

| +12H | High Priority Interrupt Queue Start Address Pointer |

| +14H | Reserved                                            |

| +16H | Message Interrupt Queue Start Address Pointer       |

| +18H | Reserved                                            |

| +lAH | Status Report Queue Start Address Pointer           |

| +lCH | Reserved                                            |

| +lEH | RT Simulation Table Address Register (RTSTAD)       |

| +20H | Amplitude Register                                  |

| +22H | Coupling Register                                   |

| +24H | Toggle Buffer Address Offset (MSB=1 Global Enable)  |

| +26H | SET OF MESSAGES Start Address                       |

| +28H | Global RT Response Time Register (µs)               |

| +2AH | RT No Response Timeout Register (µs)                |

| +2CH | Reserved                                            |

| +2EH | Reserved                                            |

| +30H | Reserved                                            |

| +32H | Reserved                                            |

| +34H | IRQ Selection Register                              |

| +36H | Minor Frame Counter Register                        |

| +38H | Load Clock HI Register                              |

| +3AH | Load Clock LO Register                              |

| +3CH | Test and Set register (TASR)                        |

| +3EH | Service Request Queue Address Pointer (SRQADSP)     |

| +40H | Cycling Interrupt Update Register                   |

| +42H | Monitor Current Address Register (CAR)              |

| +44H | Monitor Trigger Occurrence Register (TOR)           |

| +46H | Monitor Trigger Set-up Pointer (TSP)                |

| +48H | PRI Bus 1553B RT TX inhibit bits Hl                 |

| +4AH | PRI Bus 1553B RT TX inhibit bits LO                 |

| +4CH | SEC Bus 1553B RT TX inhibit bits HI                 |

| +4EH | SEC Bus 1553B RT TX inhibit bits LO                 |

| +50H | Reserved                                            |

| +52H | Reserved                                            |

| +54H | Reserved                                            |

| +56H | Reserved                                            |

|      |                                                     |

#### 3.4.2 Base Register Descriptions

The Base Register functions are defined in the following paragraphs.

#### 3.4.2.1 Control Register (Write) (00H)

| D15 | D14 | D13 | D12 | D11 | D10 | D09 | D08 | D07 | D06 | D05 | D04 | D03 | D02 | D01 | D00 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | HR  | 0   | IEN | IRQ | 0   | 0   | 0   | C1  | C0  |

C0 Clear => Command Request

Cl Clear => Insertion Request

HR Clear => Hardware RESET

If IEN is set and IRQ is set then interrupt line will be cleared.

If IEN is set and IRQ is clear then the interrupt line will be asserted (for test purposes only).

If IEN is clear the value of IRQ is unaffected.

Note: This register must be accessed to clear the interrupt during an interrupt service routine.

Examples:

- 1. 0102H generates a command request.

- 2. 0163H clears the interrupt line.

#### 3.4.2.2 Clock HI Word (Read) (00H) (Clock LO Word (Read) (02H)

- Local Clock Reading: CK (HI-LO)

- Read as a 32 bit word.

- Update Local Clock by the User:

- Write the new value in the registers (LOAD Clock (Hl-LO) Registers).

- Write the \*LOAD CK code (000CH) in the command register.

- Write CO = 0 in the control register.

- After executing the command, the on-board processor sets CO to 1.

(\* = See Command Register below)

#### • Synchronise Clock:

• If the above procedure is carried out using the synchronise clock command (0010H) the contents of LOAD Clock Hl will be added to the current clock value as a 32-bit signal offset.

# 3.4.2.3 Command Register (CR) (04H)

Prior to clearing the command request bit (CO) in the control register, the user must first test that the command register is clear. When the command register is clear the user can insert the next command to be executed. After the command is loaded, bit CO in the control register can be cleared. When the command register clears, the unit is ready for a new command. Refer to table 3-2.

Table 3-2 Command Register (CR)

| CODE  | COMMAND           |

|-------|-------------------|

| 0000Н | Illegal           |

| 0001H | GO TO BC MODE     |

| 0002H | GO TO MRT MODE    |

| 0003Н | GO TO MON MODE    |

| 0004Н | BC COLD Start     |

| 0005H | BC WARM Start     |

| 0006Н | BC STOP           |

| 0007Н | MRT COLD Start    |

| 0008H | MRT WARM Start    |

| 0009Н | MRT STOP          |

| 000AH | PAUSE             |

| 000BH | UNPAUSE           |

| 000CH | LOAD CLOCK        |

| 000DH | SELFTEST          |

| 000EH | RUN MONITOR       |

| 000FH | STOP MONITOR      |

| 0010H | Synchronise CLOCK |

**NOTE**: PAUSE = Stop the Local clock. UNPAUSE = Restart the Local Clock.

# **3.4.2.4** Status Register (SR) (06H)

The status register will contain a word reflecting the status of the unit as shown in table 3-3.

Table 3-3 Status Register

| CODE  | STATUS                           |

|-------|----------------------------------|

| 0001H | BC IDLE                          |

| 0002H | MRT IDLE                         |

| 0003H | MON IDLE                         |

| 0004H | BC RUNNING                       |

| 0005H | BC INSERTION RUNNING             |

| 8004H | BC PAUSED (Background)           |

| 8005H | BC PAUSED (Insertion)            |

| 9004H | EXECUTING SOFTWARE PAUSE (SWPSE) |

| A004H | EXECUTING HARDWARE PAUSE (HWPSE) |

| 0006Н | MRT RUNNING                      |

| 8006H | MRT PAUSED                       |

| 0007H | MON RUNNING                      |

| 0008H | MON RUNNING                      |

| XXX8H | EXECUTING SELFTEST               |

|       | FINISHED SELFTEST                |

The status register will contain the following information after completion of self-test.

| D15 | D14 | D13 | D12 | D11 | D10 | D09 | D08 | D07 | D06 | D05 | D04 | D03 | D02 | D01 | D00 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1   | 0   | 0   | LS  | 0   | 0   | LC  | M5  | M4  | M3  | M2  | M1  | 1   | 0   | 0   | 0   |

1553B Interface Test Failed LS 1 LC 1 Local Clock Test Failed M5 =1 Memory Test 5 Failed M4 1 Memory Test 4 Failed M3 = Memory Test 3 Failed 1 Memory Test 2 Failed M2= 1 Memory Test 1 Failed M1 1

Several bits can be set simultaneously. If no self-test errors are detected the code in the status register will be 8008H.

# 3.4.2.5 Background Running Pointer (BRP) (08H)

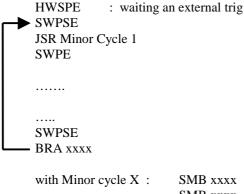

In the BC mode, the Background Running Pointer (BRP) directs the firmware to the location of a background program, which can be used to organise the message sequencing. Before sending a BC start the user must initialise the BRP. BRP is updated by the on-board processor after executing a BC STOP command. Table 3-4 is a list of the possible instructions with descriptions and examples.

**Table 3-4. Instruction Set Background Program**

| DELAY        | :   | H0000 | XXXXH | XXXX= Delay LSB of 10μs                          |     |

|--------------|-----|-------|-------|--------------------------------------------------|-----|

| NOPl         | :   | 0001H |       | PC = PC + l                                      |     |

| NOP2         | :   | 0002H |       | PC = PC + 2                                      |     |

| NOP3         | :   | 0003H |       | PC = PC + 3                                      |     |

| BSR          | :   | 0004H | XXXXH | XXXX = 16 bit signed branch to subroutine        |     |

| BRA          | :   | 0006H | XXXXH | XXXX = 16 bit signed branch                      |     |

| JMP          | :   | 0007H | XXXXH | XXXX = 16 bit absolute address for jump          |     |

| RTS          | :   | H8000 |       | Return from subroutine                           |     |

| RTI          | :   | 0009H |       | Return from insertion routine                    |     |

| ENI          | :   | 000AH |       | Enable program insertion                         |     |

| DSI          | :   | 000BH |       | Disable program insertion                        |     |

| LOOP         | :   | 000CH | XXXXH | Load loop counter, with value XXXX               |     |

| <b>DBNE</b>  | :   | 000DH | XXXXH | LOOP = LOOP-1, If $<>O$ branch signed offset $X$ | XXX |

| <b>INITF</b> | :   | 000EH | XXXXH | Initialise frame duration to XXXX (LSB = 10uS)   |     |

| <b>SWPSE</b> | :   | 000FH |       | Wait for new on-board start of frame             |     |

| HALT         | :   | 0010H |       | End of BC program                                |     |

| SITL         | :   | 0011H | XXXXH | Set low priority IRQ. Push XXXX on LO queue      |     |

| SITH         | :   | 0012H | XXXXH | Set high priority IRQ. Push XXXX on HI queue     |     |

| <b>HWPSE</b> | :   | 0013H |       | wait for external Trig LO-HI for new frame       |     |

| SMB          | :   | 0014H | XXXXH | Send message. XXXXH = absolute address of MDB    |     |

| TRGOUT       | ` : | 0015H | XXXXH | Trig out to the XXXXH level                      |     |

# • Instructions:

- NOP (1, 2, 3);

- By a NOPx, the user can replace one, two or three instruction words.

# BSR,BRA,DNBE;

- The offset is defined in bytes count (always even offset).

- BSR;

- 15 levels of subroutines available.

#### • TRGOUT xxxx

- Instructions to put TRIGOUT at 0 if xxxx = 0000H; or 1 if xxxx = 0001H.

- On power-on, the output is on 0 level (per default).

#### LOOP xxxx;

- Load loop counter with value XXXX.

- Only one level of loop.

#### • INITF xxxx;

- XXXX = Minor frame duration (minor cycle time).

- 10 µs for the LSB; the value for 20ms is 7D0H.

- It must be initialised at the beginning of the background program.

- This instruction resets the minor frame counter register.

# SWPSE (Software Pause);

• To be put at the end of each minor cycle instruction list with the minor frame duration utility to have automatic minor frame restart.

# Examples:

**INITF** xxxx

SMB xxxx

RTS

• Insertion Commands can be executed during SWPSE state.

#### • HALT;

- On completion of this instruction the unit will return to the BC idle state

- To re-start the unit: BC (Cold Warm) Start (command register).

# SITH xxxx / SITL xxxx;

The on-board processor puts the value (code) xxxx in the cycling FIFO's.

H => High Priority, L => Low Priority.

# • HWPSE (Hardware Pause);

- Restart by the external Trig In (external CK)

- All the registers are not initialised:....

- Used to synchronise messages of minor frames on external Trig In.

**Example:** See SWPSE above.

# 3.4.2.6 Insertion Running Pointer (IRP) (OAH)

The Insertion Running Pointer (IRP) has the same set of instructions as Instruction Set Background Program. To initiate an insertion the user must first load the IRP with the address of the insertion program. Then bit Cl can be cleared in the control register.

- The background program can be interrupted by an insertion command.

- The insertion program cannot be interrupted by any other insertion command. In this case the second insertion request will be delayed until the end of the first one.

- Insertion program starting just before a minor cycle start will delay this one.

- IRP is updated by the on-board processor after executing a BC stop command.

| 3.4.2.7  | Reserved (0CH) |                                                                                                        |

|----------|----------------|--------------------------------------------------------------------------------------------------------|

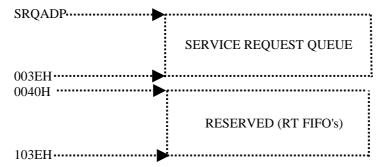

| 3.4.2.8  | LPIQAP (0EH)   | Low priority interrupt queue start address.                                                            |

| 3.4.2.9  | Reserved (10H) |                                                                                                        |

| 3.4.2.10 | HPIQAP (12H)   | High priority interrupt queue start address.                                                           |

| 3.4.2.11 | Reserved (14H) |                                                                                                        |

| 3.4.2.12 | MIQAP (16H)    | Message interrupt queue start address.                                                                 |

| 3.4.2.13 | Reserved (18H) |                                                                                                        |

| 3.4.2.14 | SRQAP (IAH)    | Status report queue start address.                                                                     |

| 3.4.2.15 | Reserved (ICH) |                                                                                                        |

| 3.4.2.16 | RTSTAD (IEH)   | RT simulation table start address.                                                                     |

|          |                | Contains the address of the RT Simulation Tables, which defines the RT status when they are simulated. |

| 3.4.2.17 | Reserved (20H) |                                                                                                        |

| 3.4.2.18 | Reserved (22H) |                                                                                                        |

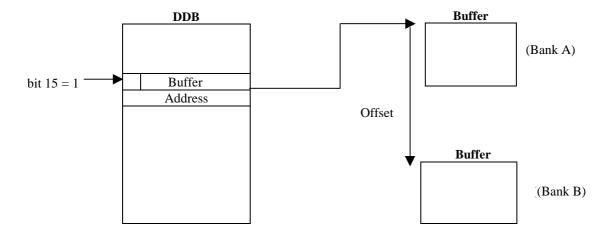

# 3.4.2.19 Toggle Buffer Address Offset (24H)

• MSB = 1 : global toggle enable

$=0 \quad : \quad no \ toggle$  offset  $: \quad 15 \ bits$

| MSB | offset |   |

|-----|--------|---|

| 15  | 14     | 0 |

- For a data buffer, if the toggle feature is selected (bit 15 = 1), the address of the toggle buffer is: (Buffer Address High + Toggle Buffer Offset), Buffer Address Low. [15 bits]

- For further details refer to paragraph 4-3.3.3.

#### 3.4.2.20 Set of Messages Start Address (26H)

- This is the pointer of a 256-word table reserved to the on-board processor to compute the registers Set of Messages.

- For further details refer to paragraph 4-5.2.

#### 3.4.2.21 Global RT Response Time Register (28H)

- This is the response time for all the simulated RT's. Different RT response time can be defined in the error description words.

- LSB =  $l\mu s$

- For some modes, this global RT response time register is not programmable (fixed at 4us);

- 1553B Mode without data

- If the value is less than 4, the on-board processor selects  $4\mu$ S.

# 3.4.2.22 RT No Response Time-Out Register (2AH)

- The programmable RT no response time-out defines the maximum RT response time allowed by the unit to an RT before detecting "NO RESPONSE".

- LSB = 1us.

#### 3.4.2.23 IRQ Selection Register (34H)

| D15 | D14 | D13 | D12 | D11     | D10 | D09     | D08 | D07      | D06 | D05 | D04      | D03 | D02 | D01 | D00 |

|-----|-----|-----|-----|---------|-----|---------|-----|----------|-----|-----|----------|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | Cycling |     | Message |     | HI Queue |     | ie  | LO Queue |     |     |     |     |

|     |     |     |     | 0       | 0   | C       | 0   | 0        | M   | 0   | 0        | Н   | 0   | 0   | L   |

C = If set, a physical INTA interrupt will be generated when a 'Broadcast Synchronise With Data' mode code occurs.

M = If set, a physical INTA interrupt will be generated when a push to the Message Queue occurs

H = If set, a physical INTA interrupt will be generated when a push to the High Priority Queue occurs

L = If set, a physical INTA interrupt will be generated when a push to the Low Priority Queue occurs

#### 3.4.2.24 Test and Set Register and SRQADP (3CH)

These two words are used to automatically manage FIFO's of vector words for each simulated RT. For simulated RTs the "Service Request bit" in the status word can be set and reset by the user. The vector word can be initialised by the user.

After a "Transmit Vector Word" mode command message, the on-board processor automatically resets the service request bit and the vector word.

On the other hand a service request queue is defined to automatically queue words representing (successive) requests for the simulated RTs. This service request queue is 3 words long starting at the initial address in the service request queue address pointer (SRQADP).

For a request, two words are set in the queue as follows:

- 1. RT number: 00000000RRRRRIXR = RT address, X = Priority, BIT 1 = 1.

- 2. Vector word

Two different priorities are available:

X = O High priority X = 1 Low priority

Reading this FIFO, the on-board processor manages each RT two 32-word vector words FIFO's (one per priority). These vector words are then used by the RT simulation. If an RT FIFO is not empty, the on-board processor reads it, then writes the value in RT vector words (RT Simulation Table) and sets the service request bit in the status word.

If a "Transmit Vector Word" mode command message occurs, the on-board processor reads the RT FIFO's

- If empty the on-board processor resets the service request bit and the vector word.

- Otherwise the on-board processor reads the FIFO's and writes this next value in the RT vector word.

High priority vector words are processed before low priority vector words.

The following 4Kbyte block after the service request queue is reserved for the individual RT requesting FIFO's managed by the on-board processor:

To enter a request in the User Requesting Queue, the user must manage the current writing pointer (SRQADP in Base Registers) and control the words pointed at are clear, if these words are non-zero, the queue is full. Reaching the end of the queue the user must restart at the beginning of the queue.

If several user CPUs can enter requests at the same time, it is necessary to share control of SRQADP, using for example the TASR flag with a test and set instruction. To enter a request a CPU must carry out the following procedure:

Test and set the TASR word (MSB bit) and:

- a) If free, the SRQADP is read to define the entry address in the queue.

- If the entry location defined by the SRQADP are clear the two words may be entered in the queue. If these words are non-zero, the queue is full.

- Increments the SRQADP (if the end is reached, reinitialise it to the beginning).

- Resets the TASR.

- b) If not free, waits until free.

#### 3.4.2.25 Reserved (46H)

# 3.4.2.26 PRI/SEC 1553B RT TX Inhibit HI-LO (48H – 4EH)

| HI: |      | RT 30 | <br>RT17 | RT16 |

|-----|------|-------|----------|------|

| LO: | RT15 | RT14  | RT1      | RT0  |

- =0: enable the transmitter

- =1: disable the transmitter

- A bit set defines the specific RT transmitter as inhibited.

- Initialisation by the user (before cold start).

- Disable/enable by corresponding mode command messages.

- The user can <u>modify</u> the inhibit bits in <u>real time</u>.

- The receive function of the simulated RT is never disabled.

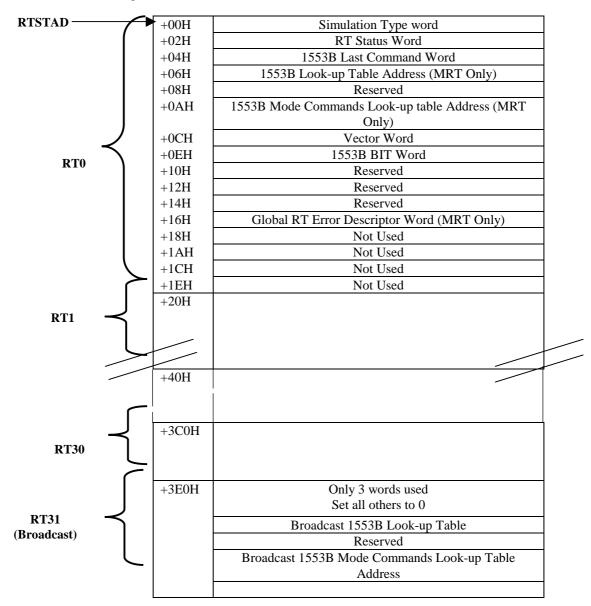

#### 3.5 REMOTE TERMINAL SIMULATION TABLE

For each RT 16 words are used to define and store information concerning RTs. The pointer to this table (RTSTAD) must be a multiple of 20H. Refer to table 3-2.

#### 3.6 REMOTE TERMINAL SIMULATION TABLE

For each RT 16 words are used to define and store information concerning RTs. The pointer to this table (RTSTAD) must be a multiple of 20H. Refer to table 3-2.

Figure 3-2. Remote Terminal Simulation Table

#### 3.6.1 Simulation Type Word

|         | BIT 15 :    | 1 = RT simulated                                           |

|---------|-------------|------------------------------------------------------------|

| Bits    | BIT 14 :    | 1 = Reserved                                               |

| 14 to 0 | BIT 13 :    | 1 = Inhibit transmitter 1553B on primary bus               |

| are for | BIT 12 :    | 1 = Inhibit transmitter 1553B on secondary bus             |

| MRT     | BIT 7 :     | 1 = Errors enabled on primary bus (status word and data)   |

| only    | BIT 6 :     | 1 = Errors enabled on secondary bus (Status word and data) |

|         | BIT 0 :     | 1 = Enable global error injection                          |

|         | other bits: | 0                                                          |

Bits 7 and 6 Enable global RT errors (defined in the RT simulation table) as message-per-message errors (defined in the look-up-tables).

#### 3.6.2 Status Word

Broadcast and message error bits are dynamically updated. Service request bit automatically set by the request files and cleared by the TX vector word mode code command. Busy bit can be set by user to disable data transmission.

# 3.6.3 1553B Last Command Word

Automatically updated (including broadcast), so the TX last command mode code is correctly simulated.

# 3.6.4 1553B Bit Word

For user purposes.

#### NOTES:

- 1. 1553B Mode Commands TX shutdown and override TX shutdown are fully simulated. The status of the transmitters are available to the user in the Base Registers.

- 2. The user can modify the RTs simulation state in real-time.

## 4 BUS CONTROLLER MODE OF OPERATION

#### 4.1 INTRODUCTION

In the Bus Controller mode the Western Avionics IIB-1553-USB unit runs a list of instruction pointed to by the Background Running Pointer defining the bus frame. Each bus message is defined by a Message Descriptor Block (MDD) and the associated data is accessed through a Look-Up Table (LUT) and Data Descriptor Blocks (DDB) the same way as in the Multi-Remote mode. Remote Terminals can simultaneously be simulated. All non-simulated data buffers can be monitored. An internal minor frame duration counter allows autonomous control of cycling frames. Acrylic messages can be inserted on the host request. Insertion instruction lists define sequences of messages to be inserted. Refer to figure 4-1 the Bus Controller Organisation Diagram.

Figure 4-1 Bus Controller Organisation Diagram

# **4.2** MESSAGE DESCRIPTOR BLOCK (MDB)

Each bus message is defined by a message descriptor block as shown in table 4-1.

Table 4-1 Message Descriptor Block

| MBD ADDRESS | MESSAGE NUMBER                       |

|-------------|--------------------------------------|

| +02H        | 1553B Event Mask                     |

| +04H        | Message Type Word                    |

| +06H        | 1553B Message Error Phase Definition |

| +08H        | 1553B Message Error Description Word |

| +0AH        | Address in Look-up Table             |

| +0CH        | Command Word 1                       |

| +0EH        | Command Word 2                       |

| +10H        | Reserved                             |

| +12H        | Reserved                             |

| +14H        | Retry Subroutine Absolute Address    |

| +16H        | Reserved                             |

| +18H        | Inter-message Gap Time               |

| +1AH        | Reserved                             |

| +1CH        | Status Word 1 (received)             |

| +1EH        | Status Word 2 for RT-RT (received)   |

# 4.2.1 Message Number (00H)

The number of the message is used in Message Status Report to identify messages.

# 4.2.2 1553B Event Mask (02H)

A logical AND is carried out with the 1553B event mask and the detected bus events. If the result is <>0 a message status report will occur and a retry if selected.

BIT 15 : Wrong/Both bus error

BIT 14 : No response error

BIT 13 : RT address error

BIT 12 : Transmission error

BIT 11 : Wrong sync error

Bit 10 to 00 : Status bits of RX status word (not including address bits)

NOTE: Transmission error includes: Manchester error, Long or Short word error, Parity error, Word

Count error and Late-Response error.

#### 4.2.3 Message Type Word (04H)

BIT 15 : 1 = 1553B TX on PRI bus BIT 14 : 1 = 1553B TX on SEC bus

BIT 13 : 0 BIT 12 : 0

BIT 11 to 8:

| 11 | 10 | 09 | 08 |                         |             |

|----|----|----|----|-------------------------|-------------|

| 0  | 0  | 0  | 0  | 1553B MODE WITHOUT DATA |             |

| 0  | 0  | 0  | 1  | 1553B MODE WITH DATA    |             |

| 0  | 0  | 1  | 0  | 1553B RT-RT             |             |

| 0  | 0  | 1  | 1  | 1553B BC-RT/RT-BC       |             |

| 0  | 1  | 0  | 0  | Reserved                |             |

| 0  | 1  | 0  | 1  | Reserved                |             |

| 0  | 1  | 1  | 0  | Reserved                |             |

| 0  | 1  | 1  | 1  | Reserved                |             |

|    |    |    |    |                         |             |

| 0  | 0  | 0  | 0  | 1553B MODE WITHOUT DATA | (BROADCAST) |

| 1  | 0  | 0  | 1  | 1553B MODE WITH DATA    | (BROADCAST) |

| 1  | 0  | 1  | 0  | 1553B RT-RT             | (BROADCAST) |

| 1  | 0  | 1  | 1  | 1553B BC-RT             | (BROADCAST) |

| 1  | 1  | 0  | 0  | Reserved                | (BROADCAST) |

| 1  | 1  | 0  | 1  | RECEIVE CLOCK           | (BROADCAST) |

| 1  | 1  | 1  | 0  | Reserved                | (BROADCAST) |

| 1  | 1  | 1  | 1  | Reserved                | (BROADCAST) |

BIT 07 : 1 = Extended Subaddress BIT 06 : 1 = Retry on EVENT

BIT 05 : 1 = Interrupt on EVENT enabled

BIT 04 : 1 = Interrupt on EVENT HI priority queue, 0 = LO priority

BIT 03 : 0 BIT 02 : 0 BIT 01 : 0 BIT 00 : 0

#### **NOTES**:

- 1. If RETRY is enabled and IRQ on EVENT is disabled the RETRY will still take place.

- Broadcast Receive Clock is a special message used for transmitting the 32-bit clock as data. This message type only requires an MBD to define the command word and the inter-message gap. No queue, interrupt or buffer control is carried out. The transmitted message will be the command word defined by the MDB followed by two data words, Clock Value HI and Clock Value LO (clock value at the end message on the bus).

- 3. The transmission of a Broadcast Synchronise with Data mode code using the 1553B mode with data broadcast message type will cause cycling interrupt to be generated (if enabled) and the associated data word defined in the data buffer will be stored in the cycling interrupt base register (40H).

## 4.2.4 1553B Message Error Phase Definition (06H)

The following word defines the location of errors that can be injected into the 1553B message.

D15 D14 D13 D12 D11 D10 D09 D08 D07 D06 D05 D04 D03 D02 D01 D00 0 0 0 0 0 0 0 0 X X X

XXX = 000 => Error Injection Disabled

XXX = 001 => Inject Error in 1st BC TX (Initial BC message)

XXX = 011 => Inject Error in 1st RT SIM (lst RT response)

XXX = 100 => Inject Error on 2nd RT SIM (2nd RT-RT response)

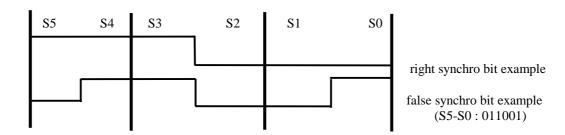

#### 4.2.5 1553B Message Error Description Word (08H)

The following word defines the errors that can be injected into the 1553B message.

D14 D13 D12 D11 D10 D09 D08 D07 D06 D05 D04 D03 D02 D01 D00 X X X X X X X X X X X X

$TTT = 000 \Rightarrow Modulation Error$

WWWWWW = Word Number For Modulation Error

$0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 0 \quad = \quad \text{Parity error}$

0 S5 S4 S3 S2 S1 S0 = Synchro Pattern Error 1 0 B4 B3 B2 B1 B0 = Manchester Bit Error

$1 \quad 1 \quad L4 \quad L3 \quad L2 \quad L1 \quad L0 = Word Length Error$

TTT = 001 => Wrong Bus Error

$TTT = 010 \Rightarrow Both Bus Error$

XXXXXXXXXXXXX = 000000000000000

TTT = 011 => Word Count Error

XXXXXXXXXXXXXX = 000000PCCCCCC

P = Word Count Error Polarity 0 = Word Count Error +VE

1 = Word Count Error -VE

CCCCCC = Word Count Error Value (Allows +/- 64 Words)

TTT = 100 => Response Time Error

XXXXXXXXXXXXXX = 000000000RRRRR

RRRR = Unique Response Time for simulated RT in uS.

TTT = 101 => Illegal Command (Not applicable for BC Mode)

TTT = 110 => Extended Subaddress (Not applicable for BC Mode)

XXXXXXXXXXXXX = 000000000000000

TTT = 111 => Resync. System Clock (Not applicable for BC Mode)

XXXXXXXXXXXXX = 00000000000000

**NOTES:** 1. Word Number : For the first word of the message (command or

status) WWWWWW = 000000.

2. Synchro Pattern Error: Defines a specific synchro bit, each Si defines

the level for 500ns duration (at least 1 bit of

S5 - S0 must be set).

3. Manchester Bit Error : B4-B0 defines the bit position in the word

for the error

4. Word Length Error : L4-L0 defines the number of bits in the word.

**NOTE:** This count has an offset of 1 such that a value of 01111 will result on a valid word with a data bit count of 16.

Wrong bus error

Both busses error

RT response on the wrong bus

RT response on both busses

• Response time error : RRRRR replaces the global RT response time

(LSB = 1 uS)

• Illegal command : Reserved for MRT only

#### 4.2.6 Address in Look-Up Table (0AH)

This will contain the address in the look-up table for the DDB pointer. (See figure 4-1).

#### **4.2.7 Command Word 1 (0CH)**

First Command Word.

# 4.2.8 Command Word 2 (0EH)

Second Command Word (RT-RT 1553B).

# 4.2.9 Retry Subroutine Absolute Address (14H)

On completion of a message, if an Event defined by the Mask has occurred and the Retry Event is enabled, the Subroutine defined by this absolute address will be called.

**NOTES** 1. The retry subroutine must be terminated by the RTS instruction to return execution back to the main background or insertion program.

2. This feature can be used for immediate insertion of Acyclic messages or retry of the same message on the alternate bus.

#### 4.2.10 Inter-message Gap Time (18H)

• Gap between the end of this message and the 1553B line and the beginning of the next one (next MDB).

• LSB = 0.1 uS.

# **4.2.11** Status Word 1 (ICH)

First RX Status Word in the message. If the BC detects no response error, this value will be updated with FFFFH.

# **4.2.12** Status Word 2 (IEH)

Second RX Status Word in the message (RT-RT). If the BC detects a no response error from the second RT, this value will be updated with FFFFH.

# 4.3 DATA BUFFERS SIMULATION AND MONITORING

The Western Avionics IIB-1553-USB unit processes all the data buffers running on the 1553B lines. Data buffers to be issued by the BC or the simulated RTs are transmitted by the Western Avionics IIB-1553-USB unit, all others can be monitored. A multiple data buffering structure is implemented.

These paths use a look-up-table and data descriptor block.

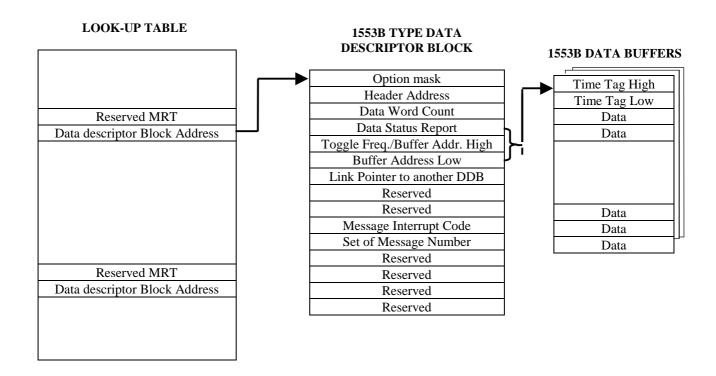

Refer to figure 4-2 Data Buffers Simulation and Monitoring.

Figure 4-2. Data Buffers Simulation and Monitoring

# 4.3.1 Look-Up-Table

The sixth word of a message descriptor block points to a double word in the look-up-table, that contains the address of a 1553B data descriptor block. An identical architecture is defined in MRT mode, but using 1553B subaddresses to point into the look-up-table.

Look-up Table Address : Error Injection Word (MRT only).

02H : DDB Address/Extended-Subaddress look-up table address.

# 4.3.2 Data Descriptor Block

A data descriptor block is associated with each data message, this 16-word set defines the data buffering and associated queue control information. Interrupt selection is defined in the option mask word; interrupt on correct or erroneous message, or after a set of different messages, priority of interrupt (three different available, one interrupt only per message).

The data word count contains the data word count expected by the user. The Western Avionics IIB-1553-USB processor compares this word count with real data word count transmitted on the bus and writes the difference if any in the data status report word. This last word also contains the status flag of the transmission; message received correct or with error, message running. The most significant byte of data buffer address can be used to enable toggled buffer control; toggle on beginning of each minor frame or on multiple cycles of this minor frame. This allows user software synchronised on the frame cycle to always access the correct buffer. The set of message interrupt features provides the possibility to send an interrupt after the last message of the set of messages. It is to be used when the frame sequence is not purely repetitive. Up to 128 different sets of messages from 2 to 16 messages each can be defined. Refer to table 4-2.

Error injection on 1553B data words is defined in the message descriptor blocks.

+1CH

+1EH

DDB ADDRESS **OPTION MASK** +02HHeader Address +04H**Data Word Count** +06HData Status Report +08HToggle Frequency and Buffer Address HI +0AH Buffer Address LO +0CHLink Pointer to Address of another DDB Address of Modify Word +0EHValue to Write +10H+12HMessage Interrupt Code +14HSet of Message Number Message Indicator in the Set of Messages +16H+18HReserved +1AHReserved

Reserved

Reserved

Table 4-2 Data Descriptor Block

# **4.3.2.1** Option Mask (00H)

```

BIT 15

1 = Interrupt on Correct Message

1 = Interrupt on Error Message

BIT 14

BIT 13

1 = HI/LO Priority Queue (0 = LO, 1 = HI)

1 = Interrupt on Set of Messages

BIT 12

1 = Message Interrupt (If Message Correct)

BIT 11

1 = Link only on Correct Message

BIT 10

BIT 09

1 = Link to New DDB Enabled

BIT 08

1 = Modify Word Enabled

BIT 07

0

BIT 06

0

0

BIT 05

Header Word Count

BIT 04 to 00

```

# 4.3.2.2 Data Status Report (06H)

```

BIT 15 to 14 00 = Good Message

01 = Message Running

10 = Error Message

BIT 13 to 00 Signed Wordcount Error. 0 = No Wordcount Error

NOTE: The wordcount error is calculated as follows:

TX Wordcount = Command Wordcount - (DDB Count + Header Count)

RX Wordcount = Wordcount Received - (DDB Count + Header Count)

```

# 4.3.2.3 Toggle Frequency and Buffer Address HI (08H)

The word +24H in Base Registers defines if the data buffer toggle feature is enabled and also the toggle offset:

• MSB = 1 : global toggle enabled = 0 : no toggle

• offset : 15 bits

| MSB |    | OFFSET |   |

|-----|----|--------|---|

| 15  | 14 |        | 0 |

The 5th word in a DDB enables the toggle feature for the corresponding data buffer and the toggle frequency:

When global toggle is enabled, for a data buffer if the toggle feature is selected (bit 15 = 1) the address of the toggle buffer is:

(Buffer Address High + Toggle Buffer Offset (15 bits)), Buffer Address Low.

The toggle is synchronised on the minor frame counter register, which is incremented on each minor cycle restart.

• The on-board processor stores the data buffer in bank A or B depending on the number of the running minor cycle and the frequency indicator of the message.

| Minor Cycle<br>(frequency F) | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | В | С |  |

|------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|--|

| F Hz.                        | A | В | A | В | Α | В | A | В | A | В | A | В | A |  |

| F/2 Hz                       | A | Α | В | В | Α | Α | В | В | В | A | В | В | A |  |

| F/4 Hz                       | A | A | A | Α | В | В | В | В | Α | A | A | A | В |  |

| F/8 Hz                       | A | Α | A | A | Α | A | A | Α | В | В | В | В | В |  |

# 4.3.2.4 Link Pointer to New DDB (0CH)

If the message is good or bit 10 of the option mask is clear and bit 9 of the option mask is set the value in this location will replace the original DDB address in the look-up table. This feature defines a different DDB for the next occurrence of the same message.

# 4.3.2.5 Address of Modify Word/Value to Write (0EH-10H)

After the message is complete and bit 8 of the option mask is set the Value to Write is written in the address defined by the contents of 0EH. (Action is limited to the first 64Kbytes of the memory).

#### 4.3.2.6 Extended Sub-Address

To enable the extended sub-address feature see the MDB type word. When enabled the value of the DDB address in the look-up-table is in fact a pointer for a further look-up-table called the extended look-up-table. The on-board processor uses the 1553B byte of the first data word received (multiplied by four) to calculate an offset in the extended look-up-table to find the true DDB address word. Therefore, the DDB and data buffer used is defined by the value of the first 1553B RX data word.

+ offset --->: Reserved MRT +02H : DDB address

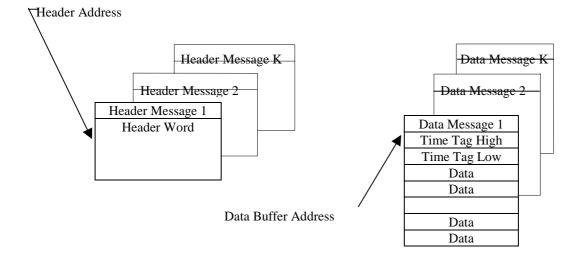

#### 4.3.3 Data Buffers

Data buffers are pointed to by the buffer address word contained in the data descriptor blocks. The address of the toggled buffer is calculated by adding the global toggle offset to the data buffer address value in the DDB. The first two words of a data buffer are updated with the value of the local clock at the beginning of the message.

1553B data buffers can be stored as follows:

- The standard way data words behind the time-tag words.

- A particular way allowing the user to store header words of the data message in a different buffer from the following data words.

The header option and the number of header words are defined in the option mask.

| DB ADDRESS | 1553B BUFFER    |

|------------|-----------------|

| +00H       | Time Tag HI     |

| +02H       | Time Tag LO     |

| +04H       | Data            |

| +06H       | Data            |

| +08H       | Data            |

| +0AH       | Data            |

| +0CH       | "               |

| "          | "               |

| "          | with or without |

|            | Header Word     |

|            | "               |

|            | "               |

|            | "               |

Table 4-3 Data Buffers

# 4.4 MODE COMMANDS

In Bus Controller mode the Western Avionics IIB-1553-USB unit can transmit all mode command messages. For each mode command message, data descriptor blocks pointed through the look-up table allow the definition of interrupt requests or associated data word address storage. If such a command is directed to an on-board simulated RT, the corresponding actions are made on the RT simulation table:

- Transmit RT status word, last command word, bit word.

- Inhibit or override inhibit

#### Examples:

- a) Synchronise with Data Word: